#### **GENERAL DESCRIPTION**

The ES1878 *Audio*Drive<sup>®</sup> is a mixed-signal single-chip solution that adds 16-bit stereo sound and FM music synthesis to notebook computers. The ES1878 includes an embedded microprocessor, a 20-voice ESFM<sup>™</sup> music synthesizer, 16-bit stereo ADC and DACs, optional ISA Plug and Play (PnP) support, hardware master volume control, DMA control logic with FIFO, ISA bus interface logic, general-purpose I/O, and digital dual game port. The ES1878 also incorporates three serial ports which allow interfacing with external DSP, wavetable, and MIDI (MPU-401 UART Mode compatible). In addition, the ES1878 offers I<sup>2</sup>S Zoom Video interface and support for the optional ES978 Expansion Audio Mixer in docking stations.

A 4-wire expansion analog bus and 2-wire serial control bus connect the ES1878 with the ES978, allowing the ES1878 to engage the docking station's audio resources when docked.

The ES1878 *Audio*Drive<sup>®</sup> can record, compress, and play back voice, sound, and music with built-in mixer controls. Using two high-performance DMA channels, the ES1878 supports full-duplex operation for simultaneous record and playback. The ESFM<sup>™</sup> synthesizer has extended capabilities within native mode operation providing superior sound and power down capabilities. The ES1878 is register compatible with Yamaha's OPL3<sup>™</sup> FM synthesizer.

The ES1878 *Audio*Drive<sup>®</sup> supports ISA Plug and Play with configuration for 4 logical devices: configuration device, audio plus ESFM<sup>™</sup>, game port, and MPU-401. The ES1878 also supports an optional non-PnP (BIOS Plug and Play) configuration for the Intel<sup>®</sup> Mobile Triton chipset in which the PCA-ISA bridge features Subtractive Decode and Positive Decode Modes.

The MPU-401 serial port is for interfacing with an external MIDI device. The digital dual game port supports two joysticks with hardware timing which uses less CPU overhead and improves system performance.

A DSP serial interface in the ES1878 allows an external DSP to take over ADC or DAC resources. A wavetable serial port allows the ES1878 to interface with either the ES689 or ES690 wavetables. I/O address, DMA, and interrupt selection can be controlled through system software or Plug and Play.

Advanced Power Management (APM) features include suspend and resume from disk.

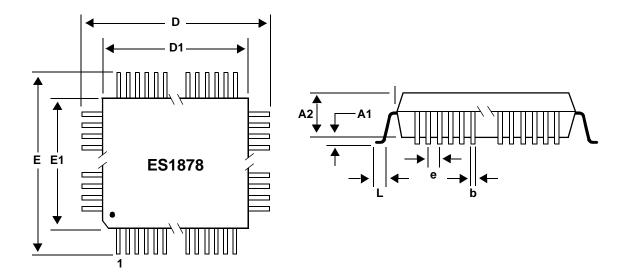

The ES1878 is available in an industry-standard 100-pin Small Quad Flat Pack (SQFP) package.

#### FEATURE HIGHLIGHTS

- Single, mixed-signal, 16-bit stereo VLSI chip for digital audio

- High-quality, 20-voice ESFM<sup>™</sup> music synthesizer; patents pending

- Supports ES978 Expansion Audio Mixer chip

- Full Plug and Play (PnP) capability

#### **Record and Playback Features**

- Record, compress, and play back voice, sound, and music

- 16-bit stereo CODEC

- 2 additional DACs for digital audio, music synthesis, and I<sup>2</sup>S Zoom Video

- Programmable sample rates from 4 kHz to 44.1 kHz for record and playback

- Patented ESPCM® compression

- Full-duplex operation for simultaneous record and playback

- 6-bit (64 step) software volume control

- 2-button or 3-button hardware master volume control for up, down, and mute

#### Inputs/Outputs

- Stereo inputs for LINE, AUXA and AUXB, and a mono input for MIC

- MIDI serial port compatible with MPU-401 UART Mode

- Serial port interface for external DSP, which optionally controls full-duplex operation

- Supports up to 7 general-purpose inputs (GPIs) and 7 general-purpose outputs (GPOs) that can be slaved with corresponding pins of the Expansion Audio Mixer

- ESS high-performance digital dual game port with hardware timing

- High-performance DMA supports demand transfer and F-type

- Software address mapping, DMA, and IRQ selections for motherboard implementation

# ESS Technology, Inc.

- I<sup>2</sup>S Zoom Video port interface for MPEG audio with sample rates up to 48 kHz

- Wavetable serial port interface for ES689/ES690 to access the music DAC

- PC speaker input/output with volume control

- DSP serial interface

## Interfaces to Expansion Audio Mixer (ES978)

- Simple hot-docking interface for ES978 Expansion Audio Mixer

- Two-wire digital status and data communication between ES1878 and ES978 supports register shadowing with worst case latency of approximately 140 microseconds

- Two pairs of on-chip analog differential signals for audio I/O with ES978 Expansion Audio Mixer

### **Mixer Features**

- 6-channel stereo mixer inputs for line, auxiliary A (CD audio), auxiliary B, digital audio (wave files), music synthesizer, I<sup>2</sup>S Zoom Video port, plus a mono channel mixer input for a microphone

- Programmable 6-bit logarithmic master volume control

## Plug and Play (PnP) Features

- On-chip PnP support for audio, joystick port, FM, and MPU-401

- Software address mapping, four DMA and six IRQ selections for motherboard implementation

#### Power

- Advanced Power Management supports suspend/ resume from disk

- Supports 3.3 or 5.0 V operation

### Compatibility

- Supports PC games in Sound Blaster<sup>™</sup> and Sound Blaster<sup>™</sup> Pro modes

- Microsoft<sup>®</sup> Windows<sup>™</sup> Sound System<sup>®</sup>

### **Operating Systems**

- Microsoft Windows<sup>®</sup>95

- Microsoft Windows<sup>™</sup> 3.1

- Microsoft Windows for Workgroups<sup>™</sup>

- Microsoft Windows NT<sup>™</sup> 3.51 & 4.0

- IBM<sup>®</sup> OS/2<sup>®</sup> Warp<sup>™</sup>

### **COPYRIGHTS AND TRADEMARKS**

### **Copyright Notice**

Copyright © 1995–1996 by ESS Technology, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc.

### Disclaimer

Information supplied by ESS Technology is believed to be accurate and reliable. However, ESS Technology assumes no responsibility for use of this information, nor for any errors contained herein.

Products in this document may be covered by U.S. Patent 4,214,125 and others; other patents pending.

### Trademarks

AudioDrive® and ESPCM® are registered trademarks of ESS Technology, Inc.

ESFM<sup>™</sup> is a trademark of ESS Technology, Inc.

All other brand names and product names mentioned in this document are trademarks or registered trademarks of their respective owners and are used for identification purposes only.

### **Revision History**

This ES1878 *Audio*Drive<sup>®</sup> Data Sheet replaces the ES1878 *Audio*Drive<sup>®</sup> Preliminary Design Guide/Data Sheet.

### CONTENTS

| GENERAL DESCRIPTION                             |          |

|-------------------------------------------------|----------|

| FEATURE HIGHLIGHTS                              | . 1      |

| COPYRIGHTS AND TRADEMARKS                       | . 2      |

| CONTENTS                                        | . 3      |

| FIGURES                                         |          |

| TABLES                                          |          |

| FUNCTIONAL BLOCK DIAGRAM                        |          |

| MIXER SCHEMATIC BLOCK DIAGRAM                   |          |

| Subsystems Description                          |          |

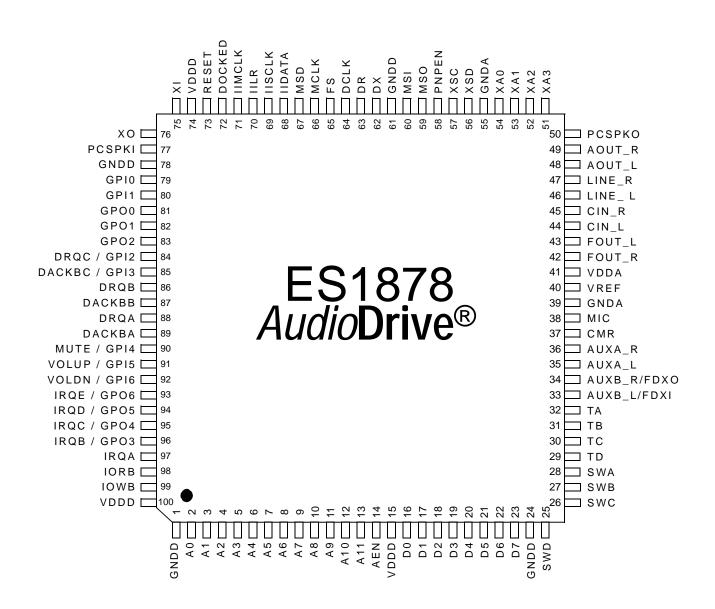

| PINOUT DIAGRAM                                  |          |

| PIN DESCRIPTIONS                                | . U<br>Q |

| TYPICAL APPLICATION                             |          |

| ANALOG HARDWARE INTERFACE                       |          |

|                                                 |          |

| Reference Generator                             |          |

| Switch-Capacitor Filter                         |          |

|                                                 |          |

| DIGITAL HARDWARE INTERFACE                      |          |

| ISA Bus Interface                               |          |

| DMA Interface                                   |          |

| DRQ Latch Feature                               |          |

| Interrupts                                      |          |

| Interrupt Sources                               |          |

| Interrupt Status Register (ISR)                 |          |

| Interrupt Mask Register (IMR)                   |          |

| Sharing Interrupts                              |          |

| PERIPHERAL INTERFACING                          |          |

| I <sup>2</sup> S Serial Interface               |          |

| I <sup>2</sup> S Serial Interface Format Select |          |

| I <sup>2</sup> S Serial Interface Timing        |          |

| MPU-401 Interface                               |          |

| MIDI                                            |          |

| Wavetable Interface                             |          |

| DSP Interface                                   |          |

| DSP Interface Serial Data Format                |          |

| Game/Joystick Interface                         |          |

| Joystick/MIDI External Interface Connector      |          |

| ES978 Interface                                 | 20       |

| Docking Status                                  | 20       |

| Playback Mode                                   | 20       |

| Record Mode                                     |          |

| No ES978 – Differential AOUT Mode               | 21       |

| Mono Full-Duplex Mode                           |          |

| Power Management                                |          |

| Expansion Audio Interface – Digital             |          |

| Expansion Audio Interface – Analog              |          |

| Mono FDXI and FDXO                              |          |

| General-Purpose I/O                             |          |

| GPI/O Registers                                 |          |

| Master Volume                                   | -        |

| Hardware Volume Controls                        |          |

| PC Speaker                                      |          |

|                                                 |          |

| CONFIGURATION DESCRIPTION                       |          |

| Plug and Play (PnP) Configuration               | 25       |

| Using ISA PnP Mode (PNPEN=1)                    | 25       |

| Accessing Non-PnP Mode (PNPEN=0)                  | 25   |

|---------------------------------------------------|------|

| Access to PnP Registers                           |      |

| "Bypass Key"                                      |      |

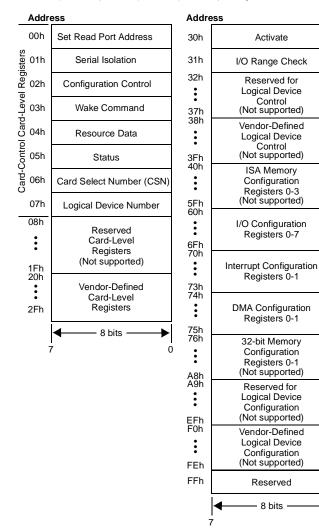

| PnP Configuration Registers                       |      |

| Example                                           | 26   |

| Register Set                                      |      |

| Card-Control Card-Level Registers (00h – 07h)     |      |

| Vendor-Defined Card-Level Registers (20h – 2Fh) . |      |

| Logical Devices                                   |      |

| Device Configuration                              |      |

| Configuring IRQ, DMA, and GPI/O Pins              |      |

| I/O PORTS                                         |      |

| Port Descriptions                                 |      |

|                                                   |      |

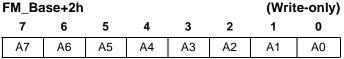

| FM Device                                         |      |

| MPU-401 Device                                    |      |

|                                                   |      |

| PROGRAMMING THE ES1878                            |      |

| Identifying the ES1878                            |      |

| Resetting the Audio Device via Software           |      |

| Modes of Operation                                |      |

| Compatibility Mode Programming                    |      |

| Extended Mode Programming                         |      |

| Accessing the ES1878 Extended Registers           |      |

| Writing ES1878 Internal Registers                 |      |

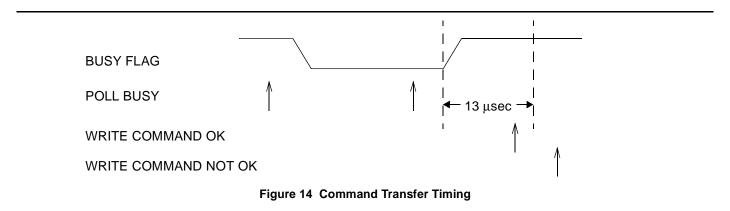

| Command/Data Handshaking Protocol                 |      |

| Writing Commands to the ES1878                    |      |

| Reading the Read Data Buffer of the ES1878        |      |

| Programming the ES1878 Mixer                      |      |

| Extended Access to Mic Mix Volume                 |      |

| Extended Access to ADC Source Select              |      |

| Programming the FIFO for DMA Playback             |      |

| Programming the FIFO for DMA Record               |      |

| Programming the FIFO for I/O Block Transfer       | . 47 |

| Full-Duplex DMA Mode (No DSP Serial Port)         | 48   |

| I <sup>2</sup> S Serial Interface Software Enable | 48   |

| I <sup>2</sup> S DAC Volume Control               | 48   |

| AUDIO REGISTERS                                   | 49   |

| Types of Register Access                          | 49   |

| Mixer Registers                                   |      |

| Sound Blaster Compatible Mixer Registers          | 49   |

| Sound Blaster Pro Master Volume Emulation         |      |

| ESS Mixer Registers                               |      |

| Extension Registers                               |      |

| AUDIO PROCESSOR COMMAND SUMMARY                   |      |

| POWER MANAGEMENT                                  |      |

| Power Management Characteristics                  |      |

| Mode Transitions                                  |      |

| BIOS Power Management                             |      |

| Suspend-to-Disk / Resume-from-Disk                |      |

| DMA and Interrupts During Suspend-to-Disk         |      |

| TIMING DIAGRAMS                                   |      |

| ELECTRICAL CHARACTERISTICS                        |      |

| Absolute Maximum Ratings                          |      |

| Thermal Characteristics                           | 67   |

## ESS Technology, Inc.

| Operating Condition                      | 37 |

|------------------------------------------|----|

| DC Electrical Characteristics            | 37 |

| Power Management Characteristics         | 38 |

| MECHANICAL DIMENSIONS                    | 39 |

| APPENDIX A: ES1878 INTERNAL PNP RESOURCE |    |

| ROM                                      | 70 |

| APPENDIX B: ES689/ES690 DIGITAL SERIAL   |    |

### FIGURES

| Figure 1 ES1878 Functional Block Diagram           | 5 |

|----------------------------------------------------|---|

| Figure 2 ES1878 Mixer Schematic Block Diagram6     | 6 |

| Figure 3 ES1878 Pinout                             | 8 |

| Figure 4 ES1878 Typical Application                | 2 |

| Figure 5 Reference Generator Pin Diagram           |   |

| Figure 6 Switch-Capacitor Filter Pin Diagram13     |   |

| Figure 7 DRQ Latch14                               | 4 |

| Figure 8 I <sup>2</sup> S Implementation in ES1878 |   |

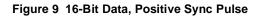

| Figure 9 16-Bit Data, Positive Sync Pulse18        |   |

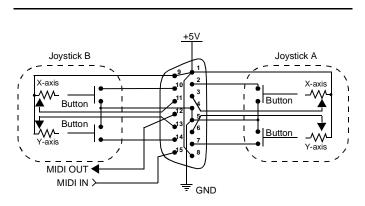

| Figure 10 Dual Joystick/MIDI Connector             |   |

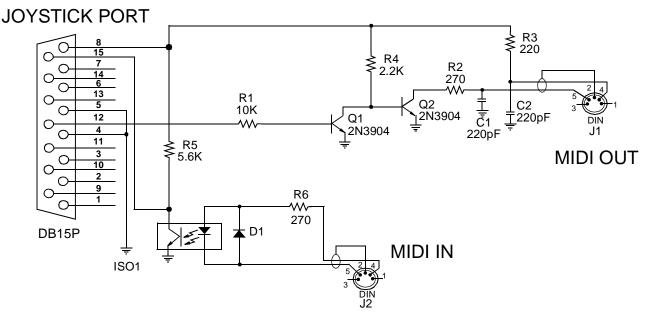

| Figure 11 MIDI Serial Interface                    |   |

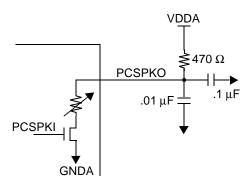

| Figure 12 PC Speaker Volume Circuitry              |   |

| Figure 13 Configuration Register Outline           |   |

| Figure 14 Command Transfer Timing                  |   |

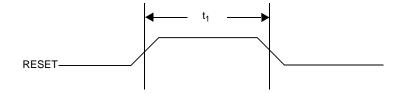

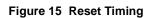

| Figure 15 Reset Timing62                           |   |

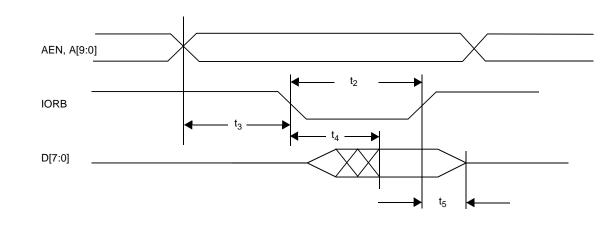

| Figure 16 I/O Read Cycle62                         |   |

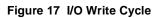

| Figure 17 I/O Write Cycle62                        |   |

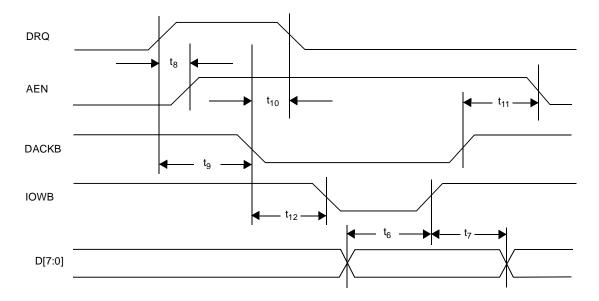

| Figure 18 Compatibility Mode DMA Write Cycle63     | 3 |

|                                                    |   |

### TABLES

| Table 1 Analog Pins                                    |

|--------------------------------------------------------|

| Table 2 Digital Pins                                   |

| Table 3 ES1878 ISA Bus Interface                       |

| Table 4    Wavetable Interface Pins    17              |

| Table 5 DSP Interface Pins                             |

| Table 6 Digital Joystick Read Values    19             |

| Table 7 Download Period                                |

| Table 8 Upload Period Data Configuration               |

| Table 9 Docked Modes for Analog Audio                  |

| Table 10 Logical Device Summary                        |

| Table 11 Configuration Device                          |

| Table 12 I/O Port for Joystick, Audio, FM, and MPU-401 |

| Devices                                                |

| Table 13 Command Sequences for DMA Playback            |

| Table 14    Command Sequence for DMA Record            |

| INTERFACE                                              | 2 |

|--------------------------------------------------------|---|

| APPENDIX C: I <sup>2</sup> S ZV INTERFACE REFERENCE 73 | 3 |

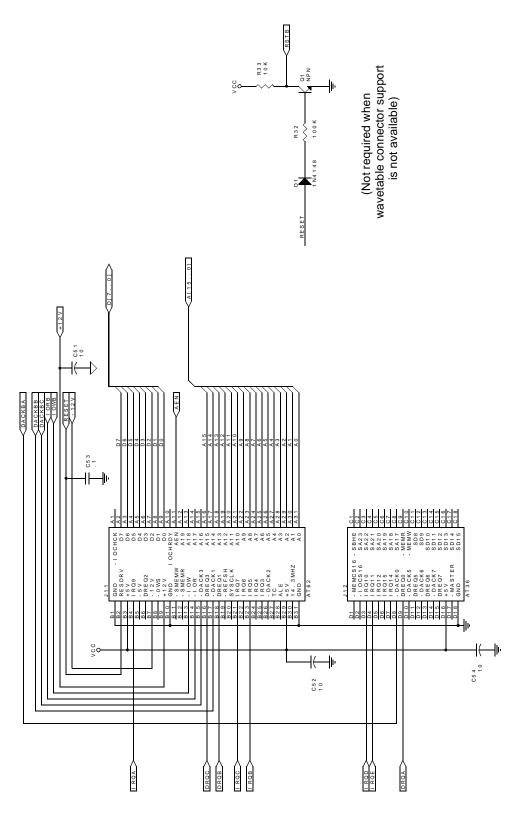

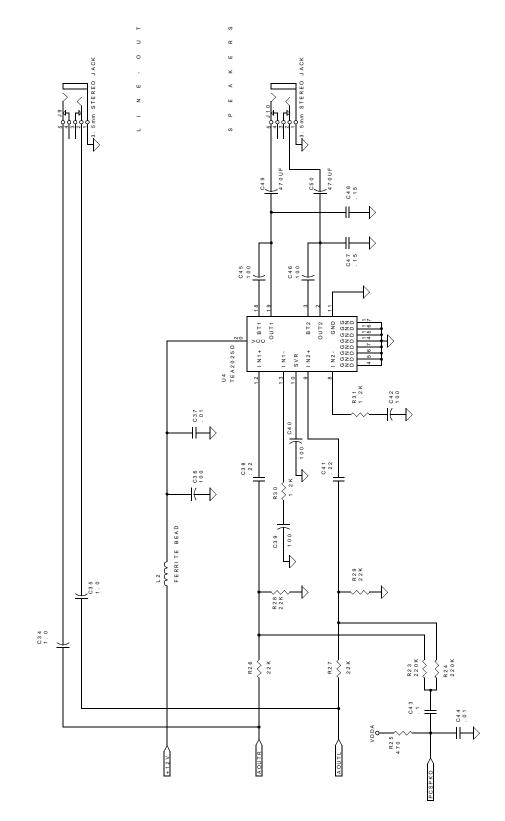

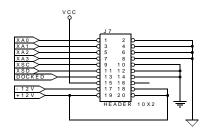

| APPENDIX D: SCHEMATIC EXAMPLES                         | 3 |

| APPENDIX E: LAYOUT GUIDELINES                          | 2 |

| APPENDIX F: ES1878 BILL OF MATERIALS 83                | 3 |

|                                                        |   |

| Figure 19 | Compatibility Mode DMA Read Cycle 63                          |

|-----------|---------------------------------------------------------------|

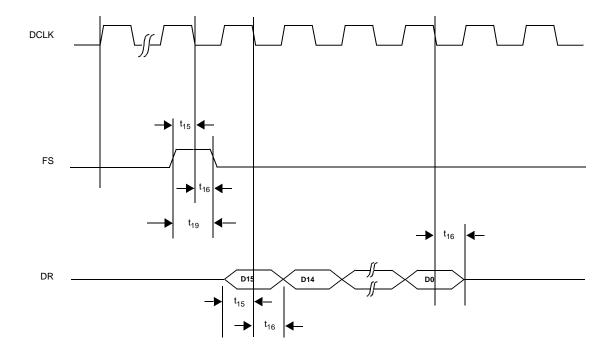

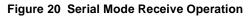

| Figure 20 | Serial Mode Receive Operation 64                              |

| Figure 21 | Serial Mode Transmit Operation 64                             |

| Figure 22 | Serial Input Timing for I <sup>2</sup> S Interface 65         |

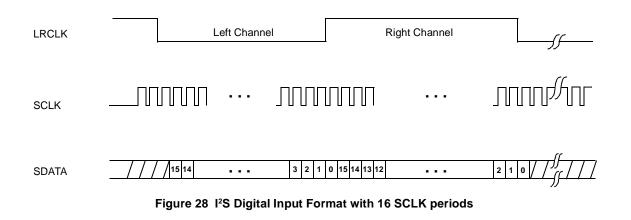

| Figure 23 | I <sup>2</sup> S Digital Input Format with 16 SCLK Periods 65 |

| Figure 24 | ES1878 Physical Dimensions 69                                 |

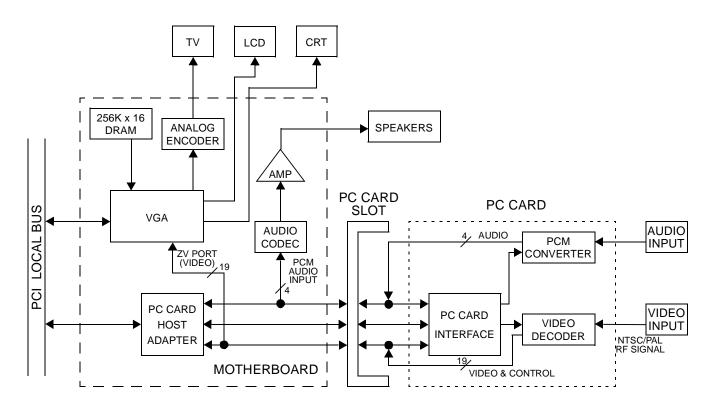

| Figure 25 | Example ZV Port Implementation                                |

| Figure 26 | Typical ZV Port Audio Implementation                          |

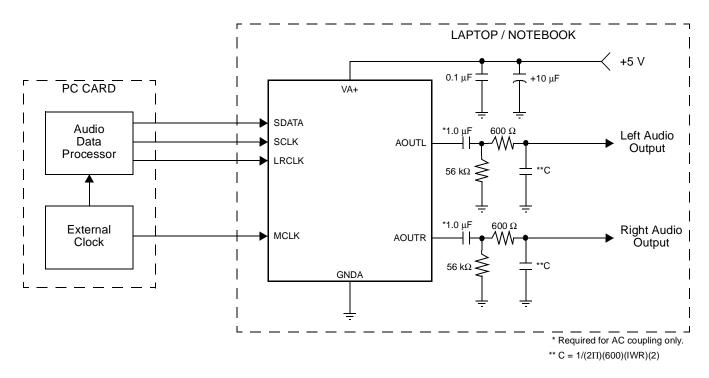

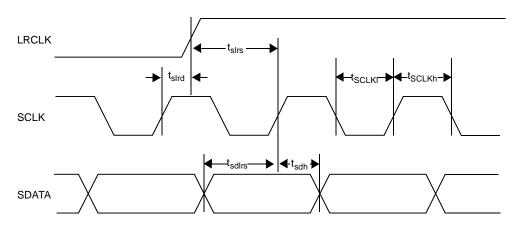

| Figure 27 | Audio Interface Timing 75                                     |

| Figure 28 | I <sup>2</sup> S Digital Input Format with 16 SCLK periods 76 |

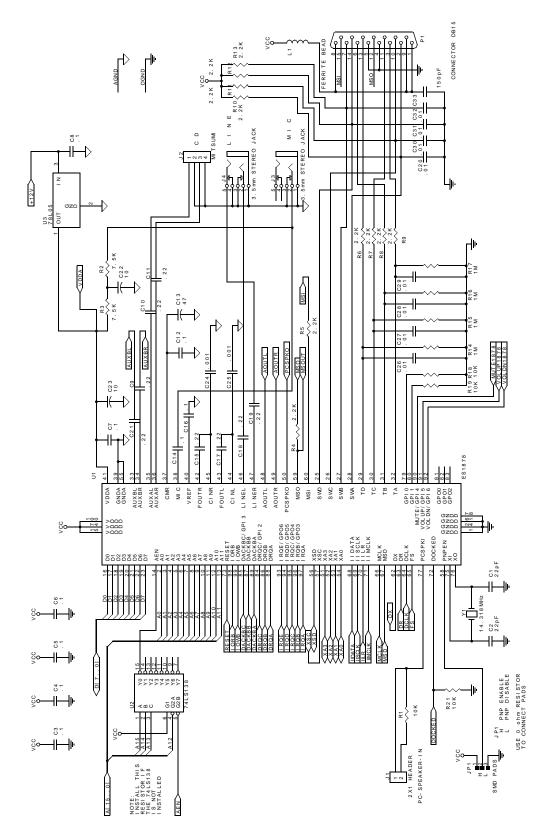

| Figure 29 | ES1878 Schematic                                              |

| Figure 30 | PC Interface                                                  |

| Figure 31 | Amplifier Section 80                                          |

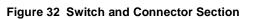

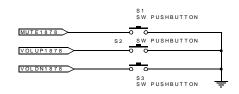

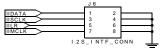

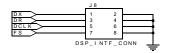

| Figure 32 | Switch and Connector Section 81                               |

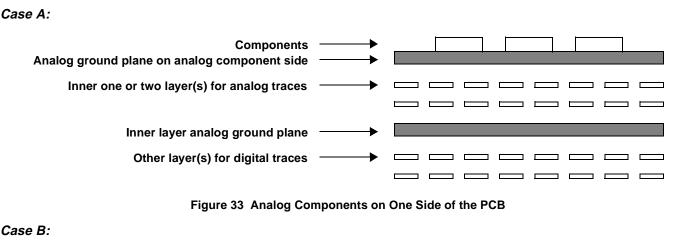

| Figure 33 | Analog Components on One Side of the PCB 82                   |

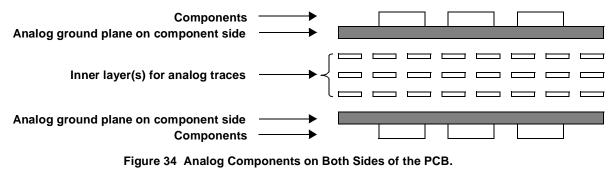

| Figure 34 | Analog Components on Both Sides of the PCB 82                 |

| Table 16<br>Table 17<br>Table 18 | Sound Blaster Compatibility Registers49Sound Blaster Pro Master Volume Emulation50ESS Mixer Registers Summary51Audio Processor Extension Registers56 |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 19                         | Command Summary 59                                                                                                                                   |

| Table 20                         | Power Mode Description 61                                                                                                                            |

| Table 21                         | ES1878 Timing Characteristics                                                                                                                        |

| Table 22                         | Digital Characteristics 67                                                                                                                           |

| Table 23                         | Analog Characteristics                                                                                                                               |

| Table 24                         | Current Consumption for Power Modes 68                                                                                                               |

| Table 25                         | Common Clock Frequencies                                                                                                                             |

| Table 26                         | AC Parameters for Audio Signals 75                                                                                                                   |

| Table 27                         | ZV Port Interface Pin Assignments                                                                                                                    |

| Table 28                         | ES1878 Bill of Materials (BOM) 83                                                                                                                    |

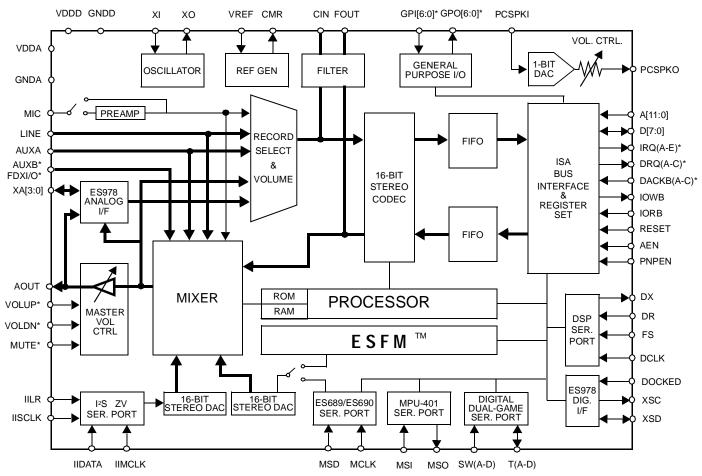

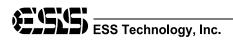

### FUNCTIONAL BLOCK DIAGRAM

\* Some of these pins are shared with other functions.

Figure 1 ES1878 Functional Block Diagram

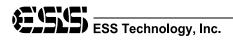

### MIXER SCHEMATIC BLOCK DIAGRAM

Figure 2 ES1878 Mixer Schematic Block Diagram

#### **Subsystems Description**

This section discusses the major subsystems shown in Figure 1.

- **RISC processor** game-compatible audio functions are performed by an embedded microprocessor.

- Oscillator circuitry to support an external crystal.

- **ROM and RAM** firmware ROM and data RAM to the embedded processor.

- FIFO RAM for a 256-byte FIFO data buffer.

- **ISA bus interface** provides interface to ISA bus address, data, and control signals.

- **Digital dual game ports** ESS high-performance digital switches for two joysticks with hardware timing.

- ES978 interface allows support for Expansion Audio Mixer in the docking station using two-wire control signals and four-wire analog bus.

- I<sup>2</sup>S Zoom Video interface supports sample rates up to 48 kHz for MPEG audio.

- MPU-401 serial port asynchronous serial port for MIDI devices such as a wavetable synthesizer or a music keyboard input.

- Wavetable serial port serial port connection from the output of an ES689 or ES690 that eliminates the requirements for an external DAC.

- DSP serial port interface for an optional external DSP for control of the CODEC.

- ESFM<sup>™</sup> music synthesizer high-quality 20-voice FM synthesizer.

- Stereo programmable mixer seven input stereo mixer. Each input is independent left and right 4-bit.

- Line In

- Mic In

- Aux A (CD)

- Aux B (or FDXI)

- Digitized audio (wave files)

- FM/ES689/ES690 music DAC

- I<sup>2</sup>S serial port DAC

- **16-Bit Stereo I<sup>2</sup>S DAC** I<sup>2</sup>S Zoom Video for MPEG audio DAC.

- **16-Bit stereo CODEC** for audio record and playback CODEC.

- **16-Bit stereo music DAC** for ESFM<sup>™</sup> or external wavetable synthesizer.

- 1-Bit DAC for PC speaker digital input.

- Recording source and input volume control input source and volume control for record. The recording source can be selected from one of five choices:

- Mic

- Line

- Aux A (CD)

- Mixer

- FDXI pin (mono full-duplex mode, DSP interface enabled)

In any of the first four cases, the selected recording source may be mixed with audio from the ES978 if the selected source is also enabled in the ES978 and the two chips are docked.

• Output volume and mute control – The master volume is controlled by either programmed I/O or volume control switch inputs. The master volume supports 6 bits per channel plus mute. When docked, the ES1878 first transmits the master volume information to the ES978 mixer before it can take effect.

The 3-pushbutton inputs with internal pull-up devices for up/down/mute can be used to adjust the master volume control.

The state of these pins is logically AND'ed with the state of the corresponding pins of the ES978 when docked. A software-selectable option allows the mute input to be omitted. The mute input is defined as the state when both up and down inputs are low. By default, this feature is disabled.

The hardware volume inputs of the ES1878 can be used as general-purpose inputs (see bits 4 and 5 of Vendor-Defined Card-Level register 25h). They cannot be used as volume control inputs.

- **Reference generator** analog reference voltage generator.

- PC speaker volume control The PC speaker is supported with a 1-bit DAC with volume control. The analog output pin PCSPKO is intended to be externally mixed at the external amplifier. PC speaker audio is not transmitted to the ES978 through the expansion audio interface (XA[3:0]) but is always heard through the portable unit's speakers.

### **PINOUT DIAGRAM**

Figure 3 ES1878 Pinout

### **PIN DESCRIPTIONS**

| Table 1 Analog Pins |                  |            |                                                                                                                                                                     |  |  |  |

|---------------------|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name                | Number           | I/O        | Description                                                                                                                                                         |  |  |  |

| Power and           | Power and Ground |            |                                                                                                                                                                     |  |  |  |

| VDDA                | 41               | I (Pwr)    | Analog power supply, 4.75 V - 5.25 V.                                                                                                                               |  |  |  |

| GNDA                | 39, 55           | I (Pwr)    | Analog ground.                                                                                                                                                      |  |  |  |

| Recording           | g Source a       | nd Input   | Volume Control                                                                                                                                                      |  |  |  |

| LINE_L              | 46               | Ι          | Line input left. 70k ohm pull-up to the CMR pin.                                                                                                                    |  |  |  |

| LINE_R              | 47               | I          | Line input right. 70k ohm pull-up to CMR.                                                                                                                           |  |  |  |

| AUXA_L              | 35               | I          | Aux A (CD) input left. 70k ohm pull-up to CMR.                                                                                                                      |  |  |  |

| AUXA_R              | 36               | I          | Aux A (CD) input right. 70k ohm pull-up to CMR.                                                                                                                     |  |  |  |

| AUXB_L              | 33               | I          | Multipurpose pin, AUXB_L (Aux B input left) or FDXI. 70k ohm pull-up to CMR.                                                                                        |  |  |  |

| AUXB_R              | 34               | I          | Multipurpose pin, AUXB_R (Aux B input left) or FDXO. 70k ohm pull-up to CMR.                                                                                        |  |  |  |

| MIC                 | 38               | I          | Mic input to +26 dB internal preamp. 70k ohm pull-up to CMR.                                                                                                        |  |  |  |

| Output Vo           | lume Cont        | trol and I | Record Monitor                                                                                                                                                      |  |  |  |

| AOUT_L              | 48               | 0          | Analog output left from master volume. This pin can drive a 10k ohm load.                                                                                           |  |  |  |

| AOUT_R              | 49               | 0          | Analog output right from master volume. This pin can drive a 10k ohm load.                                                                                          |  |  |  |

| PCSPKO              | 50               | 0          | PC speaker analog output.                                                                                                                                           |  |  |  |

| ES978 An            | alog Interf      | ace        |                                                                                                                                                                     |  |  |  |

| XA[3:0]             | 51:54            | I/O        | Bidirectional differential transmitter/receivers. Expansion audio bus. These are analog signals that are DC-coupled to the corresponding XA[3:0] pins of the ES978. |  |  |  |

| DSP Inter           | ace              |            |                                                                                                                                                                     |  |  |  |

| FDXI *              | 33               | I          | Multipurpose pin, AUXB_L or FDXI. When used as FDXI with DSP interface, provides a line-level mono input.                                                           |  |  |  |

| FDXO *              | 34               | 0          | Multipurpose pin, AUXB_R or FDXO. When used as FDXO with DSP interface, is a line-level mono output, capable of driving a 5k ohm load.                              |  |  |  |

| Miscellan           | eous Analo       | og Pins    |                                                                                                                                                                     |  |  |  |

| CIN_L               | 44               | I          | Capacitive coupled input left. The input resistance is about 50k ohms.                                                                                              |  |  |  |

| CIN_R               | 45               | I          | Capacitive coupled input right. The input resistance is about 50k ohms.                                                                                             |  |  |  |

| FOUT_L              | 43               | 0          | Filter output left. This pin is normally AC-coupled to CIN_L. The output resistance is about 5k ohms.                                                               |  |  |  |

| FOUT_R              | 42               | 0          | Filter output right. This pin is normally AC-coupled to CIN_R. The output resistance is about 5k ohms.                                                              |  |  |  |

| CMR                 | 37               | I/O        | 2.25 V buffered common mode reference output.                                                                                                                       |  |  |  |

| VREF                | 40               | I/O        | 2.25 V reference generator.                                                                                                                                         |  |  |  |

\* These pins are shared with other functions.

Table 2 Digital Pins

| Table 2     Digital Pins  |                  |              |                                                                                                                                                                                                                                      |  |

|---------------------------|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                      | Number           | I/O          | Description                                                                                                                                                                                                                          |  |

| Power and                 |                  |              |                                                                                                                                                                                                                                      |  |

| VDDD                      | 15, 74, 100      | I (Pwr)      |                                                                                                                                                                                                                                      |  |

| GNDD                      | 1, 24, 61, 78    | I (Pwr)      | Digital ground.                                                                                                                                                                                                                      |  |

| ISA Bus Int               | erface           |              |                                                                                                                                                                                                                                      |  |

| A[11:0]                   | 13:2             | I            | ISA address bus.                                                                                                                                                                                                                     |  |

| AEN                       | 14               | I            | ISA address valid when active-low, DMA when high.                                                                                                                                                                                    |  |

| D[7:0]                    | 23:16            | I/O          | ISA data bus. 24 mA drivers.                                                                                                                                                                                                         |  |

| IOWB                      | 99               | 0            | ISA active-low write strobe.                                                                                                                                                                                                         |  |

| IORB                      | 98               | I            | ISA active-low read strobe.                                                                                                                                                                                                          |  |

| IRQA                      | 97               | O/Hi Z       | ISA interrupt request. 16 mA driver. Connect to IRQ9 if PNPEN = 1.                                                                                                                                                                   |  |

| IRQB *                    | 96               | O/Hi Z       | Multipurpose pin, IRQB or GPO3. Connect to IRQ5 if PNPEN = 1.                                                                                                                                                                        |  |

| IRQC *                    | 95               | O/Hi Z       | Multipurpose pin, IRQC or GPO4. Connect to IRQ7 if PNPEN = 1.                                                                                                                                                                        |  |

| IRQD *                    | 94               | O/Hi Z       | Multipurpose pin, IRQD or GPO5. Connect to IRQ10 if PNPEN = 1.                                                                                                                                                                       |  |

| IRQE *                    | 93               | O/Hi Z       | Multipurpose pin, IRQE or GPO6. Connect to IRQ11 if PNPEN = 1.                                                                                                                                                                       |  |

| DACKBA                    | 89               | I            | ISA active-low DMA acknowledge. Connect to DACK0 if PNPEN = 1.                                                                                                                                                                       |  |

| DRQA                      | 88               | O/Hi Z       | ISA active-high DMA request. Connect to DRQ0 if PNPEN = 1.                                                                                                                                                                           |  |

| DACKBB                    | 87               | 1            | ISA active-low DMA acknowledge. Connect to DACK1 if PNPEN = 1.                                                                                                                                                                       |  |

| DRQB                      | 86               | O/Hi Z       | ISA active-high DMA request. Connect to DRQ1 if PNPEN = 1.                                                                                                                                                                           |  |

| DACKBC *                  | 85               | I            | Multipurpose pin, DACKBC or GPI3. If used as DACKBC, is ISA active-low DMA acknowledge. Connect to DACK3 if PNPEN = 1.                                                                                                               |  |

| DRQC *                    | 84               | I/O/<br>Hi Z | Multipurpose pin. DRQC or GPI2. If used as DRQC, is ISA active-high DMA request.<br>Connect to DRQ3 if PNPEN = 1.                                                                                                                    |  |

| RESET                     | 73               | I            | ISA active-high reset.                                                                                                                                                                                                               |  |

| ES978 Digi                | tal Interface    |              |                                                                                                                                                                                                                                      |  |

| DOCKED                    | 72               | I            | Input that is active-high when the ES1878 is docked to the ES978. This pin has an internal pull-down to GNDD.                                                                                                                        |  |

| XSC                       | 57               | 0            | Expansion serial bus clock and frame sync. High-impedance when DOCKED = 0.                                                                                                                                                           |  |

| XSD                       | 56               | I/O          | Expansion serial bus data I/O. High-impedance when DOCKED = 0.                                                                                                                                                                       |  |

| MPU-401 S                 | erial Port (MIDI | ) and FIF    | Os                                                                                                                                                                                                                                   |  |

| MSO                       | 59               | 0            | MIDI serial output.                                                                                                                                                                                                                  |  |

| MSI                       | 60               | 1            | MIDI serial input. MSI has an internal pull-up to VDDD.                                                                                                                                                                              |  |

| Dual Game Port Joystick   |                  |              |                                                                                                                                                                                                                                      |  |

| SW(A-D)                   |                  |              |                                                                                                                                                                                                                                      |  |

| T(A-D)                    | 32:29            | I/O          | Joystick timers. Use the digital power supply. These pins have internally weak pull-downs t GNDD (> 1M ohms).                                                                                                                        |  |

| I <sup>2</sup> S Interfac | e                |              |                                                                                                                                                                                                                                      |  |

| IISCLK                    | 69               | I            | Serial shift clock for I <sup>2</sup> S interface. This pin has an internal pull-down to GNDD.                                                                                                                                       |  |

| IIDATA                    | 68               | I            | Serial data for I <sup>2</sup> S interface. This pin has an internal pull-down to GNDD.                                                                                                                                              |  |

| IILR                      | 70               | I            | Left/right signal for I <sup>2</sup> S interface. This pin has an internal pull-down to GNDD.                                                                                                                                        |  |

| IIMCLK                    | 71               | I            | Reserved for future oversampling clock for I <sup>2</sup> S interface (software selectable to set x256 x384 or x512 sample rate). This pin has an internal pull-down to GNDD. The current desi using ES1878 does not require IIMCLK. |  |

| Name        | Number          | 1/0          | Description                                                                                                                        |  |

|-------------|-----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| ES689/ES6   | 90 Interface    | 1            |                                                                                                                                    |  |

| MCLK        | 66              | I            | Serial clock input from ES689/ES690.                                                                                               |  |

| MSD         | 67              | I            | Serial data input from ES689/ES690. This pin has an internal pull-down to GNDD.                                                    |  |

| DSP/CODE    | C Interface     | 1            |                                                                                                                                    |  |

| FS          | 65              | I            | Frame sync input. Software programmable to be active-high or active-low. This pin has an internal pull-down to GNDD.               |  |

| DCLK        | 64              | I            | Serial clock input. This pin has an internal pull-down to GNDD.                                                                    |  |

| DR          | 63              | I            | Serial data receive. This pin has an internal pull-down to GNDD.                                                                   |  |

| DX          | 62              | O/Hi Z       | Serial data transmit.                                                                                                              |  |

| External Ha | ardware Volum   | e Contro     | l                                                                                                                                  |  |

| MUTE *      | 90              | I            | Multipurpose pin, MUTE or GPI4. When used as MUTE, is an active-low mute input. This pin has an internal pull-up tp VDDD.          |  |

| VOLDN *     | 92              | I            | Multipurpose pin, VOLDN or GPI6. When used as VOLDN, is an active-low volume-down input. This pin has an internal pull-up to VDDD. |  |

| VOLUP *     | 91              | I            | Multipurpose pin, VOLUP or GPI5. When used as VOLUP, is an active-low volume-up input. This pin has an internal pull-up to VDDD.   |  |

| General-Pu  | rpose/PnP I/O   | Interface    |                                                                                                                                    |  |

| GPI6 *      | 92              | I            | Multipurpose pin, VOLDN or GPI6. If used as GPI6, is general-purpose input 6.                                                      |  |

| GPI5 *      | 91              | I            | Multipurpose pin, VOLUP or GPI5. If used as GPI5, is general-purpose input 5.                                                      |  |

| GPI4 *      | 90              | I            | Multipurpose pin, MUTE or GPI4. If used as GPI4, is general-purpose input 4.                                                       |  |

| GPI3 *      | 85              | I            | Multipurpose pin, DACKBC or PGI3. If used as GPI3, is general-purpose input 3.                                                     |  |

| GPI2 *      | 84              | I/O/<br>Hi Z | Multipurpose pin, DRQC or GPI2. If used as GPI2, is general-purpose input 2.                                                       |  |

| GPI [1:0]   | 80:79           | I            | General-purpose inputs 1:0.                                                                                                        |  |

| GPO6 *      | 93              | 0            | Multipurpose pin, IRQE or GPO6. If used as GPO6, is general-purpose output 6.                                                      |  |

| GPO5 *      | 94              | 0            | Multipurpose pin, IRQD or GPO5. If used as GPO5, is general-purpose output 5.                                                      |  |

| GPO4 *      | 95              | 0            | Multipurpose pin, IRQC or GPO4. If used as GPO4, is general-purpose output 4.                                                      |  |

| GPO3 *      | 96              | 0            | Multipurpose pin, IRQB or GPO3. If used as GPO3, is general-purpose output 3.                                                      |  |

| GPO[2:0]    | 83:81           | 0            | General-purpose outputs 2:0.                                                                                                       |  |

| Miscellane  | ous Digital Pin | s            |                                                                                                                                    |  |

| XI          | 75              | I            | 14.31818 MHz clock input, or external crystal.                                                                                     |  |

| ХО          | 76              | 0            | Output to external 14.31818 MHz crystal.                                                                                           |  |

| PNPEN       | 58              | I            | PnP enable. When high, Plug and Play is enabled; when low, Plug and Play is disabled.                                              |  |

| PCSPKI      | 77              | I            | PC speaker digital input. This pin has an internal pull-down.                                                                      |  |

Table 2 Digital Pins (Continued)

\* These pins are shared with other functions.

### **TYPICAL APPLICATION**

Figure 4 ES1878 Typical Application

### ANALOG HARDWARE INTERFACE

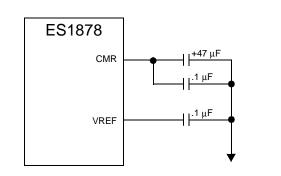

#### **Reference Generator**

Reference generator pins VREF and CMR are connected through bypass capacitors to analog ground.

Figure 5 Reference Generator Pin Diagram

### Switch-Capacitor Filter

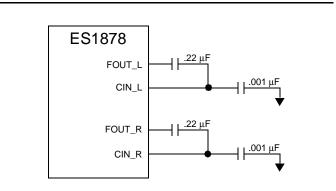

The outputs of the FOUT\_L and FOUT\_R filters must be AC-coupled to the inputs CIN\_L and CIN\_R respectively, which provides for DC blocking and an opportunity for low-pass filtering with capacitors to analog ground at these inputs.

Figure 6 Switch-Capacitor Filter Pin Diagram

### Audio Inputs and Outputs

Analog inputs MIC, stereo LINE, stereo AUXA, and stereo AUXB are to be capacitively coupled to their respective input signals. All have pull-up resistors to CMR.

ES1878 analog outputs AOUT\_L and AOUT\_R are intended to be AC-coupled to an amplifier, volume control potentiometer, or line-level outputs.

### DIGITAL HARDWARE INTERFACE

#### **ISA Bus Interface**

Table 3 shows the pins used to interface the ES1878 with the ISA bus.

| Table 3 ES1878 ISA Bus Interface |        |                                                   |  |  |

|----------------------------------|--------|---------------------------------------------------|--|--|

| Pin                              | I/O    | Description                                       |  |  |

| A[11:0]                          | I      | ISA address bus.                                  |  |  |

| AEN                              | I      | ISA address valid when active low, DMA when high. |  |  |

| D[7:0]                           | I/O    | ISA data bus 24 mA drivers.                       |  |  |

| IOWB                             | 0      | ISA active-low write strobe.                      |  |  |

| IORB                             | I      | ISA active-low read strobe.                       |  |  |

| IRQ(A-E)                         | O/Hi Z | ISA interrupt request. 16 mA driver.              |  |  |

| DACKB(A-C)                       | I      | ISA active-low DMA acknowledge.                   |  |  |

| DRQ(A-C)                         | O/Hi Z | ISA active-high DMA request.                      |  |  |

| RESET                            | I      | ISA active-high reset.                            |  |  |

#### Table 3 ES1878 ISA Bus Interface

### **DMA Interface**

The ES1878 incorporates two DMA channels. There are two sources of DMA requests and two targets for DMA acknowledge:

- Audio 1 The first audio DMA channel. This channel is used for Sound Blaster-compatible DMA, and Extended Mode DMA. It can be used for either record or playback. Ideally, this DMA channel should be assigned to ISA DMA channel 1.

- Audio 2 The second audio DMA channel. This channel is used for audio playback in full-duplex mode. This channel can be mapped to any of the three 8-bit ISA DMA channels: 0, 1, or 3.

The two DMA sources are mapped to the three DMA pin pairs through PnP registers. Also, the three DMA pin pairs are assigned ISA DMA channel numbers by Vendor-Defined Card-Level registers 23h and 24h.

In order for a DRQ output pin to be *driving* (as opposed to *high-impedance*), two things must occur: 1) The PnP register for the DMA of a given device must match the ISA DMA channel number of the pin and 2) the given device must be activated (that is, bit 0 of PnP register 30h must be high).

For detailed information, see the 'Configuration Description' section.

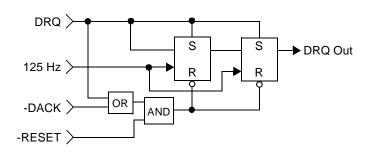

### **DRQ Latch Feature**

The DRQ latch feature is enabled when bit 7 of Vendor-Defined Card-Level register 29h is high (see Figure 7).

If this feature is enabled, each of the three audio DRQs will be latched high until one of the following occurs:

- A DACK low pulse occurs while DRQ is low or if DRQ goes low due to a DACK pulse.

- A hardware reset occurs.

- 8-16 milliseconds elapse while DRQ is low.

Figure 7 DRQ Latch

### Interrupts

#### **Interrupt Sources**

Interrupt sources are mapped to any one of the five interrupt output pins via the PnP registers. A given pin can have zero, one, or more interrupts mapped to it. Each PnP pin is assigned to an ISA interrupt channel number by Vendor-Defined Card-Level PnP registers 20h, 21h, and 22h. These registers are automatically loaded from the 8byte header in the PnP configuration data.

If a given interrupt pin has one or more sources assigned to it, and one or more of those sources is activated (register 30h, bit 0), then the interrupt pin will be active; that is, it will always be driving high or low. Each interrupt also has one or more mask bits that are AND'ed with the interrupt request.

There are four interrupt sources in the ES1878:

- audio 1

- audio 2

- hardware volume

- MPU-401

#### Audio 1

This interrupt is used for the first DMA channel (Sound Blaster-compatible DMA, Extended Mode DMA, and Extended Mode programmed I/O), as well as Sound Blaster-compatible MIDI receive. Extended register B1h controls use of this interrupt for Extended Mode DMA and programmed I/O. This interrupt request is cleared by a hardware or software reset, or by an I/O read from port Audio\_Base+Eh. The interrupt request can be polled by reading from port Audio\_Base+Ch. This interrupt is assigned to an interrupt channel by PnP register 70h of LDN #1.

#### Audio 2

Optional for the second DMA channel. The ES1878 can operate in full-duplex mode using two DMA channels. However, the second DMA channel must have the same sample rate as the first DMA channel. For this reason, it is not necessary to use a separate interrupt for the second DMA channel. This interrupt is masked by bit 6 of Mixer Extension register 7Ah. It can be polled and cleared by reading or writing bit 7 of the same register. This interrupt is assigned to an interrupt channel by PnP register 72h of LDN #1.

#### Hardware Volume

Hardware volume activity interrupt. This interrupt occurs when one of the three hardware volume controls generates a change in status (an event). Bit 1 of Mixer Extension register 64h is the mask bit for this interrupt. The interrupt request can be polled by reading bit 3 of the same register. The interrupt request is cleared by writing any value to register 66h. This interrupt is assigned to an interrupt channel by PnP register 28h. Typically this interrupt, if used, is shared with an audio interrupt.

#### MPU-401

This interrupt is generated when a MIDI byte is received. It goes low when a byte is read from the MIDI FIFO and goes high again quickly if there are additional bytes in the FIFO. The interrupt status is the same as the Read-Data-Available status flag in the MPU-401 Status register. This interrupt is masked by bit 6 of Mixer Extension register 64h and is assigned to an interrupt channel in one of two ways: If the MPU-401 is part of the audio device, then PnP register 28h is used to assign the MPU-401 interrupt. If the MPU-401 is its own logical device, it can also be assigned to an interrupt via PnP register 70h of LDN #3. Both of these methods access the same physical register.

#### Interrupt Status Register (ISR)

Register 6 of the configuration device can be read to quickly find the current state of ES1878 interrupt sources.

- Bit 0 Audio 1 interrupt request

- Bit 1 Audio 2 interrupt request AND'ed with bit 6 of Mixer Extension register 7Ah

- Bit 2 Hardware volume interrupt request AND'd with bit 1 of Mixer Extension register 64h

- Bit 3 MPU-401 receive interrupt request AND'ed with bit 6 of Mixer Extension register 64h

#### Interrupt Mask Register (IMR)

Register 7h of the configuration device can be used to mask any of the seven interrupt sources.

The mask bits can be used to force the interrupt source to be zero, but they do not put the interrupt pin in a highimpedance state. Each bit is AND'ed with the corresponding interrupt source. This register is set to all ones on a hardware reset.

The Interrupt Status Register (ISR) is not affected by the state of the Interrupt Mask Register (IMR). That is, the ISR reflects the status of the interrupt request lines before being masked by the IMR.

The IMR is useful when interrupts are shared. For example, assume that audio 1, audio 2, hardware volume, and MPU-401 all share the same interrupt in Windows<sup>TM</sup>. When returning from Windows to DOS, the hardware volume, MPU-401, and Audio 2 interrupts can be masked by setting the appropriate bits to 0.

A second use of the IMR is within an interrupt handler. The first thing the interrupt handler can do is mask all of the interrupt sources mapped to the interrupt handler. The ISR can then be polled to decide which sources to process. Just before exiting the interrupt handler, the IMR can be restored. If an unprocessed interrupt remains active, it will generate an interrupt request because the interrupt pin was low during the masked period and then went high when the interrupt sources were unmasked. While the interrupts are masked, the individual interrupt sources can change state any number of times without generating a false interrupt request.

#### Interrupt Edge Generator

The interrupt logic has a feature that makes sharing of interrupts easier. If more than one interrupt source shares an interrupt request pin, the interrupt pin is normally the logical OR of the shared interrupt requests. However, if any one interrupt request goes from high to low, circuitry inside the ES1878 will hold the interrupt request pin low briefly to generate a clock edge if one of the other interrupt sources is also high.

#### **Sharing Interrupts**

Plug and Play does not support sharing of interrupts in its resource assignment decision making. If a device wants to share an interrupt with another device that has been assigned an interrupt by PnP, the first device cannot request an interrupt for itself.

A logical device that supports interrupts can be assigned to an interrupt after the PnP sequence is generated by the Windows driver. In this case, the logical device would typically be forced to share an interrupt with the first audio interrupt. For most cases, this is done simply by programming the appropriate PnP register (70h or 72h) for the selected device.

A special case is the hardware volume interrupt. This interrupt source can be assigned to an interrupt through Vendor-Defined Card-Level register 28h, bits 7:4.

A second special case is the MPU-401 interrupt. The MPU-401 device is either part of the audio device or its own logical device. If it is part of the audio device, the interrupt can be assigned by writing to Vendor-Defined Card-Level register 28h, bits 3:0. If the MPU-401 device is its own logical device, it is assigned an interrupt by either Vendor-Defined Card-Level register 28h or LDN#3 register 70h.

### PERIPHERAL INTERFACING

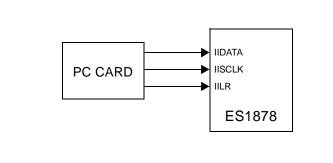

#### **I<sup>2</sup>S Serial Interface**

Three input pins, IIDATA, IISCLK, and IILR, are used for a serial interface between an external device and a stereo DAC within the ES1878. A fourth input, IIMCLK, is reserved for future devices that incorporate oversampling and should be left floating or connected to ground. IIDATA, IISCLK, and IILR can be left floating or connected to ground if the serial interface is not used.

Typical applications of the  $I^2S$  serial interface are MPEG audio, or digital CD audio.

Figure 8 I<sup>2</sup>S Implementation in ES1878

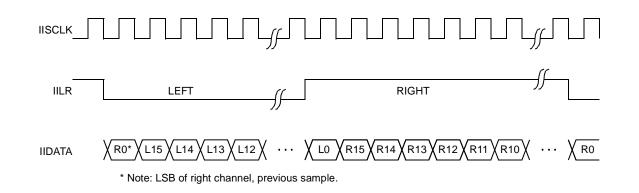

#### I<sup>2</sup>S Serial Interface Format Select

This serial interface supports two different formats: ES689/ ES690 two-wire serial interface, or I<sup>2</sup>S. When used in the ES689/ES690 format, IIDATA is the serial data and IISCLK is the bit clock. The IILR input is not used and can be left floating or connected to ground. Vendor-Defined Card-Level register 29h bits 5 and 4 select the format (this register is accessed through the configuration device). See Vendor-Defined Card-Level register 29h in the 'Configuration Description' section for more detailed information.

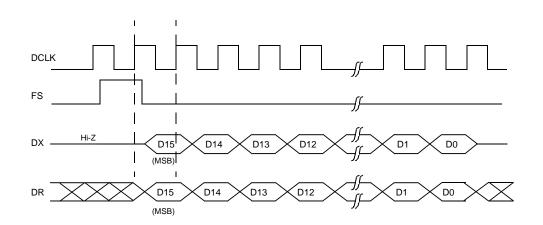

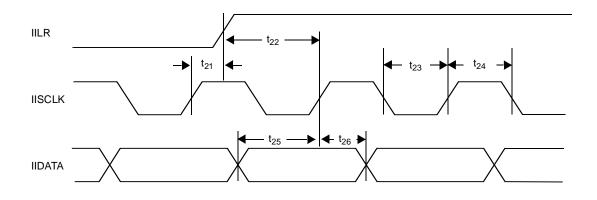

### I<sup>2</sup>S Serial Interface Timing

This section discusses the I<sup>2</sup>S serial interface signals. The signals when the port is configured for use with an ES689/ ES690 wavetable synthesizer is defined in the Wavetable Interface section.

Three signals (plus one optional) are used for I<sup>2</sup>S:

- IISCLK The bit clock/shift clock. The maximum rate is 6.4 MHz. The minimum number of IISCLK periods per IILR period is 32. Any number greater than or equal to 32 is acceptable.

- IILR Sample synchronization signal. The maximum sample rate is 50 kHz.

- IIDATA Serial data.

- IIMCLK Optional oversampling clock (for future use).

Within the ES1878, IILR and IIDATA are sampled on the rising edge of IISCLK. See Figure 22 and Figure 23 for detailed I<sup>2</sup>S timing.

#### **MPU-401** Interface

The MPU-401 port can be used for interfacing with either MIDI or with ES938 3-D stereo sound effects signals. Refer to the ES938 Data Sheet for technical details.

#### MIDI

The ES1878 has a MPU-401 MIDI interface with a 23-byte receive FIFO and an 8-byte transmit FIFO. The output of the transmit FIFO is serialized out the MSO pin and also sent to the ES978 in the expansion unit, where it is serialized out the MSO pin of that chip.

MIDI data can be received from either the MSI pin of the ES1878 or from the MSI pin of the ES978 in the expansion unit. In the unlikely event that MIDI data is received from both sources simultaneously, the data might be corrupted. Data received by the ES978 is transmitted back to the ES1878 in the next upload frame and then placed in the MPU-401 receive FIFO.

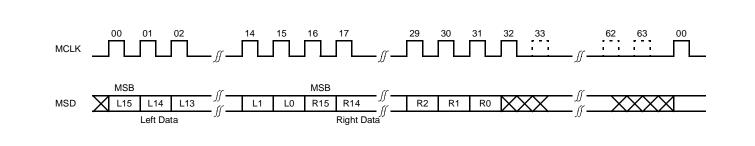

### Wavetable Interface

The ES1878 contains a synchronous serial interface for connection to a wavetable music synthesizer.

Table 4 Wavetable Interface Pins

| Pins | Descriptions                                                                                                                                                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK | Serial clock from external ES689/ES690 music synthesizer (2.75 MHz). Input with pull-down.                                                                                                                                                                              |

| MSD  | Serial data from external ES689/ES690 music<br>synthesizer. When both MCLK and MSD are<br>active, the stereo DACs normally used by the FM<br>synthesizer are acquired for use by the external<br>ES689/ES690. The normal FM output is blocked.<br>Input with pull-down. |

### **DSP** Interface

The ES1878 contains a synchronous serial interface for connection to a DSP serial interface. The typical application for this interface is a speakerphone.

|  | Table | 5 | DSP | Interface | Pins |

|--|-------|---|-----|-----------|------|

|--|-------|---|-----|-----------|------|

| Pins | Descriptions                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------|

| DCLK | Data clock. The rate can vary, but a typical value is 2.048 MHz (8 kHz x 256). Input with pull-down.                              |

| DX   | Data transmit. Active output when data is being transmitted serially from the ES1878; otherwise high-impedance. Tri-state output. |

| DR   | Serial data input with pull-down.                                                                                                 |

| FS   | Frame sync input. Software programmable to be active-high or active-low. Input with pull-down.                                    |

#### **DSP Interface Serial Data Format**

### **Game/Joystick Interface**

The ES1878 includes 8 pins for a dual joystick port. The digital game port address is decoded for timer pins TA, TB, TC, and TD, and for switch pins SWA, SWB, SWC, and SWD. The MIDI serial input and output also come from the game port connector in most applications.

Four of these eight pins, SW(A-D), are inputs for the switches of the joysticks. The remaining 4 pins, T(A-D), are "one-shot" timers that generate pulses of varying widths, where the width corresponds to the current resistance of one of the joystick potentiometers.

#### PC Joysticks

Normally, the host processor is responsible for measuring the width of the pulse. The ES1878 can also do this automatically. The host processor can read the measured widths directly rather than having to do the timing itself. This is referred to as a "digital joystick." Bit 1 of Vendor-Defined Card-Level register 29h determines whether the joystick port is a digital or analog joystick.

#### **Digital Joysticks**

For digital joysticks, the host processor first writes any value to the joystick port, and then reads back seven separate values (shown in Table 6).

#### Table 6 Digital Joystick Read Values

| Read #1 | Low byte timer A                                                             |

|---------|------------------------------------------------------------------------------|

| Read #2 | Low byte timer B                                                             |

| Read #3 | Low byte timer C                                                             |

| Read #4 | Low byte timer D                                                             |

| Read #5 | Bits 3:0 – Upper nibble timer A<br>Bits 7:4 – Upper nibble timer B           |

| Read #6 | Bits 3:0 – Upper nibble timer C<br>Bits 7:4 – Upper nibble timer D           |

| Read #7 | Bit 0 – switch A<br>Bit 1 – switch B<br>Bit 2 – switch C<br>Bit 3 – switch D |

The timer values reported range from 0 to FFFh (0-4095). The timer clock is 895 kHz.

When docked, a software programmable bit (bit 0 of Vendor-Defined Card-Level register 29h) causes the joystick connected to the ES978 to replace the one connected to the ES1878 automatically.

#### Joystick/MIDI External Interface Connector

The joystick portion of the ES1878 reference design is identical to that on a standard PC game control adaptor or game port. The PC-compatible joystick can be connected to a 15-pin D-sub connector. It supports all standard PC joystick compatible software.

If you need to support two joysticks, a joystick conversion cable is required. This cable uses a 15-pin D-sub male connector on one end and two 15-pin D-sub female connectors on the other end. All signals on this cable have direct pin-to-pin connection, except for pins 12 and 15. On the male connector, pins 12 and 15 should be left without connection. On the female connector, pin 15 is internally connected to pin 8, and pin 12 is internally connected to pin 4. The dual joystick port and MIDI port take up only one slot in your PC, leaving room for other cards. The dual joystick/MIDI connector configuration is shown in Figure 10.

The MIDI Serial Interface Adaptor from the Joystick/MIDI Connector is shown in Figure 11.

Figure 10 Dual Joystick/MIDI Connector

Figure 11 MIDI Serial Interface

#### **ES978** Interface

When docked, the ES1878 is in constant communication with the ES978 in the expansion unit. A half-duplex, bidirectional serial link keeps each chip updated on the status of the other. For example, the Mixer registers located in the ES1878 are transmitted down to the ES978. MIDI data received in the ES978 is transmitted up to the ES1878.

In addition to the digital control link, four analog wires connect the two chips directly. These four wires are configured as a pair of differential audio channels.The ES1878 uses these two audio channels in one of three ways: stereo playback (ES1878 transmits to the ES978), stereo record (the ES978 transmits to the ES1878), and mono full-duplex (one mono channel in each direction).

#### **Docking Status**

The ES1878 is either in docked or undocked state. The state is determined by the DOCKED input, which is active high when docked.

In the undocked state, the XSC and XSD pins are driven low. The XA[3:0] pins act as in mode 0 (differential outputs), except they follow the AOUT L/R outputs directly (i.e., after the master volume).

#### **Playback Mode**

The ES1878/ES978 design assumes that the active speakers move from the portable to the expansion unit

when docked. Except when recording, expansion audio sources are mixed in the expansion unit within the ES978, and played through speakers in the expansion unit. In most cases, speakers within the portable unit are programmed to be automatically muted when docked.

An exception is PC speaker beeps, which are always heard in the portable, even when docked.

Each audio input can be programmed individually on how to respond to a docking situation, in one of the three ways:

- As an analog input, such as mic, which remains in the portable (ES1878) when docked and is muted in the ES978.

- As an analog input, such as line-in, which is disabled in the ES1878 when docked and enabled in the ES978 when docked, i.e. it is muted in the mixers in the ES1878 and ES978.

- As an analog input which is enabled in both the ES1878 and ES978 mixers, and shares a common volume control. (Note: An exception to sharing a common volume control is allowed for the Mappable Volume register 6Ah; see below).

The playback master volume is controlled through software programming or by the up/down/mute switch inputs. The latter method, called hardware volume control, has active-low switch inputs in both the ES1878 and ES978.

#### **Record Mode**

In record mode, the expansion audio bus is turned around, and sound data is sent from the expansion unit ES978 chip to the ES1878 in the portable unit. The sound data from the expansion unit can be mixed inside the ES1878 with local sources before recording. Because portable unit sources (for example, FM) can be mixed into the recording, it is not possible to do a record monitor function through the expansion unit speakers (they are automatically muted in record mode). It is possible for record monitor to use the speakers in the portable unit (see bit 5 of Vendor-Defined Card-Level register 2Bh).

The default situation for most applications is to have all speakers muted during recording.

As in previous chips, one of four record sources can be selected: Mic, Line, Aux A, or Mixer. When docked, the ES1878 chip knows whether each resource is present in the portable, the docking station, or both, and acts accordingly.

#### No ES978 – Differential AOUT Mode

In some applications, there is no ES978 in the expansion unit. In this case, XA[3:0] are used as differential outputs that follow AOUT L/R and are intended to connect to a differential-input power amplifier in the expansion unit. This mode of operation is selected automatically whenever the DOCKED input is zero. When DOCKED is zero, XSC and XSD are high-impedance.

#### Mono Full-Duplex Mode

In the ES1878, host-based software applications can use full-duplex mode through two 8-bit DMA channels. The restrictions are that both record and playback are monophonic, and that record and playback are synchronous (i.e., at the same sample rate).

The record channel can record from any analog input of either the ES1878 or remote ES978 chips, or any mix of the same, or from the FDXI input to the ES1878 when using the DSP serial port.

#### **Power Management**

Power management is controlled by Vendor-Defined Card-Level register 2Dh. In previous ESS *Audio*Drive® chips, power management was controlled via I/O port Audio\_Base+7h. Only bit 5 (FM reset) and bit 7 (suspend request) of I/O port Audio\_Base+7h are supported in the ES1878.

#### **Expansion Audio Interface – Digital**

Two wires are used to transmit serial data between the ES1878 and ES978. The first signal , XSC, acts as a frame sync and shift clock. The bit clock rate is 3.58 MHz.

A typical frame consists of:

- Sync period 24 clocks wide

- Download period 144 clocks wide

- Turn-around period 8 clocks wide

- Upload Period 80 clocks wide

Total: 256 bit clocks/frame, which is equivalent to a 14 kHz frame rate.

The function of the upload and download periods is to continually update corresponding registers within each device. For example, pressing the VOLUP button in the expansion unit transmits the pin state to the ES1878 where it is AND'ed with the same pin of the ES1878. The ES1878 updates its copy of the master volume register. The ES978 will receive the new value in the master volume register during the next download period of the next frame.

#### Sync Period

In the sync period, XSC is low for 12-bit clock periods, and then high for 12-bit clock periods.

#### Download Period

In the download period, data is transmitted serially from the ES1878 to the ES978 via the signal XSD. XSC is the bit shift clock. Data is shifted out of the ES1878 on the falling edge of XSC. Data is shifted into the ES978 on the rising edge of XSC.

The download period is 144 bits wide. Each bit takes 4 oscillator clocks (bit rate = 3.58 MHz). The last 8 bits are a checksum byte.

The upload period is 80 bits wide. The last 8 bits are a checksum byte.

Table 7 contains the data configuration for the download period.

#### Table 7 Download Period

| Byte | Bits                      | Function                                                                                                                                                              |

|------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 1:0<br>4:2<br>5<br>6<br>7 | Mode of expansion analog interface<br>Record source select<br>Master output enable<br>1: MIDI loopback test<br>1: MIDI transmit signal (byte 1 contains<br>MIDI data) |

| 1    | 15:8                      | MIDI data (if bit 7 of byte 0 is high)                                                                                                                                |

| 2    | 23:15                     | XGPO[7:0] data                                                                                                                                                        |

| 3    | 31:24                     | Playback mixer – Host audio volume                                                                                                                                    |

| 4    | 39:32                     | Playback mixer – Line volume                                                                                                                                          |

| 5    | 47:40                     | Playback mixer – Mic volume                                                                                                                                           |

| 6    | 55:48                     | Playback mixer – Aux A (CD) volume                                                                                                                                    |

| 7    | 63:56                     | Playback mixer – Aux B volume                                                                                                                                         |

| 8    | 71:64                     | Playback mixer – I <sup>2</sup> S/ES689 volume                                                                                                                        |

| 9    | 79:72                     | Reserved                                                                                                                                                              |

| 10   | 87:80                     | Record mixer – Line volume                                                                                                                                            |