Am29200<sup>™</sup> and Am29205<sup>™</sup> RISC Microcontrollers

User's Manual

Advanced Micro Devices

# Am29200™ and Am29205™ RISC Microcontrollers

**User's Manual**

Rev. 1, 1994

#### © 1994 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### **Trademarks**

AMD and Am29000 are registered trademarks; Am29005, Am29027, Am29030, Am29035, Am29050, Am29200, Am29205, Am29240, Am29243, Am29245, 29K, Laser29K, EB29K, XRAY29K, MiniMON29K, and Design-Made-Easy are trademarks of Advanced Micro Devices, Inc. Fusion29K is a registered trademark of Advanced Micro Devices, Inc. PostScript is a registered trademark of Adobe Systems, Inc. High C is a registered trademark of MetaWare, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## IF YOU HAVE QUESTIONS, WE'RE HERE TO HELP YOU.

#### **Customer Service**

AMD's customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from AMD's worldwide staff of field application engineers and factory support staff to answer 29K™ Family hardware and software development questions.

## Hotline, Email, and Bulletin Board Support

For answers to technical questions, AMD provides a toll-free number for direct access to our engineering support staff. For overseas customers, the easiest way to reach the engineering support staff with your questions is via fax with a short description of your question. AMD 29K Family customers also receive technical support through electronic mail. This worldwide service is available to 29K product users via the international UNIX email service. Also available is the AMD bulletin board service, which provides the latest 29K product information, including technical information and data on upcoming product releases.

## **Engineering Support Staff**

(800) 292-9263 ext 2

toll-free for U.S.

0031-11-1163

toll-free for Japan

(512) 602-4118

direct dial worldwide

44-(0)256-811101

U.K. and Europe hotline

(512) 602-5031

fax

29k-support@amd.com

email

#### **Bulletin Board**

(800) 292-9263 ext 1

toll-free for U.S.

(512) 602-4898

worldwide and local for U.S.

#### **Documentation and Literature**

The 29K Family Customer Support Group responds quickly to information and literature requests. A simple phone call gets you free 29K Family information, such as data books, user's manuals, data sheets, application notes, the Fusion29K<sup>SM</sup> Partner Solutions Catalog and Newsletter, and other literature. Internationally, contact your local AMD sales office for complete 29K Family literature.

#### **Customer Support Group**

(800) 292-9263 ext 3

toll-free for U.S.

(512) 602-5651

local for U.S.

(512) 602-5051

fax for U.S.

.

# **TABLE OF CONTENTS**

| ŗ | Preface   | INTRODUCTION AND OVERVIEW  Am29200 AND Am29205 RISC MICROCONTROLLERS                                                                                                                                                                                                                                                                                                                                                                        |

|---|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |           | INTENDED AUDIENCE xvii USER'S MANUAL OVERVIEW xvii AMD DOCUMENTATION xix RELATED PUBLICATIONS xviii                                                                                                                                                                                                                                                                                                                                         |

| ( | Chapter 1 | FEATURES AND PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |           | 1.1 DISTINCTIVE CHARACTERISTICS       1-1         1.1.1 Am29200 Microcontroller       1-2         1.1.2 Am29205 Microcontroller       1-4                                                                                                                                                                                                                                                                                                   |

|   |           | 1.2 KEY FEATURES AND BENEFITS                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |           | 1.3       PERFORMANCE OVERVIEW       1-7         1.3.1       Instruction Timing       1-7         1.3.2       Pipelining       1-8         1.3.3       Burst-Mode and Page-Mode Memories       1-8         1.3.4       Instruction Set Overview       1-8         1.3.5       Data Formats       1-8         1.3.6       Protection       1-9         1.3.7       DRAM Mapping       1-9         1.3.8       Interrupts and Traps       1-9 |

|   |           | 1.4 DEBUGGING AND TESTING                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C | Chapter 2 | PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                 |

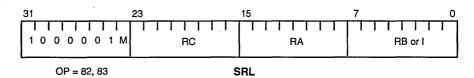

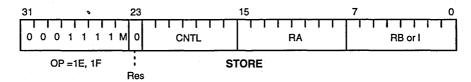

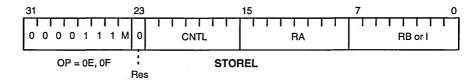

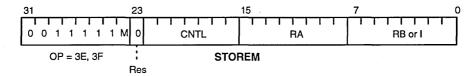

|   |           | 2.1 INSTRUCTION SET       2-1         2.1.1 Integer Arithmetic       2-1         2.1.2 Compare       2-1         2.1.3 Logical       2-4         2.1.4 Shift       2-4         2.1.5 Data Movement       2-4         2.1.6 Constant       2-5         2.1.7 Floating Point       2-6         2.1.8 Branch       2-7         2.1.9 Miscellaneous       2-7         2.1.10 Reserved Instructions       2-8                                    |

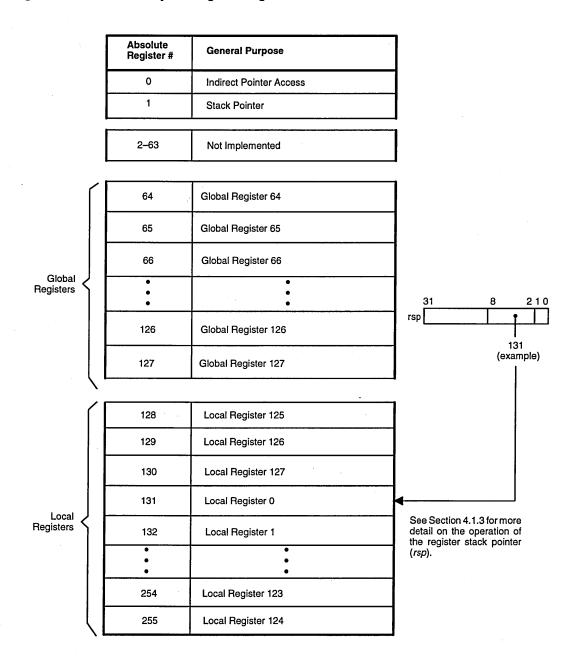

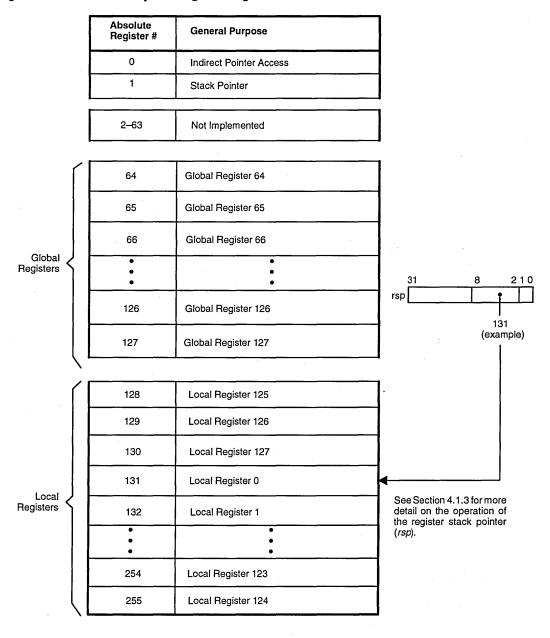

|   |           | 2.2 REGISTER MODEL       2-8         2.2.1 General-Purpose Registers       2-8                                                                                                                                                                                                                                                                                                                                                              |

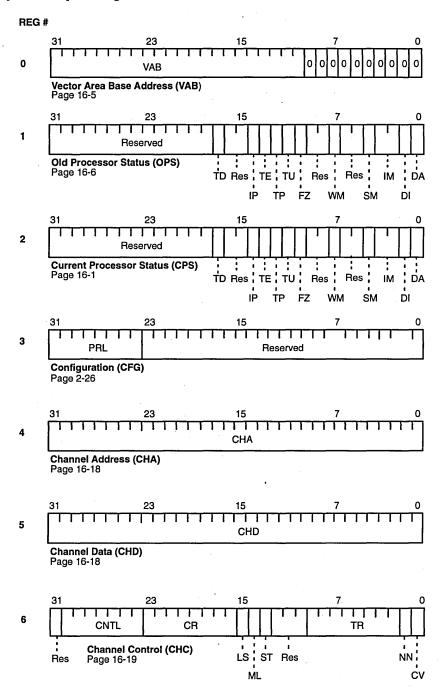

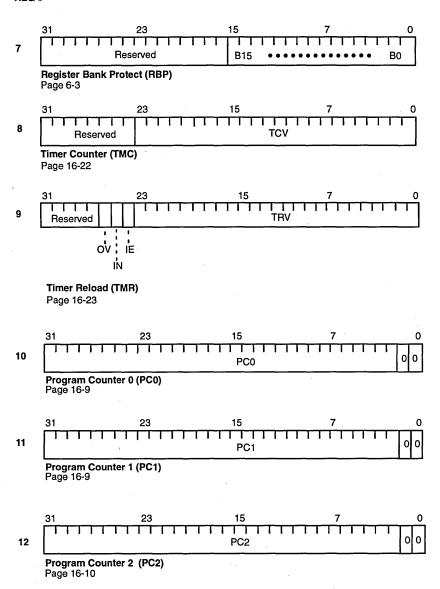

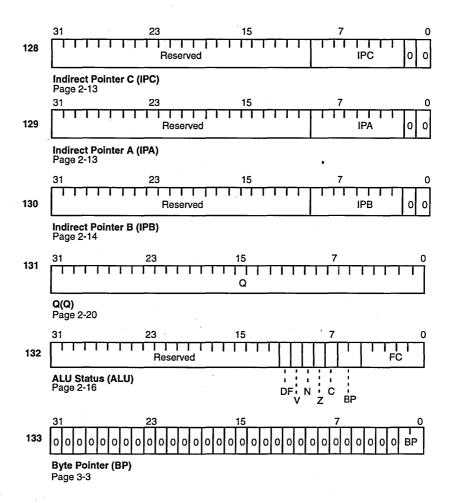

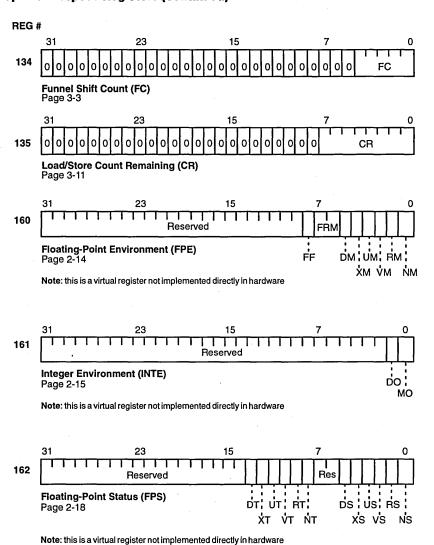

|           | 2.2.2 Special-Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

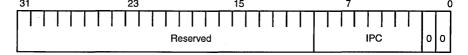

|           | 2.3       ADDRESSING REGISTERS INDIRECTLY       2-12         2.3.1       Indirect Pointer C Register (IPC, Register 128)       2-13         2.3.2       Indirect Pointer A Register (IPA, Register 129)       2-13         2.3.3       Indirect Pointer B Register (IPB, Register 130)       2-14                                                                                                                |

|           | 2.4 INSTRUCTION ENVIRONMENT                                                                                                                                                                                                                                                                                                                                                                                      |

|           | 2.5       STATUS RESULTS OF INSTRUCTIONS       2-16         2.5.1       ALU Status Register (ALU, Register 132)       2-16         2.5.2       Arithmetic Operation Status Results       2-17         2.5.3       Logical Operation Status Results       2-17         2.5.4       Floating-Point Status Results       2-18         2.5.5       Floating-Point Status Register (FPS, Register 162)       2-18     |

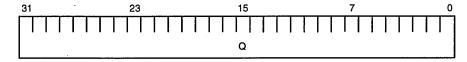

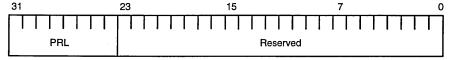

|           | 2.6       INTEGER MULTIPLICATION AND DIVISION       2-19         2.6.1       Q Register (Q, Register 131)       2-20         2.6.2       Multiplication       2-20         2.6.3       Division       2-22                                                                                                                                                                                                       |

|           | 2.7       I NEED AN INSTRUCTION FOR       2-24         2.7.1       Run-Time Checking       2-24         2.7.2       Operating-System Calls       2-24         2.7.3       Multiprecision Integer Operations       2-25         2.7.4       Complementing a Boolean       2-25         2.7.5       Large Jump and Call Ranges       2-25         2.7.6       NO-OPs       2-25                                    |

|           | 2.8 VIRTUAL ARITHMETIC PROCESSOR       2-26         2.8.1 Trapping Arithmetic Instructions       2-26         2.8.2 Virtual Registers       2-26                                                                                                                                                                                                                                                                 |

|           | 2.9 PROCESSOR INITIALIZATION       2-26         2.9.1 Configuration Register (CFG, Register 3)       2-26         2.9.2 Reset Mode       2-27                                                                                                                                                                                                                                                                    |

| Chapter 3 | DATA FORMATS AND HANDLING                                                                                                                                                                                                                                                                                                                                                                                        |

|           | 3.1       INTEGER DATA TYPES       3-1         3.1.1       Character Data       3-1         3.1.2       Half-Word Operations       3-2         3.1.3       Byte Pointer Register (BP, Register 133)       3-2         3.1.4       Bit Strings       3-3         3.1.5       Character-String Operations       3-4         3.1.6       Boolean Data       3-5         3.1.7       Instruction Constants       3-5 |

|           | 3.2FLOATING-POINT DATA TYPES3-53.2.1Single-Precision Floating-Point Values3-53.2.2Double-Precision Floating-Point Values3-63.2.3Special Floating-Point Values3-6                                                                                                                                                                                                                                                 |

|           | 3.3       EXTERNAL DATA ACCESSES       3-7         3.3.1       Load/Store Instruction Format       3-7         3.3.2       Load Operations       3-9         3.3.3       Store Operations       3-9         3.3.4       Multiple Accesses       3-9         3.3.5       Addressing and Alignment       3-11                                                                                                      |

| Chapter 4 | PROCEDURE LINKAGE                                                                                                                                                                                                                                                                                                                                                                                                |

|           | 4.1 RUN-TIME STACK ORGANIZATION AND USE                                                                                                                                                                                                                                                                                                                                                                          |

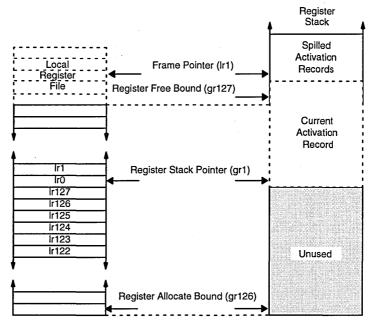

|           |     | 4.1.1       Management of the Run-Time Stack         4.1.2       Register Stack         4.1.3       Local Registers as a Stack Cache         4.1.4       Memory Stack                                                                                                                                    | 4-3<br>4-4<br>4-5                                  |

|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|           | 4.2 | PROCEDURE LINKAGE CONVENTIONS 4.2.1 Argument Passing 4.2.2 Procedure Prologue 4.2.3 Spill Handler 4.2.4 Return Values 4.2.5 Procedure Epilogue 4.2.6 Fill Handlers 4.2.7 Register Stack Leaf Frame 4.2.8 Local Variables and Memory-Stack Frames 4.2.9 Static Link Pointer 4.2.10 Transparent Procedures | 4-7<br>4-8<br>4-10<br>4-10<br>4-11<br>4-11<br>4-11 |

|           | 4.3 | REGISTER USAGE CONVENTION                                                                                                                                                                                                                                                                                | 4-13                                               |

|           | 4.4 | COMPLEX PROCEDURE CALL EXAMPLE                                                                                                                                                                                                                                                                           | 1-14                                               |

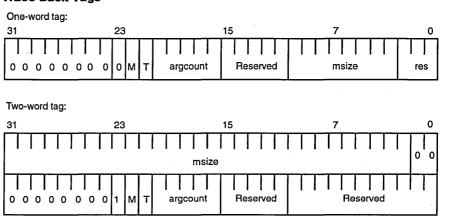

|           | 4.5 | TRACE-BACK TAGS                                                                                                                                                                                                                                                                                          | <b>1-1</b> 5                                       |

| Chapter 5 |     | ELINING AND INSTRUCTION SCHEDULING                                                                                                                                                                                                                                                                       |                                                    |

|           |     | FOUR-STAGE PIPELINE                                                                                                                                                                                                                                                                                      |                                                    |

|           |     | PIPELINE HOLD MODE                                                                                                                                                                                                                                                                                       |                                                    |

|           | 5.3 | SERIALIZATION                                                                                                                                                                                                                                                                                            |                                                    |

|           | 5.4 | DELAYED BRANCH                                                                                                                                                                                                                                                                                           | 5-2                                                |

|           | 5.5 | OVERLAPPED LOADS AND STORES                                                                                                                                                                                                                                                                              | 5-4                                                |

|           | 5.6 | DELAYED EFFECTS OF REGISTERS                                                                                                                                                                                                                                                                             | 5-5                                                |

| Chapter 6 |     | STEM PROTECTION                                                                                                                                                                                                                                                                                          |                                                    |

|           | 6.1 | USER AND SUPERVISOR MODES 6.1.1 Supervisor Mode 6.1.2 User Mode                                                                                                                                                                                                                                          | 6-1                                                |

|           | 6.2 | REGISTER PROTECTION                                                                                                                                                                                                                                                                                      |                                                    |

| Chapter 7 | SYS | STEM OVERVIEW                                                                                                                                                                                                                                                                                            |                                                    |

|           | 7.1 | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                       |                                                    |

|           |     | 7.1.1 Clocks                                                                                                                                                                                                                                                                                             |                                                    |

|           |     | 7.1.2 Processor Signals                                                                                                                                                                                                                                                                                  |                                                    |

|           |     | 7.1.4 DRAM Interface                                                                                                                                                                                                                                                                                     |                                                    |

|           |     | 7.1.5 Peripheral Interface Adapter (PIA)                                                                                                                                                                                                                                                                 | 7-4                                                |

|           |     | 7.1.6 DMA Controller                                                                                                                                                                                                                                                                                     |                                                    |

|           |     | 7.1.8 Parallel Port                                                                                                                                                                                                                                                                                      |                                                    |

|           |     | 7.1.9 Serial Port                                                                                                                                                                                                                                                                                        |                                                    |

|           |     | 7.1.10 Video Interface                                                                                                                                                                                                                                                                                   |                                                    |

|           |     | 7.1.12 Pin Changes for the Am29205 Microcontroller                                                                                                                                                                                                                                                       |                                                    |

|           | 7.2 | ACCESS PRIORITY                                                                                                                                                                                                                                                                                          |                                                    |

|           |     | SYSTEM ADDRESS PARTITION                                                                                                                                                                                                                                                                                 |                                                    |

|           | 7.4 | INTERNAL PERIPHERALS AND CONTROLLERS                                                                                                                                                                                                                                                                     | 7-8                                                |

|           |     |                                                                                                                                                                                                                                                                                                          |                                                    |

| Chapter 8  | ROM CONTROLLER                                                                                                                                                                                                                                                                                                                                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 8.1 OVERVIEW 8-                                                                                                                                                                                                                                                                                                                                                   |

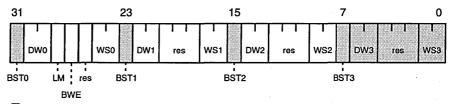

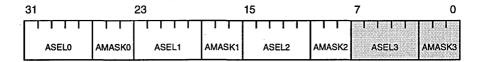

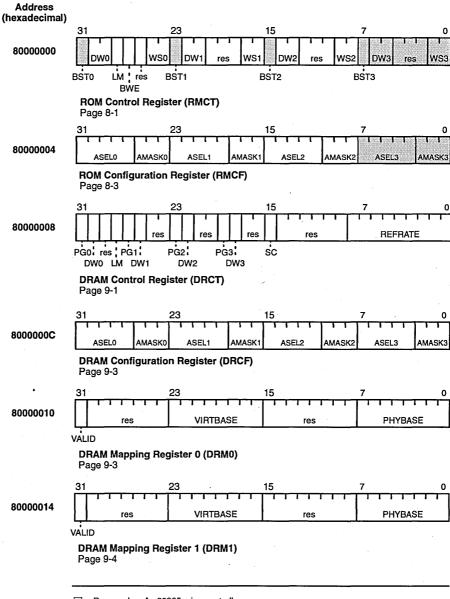

|            | 8.2       PROGRAMMABLE REGISTERS       8-         8.2.1       ROM Control Register (RMCT, Address 80000000)       8-         8.2.2       ROM Configuration Register (RMCF, Address 80000004)       8-         8.2.3       Initialization       8-                                                                                                                 |

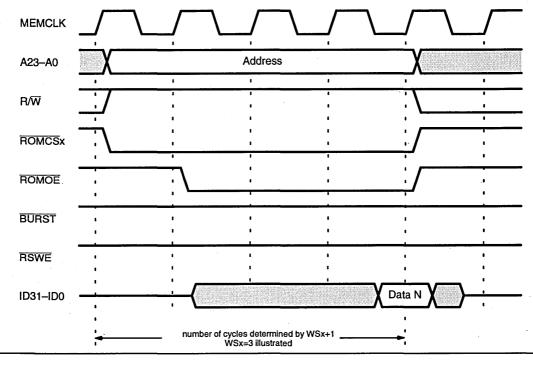

|            | 8.3       ROM ACCESSES       8-4         8.3.1       ROM Address Mapping       8-4         8.3.2       Simple ROM Accesses       8-4         8.3.3       Narrow ROM Accesses       8-4         8.3.4       Writes to the ROM Space       8-7         8.3.5       Burst-Mode ROM Accesses       8-8         8.3.6       Use of WAIT to Extend ROM Cycles       8-8 |

| Chapter 9  | DRAM CONTROLLER                                                                                                                                                                                                                                                                                                                                                   |

|            | 9.1 OVERVIEW 9-1                                                                                                                                                                                                                                                                                                                                                  |

|            | 9.2 PROGRAMMABLE REGISTERS9-                                                                                                                                                                                                                                                                                                                                      |

|            | 9.2.1 DRAM Control Register (DRCT, Address 80000008) 9-1<br>9.2.2 DRAM Configuration Register (DRCF, Address 8000000C) 9-2                                                                                                                                                                                                                                        |

|            | 9.2.2 DRAM Configuration Register (DRCF, Address 8000000C) 9-2<br>9.2.3 DRAM Mapping Register 0 (DRM0, Address 80000010) 9-3                                                                                                                                                                                                                                      |

|            | 9.2.4 DRAM Mapping Register 1 (DRM1, Address 80000014) 9-4                                                                                                                                                                                                                                                                                                        |

|            | 9.2.5 DRAM Mapping Register 2 (DRM2, Address 80000018) 9-4 9.2.6 DRAM Mapping Register 3 (DRM3, Address 8000001C) 9-4                                                                                                                                                                                                                                             |

|            | 9.2.7 Initialization9-4                                                                                                                                                                                                                                                                                                                                           |

|            | 9.3 DRAM ACCESSES9-2                                                                                                                                                                                                                                                                                                                                              |

|            | 9.3.1 DRAM Address Mapping9-2                                                                                                                                                                                                                                                                                                                                     |

|            | 9.3.2       Address Multiplexing       9-5         9.3.3       32-Bit DRAM Width       9-7                                                                                                                                                                                                                                                                        |

|            | 9.3.4 16-Bit DRAM Width9-7                                                                                                                                                                                                                                                                                                                                        |

|            | 9.3.5 Mapped DRAM Accesses9-8                                                                                                                                                                                                                                                                                                                                     |

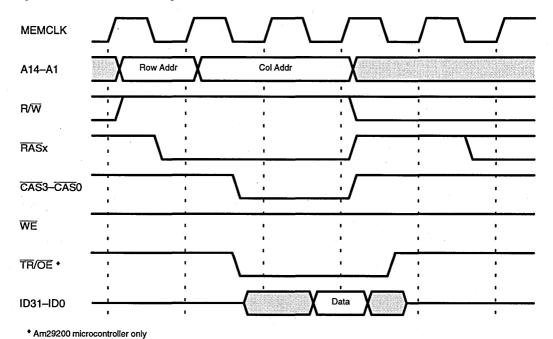

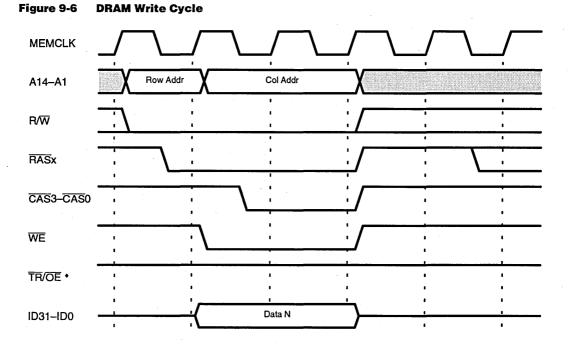

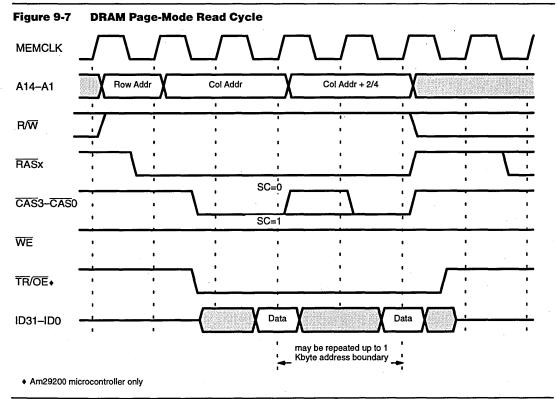

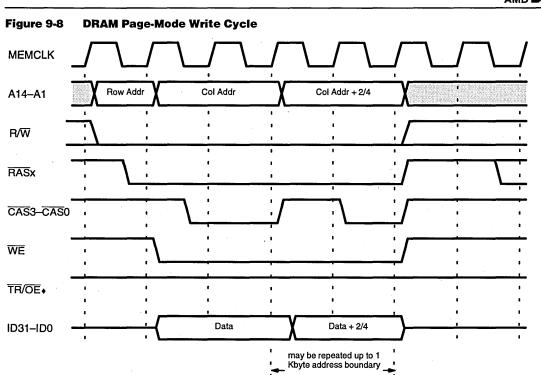

|            | 9.3.6 Normal Access Timing                                                                                                                                                                                                                                                                                                                                        |

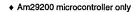

|            | 9.3.8 DRAM Refresh9-10                                                                                                                                                                                                                                                                                                                                            |

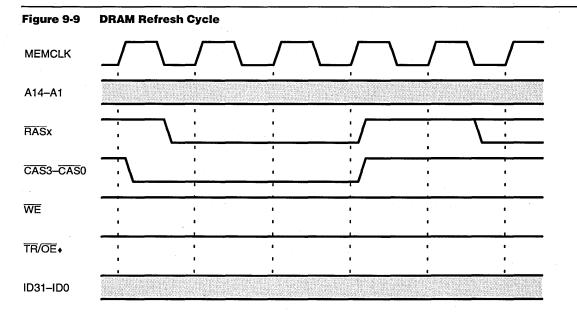

|            | 9.3.9 Video DRAM Interface9-12                                                                                                                                                                                                                                                                                                                                    |

| Chapter 10 | PERIPHERAL INTERFACE ADAPTER                                                                                                                                                                                                                                                                                                                                      |

|            | 10.1 OVERVIEW                                                                                                                                                                                                                                                                                                                                                     |

|            | 10.2 PROGRAMMABLE REGISTERS                                                                                                                                                                                                                                                                                                                                       |

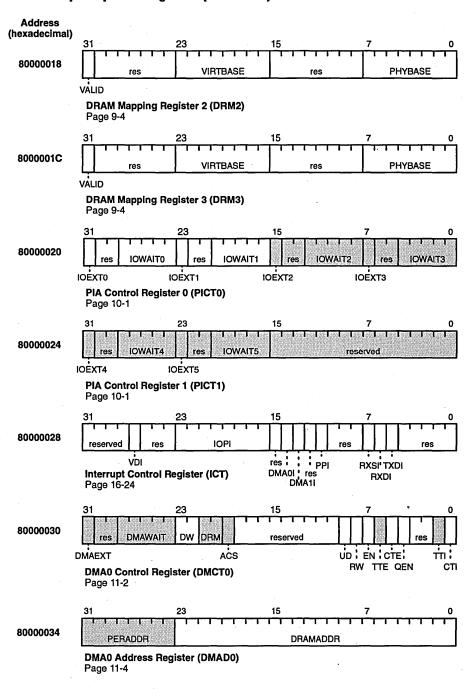

|            | 10.2.1 PIA Control Register 0/1 (PICT0/1, Address 80000020/24) 10-1                                                                                                                                                                                                                                                                                               |

|            | 10.2.2 Initialization                                                                                                                                                                                                                                                                                                                                             |

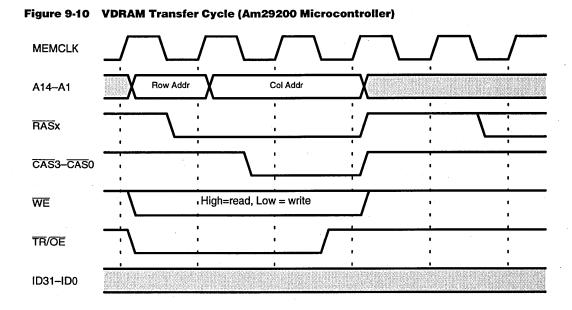

|            | 10.3 PIA ACCESSES                                                                                                                                                                                                                                                                                                                                                 |

|            | 10.3.2 Use of WAIT to Extend I/O Cycles                                                                                                                                                                                                                                                                                                                           |

| Chapter 11 | DMA CONTROLLER                                                                                                                                                                                                                                                                                                                                                    |

|            | 11.1 OVERVIEW11-1                                                                                                                                                                                                                                                                                                                                                 |

|            | 11.2 PROGRAMMABLE REGISTERS                                                                                                                                                                                                                                                                                                                                       |

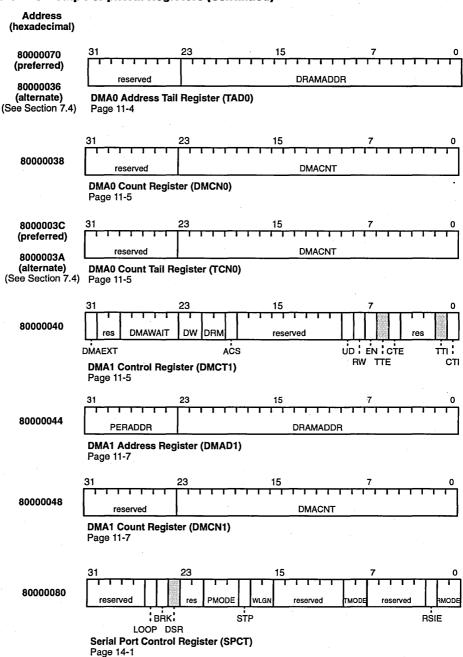

|            | 11.2.0 DIVIAT CONTROL REGISTER (DIVICT), Address 60000040) 11-5                                                                                                                                                                                                                                                                                                   |

|            | 11.2.7       DMA1 Address Register (DMAD1, Address 80000044)         11.2.8       DMA1 Count Register (DMCN1, Address 80000048)         11.2.9       Initialization                                                                                                                                                                    | 11-7                                         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|            | 11.3 DMA TRANSFERS  11.3.1 Specifying the Direction of a DMA Transfer  11.3.2 Programming Internal DMA Transfers  11.3.3 Programming External DMA Transfers  11.3.4 Generating External DMA Requests  11.3.5 External DMA Transfers  11.3.6 Latching External DMA Requests                                                             | 11-8<br>11-9<br>11-9<br>11-9                 |

|            | 11.4 DMA QUEUING (DMA CHANNEL 0)                                                                                                                                                                                                                                                                                                       | 1-12                                         |

|            | 11.5 RANDOM DIRECT MEMORY ACCESS BY EXTERNAL DEVICES 1                                                                                                                                                                                                                                                                                 | 1-12                                         |

| Chapter 12 | PROGRAMMABLE I/O PORT                                                                                                                                                                                                                                                                                                                  |                                              |

|            | 12.1 OVERVIEW                                                                                                                                                                                                                                                                                                                          | 12-1                                         |

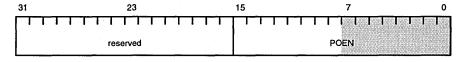

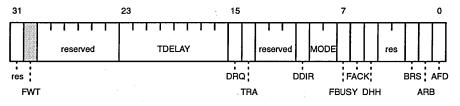

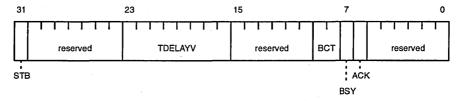

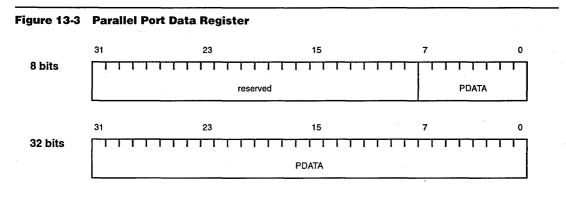

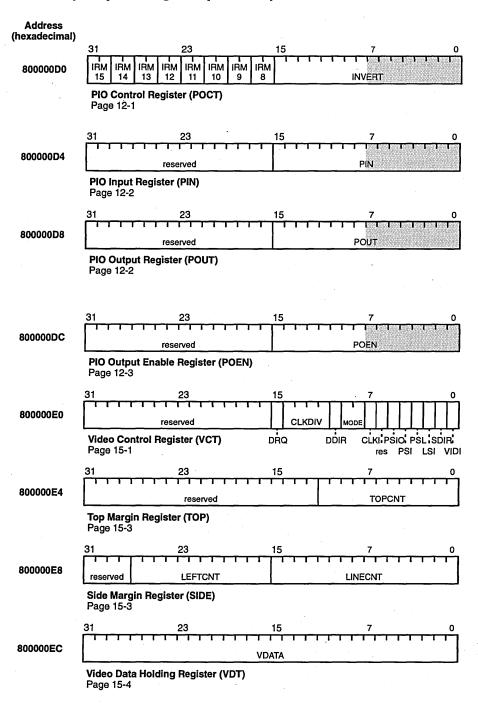

|            | 12.2 PROGRAMMABLE REGISTERS  12.2.1 PIO Control Register (POCT, Address 800000D0)  12.2.2 PIO Input Register (PIN, Address 800000D4)  12.2.3 PIO Output Register (POUT, Address 800000D8)  12.2.4 PIO Output Enable Register (POEN, Address 800000DC)  12.2.5 Initialization                                                           | 12-1<br>12-2<br>12-2<br>12-3<br>12-3         |

| •          | 12.3 OPERATING THE I/O PORT                                                                                                                                                                                                                                                                                                            | 12-3                                         |

| Chapter 13 | PARALLEL PORT                                                                                                                                                                                                                                                                                                                          |                                              |

|            | 13.1 OVERVIEW                                                                                                                                                                                                                                                                                                                          | 13-1                                         |

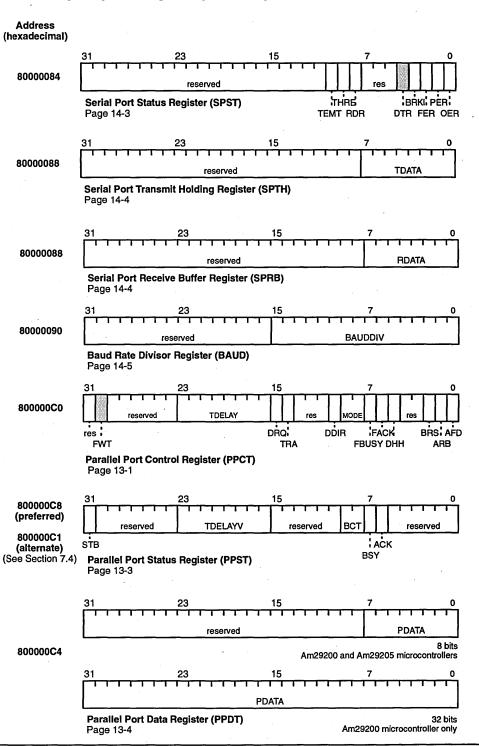

|            | 13.2 PROGRAMMABLE REGISTERS  13.2.1 Parallel Port Control Register (PPCT, Address 800000C0) 13.2.2 Parallel Port Status Register (PPST, Address 800000C8) 13.2.3 Parallel Port Data Register (PPDT, Address 800000C4) 13.2.4 Initialization  13.3 PARALLEL PORT TRANSFERS  13.3.1 Transfers from the Host 13.3.2 Transfers to the Host | 13-1<br>13-3<br>13-4<br>13-4<br>13-5<br>13-5 |

| Chapter 14 | SERIAL PORT                                                                                                                                                                                                                                                                                                                            |                                              |

|            | 14.1 OVERVIEW                                                                                                                                                                                                                                                                                                                          | 14-1                                         |

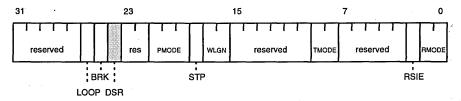

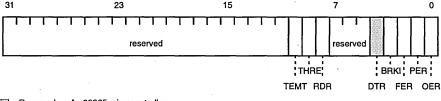

|            | 14.2 PROGRAMMABLE REGISTERS                                                                                                                                                                                                                                                                                                            | 14-1<br>14-3                                 |

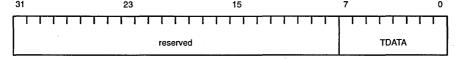

|            | 14.2.3 Serial Port Transmit Holding Register (SPTH, Address 80000088)                                                                                                                                                                                                                                                                  |                                              |

|            | (SPRB, Address 8000008C)                                                                                                                                                                                                                                                                                                               | 14-4                                         |

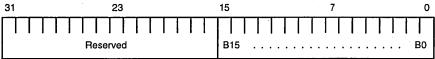

|            | 14.2.5 Baud Rate Divisor Register (BAUD, Address 80000090) 14.2.6 Initialization                                                                                                                                                                                                                                                       |                                              |

| Chapter 15 | VIDEO INTERFACE                                                                                                                                                                                                                                                                                                                        |                                              |

|            | 15.1 OVERVIEW                                                                                                                                                                                                                                                                                                                          |                                              |

|            | 15.2 PROGRAMMABLE REGISTERS                                                                                                                                                                                                                                                                                                            | 15-1<br>15 <b>-</b> 3                        |

|            | 15.2.4 Video Data Holding Register (VDT, Address 800000EC) 15-3                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------|

|            | 15.3 VIDEO INTERFACE OPERATION                                                                                  |

|            | 15.3.1 Transmitting Data on the Video Interface                                                                 |

|            | 15.3.2 Receiving Data on the Video Interface                                                                    |

| Chapter 16 | INTERRUPTS AND TRAPS                                                                                            |

|            | 16.1 OVERVIEW                                                                                                   |

|            | 16.2 INTERRUPTS AND TRAPS                                                                                       |

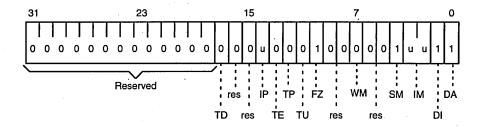

|            | 16.2.1 Current Processor Status Register (CPS, Register 2) 16-1 16.2.2 Interrupts                               |

|            | 16.2.3 Traps                                                                                                    |

|            | 16.2.4 External Interrupts and Traps                                                                            |

|            | 16.2.5 Wait Mode                                                                                                |

|            | 16.3 VECTOR AREA                                                                                                |

|            | 16.3.2 Vector Numbers                                                                                           |

|            | 16.4 INTERRUPT AND TRAP HANDLING                                                                                |

|            | 16.4.1 Old Processor Status Register (OPS, Register 1)                                                          |

|            | 16.4.2 Program Counter Stack       16-6         16.4.3 Taking an Interrupt or Trap       16-10                  |

|            | 16.4.4 Returning from an Interrupt or Trap                                                                      |

|            | 16.4.5 Lightweight Interrupt Processing                                                                         |

|            | 16.4.6 Simulation of Interrupts and Traps                                                                       |

|            | 16.5.1 WARN Input                                                                                               |

|            | 16.6 SEQUENCING OF INTERRUPTS AND TRAPS 16-14                                                                   |

|            | 16.7 EXCEPTION REPORTING AND RESTARTING 16-16                                                                   |

|            | 16.7.1 Instruction Exceptions       16-16         16.7.2 Restarting Mapped DRAM Accesses       16-17            |

|            | 16.7.2 Restarting Mapped DRAW Accesses                                                                          |

|            | 16.7.4 Floating-Point Exceptions                                                                                |

|            | 16.7.5 Correcting Out-of-Range Results                                                                          |

|            | 16.7.6 Exceptions builing interrupt and map handling                                                            |

|            | 16.8.1 Timer Facility Operation                                                                                 |

|            | 16.8.2 Timer Facility Initialization                                                                            |

|            | 16.8.3 Handling Timer Interrupts                                                                                |

|            | 16.8.4 Timer Facility Uses       16-22         16.8.5 Timer Counter Register (TMC, Register 8)       16-22      |

|            | 16.8.6 Timer Reload Register (TMR, Register 9)                                                                  |

|            | 16.9 INTERNAL INTERRUPT CONTROLLER                                                                              |

|            | 16.9.1 Interrupt Control Register (ICT, Address 80000028) 16-23                                                 |

|            | 16.9.2 Interrupt Controller Initialization       16-25         16.9.3 Servicing Internal Interrupts       16-25 |

| Chapter 17 | DEBUGGING AND TESTING                                                                                           |

|            | 17.1 OVERVIEW                                                                                                   |

|            | 17.2 TRACE FACILITY                                                                                             |

|            | 17.3 INSTRUCTION BREAKPOINTS                                                                                    |

|            | 17.4 PROCESSOR STATUS OUTPUTS                                                                                   |

|            | 17.5 CONTROL FIELD IN SCAN PATH                                                                                 |

|            |                                                                                                                 |

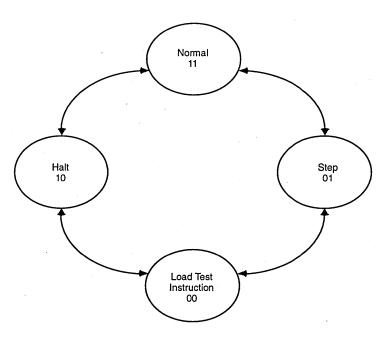

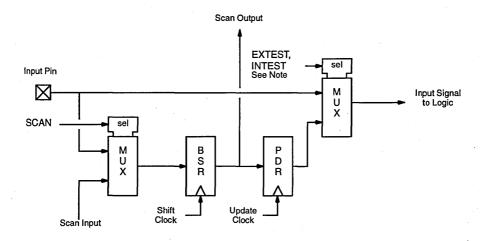

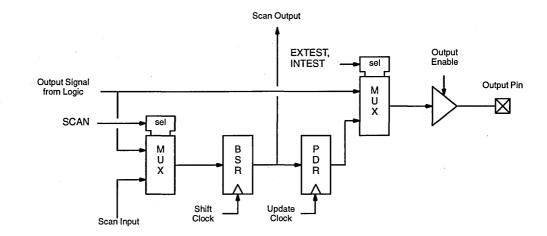

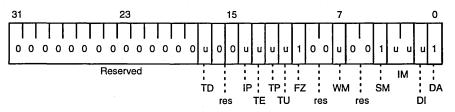

|            | 17.6 TEST ACCESS PORT  17.6.1 Boundary-Scan Cells  17.6.2 Instruction Register and Implemented Instructions  17.6.3 Order of Scan Cells in Boundary-Scan Path  17.7 IMPLEMENTING A HARDWARE-DEVELOPMENT SYSTEM  17.7.1 Halt Mode  17.7.2 Step Mode  17.7.3 Load Test Instruction Mode  17.7.4 Accessing Internal State Via Boundary Scan  17.7.5 HALT Instructions as Breakpoints  17.7.6 Forcing Outputs to High Impedance | 17-4<br>17-8<br>17-11<br>17-11<br>17-12<br>17-13<br>17-14<br>17-16 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|            | 17.8 EMULATING THE Am29205 MICROCONTROLLER                                                                                                                                                                                                                                                                                                                                                                                  | . 17-17                                                            |

| Chapter 18 | INSTRUCTION SET                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

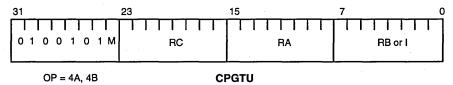

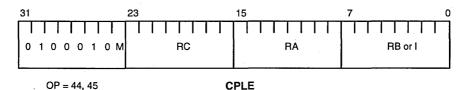

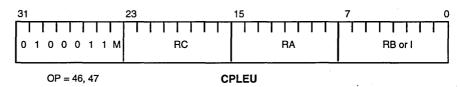

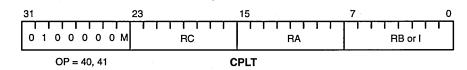

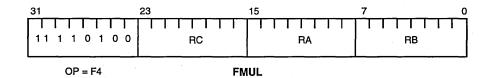

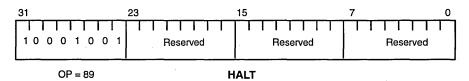

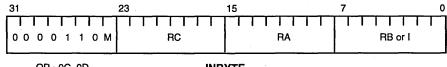

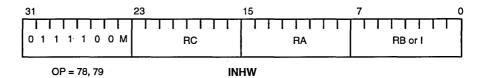

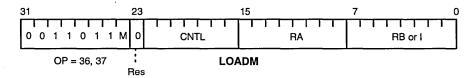

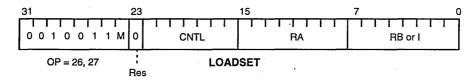

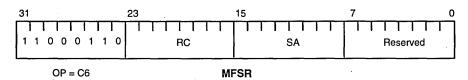

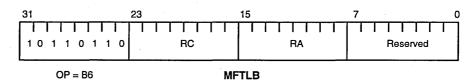

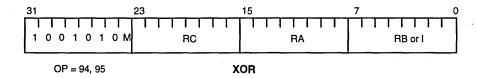

|            | 18.1 INSTRUCTION-DESCRIPTION NOMENCLATURE 18.1.1 Operand Notation and Symbols 18.1.2 Operator Symbols 18.1.3 Control-Flow Terminology 18.1.4 Assembler Syntax  18.2 INSTRUCTION FORMATS  18.3 INSTRUCTION DESCRIPTION                                                                                                                                                                                                       | 18-1<br>18-2<br>18-3<br>18-3                                       |

| Appendix A | SPECIAL SETTINGS FOR THE<br>Am29200 AND Am29205 MICROCONTROLLERS                                                                                                                                                                                                                                                                                                                                                            | A-1                                                                |

| Appendix B | PROCESSOR REGISTER SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                  | B-1                                                                |

| Appendix C | PERIPHERAL REGISTER SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                 | C-1                                                                |

| INDEV      |                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

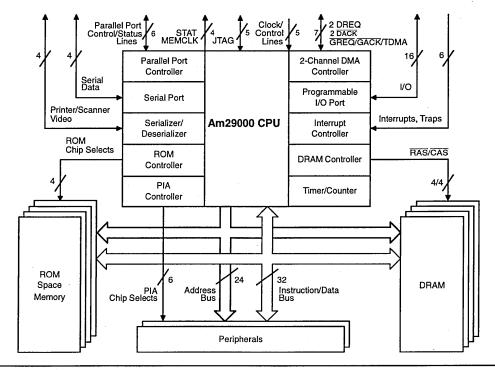

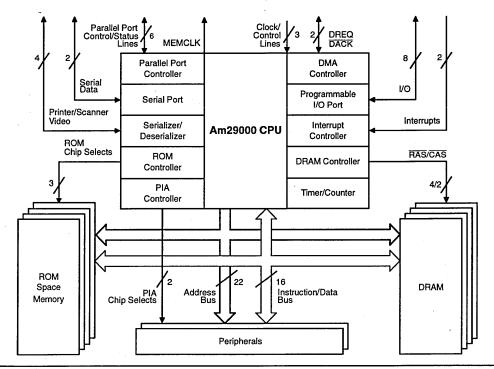

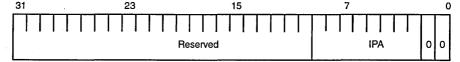

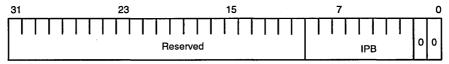

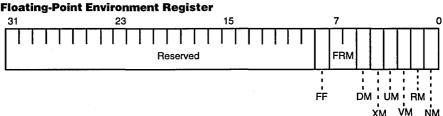

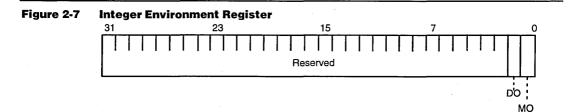

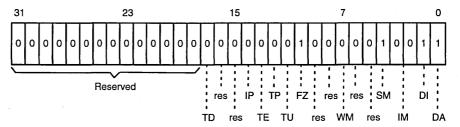

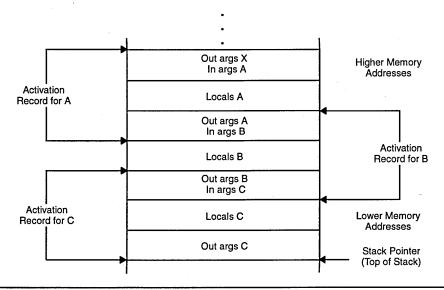

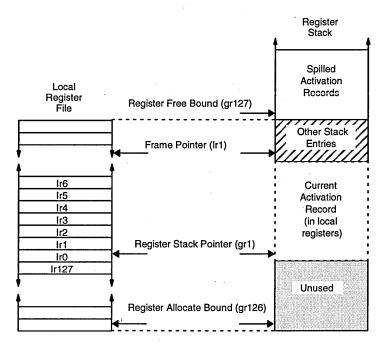

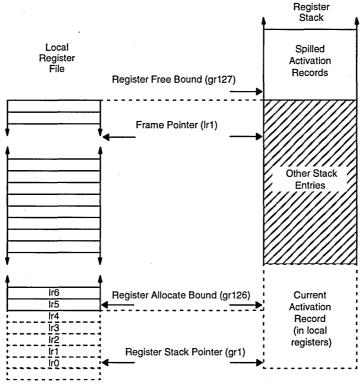

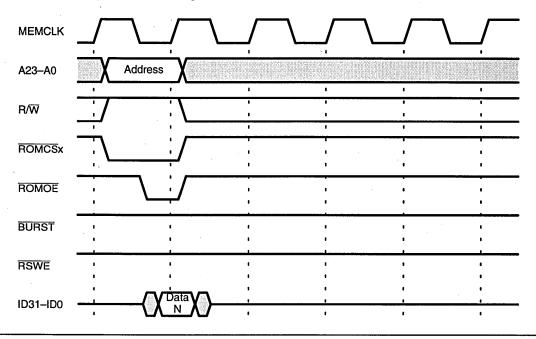

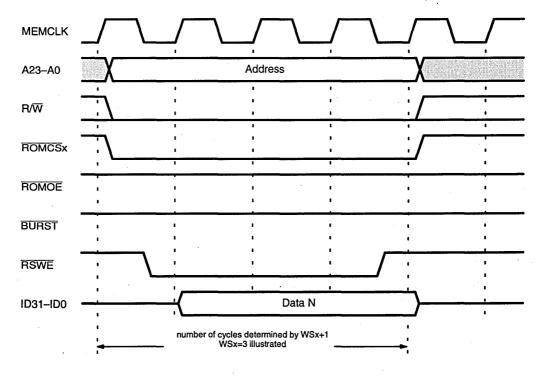

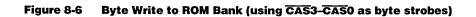

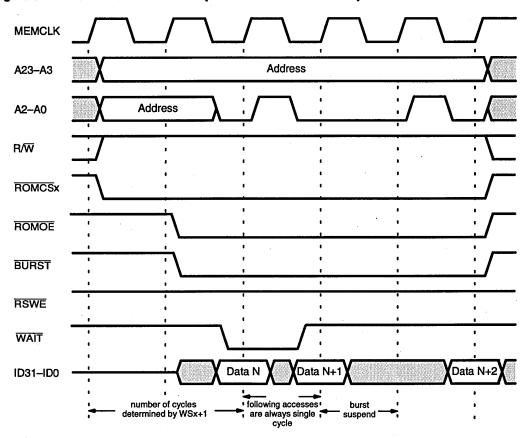

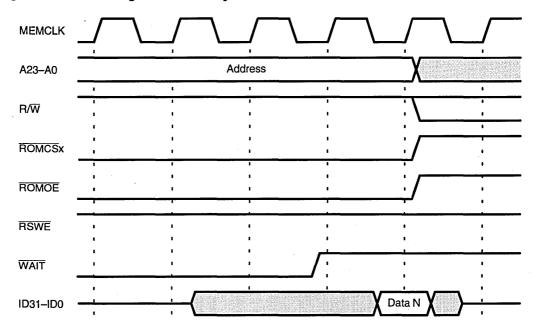

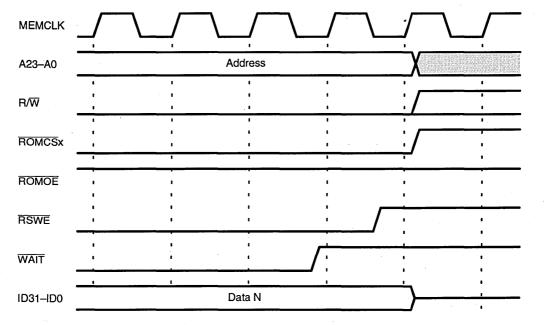

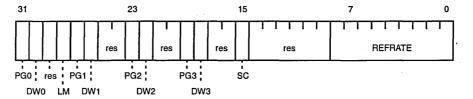

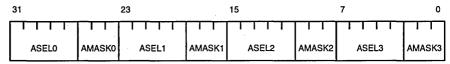

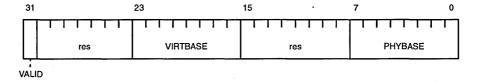

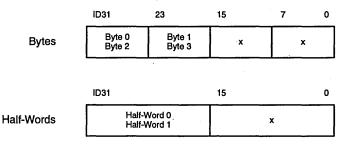

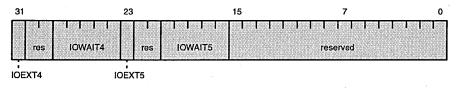

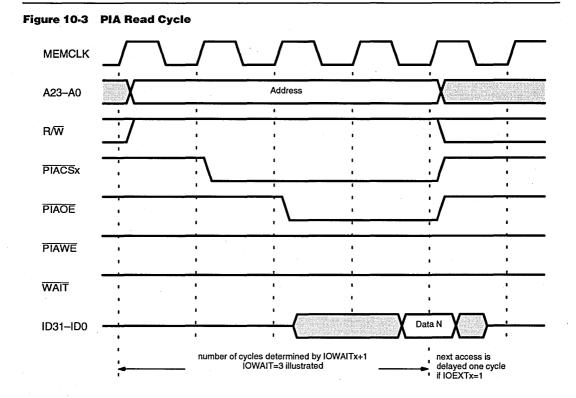

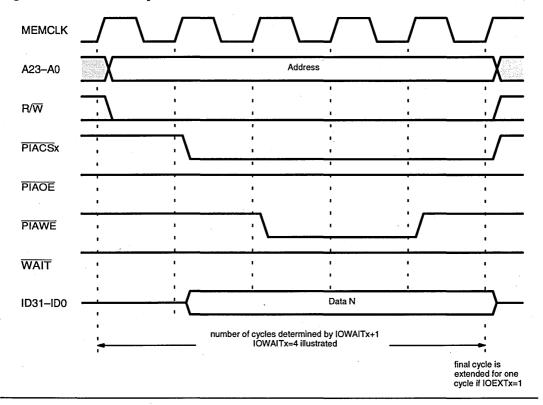

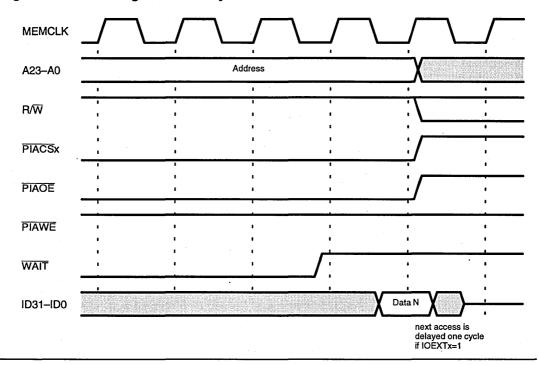

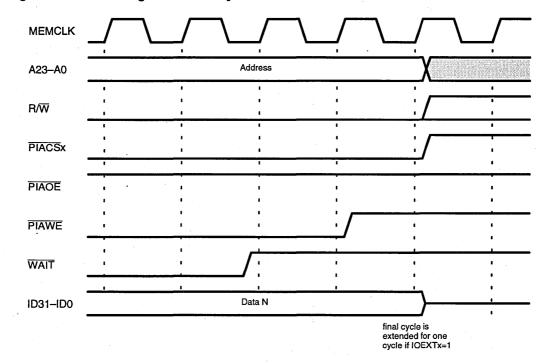

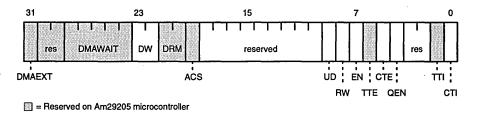

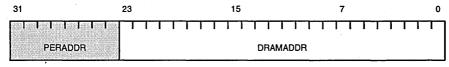

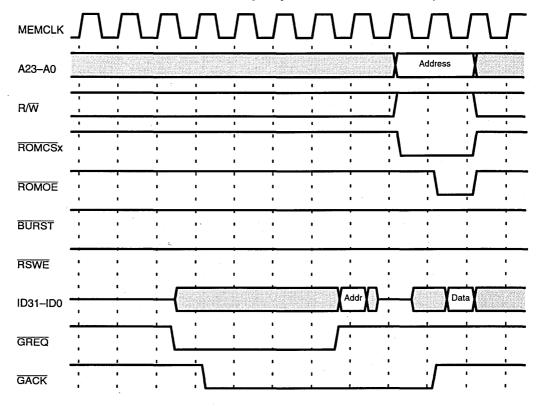

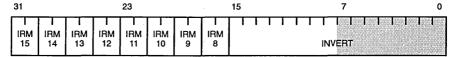

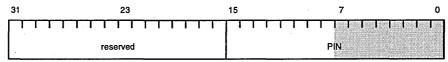

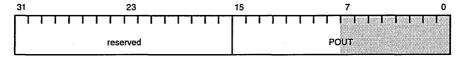

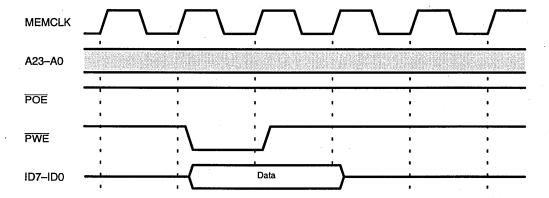

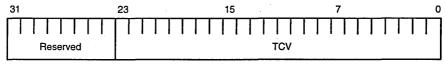

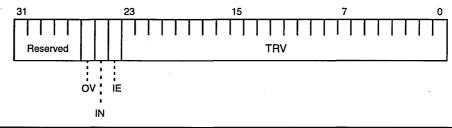

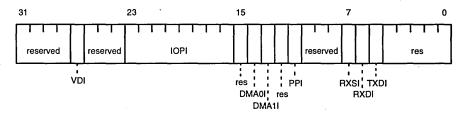

#### LIST OF FIGURES Figure 1-1 Am29200 Microcontroller Block Diagram ...... 1-3 Figure 1-2 Figure 2-1 Figure 2-2 Special-Purpose Registers ......2-12 Indirect Pointer C Register ......2-13 Figure 2-3 Figure 2-4 Figure 2-5 Figure 2-6 Figure 2-7 Integer Environment Register ......2-15 Figure 2-8 Floating-Point Status ......2-18 Figure 2-9 Figure 2-10 Figure 2-11 Configuration Register ......2-26 Current Processor Status Register In Reset Mode ......2-27 Figure 2-12 Figure 3-1 Figure 3-2 Figure 3-3 Funnel Shift Count Register ......3-3 Figure 3-4 Figure 3-5 Figure 3-6 Figure 3-7 Figure 3-8 Figure 3-9 Run-Time Stack Example ......4-2 Figure 4-1 Figure 4-2 Figure 4-3 Relationship of Stack Cache and Register Stack .......4-4 Figure 4-4 Stack Underflow .......4-7 Figure 4-5 Figure 4-6 Figure 4-7 Figure 6-1 Register Bank Organization ......6-2 Register Bank Protect Register ......6-3 Figure 6-2 ROM Control Register .......8-1 Figure 8-1 Figure 8-2 Simple ROM Read Cycle .......8-5 Figure 8-3 Figure 8-4 Simple ROM Read Cycle—Zero Wait States ...... 8-6 Figure 8-5 Simple Write to ROM Bank ......8-7 Figure 8-6 Byte Write to ROM Bank (using CAS3-CAS0 as byte strobes) ....... 8-9 Figure 8-7 Burst-Mode ROM Read ......8-10 Extending a ROM Read Cycle with WAIT ......8-11 Figure 8-8 Extending a ROM Write Cycle with WAIT ......8-11 Figure 8-9 Figure 9-1 Figure 9-2 Figure 9-3 DRAM Mapping Register 0 ......9-3 Location of Bytes and Half-Words on a 16-Bit Bus ......9-8 Figure 9-4 Figure 9-5 DRAM Read Cycle ......9-9 Figure 9-6 DRAM Write Cycle ......9-9 DRAM Page-Mode Read Cycle .....9-10 Figure 9-7 DRAM Page-Mode Write Cycle ......9-11 Figure 9-8 DRAM Refresh Cycle ...... 9-11 Figure 9-9 Figure 9-10 VDRAM Transfer Cycle ......9-12 Figure 10-1 Figure 10-2 PIA Control Register 1 (PICT1, Address 80000024) ......10-1 Figure 10-3 PIA Write Cycle ......10-4 Figure 10-4 Extending a PIA Read Cycle with WAIT .....10-5 Figure 10-5

| Figure 10-6  | Extending a PIA Write Cycle with WAIT                      | . 10-5 |

|--------------|------------------------------------------------------------|--------|

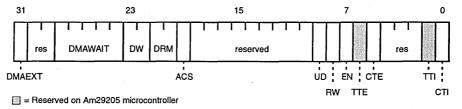

| Figure 11-1  | DMA0 Control Register                                      |        |

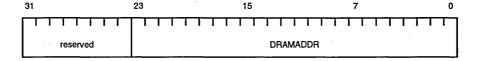

| Figure 11-2  | DMA0 Address Register                                      |        |

| Figure 11-3  | DMA0 Address Tail Register                                 |        |

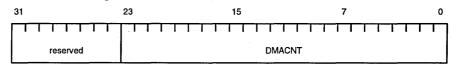

| Figure 11-4  | DMA0 Count Register                                        |        |

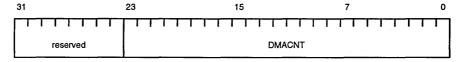

| Figure 11-5  | DMA0 Count Tail Register                                   |        |

| Figure 11-6  | DMA1 Control Register                                      |        |

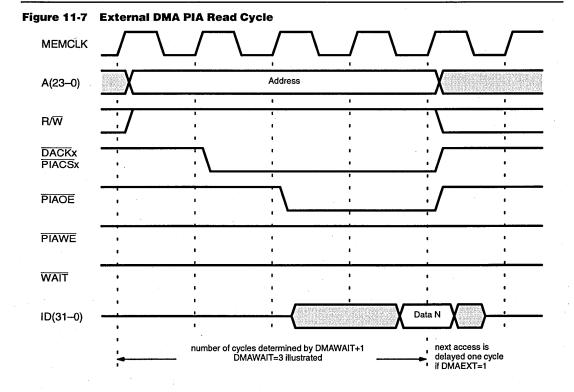

| Figure 11-7  | External DMA PIA Read Cycle                                | 11-10  |

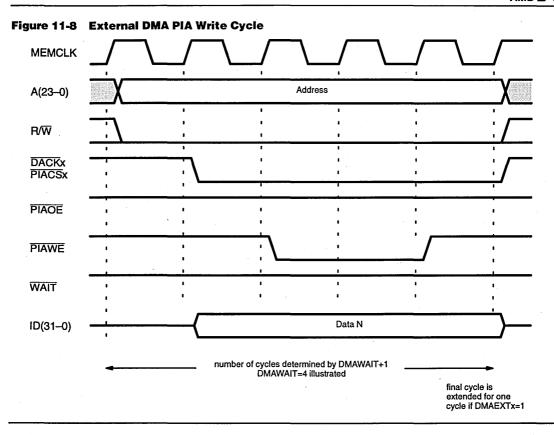

| Figure 11-8  | External DMA PIA Write Cycle                               |        |

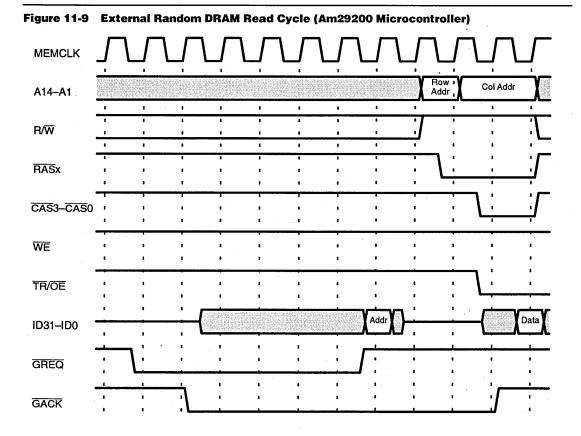

| Figure 11-9  | External Random DRAM Read Cycle                            |        |

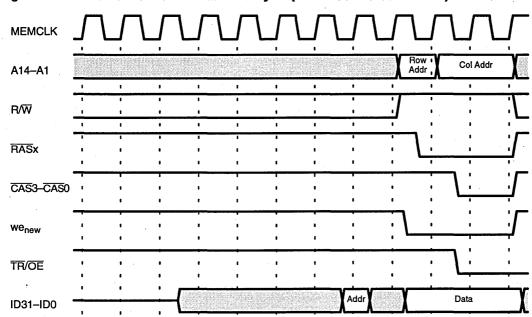

| Figure 11-10 | External Random DRAM Write Cycle                           | 11-14  |

| Figure 11-11 | External Random ROM Read Cycle                             |        |

| Figure 12-1  | PIO Control Register                                       |        |

| Figure 12-2  | PIO Input Register                                         | . 12-2 |

| Figure 12-3  | PIO Output Register                                        |        |

| Figure 12-4  | PIO Output Enable Register                                 |        |

| Figure 13-1  | Parallel Port Control Register                             |        |

| Figure 13-2  | Parallel Port Status Register                              |        |

| Figure 13-3  | Parallel Port Data Register                                |        |

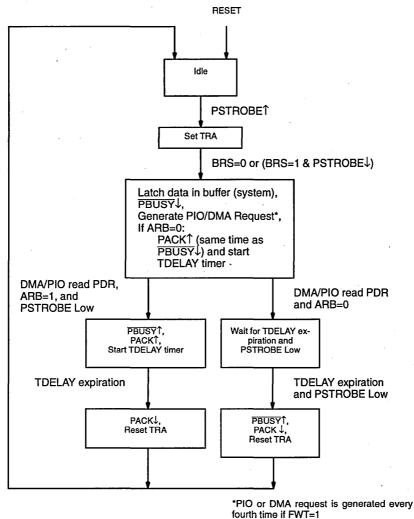

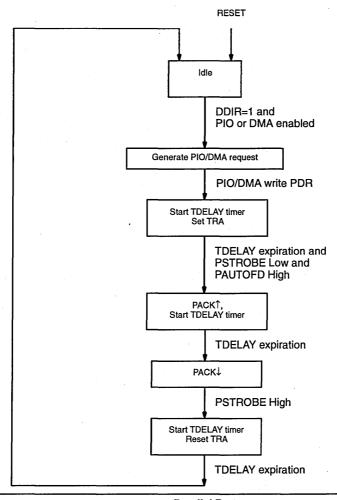

| Figure 13-4  | State Transitions for Transfers from the Host              |        |

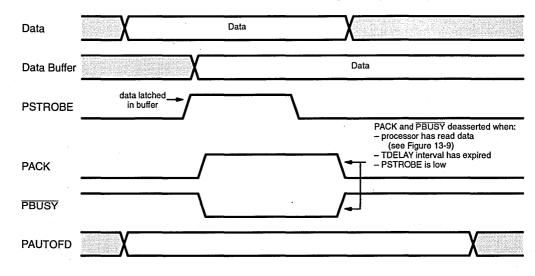

| Figure 13-5  | Transfer from the Host on the Parallel Port (BRS=0, ARB=0) |        |

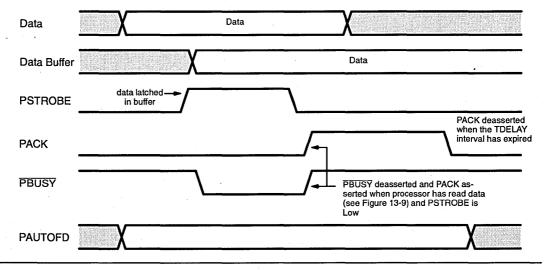

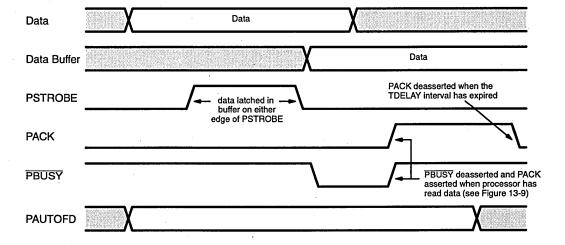

| Figure 13-6  | Transfer from the Host on the Parallel Port (BRS=0, ARB=1) |        |

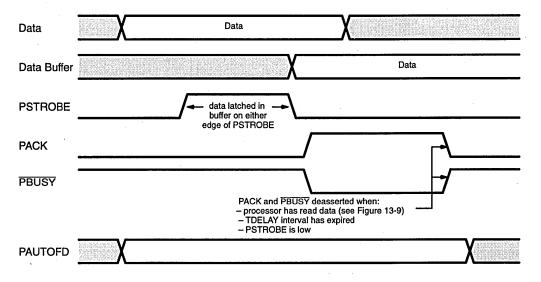

| Figure 13-7  | Transfer from the Host on the Parallel Port (BRS=1, ARB=0) |        |

| Figure 13-8  | Transfer from the Host on the Parallel Port (BRS=1, ARB=1) |        |

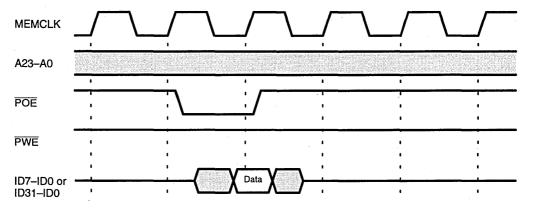

| Figure 13-9  | Parallel Port Buffer Read Cycle                            |        |

| Figure 13-10 | State Transitions for Transfers to the Host                | . 13-9 |

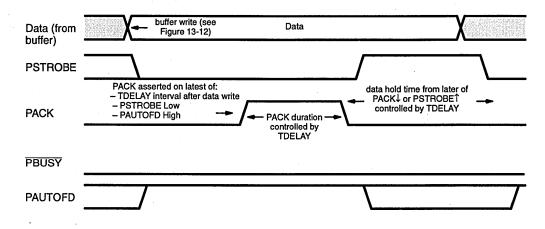

| Figure 13-11 | Transfer to the Host on the Parallel Port                  | 13-10  |

| Figure 13-12 | Parallel Port Buffer Write Cycle                           | 13-10  |

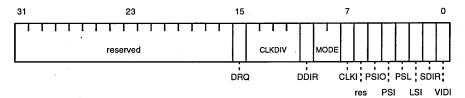

| Figure 14-1  | Serial Port Control Register                               |        |

| Figure 14-2  | Serial Port Status Register                                | . 14-3 |

| Figure 14-3  | Serial Port Transmit Holding Register                      |        |

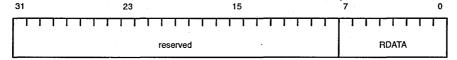

| Figure 14-4  | Serial Port Receive Buffer Register                        |        |

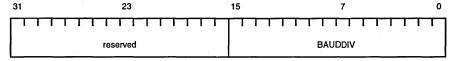

| Figure 14-5  | Baud Rate Divisor Register                                 | . 14-5 |

| Figure 15-1  | Video Control Register                                     | . 15-1 |

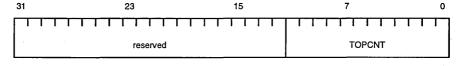

| Figure 15-2  | Top Margin Register                                        |        |

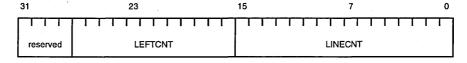

| Figure 15-3  | Side Margin Register                                       |        |

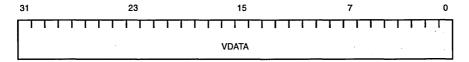

| Figure 15-4  | Video Data Holding Register                                |        |

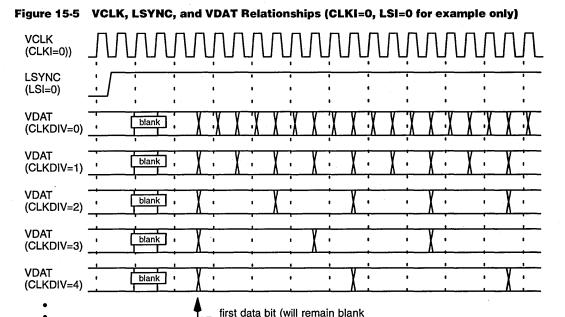

| Figure 15-5  | VCLK, LSYNC, and VDAT Relationships                        |        |

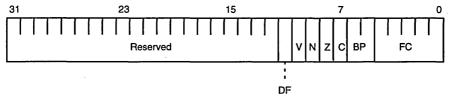

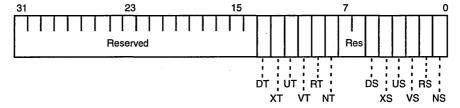

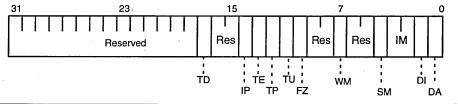

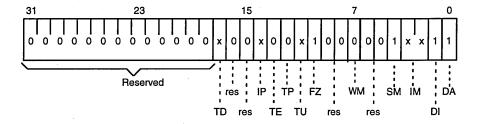

| Figure 16-1  | Current Processor Status Register                          |        |

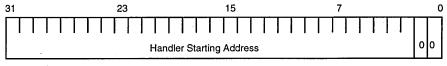

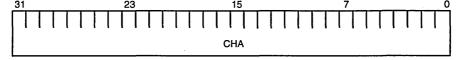

| Figure 16-2  | Vector Table Entry                                         |        |

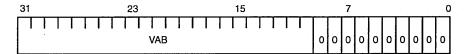

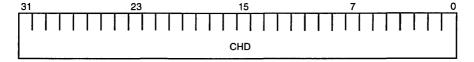

| Figure 16-3  | Vector Area Base Address Register                          |        |

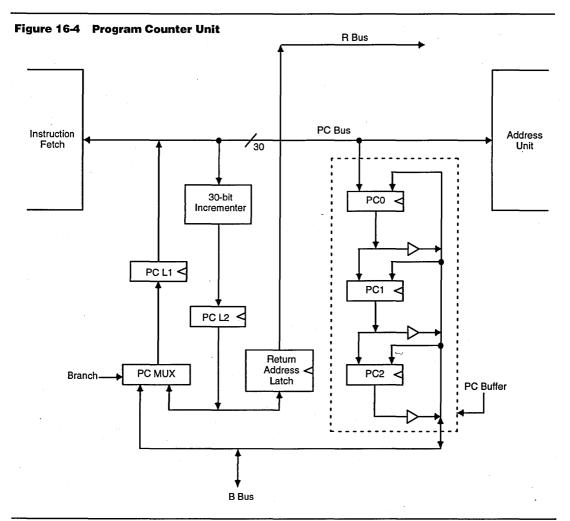

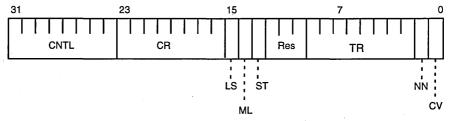

| Figure 16-4  | Program Counter Unit                                       |        |

| Figure 16-5  | Program Counter 0 Register                                 |        |

| Figure 16-6  | Program Counter 1 Register                                 |        |

| Figure 16-7  | Program Counter 2 Register                                 |        |

| Figure 16-8  | Current Processor Status After an Interrupt or Trap        |        |

| Figure 16-9  | Current Processor Status Before Interrupt Return           |        |

| Figure 16-10 |                                                            | 16-18  |

| Figure 16-11 | - · · · - · · · · · · · · · · · · · · ·                    | 16-18  |

| Figure 16-12 |                                                            | 16-19  |

| Figure 16-13 | •                                                          | 16-22  |

| Figure 16-14 | •                                                          | 16-23  |

| Figure 16-15 |                                                            | 16-24  |

| Figure 17-1  | Valid Transitions for CNTL Field                           |        |

| Figure 17-2  | Input Boundary-Scan Cell                                   |        |

| Figure 17-3  | Output Boundary-Scan Cell                                  |        |

| Figure 17-4  | Processor Status While in Load Test Instruction Mode       | 17-13  |

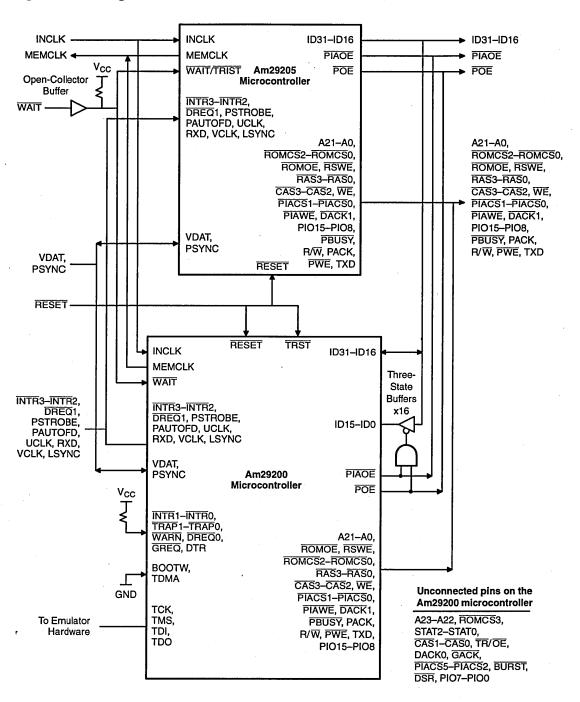

| Figure 17-5    | Using an Am29200 Microcontroller to Emulate an Am29205 Microcontroller | 17 10 |

|----------------|------------------------------------------------------------------------|-------|

| F! 40.4        |                                                                        |       |

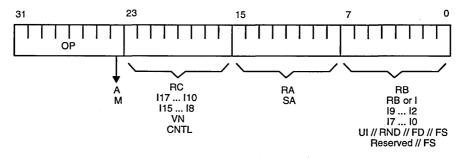

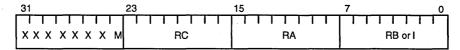

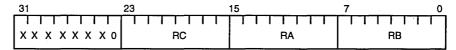

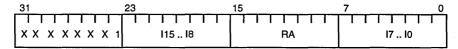

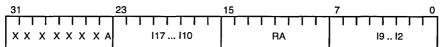

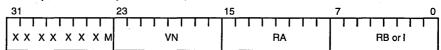

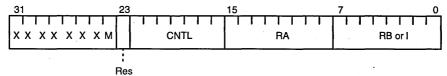

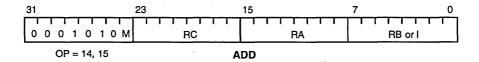

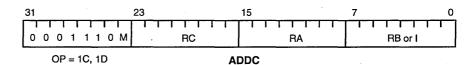

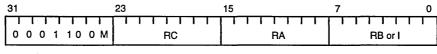

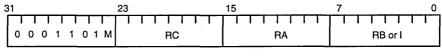

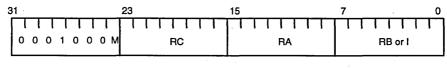

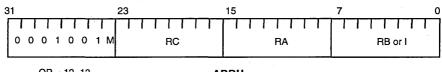

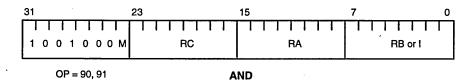

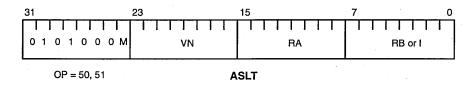

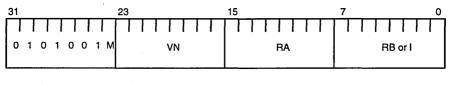

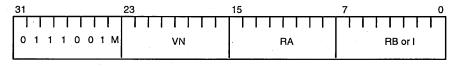

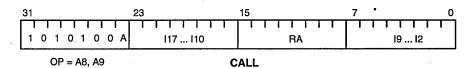

| Figure 18-1    | Instruction Format                                                     |       |

| Figure 18-2    | Frequently Occurring Instruction Field Uses                            |       |

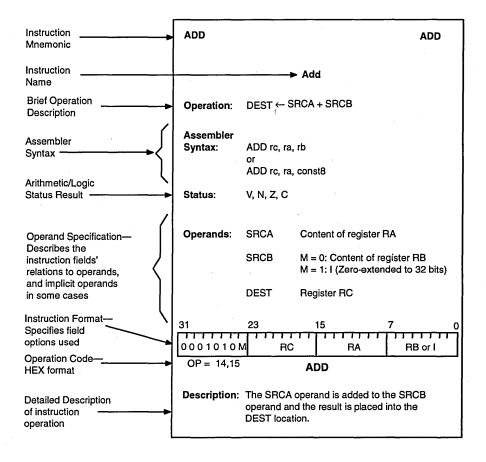

| Figure 18-3    | Instruction-Description Format                                         |       |

| Figure B-1     | General-Purpose Register Organization                                  |       |

| Figure B-2     | Register Bank Organization                                             |       |

| Figure B-3     | Special-Purpose Registers                                              |       |

| Figure C-1     | On-Chip Peripheral Registers                                           | C-1   |

| LIST OF TABLES |                                                                        |       |

| Table 1-1      | Am29200 and Am29205 Microcontrollers: Feature Summary .                | 1-2   |

| Table 2-1      | Integer Arithmetic Instructions                                        | 2-2   |

| Table 2-2      | Compare Instructions                                                   | 2-3   |

| Table 2-3      | Logical Instructions                                                   | 2-4   |

| Table 2-4      | Shift Instructions                                                     | 2-4   |

| Table 2-5      | Data Movement Instructions                                             | 2-5   |

| Table 2-6      | Constant Instructions                                                  | 2-5   |

| Table 2-7      | Floating-Point Instructions                                            | 2-6   |

| Table 2-8      | Branch Instructions                                                    |       |

| Table 2-9      | Miscellaneous Instructions                                             | 2-8   |

| Table 2-10     | Reserved Instructions                                                  | 2-8   |

| Table 7-1      | Internal Peripheral Address Ranges                                     | 7-8   |

| Table 7-2      | Internal Peripheral Address Assignments                                | 7-10  |

| Table 9-1      | Address Multiplexing for 16-bit DRAM Memory                            | 9-5   |

| Table 9-2      | Address Multiplexing for 32-bit DRAM Memory                            | 9-6   |

| Table 9-3      | DRAM Address Multiplexing (by-4 DRAMs)                                 | 9-6   |

| Table 9-4      | DRAM Address Connections to Microcontroller (by-4 DRAMs)               | 9-7   |

| Table 16-1     | Vector Number Assignments                                              |       |

| Table 16-2     | Interrupt and Trap Priority Table                                      | 16-15 |

| Table 17-1     | Instruction Scan Path                                                  | 17-8  |

| Table 17-2     | Main Data Scan Path                                                    | 17-9  |

| Table 17-3     | ICTEST1 Scan Path                                                      | 17-10 |

| Table 17-4     | ICTEST2 Scan Path                                                      | 17-11 |

| Table B-1      | Processor Register Field Summary                                       | B-7   |

| Table C-1      | Peripheral Register Field Summary                                      | C-6   |

## INTRODUCTION AND OVERVIEW

#### Am29200 AND Am29205 RISC MICROCONTROLLERS

The Am29200 and Am29205 microcontrollers are part of a growing family of 32-bit reduced-instruction set (RISC) processors employing submicron circuits to increase the degree of system integration, yielding very low system cost. Dense circuitry and a large number of on-chip peripherals minimize the number of components required to implement embedded systems, while providing performance superior to that of complex-instruction-set (CISC) microprocessors. Systems implemented with the Am29200 or Am29205 microcontroller can achieve higher performance at lower cost than existing systems. The Am29200 and Am29205 microcontrollers are binary compatible with all other members of the 29K Family, further broadening the price/performance range of the 29K Family.

The Am29200 and Am29205 microcontrollers were designed expressly to meet the requirements of embedded applications such as laser printers, graphics processing, application program interface (API) accelerators, X terminals and servers, and scanners. Such applications make the following demands on system design:

- Performance at low cost: A processor must interface with memory and peripherals with a minimum number of external components.

- Design flexibility: One basic design must be extensible to an entire product line.

- Reduced time-to-market: A complete set of development, debug, and benchmarking tools is critical for reducing product development time.

- A rational, easy upgrade path: The processor family must provide bus- and software-compatibility so processor upgrades are transparent to both hardware and software.

The Am29200 and Am29205 microcontrollers are optimized for any embedded application requiring better-than-CISC performance at minimal system cost. The electronic components for many systems, such as personal laser printers, amount to little more than the Am29200 or Am29205 microcontroller, ROM, DRAM, and electrical buffering.

## **DESIGN PHILOSOPHY**

The 29K Family of processors results from a design philosophy that considers processor performance in light of the processor's hardware and software environment. The key to maximizing performance is understanding that the processor is part of an integrated system, and is itself a collection of components that must be properly integrated.

Processor features must be considered not only on their own merits, but also in relation to other components of the system. A particular feature that, while considered alone may increase one aspect of processor performance, may actually decrease the performance of the total system, because of the burden it places elsewhere in the system.

As an illustration, consider the factors involved in the execution time of any processor task:

## Task Time = (Instructions / Task) \* (Cycles / Instruction) \* (Time / Cycle)

To minimize the time taken, it is necessary to minimize the above product. This is not equivalent to minimizing all the terms that contribute to the product; in fact, this is generally not possible due to the interaction of the terms.

As an example of the interaction of the previous terms, consider the number of instructions required for a task. An attempt to minimize this number, a more or less traditional approach to processor architecture design, increases the average number of cycles required for the execution of an instruction, because of the increased number of operations performed by each instruction. In addition, cycle time is increased because of instruction-decode time.

A second example of the interaction in the previous equation appears in an attempt to reduce the cycle time through the pipelining of operations. In theory, the cycle time can be made arbitrarily small by the definition of an arbitrarily large number of pipeline stages. In practice, at least in the case of general-purpose processors, pipelining rarely yields much of its potential benefit. This is due to situations where the pipeline cannot be kept fully occupied, such as when memory references and branches occur. In these situations, additional pipeline stages increase the number of cycles required for an operation, and thus affect the *Cycles / Instruction* term.

## **Optimum Performance**

Each of the terms in the previous equation has some minimum bound for a given implementation technology and task. In general, this minimum bound cannot be approached without an offsetting increase in the other terms, making the overall product less-than-optimum. The question then arises, what combination of terms will yield an optimum product? There are several things to note when answering this question.

The first observation is that the number of operations underlying a given task is more or less fixed. Any single processor ultimately limits the time required for a task because it has a single execution unit and a single instruction stream. The operations that must be performed are reflected in the *Instructions / Task* and *Cycles / Instruction* terms. These operations may be performed by relatively few instructions, where each instruction takes multiple cycles to execute, or by a larger number of instructions, where each takes a single cycle to execute. In the first case, the instructions are complex; in the second, they are simple.

The point is that the trade-off between simple and complex instructions is not one-to-one. For example, reducing the number of cycles per instruction by a factor of three does not increase the number of instructions per task by the same factor. There are two reasons for this. The first is that even when an instruction set supports complex operations, a large proportion of the instructions that are executed perform operations that could be performed as well by simple instructions. The second is that simple instructions expose more of the internal processor operation to an optimizing compiler. This allows the compiler to tailor the organization and sequence of operations to the task at hand, thereby reducing the total number of instructions executed.

## **Performance Leverage**

Another important observation is that there is a tremendous amount of leverage in the *Time / Cycle* and *Cycles / Instruction* terms. As they are made smaller, they have a proportionally greater effect on performance.

For example, a reduction of 10 ns in the cycle time of a processor operating with a 200-ns cycle time yields an increase of 5% in the processor's performance. The same improvement in a processor operating with a 50-ns cycle time yields a 20% increase in performance.

Correspondingly, a reduction of 0.2 in the number of cycles per instruction in a processor averaging 5 cycles per instruction yields a 4% increase in performance. However, the same reduction yields a 12.5% performance increase in a processor that averages 1.6 cycles per instruction.

#### Conclusion

It is possible, and desirable, to increase the number of instructions executed for a given task, and more than make up for the performance impact of this increase by reductions in the cycle time and in the number of cycles per instruction. For example, if both the cycle time and the number of cycles per instruction are reduced by a factor of three, while the number of instructions for a given task is allowed to grow by 50%, the resulting task time is reduced by a factor of six.

The Am29200 and Am29205 microcontrollers were designed with the above effects in mind. Maximum performance is obtained by the optimization of the product of the number of instructions per task, the number of cycles per instruction, and the cycle time, not by minimizing one factor at the expense of the others. This is accomplished by careful definition of all processor components. In particular:

- The Instruction / Task term is optimized by the definition of simple instructions. The processor provides an efficient instruction set and a large number of general-purpose registers to an optimizing, high-level language compiler. Most reductions in this term are accomplished by the compiler. The number of instructions for a given task may be greater than the number of instructions for processors with complex instruction sets. However, this increase is more than offset by other improvements in processor performance.

- The Cycles / Instruction term is optimized by the data-flow structure and performance-enhancing features of the processor. A large amount of processor hardware is dedicated to achieving an average instruction-execution rate that is close to single-cycle execution.

- The *Time / Cycle* term is optimized by the implementation technology, the processor system interface, and judicious use of pipelining. The simplicity of the instruction set and processor features helps minimize the cycle time.

#### **PURPOSE OF THIS MANUAL**

This manual describes the technical features, programming interface, on-chip peripherals, and complete instruction set of the Am29200 and Am29205 microcontrollers.

## **INTENDED AUDIENCE**

This manual is intended for system hardware and software architects and system engineers who are designing or are considering designing systems based on the Am29200 and Am29205 microcontrollers.

#### **USER'S MANUAL OVERVIEW**

This manual contains information on the Am29200 and Am29205 microcontrollers and is essential for system hardware and software architects and design engineers. Additional information is available in the form of data sheets, application notes, and other documentation provided with software products and hardware-development tools.

The information in this manual is organized into eighteen chapters:

- Chapter 1 introduces the features and performance aspects of the Am29200 and Am29205 microcontrollers.

- Chapter 2 describes the programmer's model of the Am29200 and Am29205 microcontrollers, including the instruction set and register model.

- Chapter 3 expands on the programmer's model, discussing different data formats and data handling. Instructions that manipulate external data are also discussed.

- Chapter 4 details the management of the run-time stack and defines the conventions that apply to procedure linkage and register usage.

- Chapter 5 describes the internal **pipelining** and the effects of the pipeline on program behavior.

- Chapter 6 describes the system-protection features provided by the Am29200 and Am29205 microcontrollers.

- Chapter 7 provides an overview of the processor's system interfaces and the system components that are integrated on-chip.

- Chapter 8 describes the ROM interface.

- Chapter 9 describes the DRAM interface.

- Chapter 10 describes the **peripheral interface adapter**, which is used for glueless attachment of a number of peripheral components.

- Chapter 11 describes the DMA controller.

- Chapter 12 describes the programmable I/O port.

- Chapter 13 describes the parallel port.

- Chapter 14 describes the serial port.