# コ

- tester

### **Advanced Micro Devices**

## MOS Microprocessors and Peripherals Military Data Book

#### © 1988 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This data book neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

> 901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088-3000 (408)732-2400 TWX: 910-339-9280 TELEX: 34-6306

Z8000, Z8002 and Z8530 are registered trademarks of Zilog, Inc. MULTIBUS is a registered trademark of Intel Corporation. ť

The Advanced Micro Devices MOS Microprocessors and Peripherals Military Data Book presents military versions of AMD's broad line of MOS fixed-instruction set microprocessors, peripherals, and microcontrollers. AMD has continually provided the military systems designer a complete system solution.

This document used together with AMD's MOS Microprocessors and Peripherals Data Book is your source for innovative military designs.

Today more than ever your satisfaction is essential. At Advanced Micro Devices, we bring you the quality, reliability and innovation you need from a leader in semiconductor VLSI definition, design and manufacturing. Our worldwide hardware and software support teams of field applications engineers are ready to help you utilize our advanced microprogrammable products to complete your designs in a timely and cost-effective manner.

If you have questions about any of the products described in this data book or if you'd like to know more about our product line, call your local AMD Sales office, licensed representative or franchised distributor.

George Rigg Vice President Processor Products Division Advanced Micro Devices

### Introduction

Advanced Micro Devices offers a broad range of military MOS and CMOS fixed-instruction-set microprocessors, peripherals and microcontrollers. These products enable the designer to build sophisticated military systems that meet the latest military quality and reliability standards.

AMD's advanced 32-bit processor, the Am29000, operating at a sustained 17 MIPS level, provides higher levels of performance and flexibility than ever before. This development will open the door to faster and more sophisticated military-system applications.

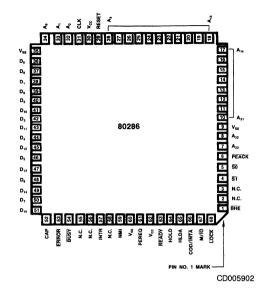

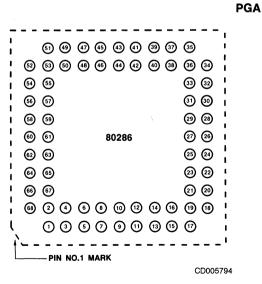

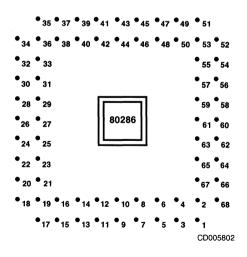

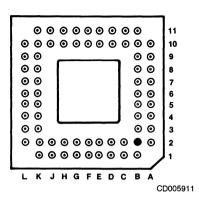

AMD is the number-one alternate source for the iAPX microprocessor family from the 8088/8086 and 80186/80188 to the high-performance 80286. Its military products are fully compatible with the latest revisions of these iAPX processors and are available in a variety of hermetic packages including DIP, PGA and LCC.

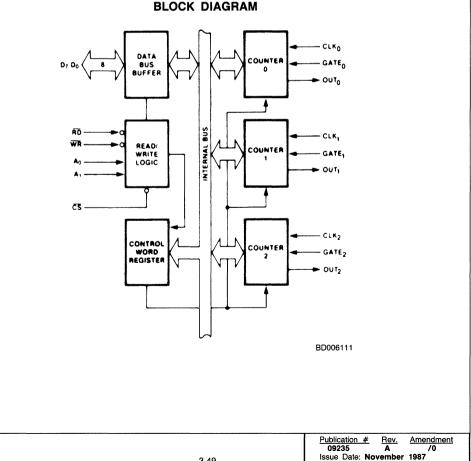

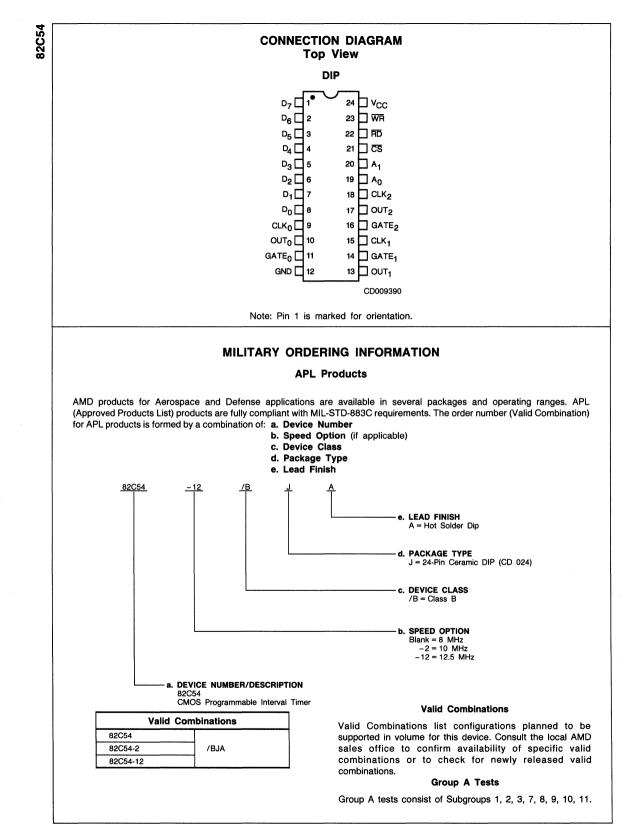

AMD offers military versions — both NMOS and CMOS — of the peripherals that support the iAPX microprocessor family. The 82C54-12/BJA is a high-performance 12-MHz CMOS part replacing the industry-standard 8254 counter/timer. High-performance proprietary advanced peripherals are available including the Am9517A-/BQA DMA Controller, the Am9513A/BQA System-Timing Controller, the Am9516A-4/BXC Advanced DMA Controller, and the industry-standard Z8530 Serial-Communication Controller.

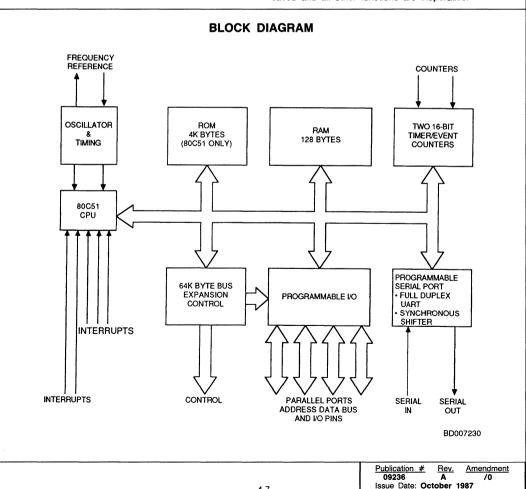

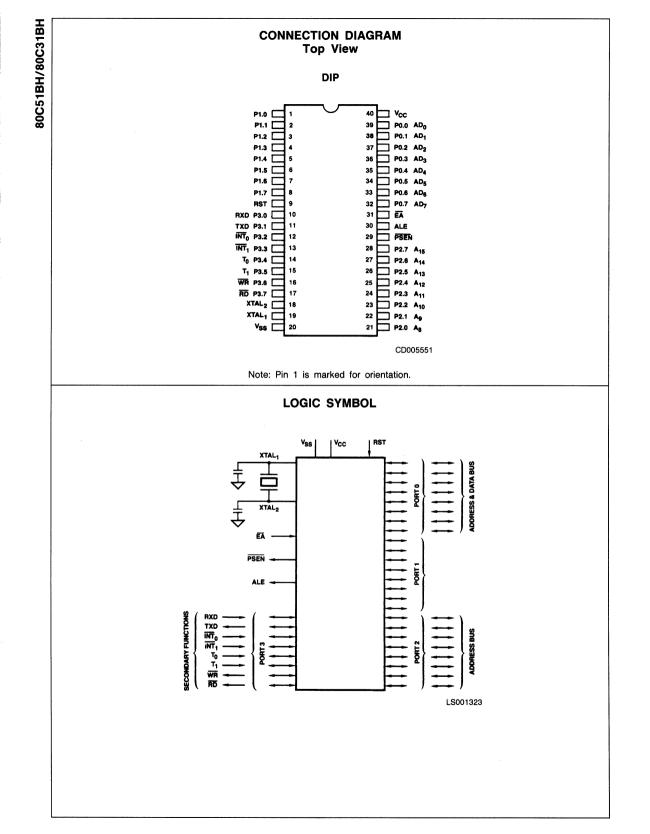

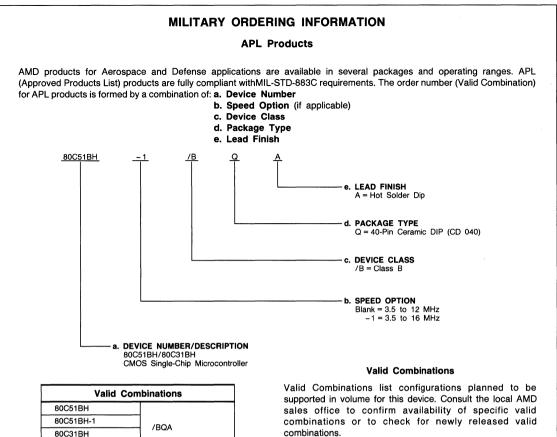

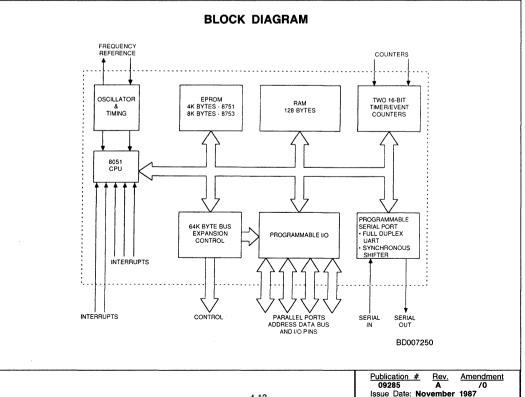

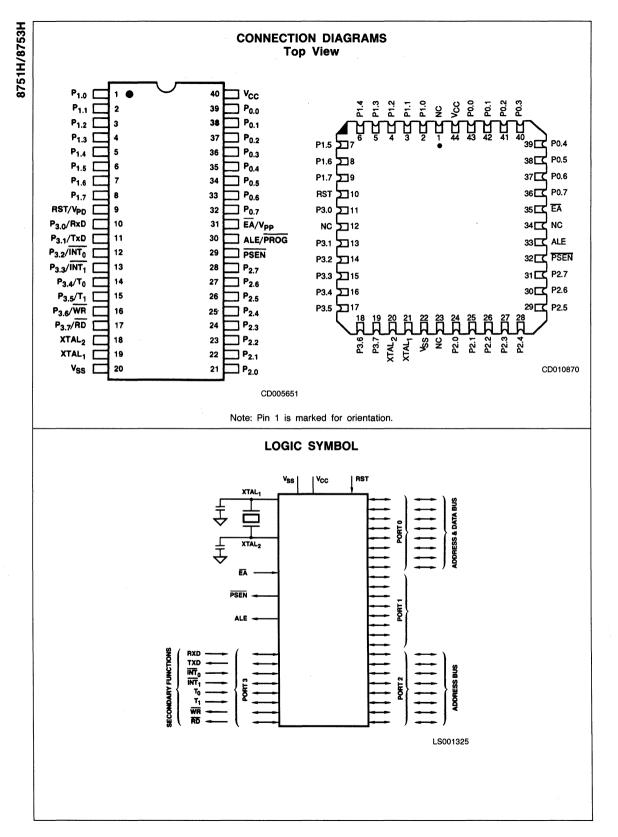

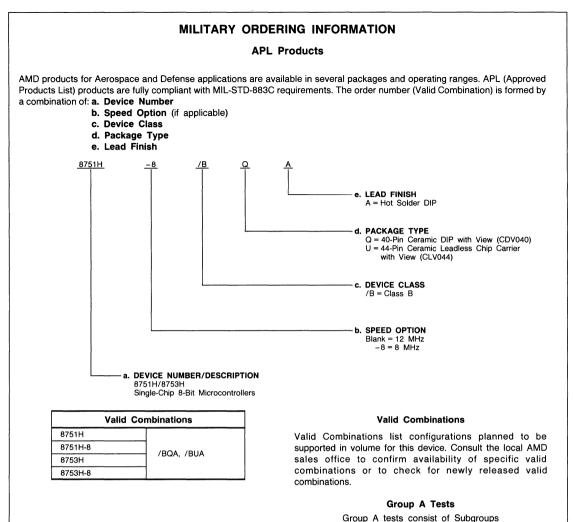

Another family of military products offered by AMD is the popular 8051 microcontroller family. For prototyping or small-volume usage, AMD supplies military options of the 8751 — an EPROM version of the 8051. For applications where more on-chip program memory is required, the 8753 has 8 Kbytes of on-chip EPROM. For high-volume military applications, AMD offers the 80C31/BQA and 80C51/BQA — the CMOS versions of the 8031/8051. These CMOS devices are ideally suited for power-sensitive military applications because they feature idle and power-down modes for additional power conservation.

Advanced Micro Devices' goal is to qualify each of its products at the Defense Electronic Supply Center so that qualified military parts can be purchased without the burden of source-control drawings. AMD's military products are tested to the most stringent military specifications; military flows and testing are based on MIL-M-38510 and MIL-STD-883. If needed, additional testing and screening are available by special order.

For more information on these products or other AMD products, contact your nearest AMD sales office, representative or distributor.

## **Table of Contents**

| CHAPTER 1 |                                                   |      |

|-----------|---------------------------------------------------|------|

|           | Military Product Requirements/Manufacturing Flows | 1-1  |

|           | Military Ordering/Marking Information             | 1-3  |

| CHAPTER 2 |                                                   |      |

|           | Am29000                                           | 2-1  |

|           | Am9511A                                           | 2-2  |

|           | Am9513A*                                          | 2-6  |

|           | Am9516A                                           | 2-13 |

|           | Am9517A*                                          | 2-21 |

|           | Am9519A*                                          | 2-27 |

| CHAPTER 3 |                                                   |      |

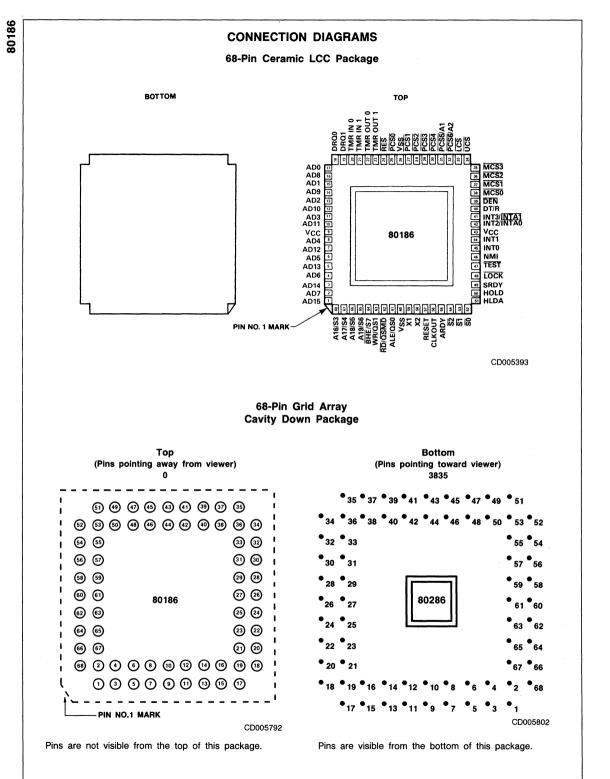

|           | 80186*                                            | 3-1  |

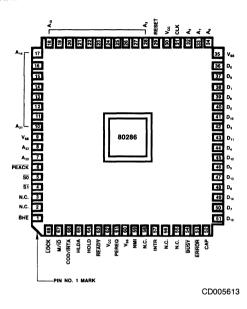

|           | 80286                                             | 3-7  |

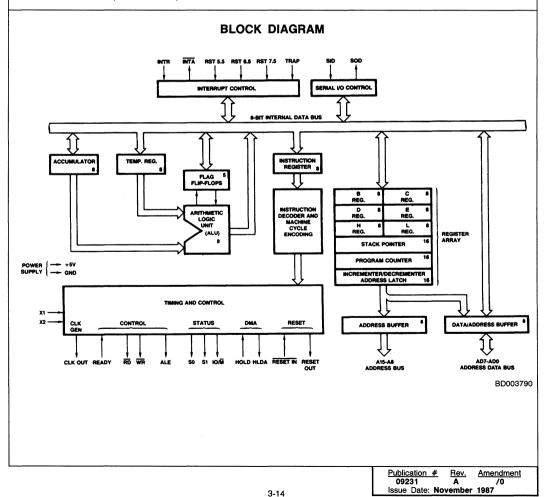

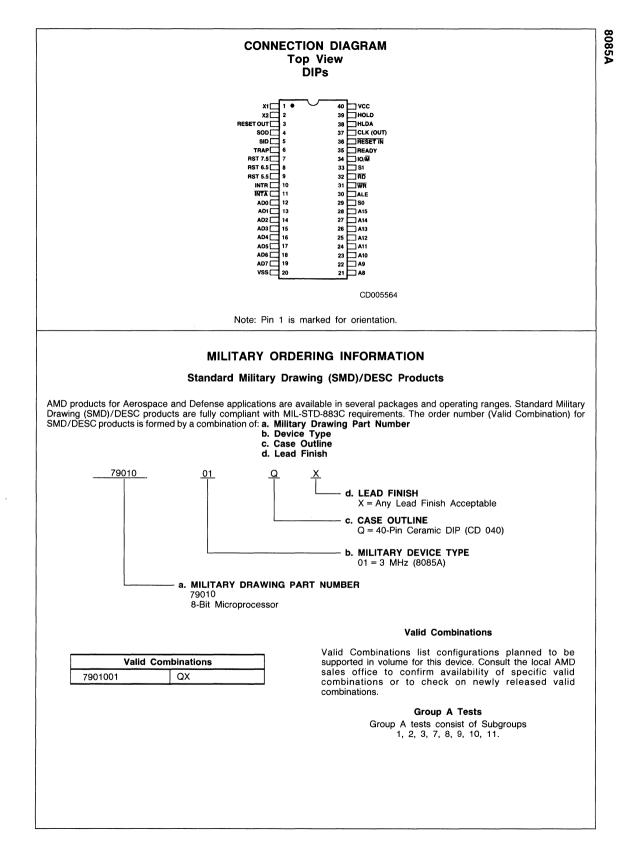

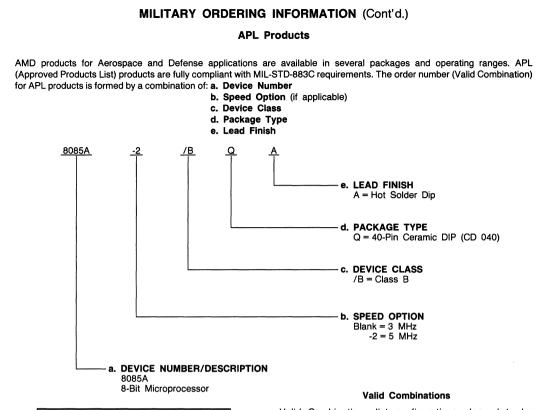

|           | 8085A*                                            | 3-14 |

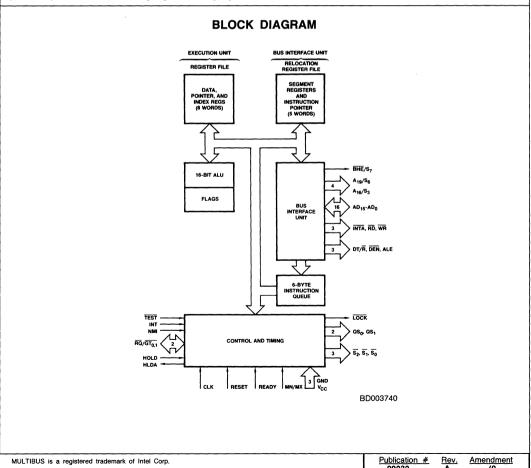

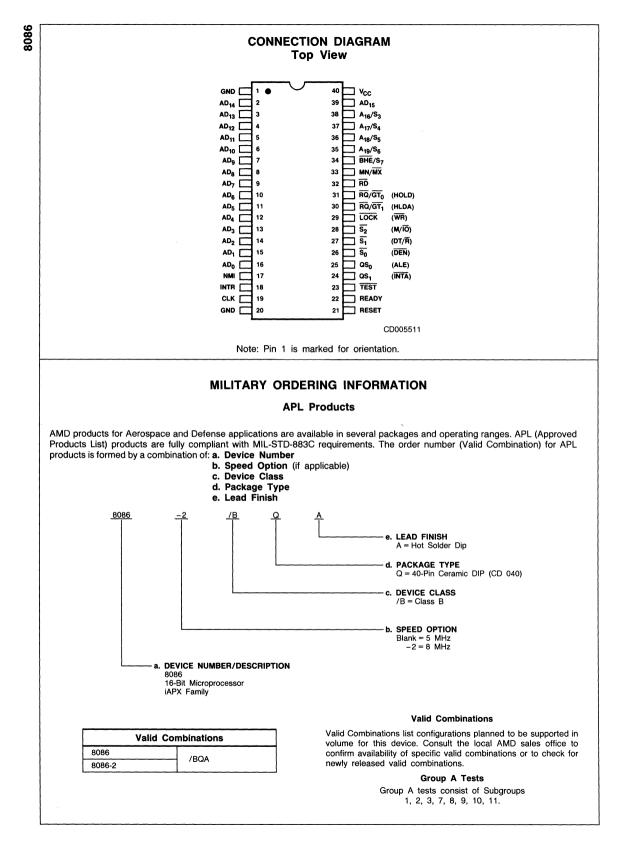

|           | 8086                                              | 3-19 |

|           | 8088*                                             | 3-26 |

|           | 8251/Am9551                                       | 3-33 |

|           | 8251A*                                            | 3-38 |

|           | 8253*                                             | 3-44 |

|           | 82C54                                             | 3-49 |

|           | 8255A*                                            | 3-54 |

|           | 8259A*                                            | 3-59 |

| CHAPTER 4 |                                                   |      |

|           | 8031AH                                            | 4-1  |

|           | 80C51BH/80C31BH                                   | 4-7  |

|           | 8751H/8753H**                                     | 4-13 |

| CHAPTER 5 |                                                   |      |

|           | Z8002                                             | 5-1  |

|           | Z8530**                                           | 5-8  |

| CHAPTER 6 | General Information                               |      |

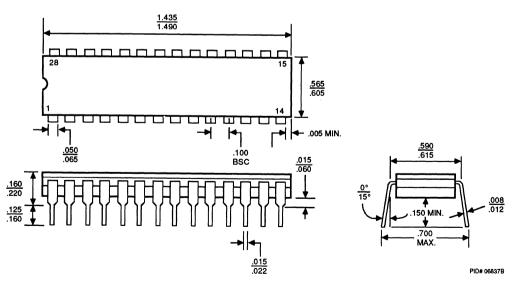

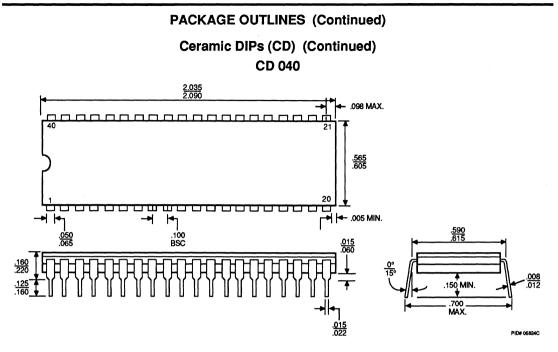

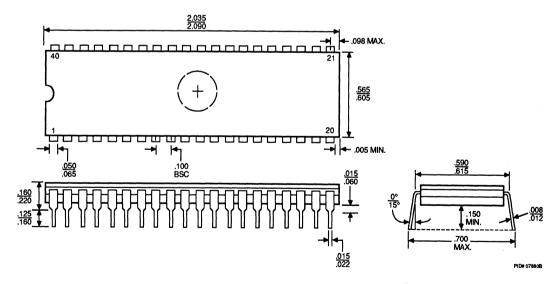

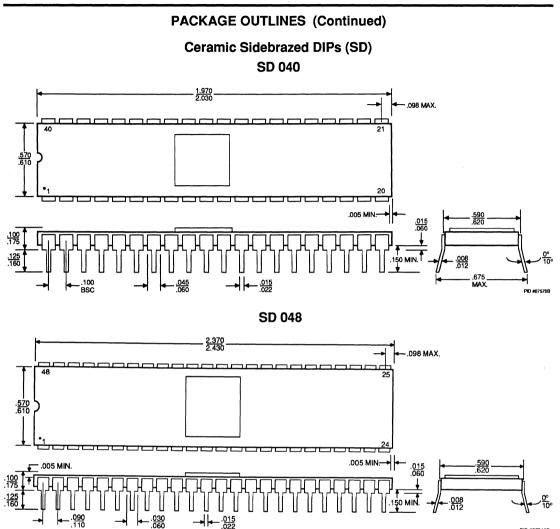

|           | Package Outlines                                  | 6-1  |

|           |                                                   |      |

\*DESC approved \*\*Pending DESC approval

#### NUMERICAL DEVICE LISTING

| Am29000 | Streamlined Instruction Processor           | 2-1  |

|---------|---------------------------------------------|------|

| Z8002   | 16-Bit Microprocessor                       | 5-1  |

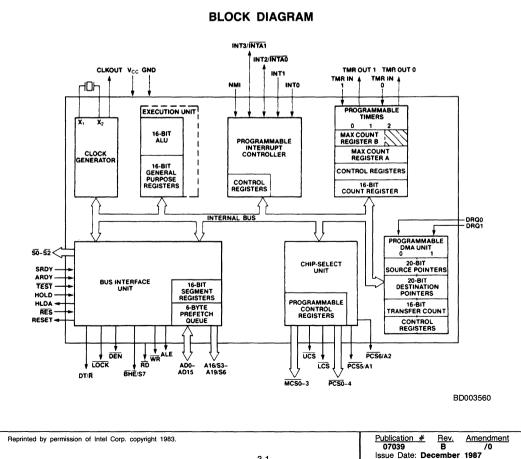

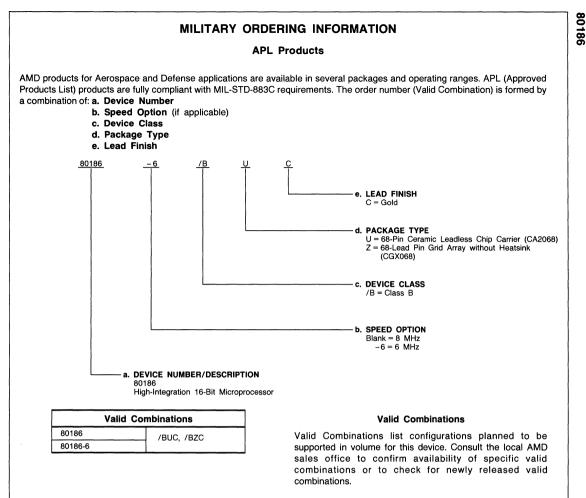

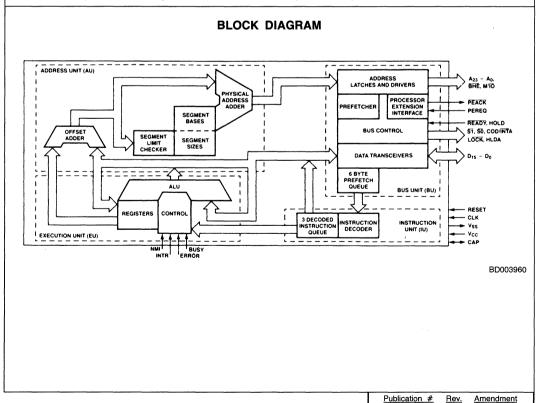

| 80186   | High-Integration 16-Bit Microprocessor      | 3-1  |

| 80286   | High-Performance Microprocessor with Memory |      |

|         | Management and Protection                   | 3-7  |

| 8031AH  | Single-Chip 8-Bit Microcontroller           | 4-1  |

| 80C31BH | CMOS Single-Chip Microcontroller            | 4-7  |

| 80C51BH | CMOS Single-Chip Microcontroller            | 4-7  |

| 8085A   | 8-Bit Microprocessor                        | 3-14 |

| 8086    | 16-Bit Microprocessor                       | 3-19 |

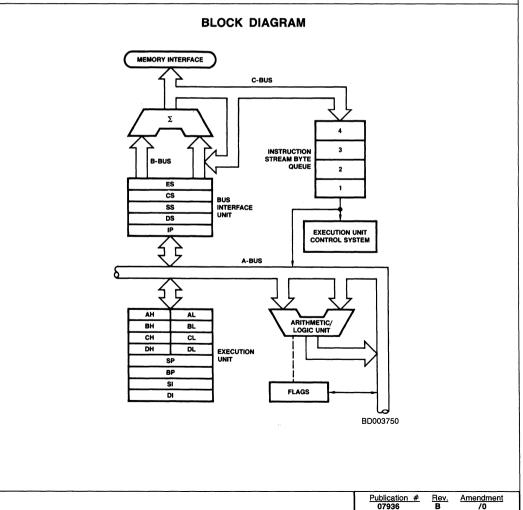

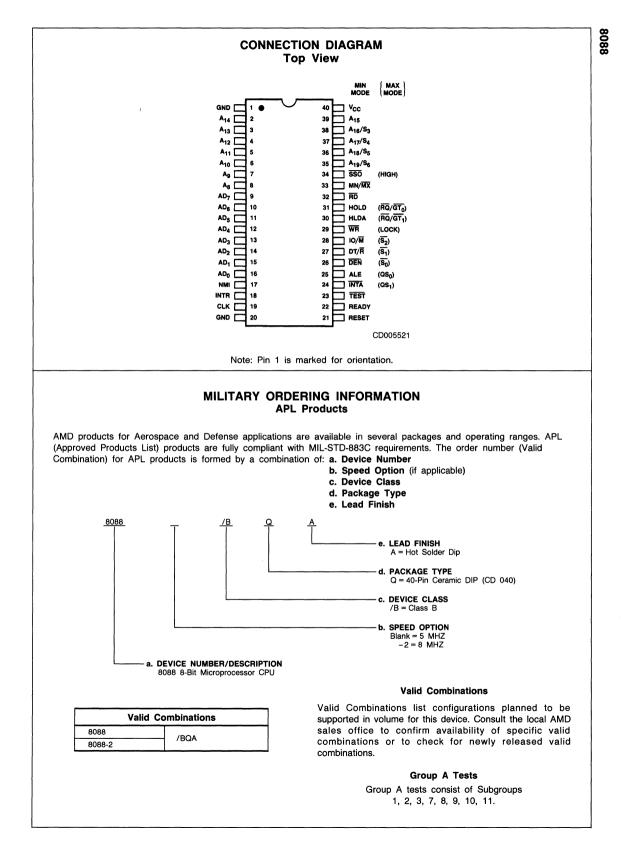

| 8088    | 8-Bit Microprocessor CPU                    | 3-26 |

| 8251    | Programmable Communication Interface        | 3-33 |

| 8251A   | Programmable Communication Interface        | 3-38 |

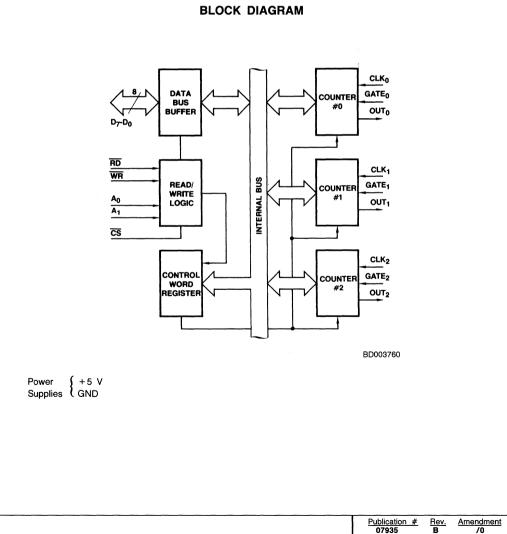

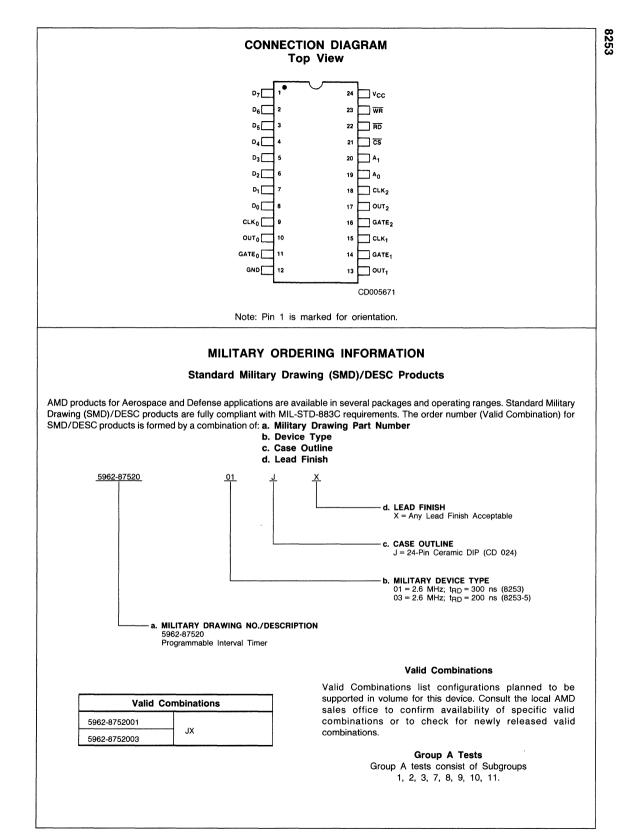

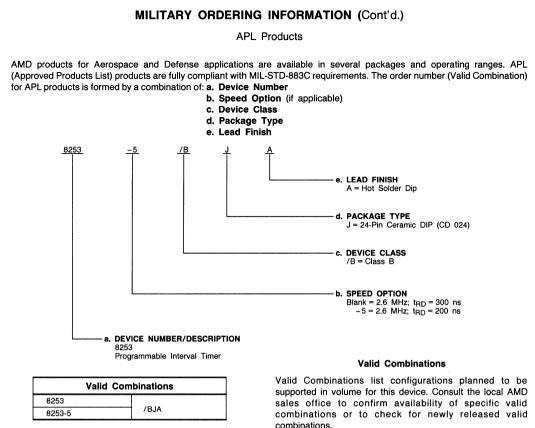

| 8253    | Programmable Interval Timer                 | 3-44 |

| 82C54   | CMOS Programmable Interval Timer            | 3-49 |

| 8255A   | Programmable Peripheral Interface           | 3-54 |

| 8259A   | Programmable Interrupt Controller           | 3-59 |

| Z8530   | Serial Communications Controller            | 5-8  |

| 8751H   | Single-Chip 8-Bit Microcontroller           | 4-13 |

| 8753H   | Single-Chip 8-Bit Microcontroller           | 4-13 |

| Am9511A | Arithmetic Processor                        | 2-2  |

| Am9513A | System Timing Controller                    | 2-6  |

| Am9516A | Universal DMA Controller                    | 2-13 |

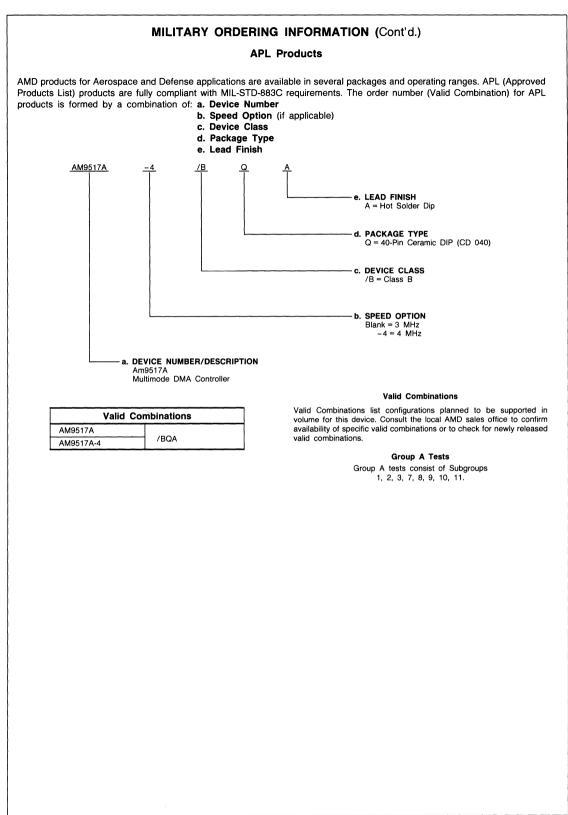

| Am9517A | Multimode DMA Controller                    | 2-21 |

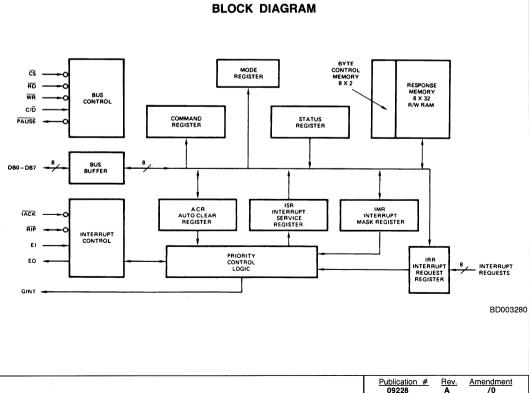

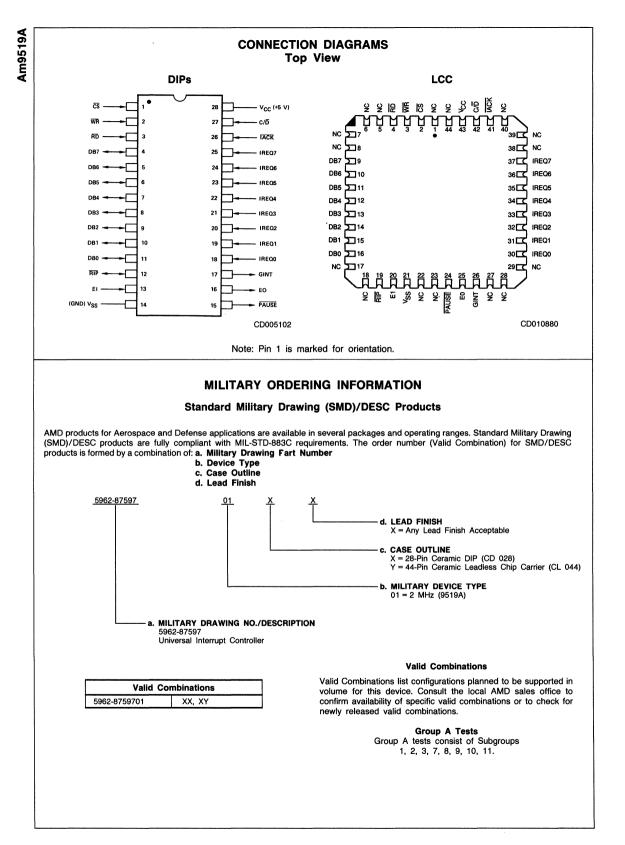

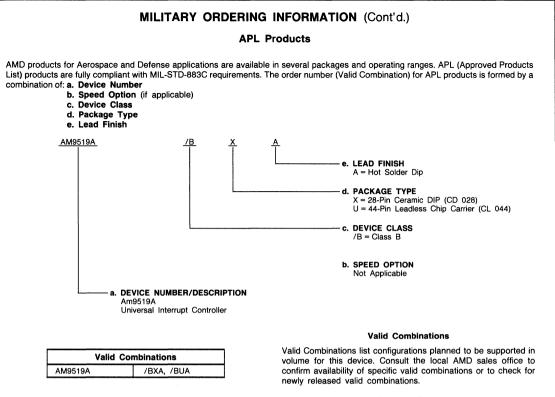

| Am9519A | Universal Interrupt Controller              | 2-27 |

| Am9551  | Programmable Communication Interface        | 3-33 |

|         |                                             |      |

## **CHAPTER 1**

| Military Product Requirements/Manufacturing Flows | 1-1 |

|---------------------------------------------------|-----|

| Military Ordering/Marking Information             | 1-3 |

## Military Manufacturing Flows

|                                                                                                                      |                                                                                                                                                         | Processing Level |                                   |                             |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------|-----------------------------|

| Description of<br>Requirements and Screens                                                                           | MIL-M-38510, MIL-STD-883 Requirements<br>Methods and Test Conditions                                                                                    | Requirement      | DESC                              | 883C Class B<br>(APL)       |

| 1. General MIL-M-38510<br>A. Pre-Certification<br>B. Qualification Test Plan<br>C. Product Assurance<br>Program Plan | The manufacturer shall establish and<br>implement a product-assurance program<br>plan and qualification test plan and submit<br>to qualifying activity. |                  | N/A                               | N/A                         |

| 2. Certification                                                                                                     | DESC survey<br>Manufacturer's Q.A. survey                                                                                                               |                  | N/A<br>X                          | N/A<br>X                    |

| 3. Traceability                                                                                                      | Traceability to wafer production lots                                                                                                                   |                  | х                                 | x                           |

| 4. Country of Origin                                                                                                 | Devices must be manufactured, assembled, and tested within U.S. or its territories.                                                                     |                  | N/A                               | N/A                         |

| MIL-STD-833, Method 5004 Sc                                                                                          | reening                                                                                                                                                 |                  |                                   |                             |

| 5. Internal Visual                                                                                                   | Method 2010 condition B                                                                                                                                 | 100%             | х                                 | x                           |

| 6. Stabilization Bake                                                                                                | Method 1008 condition C                                                                                                                                 | 100%             | х                                 | x                           |

| 7. Temperature Cycle                                                                                                 | Method 1010 condition C<br>(10 cycles, - 65° C to + 150° C)                                                                                             | 100%             | x                                 | x                           |

| 8. Constant Acceleration                                                                                             | Method 2001 condition D or E;<br>Y1 (30 kg in Y, axis)                                                                                                  | 100%             | x                                 | x                           |

| 9. Visual Inspection                                                                                                 | Method 2009 4th Optical Criteria                                                                                                                        | 100%             | х                                 | x                           |

| 10. Hermeticity<br>A. Fine Leak<br>B. Gross Leak                                                                     | Method 1014 condition A or B<br>Method 1014 condition C                                                                                                 | 100%             | x                                 | x                           |

| 11. Interium Electricals<br>(initial class test)                                                                     | Per manufacturers documented data sheet                                                                                                                 | 100%             | x                                 | x                           |

| 12. Burn-In                                                                                                          | Method 1015, condition as specified<br>Minimum 160 hours at 125° C                                                                                      | 100%             | х                                 | x                           |

| 13. Post Burn-In/<br>Final Electrical Test                                                                           | 25° C with 5% PDA and in-line Group A<br>per method 5005                                                                                                | 100%             | х                                 | x                           |

|                                                                                                                      | Data Sheet Limits at cold temperature extreme,<br>with in-line Group A, per method 5005                                                                 | 100%             | x                                 | x                           |

| 14. Lead Finish                                                                                                      | A. Hot solder dip<br>B. Gold                                                                                                                            | 100%             | x                                 | x                           |

| 15. Mark                                                                                                             | Fungus inhibiting ink includes ESD and Part<br>Nomenclature.                                                                                            | 100%<br>596      | X<br>2-8552301<br>+ Vendor<br>P/N | X<br>QX JEDEC 101<br>"/BQA" |

## Military Manufacturing Flows (continued)

|                                            |                                                                                          |                                    | Processing Level             |                              |

|--------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------|------------------------------|------------------------------|

| Description of<br>Requirements and Screens | MIL-M-38510, MIL-STD-883 Requirements<br>Methods and Test Conditions                     | Requirement                        | DESC                         | 883C Class B<br>(APL)        |

| MIL-STD-833, Method 5004 Sc                | reening (continued)                                                                      |                                    |                              |                              |

| 16. Quality Conformance<br>Inspection      | Method 5005 in-line Group B                                                              | Sub-groups<br>B1, B2, B3<br>B4, B5 | x                            | x                            |

| 17. Post Mark/Final Electrical<br>Test     | Data Sheet Limits at hot temperature extreme.<br>Balance of Method 5005, in-line Group A | 100%                               | x                            | x                            |

| 18. Lead Scan/Straighten                   |                                                                                          | AMD 07-549.1<br>100%               | x                            | x                            |

| 19. Hermetic Fine and Gross<br>Leak Sample | Method 1014                                                                              | AMD 06-099<br>Sample               | x                            | x                            |

| 20. Visual/Mechanical/<br>Paperwork        | Method 2009                                                                              | AMD 16-049<br>100%                 | x                            | x                            |

| 21. Pack/Ship                              | Per MIL-M-38510,<br>Includes C of C                                                      | AMD 16-050<br>100%                 | x                            | . X                          |

| Quality Conformance Inspection             | n per Method 5005 of MIL-STD-833 (attributes dat                                         | a only)                            |                              |                              |

| 22. Group A                                | Electrical per slash sheet or manufacturer's data sheets: sub-groups 1-11 as specified.  | Each lot/<br>sublot                | In-line                      | In-line                      |

| 23. Group B                                | Package functional and constructional Each package type on each lot                      |                                    | In-line                      | In-line                      |

| 24. Group C                                | Die related test (1,000 hour operating life).                                            | Each micro-<br>circuit group       | Generic<br>every 52<br>weeks | Generic<br>every 52<br>weeks |

| 25. Group D                                | Package related test.                                                                    | Each package<br>type               | Generic<br>every 52<br>weeks | Generic<br>every 52<br>weeks |

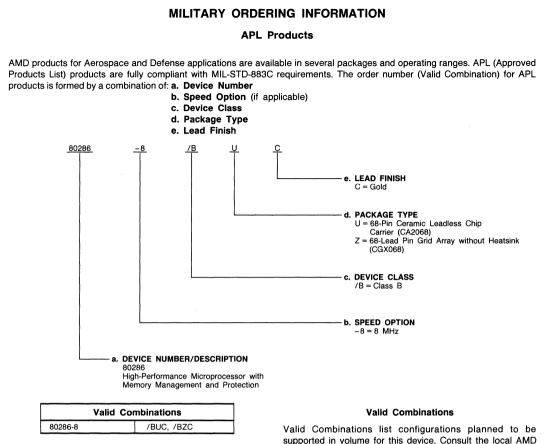

## Military Ordering/Marking Information

MIL-STD-883C devices listed on AMD's <u>Approved Products List are fully compliant to all provisions of paragraph 1.2</u>.

A. Part Number: The complete part number shall be as shown in the following example:

| <u>80186</u> | L     | B      | U       | ç      |

|--------------|-------|--------|---------|--------|

| Device       | Slash | Device | Case    | Lead   |

| Туре         |       | Class  | Outline | Finish |

| (1)          | (2)   | (3)    | (4)     | (5)    |

- 1) Device type is standard generic type including considerations for revision level of die, speed requirements, or limited temperature per M38510.

- 2) A Slash (/) separates the device type and device class.

- 3) The device class is the M38510 product assurance designator, i.e., B=Class B.

- 4) The case outline is in accordance with Appendix C of MIL-M-38510 and listed in AMD's 09-000. See Case Outline Table.

- 5) The lead finish designator shall be as defined in MIL-M-38510 and documented in AMD's 16-018.1. A = Hot Solder Dip

- B = Tin Reflow

- C = Gold

- II. Devices listed utilizing AMD's existing nomenclature are existing products not on the APL/CPL list processed to MIL-STD-883B, Method 5004 and QCI per Method 5005.

A. The part number shall be as shown in the following example:

| <u>Am9511A</u> | D   | М           | <u>B</u> |

|----------------|-----|-------------|----------|

| Device         | Pkg | Military    | Military |

| Туре           |     | Temperature | Burn-in  |

|                |     | Range       |          |

| (1)            | (2) | (3)         | (4)      |

- 1) Standard Generic Part

- Package Configuration

D = Dual-in Line

L = Leadless Chip Carrier

- 3) Military Temperature Range Testing

- 4) Military Burn-in

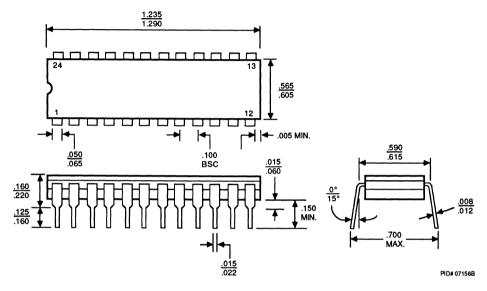

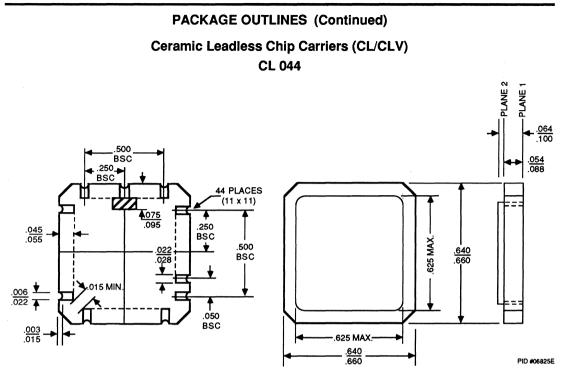

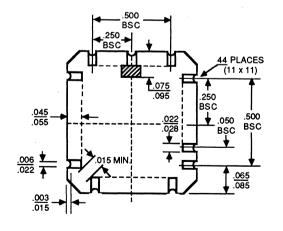

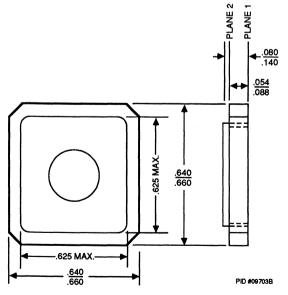

#### Case Outline Table Military Package Designators

Letter Description

- J 24-lead DIP (1/2" x 1-1/4")

- Q 40-lead DIP (9/16" x 2-1/16")

- U 44-terminal SQ. CCP (.650" x .650")

- U 68-terminal SQ. CCP (.950" x .850")

If the case outline or case outline letter is not included in the above table, use letter:

- U For all chip carrier packages.

- X For dual-in-line packages

- (i.e., Cerdips and sidebraze).

- Z For all other configurations (PGAs, etc.).

## **CHAPTER 2**

| Am29000  | 2-1  |  |

|----------|------|--|

| Am9511A  | 2-2  |  |

| Am9513A* | 2-6  |  |

| Am9516A  | 2-13 |  |

| Am9517A* | 2-21 |  |

| Am9519A* | 2-27 |  |

| Am9517A* | 2-21 |  |

# Am29000

#### Streamlined Instruction Processor

#### ADVANCE INFORMATION

#### DISTINCTIVE CHARACTERISTICS

- · Full 32-bit, three-bus architecture

- 17 million instructions per second (MIPS) sustained

- 25-MHz operating frequency

- Efficient execution of high-level language programs

- CMOS technology

- 4-gigabyte virtual address space with demand paging

- Concurrent instruction and data accesses .

- Burst-mode access support

- 192 general-purpose registers

- 512-byte Branch Target Cache

- 64-entry Memory-Management Unit

- De-multiplexed, pipelined address, instruction, and data buses

- Three-address instruction architecture

#### **GENERAL DESCRIPTION**

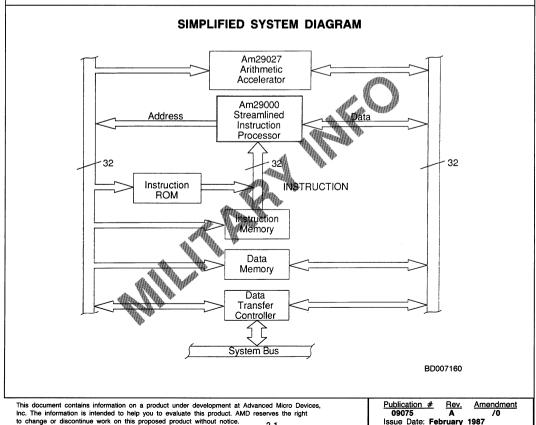

The Am29000 Streamlined Instruction Processor is a highperformance, general-purpose, 32-bit microprocessor implemented in CMOS technology. It supports a variety of applications, by virtue of a flexible architecture and rapid execution of simple instructions which are common to a wide range of tasks.

The Am29000 efficiently performs operations common to all systems, while deferring most decisions on system policies to the system architect. It is well suited for application in high-performance workstations, general-purpose super-minicomputers, high-performance real-time controllers, laser printer controllers, network protocol converters, and many other applications where high-performance, flexibility, and the ability to program using standard software tools is important.

The Am29000 instruction set has been influenced by the results of high-level-language, optimizing-compiler research. It is appropriate for a variety of languages, because it efficiently executes operations which are common to all languages. Consequently, the Am29000 is an ideal target for high-level languages such as C. Fortran, Pascal, and ADA.

The processor is packaged in a 169-terminal pin-grid-array (PGA) package, using 141 signal pins, 27 power and ground pins, and 1 alignment pin. A representative system diagram is shown below.

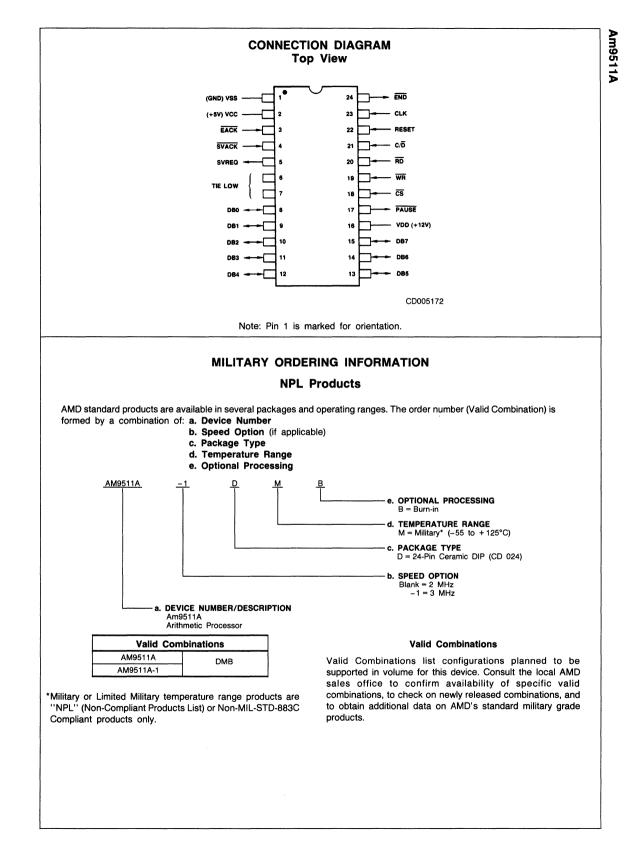

# Am9511A

#### Arithmetic Processor

#### MILITARY INFORMATION

#### **DISTINCTIVE CHARACTERISTICS**

- 2 and 3 MHz operation; fixed point 16-bit and 32-bit operations

- · Floating point 32-bit operations; binary data formats

- Add, Subtract, Multiply and Divide; trigonometric and inverse trigonometric functions

- Square roots, logarithms, exponentiation; float-to-fixed fixed-to-float conversions

- Stack-oriented operand storage; DMA or programmed I/O data transfers

- End signal simplifies concurrent processing; Synchronous/Asynchronous operations

- General purpose 8-bit data bus interface; standard 24pin package

#### GENERAL DESCRIPTION

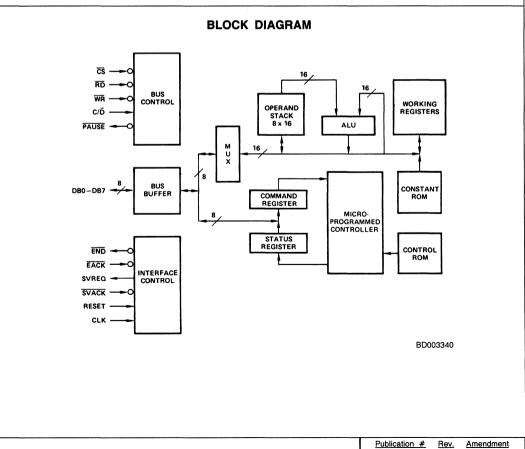

The Am9511A Arithmetic Processing Unit (APU) is a monolithic MOS/LSI device that provides high-performance fixed and floating point arithmetic and a variety of floating point trigonometric and mathematical operations. It may be used to enhance the computational capability of a wide variety of processor-oriented systems.

All transfers, including operand, result, status, and command information, take place over an 8-bit bidirectional data bus. Operands are pushed onto an internal stack, and a command is issued to perform operations on the data in the stack. Results are then available to be retrieved from the stack, or additional commands may be entered.

Transfers to and from the APU may be handled by the associated processor using conventional programmed I/O, or may be handled by a direct memory access controller for improved performance. Upon completion of each command, the APU issues an end-of-execution signal that may be used as an interrupt by the CPU to help coordinate program execution.

09224 A /0 Issue Date: December 1987

2-3

# Am9511A

#### **ABSOLUTE MAXIMUM RATINGS**

#### **OPERATING RANGES**

| Storage Temperature65 to +150°C                                  |

|------------------------------------------------------------------|

| V <sub>DD</sub> with Respect to V <sub>SS</sub> 0.5 V to +15.0 V |

| V <sub>CC</sub> with Respect to V <sub>SS</sub> 0.5 V to +7.0 V  |

| All Signal Voltages                                              |

| with Respect to V <sub>SS</sub> 5.0 V to +7.0 V                  |

| Power Dissipation (Package Limitation)2.0 W                      |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### DC CHARACTERISTICS over operating range

Operating ranges define those limits between which the functionality of the device is guaranteed.

| Parameter<br>Symbol | Parameter<br>Description       | Test Conditions                 | Min.   | Max. | Unit |

|---------------------|--------------------------------|---------------------------------|--------|------|------|

| VOH                 | Output HIGH Voltage            | I <sub>OH</sub> = -200 μA       | 3.7    |      | v    |

| VOL                 | Output LOW Voltage             | I <sub>OL</sub> = 3.2 mA        |        | 0.4  | v    |

| VIH                 | Input HIGH Voltage             |                                 | 20     | Vcc* | v    |

| VIL                 | Input LOW Voltage              |                                 | -0.5*  | 0.8  | v    |

| ll <sub>X</sub>     | Input Load Current             | $V_{SS} \leq VI \leq V_{CC}$    |        | ±10  | μA   |

| loz                 | Data Bus Leakage               | $V_0 = 0.4 V$<br>$V_0 = V_{00}$ | 10     | 10   | μA   |

| lcc                 | V <sub>CC</sub> Supply Current |                                 |        | 100  | mA   |

| CAPACIT             | ANCE                           |                                 |        | r    |      |

| Symbol              | Description                    | Test Conditions                 | Min.   | Max. | Unit |

| Co                  | Output Capacitance             |                                 |        | 10*  | pF   |

| CI                  | Input Capacitance              | $f_C = 1.0$ MHz, Inputs = 0 V   |        | 8*   | pF   |

| CIO                 | I/O Capacitance                |                                 |        | 12*  | pF   |

| Not tested a        | uaranteed by design.           |                                 |        |      |      |

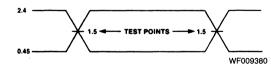

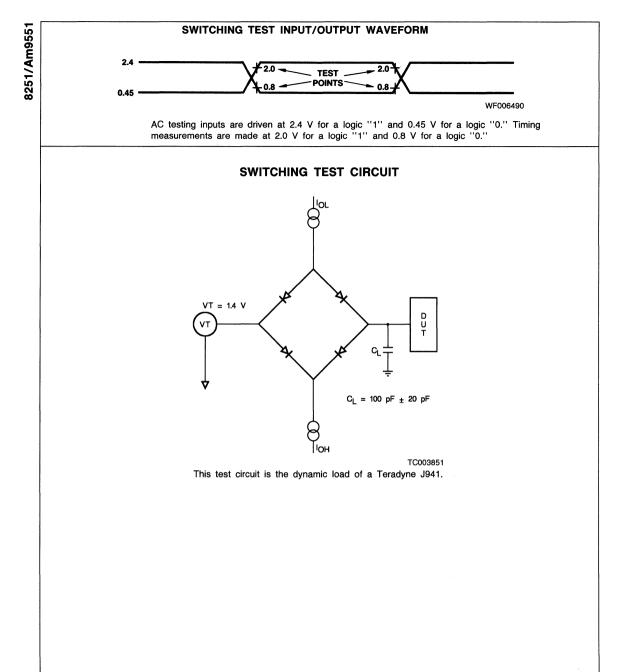

|                     | 2.4                            |                                 |        |      |      |

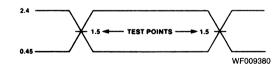

|                     | 0.45                           | LO.8 POINTS 0.8                 | WF0040 | 60   |      |

|                     |                                |                                 |        |      |      |

|                     |                                |                                 |        |      |      |

|                     |                                |                                 |        |      |      |

|                     |                                |                                 |        |      |      |

|                     |                                |                                 |        |      |      |

|                     |                                |                                 |        |      |      |

|                     |                                |                                 |        |      |      |

#### SWITCHING CHARACTERISTICS over operating range

| <b>B</b>            |                                              |          | Am9         | 511A                       | Am95        | 11A-1        |      |

|---------------------|----------------------------------------------|----------|-------------|----------------------------|-------------|--------------|------|

| Parameter<br>Symbol | Parameter<br>Description                     |          | Min.        | Max.                       | Min.        | Max.         | Unit |

| TAPW                | EACK LOW Pulse Width                         |          | 100         |                            | 75          |              | ns   |

| TCDR                | C/D to RD LOW Setup Time                     |          | 0           |                            | 0           |              | ns   |

| TCDW                | C/D to WR LOW Setup Time                     |          | 0           |                            | 0           |              | ns   |

| тсрн                | Clock Pulse HIGH Width                       |          | 200         |                            | 140         |              | ns   |

| TCPL                | Clock Pulse LOW Width                        |          | 240         |                            | 160         |              | ns   |

| TCSR                | CS LOW to RD LOW<br>Setup Time               |          | 0           |                            | 0           |              | ns   |

| TCSW                | CS LOW to WR LOW Setup Time                  |          | 0           |                            | 0           |              | ns   |

| TCY                 | Clock Period                                 |          | 480         | 5000                       | 320         | 3300         | ns   |

| TDW                 | Data Bus Stable to WR<br>HIGH Setup Time     |          | 150         |                            | 150         |              | ns   |

| TEAE                | EACK LOW to END HIGH Delay                   |          |             | 200                        |             | 175          | ns   |

| TEPW                | END LOW Pulse Width (Note 4)                 |          | 400         | The second second          | 270         |              | ns   |

| TOP                 | Data Bus Output Valid to<br>PAUSE HIGH Delay |          | 0           |                            | 0           |              | ns   |

| TPPWR               | PAUSE LOW Pulse                              | Data     | 3,5TCY + 50 | <sup>19</sup> 5.5TCY + 300 | 3.5TCY + 50 | 5.5TCY + 200 | ns   |

| IPPWR               | Width Read (Note 5)                          | Status   | 5TCY 50     | 3.5TCY + 300               | 1.5TCY + 50 | 3.5TCY + 200 |      |

| TPPWW               | PAUSE LOW Pulse Width Write<br>(Note 8)      | -        |             | 50                         |             | 50           | ns   |

| TPR                 | PAUSE HIGH to RD<br>HIGH Hold Time           |          | 0           |                            | 0           |              | ns   |

| TPW                 | PAUSE HIGH to WR<br>HIGH Hold Time           | al k     | 0           |                            | 0           |              | ns   |

| TRCD                | RD HIGH to C/D Hold Time                     |          | 0           |                            | 0           |              | ns   |

| TRCS                | RD HIGH to CS HIGH Hold Time                 | ф.<br>ф. | 0           |                            | 0           |              | ns   |

| TRO                 | RD LOW to Data Bus ON Delay                  |          | 50          |                            | 50          |              | ns   |

| TRP                 | RD LOW to PAUSE LOW<br>Delay (Note 6)        |          |             | 150                        |             | 150          | ns   |

| TRZ                 | RD HIGH to Data Dus OFF Delay                |          | 50          | 200                        | 50          | 150          | ns   |

| TSAPW               | SVACK LOW Pulse Width                        |          | 100         |                            | 75          |              | ns   |

| TSAR                | SVACK LOW to SVREQ<br>LOW Delay              |          |             | 300                        |             | 200          | ns   |

| TWCD                | WR HIGH to C/D Hold Time                     |          | 60          |                            | 30          |              | ns   |

| TWCS                | WR HIGH to CS HIGH Hold Time                 |          | 60          |                            | 30          |              | ns   |

| TWD                 | WR HIGH to Data Bus Hold Time                |          | 20          |                            | 20          |              | ns   |

| TWI                 | Write Inactive Time                          | Command  | 4TCY        |                            | 4TCY        |              | ne   |

| 1 441               | while mactive time                           | Data     | 5TCY        |                            | 5TCY        |              | — ns |

| TWP                 | WR LOW to PAUSE LOW<br>Delay (Note 6)        |          |             | 150                        |             | 150          | ns   |

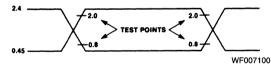

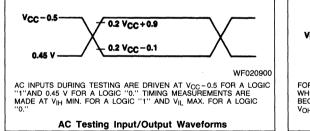

Notes: 1. Typical values are for T<sub>A</sub> = 25°C, nominal supply voltages and nominal processing parameters.

2. Switching parameters are listed in alphabetical order.

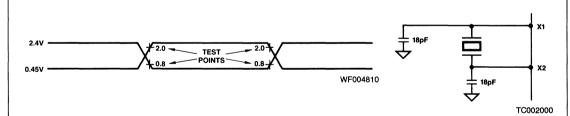

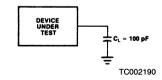

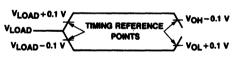

3. Test conditions assume transition times of 20 ns or less, output loading of one TTL gate plus 100 pF ±20 pF and timing reference levels of 0.8 V and 2.0 V.

END low pulse width is specified for EACK tied to V<sub>SS</sub>. Otherwise TEAE applies.

Minimum values shown assume no previously entered command is being executed for the data access. If a previously entered command is being executed, PAUSE LOW Pulse Width is the time to complete execution plus the time shown. Status may be read at any time without exceeding the time shown. 6. PAUSE is pulled low for both command and data operations. 7. <u>TEX is</u> the execution time of the current command (see the Command Execution Times table).

PAUSE to be executed rune of the content command (see the command executed runes table).

PAUSE low pulse width is less than 50 ns when writing into the data port or the control port as long as the duty requirement (TWI) is observed and no previous command is being executed. TWI may be safely violated up to 500 ns as long as the extended TPPWW that results is observed. If a previously entered command is being executed, PAUSE LOW Pulse Width is the time to complete execution plus the time shown.

# Am9513A

System Timing Controller

#### MILITARY INFORMATION

#### DISTINCTIVE CHARACTERISTICS

- Am9513A

- SMD/DESC qualified

- Five independent 16-bit counters

- High speed counting rates

- Up/down and binary/BCD counting

- Internal oscillator frequency source

- Tapped frequency scaler

- Programmable frequency output

- 8-bit or 16-bit bus interface

- Time-of-day option

- Alarm comparators on counters 1 and 2

- One-shot or continuous outputs

- Programmable count/gate source selection

- Programmable input and output polarities

- Programmable gating functions

- Retriggering capability

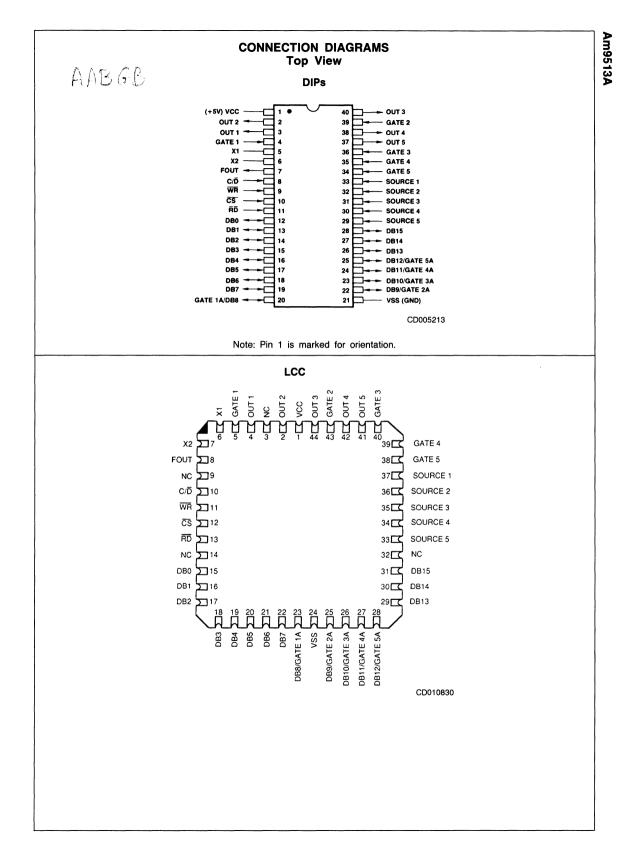

- Standard 40-pin DIP package; 44-Pin LCC

#### **GENERAL DESCRIPTION**

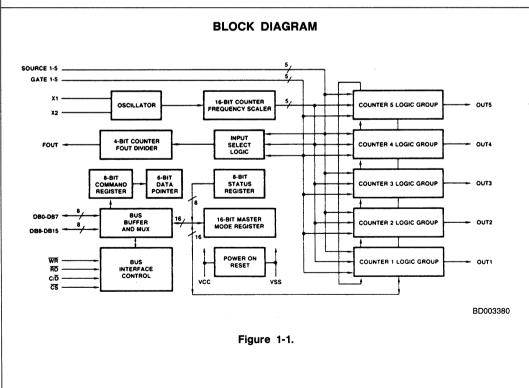

The Am9513A System Timing Controller is an LSI circuit designed to service many types of counting, sequencing and timing applications. It provides the capability for programmable frequency synthesis, high resolution programmable duty cycle waveforms, retriggerable digital oneshots, time-of-day clocking, coincidence alarms, complex pulse generation, high resolution baud rate generation, frequency shift keying, stop-watching timing, event count accumulation, waveform analysis, etc. A variety of programmable operating modes and control features allow the Am9513A to be personalized for particular applications as well as dynamically reconfigured under program control. The STC includes five general-purpose 16-bit counters. A variety of internal frequency sources and external pins may be selected as inputs for individual counters with software selectable active-high or active-low input polarity. Both hardware and software gating of each counter is available. Three-state outputs for each counter provide pulses or levels and can be active-high or active-low. The counters can be programmed to count up or down in either binary or BCD. The host processor may read an accumulated count at any time without disturbing the counting process. Any of the counters may be internally concatenated to form any effective counter length up to 80 bits.

Publication #<br/>09225Rev.<br/>AAmendment<br/>/0Issue Date:November1987

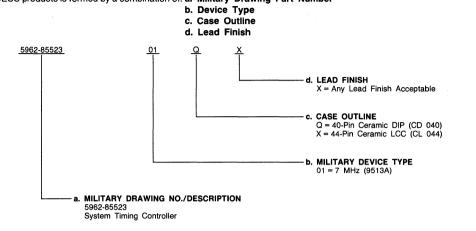

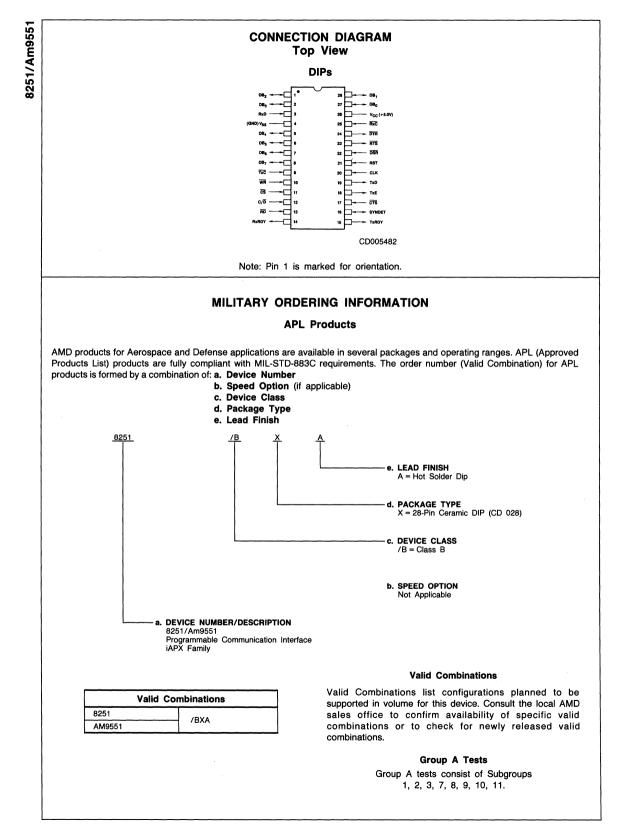

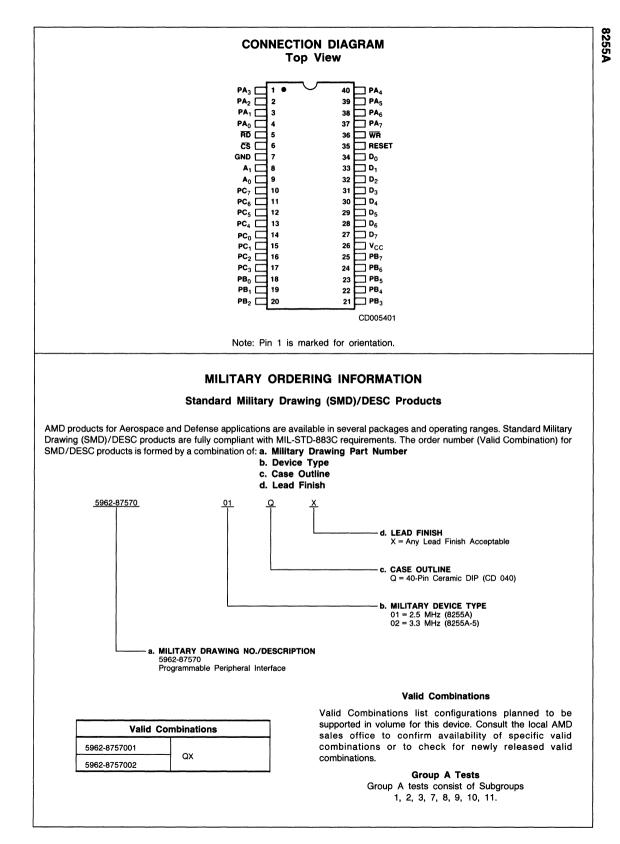

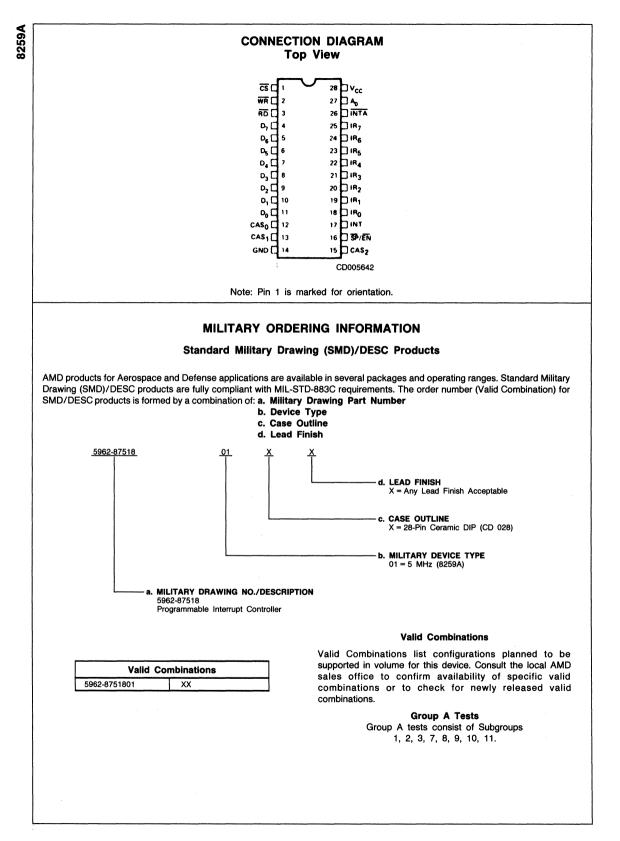

#### Standard Military Drawing (SMD)/DESC Products

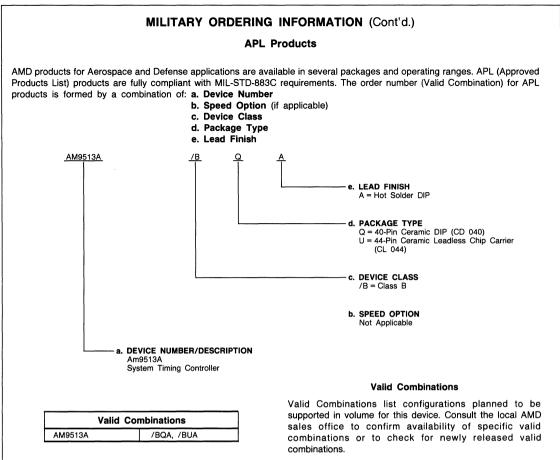

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. Standard Military Drawing (SMD)/DESC products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for SMD/DESC products is formed by a combination of: **a. Military Drawing Part Number**

| Valid Combinations |        |  |  |  |

|--------------------|--------|--|--|--|

| 5962-8552301       | QX, XX |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

> Group A Tests Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### Group A Tests Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

Am9513A

#### ABSOLUTE MAXIMUM RATINGS

#### **OPERATING RANGES**

Storage Temperature ......-65°C to +150°C VCC with Respect to VSS ......-0.5 V to +7.0 V All Signal Voltages with Respect to VSS ......-0.5 V to +7.0 V

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability. Operating ranges define those limits between which the functionality of the device is guaranteed.

## **DC CHARACTERISTICS** over operating range (for SMD/DESC and APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol |                         | imeter<br>ription     | Test Conditions                                | Min.       | Max. | Unit |

|---------------------|-------------------------|-----------------------|------------------------------------------------|------------|------|------|

|                     | Innut I and Maltana     | All Inputs Except X2  |                                                | VSS - 0.5* | 0.8  | v    |

| VIL                 | Input Low Voltage       | X2 Input              |                                                | VSS - 0.5* | 0.8  | 1 V  |

|                     |                         | All Input Except X2   |                                                | 2.2 V      | VCC* | v    |

| VIH                 | Input High Voltage      | X2 Input              |                                                | 3.8        | VCC* | l v  |

| VITH                | Input Hysteresis (SRC a | ind GATE Inputs Only) |                                                | 0,2        |      | V    |

| VOL                 | Output Low Voltage      | W allow               | IOL = 3.2 mA                                   |            | 0.4  | V    |

| VOH                 | Output High Voltage     |                       | IOH = -200 μA                                  | 2.4        |      | V    |

| lix                 | Input Load Current (Exc | ept X2)               | $VSS \leq VIN \leq VCC$                        |            | ±10  | μA   |

| IIX                 | Input Load Current X2   |                       | $VSS \le VIN \le VCC$                          |            | ±100 | μA   |

| IOZ                 | Output Leakage Ourrent  | (Except X1)           | VSS + 0.4 ≤ VOUT ≤ VCC<br>High-Impedance State |            | ±25  | μA   |

| ICC                 | VCC Supply Current (St  | eady State)           |                                                |            | 275  | mA   |

| CIN †               | Input Capacitance       |                       | f = 1 MHz, T <sub>C</sub> = + 25°C.            |            | 20*  |      |

| COUT †              | Output Capacitance      |                       | All pins not under                             |            | 20*  | pF   |

| CIO †               | IN/OUT Capacitance      | test at 0 V.          |                                                |            | 20*  | 1    |

\* Guaranteed by design; not tested.

† Not included in Group A tests.

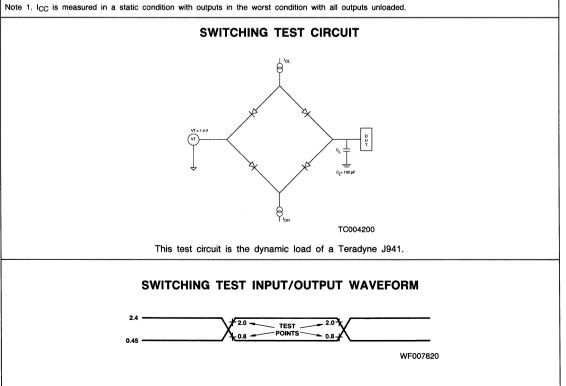

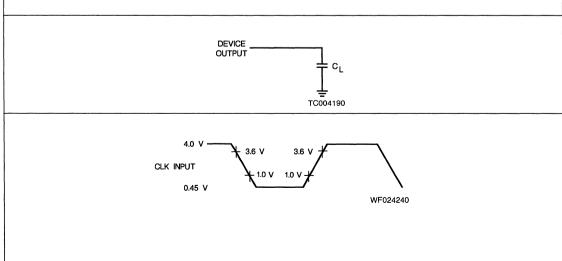

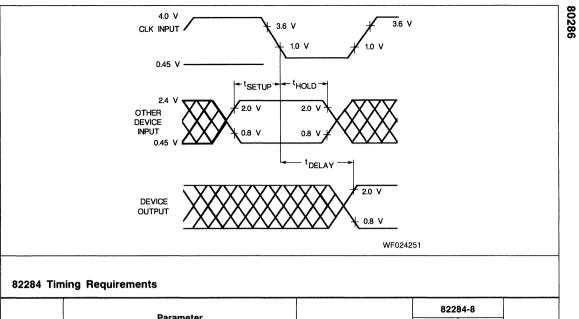

#### SWITCHING TEST INPUT/OUTPUT WAVEFORMS

Crystal is fundamental mode parallel resonant 32 pF load capacitance less than 100  $\Omega$  ESR C<sub>0</sub> less than 100 pF.

SWITCHING CHARACTERISTICS over operating range (for SMD/DESC and APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

|                     |                                                                                | Am9   | 513A |     |

|---------------------|--------------------------------------------------------------------------------|-------|------|-----|

| Parameter<br>Symbol | Parameter<br>Description                                                       | Min.  | Max. | Uni |

| TAVRL               | C/D Valid to Read Low                                                          | 25    |      | ns  |

| TAVWH               | C/D Valid to Write High                                                        | 170   |      | ns  |

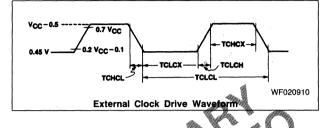

| тснсн               | X2 High to X2 High (X2 Period) (Note 13)                                       | 145   |      | ns  |

| TCHCL               | X2 High to X2 Low (X2 High Pulse Width) (Note 13)                              | 70    |      | ns  |

| TCLCH               | X2 Low to X2 High (X2 Low Pulse Width) (Note 13)                               | 70    |      | ns  |

| TDVWH               | Data In Valid to Write High                                                    | 80    |      | ns  |

| ТЕНЕН               | Count Source High to Count Source High<br>(Source Cycle Time) (Note 7)         | 145   |      | ns  |

| TEHEL<br>TELEH      | Count Source Pulse Duration (Note 7)                                           | 70    |      | ns  |

| TEHFV               | Count Source High to FOUT Valid (Note 7)                                       |       | 500  | ns  |

| TEHGV               | Count Source High to Gate Valid (Level Gating Hold Time)<br>(Notes 7, 9, 10)   | 10    |      | ns  |

| TEHRL               | Count Source High to Read Low (Set-up Time) (Notes 2, 7)                       | 190   |      | ns  |

| TEHWH               | Count Source High to Write High (Set-up Time) (Notes 3, 7)                     | - 100 |      | ns  |

|                     | TC Output                                                                      |       | 300  |     |

| TEHYV               | Count Source High to Out Valid (Note 7) Immediate or Delayed Toggle Output     |       | 300  | ns  |

|                     | Comparator Output                                                              |       | 350  |     |

| TFN                 | FN High to FN + 1 Valid (Note 11)                                              |       | 75   | ns  |

| TGVEH               | Gate Valid to Count Source High (Level Gating Set-up Time)<br>(Notes 7, 9, 10) | 100   |      | ns  |

| TGVGV               | Gate Valid to Gate Valid (Gate Pulse Duration) (Notes 8, 10)                   | 145   |      | ns  |

| TGVWH               | Gate Valid to Write High (Notes 3, 10)                                         | -100  |      | ns  |

| TRHAX               | Read High to C/D Don't Care                                                    | 0     |      | ns  |

| TRHEH               | Read High to Count Source High (Notes 4, 7)                                    | 0     |      | ns  |

| TRHQX               | Read High to Data Out Invalid                                                  | 10    |      | ns  |

| TRHQZ               | Read High to Data Out int High-Impedance<br>(Data Bus Release Time)            |       | 85   | ns  |

| TRHRL               | Read High to Read Low (Read Recovery Time)                                     |       |      | ns  |

| TRHSH               | Read High to CS High (Note 12)                                                 |       |      | ns  |

| TRHWL               | Read High to Write Low (Read Recovery Time)                                    | 1000  |      | ns  |

| TRLQV               | Read Low to Data Out Vand                                                      |       | 110  | ns  |

| TRLQX               | Read Low to Data Bus Driven (Data Bus Drive Time)                              | 20    |      | ns  |

| TRLRH               | Read Low to Read High (Head Pulse Duration) (Note 12)                          | 160   |      | ns  |

| TSLRL               | CS Low to Read Low (Note 12)                                                   | 20    | 1    | ns  |

| TSLWH               | CS Low to Write High Note 12)                                                  | 170   | ļ    | ns  |

| TWHAX               | Write High to C/D Doon't Care                                                  | 20    | ļ    | ns  |

| TWHDX               | Write High to Data In Don't Care                                               | 20    |      | ns  |

| TWHEH               | Write High to Count Source High (Notes 5, 7, 14, 15)                           | 550   | ļ    | ns  |

| TWHGV               | Write High to Gate Valid (Notes 5, 10, 14)                                     | 475   | ļ    | ns  |

| TWHRL               | Write High to Read Low (Write Recovery Time) (Note 16)                         | 1500  |      | ns  |

| TWHSH               | Write High to CS High (Note 12)                                                | 20    |      | ns  |

| TWHWL               | Write High to Write Low (Write Recovery Time) (Note 16)                        | 1500  |      | ns  |

| TWHYV               | Write High to Out Valid (Notes 6, 14)                                          |       | 650  | ns  |

| TWLWH               | Write Low to Write High (Write Pulse Duration) (Note 12)                       | 150   |      | ns  |

| TGVEH2              | Gate Valid to Count Source High (Special Gate) (Notes 10, 13, 17)              | 200   |      | ns  |

| TEHGV2              | Count Source High to Gate Valid (Special Gate) (Notes 10, 13, 18)              | 80    |      | ns  |

#### Notes:

- Abbreviations used for the switching parameter symbols are given as the letter T followed by four or five characters. The first and third characters represent the signal names on which the measurements start and end. Signal abbreviations used are:

- A (Address) =  $C/\overline{D}$

- C (Clock) = X2

D (Data In) = DB0-DB15

E (Enabled counter source input) = SRC1-SRC5, GATE1-GATE5, F1-F5,TCN-1

F = FOUT

- G (Counter gate input) = GATE1-GATE5, TCN-1

- Q (Data Out) = DB0-DB15

- R (Read) = RD

- S (Chip Select) =  $\overline{CS}$

- W (Write) = WR

- Y (Output) = OUT1-OUT5

- Continued on next page -

Am9513A

The second and fourth letters designate the reference states of the signals named in the first and third letters respectively, using the following abbreviations.

- H = HIGH

- L = LOW

- V = VALID

- X = Unknown or Don't care

- Z = High-Impedance

- Any input transition that occurs before this minimum setup requirement will be reflected in the contents read from the status register.

- Any input transition that occurs before this minimum setup requirement will act on the counter before the execution of the operation initiated by the write and the counter may be off by one count.

- Any input transition that occurs after this minimum hold time is guaranteed to not influence the contents read from the status register on the current read operation.

- Any input transition that occurs after this minimum hold time is guaranteed to be seen by the counter as occurring after the action initiated by the write operation and the counter may be off by one count.

- 6. This parameter applies to cases where the write operation causes a change in the output bit.

- 7. The enabled count source is one of F1-F5, TCN-1 SRC1-SRC5 or GATE1-GATE 5, as selected in the applicable Counter Mode register. The timing diagram assumes the counter counts on rising source edges. The timing specifications are the same for falling-edge counting.

- 8. This parameter applies to edge gating (CM15-CM13 = 110 or 111) and gating when both CM7 = 1 and  $CM15-CM13 \neq 000$ . This parameter represents the minimum GATE pulse width needed to ensure that the pulse initiates counting or counter reloading.

- 9. This parameter applies to both edge and level gating (CM15-CM13 = 001 through 111 and CM7 = 0). This pa-

rameter represents the minimum setup or hold times to ensure that the Gate input is seen at the intended level on the active source edge and the counter may be off by one count.

- 10. This parameter assumes that the GATENA input is unused (16-bit bus mode) or is tied high. In cases where the GATENA input is used, this timing specification must be met by both the GATE and GATENA inputs.

- 11. Signals F1-F5 cannot be directly monitored by the user. The phase difference between these signals will manifest itself by causing counters using two different F signals to count at different times on nominally simultaneous transitions in the F signals. F1 = X2.

- 12. This timing specification assumes that  $\overline{CS}$  is active whenever  $\overline{RD}$  or  $\overline{WR}$  are active.  $\overline{CS}$  may be held active indefinitely.

- 13. This parameter assumes X2 is driven from an external gate with a square wave.

- 14. This parameter assumes that the write operation is to the command register.

- 15. This timing specification applies to single-action commands only (e.g., LOAD, ARM, SAVE, etc.). For doubleaction commands such as LOAD AND ARM and DISARM AND SAVE, TWHEH minimum = 700 ns.

- 16. In short data write mode, TWHRL and TWHWL minimum = 1000 ns.

- 17. This parameter applies to the hardware retrigger/save modes N, O, Q, R, and X (CM7 = 1 and CM15-CM13 <> 000). This parameter ensures that the gating pulse initiates a hardware retrigger/save operation.

- 18. This parameter applies to hardware load source select modes S and V (CM7 = 1 and CM15-CM13 = 000). This parameter represents the minimum hold time to ensure that the GATE input selects the correct load source on the active source edge.

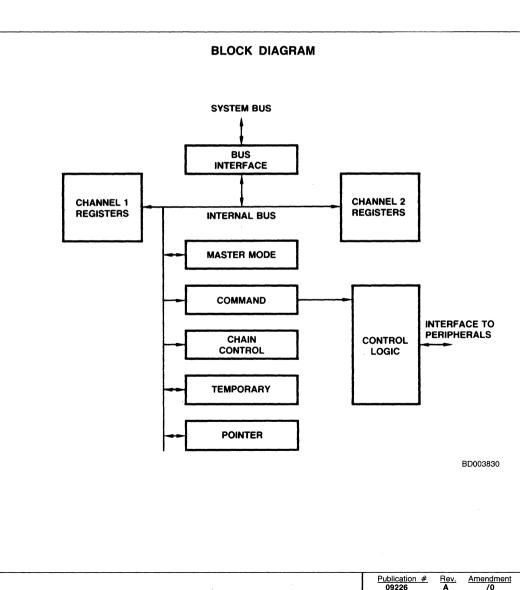

# Am9516A

Universal DMA Controller (UDC)

#### MILITARY INFORMATION

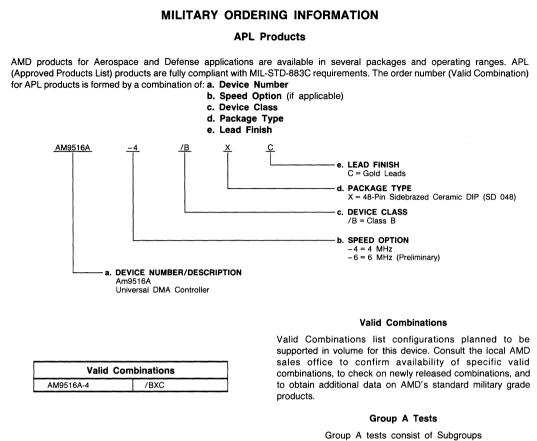

Issue Date: November 1987

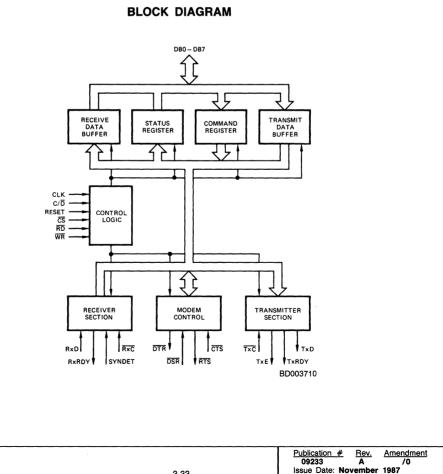

#### **GENERAL DESCRIPTION**

The Am9516A Universal DMA Controller (UDC) is a highperformance peripheral interface circuit for 8086 and 68000 CPUs. In addition to providing data block transfer capability between memory and peripherals, each of the UDC's two channels can perform peripheral-to-peripheral, as well as memory-to-memory transfer. A special Search Mode of Operation compares data read from a memory or peripheral source to the content of a pattern register.

For all DMA operations (search, transfer, and transfer-andsearch), the UDC can operate with either byte or word data sizes. In some system configurations it may be necessary to transfer between word-organized memory and a byteoriented peripheral. The UDC provides a byte packing/ unpacking capability through its byte-word funneling transfer or transfer-and-search option. Some DMA applications may continuously transfer data between the same two memory areas. These applications may not require the flexibility inherent in reloading registers from memory tables. To service these repetitive DMA operations, base registers are provided on each channel which re-initialize the current source and destination Address and Operation Count registers. To change the data transfer direction under CPU control, provision is made for reassigning the source address as a destination and the destination as a source, eliminating the need for actual reloading of these address registers.

Frequently, DMA devices must interface to slow peripherals or slow memory. In addition to providing a hardware WAIT input, the Am9516A UDC allows the user to select independently for both source and destination addresses and automatic insertion of 0, 1, 2 or 4 wait states. The user may even disable the WAIT input pin function altogether and use these software-programmed wait states exclusively.

High throughput and powerful transfer options are of limited usefulness if a DMA requires frequent reloading by the host CPU. The Am9516A UDC minimizes CPU interactions by allowing each channel to load its control parameters from memory into the channel's control registers. The only action required of the CPU is to load the address of the control parameter table into the channel's Chain Address register and then issue a "Start Chain" Command to start the register loading operation.

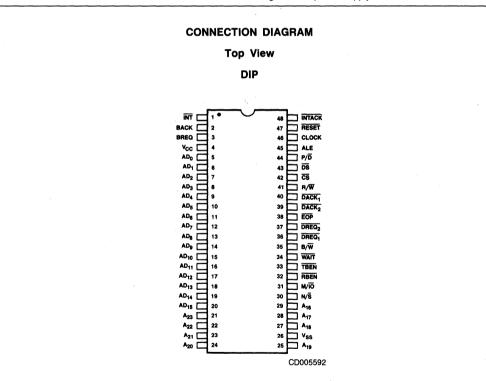

The Am9516A UDC is packaged in a 48-pin DIP and uses a single +5 V power supply.

Note: Pin 1 is marked for orientation.

1, 2, 3, 7, 8, 9, 10, 11.

Am9516A

#### ABSOLUTE MAXIMUM RATINGS

#### Storage Temperature .....-65°C to +150°C V<sub>CC</sub> with Respect to V<sub>SS</sub> .....-0.5 to +7.0 V All Signal Voltages with Respect to VSS .. -0.5 to +7.0 V

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

Military (M) Devices

| Temperature (T <sub>C</sub> )55    | 5 to 125°C |

|------------------------------------|------------|

| Supply Voltage (V <sub>CC</sub> )5 | V ± 10%    |

Operating ranges define those limits between which the functionality of the device is guaranteed.

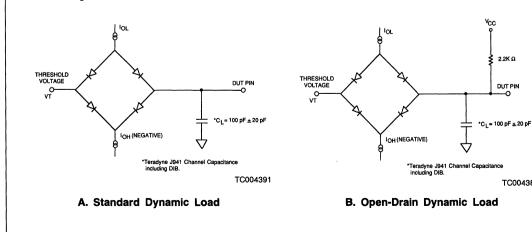

2.2K Ω

DUT PIN

0

TC004381

DC CHARACTERISTICS over operating range (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description          | Test Conditions                                                                       | Min.  | Max.                   | Unit |

|---------------------|-----------------------------------|---------------------------------------------------------------------------------------|-------|------------------------|------|

| V <sub>CH</sub> †   | Clock Input HIGH Voltage          | Driven by External Clock Generator                                                    | 3.8   | V <sub>CC</sub> + 0.3* | V    |

| V <sub>CL</sub> †   | Clock Input LOW Voltage           | Driven by External Clock Generator                                                    | -0.5* | 0.45                   | v    |

| VIH1 †              | Input HIGH Voltage                | All Pins Except 2, 36, 37, 38, 47, 48                                                 | 2.0   | V <sub>CC</sub> + 0.3* | v    |

| V1H2 †              | Input HIGH Voltage                | Pins 2, 36, 37, 38, 47, 48                                                            | 2.2   | V <sub>CC</sub> + 0.3* | V    |

| VIL †               | Input LOW Voltage                 |                                                                                       | -0.5* | 0.8                    | V    |

| V <sub>OH1</sub>    | Output HIGH Voltage               | I <sub>OH</sub> = -250µA Except Pins 1, 32, 33, 38                                    | 2.4   |                        | v    |

| V <sub>OH2</sub>    | Output HIGH Voltage               | I <sub>OH</sub> = -200 μA, Pins 1, 32, 33, 38                                         | 2.0   |                        | V    |

| VOL                 | Output LOW Voltage                | $I_{OL} = 3.2 \text{ mA}$                                                             |       | 0.45                   | ٧    |

| կլ                  | Input Leakage                     | Vss < VIN VCC                                                                         |       | ±10                    | μA   |

| lol                 | Output Leakage                    | Vss Vout < Vcc                                                                        |       | ±10                    | μA   |

|                     | V <sub>CC</sub> Supply Current    | Tc = −55°C                                                                            |       | 350                    | mA   |

| lcc                 | VCC Supply Current                | T <sub>C</sub> = + 125°C                                                              |       | 200                    | mA   |

| C <sub>CLK</sub> †† | Input Capacitance (Clock)         | Unmeasured pins returned to ground.<br>f = 1 MHz over specified temperature<br>range. |       | 25*                    | pF   |

| C <sub>IN</sub> ††  | Input Capacitance (Except Pin 46) | Unmeasured pins returned                                                              |       | 10*                    | pF   |

| COUT ††             | Output Capacitance                | to ground. f = 1MHz over                                                              |       | 15*                    | рF   |

| CI/O tt             | Bidirectional Capacitance         | specified temperature range.                                                          |       | 20*                    | pF   |

Guaranteed by design; not tested.

Group A, Subgroups 9, 10, and 11 only are tested.

++ Not included in Group A tests.

#### Standard Test Conditions

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin. Standard conditions are as follows:

$+4.75 \le V_{CC} \le +5.25 V$ GND = 0 V $-55 \leq T_C \leq +125^\circ C$

Am9516A

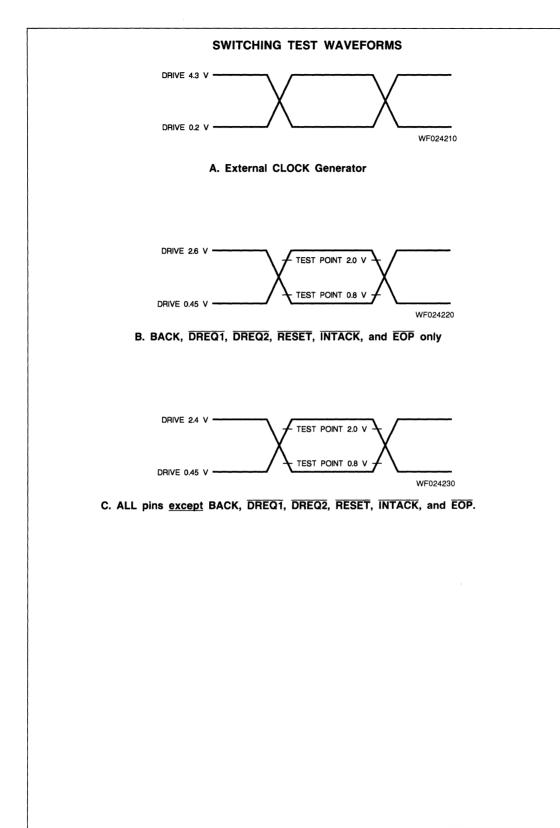

SWITCHING CHARACTERISTICS over operating range (for APL Products, Subgroups 9, 10, 11 are tested unless otherwise noted)

#### TIMING FOR UDC AS BUS MASTER

|      | 1         |                                                                              |      |          |      | ninary |     |

|------|-----------|------------------------------------------------------------------------------|------|----------|------|--------|-----|

| AL - | Parameter | Parameter                                                                    |      | MHz      |      | MHz    |     |

| No.  | Symbol    | Description                                                                  | Min. | Max.     | Min. | Max.   | Uni |

| 1    | TcC       |                                                                              | 250  | 2000     | 165  | 2000   | ns  |

| 2    | TwCh      | Clock Width (HIGH)                                                           | 105  | 1000     | 70   | 1000   | ns  |

| 3    | TwCl      | Clock Width (LOW)                                                            | 105  |          | 70   |        | ns  |

| 4    | TfC       | Clock Fall Time                                                              |      | 20       |      | 10     | ns  |

| 5    | TrC       | Clock Rise Time                                                              |      | 20       |      | 15     | ns  |

| 6    | TdC(AUv)  | Clock RE to Upper Address (A <sub>16</sub> -A <sub>23</sub> ) Valid<br>Delay |      | 90       |      | 80     | ns  |

| 7    | ThC(AUv)  | Clock RE to Upper Address Valid Hold Time                                    | 5    |          | 5    |        | ns  |

| 8    | TdC(ST)   | Clock RE to $R/W$ and $B/W$ Valid Delay                                      |      | 110      |      | 90     | ns  |

| 9    | TdC(A)    | Clock RE to Lower Address (A <sub>0</sub> -A <sub>15</sub> ) Valid<br>Delay  |      | 90       |      | 90     | ns  |

| 10   | TdC(Az)   | Clock RE to Lower Address (A <sub>0</sub> -A <sub>15</sub> ) Float<br>Delay  |      | 60       |      | 60     | ns  |

| 11   | TdC(ALr)  | Clock RE to ALE RE Delay                                                     |      | 70       |      | 60     | ns  |

| 12   | TdC(AL)   | Clock FE to ALE FE Delay                                                     |      | 70       |      | 60     | ns  |

| 13   | TdC(DS)   | Clock RE to DS (Read) FE Delay                                               |      | 60       |      | 60     | ns  |

| 14   | TdC(DSf)  | Clock FE to DS (Write) FE Delay                                              |      | 60       |      | 60     | ns  |

| 15   | TdC(DSr)  | Clock FE to DS RE Delay                                                      | atti | 60       |      | 60     | ns  |

| 16   | TdC(DO)   | Clock RE to Data Out Valid Delay                                             |      | 90       |      | 90     | ns  |

| 17   | TsDI(C)   | Data in to Clock FE Setup Time                                               | 20   | 1610     | 15   |        | ns  |

| 18   | TdA(AL)   | Address Valid to ALE FE Delay                                                | 50   | 11111-   | 35   |        | ns  |

| 19   | ThAL(A)   | ALE FE to Lower Address Valid Hold Time                                      | 60   | <u> </u> | 40   |        | ns  |

| 20   | TwAL      | ALE Width (HIGH)                                                             | 80   |          | 60   |        | ns  |

| 21   | TdAz(DS)  | Lower Address Float to DS LOW Delay                                          | 0    | +        | 0    |        | ns  |

| 22   | TdAL(DS)  | ALE FE to DS (Read) FE Delay                                                 | 75   |          | 35   |        | ns  |

| 23   | TdAL(DI)  | ALE FE to Data in Required Valid Delay                                       |      | 300      | - 35 | 215    | ns  |

| 24   | TdA(DI)   | Address Valid to Data in Required Valid Delay                                |      | 410      |      | 305    | ns  |

| 25   | TdDS(A)   | DS RE to Address Active Delay                                                | 80   | 410      | 45   |        |     |

| 26   | TdDS(A)   | DS RE to ALE RE Deav                                                         | 75   |          | 40   |        | ns  |

| 20   | TdA(DS)   | Address Vand to DS (Read) FE Delay                                           | 160  |          | 110  |        | ns  |

| 28   |           | Data Out Valid to DS RE Delay                                                |      |          |      |        | ns  |

|      | TdDO(DSr) |                                                                              | 230  |          | 150  |        | ns  |

| 29   | TdDO(DSf) | Data Out Valid to DS FE Delay                                                | 55   | <u> </u> | 35   |        | ns  |

| 30   | ThDS(DO)  | DS RE to Data Out Valid Hold Time                                            | 85   |          | 45   |        | ns  |

| 31   | TdDS(DI)  | OS (Read) FE to Data in Required Valid Delay                                 |      | 205      |      | 155    | ns  |

| 33   | ThDI(DS)  |                                                                              | 0    | ļ        | 0    |        | ns  |

| 34   | TwDSmw W  | DS (Write) Width (LOW)                                                       | 185  | ļ        | 110  |        | ns  |

| 35   | TwDSmr    | DS (Read) Width (LOW)                                                        | 275  | <u> </u> | 220  |        | ns  |

| 36   | TdC(RBr)  | Clock FE to RBEN RE Delay*                                                   |      | 70       | ļ    | 65     | ns  |

| 37   | ThDS(ST)  | DS RE to B/W, N/S, R/W and M/IO Valid Hold<br>Time                           | 70   |          | 45   |        | ns  |

| 38   | TdC(TRf)  | Clock RE to TBEN or RBEN FE Delay                                            |      | 60       |      | 60     | ns  |

| 39   | TdC(TRr)  | Clock RE to TBEN RE Delay                                                    |      | 60       |      | 60     | ns  |

| 40   | TdC(ST)   | Clock RE to M/IO and N/S Valid Delay                                         |      | 90       |      | 75     | ns  |

| 41   | TdS(AL)   | R/₩, M/IO, B/₩ and N/S Valid to ALE FE<br>Delay                              | 60   |          | 35   |        | ns  |

| 42   | TsWT(C)   | WAIT to Clock FF Setup Time                                                  | 20   |          | 20   |        | ns  |

| 43   | ThWT(C)   | WAIT to Clock FE Hold Time                                                   | 20   |          | 20   |        | ns  |

| 44   | TwDRQ     | DREQ Pulse Width (Single Transfer Mode)                                      | 20   | 1        | 20   |        | ns  |

| 45   | TsDRQ(C)  | DREQ Valid to Clock RE Setup Time                                            | 60   |          | 50   | 1      | ns  |

| 46   | ThDRQ(C)  | Clock RE to DREQ Valid Hold Time                                             | 20   | 1        | 20   |        | ns  |

| 47   | TdC(INTf) | Clock FE to INT FE Delay                                                     | t    | 150      | 1    | 150    | ns  |

#### Am9516A CLOCK-CYCLE-TIME-DEPENDENT CHARACTERISTICS

The parameters listed below are also shown in the Switching specification. However, they are dependent on the actual values of the clock periods. The equations below define that dependence so that the exact limit for these parameters may be determined for any given system in relation to its specific clock characteristics.

| Number | Parameters | Derivation                         |

|--------|------------|------------------------------------|

| 18     | TdA (AL)   | 0.5TcC - #9 + (#12 - tr)           |

| 19     | ThAL (A)   | 0.5TcC - #12 (ALE FE @ 0.8V) + #10 |

| 21     | TdAz (DS)  | #13 – #10                          |

| 22     | TdAL (DS)  | 0.5TcC - #12 + #13                 |

| 23     | TdAL (DI)  | 2TcC - #12 - #17                   |

| 24     | TdA (DI)   | 2.5TcC - #9 - #17                  |

| 25     | TdDS (A)   | 0.5TcC - #15 + #9                  |

| 26     | TsDS (AL)  | 0.5ToC-#15 + #11 (ALE RE)          |

| 27     | TdA (DS)   | TcC-#0+#10                         |

| 28     | TdDO (DSr) | 1.5ToC - #16 + #15                 |

| 29     | Todo (DSI) | 0.5TcC - #16 + #14                 |

| 30     | ThDS (DO)  | 0.5TcC - #15 + #32                 |

| 31     | TdDS (DI)  | 1.5TcC - #13 - #17                 |

| 34     | TwDSmw     | TcC - #14 + #15                    |

| 35     | TwDSmr     | 1.5TcC - #13 + #15                 |

| 37     | ThDS (ST)  | 0.5TcC - #15 + (#40 - tr)          |

| 41     | TdS (AL)   | 0.5TcC - #40 + (#12 - tr)          |

Note: tr (nominal) = 10 ns #32 CLCK RE to Data Out Not Valid Delay = 20 ns (4 and 6 MHz)

# Am9516A

# SWITCHING CHARACTERISTICS (Cont'd.) UDC AS BUS SLAVE BUS EXCHANGE

|     |             |                                                     | T        |       |      | ninary |     |

|-----|-------------|-----------------------------------------------------|----------|-------|------|--------|-----|

|     | Parameter   | Parameter                                           | 4 N      | 4 MHz |      | 6 MHz  |     |

| No. | Symbol      | Description                                         | Min.     | Max.  | Min. | Max.   | Uni |

| 61  | TdIN(DO)    | INTACK FE to Data Output Valid Delay                |          | 135   |      | 135    | ns  |

| 62  | TdIN(DOz)   | INTACK RE to Data Output Float Delay                |          | 80    |      | 80     | ns  |

| 63  | TdDS(DO)    | DS FE (IOR) to Data Output Driven Delay             |          | 135*  |      | 135    | ns  |

| 64  | TdDS(DOz)   | DS RE (IOR) to Data Output Float Delay              |          | 80    |      | 80     | ns  |

| 65  | TsDI(DS)    | Data Valid to DS RE (IOW) Setup Time                | 40       |       | 40   |        | ns  |

| 66  | ThDS(DI)    | DS RE (IOW) to Data Valid Hold Time                 | 40       |       | 30   |        | ns  |

| 67  | TwDS        | DS LOW Width                                        | 150*     |       | 150* |        | ns  |

| 68  | TwiN        | INTACK LOW Width                                    | 150      |       | 150  |        | ns  |

| 69  | ThDS(CS)    | DS RE to CS Valid Hold Time                         | 20       |       | 20   |        | ns  |

| 70  | ThDS(PD)    | DS RE to P/D Valid Hold Time                        | 20       |       | 20   |        | ns  |

| 74  |             | P/D Valid to DS FE Setup Time (IOR)                 | 10       |       | 10   |        | ns  |

| 71  | TsPD(DS)    | P/D Valid to DS FE Setup Time (IOW)                 | 50       |       | 50   |        |     |

| 72  | TsCS(DS)    | CS Valid to DS FE Setup Time                        | 30       |       | 30   |        | ns  |

| 73  | TrDS        | DS RE to DS FE Recovery Time (for Commands<br>Only) | 4TcC     |       | 4TcC |        | ns  |

| 74  | TwRST       | RESET LOW Width                                     | 3TcC     |       | 3TcC |        | ns  |

| 75  | TdC(BRQf)   | Clock RE to BREQ RE Delay                           | attition | 165   |      | 150    | ns  |

| 76  | TdC(BRQr)   | Clock FE to BREQ FE Delay                           | A market | 150   |      | 150    | ns  |

| 77  | TdBRQ(CTRz) | BREQ FE to Control Bus Float Delay                  |          | 140   |      | 140    | ns  |

| 78  | TdBRQ(ADz)  | BREQ FE to AD Bus Float Delay                       |          | 140   |      | 140    | ns  |

| 79  | TdBRQ(BAK)  | BREQ RE to BACK RE Required Delay                   | 6        |       | 0    |        | ns  |

| 80  | TsBAK(C)    | BACK Valid to Clock RE Setup Time                   | 50       |       | 45   |        | ns  |

| 81  | TdRES(ADz)  | RESET FE to A and AD Buses Float Delay              |          | 135** |      | 135    | ns  |

| 82  | TdRES(CTRz) | RESET FE to Control Bus Float Delay                 |          | 100** |      | 100    | ns  |

| 83  | TdRES(DSz)  | RESET FE to DS Float Delay                          |          | 90**  |      | 90     | ns  |

| 84  | TsRW(DS)    | R/W Valid to DS FE Setup fine (IOW)                 | 2        |       | 2    |        | ns  |

| 85  | ThDS(RW)    | DS RE to R/W Valid Hold Time (IDW)                  | -10      |       | -10  |        | ns  |

| 86  | TsRW(DS)    | R/W Valid to DS FE Setup Time (IOR)                 | 20       |       | 20   |        | ns  |

| 87  | ThDS(RW)    | DS RE to R/W Valid Hold Time (IOR)                  | 20       |       | 20   |        | ns  |

\*2000 ns for slow readable registers (worst case) \*\*Guaranted but not tested. Note: RE = rising edge FE = talling edge

#### UDC-PERIPHERAL INTEREAC

|     | Demomenter          | Parameter                                                        | 4 MHz |      | 6 MHz |      |    |

|-----|---------------------|------------------------------------------------------------------|-------|------|-------|------|----|

| No. | Parameter<br>Symbol | Description                                                      | Min.  | Max. | Min.  | Max. | Ur |

| 90  | TCHDL               | Clock RE to Pulsed DACK FE Delay<br>(Flyby Transactions Only)    |       | 100  |       | 85   | n  |

| 91  | тснрн               | Clock RE to Pulsed DACK RE Delay<br>(To Flyby Transactions Only) |       | 100  |       | 85   | n  |

| 92  | TDSK                | DS RE to Pulsed DACK RE Delay<br>(FROM Flyby Transactions Only)  | 10    |      | 10    |      | n  |

| 93  | TDAD                | Clock RE to Level DACK Valid Delay                               |       | 100  |       | 85   | n  |

| 94  | TDAH                | Clock FE to Level DACK Valid Hold Time                           |       | 100  |       | 85   | n  |

| 95  | TEIDL               | Clock FE to Internal EOP LOW Delay                               |       | 110  |       | 90   | n  |

| 96  | TEIDH               | Clock FE to Internal EOP RE Delay                                |       | 110  |       | 90   | n  |

| 97  | TES                 | External EOP Valid to Clock RE Setup<br>Time During Operation    | 10    |      | 10    |      | n  |

| 98  | TEW                 | External EOP Pulse Width Required During Operation               | 20    |      | 20    |      | n  |

| 99  | TES(BH)             | External EOP Valid to Clock RE Setup Time During Bus<br>Hold     | 10    |      | 10    |      | n  |

| 100 | TEW(BH)             | External EOP Pulse Width Required During Bus Hold                | 20    |      | 20    | T    | n  |

# Am9517A

Multimode DMA Controller

#### MILITARY INFORMATION

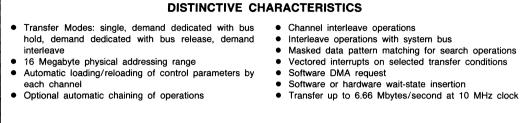

#### DISTINCTIVE CHARACTERISTICS

- SMD/DESC qualified

- Four independent DMA channels, each with separate registers for Mode Control, Current Address, Base Address, Current Word Count and Base Word Count

- Transfer modes: Block, Demand, Single Word, Cascade

- Independent Autoinitialization of all channels

- Memory-to-memory transfers

- · Memory block initialization

- Address increment or decrement

- Master system disable

- Enable/disable control of individual DMA requests

- · Directly expandable to any number of channels

- End of Process input for terminating transfers

- Software DMA requests

- Independent polarity control for DREQ and DACK signals

- Compressed timing option speeds transfers up to 2.5M bytes/second

- 40-pin Hermetic DIP package

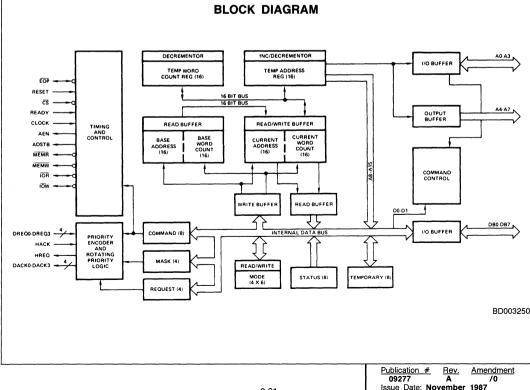

- **GENERAL DESCRIPTION**

The Am9517A Multimode Direct Memory Access (DMA) Controller is a peripheral interface circuit for microprocessor systems. It is designed to improve system performance by allowing external devices to directly transfer information to or from the system memory. Memory-to-memory transfer capability is also provided. The Am9517A offers a wide variety of programmable control features to enhance data throughput and system optimization and to allow dynamic reconfiguration under program control.