### The SUPERNET® 2 Family for FDDI

1991/1992 World Network Data Book

Advanced Micro Devices

2

1991/1992

## The SUPERNET<sup>®</sup>2 Family for FDDI 1991/1992 World Network<sup>™</sup> Data Book

ADVANCED MICRO DEVICES

#### © 1991 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### Trademarks

SUPERNET is a registered trademark of Advanced Micro Devices, Inc.

FASTcard is a trademark of Advanced Micro Devices, Inc.

World Network is a trademark of Advanced Micro Devices, Inc.

### **TABLE OF CONTENTS**

| Introduction                                                        | 1–1 |

|---------------------------------------------------------------------|-----|

| Am79C830A<br>FORMAC Plus                                            | 2–1 |

| Am79C830<br>FORMAC Plus                                             | 2–3 |

| Am79C864 Physical Layer Controller                                  | 3–1 |

| Am79865/Am79866<br>Physical Data Transmitter/Physical Data Receiver | 4–1 |

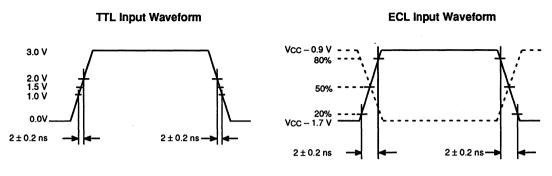

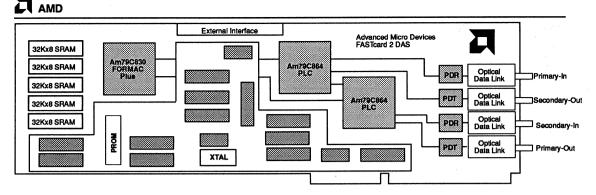

| FASTcard 2                                                          | 5–1 |

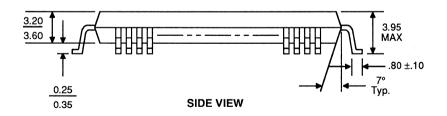

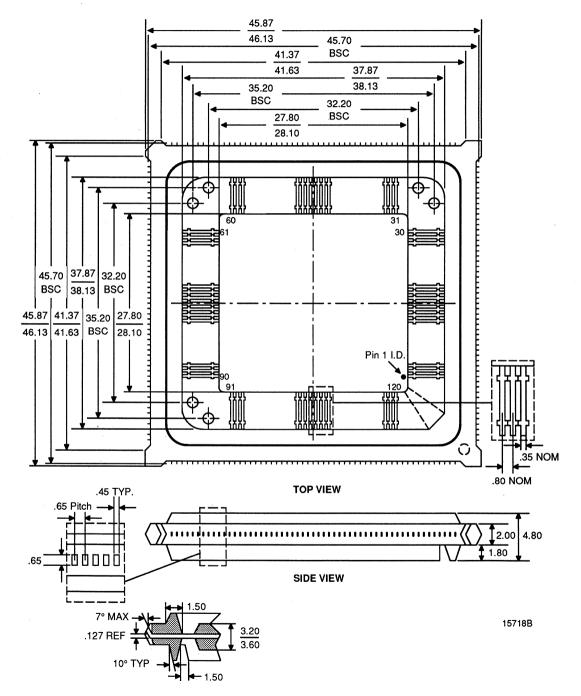

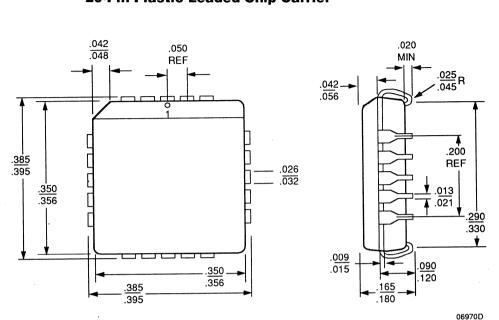

| Physical Dimensions                                                 | 6–1 |

| Appendix Interface Connection Diagrams                              | A-1 |

### The SUPERNET<sup>®</sup>2 Family for FDDI (Am79C830, Am79C864, Am79865, Am79866)

#### **DISTINCTIVE CHARACTERISTICS**

- Compliant with the ANSI X3T9.5/ISO 9314 specifications

- 100 Mbps data rate

- Timed token-passing protocol

- Ring topology

- Complete memory management

- Supports 256K bytes of local frame buffer memory

- Supports buffer memory bandwidths of 200 Mbps to 400 Mbps

- Non-Tag Mode: linked list transmit frame structure compatible with SUPERNET 1

- Tag-Mode: minimum latency/highest performance buffer memory management, ideal for adapter card designs

- Full duplex operation: 200 Mbps continuous data rate

- Supports both fiber optic and copper media

- Diagnostic features

- Multiple loopback modes for run-time diagnostics

- Built In Self Test (BIST) in Physical Layer Controller (PLC)

- Hardware Physical Connection Management support

- Low power consumption—reduction of more than 50% from SUPERNET 1 solution

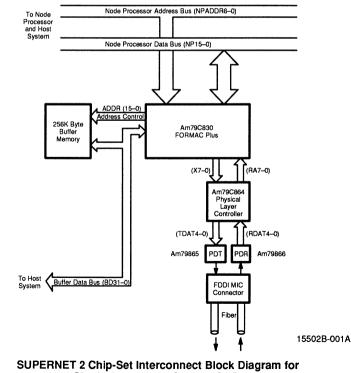

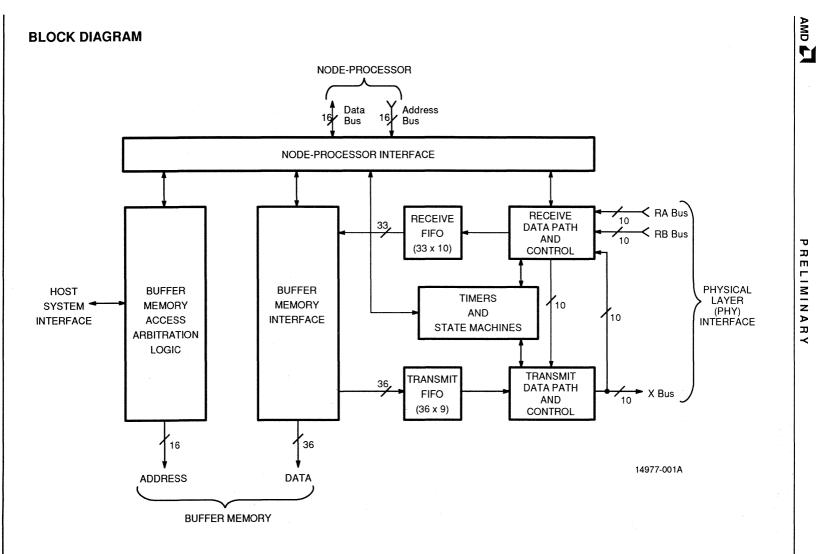

#### **BLOCK DIAGRAM**

Single Attachment Station (SAS)

#### **GENERAL DESCRIPTION**

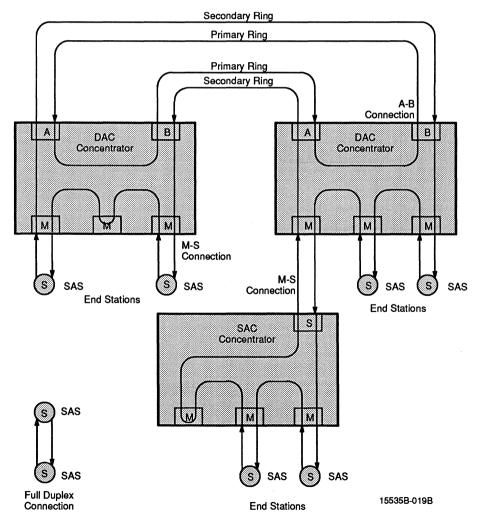

The ANSI X3T9.5/ISO 9314 specifications, named the Fiber Distributed Data Interface (FDDI), define a means of interconnecting equipment with a very high-speed network. Running at a data rate of 100 Mbps over fiber optic or copper twisted pair cable, this standard offers ten times the speed of Ethernet, excellent noise immunity, and a timed-token passing protocol which guarantees each node access to the network. The 4-chip SUPERNET 2 family implements the FDDI standards and offers a variety of additional system features.

SUPERNET 2 is a second generation FDDI chip-set from AMD. Like the first generation SUPERNET solution, SUPERNET 2 provides complete buffer management functions common to most network protocols. When used in non-tag mode, the FORMAC Plus replaces and is fully downward compatible with the previous generation three chip combination made up of the Am79C81A (RBC), the Am79C82A (DPC) and the Am79C83 (FORMAC). In tag-mode, the FORMAC Plus manages the buffer memory as multiple FIFOs.

There are two key advantages to tag-mode operation; 1) programmable transmit and receive thresholds allow early notification (receive) and transmission yielding absolute minimum frame latencies and 2) the multiple FIFO structure simplifies interfacing with the FORMAC Plus thus reducing software/hardware overhead. Because of these characteristics, tag-mode is particularly well suited to adapter cards and motherboards where the local memory is tuned to allow high performance operation with network and buffer latencies taken into consideration. For a more detailed understanding of buffer memory sizing in FDDI adapter designs, refer to AMD PID#16294A, "Sizing Local Buffer Memory in FDDI."

In addition to providing a software compatible upgrade path from SUPERNET 1, the linked-list data structure of non-tag mode is well suited for concentrator designs where the FORMAC Plus buffer memory is the target memory. In this case, frames can be operated on in the FORMAC Plus controlled buffer memory obviating the need for an additional component to perform "system interface functions."

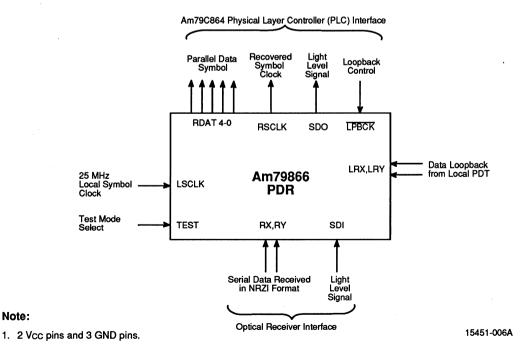

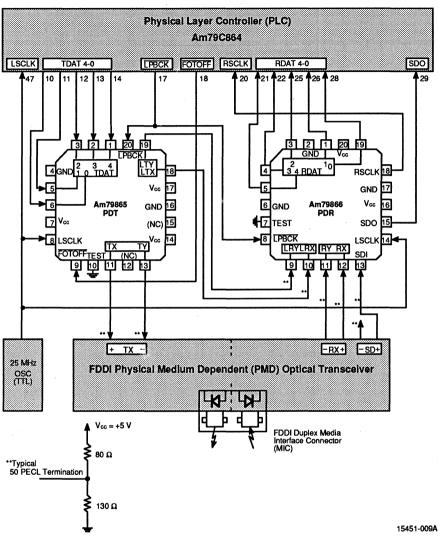

The FORMAC Plus provides DMA channels, arbitrates access to the network buffer memory, and controls the data path between the buffer memory and the medium. The FORMAC Plus also fully implements the timed-token protocol and receive/transmit control specified for the Media Access Control (MAC) sublayer of the ISO standard 9314-2 for FDDI. Physical sublayer (PHY) tasks defined by the ISO standard 9314-1 are performed by a three-chip combination of the Am79C864 Physical Layer Controller (PLC), the Am79865 Physical Data Transmitter (PDT) and the Am79866 Physical Data Receiver (PDR). The three chips are collectively known as the AmPHY. The PDT/PDR connect to the fiber optic transceiver which converts an optical signal coming from the medium to an equivalent electrical logic signal or vice versa. The PDT/R devices can also drive copper media directly as shown in AMD PID#15923A/0, "FDDI on Copper with AMD PHY Components."

#### INTRODUCTION

The block diagram on page 1 shows AMD's SUPERNET 2 architecture which meets the ISO 9314 FDDI data communications standard. The primary function of the SUPERNET2 chip-set is to act as an interface between a host computer and the network medium, using the FDDI protocol, to transfer and convert data between parallel form, at the host, and serial form, at the media.

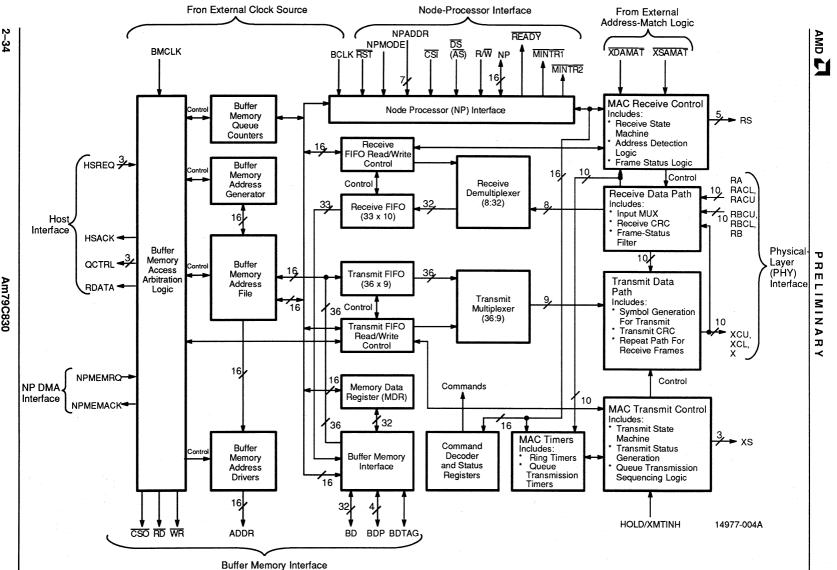

#### SYSTEM DATA PATHS

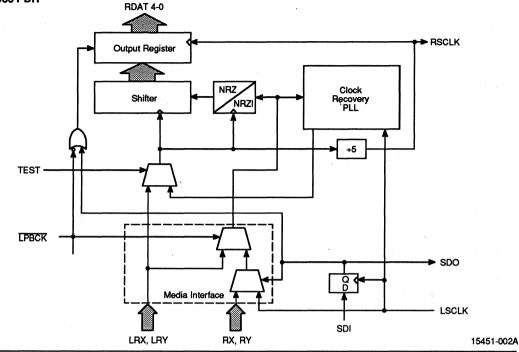

The station receives data in serial form from the network medium. The fiber optic or copper transceiver interfaces the medium to the PDR. Using its clock recovery PLL, the PDR derives clocking information from the encoded stream and converts the bit stream to unframed 5-bit symbols. The PLC chip receives the symbol-wide (5-bit) data along with a 25 MHz recovered clock from the PDR and searches for a JK symbol pair, also known as the starting delimiter. The PLC uses a starting delimiter to establish byte boundaries and to frame the incoming data. The data is decoded and sent to the FORMAC Plus. The receive demultiplexer in the FORMAC Plus formats four bytes of data into a 32-bit long word which is temporarily stored in the receive FIFO until the buffer memory is ready to receive it. The FORMAC Plus sets up addresses on the 16-bit address bus to store the frame in buffer memory.

The data can then be sent to the host memory from the buffer memory on the 32-bit data bus. Initialization and control of the SUPERNET 2 chipset is realized through a node processor (NP) interface via a 16-bit bus called the NP bus. In addition, the NP interface provides an alternate access method to buffer memory using the MAR and MDR registers.

#### SYSTEMS COMPONENTS

#### **Host Systems**

The term "host" is used here to refer to any mainframe, workstation, minicomputer, or computer peripheral (such as a disk drive or a printer) to which a network interface is attached. In a large system, a powerful NP may be used to off-load various networking specific chores. In simpler systems, the host and NP may be one and the same, meaning that the host computer performs all NP functions. Lower-cost systems may use this configuration.

#### **Node Processor**

The Node Processor (NP) can be a microprogrammed or conventional microprocessorbased system used for overseeing the operation of the SUPERNET 2 chip-set. Its main function is to initialize the devices and respond to various system-level and frame-level interrupts. In the simplest case it can be a minimal state machine. More complex architectures can have all the sophistication required to execute the upper-layer protocols specified by the seven-layer International Standards Organization (ISO) Open System Interface (OSI) model.

The NP communicates with the SUPERNET 2 chip-set using the NP-bus and various bus handshakes and instructions lines. Its handshake with the Host system is user-defined and depends on the partitioning of functions between the Host and the Node Processor.

The NP can communicate with the buffer memory by issuing an NP memory request to the FORMAC Plus and, when access is granted, using the 32-bit data bus. An alternate method is provided through use of software instructions to the FORMAC Plus in conjunction with accessing the internal MAR and MDR registers. The 32-bit wide Memory Data Register (MDR) is used for data transfer between the node processor and buffer memory. A typical NP could consist of a microprocessor with assorted peripheral chips (for DMA, interrupts, etc.) and local memory. The NP treats the SUPERNET 2 chip-set as a peripheral for networking functions. The NP has complete control over (and knowledge of) the state of the SUPERNET 2 chip-set and buffer memory. These chips make their status available to the NP to help it maintain this control.

The NP can run either synchronously or asynchronously with respect to the network clock. Any required synchronization with ICs surrounding the SUPERNET chip-set is performed by the FORMAC Plus.

#### **Buffer Memory**

The Buffer memory, consisting of static RAM, is used for intermediate storage of frames. Its addresses are generated and controlled by the FORMAC Plus. The buffer memory cycles are controlled by a buffer memory clock (BMCLK) which is independent of the network clock. The BMCLK may have a frequency between 12.5 MHz and 25 MHz giving a total memory bandwidth of 200 Mbps to 400 Mbps. This allows for the possibility of operating on the frames as they reside in the buffer memory while leaving ample bandwidth to continue the exchange of frames on the network. Optionally, a node processor (NP) can do any processing necessary to assure the host that the frame is good. Finally, the frame is transferred to the host. Frame transmission is just the reverse. At a 100 Mbps data rate, a 70-ns access time is generally adequate. Both separate I/O and multiplexed I/O configurations can be used. As an option, the memory can be set up to be protected with byte parity.

The memory can be accessed by the FORMAC Plus, NP and the host. Only one of these can access the memory at any time, and the FORMAC Plus arbitrates all requests to determine who can access the memory.

#### Am79C830 Fiber Optic Media Access Controller (FORMAC) Plus

The FORMAC Plus performs the Media Access Control (MAC) layer protocol for the FDDI standard networking scheme. The FORMAC Plus determines when a node can get access to the network and implements the logic required for token handling, address recognition, and CRC.

Upon receiving a frame, the FORMAC Plus strips away all the physical layer headers. Any preamble or start of frame delimiters are detected and discarded. Also, any end-offrame characters or postamble is removed. The FORMAC Plus checks incoming frames for destination address and when a match does occur the data from the received frame is loaded into the receive FIFO and the long words are transferred into buffer memory. It also generates and checks CRC on frames.

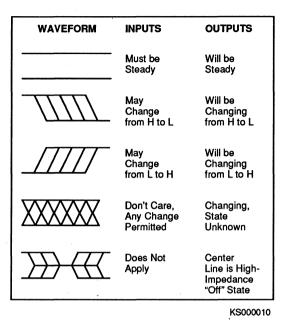

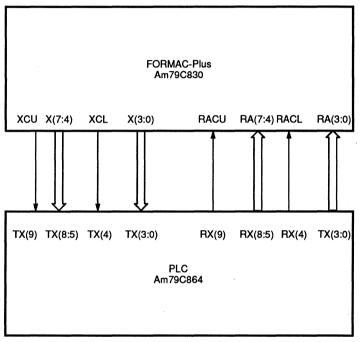

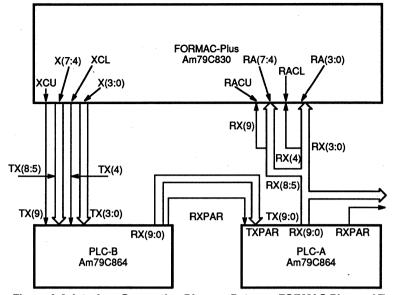

The FORMAC Plus's interface with the PLC consists of three 10-bit (eight data bits and two control bits) buses. Two of these handle received data frames, while the third is used for data transmission. Data on these buses move synchronously with the byte rate clock (BCLK).

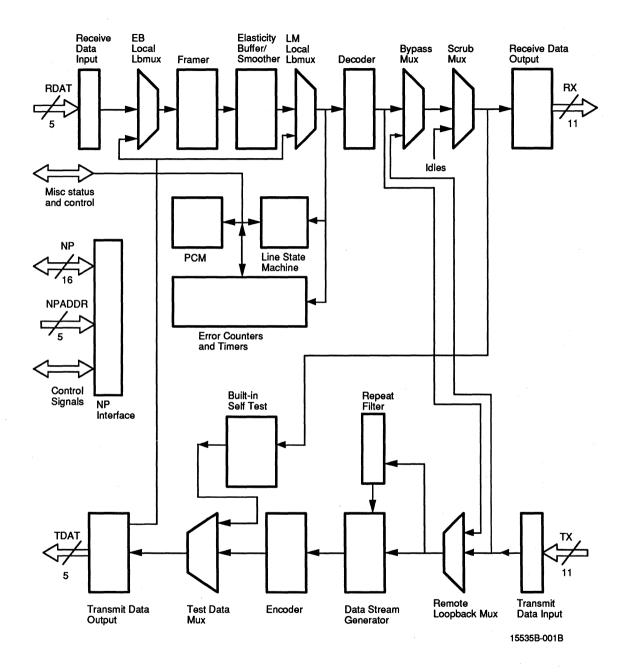

#### Am79C864 Physical Layer Controller (PLC)

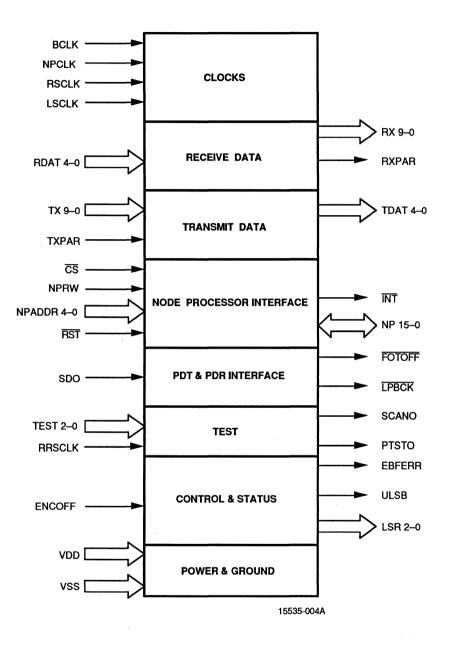

The PLC, along with the PDT and PDR, perform the Physical sub-layer (PHY) protocol and portions of Station Management (SMT) for the FDDI standard.

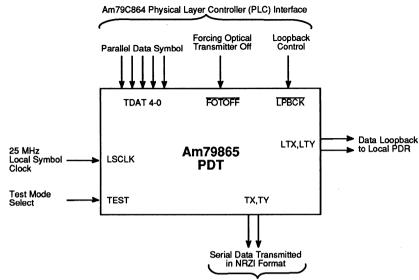

The FORMAC Plus transmits data frames in the form of 8-bit bytes accompanied by two control characters. The PLC receives byte-wide data from the MAC at 12.5 million bytes per second, then performs 4B/5B encoding which maintains the DC balance in the output waveform and guarantees that no more than three consecutive 0's will be present in an encoded pattern. The encoded data is sent out symbol-wide at 25 million symbols per second to the PDT. The repeat filter in the transmit path detects corrupted symbols and converts them into a specific pattern of HALT and Idle symbols.

During frame reception, the PLC receives symbol-wide (5 bits) data along with a 25 MHz clock. The PLC frames data using the start delimiter. The framed data is then sent to the Elasticity Buffer which serves to compensate for the frequency difference between the recovered clock and the local clock. The data is then decoded and sent to the FORMAC Plus. The data is byte-wide (10bits) and clocked by a 12.5 MHz local clock.

The PLC also communicates with the NP to force FDDI-specified line states onto the medium and performs various loopback functions and BIST.

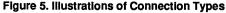

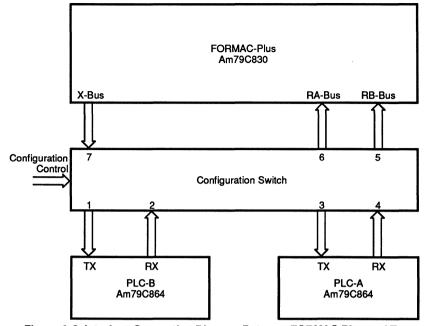

Some functions specific to Station Management is also performed by the PLC. The PLC chip contains the Physical Connection Management (PCM) state machine which determines the timing and state requirement. Also contained in the PLC is the Physical Connection Insertion (PCI) state machine which performs the necessary ring scrubbing and data path switching.

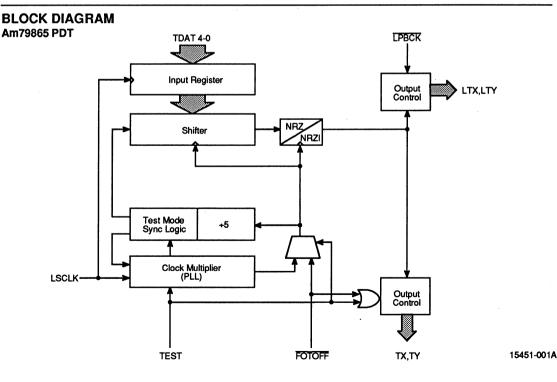

## Am79865 Physical Data Transmitter (PDT)/Am79866 Physical Data Receiver (PDR)

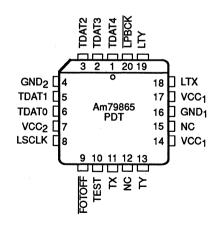

The PDT in the transmit path converts the symbol-wide data received from the PLC to serial format and sends an NRZI (non-return-to-zero, inverted on ones) bit stream to the fiber optic transmitter. The on-chip PLL in the PDT, driven by a 25 MHz external crystal controlled clock source, generates a bit rate clock.

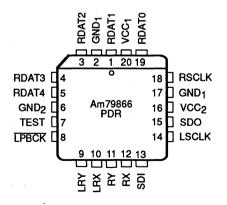

The PDR receives serial NRZI data stream and converts them to NRZ. Using its on-chip PLL, the PDR extracts encoded clock information from the serial NRZI data stream and recovers the data. The recovered clock is used for the serial-to-parallel data conversion. The PDR provides a symbol-wide unframed data to the PLC.

#### **Fiber Optic Transceiver**

Fiber optic receivers typically consists of a pin diode, amplifier, equalizer, automatic gain control circuit, and comparator. The PIN diode receives an optical signal from the fiber and converts it into an electrical waveform. The signal is then amplified and conditioned. Amplifier gain is variable and depends on the magnitude of the incoming signal. The conditioned waveform is then passed through comparator which determined whether the output should be a logic "1" or "0". The resulting bit stream is then fed to the PDR with a pair of differential drivers.

The fiber optic transmitter accepts a differential signal from the PDT and, by means of a light-emitting diode (LED), converts it into an optical output for transmission onto the fiber optic cable.

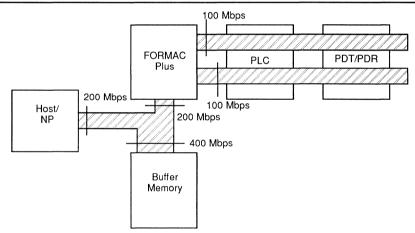

#### SYSTEM BANDWIDTH

The SUPERNET 2 chip-set is designed to provide the maximum data rate of 100 Mbps on the network medium. This speed implies that the buffer memory bus on the FORMAC Plus can support a minimum data rate of 12.5 MBytes/sec. the equivalent of 100 Mbps. Figure 1 shows the bandwidth provided in the complete system. The buffer memory interface is designed to support 200-Mbps to 400-Mbps sustained transfer rates on the 32-bit buffer memory bus. This translates to a minimum rate of 25 MBytes/sec or 6.25 Mega "long words"/sec at the buffer memory. Therefore, at 12.5 MHz with network transmit or receive occurring (100 Mbps) at a node, only half the memory bandwidth is used by the FORMAC Plus for reception or transmission of frames. The remaining 100 Mbps bandwidth on the memory is available to either the NP or the host. At 25 MHz, only one fourth of the bandwidth is required for network activity leaving 300Mbps of bandwidth available. The FORMAC Plus lets the NP or the host share this bandwidth through cycle stealing while frames are transferred. When the FORMAC Plus is neither transmitting nor receiving, the complete bandwidth of the buffer memory can be available to the NP or the Host. This bandwidth may be used by either the NP or host exclusively, or shared between the two.

This ample availability of memory bandwidth is provided to minimize the buffer space required. SUPERNET 2 allows partial or complete frames to be emptied as they are received. Buffers can be small and the node interface can be simple.

15502B-002A

## Am79C830A

#### Formac Plus

#### **DISTINCTIVE CHARACTERISTICS**

- Am79C830 with enhanced features

- Supports Void Frame Stripping in on-line special mode

When programmed to operate in the "on-line special" mode, the FORMAC Plus will issue two auto void frames prior to releasing the token. With the internal counter, the void and counter stripping algorithm can be implemented as described in both the bridge networking group documents of ANSI X3T9.5 and the IEEE 802.1D standard.

#### MAC Status Copying (MSC) Handling of A & C indicators

When the FORMAC Plus is programmed to operate in the "on-line special" mode, the A & C indicators will be set in accordance with the bridge type described as "MAC Status Copying" (MSC) when the external destination address match signal (XDAMAT) is activated. The A & C indicators will be handled normally for addresses recognized through the internal FORMAC Plus registers.

### Advanced Micro Devices

#### SRCOMP bit functional in Tag Mode

The SRCOMP bit in status register two upper will be valid in tag mode. The SRCOMP bit indicates that the status word has been written to the buffer memory following the reception of a frame. In Am79C830, this bit is meaningful only in non-tag mode. The SRCOMP bit will now also indicate when the status word is written into the buffer memory in tag mode as well as non-tag mode.

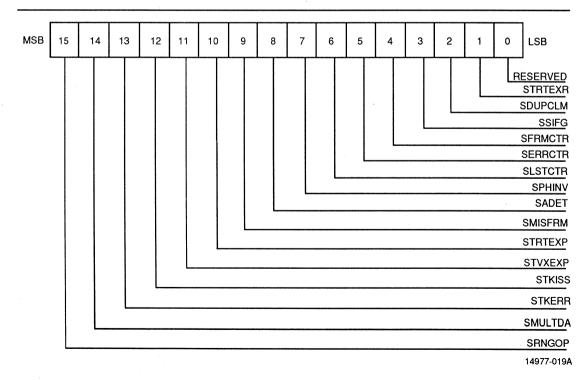

■ Timer for detection of duplicate MAC addresses

When the ring is not operational, during claim or beacon states, the TSYNC timer is utilized to time transitions RM34a and RM34b of the Ring Management (RMT) state machine. The timer is initialized with a value of twice Dmax (3.546 ms). It begins to count as the MAC transmit state machine takes transitions T45 (claim state to beacon state) or T54 (beacon state to claim state). It is reinitialized at the transition between claim and beacon states. If the timer expires while the MAC is still in T4 or T5 and MY\_CLAIM or MY\_BEACON is received, the existence of a duplicate MAC address on the ring is detected. This will be indicated by setting SDUPCLM (bit 2) in status register 2 lower.

#### **GENERAL DESCRIPTION**

The Am79C830A is an enhanced version of the current Am79C830. The enhancement incorporates new functions to support transparent bridging in addition to other new features. This an identical device to Am79C830 with respect to pin-outs and dimensions. Contact your local AMD sales office for more information.

e .

# Am79C830

#### **DISTINCTIVE CHARACTERISTICS**

- Implements the FDDI Media Access Control (MAC) layer protocol for ISO standard 9314-2

- Buffer-memory clock frequency range: 12.5 MHz to 25 MHz

- Full-duplex operation: 200 Mbps continuous data rate

- Supports buffer memory bandwidths of 200 Mbps to 400 Mbps

- Full support for synchronous transmission

- Three asynchronous priority queues with individually programmable threshold levels

- Two basic modes of operation:

Nontag mode: On a per-frame basis, identical in operation with the AMD RBC/DPC/FORMAC combination

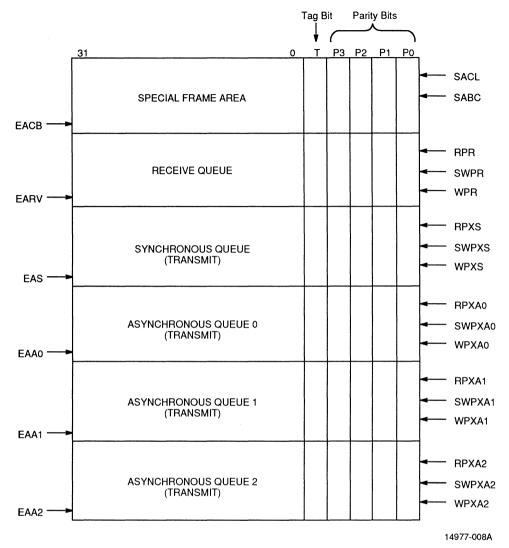

Tag Mode: Operates on partial frames in buffer memory for both transmit and receive, allowing for reduced buffer-memory requirements and increased station data throughput

#### **GENERAL DESCRIPTION**

The Am79C830 FORMAC Plus implements the timedtoken protocol and receive/transmit control specified for the Media Access Control (MAC) sublayer of the ISO Standard 9314-2 describing the Fiber Distributed Data Interface (FDDI). The FORMAC Plus is a CMOS device that provides in a single chip an interface between the physical layer of a station on an FDDI network, and the station's memory. Also provided on the Am79C830 is its interface to a host system and a complete interface to a buffer memory for transmitted and received data. The FORMAC Plus operates in either of two modes. In one mode (called the nontag mode), it replaces and is fully downward compatible with the previous-generation SUPERNET 1 three-chip combination made up of the Am79C81A (RBC), the Am79C82A (DPC), and the Am79C83 (FORMAC). In its second mode (called the tag mode), in addition to having the full operational capabilities of the nontag mode, FORMAC Plus transforms the associated buffer memory into multiple FIFOs, thus reducing data movement within the buffer memory and substantially improving throughput. Other FORMAC Plus features include on-chip receive and transmit FIFOs; separate receive and transmit CRC generation and checking logic; SMT capabilities; and three separately-prioritized asynchronous queues.

- Pointers to claim and beacon frames

- Supports transmit linked-list addressing

- Integrated buffer-memory management: DMA arbitration between NP, buffer memory, and host interfaces

MAC of choice for FDDI concentrators. Handles SMT and MAC frames without the need for complex network DMA function

Bridging features:

Control of CRC on a per-frame basis Control of A and C bits

- External address-match support

- Programmable delay for frame flushing

- Tag mode allows maximized frame-forwarding rates

Am79C830

24

PRELIMINARY

#### TABLE OF CONTENTS

| DISTINCTIVE CHARACTERISTICS                                                                                                                                                                                                                                                                    | . 2–3                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                            | . 2–3                                        |

| BLOCK DIAGRAM                                                                                                                                                                                                                                                                                  | . 2–4                                        |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                              | . 2–5                                        |

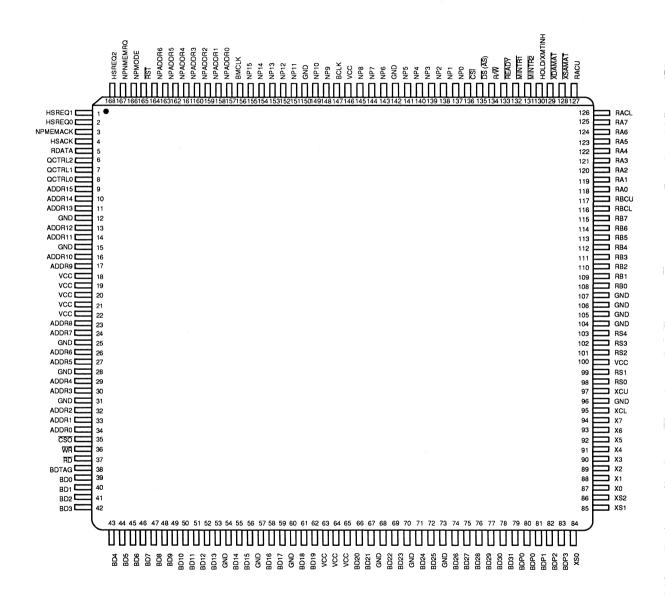

| 169-Pin PGA CONNECTION DIAGRAM                                                                                                                                                                                                                                                                 | 2-11                                         |

| 169-Pin PGA PIN DESIGNATIONS                                                                                                                                                                                                                                                                   | 2–12                                         |

| 168-Pin PQFP CONNECTION DIAGRAM                                                                                                                                                                                                                                                                | 2–16                                         |

| 168-Pin PQFP PIN DESIGNATIONS                                                                                                                                                                                                                                                                  | 2–17                                         |

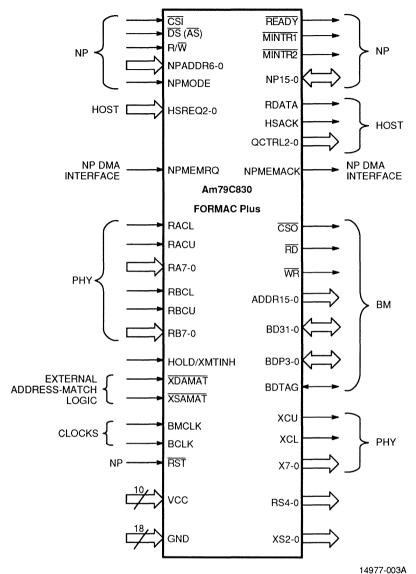

| LOGIC SYMBOL                                                                                                                                                                                                                                                                                   | 2–21                                         |

|                                                                                                                                                                                                                                                                                                | 2–22                                         |

| PIN DESCRIPTION         Physical Layer (PHY) Interface         Node Processor (NP) Interface         Buffer Memory Interface         Host/Buffer Memory Interface         Node Processor (NP)/Buffer Memory Interface         Special Functions         Other Signals         Power and Ground | 2–23<br>2–25<br>2–26<br>2–27<br>2–28<br>2–30 |

| INTERFACE DESCRIPTION<br>Physical Layer (PHY) Interface<br>Node Processor (NP) Interface<br>Buffer Memory Interface<br>Host interface<br>Node Processor to Buffer Memory Interface<br>Special Interface Lines                                                                                  | 2–32<br>2–32<br>2–32<br>2–32<br>2–32         |

| FUNCTIONAL DESCRIPTION Receive Data Path General Input Multiplexer Receive CRC Checker Symbol Filter                                                                                                                                                                                           | 2–33<br>2–33<br>2–33<br>2–33                 |

| MAC Receive Control<br>General<br>Receive State Machine<br>Address Detection Logic<br>Frame Status Logic                                                                                                                                                                                       | 2–35<br>2–35<br>2–35<br>2–35                 |

| MAC Timers                                                                                                                                                                                                                                                                                     |                                              |

| Timer Logic                                  | 2–35         |

|----------------------------------------------|--------------|

| Synchronous and Asynchronous Queue Timing    | 2–35         |

| Receive Demultiplexer                        | 2–36         |

| Receive FIFO Read/Write Control              | 2–36         |

| Receive FIFO                                 | 236          |

| Buffer-Memory Interface                      | 2–36         |

| Memory Data Register (MDR)                   | 2–36         |

| Node-Processor (NP) Interface                | 2-36         |

| Command Decoder and Status Registers         | 2–36         |

| Buffer Memory Address File                   | 2–36         |

| Buffer Memory Address Generator              | 2–37         |

| Buffer Memory Queue Counters                 | 2–37         |

| Introduction                                 | 2–37         |

| Almost-Full Detection                        | 2–37         |

| Threshold Detection                          | 2–37         |

| Buffer Memory Access Arbitration Logic       | 2–37         |

| Buffer Memory Address Drivers                |              |

| Transmit FIFO                                | 2–37         |

| Transmit FIFO Read/Write Control             | 2–37         |

| Transmit Multiplexer                         | 2–38         |

| Transmit Data Path                           | 2–38         |

| General                                      | 2–38         |

| Input to Transmit Data Path                  | 2–38         |

| Adding CRC to Transmitted Frames             | 2–38         |

| Adding Control Symbols to Transmitted Frames | 2–38         |

| MAC Transmit Control                         | 2–38         |

| FORMAC Plus OPERATIONAL MODES                | 2–39         |

| Introduction                                 | 2-39         |

| (1) Initialization Mode                      |              |

| (2) Memory Active Mode                       |              |

| (3) On-line Mode                             |              |

| Receive State                                |              |

| Frame Reception                              |              |

| Frame Flushing                               |              |

| Frame Flushing in Tag Mode                   |              |

| Frame Flushing in Nontag Mode                |              |

| Frame Flushing of Stripped and Lost Frames   | 2-41         |

| Frame Abort                                  | 2–41         |

| Frame Stripping (Non-Repeat to Ring)         |              |

| Frame-Status (FS) Handling                   |              |

| Non-Repeated Frames                          |              |

| Special Functions                            |              |

|                                              | 2-42         |

| Transmit State                               |              |

| Transmit State                               | 2–42         |

|                                              | 2–42<br>2–42 |

| AMD | L |

|-----|---|

|     |   |

| (4) On-Line Special Mode                                         | 2–44 |

|------------------------------------------------------------------|------|

| (5) Loopback Mode                                                | 2–44 |

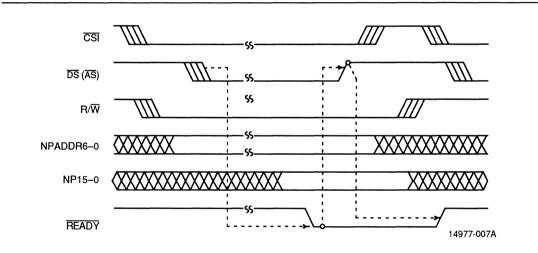

| NODE PROCESSOR BUS OPERATION                                     | 2–45 |

| Synchronous Mode                                                 | 2–45 |

| Asynchronous Mode                                                |      |

|                                                                  | 2-48 |

| Introduction                                                     |      |

| Tag Mode                                                         |      |

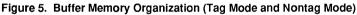

| Loading of Transmit Frames (Tag Mode)                            |      |

| Frame Transmission from Buffer Memory (Tag Mode)                 |      |

| Transmitting Send-Immediate Frames from Buffer Memory (Tag Mode) |      |

| Loading of Claim/Beacon/Auto-Void Frames (Tag Mode)              |      |

| Transmitting Claim/Beacon/Auto-Void Frames (Tag Mode)            |      |

| Loading Receive Frames into Buffer Memory (Tag Mode)             | 2–52 |

| Unloading Receive Frames from Buffer Memory (Tag Mode)           | 2–54 |

| Nontag Mode                                                      | 2–54 |

| Loading Transmit Frames (Nontag Mode)                            | 2–54 |

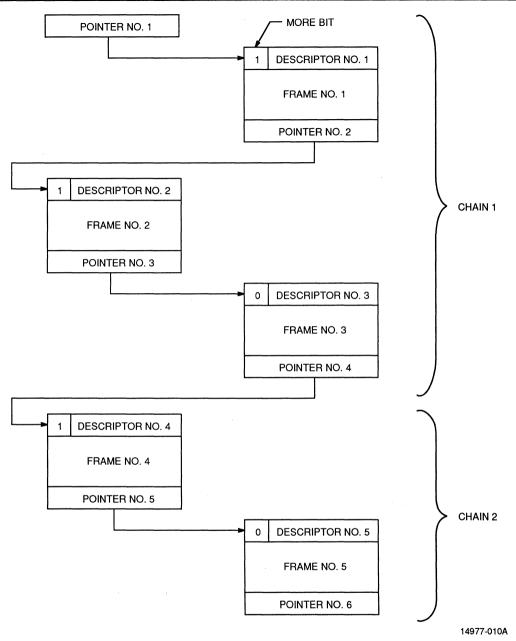

| Chained Transmit Operation (Nontag Mode)                         | 2–54 |

| Transmission of Transmit Frames (Nontag Mode)                    | 2–56 |

| Loading Claim/Beacon/Auto-Void Frames (Nontag Mode)              | 2–57 |

| Transmitting Claim/beacon/Auto-Void Frames (Nontag Mode)         | 2–57 |

| Send-Immediate Frames (Nontag Mode)                              | 2–57 |

| Loading Receive Frames (Nontag Mode)                             | 2–57 |

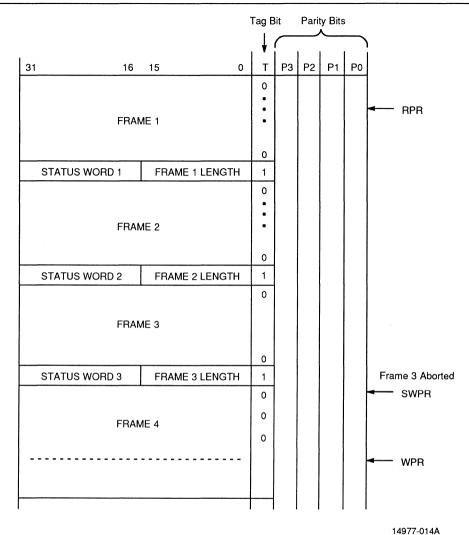

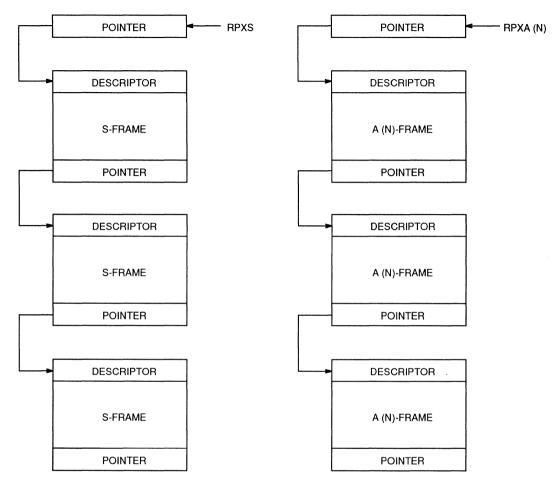

| Unloading Receive Frames (Nontag Mode)                           | 2–59 |

| INTERFACING WITH THE PHYSICAL LAYER                              | 2–60 |

| STATUS AND INTERRUPTS                                            | 2–60 |

| Introduction                                                     | 2–60 |

| Status Register 1 (ST1)                                          | 2–60 |

| Status Register 2 (ST2)                                          | 2–64 |

| DATA HANDLING AND FORMATS                                        | 0.67 |

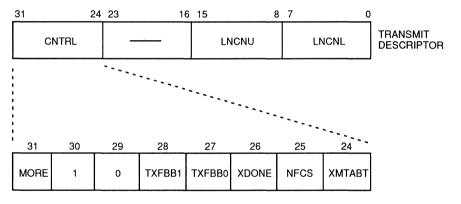

| Data Format of Transmit Frames in Buffer Memory                  |      |

|                                                                  |      |

| Transmit Descriptor Format                                       |      |

| Transmit Pointer Format (Nontag Mode only)                       |      |

| Data Format of Receive Frames in Buffer Memory                   |      |

|                                                                  |      |

| Format of Receive Status-Word                                    |      |

|                                                                  |      |

| CONFIGURATION-STRAPPING of FORMAC-Plus PINS                      |      |

|                                                                  |      |

| PROGRAMMING THE FORMAC Plus                                      |      |

| Table of Programmable Resources                                  |      |

| Programming the Mode Registers                                   |      |

| Mode Register 1 (MDREG1)                                         | 2-79 |

| Mode Register 2 (MDREG2)                                                     |         |

|------------------------------------------------------------------------------|---------|

| Command Registers 1 and 2 and their Instruction Set                          | 2–86    |

| Command Register 1                                                           | 2–87    |

| Send-Immediate Commands                                                      | 2–90    |

| Command Register 2                                                           | 2–90    |

| Initialization Values for Timers, Counters and Related Registers             | 2–91    |

| FDDI Timer Implememtation                                                    | 2–92    |

| Station-Address Registers                                                    | 2–92    |

| MAC Information Register (MIR)                                               | 2–92    |

| Priority Sequence Registers (PRI2-0)                                         | 2–92    |

| Timer and Counter Registers                                                  | 2–92    |

| TMAX Register                                                                | 2–92    |

| TVX Register and Timer (Valid Transmission Timer)                            | 2–93    |

| Requested TRT Register (TREQ)                                                | 2–93    |

| Token Rotation Timer (TRT)                                                   | 2–93    |

| Token Holding Timer (THT)                                                    | 2–93    |

| Negotiated TRT Register (TNEG)                                               | 2–93    |

| Synchronous-Transmission Bandwidth Register and                              |         |

| TMSYNC Timer (TSYNC and TMSYNC)                                              | 2–93    |

| Frame Counter (FCNTR)                                                        | 2–94    |

| Error Counter (ECNTR)                                                        | 2–94    |

| Lost Counter (LCNTR)                                                         | 2–94    |

| TMRS Register                                                                | 2–94    |

| MAC State-Machine Register                                                   | 2–94    |

| Programming the Buffer Memory Management Registers                           | 2–95    |

| Reset status                                                                 | 2–95    |

| Buffer Memory Management Registers in Nontag Mode                            | 2–95    |

| Buffer Memory Management Registers in Tag Mode                               | 2–96    |

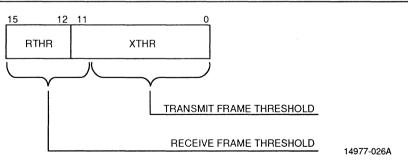

| Frame Threshold Register (FRMTHR)                                            | 2–97    |

| Memory Address Register for Random Reads (MARR)                              | 2–98    |

| Memory Address Register for Random Writes (MARW)                             | 2–98    |

| Memory Data Register for Random Access (MDR)                                 | 2–98    |

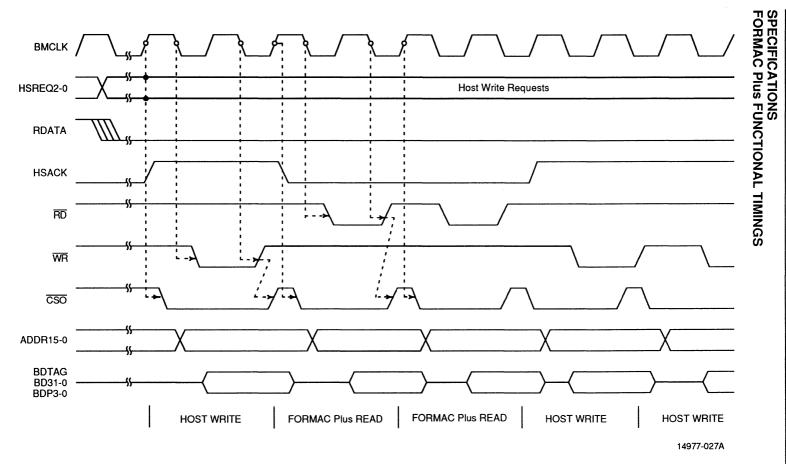

| SPECIFICATIONS                                                               | 0.00    |

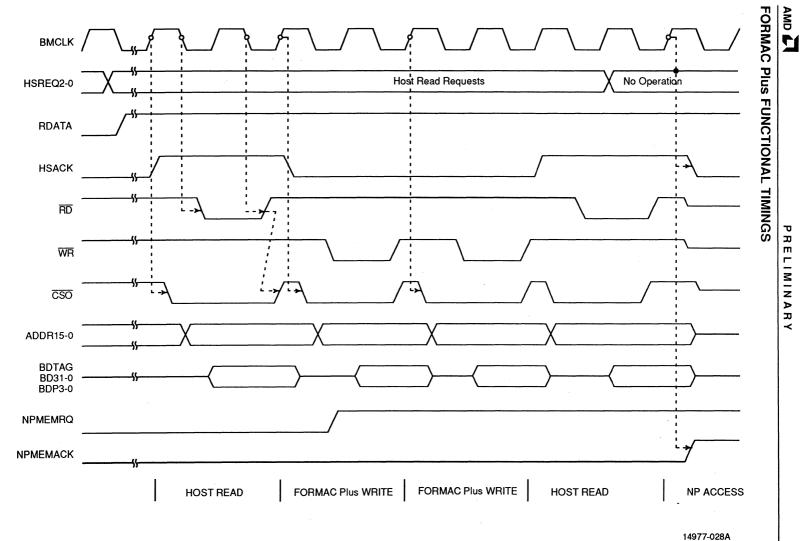

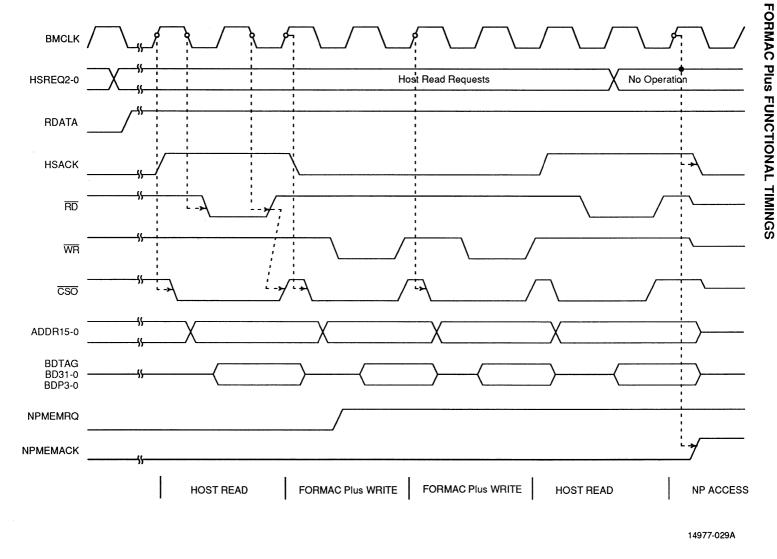

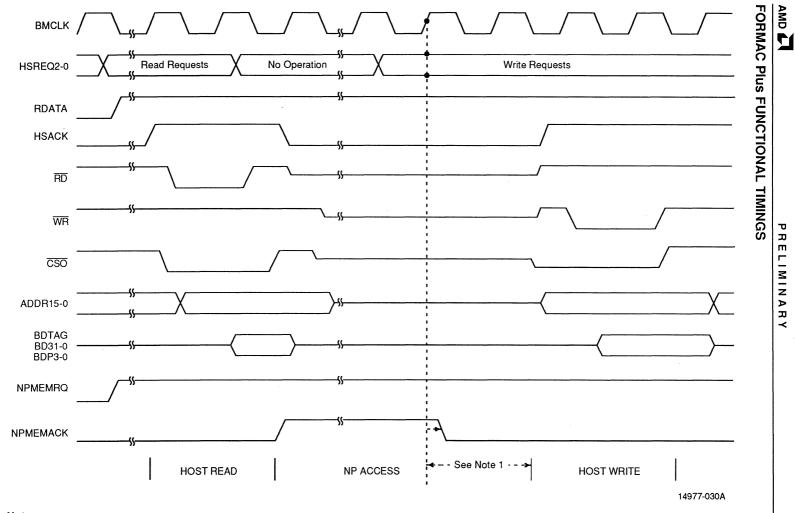

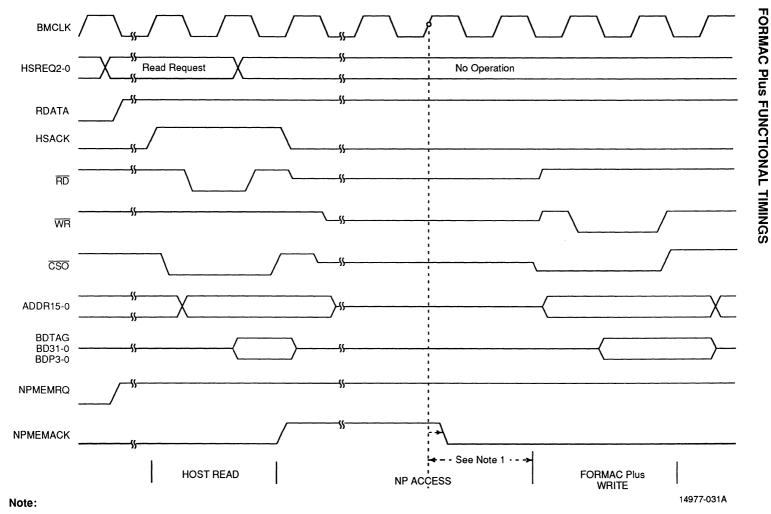

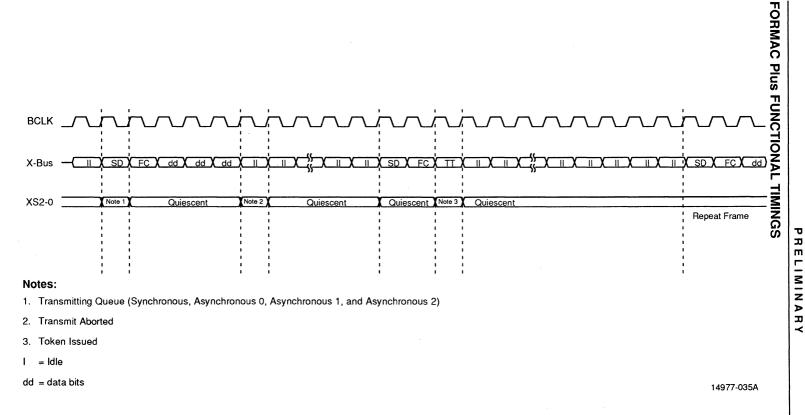

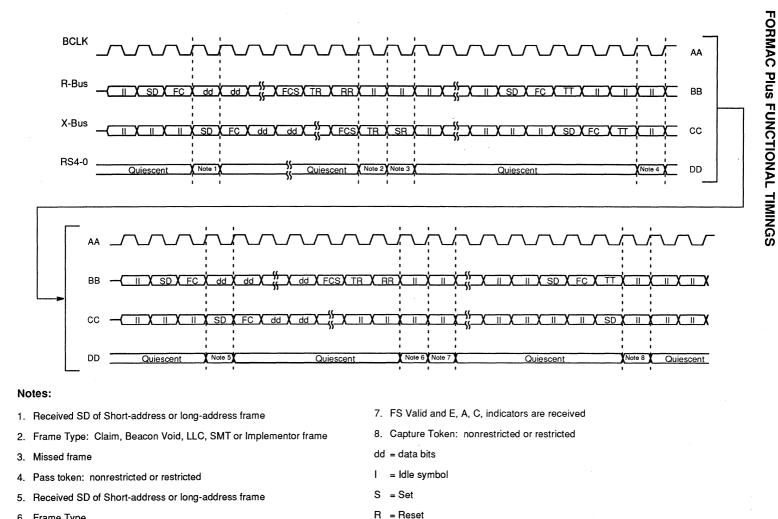

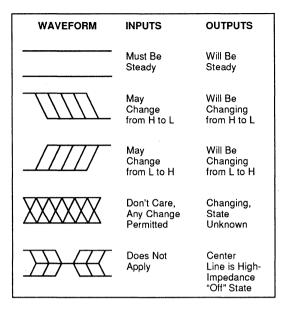

| FORMAC Plus Functional Timings                                               |         |

| Absolute Maximum Ratings                                                     |         |

| Operating Ranges .                                                           |         |

| DC Characteristics Over Commercial Operating Ranges                          |         |

|                                                                              |         |

| Switching Characteristics Over Commercial Operating Ranges                   |         |

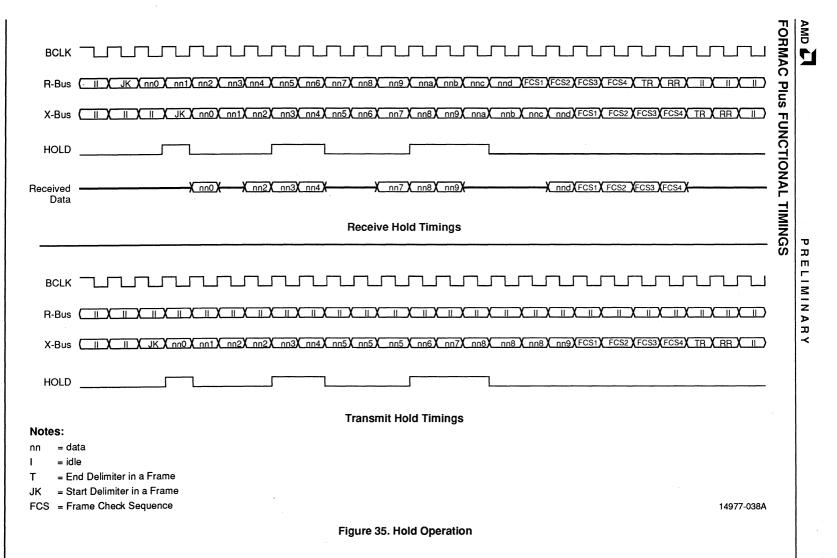

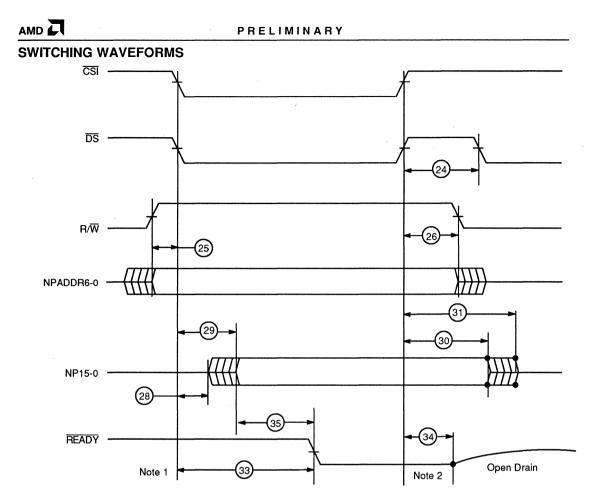

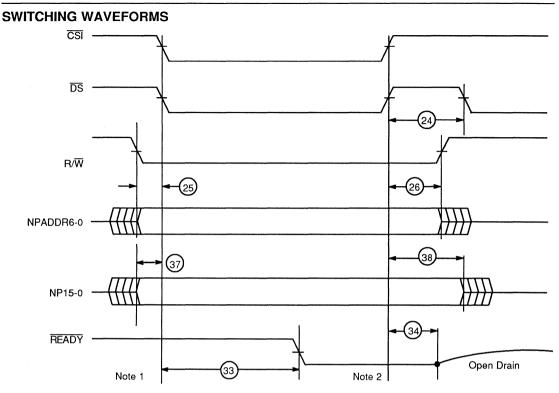

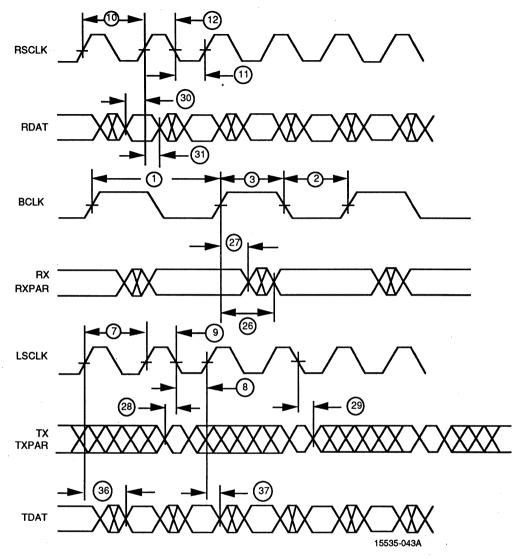

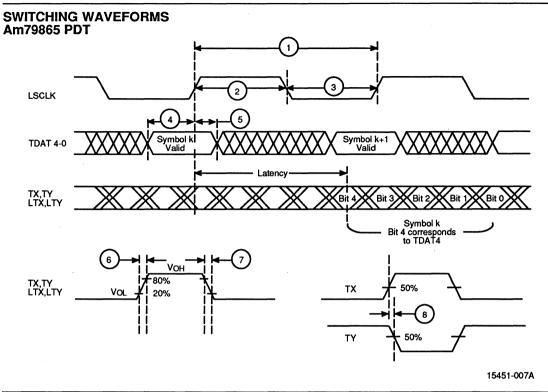

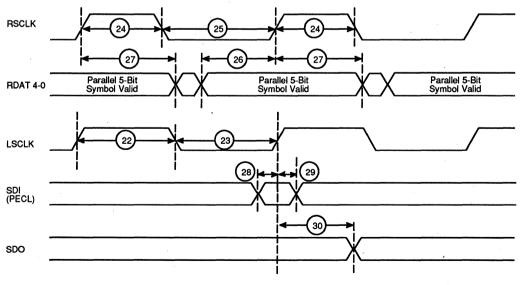

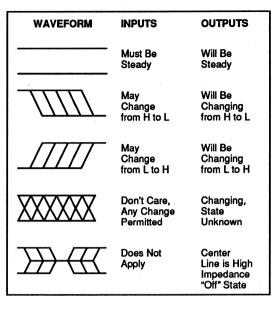

| Switching Waveforms                                                          |         |

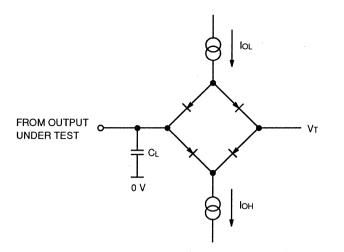

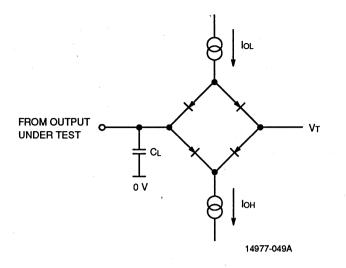

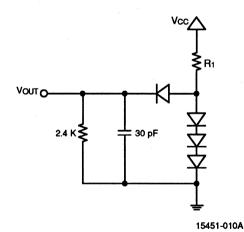

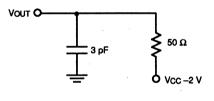

| Switching Test Circuit                                                       | . 2–126 |

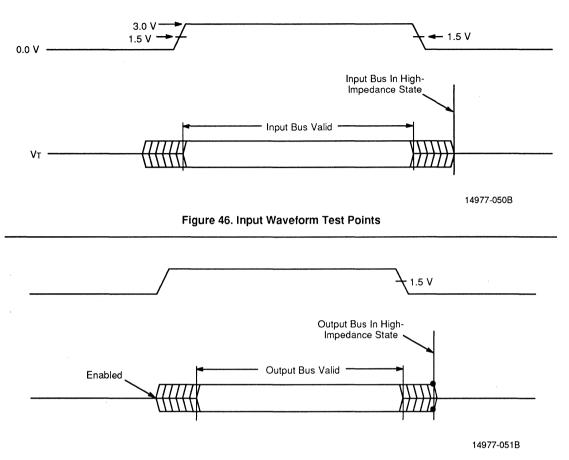

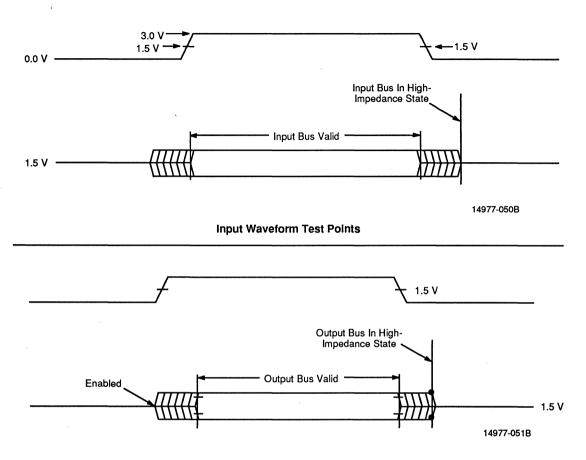

| Switching Test Waveforms                                                     | 2–127   |

| APPENDIX A                                                                   |         |

| GLOSSARY OF FORMAC Plus MNEMONICS                                            | . 2–128 |

|                                                                              |         |

|                                                                              |         |

| SUMMARY TABLES DESCRIBING FORMAC PLUS STATUS<br>REGISTERS AND MODE REGISTERS | 0 100   |

|                                                                              | . 2-136 |

#### FIGURE LIST

| BLOCK DIAGRAM                                                                      |

|------------------------------------------------------------------------------------|

| 169-Pin PGA CONNECTION DIAGRAM                                                     |

| 168-Pin PQFP CONNECTION DIAGRAM                                                    |

| LOGIC SYMBOL                                                                       |

| ORDERING INFORMATION                                                               |

| 1. FORMAC Plus FUNCTIONAL BLOCK DIAGRAM                                            |

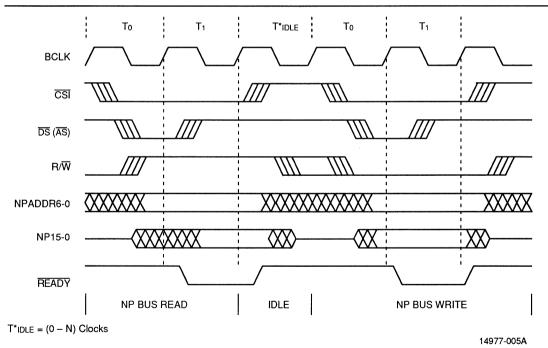

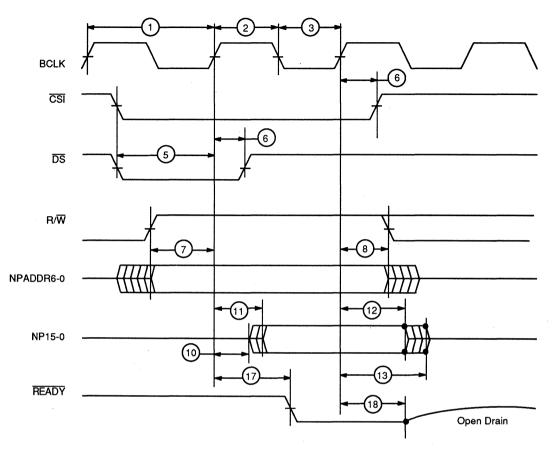

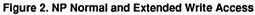

| 2. NP Bus Synchronous Read/Write Cycles                                            |

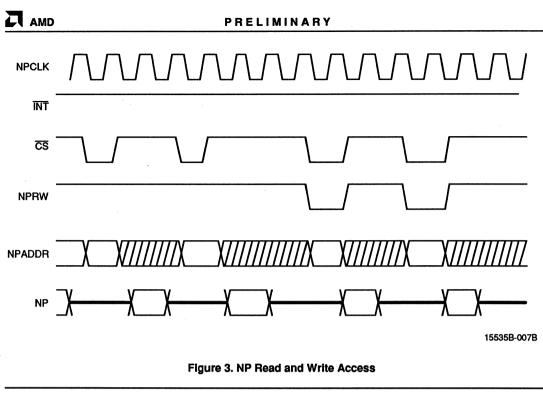

| 3. NP Bus Synchronous MDRU/MDRL Read/Write Cycles 2–46                             |

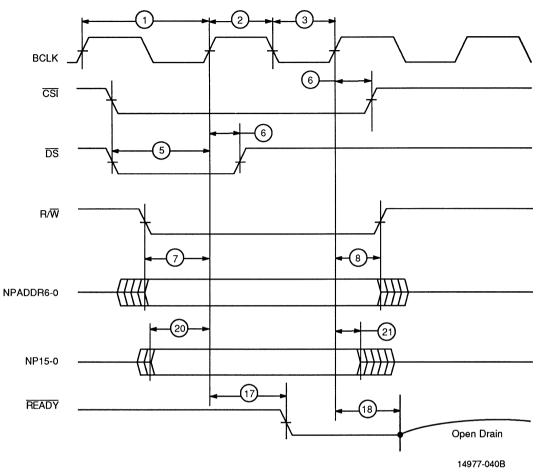

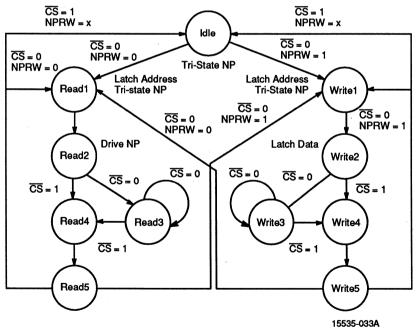

| 4. NP Bus Asynchronous Read/Write Cycles                                           |

| 5. Buffer Memory Organization (Tag and Nontag Modes) 2–49                          |

| 6. Buffer Memory Transmit Queue (Tag Mode) 2–50                                    |

| 7. Buffer Memory Receive Queue (Tag Mode)                                          |

| 8. Buffer Memory Transmit Queue (Nontag Mode) 2–55                                 |

| 9. Buffer Memory Transmit Chain (Nontag Mode) 2–56                                 |

| 10. Buffer Memory Receive Queue (Nontag Mode)                                      |

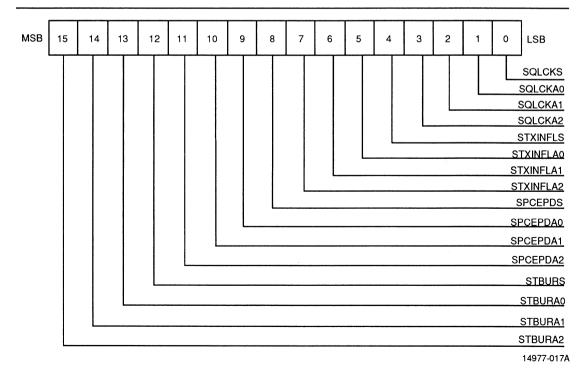

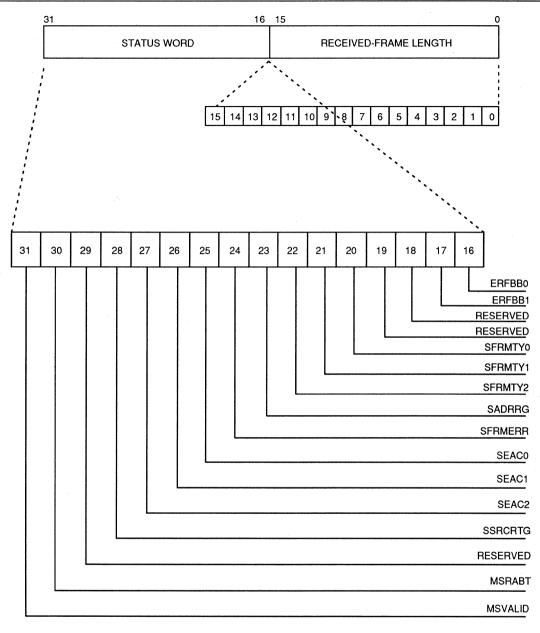

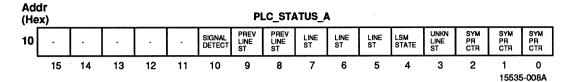

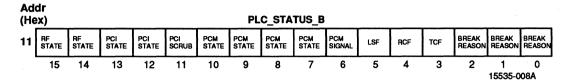

| 11. Status Register 1: Upper 16 Bits (ST1U) 2-61                                   |

| 12. Status Register 1: Lower 16 Bits (ST1L) 2-61                                   |

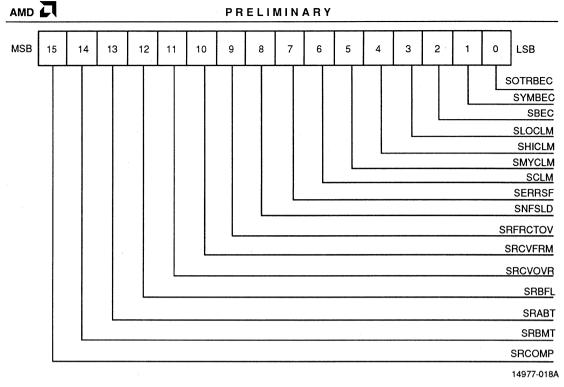

| 13. Status Register 2: Upper 16 Bits (ST2U)                                        |

| 14. Status Register 2: Lower 16 Bits (ST2L) 2–62                                   |

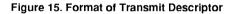

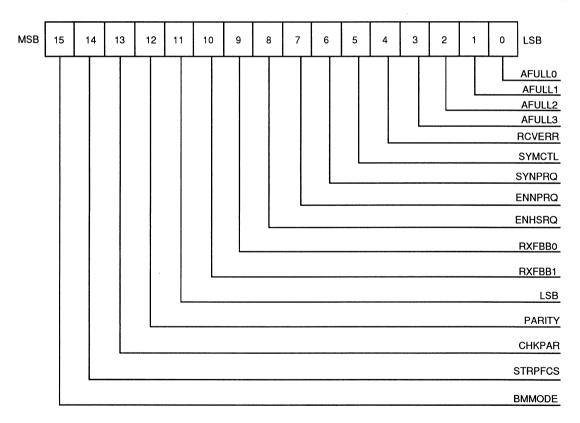

| 15. Format of Transmit Descriptor (Tag and Nontag Mode) 2–67                       |

| 16. Format of a Pointer (Nontag Mode) 2–67                                         |

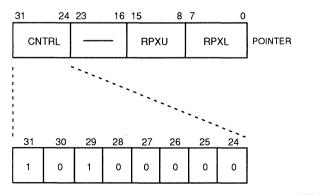

| 17. Receive Frame Status Word                                                      |

| <b>18. FDDI Frame Format</b>                                                       |

| 19. Mode Register 1 (MDREG1)                                                       |

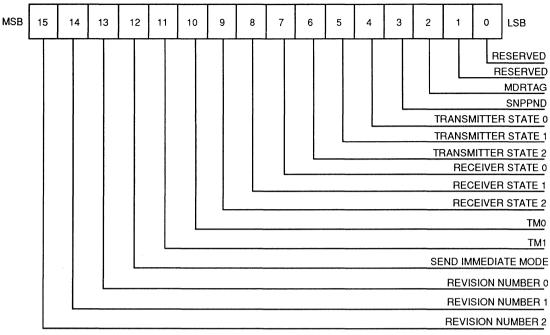

| 20. Mode Register 2 (MDREG2)                                                       |

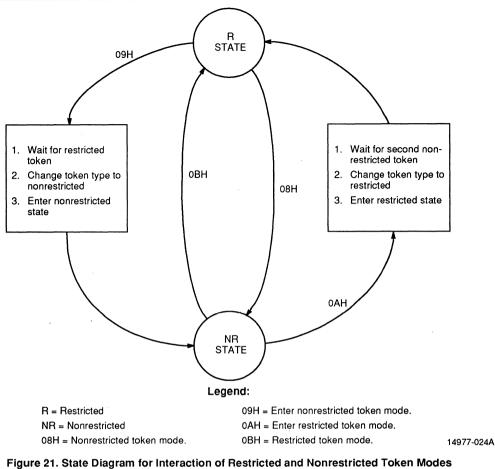

| 21. State Diagram for Interaction of Restricted and Nonrestricted Token Modes 2–89 |

| 22. MAC State Machine Register 2-95                                                |

| 23. Frame Threshold Register                                                       |

| 24. Host and FORMAC Plus Buffer Memory Access Timing (Back-to-Back Read) 2–99      |

| 25. Host and FORMAC Plus Buffer Memory Access Timing (Back-to-Back Write) 2–100    |

| 26. NP (DMA) Buffer Memory Access: Normal Handshake                                |

| 27. NP (DMA) Buffer Memory Access: Preemptive Host Write        | 2–102 |

|-----------------------------------------------------------------|-------|

| 28. NP (DMA) Buffer Memory Access: Preemptive FORMAC Plus Write | 2–103 |

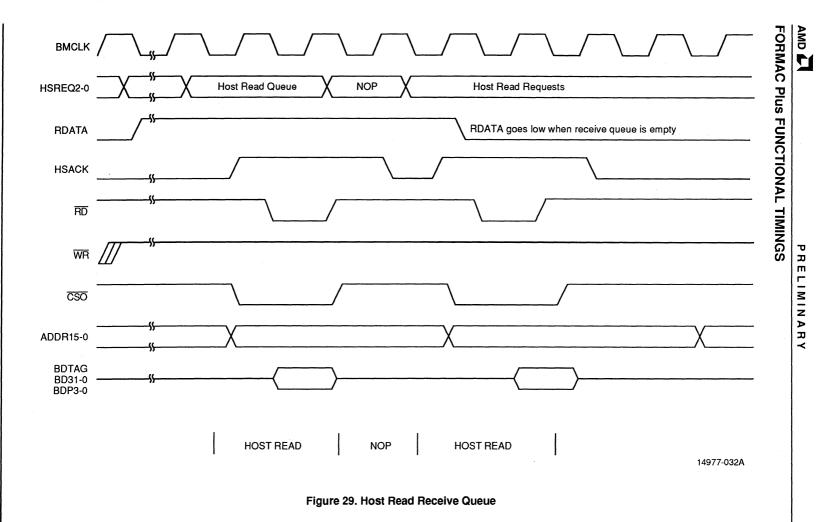

| 29. Host-Read Receive Queue                                     | 2–104 |

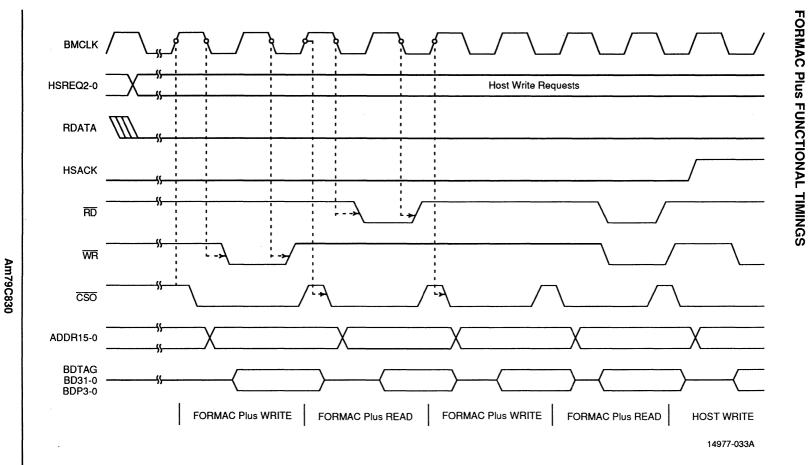

| 30. FORMAC Plus Buffer Memory Access                            | 2–105 |

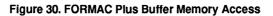

| 31. QCTRL and RDATA Operation During Host Buffer Memory Access  | 2–106 |

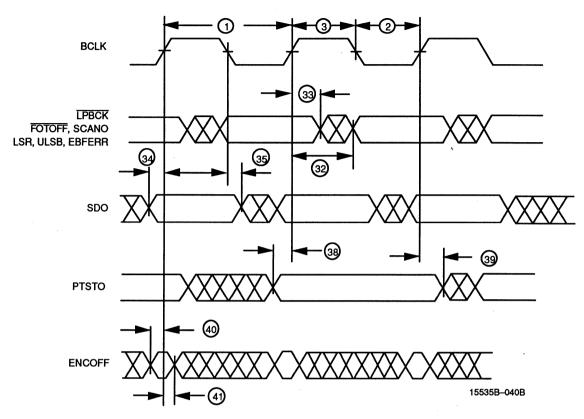

| 32. Transmit Signals Timing                                     | 2–107 |

| 33. Receive Status-Signals Timing                               | 2–108 |

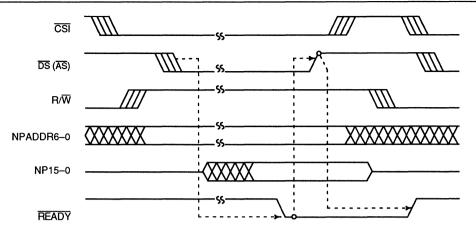

| 34. External Address Detection                                  | 2–109 |

| 35. Hold Operation                                              | 2–110 |

| 36. Node Processor (NP) Synchronous Read Timings                | 2–116 |

| 37. Node Processor (NP) Synchronous Write Timings               | 2–117 |

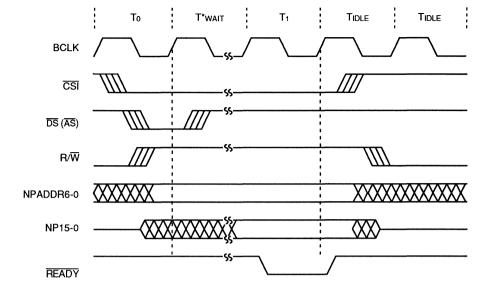

| 38. Node Processor (NP) Asynchronous Read Timings               | 2–118 |

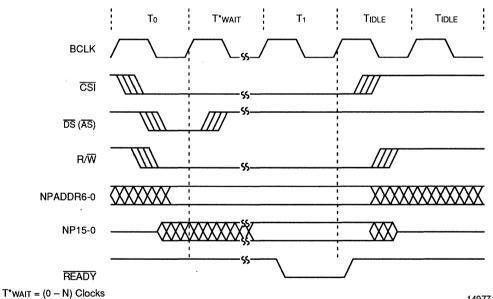

| 39. Node Processor (NP) Asynchronous Write Timings              | 2–119 |

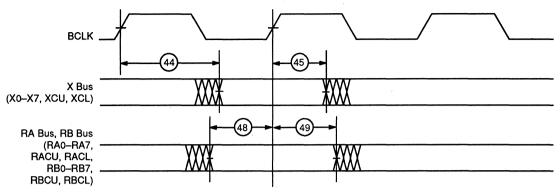

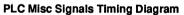

| 40. Physical Layer (PHY) Interface Timings                      | 2–120 |

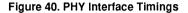

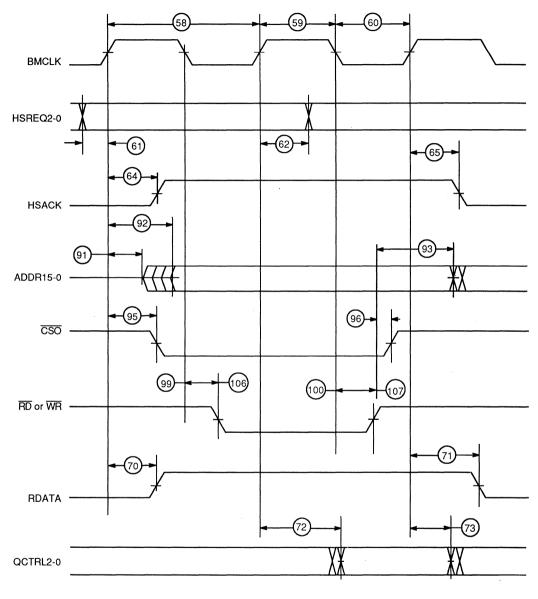

| 41 Host Interface Signal Timings                                | 2–121 |

| 42. Buffer Memory Read Cycle Timings                            | 2–122 |

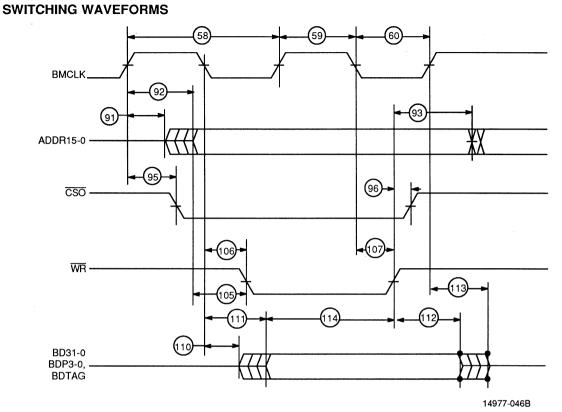

| 43. Buffer Memory Write Cycle Timings                           | 2–123 |

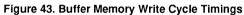

| 44. Node Processor (NP) DMA Cycle Timings                       | 2–124 |

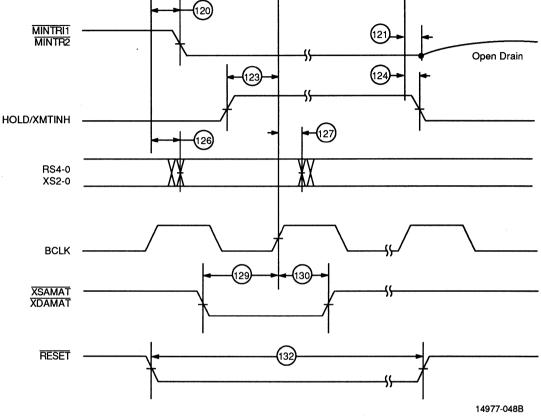

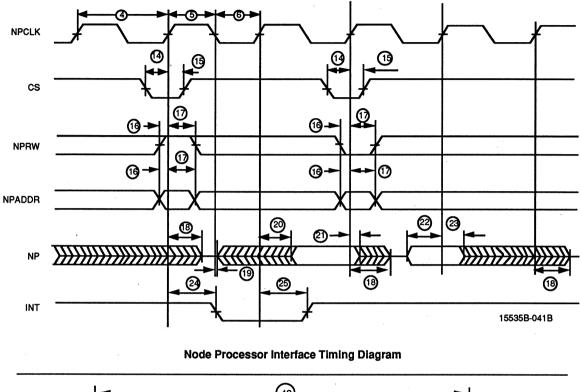

| 45. Miscellaneous Signals: AC Timings                           | 2–125 |

| 46. Input Waveform Test Points                                  | 2–127 |

| 47. Output Waveform Test Points                                 | 2–127 |

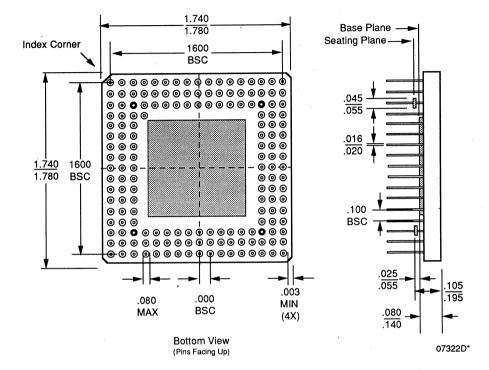

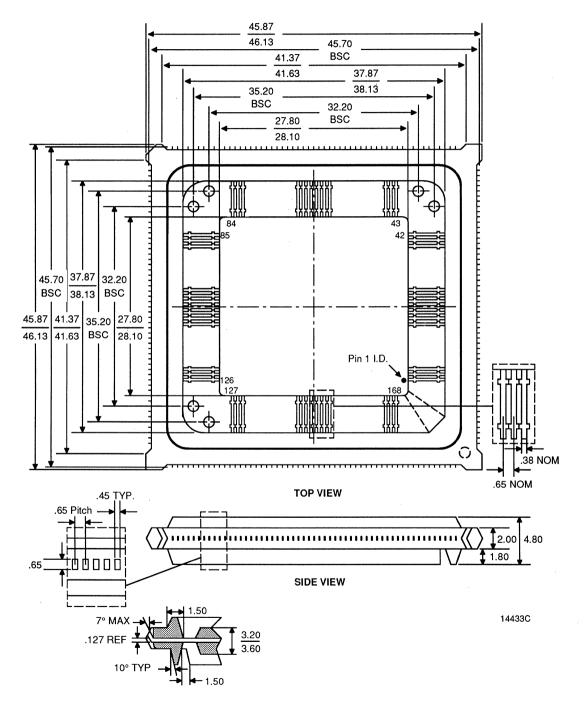

#### CONNECTION DIAGRAM 169-Pin PGA Bottom View (Pins Facing Up)

|    | A      | в      | С       | D        | Е       | F       | G    | н    | J     | к    | L    | М   | N      | Р        | R        | Т      | U          |    |

|----|--------|--------|---------|----------|---------|---------|------|------|-------|------|------|-----|--------|----------|----------|--------|------------|----|

| 1  | HSREQ2 | RST    | NPADDR4 | NPADDR3  | NPADDRO | NP14    | NP12 | NP10 | BCLK  | NP7  | NP6  | NP3 | NP1    | DS (AS)  | MINTRI   | XDAMAT | RACL       | 1  |

| 2  | RDATA  | HSREQ0 | NPMEMRQ | NPADDR6  | NPADDR2 | BMCLK   | NP13 | NP11 | NP9   | NP8  | NP5  | NP2 | CSI    | R/₩      | MINTR2   | XSAMAT | RA5        | 2  |

| 3  | QCTRL1 | HSACK  | HSREQ1  | NPMODE   | NPADDR5 | NPADDR1 | NP15 | GND  | vcc   | GND  | NP4  | NP0 | READY  | HOLD/XMT | INH RACU | RA7    | RA4        | 3  |

| 4  | ADDR15 | QCTRL2 | NPMEMAC | кеч<br>● |         |         |      |      |       |      |      |     |        |          | RA6      | RA3    | RA1        | 4  |

| 5  | ADDR14 | QCTRLO | GND     |          |         |         |      |      |       |      |      |     |        |          | RA2      | RAO    | RBCL       | 5  |

| 6  | ADDR12 | ADDR13 | GND     |          |         |         |      |      |       |      |      |     |        |          | RBCU     | RB7    | RB6        | 6  |

| 7  | ADDR10 | ADDR11 | vcc     |          |         |         |      |      |       |      |      |     |        |          | GND      | RB5    | RB4        | 7  |

| 8  | ADDR8  | ADDR9  | VCC     |          |         |         |      |      |       |      |      |     |        |          | GND      | RB3    | R82        | 8  |

| 9  | ADDR7  | ADDR6  | VCC     |          |         | FOF     |      |      |       | Am7  | '9C8 | 30  |        |          | GND      | RBO    | RB1        | 9  |

| 10 | ADDR5  | ADDR4  | VCC     |          |         |         |      | 1691 | PIN F | GA   |      |     |        |          | GND      | RS3    | RS4        | 10 |

| 11 | ADDR3  | ADDR2  | VCC     |          |         |         |      |      |       |      |      |     |        |          | VCC      | RS1    | RS2        | 11 |

| 12 | ADDR1  | ADDR0  | GND     |          |         |         |      |      |       |      |      |     |        |          | GND      | XCU    | RS0        | 12 |

| 13 | cso    | WR     | GND     |          |         |         |      |      |       |      |      |     |        |          | ХЗ       | X6     | XCL        | 13 |

| 14 | RD     | BDTAG  | GND     |          |         |         |      |      |       |      |      |     |        |          | хо       | X4     | <b>X</b> 7 | 14 |

|    |        |        |         |          |         |         |      |      |       |      |      |     |        |          |          |        |            | 15 |

| 15 | BD0    | BD1    | BD3     | GND      | GND G   | ND VC   | c \  | /CC  | VCC   | GND  | GND  | GI  | ND BC  | 30 BDP1  | XS0      | X1     | X5         | 15 |

| 16 | BD2    | BD4    | BD6     | BD8      | BD10 BC | 013 BD  | 15 B | D17  | BD20  | BD22 | BD24 | BC  | )26 BC | 28 BD31  | BDP2     | XS1    | X2         | 16 |

| 17 | BD5    | BD7    | BD9     | BD11 E   | BD12 BC | 014 BD  | 16 B | D18  | BD19  | BD21 | BD23 | BC  | 025 BC | 27 BD29  | BDP0     | BDP3   | XS2        | 17 |

|    | Α      | в      | С       | D        | E I     | = G     | ì    | н    | J     | к    | L    | N   | /1 N   | Р        | R        | т      | U          | •  |

14977-002A

AMD

## PGA PIN DESIGNATIONS (Listed by Pin Number)

| Pin Name | Pin No. | Pin Name | Pin No. | Pin Name | Pin No. | Pin Name                                          | Pin No. |

|----------|---------|----------|---------|----------|---------|---------------------------------------------------|---------|

| HSREQ2   | A-1     | NPADDR4  | C-1     | BD14     | F-17    | GND                                               | M-15    |

| RDATA    | A-2     | NPMEMRQ  | C-2     | NP12     | G-1     | BD26                                              | M-16    |

| QCTRL1   | A-3     | HSREQ1   | C-3     | NP13     | G-2     | BD25                                              | M-17    |

| ADDR15   | A-4     | NPMEMACK | C-4     | NP15     | G-3     | NP1                                               | N-1     |

| ADDR14   | A-5     | GND      | C-5     | vcc      | G-15    | CSI                                               | N-2     |

| ADDR12   | A-6     | GND      | C-6     | BD15     | G-16    | READY                                             | N-3     |

| ADDR10   | A-7     | VCC      | C-7     | BD16     | G-17    | BD30                                              | N-15    |

| ADDR8    | A-8     | VCC      | C-8     | NP10     | H-1     | BD28                                              | N-16    |

| ADDR7    | A-9     | VCC      | C-9     | NP11     | H-2     | BD27                                              | N-17    |

| ADDR5    | A-10    | VCC      | C-10    | GND      | H-3     | $\overline{\text{DS}}$ ( $\overline{\text{AS}}$ ) | P-1     |

| ADDR3    | A-11    | VCC      | C-11    | VCC      | H-15    | R/W                                               | P-2     |

| ADDR1    | A-12    | GND      | C-12    | BD17     | H-16    | HOLD/XMTINH                                       | P-3     |

| CSO      | A-13    | GND      | C-13    | BD18     | H-17    | BDP1                                              | P-15    |

| RD       | A-14    | GND      | C-14    | BCLK     | J-1     | BD31                                              | P-16    |

| BD0      | A-15    | BD3      | C-15    | NP9      | J-2     | BD29                                              | P-17    |

| BD2      | A-16    | BD6      | C-16    | VCC      | J-3     | MINTR1                                            | R-1     |

| BD5      | A-17    | BD9      | C-17    | VCC      | J-15    | MINTR2                                            | R-2     |

| RST      | B-1     | NPADDR3  | D-1     | BD20     | J-16    | RACU                                              | R-3     |

| HSREQ0   | B-2     | NPADDR6  | D-2     | BD19     | J-17    | RA6                                               | R-4     |

| HSACK    | B-3     | NPMODE   | D-3     | NP7      | K-1     | RA2                                               | R-5     |

| QCTRL2   | B-4     | GND      | D-15    | NP8      | K-2     | RBCU                                              | R-6     |

| QCTRL0   | B-5     | BD8      | D-16    | GND      | К-3     | GND                                               | R-7     |

| ADDR13   | B-6     | BD11     | D-17    | GND      | K-15    | GND                                               | R-8     |

| ADDR11   | B-7     | NPADDR0  | E-1     | BD22     | K-16    | GND                                               | R-9     |

| ADDR9    | B-8     | NPADDR2  | E-2     | BD21     | K-17    | GND                                               | R-10    |

| ADDR6    | B-9     | NPADDR5  | E-3     | NP6      | L-1     | VCC                                               | R-11    |

| ADDR4    | B-10    | GND      | E-15    | NP5      | L-2     | GND                                               | R-12    |

| ADDR2    | B-11    | BD10     | E-16    | NP4      | L-3     | ХЗ                                                | R-13    |

| ADDR0    | B-12    | BD12     | E-17    | GND      | L-15    | XO                                                | R-14    |

| WR       | B-13    | NP14     | F-1     | BD24     | L-16    | XS0                                               | R-15    |

| BDTAG    | B-14    | BMCLK    | F-2     | BD23     | L-17    | BDP2                                              | R-16    |

| BD1      | B-15    | NPADDR1  | F-3     | NP3      | M-1     | BDP0                                              | R-17    |

| BD4      | B-16    | GND      | F-15    | NP2      | M-2     | XDAMAT                                            | T-1     |

| BD7      | B-17    | BD13     | F-16    | NP0      | M-3     | XSAMAT                                            | T-2     |

# PGA PIN DESIGNATIONS (Continued) (Listed by Pin Number)

| Pin Name | Pin No. |

|----------|---------|----------|---------|----------|---------|----------|---------|

| RA7      | T-3     | RS1      | T-11    | RA5      | U-2     | RS4      | U-10    |

| RA3      | T-4     | XCU      | T-12    | RA4      | U-3     | RS2      | U-11    |

| RA0      | T-5     | X6       | T-13    | RA1      | U-4     | RS0      | U-12    |

| RB7      | T-6     | X4       | T-14    | RBCL     | U-5     | XCL      | U-13    |

| RB5      | T-7     | X1       | T-15    | RB6      | U-6     | X7       | U-14    |

| RB3      | Т-8     | XS1      | T-16    | RB4      | U-7     | X5       | U-15    |

| RB0      | Т-9     | BDP3     | T-17    | RB2      | U-8     | X2       | U-16    |

| RS3      | T-10    | RACL     | U-1     | RB1      | U-9     | XS2      | U-17    |

,

## PGA PIN DESIGNATIONS (Listed by Pin Name)

| Pin Name | Pin No. | Pin Name | Pin No. | Pin Name    | Pin No. | Pin Name | Pin No. |

|----------|---------|----------|---------|-------------|---------|----------|---------|

| ADDR0    | B-12    | BD17     | H-16    | GND         | K-15    | NPADDR3  | D-1     |

| ADDR1    | A-12    | BD18     | H-17    | GND         | L-15    | NPADDR4  | C-1     |

| ADDR2    | B-11    | BD19     | J-17    | GND         | M-15    | NPADDR5  | E-3     |

| ADDR3    | A-11    | BD20     | J-16    | GND         | R-7     | NPADDR6  | D-2     |

| ADDR4    | B-10    | BD21     | K-17    | GND         | R-8     | NPMEMACK | C-4     |

| ADDR5    | A-10    | BD22     | K-16    | GND         | R-9     | NPMEMRQ  | C-2     |

| ADDR6    | B-9     | BD23     | L-17    | GND         | R-10    | NPMODE   | D-3     |

| ADDR7    | A-9     | BD24     | L-16    | GND         | R-12    | QCTRL0   | B-5     |

| ADDR8    | A-8     | BD25     | M-17    | HOLD/XMTINH | P-3     | QCTRL1   | A-3     |

| ADDR9    | B-8     | BD26     | M-16    | HSACK       | B-3     | QCTRL2   | B-4     |

| ADDR10   | A-7     | BD27     | Ň-17    | HSREQ0      | B-2     | RA0      | T-5     |

| ADDR11   | B-7     | BD28     | N-16    | HSREQ1      | C-3     | RA1      | U-4     |

| ADDR12   | A-6     | BD29     | P-17    | HSREQ2      | A-1     | RA2      | R-5     |

| ADDR13   | B-6     | BD30     | N-15    | MINTR1      | R-1     | RA3      | T-4     |

| ADDR14   | A-5     | BD31     | P-16    | MINTR2      | R-2     | RA4      | U-3     |

| ADDR15   | A-4     | BDP0     | R-17    | NP0         | M-3     | RA5      | U-2     |

| BCLK     | J-1     | BDP1     | P-15    | NP1         | N-1     | RA6      | R-4     |

| BD0      | A-15    | BDP2     | R-16    | NP2         | M-2     | RA7      | T-3     |

| BD1      | B-15    | BDP3     | T-17    | NP3         | M-1     | RACL     | U-1     |

| BD2      | A-16    | BDTAG    | B-14    | NP4         | L-3     | RACU     | R-3     |

| BD3      | C-15    | BMCLK    | F-2     | NP5         | L-2     | RB0      | T-9     |

| BD4      | B-16    | CSI      | N-2     | NP6         | L-1     | RB1      | U-9     |

| BD5      | A-17    | CSO      | A-13    | NP7         | K-1     | RB2      | U-8     |

| BD6      | C-16    | DS (AS)  | P-1     | NP8         | K-2     | RB3      | T-8     |

| BD7      | B-17    | GND      | C-5     | NP9         | J-2     | RB4      | U-7     |

| BD8      | D-16    | GND      | C-6     | NP10        | H-1     | RB5      | T-7     |

| BD9      | C-17    | GND      | C-12    | NP11        | H-2     | RB6      | U-6     |

| BD10     | E-16    | GND      | C-13    | NP12        | G-1     | RB7      | T-6     |

| BD11     | D-17    | GND      | C-14    | NP13        | G-2     | RBCL     | U-5     |

| BD12     | E-17    | GND      | D-15    | NP14        | F-1     | RBCU     | R-6     |

| BD13     | F-16    | GND      | E-15    | NP15        | G-3     | RDATA    | A-2     |

| BD14     | F-17    | GND      | F-15    | NPADDR0     | E-1     | RD       | A-14    |

| BD15     | G-16    | GND      | H-3     | NPADDR1     | F-3     | READY    | N-3     |

| BD16     | G-17    | GND      | K-3     | NPADDR2     | E-2     | RS0      | U-12    |

## PGA PIN DESIGNATIONS (Continued) (Listed by Pin Name)

| Pin Name | Pin No. | Pin Name | Pin No. | Pin Name | Pin No. | Pin Name   | Pin No. |

|----------|---------|----------|---------|----------|---------|------------|---------|

| RS1      | T-11    | VCC      | C-9     | WR       | B-13    | <b>X</b> 7 | U-14    |

| RS2      | U-11    | vcc      | C-10    | XO       | R-14    | XCL        | U-13    |

| RS3      | T-10    | vcc      | C-11    | X1       | T-15    | XCU        | T-12    |

| RS4      | U-10    | vcc      | G-15    | X2       | U-16    | XDAMAT     | T-1     |

| RST      | B-1     | vcc      | H-15    | Х3       | R-13    | XSO        | R-15    |

| R/W      | P-2     | vcc      | J-3     | X4       | T-14    | XS1        | T-16    |

| vcc      | C-7     | vcc      | J-15    | X5       | U-15    | XS2        | U-17    |

| vcc      | C-8     | vcc      | R-11    | X6       | T-13    | XSAMAT     | T-2     |

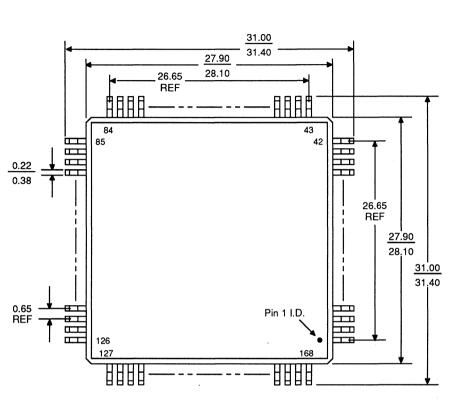

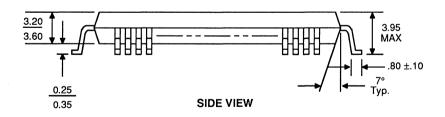

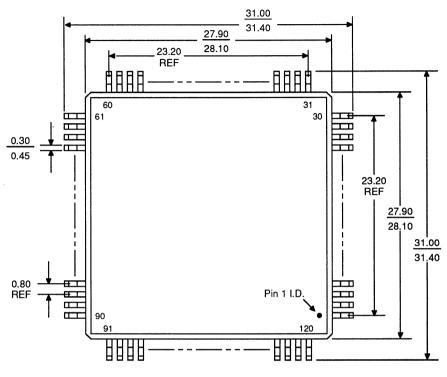

#### CONNECTION DIAGRAM

168-Pin PQFP (Top View)

14977-039A

#### PQFP PIN DESIGNATIONS (Listed by Pin Number)

| Pin Name | Pin No. | Pin Name | Pin No. | Pin Name | Pin No. | Pin Name    | Pin No. |

|----------|---------|----------|---------|----------|---------|-------------|---------|

| HSREQ1   | 1       | CSO      | 35      | BD23     | 69      | RS4         | 103     |

| HSREQ0   | 2       | WR       | 36      | GND      | 70      | GND         | 104     |

| NPMEMACK | 3       | RD       | 37      | BD24     | 71      | GND         | 105     |

| HSACK    | 4       | BDTAG    | 38      | BD25     | 72      | GND         | 106     |

| RDATA    | 5       | BD0      | 39      | GND      | 73      | GND         | 107     |

| QCTRL2   | 6       | BD1      | 40      | BD26     | 74      | RB0         | 108     |

| QCTRL1   | 7       | BD2      | 41      | BD27     | 75      | RB1         | 109     |

| QCTRL0   | 8       | BD3      | 42      | BD28     | 76      | RB2         | 110     |

| ADDR15   | 9       | BD4      | 43      | BD29     | 77      | RB3         | 111     |

| ADDR14   | 10      | BD5      | 44      | BD30     | 78      | RB4         | 112     |

| ADDR13   | 11      | BD6      | 45      | BD31     | 79      | RB5         | 113     |

| GND      | 12      | BD7      | 46      | BDP0     | 80      | RB6         | 114     |

| ADDR12   | 13      | BD8      | 47      | BDP1     | 81      | RB7         | 115     |

| ADDR11   | 14      | BD9      | 48      | BDP2     | 82      | RBCL        | 116     |

| GND      | 15      | BD10     | 49      | BDP3     | 83      | RBCU        | 117     |

| ADDR10   | 16      | BD11     | 50      | XS0      | 84      | RA0         | 118     |

| ADDR9    | 17      | BD12     | 51      | XS1      | 85      | RA1         | 119     |

| vcc      | 18      | BD13     | 52      | XS2      | 86      | RA2         | 120     |

| vcc      | 19      | GND      | 53      | X0       | 87      | RA3         | 121     |

| VCC      | 20      | BD14     | 54      | X1       | 88      | RA4         | 122     |

| VCC      | 21      | BD15     | 55      | X2       | 89      | RA5         | 123     |

| VCC      | 22      | GND      | 56      | ХЗ       | 90      | RA6         | 124     |

| ADDR8    | 23      | BD16     | 57      | X4       | 91      | RA7         | 125     |

| ADDR7    | 24      | BD17     | 58      | X5       | 92      | RACL        | 126     |

| GND      | 25      | GND      | 59      | X6       | 93      | RACU        | 127     |

| ADDR6    | 26      | BD18     | 60      | X7       | 94      | XSAMAT      | 128     |

| ADDR5    | 27      | BD19     | 61      | XCL      | 95      | XDAMAT      | 129     |

| GND      | 28      | VCC      | 62      | GND      | 96      | HOLD/XMTINH | 130     |

| ADDR4    | 29      | vcc      | 63      | XCU      | 97      | MINTR2      | 131     |

| ADDR3    | 30      | VCC      | 64      | RS0      | 98      | MINTR1      | 132     |

| GND      | 31      | BD20     | 65      | RS1      | 99      | READY       | 133     |

| ADDR2    | 32      | BD21     | 66      | VCC      | 100     | R/W         | 134     |

| ADDR1    | 33      | GND      | 67      | RS2      | 101     | DS (AS)     | 135     |

| ADDR0    | 34      | BD22     | 68      | RS3      | 102     | CSI         | 136     |

###

# PQFP PIN DESIGNATIONS (Listed by Pin Number)

| Pin Name | Pin No. |

|----------|---------|----------|---------|----------|---------|----------|---------|

| NP0      | 137     | NP7      | 145     | NP12     | 153     | NPADDR3  | 161     |

| NP1      | 138     | NP8      | 146     | NP13     | 154     | NPADDR4  | 162     |

| NP2      | 139     | vcc      | 147     | NP14     | 155     | NPADDR5  | 163     |

| NP3      | 140     | BCLK     | 148     | NP15     | 156     | NPADDR6  | 164     |

| NP4      | 141     | NP9      | 149     | BMCLK    | 157     | RST      | 165     |

| NP5      | 142     | NP10     | 150     | NPADDR0  | 158     | NPMODE   | 166     |

| GND      | 143     | GND      | 151     | NPADDR1  | 159     | NPMEMRQ  | 167     |

| NP6      | 144     | NP11     | 152     | NPADDR2  | 160     | HSREQ2   | 168     |

| Pin Name | Pin No. | Pin Name | Pin No. | Pin Name    | Pin No. | Pin Name | Pin No. |

|----------|---------|----------|---------|-------------|---------|----------|---------|

| ADDR0    | 34      | BD17     | 58      | GND         | 73      | NPADDR3  | 161     |

| ADDR1    | 33      | BD18     | 60      | GND         | 96      | NPADDR4  | 162     |

| ADDR2    | 32      | BD19     | 61      | GND         | 104     | NPADDR5  | 163     |

| ADDR3    | 30      | BD20     | 65      | GND         | 105     | NPADDR6  | 164     |

| ADDR4    | 29      | BD21     | 66      | GND         | 106     | NPMEMACK | 3       |

| ADDR5    | 27      | BD22     | 68      | GND         | 107     | NPMEMRQ  | 167     |

| ADDR6    | 26      | BD23     | 69      | GND         | 143     | NPMODE   | 166     |

| ADDR7    | 24      | BD24     | 71      | GND         | 151     | QCTRL0   | 8       |

| ADDR8    | 23      | BD25     | 72      | HOLD/XMTINH | 130     | QCTRL1   | 7       |

| ADDR9    | 17      | BD26     | 74      | HSACK       | 4       | QCTRL2   | 6       |

| ADDR10   | 16      | BD27     | 75      | HSREQ0      | 2       | RA0      | 118     |

| ADDR11   | 14      | BD28     | 76      | HSREQ1      | 1       | RA1      | 119     |

| ADDR12   | 13      | BD29     | 77      | HSREQ2      | 168     | RA2      | 120     |

| ADDR13   | 11      | BD30     | 78      | MINTR1      | 132     | RA3      | 121     |

| ADDR14   | 10      | BD31     | 79      | MINTR2      | 131     | RA4      | 122     |

| ADDR15   | 9       | BDP0     | 80      | NP0         | 137     | RA5      | 123     |

| BCLK     | 148     | BDP1     | 81      | NP1         | 138     | RA6      | 124     |

| BD0      | 39      | BDP2     | 82      | NP2         | 139     | RA7      | 125     |

| BD1      | 40      | BDP3     | 83      | NP3         | 140     | RACL     | 126     |

| BD2      | 41      | BDTAG    | 38      | NP4         | 141     | RACU     | 127     |

| BD3      | 42      | BMCLK    | 157     | NP5         | 142     | RB0      | 108     |

| BD4      | 43      | CSI      | 136     | NP6         | 144     | RB1      | 109     |

| BD5      | 44      | CSO      | 35      | NP7         | 145     | RB2      | 110     |

| BD6      | 45      | DS (AS)  | 135     | NP8         | 146     | RB3      | 111     |

| BD7      | 46      | GND      | 12      | NP9         | 149     | RB4      | 112     |

| BD8      | 47      | GND      | 15      | NP10        | 150     | RB5      | 113     |

| BD9      | 48      | GND      | 25      | NP11        | 152     | RB6      | 114     |

| BD10     | 49      | GND      | 28      | NP12        | 153     | RB7      | 115     |

| BD11     | 50      | GND      | 31      | NP13        | 154     | RBCL     | 116     |

| BD12     | 51      | GND      | 53      | NP14        | 155     | RBCU     | 117     |

| BD13     | 52      | GND      | 56      | NP15        | 156     | RD       | 37      |

| BD14     | 54      | GND      | 59      | NPADDR0     | 158     | RDATA    | 5       |

| BD15     | 55      | GND      | 67      | NPADDR1     | 159     | READY    | 133     |

| BD16     | 57      | GND      | 70      | NPADDR2     | 160     | RS0      | 98      |

# PQFP PIN DESIGNATIONS (Listed by Pin Name)

| Pin Name | Pin No. |

|----------|---------|----------|---------|----------|---------|----------|---------|

| RS1      | 99      | VCC      | 20      | WR       | 36      | X7       | 94      |

| RS2      | 101     | vcc      | 21      | XO       | 87      | XCL      | 95      |

| RS3      | 102     | vcc      | 22      | X1       | 88      | xcu      | 97      |

| RS4      | 103     | vcc      | 62      | X2       | 89      | XDAMAT   | 129     |

| RST      | 165     | VCC      | 63      | Х3       | 90      | XS0      | 84      |

| R/W      | 134     | vcc      | 64      | X4       | 91      | XS1      | 85      |

| vcc      | 18      | vcc      | 100     | X5       | 92      | XS2      | 86      |

| vcc      | 19      | vcc      | 147     | X6       | 93      | XSAMAT   | 128     |

#### LOGIC SYMBOL

#### Legend:

NP - NODE PROCESSOR

- PHY PHYSICAL LAYER

- BM BUFFER MEMORY

- VCC +5 VOLTS

#### ORDERING INFORMATION

#### **Standard Products**

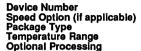

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of these elements:

| Valid Combinations |              |  |  |

|--------------------|--------------|--|--|

| AM79C830           | GC, KC, KC/W |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### **PIN DESCRIPTION**

#### Physical-Layer (PHY) Interface (30 pins)

The following section describes the pins that interface the FORMAC Plus with the physical layer (PHY) device. These signals are synchronous to BCLK.

#### RACU

#### **Receive A Control Upper (input)**

RACU is asserted high to indicate that the upper nibble of the RA bus (RA7-4) is a network control character. When RACU is low, this nibble contains data. RACU is synchronous to BCLK.

#### RACL

#### **Receive A Control Lower (input)**

RACL is asserted high to indicate that the lower nibble of the RA bus (RA3-0) is a network control character. When RACL is low, this nibble contains data. RACL is synchronous to BCLK.

#### RA7-0

#### Receive Bus A (input)

The RA bus is used to receive information from the physical layer (PHY) device. Bytes clocked from the physical layer (PHY) into the FORMAC Plus RA bus input are synchronous to BCLK.

#### RBCU

#### **Receive B Control Upper (input)**

RBCU is asserted high to indicate that the upper nibble of the RB bus (RB7-4) is a network control character. When RBCU is low, this nibble contains data. RBCU is synchronous to BCLK.

#### RBCL

#### **Receive B Control Lower (input)**

RBCL is asserted high to indicate that the lower nibble of the RB bus (RB3-0) is a network control character. When RBCL is low, this nibble contains data. RBCL is synchronous to BCLK.

#### RB7-0

#### Receive Bus B (input)

The RB-bus is used to receive information from the physical layer (PHY) device. Bytes clocked from the physical layer (PHY) into the FORMAC Plus RB bus input are synchronous to BCLK.

#### XCU

#### Transmit Control Upper (output)

The XCU output signal is used to flag control symbols being presented on the upper nibble of the transmit bus. This signal is synchronous to BCLK. If XCU is asserted high, the upper nibble of the X bus is interpreted as a network control character. Otherwise, it is interpreted as a data nibble.

#### XCL

#### **Transmit Control Lower (output)**

The XCL output signal is used to flag control symbols being presented on the lower nibble of the transmit bus. This signal is synchronous to BCLK. If XCL is asserted high, the lower nibble of the X bus is interpreted as a network control character. Otherwise, it is interpreted as a data nibble.

#### X7-0

#### Transmit Bus (output)

This eight-bit output bus is used to send control and data information to the physical layer (PHY) device to be transmitted over the medium. Information on the X bus output is synchronous to BCLK.

#### Node-Processor (NP) interface (30 pins)

The following paragraphs describe the pins used to interface the FORMAC Plus with the node processor (NP) or other control devices. The NP interface is used for initializing the FORMAC Plus as well as for reporting status.

#### CSI

#### **Chip Select Input (input)**

- Asynchronous when NPMODE = 0

- Synchronous when NPMODE = 1

The chip-select Input (active low) enables Read and Write operations to the FORMAC Plus. In the asynchronous mode, the data output is enabled while  $\overline{CSI}$  and  $\overline{DS}$  are both low and  $\overline{R/W}$  is high. In the synchronous mode, the data output is enabled while  $\overline{CSI}$  is low and  $\overline{R/W}$  is high.

#### DS (AS) Data Strobe/Address Strobe (input)

-Asynchronous when NPMODE = 0

-Synchronous when NPMODE = 1

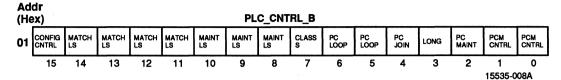

The  $\overline{\text{DS}}$  input (active low) is used in the handshake between the NP and FORMAC Plus when the FORMAC Plus acts as bus slave during register accesses. In the asynchronous mode, this input signal is set by the node processor to transfer data between the NP and the FORMAC Plus. The direction of the data transfer is dictated by the logic level of the R/W line. The NP sets  $\overline{\text{DS}}$ low to initiate a data transfer. In the synchronous mode,  $\overline{\text{DS}}$  functions as an address strobe ( $\overline{\text{AS}}$ ) and is used in conjunction with BCLK to latch the NPADDR bus (see Figure 2). In either mode, the chip-select input ( $\overline{\text{CSI}}$ ) must be low while  $\overline{\text{DS}}$  is low in order to start an NP bus transaction.

#### NPADDR6-0

#### NP Address bus (input)

The NPADDR6-0 input lines allow direct access to FOR-MAC Plus internal registers. In addition, these lines are used to place FORMAC Plus into different operating states.

The NPADDR bus of the FORMAC Plus performs two control functions. First, the input on NPADDR6-0 acts as an address, selecting the proper internal register for a read or write operation that is controlled by the  $R/\overline{W}$  pin. The data is either read onto or loaded from the 16-bit NP bus. For a discussion of the results of read and load instructions, see the section under Programming the FORMAC Plus. Secondly, using the NPADDR bus, instructions or commands can be issued to FORMAC Plus.

#### NP15-0

#### NP Data Bus (input, output, high impedance)

The NP bus is a 16-bit wide bidirectional data bus used to interface the FORMAC Plus to the node processor. Data transfer on the NP bus can be synchronous or asynchronous depending upon the setting of the NPMODE pin. For asynchronous operation, a two-wire handshake is provided through the  $\overline{\text{READY}}$  and datastrobe ( $\overline{\text{DS}}$ ) lines.

#### NPMODE

#### NP Bus Mode (input)

The level on the NPMODE pin defines the type of NPbus interface with the FORMAC Plus. When NPMODE is strapped high, the NP interface operates synchronously with BCLK. When NPMODE is strapped low, asynchronous interface operation is selected.

### MINTR1

#### Maskable Interrupt 1 (output, open drain)

The MINTR1 output (active low) is an attention line to the NP. MINTR1, when active, indicates an interrupt due to one or more unmasked flags in status register 1. In general, the active state of MINTR1 indicates that an unmasked interrupt condition or a transmit condition has occurred. MINTR1 is deactivated once either the lower or upper 16 bits of status register 1 (ST1L or ST1U) are read. Once MINTR1 is asserted, all 32 bits of status register 1 must be read to enable any future interrupt on this pin.

#### MINTR2

#### Maskable Interrupt 2 (output, open drain)

The MINTR2 output (active low) is an attention line to the NP. MINTR2, when active, indicates an interrupt due to one or more unmasked flags in status register 2. In general, the active state of MINTR2 indicates that an unmasked interrupt condition, a receive condition, or a change in ring status has occurred. MINTR2 is deactivated once either the lower or upper 16 bits of status register 2 (ST2L or ST2U) are read. Once MINTR2 is asserted, all 32 bits of status register 2 must be read in order to enable any future interrupt on this pin.

#### READY

#### Ready (output, open drain)

In asynchronous mode, the READY output (active low) is used in the handshake between the NP and FORMAC Plus. The FORMAC Plus READY output provides an asynchronous acknowledgment to the NP that data transfer is complete. The FORMAC Plus asserts READY when it has put the data onto the NP bus during a read cycle, or when it has taken the data from the NP bus during a write cycle. READY is a response to the CSI and DS, and returns high after the CSI or DS signal goes high.

In the synchronous mode, the  $\overline{READY}$  line goes active on the BCLK edge when  $\overline{CSI}$  and  $\overline{DS}$  are active.  $\overline{READY}$ goes inactive on the following BCLK edge. In the case of loading/reading of the MDR (memory data register),  $\overline{READY}$  goes active on the BCLK edge after the completion of any pending data transfer from/to buffer memory.

#### R/W

#### Read or Write select (input)

The R/ $\overline{W}$  line is used to select the type of access (i.e. read or write) between the FORMAC Plus and the NP. If R/ $\overline{W}$  is high, data is read from the FORMAC Plus to the NP. If R/ $\overline{W}$  is low, the data flow is from the NP to the FORMAC Plus.

BDTAG

#### **Buffer-Memory Interface (56 Pins)**

### \_\_\_\_\_

#### **ADDR15-0**

#### Buffer Memory Address (output, high impedance)

The 16-bit ADDR-bus provides the addresses that access the buffer memory. The address selection depends on the result of bus arbitration in the FORMAC Plus. Each memory access lasts for two BMCLK clock cycles and the address is valid for both of these cycles. When buffer memory control has been released to the NP, the ADDR bus is in the high-impedance state.

**Note**: As long as the use of the buffer memory has not been granted to the node processor or host (HSACK and NPMEMACK not active), the FORMAC Plus may drive the address lines even though no control signals are active.

#### BD31-0

### Buffer Memory Data Bus (input, output, high impedance)

The 32-bit BD bus interfaces the FORMAC Plus to the buffer memory or any external logic using this bus. These lines transfer data to and from the buffer memory for the FORMAC Plus. These signals are synchronous to BMCLK.

#### BDP3-0

## Buffer Data Parity Bus (input, output, high impedance)

The BDP3-0 bus contains the four byte-parity lines for the BD bus, in both the nontag and tag modes, as shown in the following table:

| BD-Bus Lines                      | Corresponding Parity Lines |

|-----------------------------------|----------------------------|

| BD7-0 and tag bit (tag mode only) | BDP0                       |

| BD15-8                            | BDP1                       |

| BD23-16                           | BDP2                       |

| BD31-24                           | BDP3                       |

#### Note:

BD bus parity can be either even or odd, based on the state of the parity bit (bit 12) in mode register 2 (MDREG2).

#### Tag Mode Only (input, output, high impedance)

In receive mode, this bit defines whether the information on the BD bus is data (BDTAG = 0) or frame status (BDTAG = 1). In transmit mode, when BDTAG = 1, it indicates that the end of a frame has been reached, as indicated by the presence of a tag bit in both the last long word and the descriptor word at the end of the frame. In transmit mode, when BDTAG = 0, it indicates that the information on the BD bus is data, i.e. end-of-frame not yet reached.

#### <u>cso</u>

#### Chip-Select Output (output, high impedance)

The chip-select output (active low) is a select signal for buffer memory read and write operations. This line is in the high-impedance state when buffer memory control is released to the NP.

#### RD

#### Buffer Memory Read (output, high impedance)

This output signal (active low) controls the buffer memory during a buffer-memory read accesses. This line is in the high-impedance state when buffer memory control is released to the NP.

#### WR

#### Buffer Memory Write (output, high impedance)