# Super386<sup>m</sup> DX

Programmer's Reference Manual

#### **Copyright Notice**

Software Copyright © 1992, Chips and Technologies, Inc. Manual Copyright © 1992, Chips and Technologies, Inc. All Rights Reserved.

Printed in U.S.A.

#### **Trademark Acknowledgment**

CHIPS<sup>®</sup> and the CHIPS logotype are registered trademarks of Chips and Technologies, Inc. Super386<sup>™</sup>, SuperSpace<sup>™</sup>, SuperState<sup>™</sup>, and SuperMath<sup>™</sup> are trademarks of Chips and Technologies, Inc.

${\bf IBM}^{\circledast} \mbox{ is a registered trademark of International Business Machines Corporation.} \\ {\bf Intel}^{\circledast} \mbox{ is a registered trademark of Intel Corp.}$

UNIX® is a registered trademark of AT&T Laboratories.

#### Disclaimer

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without express written permission of Chips and Technologies, Inc.

The information contained in this document is being issued in advance of the production cycle for the device(s). The parameters for the device(s) may change before final production.

Chips and Technologies, Inc. makes no representations or warranties regarding the contents of this manual. We reserve the right to revise the manual or make changes in the specifications of the product described within it at any time without notice and without obligation to notify any person of such revision or changes.

The information contained in this manual is provided for general use by our customers. Our customers should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

#### **Restricted Rights and Limitations**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013

Chips and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600

## Preface

This manual describes the software architecture of the Chips and Technologies Super386<sup>™</sup> DX/DXE processors—38600DX, 38605DX, 38600DXE, and 38605DXE. These processors are software-compatible with the industry-standard 80386 processor. The manual is addressed to experienced assembly-level programmers writing either application or system software. No previous knowledge of the 80386 processor or any similar processor architecture is assumed.

Unless otherwise stated, the term "processor" refers to both the 38600DX/DXE and 38605DX/DXE processors. The descriptions throughout most of the manual assume that the processor is running in its fully featured, 80386-compatible protected mode, which is explained in Chapter 2. The processors support two other modes for 8086 programs: real mode and virtual-8086 mode. The functioning of these modes is explained in the section entitled "Other Processor Modes" in Chapter 4.

## Organization

The manual contains four chapters and three appendices:

- Chapter 1, Introduction—Overview of the Super386 processors and a list of their features, including the SuperState V feature of the DXE processors.

- Chapter 2, Programmer's Model—Description of the Super386 processor as a collection of resources available to software. The chapter discusses the three execution modes, the data types directly supported by the instruction set, the organization of external memory and I/O spaces, the registers visible to software, and interrupts and exceptions. The chapter also describes the on-chip instruction cache of the 38605DX and DXE processors.

- Chapter 3, Instruction Set—Overview of the instruction set, organized by function. The chapter discusses operand types, addressing modes, flags, condition codes, and instruction encoding.

- Chapter 4, System Programming—Discussion of such operating-system issues as memory management, protection, I/O access, multitasking, interrupt and exception handling, and processor initialization. The chapter describes the use of execution modes other than the processor's native protected mode. It also describes the SuperState<sup>™</sup> V features of the DXE processors.

Application programmers need most of the material in the first three chapters. In these chapters, items of interest only to system programmers are identified as such. System programmers need all the material in the book.

Reference material is provided in three appendices:

- Appendix A, Instruction Set Reference—List of the instructions arranged alphabetically by assembler mnemonic. Gives detailed information on each instruction.

- Appendix B, Quick Reference Tables—Summary lists of opcodes, flag cross references, status flags, condition codes, instruction formats, and timing.

- Appendix C, Special Programming Considerations—Discussion of the effective use of advanced features.

A glossary of acronyms is provided along with an index.

## **Notations and Conventions**

The following notations and conventions are used:

- Processor Names—In general, the terms *processor* and *Super386 processor* apply to all the Super386 DX and DXE processors. When only one of these processors is referred to, or when the 80386 processor is referred to, the processor is named explicitly.

- Byte Quantities—Kilobytes is kB, megabytes is MB, gigabytes is GB.

- Binary and Hexadecimal Numbers—Binary numbers are followed by a b and hexadecimal numbers by an h. Numbers without a suffix are decimal. Thus, 00010001b = 17 = 11h.

- LSB—The least significant bit in the binary representation of a number is bit 0. In diagrams, bit 0 is at the right and the most-significant bit is at the left.

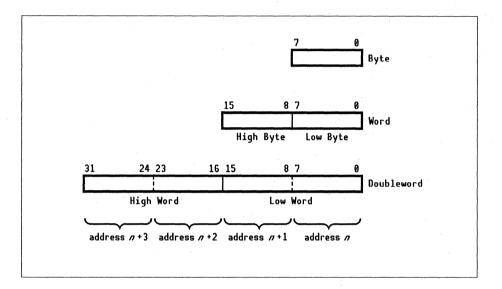

- Little-Endian Format—The Super386 processor is a *little-endian* machine. That is, a multiple-byte quantity is always stored with its least-significant byte at the lowest byte address. In illustrations, words and doublewords are shown with the least significant byte at the right. Byte addresses increase from right to left. As a consequence, strings are shown in reverse order.

- Memory Addresses—In illustrations of data structures in memory, the lowest memory address is at the bottom.

- Addressable Quantities—An 8-bit quantity is referred to as a byte; a 16-bit quantity is a word; and a 32-bit quantity is a doubleword or dword. The precessors described herein use byte addressing, in which memory is accessed as a sequence of addressable bytes.

- Segmented Addressing—When a segmented address contained in a register is mentioned, the acronym for both the segment and the register are shown, separated by a colon. For example, the address of a memory location contained in the data segment (DS) with an offset contained in the EBX register would be written as DS:EBX.

- Bit Ranges—When a range of bits is referred to, the highest and lowest bit numbers are shown, separated by a colon. For example, when the range is bit 15 to bit 9, it is referred to as 15:9.

- Bit Values—Bits can either be *set* or *cleared*. The term *set* means the bit has a binary value of 1. The term *cleared* means the bit has a binary value of 0.

- Reserved Bits—Some bits and bytes in register illustrations are marked *not available*. Do not store or use data at these locations. These bits should be masked out before testing, and the bit states should not be changed when the rest of the register is accessed.

## **Related Documents**

The following related documents are available from Chips and Technologies:

- Super386™DX/DXE High Performance CMOS Microprocessor Data Book

- Super386™DX Performance Test Report

- Super386<sup>™</sup>/SuperMath Compatibility Brief

- SuperState V<sup>™</sup>Architecture Manual.

In addition to these publications from Chips and Technologies, several commercial books provide special insights and different perspectives on programming with the Super386 processor. Rakesh Agarwal's two-volume book, *80x86 Architecture & Programming*, is an excellent guide for system programmers, with many examples of system routines written in pseudo-code. John Crawford and Patrick Gelsinger's book, *Programming the 80386*, provides another valuable viewpoint. This book is well illustrated and provides pseudo-code examples of common system software routines. Stephen Morse, Eric Isaacson, and Douglas Albert's book, *The 80386/387 Architecture*, is a clearly written text that relates the basic concepts of 80386 architecture to the earlier versions of that architecture.

# Contents

| Preface                   | iii |

|---------------------------|-----|

| Organization              | iii |

| Notations and Conventions | iv  |

| Related Documents         | v   |

### CHAPTER 1

| Introduction    |                       | 1-1 |

|-----------------|-----------------------|-----|

| Features of All | 1 Super386 Processors | 1-2 |

| Special Feature | res                   | 1-3 |

### CHAPTER 2

| Programmer's Model                      |

|-----------------------------------------|

| Memory Organization                     |

| Address Translation                     |

| Addressing Segmented Memory 2-6         |

| Descriptor Tables and Memory Models     |

| Storing Data in Memory 2-10             |

| Stack Operations                        |

| Input/Output                            |

| I/O Space                               |

| Memory-Mapped I/O 2-16                  |

| Resource Protection                     |

| Execution Modes                         |

| Data Types                              |

| Integers                                |

| Binary-Coded Decimal (BCD) Numbers 2-23 |

| Strings                                 |

| Pointers                                |

| Application Registers        | 2-27 |

|------------------------------|------|

| General Registers            | 2-29 |

| Status and Control Registers | 2-32 |

| Segment Registers            | 2-35 |

| Interrupts and Exceptions    | 2-36 |

| Interrupts                   | 2-36 |

| Exceptions                   | 2-37 |

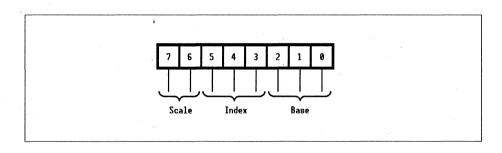

| On-Chip Instruction Cache    | 2-38 |

#### CHAPTER 3

| Instruction Set Overview              |

|---------------------------------------|

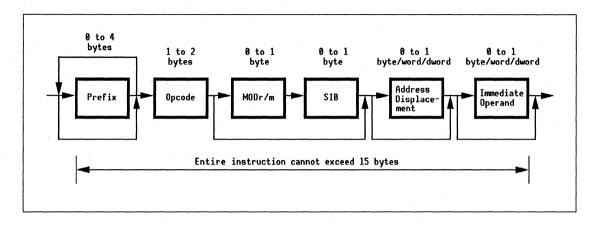

| Basic Instruction Format              |

| Prefixes                              |

| Opcode                                |

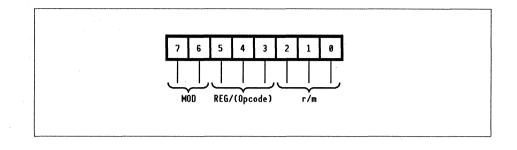

| MODr/m Encoding                       |

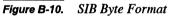

| SIB Encoding                          |

| Address Displacement                  |

| Immediate Operand                     |

| Operands                              |

| Operand Sizes                         |

| Register Operands                     |

| Memory Operands                       |

| Immediate Operands                    |

| I/O Operands                          |

| Flags                                 |

| Instruction Set                       |

| Data Movement Instructions            |

| I/O Data Movement Instructions        |

| Arithmetic Instructions               |

| Logical Instructions                  |

| Shift and Rotate Instructions         |

|                                       |

| Bit Manipulation Instructions         |

| String Instructions                   |

| Control Transfer Instructions         |

| Flag Instructions    3-2              |

| Segment Manipulation Instructions 3-2 |

| Protection Control Instructions 3-2   |

| Miscellaneous Instructions 3-2        |

#### PRELIMINARY

| Programming Guidelines       | <br>3-27 |

|------------------------------|----------|

| Register Usage               | <br>3-27 |

| Optimizing Execution Speed . | <br>3-28 |

### CHAPTER 4

| System Programming                              | 4-1  |

|-------------------------------------------------|------|

| System Registers                                | 4-3  |

| General Registers                               | 4-7  |

| Flags Register (EFLAGS)                         | 4-7  |

| Control Registers (MSW and Paging Control)      | 4-11 |

| Segmentation                                    | 4-13 |

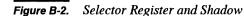

| Segment Registers and Their Shadows             | 4-14 |

| Segment Selectors                               | 4-15 |

| Segment Descriptors                             | 4-17 |

| Descriptor Tables and Their Registers           | 4-22 |

| Paging                                          | 4-30 |

| Entries in the Page Directories and Page Tables | 4-32 |

| Translation Lookaside Buffer (TLB)              | 4-35 |

| Page Aliases                                    | 4-36 |

| Paging and Multiprocessing                      | 4-37 |

| Control Gates and System Calls                  | 4-37 |

| Control Gate Descriptors                        | 4-41 |

| Call Gate                                       | 4-42 |

| Protection Mechanisms                           | 4-43 |

| Segment-Level Protection                        | 4-45 |

| Control Gate Protection                         | 4-49 |

| Page-Level Protection                           | 4-49 |

| I/O Protection                                  | 4-50 |

| Summary of Privilege-Level Checking and the CPL | 4-51 |

| Privileged Instructions                         | 4-53 |

| Conforming Code Segments                        | 4-53 |

| Multitasking                                    | 4-54 |

| Registers and Data Structures                   | 4-55 |

| Task Switching (Dispatching)                    | 4-68 |

| Task Memory Space                               |      |

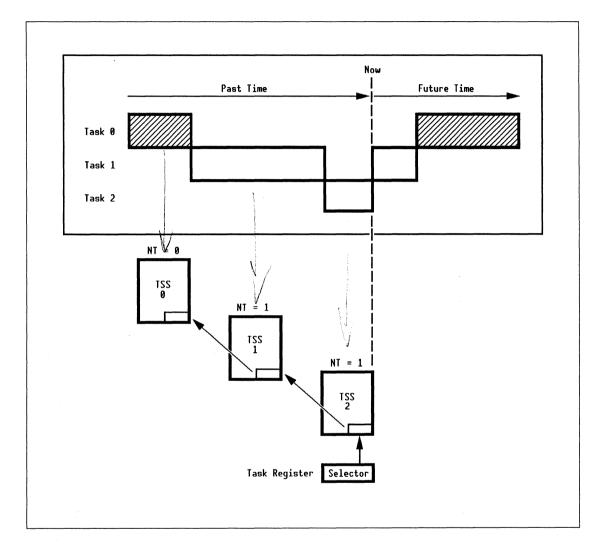

| Nested (Linked) Tasks                           | 4-70 |

|  | nts |  |

|--|-----|--|

|  |     |  |

|  |     |  |

2

|     | I/O                                                  | 4-72  |

|-----|------------------------------------------------------|-------|

|     | The I/O Space                                        | 4-72  |

|     | Memory-Mapped I/O                                    |       |

|     | I/O Privilege Level (IOPL)                           | 4-74  |

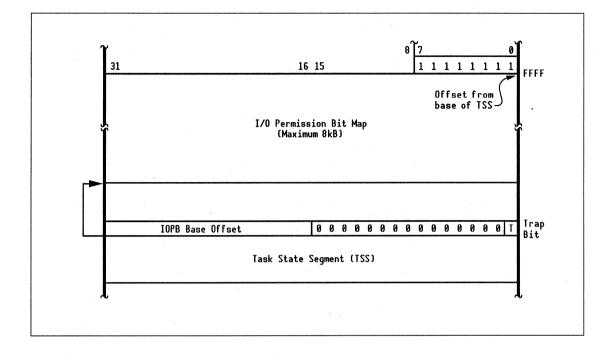

|     | I/O Permission Bitmap (IOPB)                         | 4-75  |

|     | Interrupts and Exceptions                            | 4-77  |

|     | Registers and Data Structures                        | 4-79  |

|     | Interrupt and Exception Handlers                     | 4-87  |

|     | Summary of Interrupt and Exception Conditions        | 4-90  |

|     | Simultaneous Interrupts or Exceptions                | 4-95  |

|     | Disabling Interrupts                                 | 4-97  |

| 5 × | Interrupt-Related Instructions                       | 4-98  |

|     | Initialization                                       | 4-99  |

|     | Reset                                                | 4-99  |

|     | Real-Mode Initialization                             | 4-102 |

|     | Protected-Mode Initialization                        | 4-102 |

|     | SuperState V Mode                                    | 4-104 |

|     | Entering SuperState V Mode                           | 4-105 |

|     | SuperState V Segment Descriptor                      | 4-105 |

|     | Saved Information                                    | 4-106 |

|     | SuperState V Entry Vectors                           | 4-106 |

|     | Events, Ports, and Interrupt Capture (EPIC) Facility |       |

|     | SuperState V Programmer's Environment                |       |

|     | 16-Byte Alignment of Segment Base Address            |       |

|     | The SCALL Instruction                                |       |

|     | System Security Issues                               |       |

|     | Instruction Pipeline and Cache Consistency           | 4-110 |

|     | Instruction Cache (38605 Only)                       | 4-110 |

|     | Shutdown and Halt                                    |       |

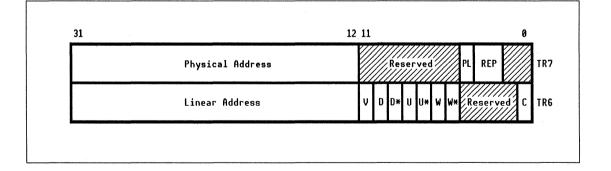

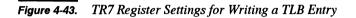

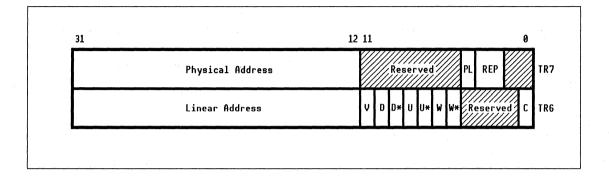

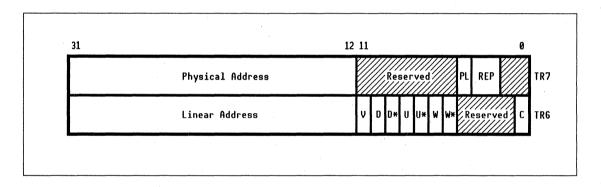

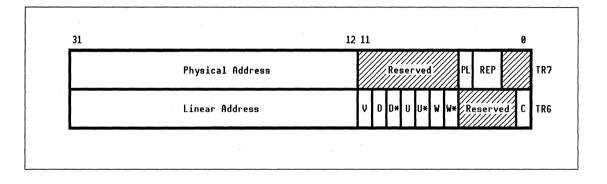

|     | Testing the TLB                                      | 4-112 |

|     | Writing TLB Entries                                  | 4-113 |

|     | Reading TLB Entries                                  | 4-116 |

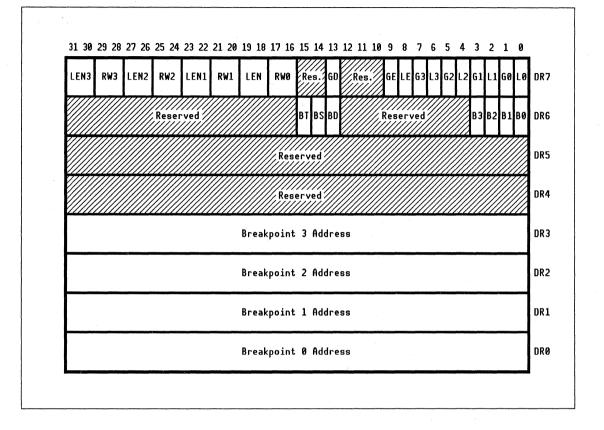

|     | Debugging                                            | 4-119 |

|     | Traditional Debugging With Interrupt Vector 03       | 4-119 |

|     | Using the Debug Registers                            | 4-119 |

|     |                                                      |       |

X

| Other Processor Modes                    | 4-128 |

|------------------------------------------|-------|

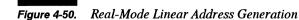

| Real Mode                                | 4-129 |

| Virtual-8086 Mode                        | 4-135 |

| Executing Protected-Mode 80286 Code      | 4-139 |

| Using Intermixed Word and Dword Operands | 4-142 |

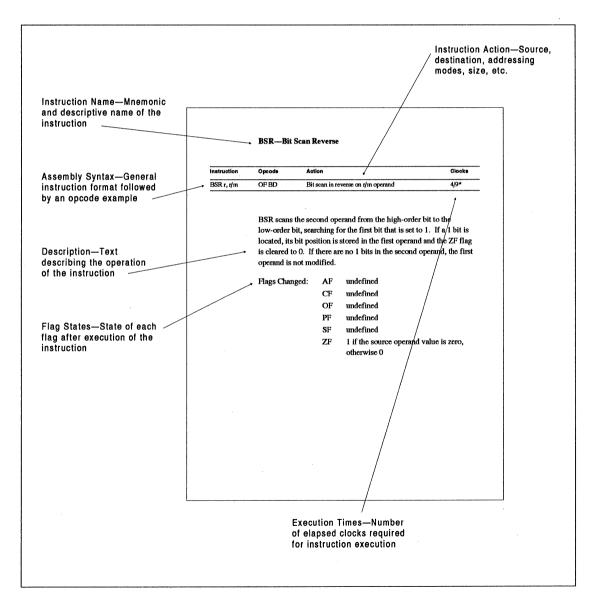

#### APPENDIX A

| The Super386 Instruction Set          |

|---------------------------------------|

| Notations A-1                         |

| Register Encoding A-4                 |

| Clock Counts A-5                      |

| Notations A-5                         |

| Basic Assumptions                     |

| Operand Conflicts                     |

| External Bus Wait and Hold States A-7 |

| Instruction Prefixes                  |

| Instruction Descriptions              |

#### APPENDIX B

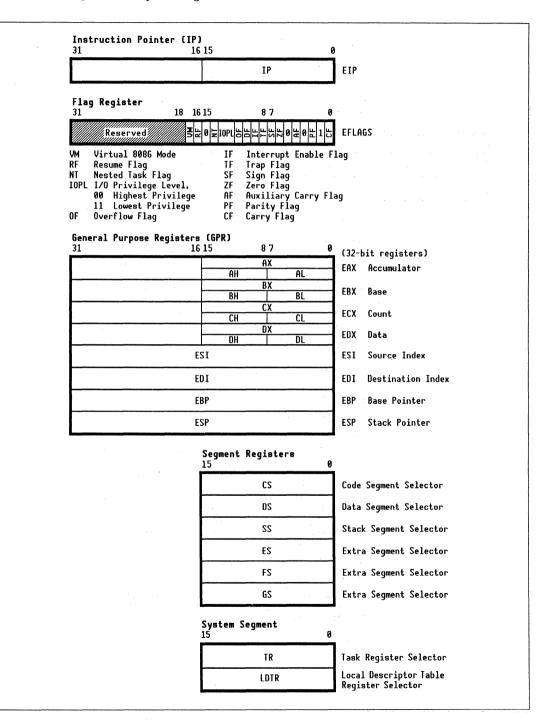

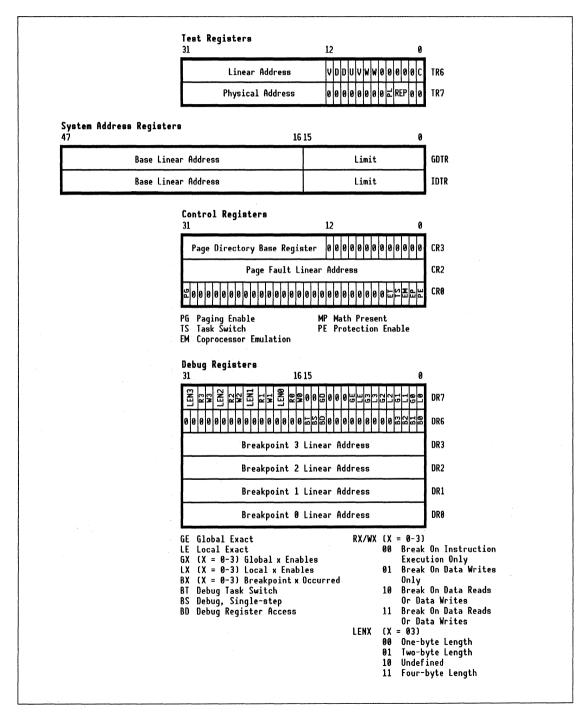

| Super386 Quick Reference  | B-1        |

|---------------------------|------------|

| System Register Reference | B-1        |

| Protected Mode Reference  | <b>B-4</b> |

| Instruction Reference     | B-12       |

| Address Mode Reference    | B-19       |

#### APPENDIX C

| Special Programming Considerations | <b>C-1</b> |

|------------------------------------|------------|

| The Translation Lookaside Buffer   | C-3        |

| Table Filling Mechanism            | C-3        |

| Modification of Translation Tables | C-4        |

| Page Aliasing                      | C-6        |

| Validating Multiple Translations   | C-6        |

| Exceptions                         | C-7        |

| Addresses Not Translated           | C-7        |

| Segment Descriptors                                  |

|------------------------------------------------------|

| In Real and Protected Modes C-8                      |

| Descriptor Table Modification                        |

| Segment Aliasing                                     |

| The 38605DX/DXE Instruction Cache                    |

| Cache Consistency Mechanism C-9                      |

| Enabling and Disabling the Instruction Cache         |

| The Instruction Fetching Mechanism                   |

| Sequence of Storage References C-12                  |

| Factors Influencing the Order of Instruction Fetches |

| Instruction Execution Ordering C-13                  |

| Instruction-Fetch Reordering C-13                    |

| Semaphore Locking C-15                               |

### GLOSSARY

INDEX

**Regional Sales Offices and Sales Representatives**

### List of Figures

| Figure 2-1.  | Example of Segmented Memory 2-2                            |

|--------------|------------------------------------------------------------|

| Figure 2-2.  | Logical Addressing of Segments 2-3                         |

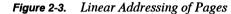

| Figure 2-3.  | Linear Addressing of Pages 2-4                             |

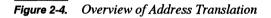

| Figure 2-4.  | Overview of Address Translation                            |

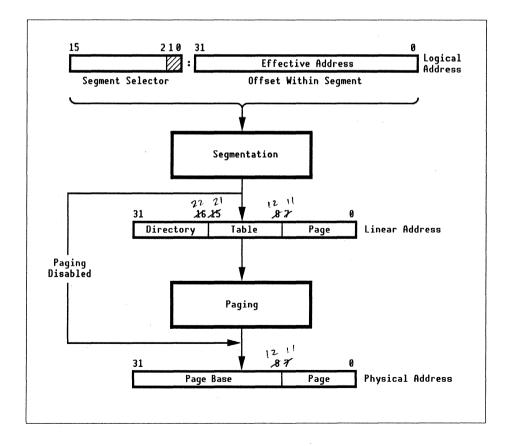

| Figure 2-5.  | Flat Memory Model 2-7                                      |

| Figure 2-6.  | Segmentation Strategy: Example 1 2-8                       |

| Figure 2-7.  | Segmentation Strategy: Example 2 2-9                       |

| Figure 2-8.  | Representation of Data in Memory 2-10                      |

| Figure 2-9.  | Data Alignment 2-11                                        |

| Figure 2-10. | Unaligned Accesses 2-12                                    |

| Figure 2-11. | Stack Organization, 32-Bit Operation 2-13                  |

| Figure 2-12. | I/O Space and Memory-Mapped I/O 2-15                       |

| Figure 2-13. | Privilege Levels 2-17                                      |

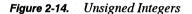

| Figure 2-14. | Unsigned Integers 2-20                                     |

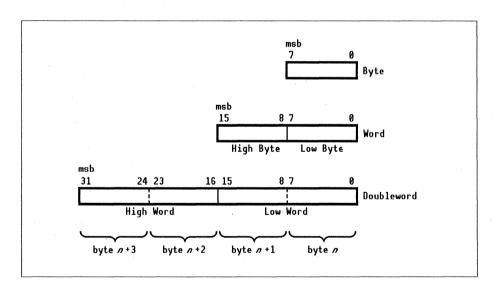

| Figure 2-15. | Two's-Complement Integers 2-21                             |

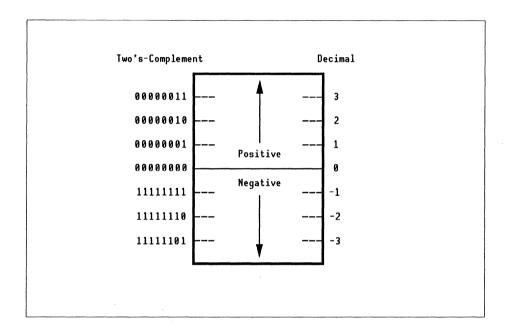

| Figure 2-16. | Signed Integers 2-22                                       |

| Figure 2-17. | Binary-Coded Decimal Numbers 2-23                          |

| Figure 2-18. | ASCII String                                               |

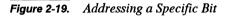

| Figure 2-19. | Addressing a Specific Bit 2-25                             |

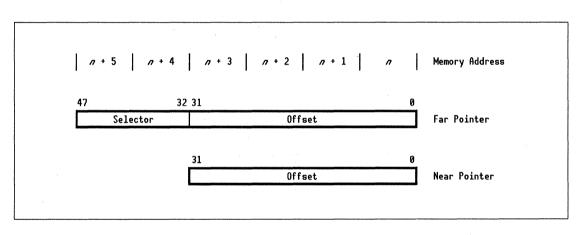

| Figure 2-20. | Near and Far Pointers                                      |

| Figure 2-21. | Registers Available to Application Programs 2-28           |

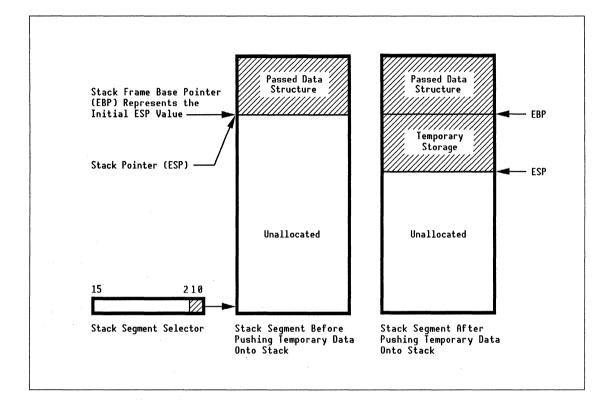

| Figure 2-22. | Use of the Stack-Frame Pointer 2-31                        |

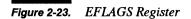

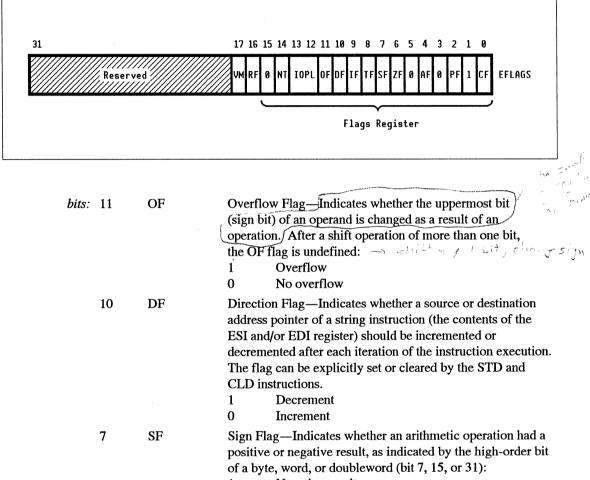

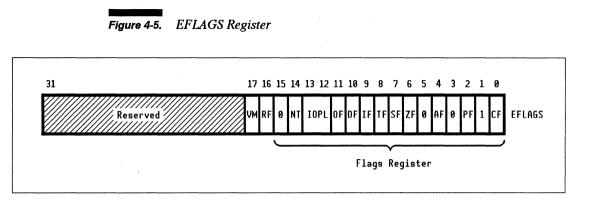

| Figure 2-23. | EFLAGS Register 2-33                                       |

| Figure 2-24. | Segment Register 2-35                                      |

|              |                                                            |

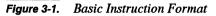

| Figure 3-1.  | Basic Instruction Format 3-2                               |

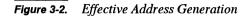

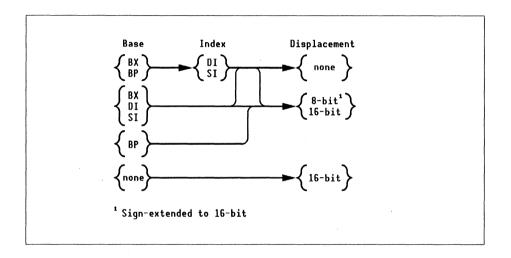

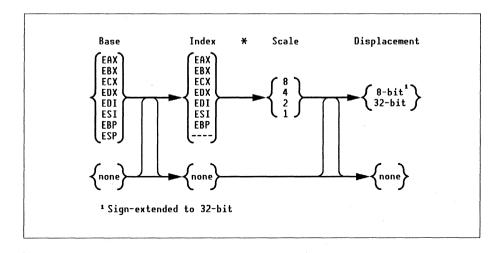

| Figure 3-2.  | Effective Address Generation 3-11                          |

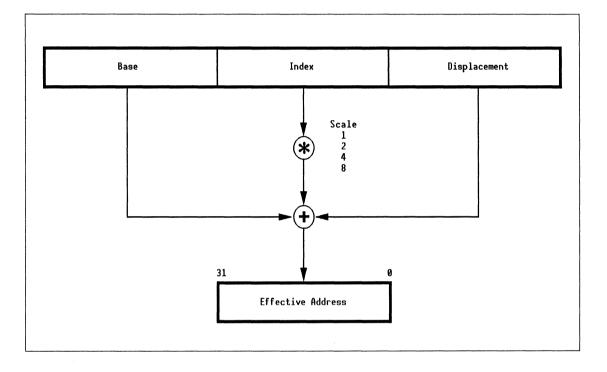

| Figure 3-3.  | Registers Used in 8-Bit and 16-Bit Effective               |

|              | Address Generation                                         |

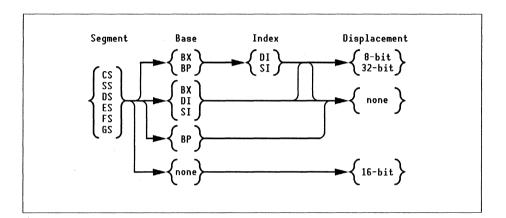

| Figure 3-4.  | Registers Used in 32-Bit Effective Address Generation 3-12 |

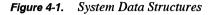

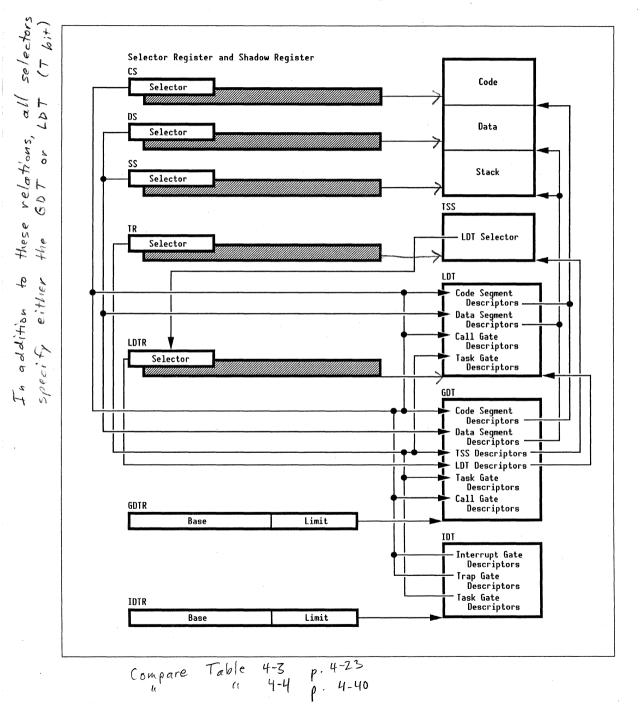

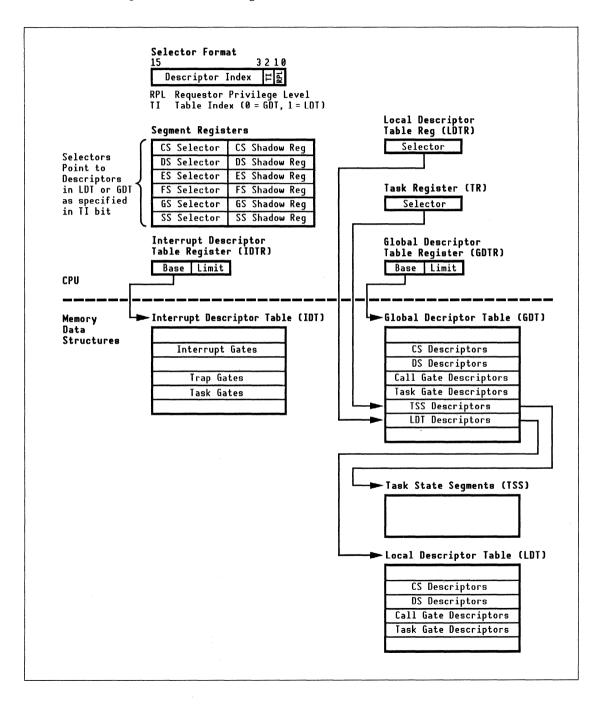

| Figure 4-1.  | System Data Structures 4-2                                        |

|--------------|-------------------------------------------------------------------|

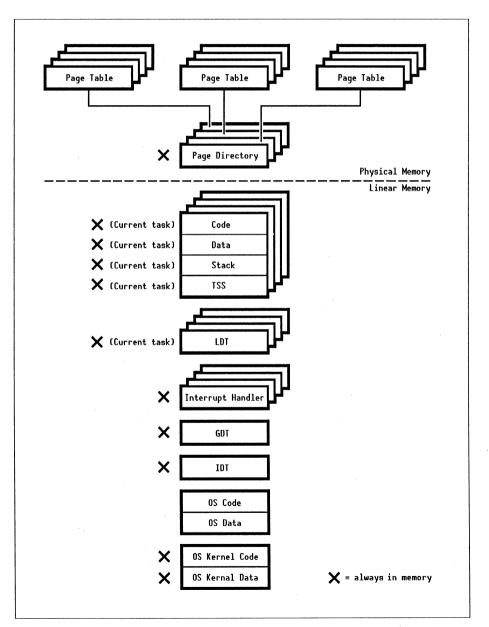

| Figure 4-2.  | System Registers 4-5                                              |

| Figure 4-3.  | Registers Associated With Segments and Tables                     |

| Figure 4-4.  | General Registers 4-7                                             |

| Figure 4-5.  | EFLAGS Register                                                   |

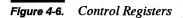

| Figure 4-6.  | Control Registers 4-12                                            |

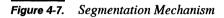

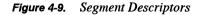

| Figure 4-7.  | Segmentation Mechanism 4-15                                       |

| Figure 4-8.  | Segment Selector                                                  |

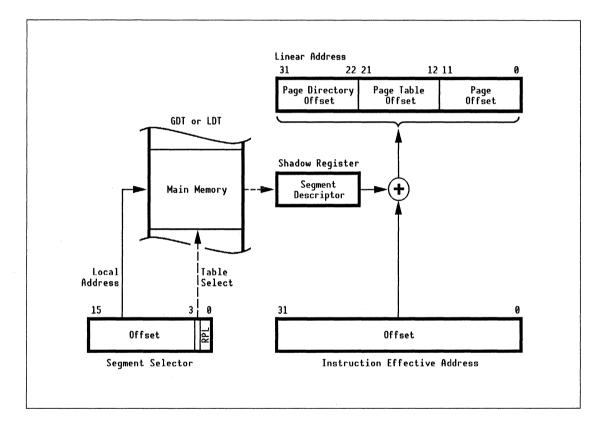

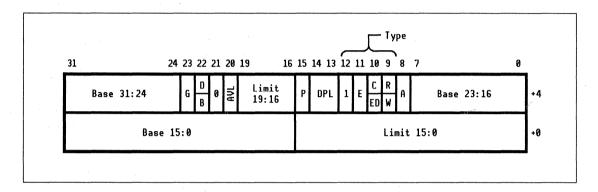

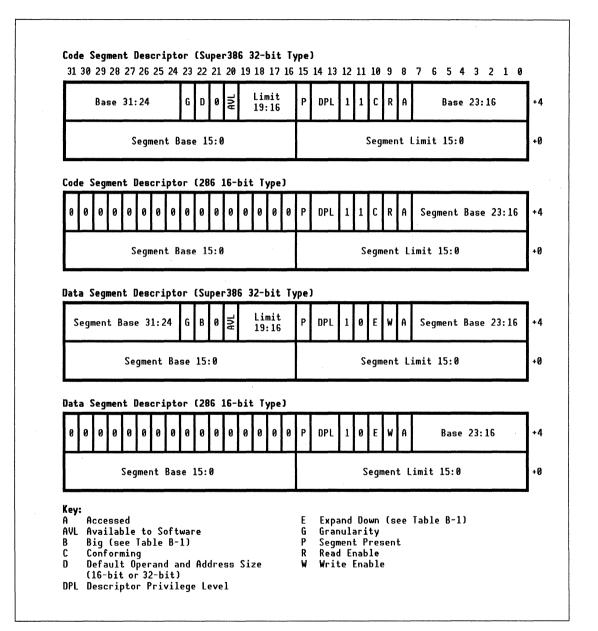

| Figure 4-9.  | Segment Descriptors 4-18                                          |

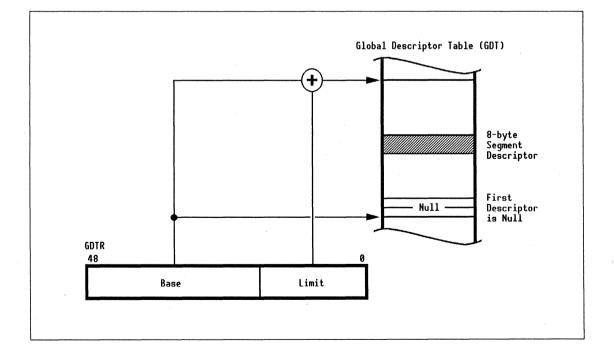

| Figure 4-10. | GDT and GDTR                                                      |

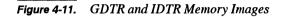

| Figure 4-11. | GDTR and IDTR Memory Images                                       |

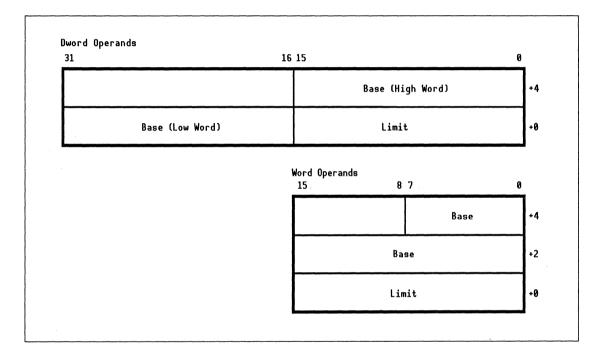

| Figure 4-12. | IDT and IDTR                                                      |

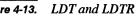

| Figure 4-13. | LDT and LDTR                                                      |

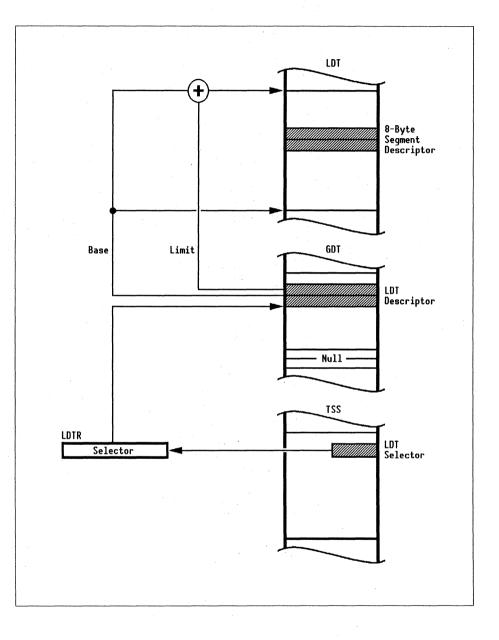

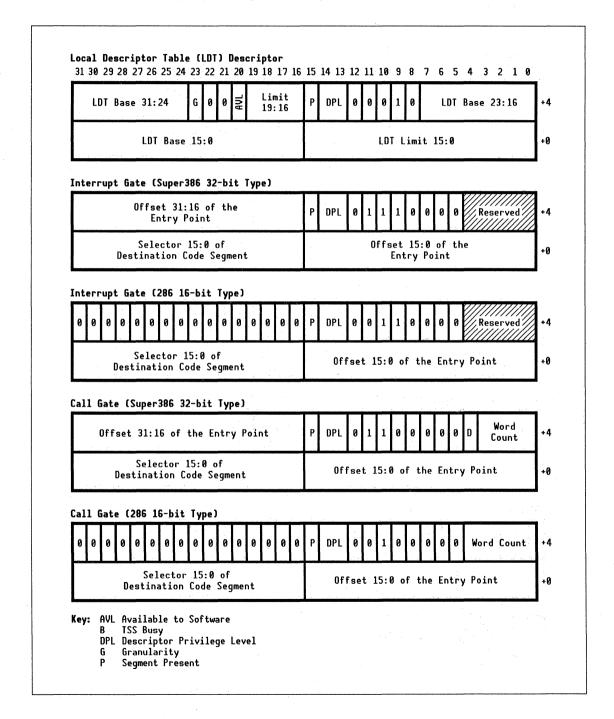

| Figure 4-14. | Local Descriptor Table (LDT) Descriptor                           |

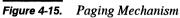

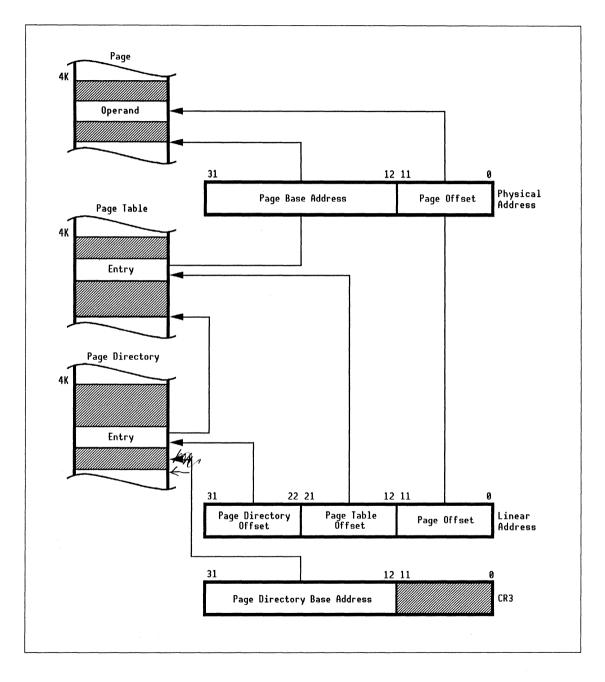

| Figure 4-15. | Paging Mechanism 4-31                                             |

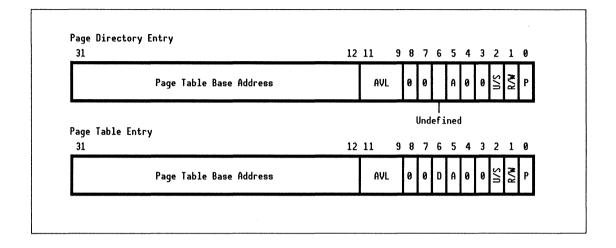

| Figure 4-16. | Format of Page Directory and Page Table Entries                   |

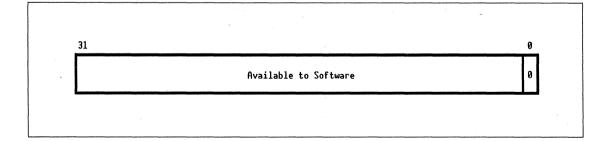

| Figure 4-17. | Format of Not-Present Entries (Page Directory or Page Table) 4-34 |

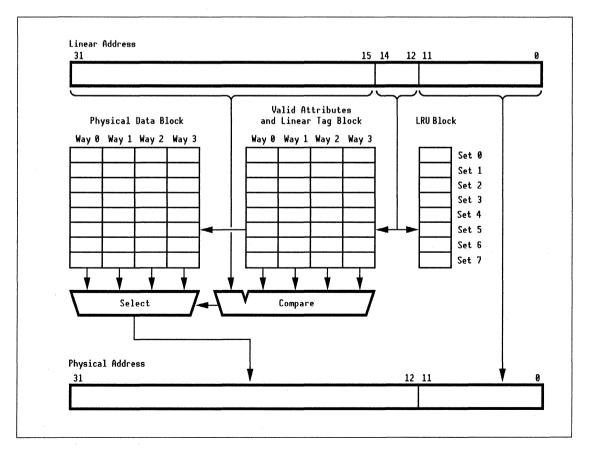

| Figure 4-18. | Translation Lookaside Buffer 4-35                                 |

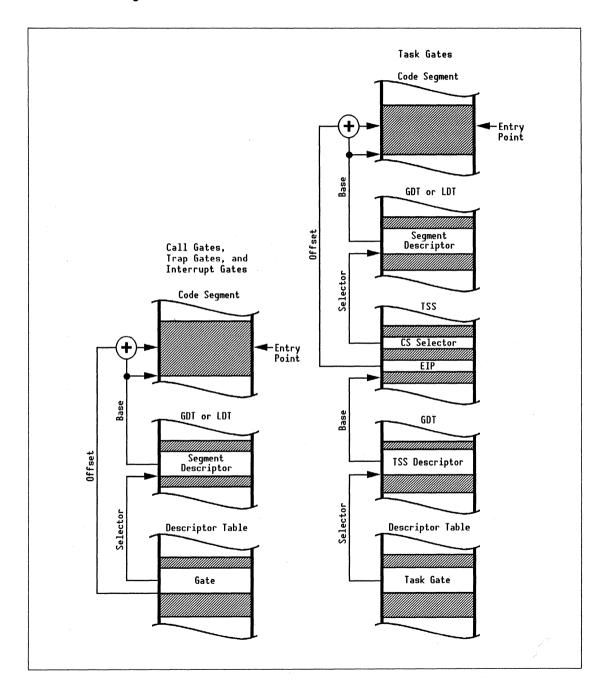

| Figure 4-19. | Control Gate Mechanism 4-39                                       |

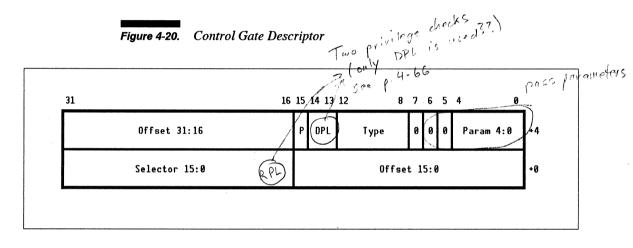

| Figure 4-20. | Control Gate Descriptor 4-41                                      |

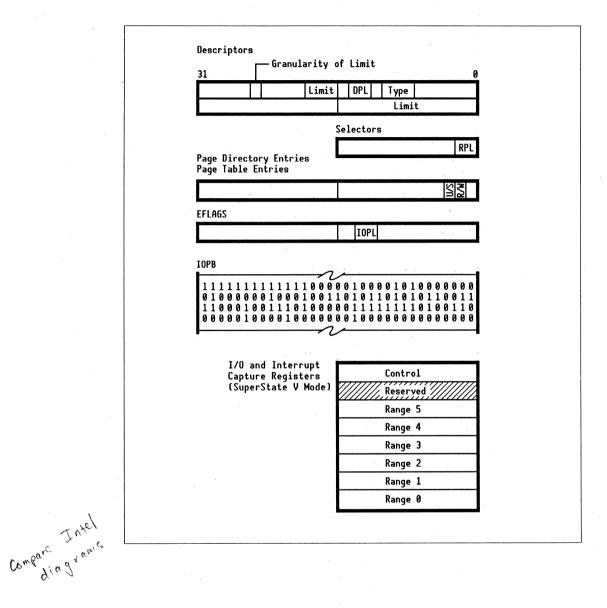

| Figure 4-21. | Data Structures Containing Privilege-Level Variables 4-44         |

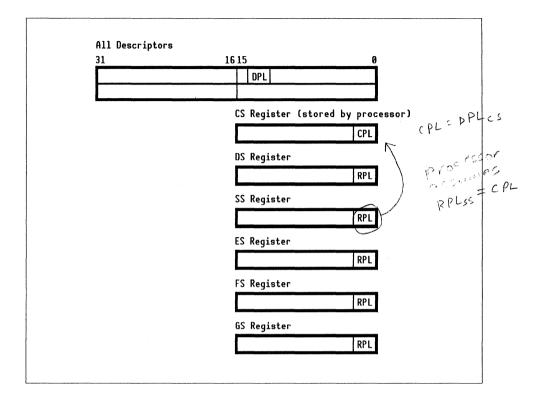

| Figure 4-22. | CPL, DPL, and RPL Fields 4-47                                     |

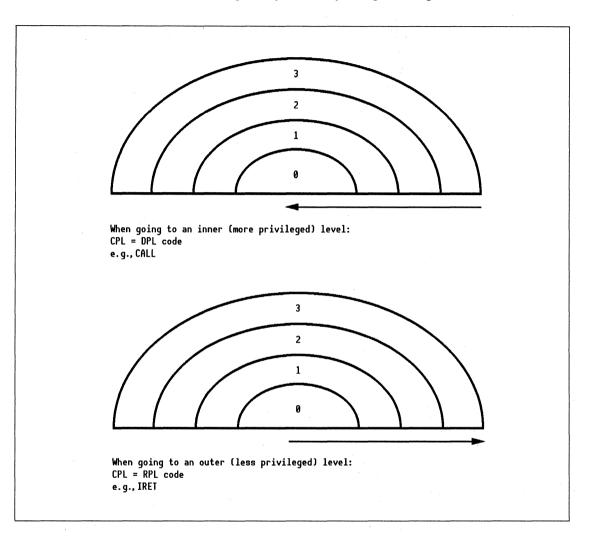

| Figure 4-23. | CPL Assignment for Nonconforming Code Segments 4-48               |

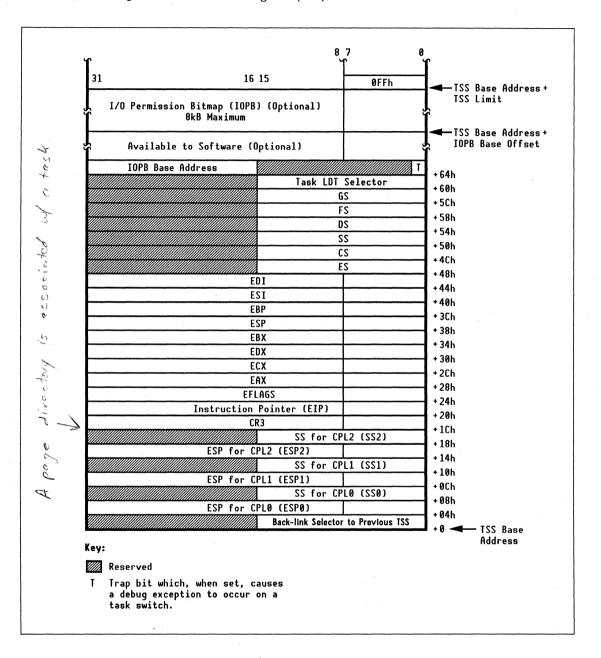

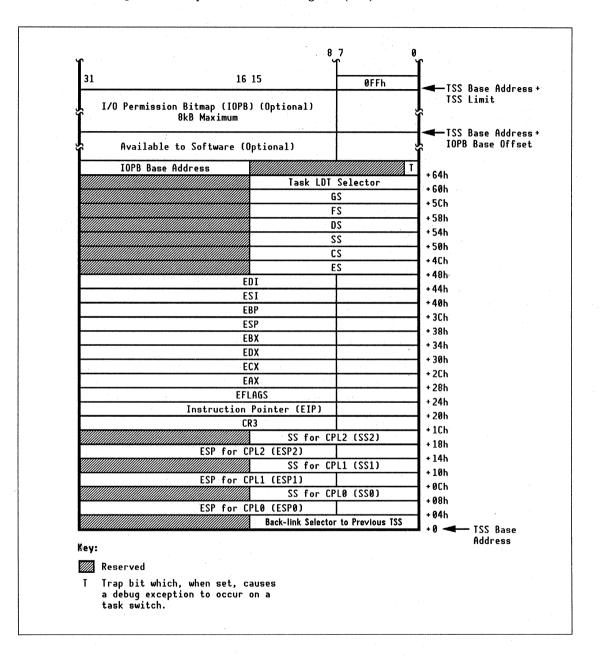

| Figure 4-24. | Task State Segment (TSS) Structure    4-56                        |

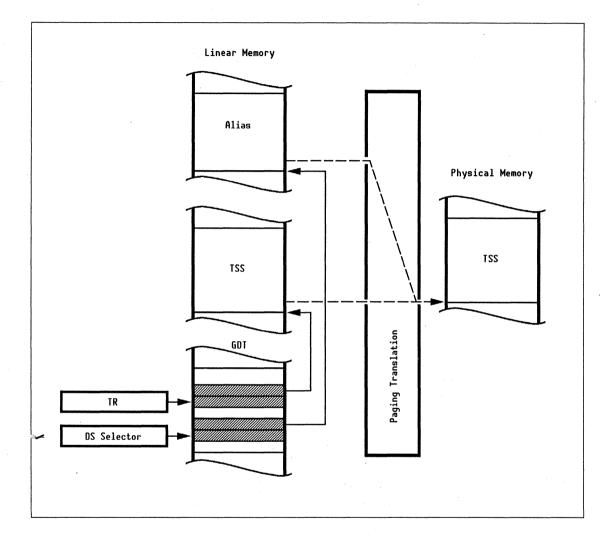

| Figure 4-25. | Accessing a TSS With a Segmentation Alias 4-59                    |

| Figure 4-26. | Accessing a TSS With a Paging Alias                               |

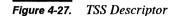

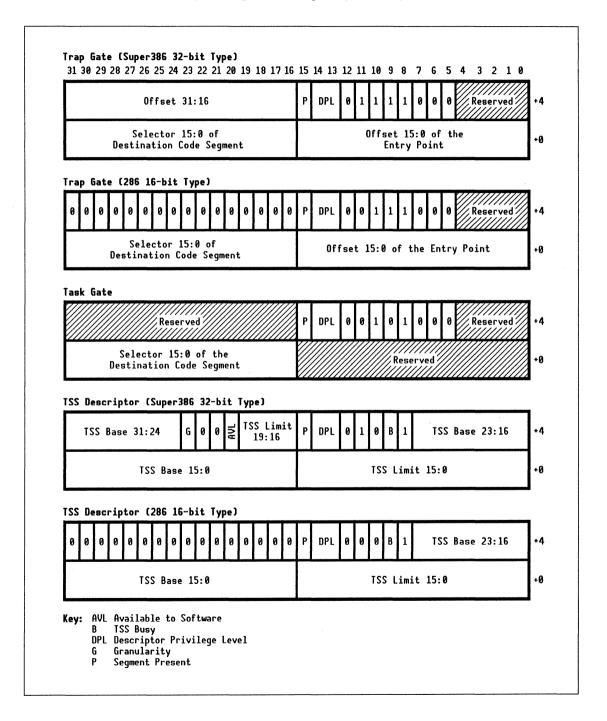

| Figure 4-27. | TSS Descriptor         4-61                                       |

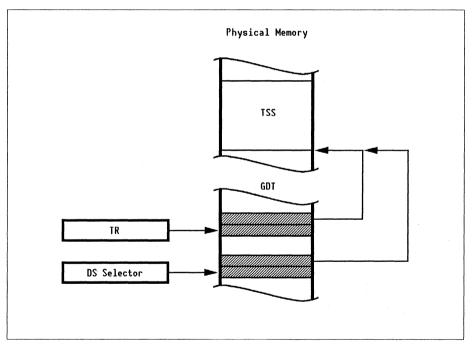

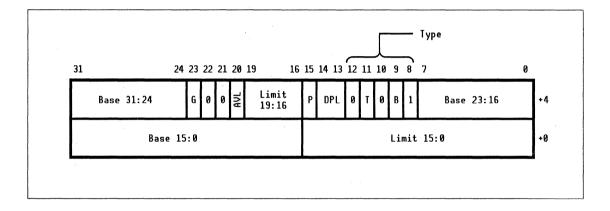

| Figure 4-28. | TSS Selection With the TR Register 4-64                           |

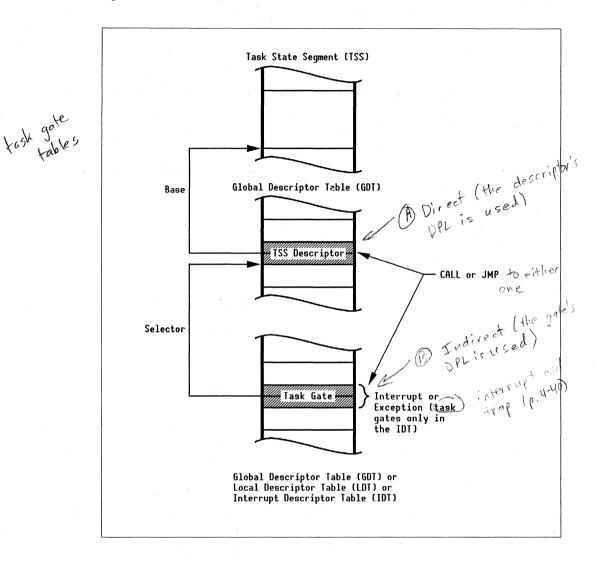

| Figure 4-29. | Task Gate Mechanism    4-66                                       |

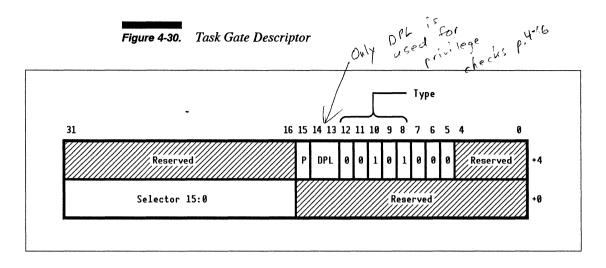

| Figure 4-30. | Task Gate Descriptor    4-67                                      |

| Figure 4-31. | Nested Tasks 4-71                                                 |

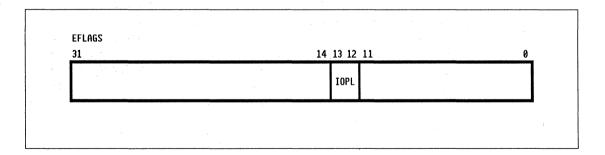

| Figure 4-32. | I/O Privilege Level (IOPL)                                        |

| Figure 4-33. | I/O Permission Bit Map (IOPB) 4-76                                |

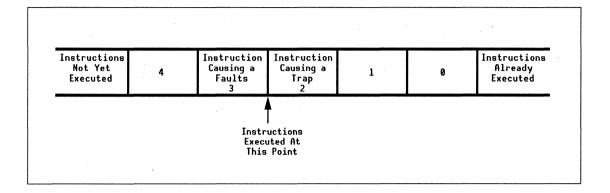

| Figure 4-34. | State of Instruction Pointer After Exceptions                     |

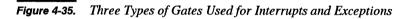

| Figure 4-35. | Three Types of Gates Used for Interrupts and Exceptions 4-81      |

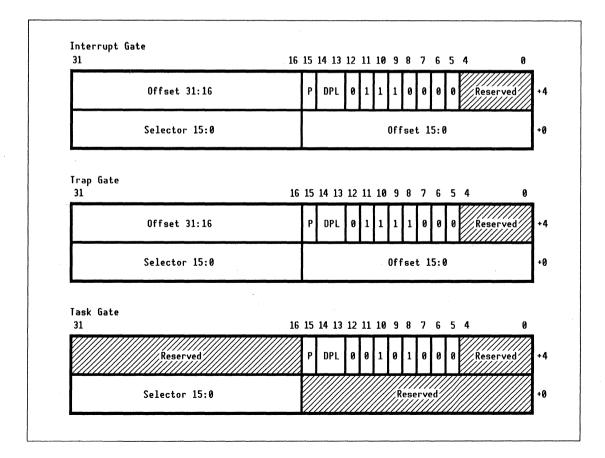

| Figure 4-36. | Vectoring for Interrupt Gates and Trap Gates                 |  |

|--------------|--------------------------------------------------------------|--|

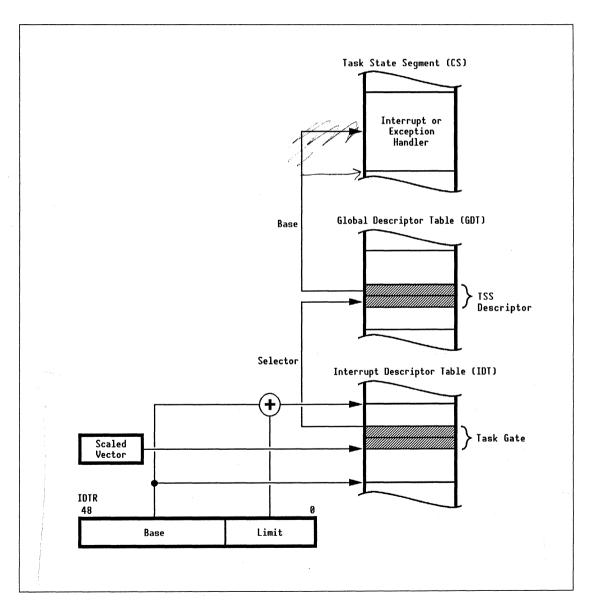

| Figure 4-37. | Vectoring for Task Gates 4-83                                |  |

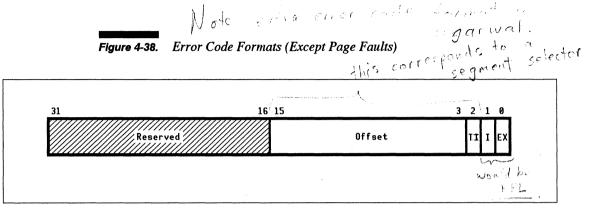

| Figure 4-38. | Error Code Formats (Except Page Faults)                      |  |

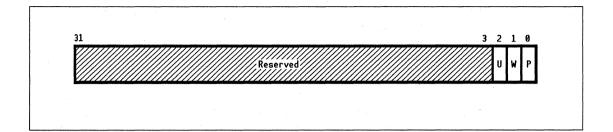

| Figure 4-39. | Error Code Format (Page Faults)                              |  |

| Figure 4-40. | Stack Frame for Interrupt or Exception Procedure             |  |

| Figure 4-41. | Typical Memory Use at Start of Execution                     |  |

| Figure 4-42. | Test Registers TR7 and TR6 4-112                             |  |

| Figure 4-43. | TR7 Register Settings for Writing a TLB Entry 4-113          |  |

| Figure 4-44. | TR6 Register Settings for Writing a TLB Entry 4-114          |  |

| Figure 4-45. | TR6 Settings for Searching and After Searching the TLB 4-116 |  |

| Figure 4-46. | TR7 Return Values After TLB Search 4-118                     |  |

| Figure 4-47. | Debug Register Set 4-120                                     |  |

| Figure 4-48. | Debug Control Register DR7 4-122                             |  |

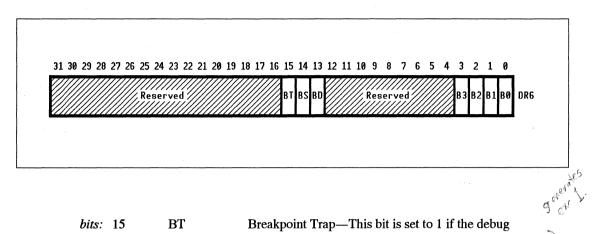

| Figure 4-49. | Debug Register DR6 4-124                                     |  |

| Figure 4-50. | Real-Mode Linear Address Generation                          |  |

|              |                                                              |  |

| Figure A-1.  | Instruction Example A-9                                      |  |

|              |                                                              |  |

| Figure B-1.  | System Register Overview                                     |  |

| Figure B-2.  | Selector Register and Shadow                                 |  |

| Figure B-3.  | Non-System Segment Descriptors                               |  |

| Figure B-4.  | System Segment Descriptors                                   |  |

| Figure B-5.  | Super386 Task State Segment (TSS) Structure                  |  |

| Figure B-6.  | 80286 Task State Segment (TSS) Structure                     |  |

| Figure B-7.  | Registers Used in 16-Bit Effective Address Generation B-19   |  |

| Figure B-8.  | Desisters Heading 20 Dit Effectives Address Commention D 10  |  |

| Figure B-9.  | Registers Used in 32-Bit Effective Address Generation B-19   |  |

| -            | MODr/m Byte Format                                           |  |

| Figure B-10. | -                                                            |  |

| Figure B-10. | MODr/m Byte Format                                           |  |

XV

#### List of Tables

| Table 3-1.  | The Parts of an Instruction                               |

|-------------|-----------------------------------------------------------|

| Table 3-2.  | Operand Types and Sizes 3-7                               |

| Table 3-3.  | Data Movement Instructions 3-16                           |

| Table 3-4.  | I/O Data Movement Instructions 3-17                       |

| Table 3-5.  | Arithmetic Instructions                                   |

| Table 3-6.  | Binary Instruction Flag Setting 3-19                      |

| Table 3-7.  | Logical Instructions 3-19                                 |

| Table 3-8.  | Shift and Rotate Instructions 3-20                        |

| Table 3-9.  | Bit Manipulation Instructions                             |

| Table 3-10. | String Instructions                                       |

| Table 3-11. | Control Transfer Instructions                             |

| Table 3-12. | Flag Instructions    3-23                                 |

| Table 3-13. | Load and Store Segment Instructions 3-24                  |

| Table 3-14. | Segment Selection Rules 3-24                              |

| Table 3-15. | Protection Control Instructions                           |

| Table 3-16. | Miscellaneous Instructions 3-26                           |

|             |                                                           |

| Table 4-1.  | Types of Segments 4-14                                    |

| Table 4-2.  | Relation of the D/B, E, C/ED, and R/W Fields 4-21         |

| Table 4-3.  | Descriptor Table Characteristics                          |

| Table 4-4.  | The Four Types of Gate Descriptors 4-40                   |

| Table 4-5.  | Privilege-Level Rules for Access or Control Transfer 4-52 |

| Table 4-6.  | Privileged Instructions 4-53                              |

| Table 4-7.  | Processor Changes During Task Switch 4-63                 |

| Table 4-8.  | Exception Conditions Verified During Task Switching 4-69  |

| Table 4-9.  | PC/AT Reserved I/O Addresses 4-73                         |

| Table 4-10. | Events With Error Codes 4-84                              |

| Table 4-11. | Super386 Interrupts and Exceptions 4-91                   |

| Table 4-12. | PC/AT Interrupt and Exception Vectors 4-94                |

| Table 4-13. | Interrupt and Exception Priority 4-96                     |

| Table 4-14. | State of Registers After Reset 4-100                      |

| Table 4-15. | Debug Register Functions 4-121                            |

| Table A-1.  | General Register Encoding A-4                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------|

| Table A-2.  | Segment Register Encoding A-4                                                                                            |

| Table A-3.  | Instruction Prefixes A-8                                                                                                 |

| Table A-4.  | Far CALL Clocks                                                                                                          |

| Table A-5.  | Task CALL Clocks    A-28                                                                                                 |

| Table A-6.  | DIV Element Storage Locations A-43                                                                                       |

| Table A-7.  | IDIV Element Storage Locations                                                                                           |

| Table A-8.  | IN Privilege Level Checks                                                                                                |

| Table A-9.  | INT <i>n</i> Clock Counts in Task-Switched Protected Mode and<br>in Task-Switched Virtual-8086 Mode When CPL > IOPL A-53 |

| Table A-10. | INT 3 Clock Counts in Task-Switched Protected Mode A-55                                                                  |

| Table A-11. | INTO Clock Counts in Task-Switched Protected Mode A-56                                                                   |

| Table A-12. | IRET and IRETD Clock Counts in Task-Switched<br>Protected Mode and in Task-Switched Virtual-8086 Mode<br>When CPL > IOPL |

| Table A-13. | Jcc Clock Counts A-60                                                                                                    |

| Table A-14. | Near JMP rel and rel8 Clock Counts A-62                                                                                  |

| Table A-15. | Task JMP Clock Counts    A-64                                                                                            |

| Table A-16. | LAR Access-Rights Bit Definitions A-66                                                                                   |

| Table A-17. | Loop Conditions A-79                                                                                                     |

| Table A-18. | OUT Privilege Level Checks A-97                                                                                          |

| Table A-19. | REP Prefixes A-108                                                                                                       |

| Table A-20. | RET Clock Counts A-110                                                                                                   |

| Table A-21. | OF Flag Values A-114                                                                                                     |

| Table A-22. | SCALL Vector Functions A-116                                                                                             |

| Table B-1.  | E-bit and B-bit EncodingB-7                                                                                              |

| Table B-2.  | Super386 Instruction Summary B-12                                                                                        |

| Table B-3.  | Super386 Instruction Summary—Flags Description                                                                           |

| Table B-4.  | Super386 Instruction Summary—Registers Description B-16                                                                  |

| Table B-5.  | Super386 Instruction Summary—Memory Description B-16                                                                     |

| Table B-6.  | Super386 Instruction Summary—Exceptions Description B-17                                                                 |

| Table B-7.  | Super386 Instruction Summary—Other Description                                                                           |

| Table B-8.  | Super386 16-Bit Address MODr/m Encodings B-21 |

|-------------|-----------------------------------------------|

| Table B-9.  | Super386 32-Bit Address MODr/m Encodings B-22 |

| Table B-10. | Super386 32-Bit Address SIB Encodings B-23    |

| Table B-11. | Super386 Opcode Map B-24                      |

| Table B-12. | Super386 Opcode Map With 0Fh Prefix B-26      |

| Table B-13. | Super386 Opcode Map for Group Instructions    |

|             |                                               |

| Table C-1. | <b>Operand Accessing Rules</b> | · · · · · · · · · · · · · · · · · · · | 2-15 |

|------------|--------------------------------|---------------------------------------|------|

|            |                                |                                       |      |

### CHAPTER 1

# Introduction

The Super386 DX/DXE processors provide higher performance than the comparable standard 80386 processors, with which they are code-compatible. Like the 80386 processors, the Super386 processors support multitasking operating systems and are designed for use in computation-intensive applications. They operate faster than standard 80386 processors due to their entirely redesigned internal architecture and unique microcode.

There are currently four Super386 DX/DXE processors:

- 38600DX

- 38600DXE

- 38605DX

- 38605DXE.

These processors are discussed below.

The 38600DX processor is a high-performance, static CMOS implementation of the 80386 DX processor's 32-bit architecture, with hardware support for jump instructions. It is pin-compatible with the 80386 DX processor and is a superset of its functionality.

Processor 38600DXE is identical to the 38600DX but it incorporates the SuperState V feature, a system for power management. This feature works in all modes and makes the 38600DXE processor suitable for low-power applications.

The 38605DX processor has all the features of the 38600DX processor but adds a 512-byte instruction cache. The 144-pin package is a superset of the 38600DX pinout. Systems designed for the 38605DX footprint can also use the 38600DX processor in the same socket.

The 38605DXE features both the 512-byte instruction cache and SuperState V mode for special applications. Two special pins are added to facilitate operation in SuperState V mode: ANMI\*, an alternate non-maskable interrupt input, and AADS\*, an alternate address space output. See the section entitled "SuperState V Mode" in Chapter 4 for a description of these signals.

In general, the terms *Super386 processor* and *processor* apply to both the 38600DX/DXE and the 38605DX/DXE processors. When only one of these processors is referred to, or when the 80386 processor is referred to, the processor is named explicitly.

### Features of All Super386 Processors

Features common to all processors in the Super386 family are:

- 80386 compatibility

- Memory management

- High-performance pipeline

- Advanced CPU clock design

- Static design

- Coprocessor support.

These features are discussed in the following paragraphs.

80386 Compatibility—The Super386 processors are object-code compatible with the standard 80386 processor and support all operating modes supported by the 80386 processor.

Memory Management—The memory management features include segmentation and paging. Segmentation allows programmers to create independent, protected address spaces. Paging makes it possible to use virtual data structures that are larger than the available memory space, by keeping the data partly in memory and partly in a mass-storage device.

High-performance Pipeline—The new pipeline design permits overlapping of instruction execution at CPU clock rates up to 40MHz.

Advanced CPU Clock Design—Systems designers can use a 1x or 2x CPU clock running from 0 to 25, 33, or 40MHz.

Static Design—All on-chip registers, buffers, and instruction cache (38605 only) are fully static, allowing the CPU clock to be stopped without losing data.

Coprocessor Support—For floating-point operations, the Super386 processors support the SuperMath<sup>™</sup> coprocessor and standard 80387 coprocessors.

## **Special Features**

Certain new features distinguish the 38605 processor from its predecessors: The 38605 processor prefetches instructions and stores them in a 512-byte instruction cache located on the chip. The processor goes to the cache for the next instruction and only fetches instructions from memory when the next instruction is not in the cache.

Near jump instructions are handled by dedicated hardware, as in the 38600 processor. But in combination with the instruction cache, this jump hardware improves near jump execution speed dramatically: two cycles with the jump hardware and cache versus six cycles without.

The 38600DXE and 38605DXE processors both feature SuperState V Mode. This special mode of operation is designed for power management and device emulation. It is transparent to the normal operating environment, permitting a control program, running at a more priviledged level, that allows the operating system to access the processor for special power management and feature control purposes.

## Programmer's Model

The Super386 architecture offers software developers a variety of registers, data structures, and other resources. This chapter describes the organization of memory, mechanisms by which system-level resources are protected from use by application software, and the different modes of instruction execution. It also defines the data types supported by the instruction set, describes the processor registers available to application programs, and introduces the basic types of interrupts and exceptions. The concepts covered in this chapter are referred to throughout this manual. For system programmers, the discussion continues in Chapter 4, "System Programming.

## **Memory Organization**

The processor can directly access up to 4GB of *physical address space*, each byte of which is separately addressable using a 32-bit *physical address*. During each memory access (or for the 38605 processor, each non-cached memory access), a physical address appears on the processor bus. External logic decodes the physical address into control signals for external memory or peripheral devices.

Software does not supply physical addresses directly to the processor. Every instruction that accesses memory supplies instead a *logical* (or *virtual*) *address*, which is translated into a physical address by the processor's memory-management unit.

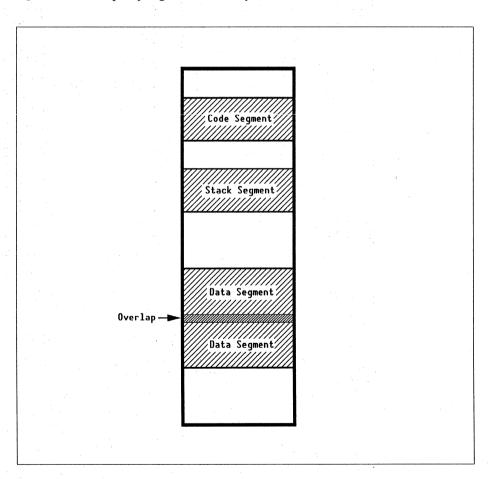

In the processor's native, fully featured 32-bit mode—called *protected mode* the address-translation mechanism makes use of translation tables created and maintained by the operating system. Thus, while the physical address space is a simple one-dimensional sequence of bytes, the *logical* organization of the external memory space—the way memory appears to software—can take on more complex forms determined by the operating system. In particular, the processor supports *segmented memory*, in which a linear onedimensional memory space is broken up by the operating system into independent linear, unbroken regions called *segments*. In protected mode, each program can have up to 16,384 segments, possibly overlapping, with sizes up to 4GB. Segments can be explicitly assigned to hold code, program stacks, or data. Segmentation can preserve the integrity of program code and data during unanticipated software accesses, such as erroneous or unauthorized access to one program's data or stack by another program. Figure 2-1 illustrates one way in which memory could be organized into segments.

#### Figure 2-1. Example of Segmented Memory

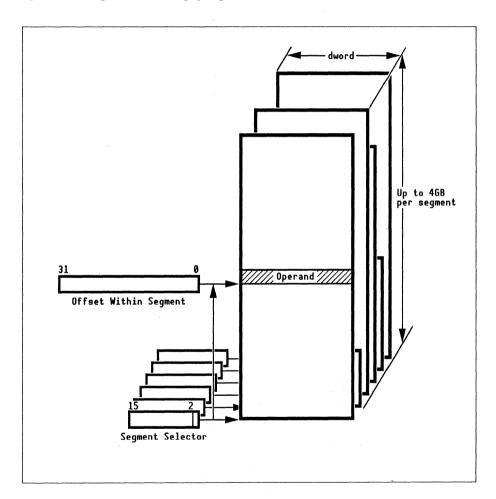

Figure 2-2 shows how a logical address is used to locate an operand in a segmented memory space. One part of the logical address identifies a segment; the other part specifies an offset into that segment. In protected mode, the *segment selector* provides an index into a descriptor table. Data in the descriptor table locates the *base address* of the segment. The *offset* then locates the addressed byte within the segment.

#### Figure 2-2. Logical Addressing of Segments

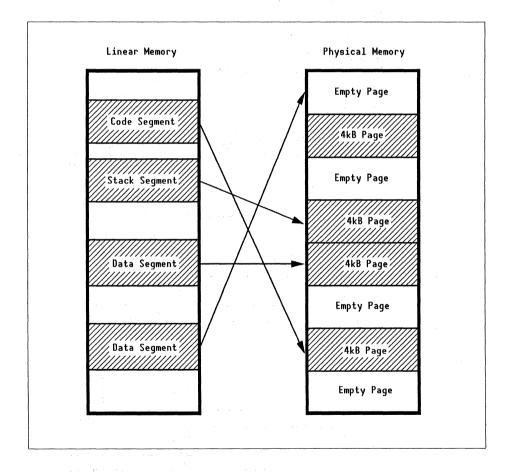

*Paging*, which is illustrated in Figure 2-3, is another aspect of memory management. Paging maps linear addresses generated by segmentation into physical addresses in memory. It is a technique for simulating a large external memory by swapping data between RAM and a mass-storage device such as a disk. Data is swapped in units of 4kB called *pages*. The operating system keeps track of which pages are in RAM at any given time and which are on a disk. A request for data currently held on disk causes an exception. The service routine for the exception loads the page with the requested data into RAM, swapping some other page out to disk if necessary.

PRELIMINARY

## **Address Translation**

Address translation is part of the processor's segmentation and paging mechanisms. It has two stages, as illustrated in Figure 2-4.

Segmentation—In the segmentation stage, the processor's segmentation unit translates the logical address supplied by software into a linear address, which specifies the location of a byte in a one-dimensional linear address space.

Paging—If paging is enabled, the linear address undergoes further translation. This stage of address translation is carried out with information contained in page directories and page tables. These data structures reside in memory and are maintained by the operating system. If paging is disabled, or is unavailable in the processor's current execution mode, the linear address is used as the physical address.

### Addressing Segmented Memory

While paging is transparent to application programs (except for occasional delays when data needs to be swapped), segmentation is an everyday fact of life for even the most casual assembly-language programmer. Every instruction that accesses memory must indicate a segment for the intended access as well as an offset into that segment.

At any given time, up to six segment selectors reside on-chip in the processor's six *segment registers*. A memory reference in an assembly language instruction must specify—either explicitly or by default—one of these registers. In protected mode, the high-order 13 bits in a segment register specify an offset into a segment descriptor table, which in turn locates the segment. Segment descriptors are described further in the next section.

Memory references also have an offset into the selected segment. This offset, or *effective address*, can be specified in various ways known as the *addressing modes* of the processor. Basically, up to three components can be added together to form the offset: the contents of a specified base register, the scaled contents (multiplied by 1, 2, 4, or 8) of a specified *index register*, and a constant value called a *displacement*. The various addressing modes support complex data structures typically used in high-level languages.

The ways in which instructions address memory operands are discussed in detail in Chapter 3, "Instruction Set Overview."

#### **Descriptor Tables and Memory Models**

In protected mode, the offset into a segment descriptor table that the segment selector provides locates an 8-byte *segment descriptor* associated with the selector. The segment descriptor contains information about the corresponding segment, including its base address (in the linear address space) and its size. This information is used in logical-to-linear address translations. Segment descriptors, along with descriptors of other kinds, are maintained by the operating system in data structures called *descriptor tables*. By controlling the contents of the descriptor tables, therefore, the operating system controls the logical organization of memory.

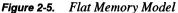

The simplest memory organization is the *flat model*, in which all segment descriptors point to the same base address and specify the same segment size. Figure 2-5 illustrates a flat memory organization.

While there is no way to disable the processor's segmentation mechanism, using the flat model achieves the same result: memory is accessed as a single range of linear addresses. The size of this range can be up to the 4GB maximum or restricted to the actual size of the external memory. The latter approach has the advantage that out-of-range addresses will be trapped by the segmentation unit. See the section entitled "Protection."

Segmented memory models, on the other hand, can be quite complex. Each application can be given its own descriptor table, defining up to 16,384 distinct segments. Each of these segments can be of any size up to the 4GB maximum. Some segments can be reserved for a given application, while others are shared. The operating system can map segments to overlapping ranges in the linear address space.

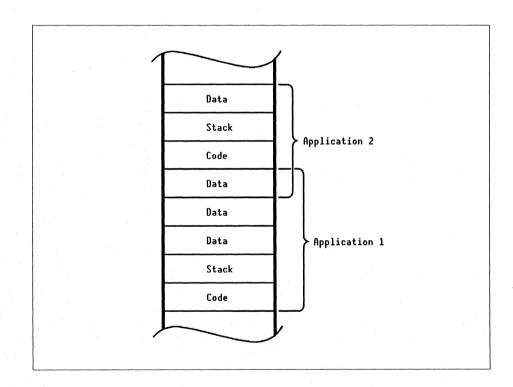

Figure 2-6 illustrates a moderately complex segmentation strategy in which each of two applications has multiple data segments. The two applications also share a data segment.

#### Figure 2-6. Segmentation Strategy: Example 1

Figure 2-7 illustrates a simpler segmentation strategy, in which each application has a single segment to hold its stack and data. This arrangement has the advantage that 32-bit pointers can be used to access data (instead of 48-bit pointers). On the other hand, the stack is not prevented from growing down into the region where the program stores data. See the sections entitled "Resource Protection" and "Stack Operations" for futher information.

#### Figure 2-7. Segmentation Strategy: Example 2

## **Storing Data in Memory**

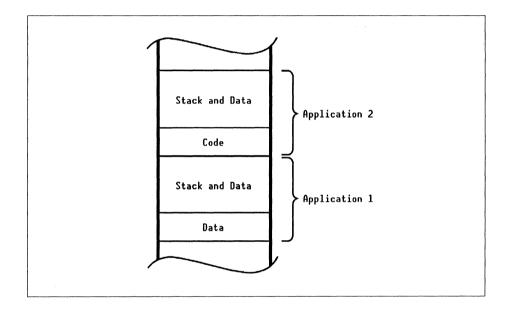

Data items held in memory or in processor registers can be of several different lengths. A *byte* is an ordered sequence of 8 bits; it is the smallest addressable quantity. A *word* is a sequence of 16 bits. A *doubleword* (or *dword*) is a sequence of 32 bits. See Figure 2-8.

The processor uses *little-endian* encoding, in which a multi-byte quantity is stored with its least-significant byte at the lowest byte address. In the illustration, words and doublewords are shown with the least significant byte at the right. Byte addresses increase from right to left. As a consequence, numerical data reads normally, with the most significant hexadecimal digits appearing at the left. Strings, however, read in reverse order.

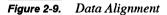

Multi-byte quantities in memory are always addressed using the byte address of the least-significant byte. A memory word is said to be aligned when this address is an even number. A dword is aligned when the address of its least-significant byte is divisible by 4. In general, any  $2^{n}$ -byte quantity is aligned if its address is a multiple of its size in bytes. See Figure 2-9.

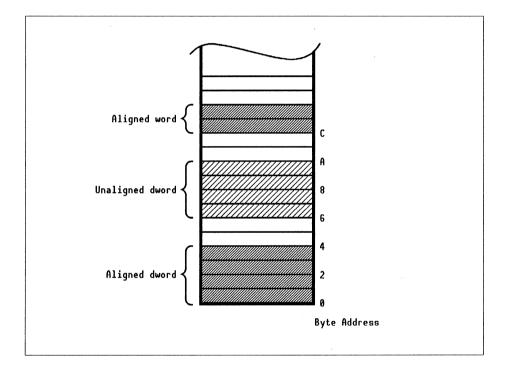

Physically, each external memory access transfers between one and four bytes of an aligned dword between the processor and memory. To access a multi-byte quantity that crosses a dword boundary, the processor performs multiple transfers. For example, to transfer an unaligned dword requires two transfers, as illustrated in Figure 2-10. While such accesses are handled automatically by hardware, they do require extra bus cycles with a consequent penalty in performance.

Figure 2-10. Unaligned Accesses

## **Stack Operations**

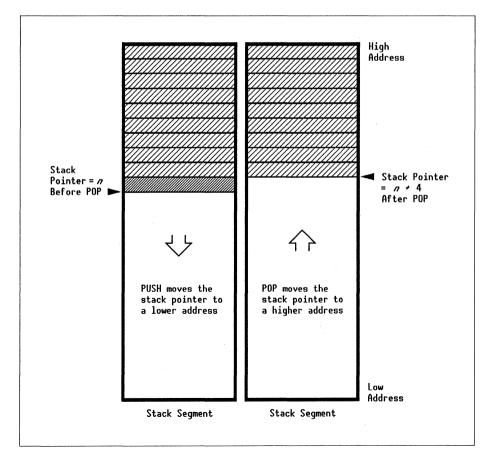

Several instructions directly manipulate the *program stack* (or simply *stack*). Stacks implement a last-in first-out (LIFO) data structure. They are typically used in situations that require nested storage such as subroutine calls and the evaluation of complex expressions. Each stack can be contained in a separate memory segment. One stack—the *current stack*—is directly addressable at any given time. Its segment selector is the value in the Stack Segment (SS) register. The location of the current *top of stack* (the last operand written to the stack) is the value in the Stack Pointer (ESP) register. The ESP register specifies an offset into the current stack segment. Data can be appended to the current stack using a PUSH instruction, or removed from the stack using a POP instruction. When data is appended, the stack grows toward lower memory addresses in the linear address space, as shown in Figure 2-11 for 32-bit addresses.

#### Figure 2-11. Stack Organization, 32-Bit Operation

A procedure call automatically pushes its return address onto the stack. Upon return from the procedure, the address is popped. The last-in-first-out allocation rule makes it easy and efficient to handle nested subroutines, even when these are recursive or re-entrant. A series of CALL instructions will leave a sequence of addresses on the stack. The first RET instruction thus finds the return address of the most recent CALL at the top of the stack. The stack can also be used to pass parameters to a subroutine, or to store a subroutine's local variables.

The registers used to implement stack operations are discussed in more detail in the section entitled "Registers." Details of the PUSH and POP instructions are discussed in Appendix A, "Instruction Set Reference."

#### Input/Output

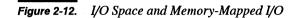

Depending on system implementation, I/O peripheral devices can be accessed in one of two address spaces: I/O space and memory-mapped I/O.

I/O Space—In this arrangement, the control, status, and data ports for peripheral devices are located in an addressable space that is separate from the memory space. Special I/O instructions are used to transfer data between these ports and the processor registers or memory.

Memory-Mapped I/O—In memory-mapped I/O, the control, status, and data ports for peripheral devices share the normal memory space with all other memory segments. Accesses to these I/O addresses work in the same way as normal memory accesses.

Figure 2-12 shows these two alternative arrangements.

## I/O Space

The I/O space is a 64kB linear address space beginning at I/O address 0. Ports can be 1, 2, or 4 bytes wide. Architecturally and physically, I/O space is separate from memory space. Separation of memory and I/O space offers the most reliable system protection: the I/O space has its own protection mechanisms, separate from those applied to the memory space. For example, the system design can prevent reads and writes to I/O space from being captured by a cache. When a separate I/O space is used, however, it can only be accessed by the I/O instructions IN, INS, OUT, and OUTS.

# Memory-Mapped I/O

The chief advantage of memory-mapped I/O is that the general-purpose arithmetic and logical instructions, which operate on memory-space operands, can also be used for I/O. For example, memory-mapped I/O allows application software to set bits in a peripheral register without passing the contents of the peripheral register through a processor register.

#### **Resource Protection**

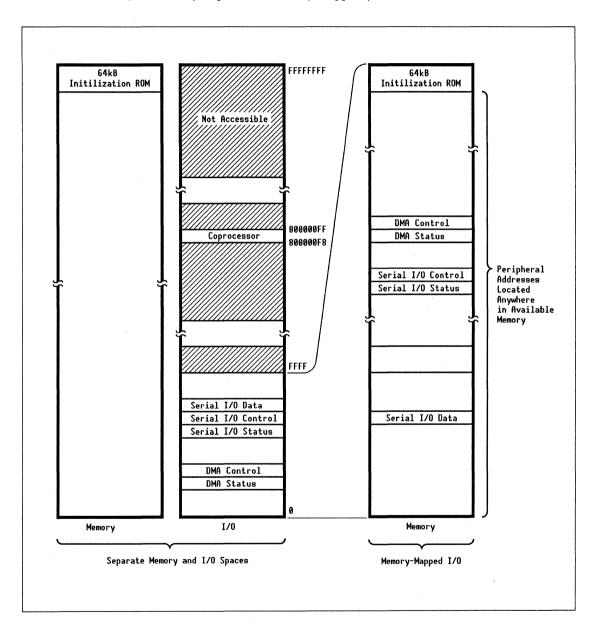

Every memory segment has an associated privilege level represented as a number between 0 (most privileged) and 3 (least privileged). The privilege level of the code segment from which instructions are currently being fetched is called the *current privilege level* (CPL). In general, protected resources can be used only by sufficiently privileged code.

In a typical arrangement, the operating system kernel runs at level 0 and the rest of the operating system runs at level 1. Applications run at level 3, and level 2 is left free for special-purpose code requiring an intermediate degree of privilege. Figure 2-13 illustrates this arrangement.

#### Figure 2-13. Privilege Levels

The operating system can implement protections for three types of resources:

- Privileged instructions

- Memory

- I/O.

These resources are discussed in the following paragraphs.

Privileged Instructions—Privileged instructions are machine instructions that can be used only by code at privilege level 0. Examples are instructions that explicitly modify system control registers.

Memory—The tables used in address translation (descriptor tables, page directories, and page tables) contain bits that restrict access to individual segments and pages. Attempted memory accesses by insufficiently privileged code are trapped.

I/O—The use of I/O instructions and ports can be restricted by the operating system to code of a given privilege level (or better). Global protection is applied through the two-bit I/O privilege level (IOPL) flag in the EFLAGS register. The IOPL specifies the minimum privilege level required to execute I/O instructions. Portlevel protection is provided by an operating system data structure called the I/O permission bitmap (IOPB), which controls access to individual I/O ports based on privilege level.

Access rules for the various protected resources are discussed in detail in Chapter 4, "System Programming."

# **Execution Modes**

The processor has three mutually exclusive modes of instruction execution that are selectable by system software:

- Protected mode

- Real mode

- Virtual-8086 mode.

These modes provide full 32-bit processing, protection, and virtual-memory features for newly written code while ensuring compatibility with code written for 16-bit processors. The modes also provide support for mixing 16-bit and 32-bit code.

Protected Mode—In protected mode, all of the processor's segmentation, paging, protection, and multitasking capabilities are available. Programs written for protected mode on the 80386 and 80286 processors can be run in protected mode on a Super386 processor. Maximum linear memory size is 4GB, and default operand size can be 16 or 32 bits.

Real Mode—Real mode is the 8086 real-address emulation mode. Maximum memory size (1MB), default operand size (16-bit), address generation, and interrupt handling are nearly identical to the 80286 real mode. Instruction prefixes allow use of 32-bit operands, giving full use of the 32-bit registers. All code runs at privilege level 0. Protected segmentation and paging are not available.

Virtual-8086 Mode—In virtual 8086 mode the processor generates 8086 real-mode addresses, but with the virtual-memory paging capabilities of protected mode. Like real mode, virtual-8086 mode has a maximum memory size of 1MB. Programs run as tasks. The processor can safely enter this mode from protected mode, run an 8086 program, and return to protected mode. All code runs at privilege level 3. Protected segmentation is not available.

The descriptions in this manual assume protected-mode operation. The section entitled "Other Processor Modes" in Chapter 4 focuses specifically on the real mode and virtual-8086 mode. Most application instructions work the same way in all three modes. The operational differences between the various modes are discussed briefly below and in detail in Chapter 4, "System Programming." Segmentation works differently, depending on the mode. In protected mode, the segment selector is used as a pointer into a segment descriptor table. The descriptors in the table specify the base and limit of the segment in linear address space, and they enforce segment access restrictions based on privilege level. In real mode and virtual-8086 mode, the segment selector is multiplied by 16 to form the base address of the segment; each segment is therefore 64kB in size. There is no segment-level protection.

Page translation, with full page-level protection, is available in protected mode and virtual-8086 mode. Paging is not available in real mode.

The use of instructions that access I/O devices, like IN and OUT, can be restricted in protected mode and virtual-8086 mode to code of a certain privilege level (the IOPL). In virtual-8086 mode, instructions that reference the interrupt flag (IF) are also sensitive to the IOPL.

Handling or service routines for interrupts and exceptions are located using a vector into a data structure in memory. This table has two formats, one for real mode and the other for protected and virtual-8086 mode. In real mode, the table is called an *interrupt vector table*. In protected mode and virtual-8086 mode, the table is called an *interrupt descriptor table*.

# **Data Types**

The supported data types include unsigned and signed integers, binary-coded decimal numbers, strings (including bit strings), and pointers. These types are described later. Floating-point data types are supported by numerical coprocessors that the Super386 processor in turn supports—such as the SuperMath and standard 80387 coprocessors—and by software packages that emulate coprocessors. For details on these floating-point data types, refer to the documentation for the coprocessors or emulation software.

#### Integers

The processor supports the representation of integers in unsigned and signed formats of various widths.

#### **Unsigned Integers**

An unsigned integer represents a non-negative value in binary (radix-2) form. Unsigned numbers can be a byte, word, or dword in length, as shown in Figure 2-14. An unsigned byte can represent integers between 0 and 255 (inclusive). For unsigned words, the range is from 0 to 65,535; for unsigned dwords, from 0 to  $2^{32}$ -1.

The various instructions that add or subtract integers work equally well with unsigned and signed integers. Special instructions supporting unsigned numbers are available for multiplication and division.

#### Signed Integers

A signed number represents an integer in *two's-complement* format, as shown in Figure 2-15. In this format, the most-significant bit indicates the sign: 0 for positive, 1 for negative. The remaining bits indicate the magnitude. For positive numbers, these bits directly represent the magnitude in binary (radix-2) form. For negative numbers, every bit of the absolute value in binary form is inverted (one's complement), and 1 is added to the result.

#### Figure 2-15. Two's-Complement Integers

Signed numbers can be a byte, a word, or a dword in length. An *n*-bit signed number can represent integers between  $-2^{n-1}$  and  $+2^{n-1}$ . The signed number types are illustrated in Figure 2-16.

The various instructions that add or subtract integers work equally well with unsigned and signed integers. Special instructions supporting signed numbers are available for multiplication and division.

*Quadword* numbers (8 bytes long) also occur. They are generated by the 32-bit multiply instructions. The low-order dword is normally stored in register EAX and the high-order dword is stored in register EDX. Similarly, in a 32-bit divide instruction, the dividend is a quadword taken from the EAX and EDX registers.

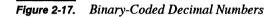

# **Binary-Coded Decimal (BCD) Numbers**

In a BCD number, each digit of a decimal numeral is represented in binary form (from 0 = 0000b to 9 = 1001b). In the *unpacked* BCD representation, each digit is stored in a separate byte. Alternatively, two digits can occupy a single byte in *packed* BCD format, where the digit represented by bits 7:4 is more significant than the digit in bits 3:0. Figure 2-17 illustrates both varieties.

Special BCD arithmetic instructions act directly on one-byte BCD numbers. Multi-byte BCD numbers must be handled as strings (see "Strings" on page 2-24). BCD strings do not have a set length and can therefore be used to represent numbers of arbitrary precision.

### Strings

A string is a sequence of bits, bytes, words, or doublewords that occupies a single contiguous block of memory. The processor operates on a string by applying a specified string instruction to each successive element. There are instructions for moving strings around in memory, filling a string with repetitions of a fixed value, transferring strings between memory and I/O ports, and searching strings for specific values. The string instructions are discussed in Chapter 3, "Instruction Set Overview." Bit strings can contain up to 2<sup>32</sup>-1 bits. Other types of strings can be up to 4GB in size.

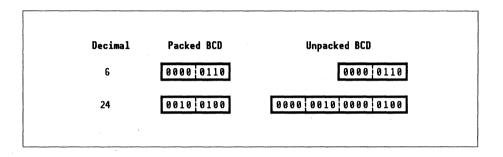

#### ASCII

The American Standard Code for Information Interchange (ASCII) represents alphanumeric and control characters in a 7-bit binary code. Sequences of ASCIIencoded characters are among the most commonly used strings. Each byte of an ASCII string contains a character in bits 6:0. Bit 7 is cleared to 0. The processor can perform arithmetic operations on one-byte ASCII code numbers. Figure 2-18 shows an ASCII string.

Figure 2-18. ASCII String

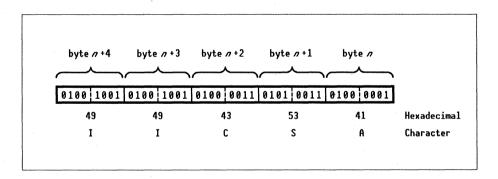

#### **Bit Strings**

Bit operations support data that does not break down conveniently into bytes, such as a display bitmap or a single-bit datum like a semaphore. In the former case, it would be inconvenient to have to manipulate the data in byte-sized pieces. In the latter case, it would waste memory to use an entire byte in order to store a single bit.

Bit strings are indexed by a dword, and can therefore be up to  $2^{32}$  bits in length. The index is a signed integer called the *bit offset*. It specifies the location of a specific bit within the string. Figure 2-19 gives an example of bit addressing.

#### **Pointers**

A pointer contains the address of a data item. Pointers can be used to build and access complex data structures that can change in size and structure during execution. Each element in a linked list, for example, contains a pointer to another element. Elements can be linked and unlinked by writing new values to the pointers.

There are two types of pointers, a *far pointer* containing a segment selector as well as an offset, and a *near pointer* containing just an offset. See Figure 2-20.

Figure 2-20. Near and Far Pointers

Far Pointer—A far pointer contains a two-part address which is required for accessing an element located in a different segment of memory. The offset part is stored in the low-order 32 bits (16 bits in real and virtual-8086 modes), and the segment selector is in the high-order 16 bits.

Near Pointer—A near pointer contains only an offset. Near pointers can only be used when all pointer references lie in one segment.

Instructions exist for loading pointers from memory. The segment selector (for far pointers) is loaded into a segment register. The offset is loaded into a general register, to be used as the base in an address calculation.

# **Application Registers**

The 16 registers available to application programs are shown in Figure 2-21. Application registers are of three kinds:

- General registers

- Status and control registers

- Segment registers.

The registers are discussed briefly in the following paragraphs. Full details are given in Appendix A, "Instruction Set Reference."

General Registers—The eight 32-bit general registers, also called *general purpose registers*, are EAX, EBX, ECX, EDX, ESI, EDI, EBP, and ESP. They are used for a variety of programming operations, such as holding intermediate results in computations, holding base and index values for address computations, and holding parameters and local variables during subroutine calls. Some instructions use one or more of the general registers in a special way.

Status and Control Registers—Status and control registers, EFLAGS and EIP, are 32-bit *flag* registers. EFLAGS contains bits that either modify the effect of instruction execution, reflect the outcome of instruction execution, or configure certain system-level resources. The 32-bit *instruction pointer* (EIP) register acts as the program counter.

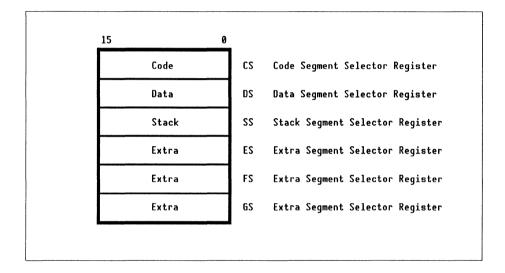

Segment Registers—The six 16-bit segment registers (CS, DS, SS, ES, FS, and GS) contain selectors that identify the currently addressable code segment (CS), data segment (DS), or stack segment (SS) of memory. The ES, FS, and GS are extra data-type segments.

The general registers plus the status and control registers are sometimes called the *base register set* in other literature. In addition to these application registers, the processor also has several other registers—usually not available to application programs—through which segmentation, paging, debugging, testing, and other system operations are controlled. The registers typically used by application programs are described below. Those typically used by system programs are described in Chapter 4, "System Programming."

Figure 2-21. Registers Available to Application Programs

|                                               | General Registers<br>31 16                                                 | 8-bit<br>Registers<br>15 8                           | 8-bit<br>Registers<br>7 0                          | 16-bit<br>Registers  | 32-bit<br>Registers |

|-----------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------|----------------------|---------------------|

| General Purpose                               |                                                                            | AH                                                   | AL                                                 | AX                   | EAX                 |

| General Purpose                               |                                                                            | вн                                                   | BL                                                 | BX                   | EBX                 |

| General Purpose                               |                                                                            | СН                                                   | CL                                                 | CX                   | ECX                 |

| General Purpose                               |                                                                            | DH                                                   | DL                                                 | DX                   | EDX                 |

| Source Index                                  |                                                                            | s S                                                  | I                                                  | SI                   | ESI                 |

| Destination Index                             |                                                                            | D                                                    | I                                                  | DI                   | EDI                 |

| Stack-Frame Base<br>Pointer                   |                                                                            | B                                                    | P                                                  | BP                   | EBP                 |

| Stack Pointer                                 |                                                                            | S                                                    | P                                                  | SP                   | ESP                 |

|                                               |                                                                            |                                                      |                                                    |                      |                     |

|                                               | Status and Cor<br>31 16                                                    | ntrol Regis<br>15                                    | ters<br>Ø                                          | * .                  |                     |

| Flags                                         | Status and Cor<br>31 16                                                    | 15                                                   | ters<br>Ø<br>ags                                   | FLAGS                | EFLAGS              |

| Flags<br>Instruction Pointer                  | Status and Cor<br>31 16                                                    | 15                                                   | 0<br>ags                                           | FLAGS<br>IP          | EFLAGS              |

| -                                             | Status and Cor<br>31 16                                                    | 15<br>Fla                                            | 0<br>ags                                           | ĸ                    |                     |

| Instruction Pointer                           | Status and Cor<br>31 16                                                    | 15<br>Fla<br>I<br>Segment                            | 0<br>ngs<br>P<br>Registers<br>Ø                    | ĸ                    |                     |

| Instruction Pointer<br>Co                     | 31 16                                                                      | 15<br>Fla<br>I<br>Segment<br>15                      | 0<br>ags<br>P<br>Registers<br>0<br>de              | IP                   |                     |

| Instruction Pointer<br>Co<br>Da               | 31 16                                                                      | 15<br>Fla<br>II<br>Segment<br>15<br>Coo<br>Da        | 0<br>ags<br>P<br>Registers<br>0<br>de              | IP<br>CS             |                     |

| Instruction Pointer<br>Co<br>Da<br>Sta        | 31 16                                                                      | 15<br>Fla<br>II<br>Segment<br>15<br>Coo<br>Da<br>Sta | 0<br>ags<br>P<br>Registers<br>0<br>de<br>ta        | IP<br>CS<br>DS       |                     |

| Instruction Pointer<br>Co<br>Da<br>Sta<br>Ext | 31 16<br>de Segment Selector<br>ta Segment Selector<br>ck Segment Selector | 15<br>Fla<br>II<br>Segment<br>15<br>Coo<br>Da<br>Sta | 0<br>ags<br>P<br>Registers<br>0<br>de<br>ta<br>ack | IP<br>CS<br>DS<br>SS |                     |

# **General Registers**

The eight general registers shown in Figure 2-21 support doubleword, word, and byte operands. The full 32-bit registers have names that begin with E (for *extended*). To handle 16-bit operands, the lower word of each general register is separately addressable. It has the same name as the full 32-bit register, minus the E. Four of the general registers (those whose names end in X) also support 8-bit operands. In these registers, each byte of the lower word is separately addressable. The high-order bytes are AH through DH. The low-order bytes are AL through DL.

Some instructions operate on bytes, others on words or dwords. Those that operate on words or dwords determine the operand size via a bit (the default size) in the segment descriptor for the code segment. An instruction prefix called the *operandsize override* allows switching between operand sizes. Byte and word operations that modify a general register affect only the specified portion of that register. The other bits remain unchanged. When a general register is pushed on or popped from the stack, the operand size matches the operand; flue remaining bits care

Most instructions can use any of the general registers as operands. Some instructions, however, implicitly use one or more of the general registers in a special way:

- String instructions

- Double-precision arithmetic

- Variable shifts

- Input/output instructions

- Stack manipulation.

These uses are discussed in the following paragraphs.

String Instructions—Strings are processed by applying a specified instruction to each string. The source index (ESI) register and destination index (EDI) register indicate the operation's source and destination strings. These registers are incremented or decremented as each successive element of the string is processed. The value in ECX is interpreted as the total length of the string.

Double Precision Arithmetic—EAX and EDX together hold the 64-bit product in a double-precision multiplication. They hold the 64-bit dividend in a double-precision division.

demont ina,

Variable Shifts—For some shift instructions, the CL register specifies the number of bits to be shifted.

Input/Output—I/O instructions use the EAX, AX, and AL registers as sources for output data and as destinations to receive input data. Block I/O transfers use the DX register to specify a port in I/O space, and they use the source and destination index registers ESI and EDI as string indexes.

Stack Manipulation—The stack pointer (ESP) and stack-frame base pointer (EBP) registers are used for stack manipulation. They contain offsets into the current stack segment. The ESP register contains the offset of the current top of stack. It is decremented when an item is added to the stack and incremented when an item is removed. The stack thus grows down toward lower memory addresses. Figure 2-11 illustrates the stack storage-allocation discipline.

The entire structure of the stack, including the stack pointer and its stack-frame base pointer, is called the *stack frame*. The base pointer in the EBP register is typically used as a fixed reference point for accessing the stack in situations where the stack pointer itself is changing. For example, suppose a data structure is passed on the stack to a subroutine that also uses the stack for temporary storage of local variables, as shown in Figure 2-22. In this situation, ESP-relative addresses for data in the fixed data structure would have to change as the amount of temporary storage allocated for local variables changed. By copying the initial ESP value into the EBP register before pushing anything onto the stack, the subroutine can instead use fixed, EBP-relative addresses to access the passed data structure.

The ENTER and LEAVE instructions automatically set up a stack frame for procedures and exit from them. The instruction descriptions in Appendix A, "Instruction Set Reference," give full details concerning these instructions and all of the implicit uses of general registers.

2-22. Use of the Stack-Frame Pointer

#### **Status and Control Registers**

The two status and control registers, illustrated in Figure 2-21, are of significance to application programmers. One points to the current or next instruction, and the other contains control and status flags.

#### Instruction Pointer (EIP) Register

The EIP register contains an offset into the current code segment, which is the segment pointed to by the value in the CS register. The EIP register is loaded automatically by an interrupt, an exception, or a control-transfer instruction such as JMP or RET. For 16-bit addressing, the lower word (IP) of the EIP register provides the offset. When used independently, this portion of the EIP register is called the IP register.

#### Status and Control Flags (EFLAGS)

The EFLAGS register, shown in Figure 2-23, has 13 non-reserved flag fields. There are three kinds of flags:

- Status flags

- Control flags

- System flags.

These flags are discussed in the following paragraphs.