ADVANCE INFORMATION

# EXPONENTIAL X<sup>704m</sup> RISC MICROPROCESSOR

AN IMPLEMENTATION OF THE POWERPC<sup>TM</sup> ARCHITECTURE

TECHNICAL SUMM<sub>P</sub>ARY

exponential

NIC

Δ

# EXPONENTIAL X<sup>704™</sup> RISC MICROPROCESSOR

AN IMPLEMENTATION OF THE POWERPC<sup>™</sup> ARCHITECTURE

#### © Exponential Technology 1996

All rights reserved. No part of the contents of this document may be reproduced or transmitted in any form without the express written permission of Exponential Technology, Inc.

This document contains information on a product which has not been commercially released, and may contain technical inaccuracies or typographical errors. Information in this document is subject to change without notice. Exponential makes no express or implied warranty of any kind and assumes no liability or responsibility for any errors or omissions in this document.

PowerPC, PowerPC Architecture, POWER and POWER Architecture are trademarks of International Business Machines Corporation. Exponential and the Exponential logo are trademarks of Exponential Technology, Inc. All other trademarks and registered trademarks are the property of their respective owners.

一次にもある

#### Contents

|    | Preface                                                             |

|----|---------------------------------------------------------------------|

| 1. | Processor Overview 5                                                |

|    | 1.1 Processor Features                                              |

|    | <b>1.2 Processor Organization</b> 7                                 |

|    | 1.2.1 Instruction Fetch Unit                                        |

|    | 1.2.2 Decode Unit                                                   |

|    | 1.2.3 Branch Unit                                                   |

|    | 1.2.4 Integer Executior, Unit                                       |

|    | 1.2.5 Load/Store Unit                                               |

|    | 1.2.6 Floating-Point Execution Unit                                 |

|    | 1.2.7 Level 2 Cache                                                 |

|    | 1.2.8 Bus Interface Unit 15                                         |

| 2. | PowerPC Architecture Compliance                                     |

|    | <b>2.1 X<sup>704</sup> User Instruction Set Architecture (UISA)</b> |

|    | 2.1.1 Reserved Fields                                               |

|    | 2.1.2 Classes of Instructions 17                                    |

|    | 2.1.2.1 Defined Instruction Class                                   |

|    | 2.1.2.2 Illegal Instruction Class                                   |

|    | 2.1.2.3 Reserved Instruction Class                                  |

|    | 2.1.3 Exceptions                                                    |

|    | 2.1.4 Branch Processor 19                                           |

|    | 2.1.4.1 Instruction Fetching                                        |

Ш

|       | 2.1.4.2 Branch Prediction                                         | 9  |

|-------|-------------------------------------------------------------------|----|

|       | 2.1.4.3 Invalid Branch Instruction Forms 1                        | 9  |

| 2.1.5 | Fixed-Point Processor 2                                           | 0  |

|       | 2.1.5.1 Load/Store Unit                                           | 0  |

|       | 2.1.5.2 Invalid Load/Store Instruction Forms                      |    |

|       | 2.1.5.3 Reservation Granularity                                   |    |

|       | 2.1.5.4 Synchronization Instruction 2                             | 1  |

|       | 2.1.5.5 Data Breakpoints                                          | .1 |

| 2.1.6 | Fixed-Point Unit 2                                                | 2  |

|       | 2.1.6.1 Invalid Fixed-Point Instruction Forms                     | 2  |

| 2.1.7 | Floating-Point Unit                                               | 3  |

|       | 2.1.7.1 Conformance with IEEE Standard 2                          | 3  |

|       | 2.1.7.2 Floating-Point Load/Store Operations                      | 3  |

|       | 2.1.7.3 Floating-Point Arithmetic Instructions                    | 3  |

|       | 2.1.7.4 Floating-Point Status and Control Register Instructions 2 |    |

|       | 2.1.7.5 Optional Instructions                                     |    |

|       | 2.1.7.6 Denormalized Numbers 2                                    |    |

|       | 2.1.7.7 Floating-Point Exceptions                                 |    |

|       | 2.1.7.8 Invalid Floating-Point Instruction Forms                  | 25 |

| 2.2 X | <sup>704</sup> Virtual Environment Architecture (VEA)             | 25 |

| 2.2.1 | Storage Model                                                     | 25 |

|       | 2.2.1.1 Caches                                                    | 25 |

|       | 2.2.1.2 Storage Consistency                                       | 27 |

| 2.2.2 | Effect of Operand Placement on Performance                        | 27 |

| 2.2.3 | Cache Management Instructions                                     | 27 |

|       | 2.2.3.1 Instruction Cache Block Invalidate ( <i>icbi</i> )        | 27 |

|       | 2.2.3.2 Instruction Synchronize ( <i>isync</i> )                  | 28 |

|       | 2.2.3.3 Data Cache Block Touch ( <i>dcbt</i> )                    | 28 |

|       | 2.2.3.4 Data Cache Block Touch for Store ( <i>dcbtst</i> )        |    |

|       | 2.2.3.5 Data Cache Block Zero ( <i>dcbz</i> )                     | 29 |

|       | 2.2.3.6 Data Cache Block Store ( <i>dcbst</i> )                   | 29 |

|       | 2.2.3.7 Data Cache Block Flush ( <i>dcbf</i> )                    | 30 |

| 2.2.4 | Additional Diagnostic Instructions.                               | 30 |

| 2.2.5 | Storage Access Ordering                                           | 32 |

| 2.2.6              | Executing Modified Code                                                                                          |

|--------------------|------------------------------------------------------------------------------------------------------------------|

| 2.2.7              | Atomic Update Primitives                                                                                         |

| 2.2.8              | Timer Facilities                                                                                                 |

| 2.3 X <sup>7</sup> | <sup>704</sup> Operating Environment Architecture (OEA)                                                          |

|                    | Reserved Fields in Storage Tables                                                                                |

| 2.3.2              | Exceptions                                                                                                       |

| 2.3.3 [            | Branch Processor                                                                                                 |

| •                  | 2.3.3.1 SRRO and SRR1                                                                                            |

| :                  | 2.3.3.2 MSR                                                                                                      |

| 2.3.4 F            | Fixed-Point Processor                                                                                            |

| :                  | 2.3.4.1 Software Use SPRs                                                                                        |

| :                  | 2.3.4.2 Processor Version Register                                                                               |

| 2                  | 2.3.4.3 Additional Special Purpose Registers                                                                     |

| 2                  | 2.3.4.4 TLB Miss Registers                                                                                       |

|                    | 2.3.4.4.1 TLB Miss Address Register (MAR)                                                                        |

|                    | 2.3.4.4.2 TLB Miss Interrupt Status Register (MISR)                                                              |

|                    | 2.3.4.4.4 TLB Miss PTEG Address Hash Registers (HASH1 and HASH2) 40                                              |

|                    | 2.3.4.4.5 TLB Miss Update LRU Registers (TLBLRU0 and TLBLRU1)                                                    |

|                    | 2.3.4.6 TLB Miss Update MRF Register (TLBMRF) 41                                                                 |

| 2                  | 2.3.4.5       Debugging Registers       41         2.3.4.5.1       Breakpoint Control Register (BPTCTL)       42 |

|                    | 2.3.4.5.2 Instruction Address Breakpoint Register (IABR)                                                         |

|                    | 2.3.4.5.3 Extended Data Address Breakpoint Register (XDABR)                                                      |

|                    | 2.3.4.5.4 Data Address Breakpoint Register (DABR)                                                                |

| _                  | 2.3.4.5.5 Event Register (EVENT)                                                                                 |

| 2                  | 2.3.4.6 Processor Control Registers                                                                              |

|                    | 2.3.4.6.2 Machine Check Register (CHECK)                                                                         |

|                    | 2.3.4.6.3 L2/Bus Control Register (L2CTL)                                                                        |

|                    | 2.3.4.6.4 L2 Column Disable Register (L2CDR)                                                                     |

| 2                  | 2.3.4.7 Processor Identification Register (PIR)                                                                  |

| 2.3.5 S            | itorage Control                                                                                                  |

|                    | 2.3.5.1 Translation Lookaside Buffer (TLB)                                                                       |

| 2                  | .3.5.2 Block Address Translation                                                                                 |

|                    | .3.5.3 Storage Access Modes                                                                                      |

| 2                  | .3.5.4 Reference and Change Recording 54                                                                         |

V

|    |        | 2.3.5.5        | Storage Control Instructions                                                            |    |

|----|--------|----------------|-----------------------------------------------------------------------------------------|----|

|    |        |                | 2.3.5.5.2 TLB Invalidate Entry ( <i>tlbie</i> )                                         |    |

|    |        |                | 2.3.5.5.3 TLB Invalidate All ( <i>tlbia</i> )                                           |    |

|    |        |                | 2.3.5.5.4 TLB Synchronize ( <i>tlblsync</i> )                                           | 55 |

|    | 2.3.6  | Interru        | ıpts                                                                                    | 56 |

|    |        | 2.3.6.1        | Interrupt Classes                                                                       | 56 |

|    |        | 2.3.6.2        | Interrupt Definitions                                                                   |    |

|    |        |                | 2.3.6.2.1 System Reset Interrupt                                                        |    |

|    |        |                | 2.3.6.2.2       Machine Check Interrupt.         2.3.6.2.3       Data Storage Interrupt |    |

|    |        |                | 2.3.6.2.4 Instruction Storage Interrupt.                                                |    |

|    |        |                | 2.3.6.2.5 External Interrupt                                                            |    |

|    |        |                | 2.3.6.2.6 Alignment Interrupt.                                                          | 60 |

|    |        |                | 2.3.6.2.7 Program Interrupt                                                             |    |

|    |        |                | 2.3.6.2.8 Floating-Point Unavailable                                                    |    |

|    |        |                | 2.3.6.2.10 System Call Interrupt                                                        |    |

|    |        |                | 2.3.6.2.11 Trace Interrupt                                                              |    |

|    |        |                | 2.3.6.2.12 Floating-Point Assist Interrupts                                             | 61 |

|    |        |                | 2.3.6.2.13 TLB Miss interrupt.                                                          |    |

|    |        |                | 2.3.6.2.14 TLB Store Interrupt                                                          |    |

|    |        | 2.3.6.3        | Exception Ordering                                                                      | 64 |

|    | 2.3.7  | Synch          | ronization Requirements for Special Registers                                           | 64 |

| 3. | Proce  | 9 <b>88</b> 0r | Operation                                                                               | 67 |

|    | 3.1 E  | xecuti         | on Pipeline                                                                             | 67 |

|    | 3.1.1  | Fetch          | Stage (F)                                                                               | 68 |

|    | 3.1.2  | Decod          | de Stage (D)                                                                            | 68 |

|    | 3.1.3  | Addre          | ess Generation Stage (A)                                                                | 68 |

|    | 3.1.4  | Cache          | Access Stage (C)                                                                        | 68 |

|    | 3.1.5  | Tag N          | latch Stage (M)                                                                         | 68 |

|    | 3.1.6  | Write          | back Stage (W)                                                                          | 68 |

|    | 3.1.7  | ALU C          | Operations                                                                              | 69 |

|    | 3.1.8  | Floatir        | ng-Point Operations                                                                     | 69 |

|    | 3.2 lr | nstruc         | tion Cache                                                                              | 69 |

|    | 3.3 D  | ata Ca         | ache                                                                                    | 70 |

|    | <b>3.4 Level 2 Cache</b>                                       |

|----|----------------------------------------------------------------|

|    | 3.4.1 Level 2 Cache Tags                                       |

|    | 3.4.2 Address Translation and the Level 2 Cache                |

|    | 3.4.3 Level 2 Cache Replacement Policy                         |

|    | 3.4.4 Disabling the Level 2 Cache                              |

|    | 3.4.5 Flushing the Level 2 Cache                               |

|    | 3.4.6 Cache Coherency Protocol                                 |

|    | 3.4.7 Cache Prefetching                                        |

|    | <b>3.5 Translation Lookaside Buffer (TLB)</b>                  |

|    | <b>3.6 Instruction TLB (ITLB)</b>                              |

|    | 3.7 Block Address Translation                                  |

|    | 3.8 Branch Prediction                                          |

|    | 3.8.1 Branch Direction Prediction                              |

|    | 3.8.2 Branch Target Prediction                                 |

|    | 3.8.3 Finder Initialization                                    |

|    | 3.9 Diagnostic Accesses                                        |

|    | 3.10 Power-On Reset and Hard Reset Initialization              |

| 4. | Instruction Execution                                          |

|    | 4.1 Pipeline Diagrams                                          |

|    | 4.2 Sliding ALU Stage                                          |

|    | 4.3 Branch Resolution                                          |

|    | <b>4.4 Instruction Grouping Rules</b>                          |

|    | <b>4.5 Fetch Stalls</b>                                        |

|    | 4.6 Decode Stalls                                              |

|    | <b>4.7 Pipe Stalls</b>                                         |

|    | 4.8 Penalties for Algebraic and Misaligned Loads and Stores 99 |

|    | 4.8.1 Pipeline Diagrams for Algebraic Loads                    |

|    | 4.8.2 Pipeline Diagrams for Misaligned Loads                     | 100 |

|----|------------------------------------------------------------------|-----|

|    | 4.8.3 Pipeline Diagram for Misaligned Stores.                    | 101 |

|    | 4.9 Floating-Point Execution                                     | 101 |

|    | 4.9.1 Floating-Point Computational Instructions                  | 103 |

|    | 4.9.2 Floating-Point Compare Instructions                        | 103 |

|    | 4.9.3 Floating-Point Load and Store Instructions                 | 104 |

|    | 4.9.4 Floating Point Exceptions and Condition Register Updates 1 | 104 |

|    | 4.9.5 Floating-Point and Integer Pipeline Synchronization        | 105 |

|    | 4.9.6 Optimizing Floating-Point Performance                      | 106 |

| 5. | Signal Descriptions 1                                            | 107 |

|    | 5.1 Bus Interface Signals 1                                      | 07  |

|    | 5.2 Signal Descriptions 1                                        | 09  |

|    | 5.2.1 Clock and Phase-Locked Loop Signals 1                      | 11  |

|    | 5.2.2 Test Signals 1                                             | 113 |

|    | 5.2.3 Thermal Monitoring and Control Signals                     | 13  |

| 6. | Processor Interface                                              | 15  |

|    | 6.1 Address Bus                                                  | 16  |

|    | 6.2 Data Bus 1                                                   | 16  |

|    | 6.3 Coherency Protocol 1                                         | 16  |

|    | 6.4 Features for Improved Bus Performance                        | 17  |

| 7. | Test Interface                                                   | 19  |

|    | 7.1 JTAG Interface                                               | 19  |

|    | <b>7.2 Scan Chains</b>                                           | 19  |

|    | 7.3 At-Speed Testing 1                                           | 20  |

| 8. | Package Description 1                                            | 21  |

|    | Appendix A. Sample TLB Interrupt Handlers                        | 27  |

|    | Index                                                            | 133 |

٠

Figures

| Figure 1: Data Path Simplified Block Diagram               |

|------------------------------------------------------------|

| Figure 2: Instruction Fetch Unit Simplified Block Diagram9 |

| Figure 3: Integer Execution Unit Simplified Block Diagram  |

| Figure 4: Load/Store Unit Simplified Block Diagram         |

| Figure 5: Floating-Point Execution Unit Block Diagram      |

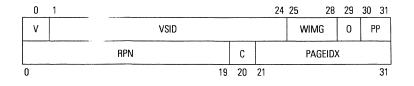

| Figure 6: TLB Miss PTE Compare Register                    |

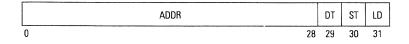

| Figure 7: TLB Miss PTEG Address Hash Registers             |

| Figure 8: TLBLRU Registers 40                              |

| Figure 9: TLB Entry 41                                     |

| Figure 10: Breakpoint Control Register                     |

| Figure 11: Instruction Address Breakpoint Register         |

| Figure 12: Data Address Breakpoint Register                |

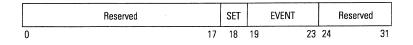

| Figure 13: Event Register                                  |

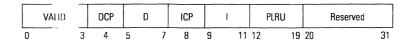

| Figure 14: Modes Register                                  |

| Figure 15: Machine Check Register                          |

| Figure 16: L2/Bus Control Register 50                      |

| Figure 17: L2 Column Disable Register                      |

| Figure 18: Instruction Cache Tags                          |

| Figure 19: Data Cache Tags 71                              |

| Figure 20: Level 2 Cache Tags                              |

| Figure 21: L2 Cache Use Record                             |

| Figure 22: TLB Entry                                       |

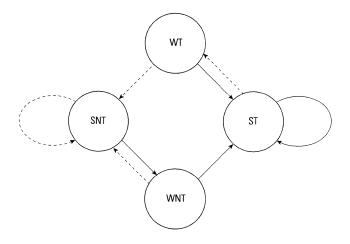

| Figure 23: Predicted Branch Direction State Transitions    |

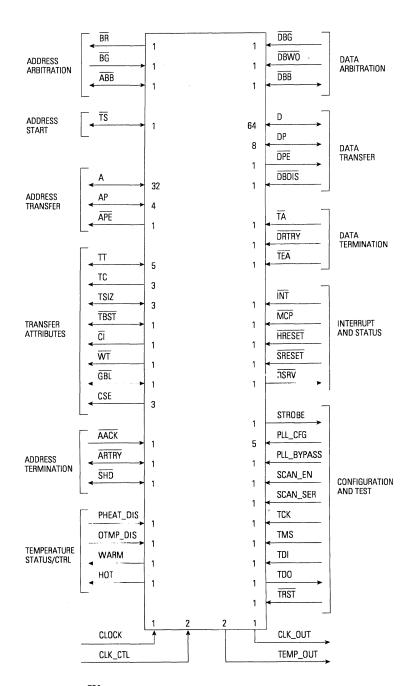

| Figure 24: X <sup>704</sup> Bus Interface Signals 108      |

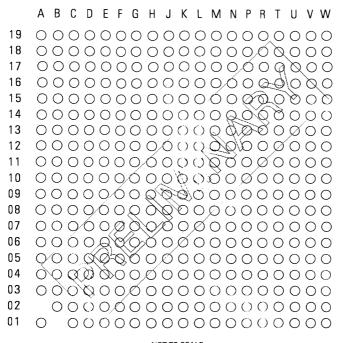

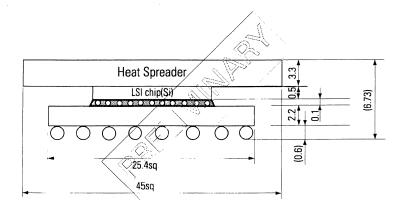

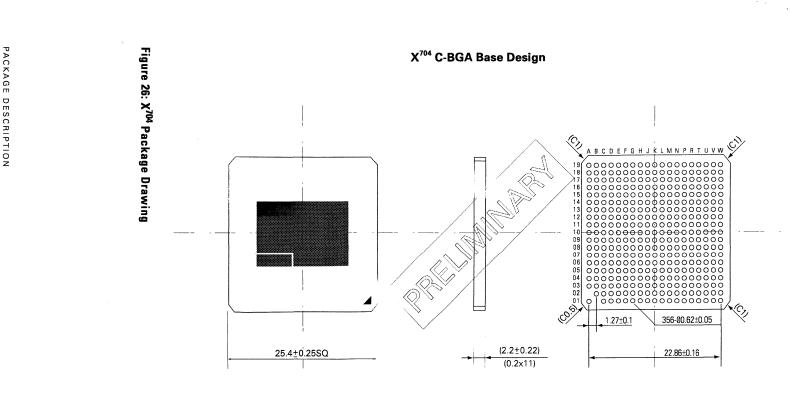

| Figure 25: Pinout Diagram for the X <sup>704</sup> Package |

| Figure 26: X <sup>704</sup> Package Drawing                |

iх

# EXPONENTIAL X<sup>704</sup> TECHNICAL SUMMARY

# Tables

| Table 1: Processor Revision Values    35                               |

|------------------------------------------------------------------------|

| Table 2: Special Purpose Registers    36                               |

| Table 3: Event Counter Selections.    46                               |

| Table 4: Interrupt Vector Offsets    56                                |

| Table 5: Synchronization Requirements for Implementation-              |

| Dependent SPRs64                                                       |

| Table 6: Level 2 Cache Tag MESI State Values.    73                    |

| Table 7: Diagnostic Address Space    84                                |

| Table 8: Hard Reset State Initialization    86                         |

| Table 9: Floating-Point Instruction Bandwidth and Latency.         102 |

| Table 10: Floating-Point and Integer Pipeline Alignments         105   |

| Table 11: Processor-Dependent Signal Descriptions         109          |

| Table 12: Typical PLL_CFG Settings    112                              |

| Table 13: CLK_CTL Settings    112                                      |

| Table 14: Pinout Listing for the X <sup>704</sup> Package    122       |

хı

#### EXPONENTIAL X<sup>704</sup> TECHNICAL SUMMARY

хп

# Scope of this Document

This document presents information supporting hardware design and systems programming with Exponential Techology's  $X^{704}$ . Note that this document is in progress and is subject to change at any time. Presently, it consists of eight chapters and an appendix, as follows:

- Chapter 1, "Processor Overview," describes basic features of the X<sup>704</sup> and provides an overview of the processor's organization and architecture.

- Chapter 2, "PowerPC Architecture Compliance," contrasts the implementation of the X<sup>704</sup> to the Apple-IBM-Motorola specification for PowerPC architecture provides details of features specific to the X<sup>704</sup> implementation.

- Chapter 3, "Processor Operation," provides a detailed look at the X<sup>704</sup> hardware features that are of particular interest to systems programmers.

- Chapter 4, "Instruction Execution," provides details on the operation of the instruction pipelines. It will benefit software engineers working to predict processor performance or to optimize software.

- Chapter 5, "Signal Descriptions," presents details on the  $X^{704}$  hardware interface.

- Chapter 6, "Processor Interface," summarizes aspects of the hardware interface that are unique to the X<sup>704</sup>.

- Chapter 7, "Test Interface," presents details on X<sup>704</sup> testability.

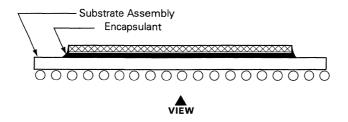

- Chapter 8, "Package Description," provides a physical and mechanical description of the X<sup>704</sup>.

- Appendix A, "Sample TLB Interrupt Handlers," provides code examples.

1

# **Documentation Conventions and Definitions**

This document follows the notation conventions used in the *PowerPC Architecture Specification* referenced on page 3. In addition, the following notation is used:

- Obnnnn indicates a number expressed in binary format; 0xnnnn indicates a number expressed in hexadecimal format (for example, 0x4F00).

- Instruction mnemonics appear in lowercase, bold italic typefaces (for example, sync, tlbsync).

- Bits are numbered from left to right, starting with the lower numbered bit.

- Ranges of bits are specified in parentheses with starting and ending numbers separated by a colon. For example, (5:7) denotes bits five through seven.

- Register names, fields of instructions, fields of special purpose registers, and macro names appear in uppercase (for example, MSR, BO, RA, and VSID).

- REG[FIELD] indicates a specific field within a register (for example, FPSCR[NI]).

- REG(p) or REG(p:q) indicates a specific bit or range of bits, respectively, within a register (for example, BO(2)).

- (x) indicates the contents of register x, when x is an instruction field name. For example, (RA) means the contents of register RA, and (FRA) means the contents of FRA, where RA and FRA are instruction fields.

- (RAI0) indicates the contents of register RA where RA has the value of 1-31, or the value 0 when RA contains 0.

- ACTIVE\_HIGH signals appear in uppercase text (for example, SCAN\_EN and SCAN\_SER).

- ACTIVE\_LOW signals appear in uppercase text with an overbar (for example, ABB and DBB).

- SIG0–SIG7 indicates a group of signals from SIG0 to SIG7.

- The term *power-endian* is used to refer to the pseudo-little-endian mode defined for the PowerPC.

# **Applicable Documents**

The X<sup>704</sup> is compatible with the PowerPC architecture as specified in the following documents:

- IBM, *PowerPC User Instruction Set Architecture (Book I)*, Morgan Kaufmann, San Francisco, CA, second edition, December 13, 1994.

- IBM, *PowerPC Virtual Environment Architecture (Book II–AIM)*, Morgan Kaufmann, San Francisco, CA, second edition, December 13, 1994.

- IBM, *PowerPC Operating Environment Architecture (Book III–AIM)*, Morgan Kaufmann, San Francisco, CA, second edition, December 13, 1994.

These documents are collectively referred to as the *PowerPC Architecture Specification, PowerPC architecture,* or simply as the architecture specification and are individually referred to as Book I, Book II, and Book III. Readers of this document should be familiar with these books.

The X<sup>704</sup> bus interface is compatible with the interface described in:

Motorola: PowerPC 604 Microprocessor Interface Specification, March 28, 1994.

This document is referred to as the bus specification.

The  $X^{704}$  supports a test interface compatible with the IEEE 1149.1 standard described in:

• IEEE, New York, NY: IEEE Standard Test Access Port and Boundary-Scan Architecture, IEEE Standard 1149.1, May, 1990

4

# **1. Processor Overview**

This document describes the X<sup>704</sup> implementation of the PowerPC architecture.

#### **1.1 Processor Features**

The Exponential Technology  $X^{704}$  is a single-chip implementation of the 32bit PowerPC architecture that conforms fully to the *PowerPC Architecture Specification*. The  $X^{704}$  processor features:

- separate integer, load/store, branch, and floating-point units

- up to three instructions issued each cycle

- separate level 1 data and instruction caches

- unified data and instruction level 2 cache

- on-chip translation lookaside buffer (TLB)

#### **Integer Unit**

- executes all arithmetic, logical, compare, rotate, and shift instructions except multiply and divide in a single cycle

- executes multiply instructions in 3 to 6 cycles

- bypasses results to following instructions with no delay

#### Load/Store Unit

- · supports issue of a load or store each cycle

- handles all big-endian mode misaligned loads and stores in hardware

- · supports power-endian mode, including some misaligned accesses

- forwards load data to the integer unit with no load-use penalty

#### **Branch Unit**

- supports issue of a branch or condition register logical instruction each cycle

- maintains 2-bit dynamic branch prediction in hardware

- supports prediction through both PC-relative and indirect branches

- no penalty for following correctly predicted branches

- · recovers quickly from mispredicted branches

#### **Floating-Point Unit**

- complies with IEEE-754 single-precision and double-precision arithmetic standard

- implements optional *fsel* and *stfiwx* instructions

- supports denormalized numbers in hardware

#### Caches

- 2-level cache hierarchy

- 2KB direct-mapped instruction cache with 32-byte blocks

- 2KB direct-mapped write through data cache with 32-byte blocks

- 32 KB 8-way set-associative unified level 2 cache with 32-byte blocks

- supports write through and copy back protocols (level 2 cache)

- supports all PowerPC cache operations

- physically indexed and physically tagged caches

- features 4-doubleword store queue between load/store unit and data/level 2 caches

- features software disables

- maps out damaged blocks and columns (level 2 cache)

#### Memory Management Unit

- contains 128-entry, 4-way set-associative TLB with hardwareassisted software refill

- contains four-entry, fully associative instruction TLB with hardware refill from main TLB

- supports block address translation for four instruction blocks and four data blocks

#### **MultiProcessing Support**

- supports MESI cache coherency protocol

- supports *Iwarx* and *stwcx*. memory synchronization instructions for atomic updates

- broadcast synchronization of cache operations and serialization

- broadcast TLB invalidates

#### **Bus Interface**

- supports standard 64-bit data, 32-bit address 60x bus

- supports data streaming with optional fast L2 mode

- supports pipelined and split transactions

- supports processor clock that is an integral multiple of bus clock

#### **Test Interface**

- features JTAG TAP controller with boundary scan

- proprietary scan access to all internal flip flops

- supports scan access to all internal RAM structures

- supports instruction-level access to all internal RAM structures

- performs at-speed fault testing

# **1.2 Processor Organization**

This section presents a high-level view of the  $X^{704}$  processor. See Chapter 3 for detailed descriptions of the  $X^{704}$  micro-architecture and implementation.

The major functional blocks of the X<sup>704</sup> include the following:

- instruction fetch unit, including the instruction cache

- decode unit

- integer execution unit

- · load/store unit, including the data cache and TLB

- floating-point execution unit

- level 2 cache

- bus interface unit

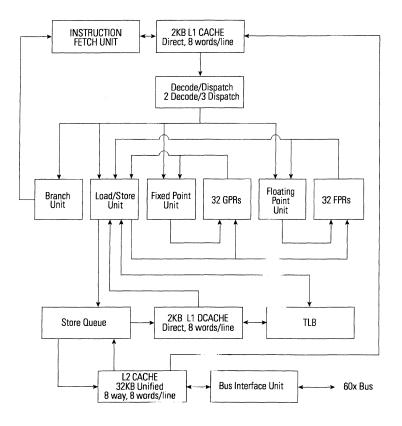

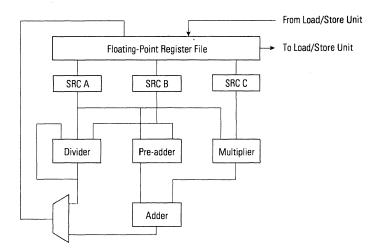

The block diagram in Figure 1 depicts an overview of the  $X^{704}$  data paths.

Figure 1: Data Path Simplified Block Diagram

# **1.2.1 Instruction Fetch Unit**

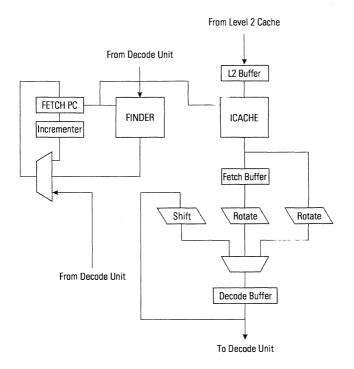

The instruction fetch unit contains the instruction cache, the instruction TLB and the IBAT registers, a branch prediction RAM known as the *finder*, and a 6-word instruction buffer. The instruction buffer consists of a four-entry decode buffer and a two-entry fetch buffer. Figure 2 shows a simplified block diagram of the instruction fetch unit.

As the decode unit empties the decode buffer, the fetch unit continually reads instructions from the instruction cache and places them in the instruction buffer. Instructions not consumed by the decode unit are moved to the front of the decode buffer. An aligned doubleword can be read from the instruction cache on each cycle. The instruction cache is not read during an instruction TLB miss, during an instruction cache miss, or when the fetch buffer is not empty. Only one instruction can be placed in the decode buffer after the instruction stream branches to an instruction on an odd word address. Instructions are placed directly in the decode buffer portion of the instruction buffer if it is not full; the fetch buffer holds any overflow.

The fetch unit maintains its own copy of the program counter, called the fetch PC, that is updated in one of three ways:

- If the finder indicates that the instruction being read is not a branch or is a branch that is predicted to be not taken, the fetch unit increments the counter.

- If the finder predicts that a branch will be taken, the fetch unit sets the counter to the branch target address.

- If the decode unit indicates that a previous branch was predicted incorrectly, the fetch unit sets the counter to the correct branch target address provided by the decode unit.

Figure 2: Instruction Fetch Unit Simplified Block Diagram

The fetch unit predicts indirect branches, including return-from-interrupt, and some interrupts. However, not all branches can be predicted. See Section 3.8 on page 81 for more information on branch prediction.

# 1.2.2 Decode Unit

The decode unit examines the contents of the first three entries in the decode buffer and determines whether the first, the first and the second, or all three of those instructions can be *issued*—sent to the appropriate execution unit—on each cycle. Integer register operands are read from the integer register file, which is part of the decode unit. The decode unit tracks interinstruction interlocks and ensures that all results are correctly bypassed to any instructions that need them. This unit also processes exceptions.

# 1.2.3 Branch Unit

The branch unit determines whether branches are taken and computes branch target addresses. The branch unit tracks all branch predictions made by the fetch unit and handles mispredicted branches by flushing the pipeline and sending the correct branch target address back to the fetch unit.

The condition register resides in the branch unit, so all condition register logical instructions are executed here. The branch unit also contains the link register, count register, XER, MSR, SRR0, SRR1, DEC, TBU, and TBL special purpose registers.

#### **1.2.4 Integer Execution Unit**

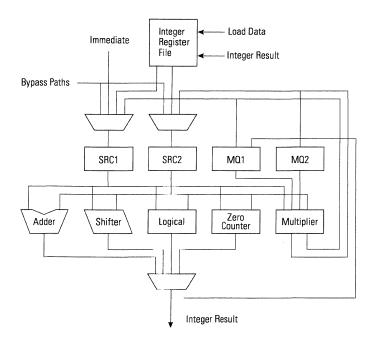

The integer execution unit consists of a single pipe stage that executes instructions in one of five subunits: an adder unit, a logical operation unit, a shifter/rotator, a leading-zero counter, and a multiplier. The multiplier takes multiple cycles and includes two internal registers, MQ1 and MQ2, that hold intermediate results. Divides use a combination of the adder and the shifter/rotator. Only one subunit can execute an instruction in any one cycle. Figure 3 shows a simplified block diagram of the integer execution unit.

#### Figure 3: Integer Execution Unit Simplified Block Diagram

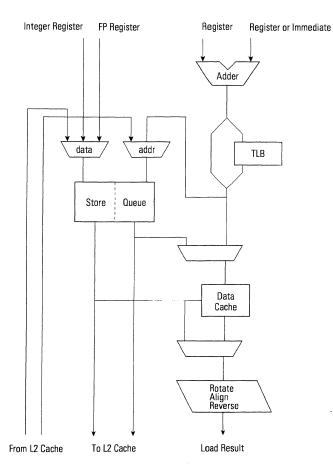

# 1.2.5 Load/Store Unit

In conjunction with the level 2 cache and bus interface unit, the load/store unit executes load, store, and cache operation instructions. This unit consists of an adder that produces the effective address from the address operands, the TLB, the data cache, a rotator that handles misaligned data and performs byte-reversal, and a store queue. Figure 4 on page 13 shows a simplified block diagram of the load/store unit. A number of SPRs, including the DAR, DSISR, SDR1, SPRG, and DBATs, and the segment registers, reside in the load/store unit.

The load/store unit reads the results of load instructions from the data cache. It then immediately bypasses the results to any execution unit that may need them as operands for other instructions, even to fixed-point instructions that are issued in the same cycle as the load. Because of this intra-cycle bypassing, the load-use penalty for ALU operations on the  $X^{704}$  is effectively zero cycles. Store instructions do not usually delay the execution pipeline. Store data is placed in the store queue where it waits for a free cycle when it can be written to the level 2 cache and possibly to the data cache.

Data in the store queue can be written to both the data cache and the level 2 cache. Store queue entries also hold data sent from the level 2 cache in response to a data cache miss. The store queue allows subsequent load instructions to proceed and potentially complete before it writes the store data to either cache. Stores that miss in the data cache do not cause a data cache miss; instead, the data is sent directly to the level 2 cache, where a miss occurs if necessary. This process is known as *store-around*.

The store queue contains four doubleword entries. Cacheable stores that hit existing entries in the store queue combine with the existing entry rather than allocate a new entry. This significantly improves the performance of consecutive stores, particularly those using the store multiple instruction. In most cases, data held in the store queue can be bypassed back into the pipeline when a load instruction hits it; the load need not wait until the store queue data is written into the data cache.

Cache operations are placed in the store queue and sent to the level 2 cache, which actually performs the operations, without holding up the execution pipeline. The **sync**, **tlbsync**, and **eieio** synchronization instructions also execute in the load/store unit and do not complete until all of the appropriate entries have been removed from the store queue.

# Figure 4: Load/Store Unit Simplified Block Diagram

# **1.2.6 Floating-Point Execution Unit**

The floating-point execution unit contains the floating-point register file, a pipelined adder, a pipelined multiplier, and a divider that all support the IEEE-754 standard for floating-point arithmetic. Figure 5 shows a simplified block diagram of the floating-point execution unit.

The X<sup>704</sup> processor supports IEEE NaNs and denormalized numbers. See Section 2.1.7.6 on page 24 for more information on denormalized numbers.

Figure 5: Floating-Point Execution Unit Block Diagram

# 1.2.7 Level 2 Cache

The level 2 cache moves data between external caches or memory and the faster instruction and data caches. The level 2 cache controller handles multiple misses and processes hits from either level 1 cache while satisfying a miss from one or both of them.

The level 2 cache also executes cache operations such as block touch, block store, and block zero, maintaining both the storage reservation used by the **stwcx**. instruction and cache coherency in a multiprocessor system using the MESI protocol.

The level 1 caches must be subsets of the level 2 cache; the level 2 cache tags record which lines, if any, are present in either level 1 cache. This allows the level 2 cache to execute most cache operations and process most snoop requests without interfering with the operation of the level 1 caches.

#### 1.2.8 Bus Interface Unit

The bus interface unit passes information between the level 2 cache and the system bus using the basic transfer protocol described in the bus specification. It contains:

- a 32-byte writeback buffer that stages data being evicted from the level 2 cache

- a 16-byte write buffer that holds write data being sent to the system in response to a snoop

- address buffers that hold information for up to three read, write, coherency, or synchronization requests and a single incoming snoop request

In a multiprocessor system, the bus interface unit maintains information on the state of broadcast coherency and synchronization operations.

#### PROCESSOR OVERVIEW

# EXPONENTIAL X<sup>704</sup> TECHNICAL SUMMARY

-

# 2. PowerPC Architecture Compliance

This chapter describes implementation-defined features of the X<sup>704</sup> and elaborates on general architectural details where necessary.

# 2.1 X<sup>704</sup> User Instruction Set Architecture (UISA)

This section follows the structure of Book I of the *PowerPC Architecture Specification*. The reader should be familiar with that book.

#### 2.1.1 Reserved Fields

The PowerPC architecture does not require the implementation of reserved bits in special purpose registers. For reserved bits, do not assume that a read returns the last value written when writing software. When the  $X^{704}$  writes zero to a reserved bit, subsequent reads return zero; when the  $X^{704}$  writes one to a reserved bit, subsequent reads return an undefined value.

#### 2.1.2 Classes of Instructions

The PowerPC architecture defines three instruction classes:

- Defined

- Illegal

- Reserved

The following sections describe the  $X^{704}$ 's implementation.

#### 2.1.2.1 Defined Instruction Class

The X<sup>704</sup> supports all required instructions defined for 32-bit implementations of the PowerPC architecture. It also supports the optional **fsel**, **stfiwx**, and **tlbie** instructions. The X<sup>704</sup> does not support the optional *fres, frsqrte, fsqrt, fsqrts, tlbia, eciwx,* and *ecowx* instructions. Attempts to execute these instructions cause the system illegal instruction error handler to be invoked.

Book I of the architecture defines certain instructions to have preferred forms. The  $X^{704}$  does not distinguish between preferred forms and other forms of valid defined instructions.

The architecture allows invalid forms of defined instructions to cause boundedly undefined results. The operation of the  $X^{704}$  on invalid forms of instructions is described for each of the functional units in Section 2.1.4.3 on page 19, Section 2.1.5.2 on page 21, Section 2.1.6.1 on page 22, and Section 2.1.7.8 on page 25, respectively.

#### 2.1.2.2 Illegal Instruction Class

Attempts to execute instructions in this class cause the system illegal instruction error handler to be invoked. PowerPC instructions defined only for 64-bit implementations are treated as illegal instructions.

#### 2.1.2.3 Reserved Instruction Class

The reserved instruction class comprise the following four subclasses:

- the instruction having primary opcode zero except for the instruction consisting entirely of zeros

- POWER instructions that were not included in the PowerPC architecture

- implementation-dependent instructions required to conform to the architecture specification

- other implementation-dependent instructions

The X<sup>704</sup> invokes the system illegal instruction error handler on attempts to execute instructions with primary opcode zero or POWER instructions that are not included in the PowerPC architecture. See Section G.27 of Book I for POWER instructions not implemented in the PowerPC architecture.

There are no implementation-dependent instructions required to conform to the *PowerPC Architecture Specification*.

The  $X^{704}$  supports two implementation-dependent instructions, *lwdx* and *stwdx*, that provide diagnostic access to the on-chip caches and TLB. See Section 2.2.4 on page 30.

The X<sup>704</sup> also supports several privileged special purpose registers (SPRs) that are not defined in the architecture specification. The *mfspr* and *mtspr* instructions provide access to these registers. These implementation-dependent SPRs are described in Section 2.3.4.3 on page 35.

# 2.1.3 Exceptions

The X<sup>704</sup> supports the standard PowerPC exceptions, including single-step and branch tracing; it also supports two additional exceptions not described in the architecture specification: TLB miss and TLB store. These exceptions handle software reloading and updating of the translation lookaside buffer (TLB). See Section 2.3.6.2 on page 56 for additional information on these interrupts.

# 2.1.4 Branch Processor

The following sections describe the  $X^{704}$  UISA for the branch processor.

# 2.1.4.1 Instruction Fetching

The X<sup>704</sup> prefetches instructions before it determines whether they will actually execute. Instructions are never fetched from guarded storage unless they are either in the cache, known to be on the branch path, or are on the same page as an instruction known to be on the branch path. The X<sup>704</sup> requires software cache operations when a program modifies an instruction it intends to execute. Software must execute the instruction sequence described in Section 2.2.6 on page 32 to ensure that the modified instruction is visible to the fetch unit.

The instruction fetch unit includes an Instruction Address Breakpoint Register (IABR) that triggers a trace interrupt when an instruction is fetched from a specified address. See Section 2.3.4.5 on page 41 for more information on IABR and its associated interrupt.

#### 2.1.4.2 Branch Prediction

The  $X^{704}$  improves its performance by predicting branch directions and target addresses using the algorithms described in Section 3.8 on page 81. The  $X^{704}$  ignores the *y* bit in the BO field of branch conditional instructions.

#### 2.1.4.3 Invalid Branch Instruction Forms

Attempts to execute invalid forms of the *bcctr* instruction where BO(2) is clear will cause the system illegal instruction error handler to be invoked.

Execution of invalid forms of the *mcrf* and condition-register logical instructions with the Rc bit set may cause CR0 to be set to an undefined value.

#### 2.1.5 Fixed-Point Processor

The following sections describe the  $X^{704}$  implementation of the fixed-point processor.

#### 2.1.5.1 Load/Store Unit

Book I of the architecture specification notes that the load algebraic, load with byte reversal, and load with update instructions may have greater latency than other load instructions. On the  $X^{704}$ , load algebraic instructions (*Iha, Ihax, Ihau*, and *Ihaux*) require an additional cycle before the result can be used by another instruction, but can still issue at the rate of one per cycle. Load with byte reversal and load with update instructions, however, incur no additional latency penalty, although update instructions do prevent the simultaneous issue of an integer instruction. See Chapter 4 for more information on instruction latency and performance.

When operating in big-endian mode, the load/store unit supports arbitrary alignment of halfword, word, floating-point single, and floating-point double scalar values. In power-endian mode, the load/store unit supports misaligned word and halfword loads and stores that do not cross a doubleword boundary. Some alignments may incur additional cycles of execution time as described in Section 4.8 on page 99. Power-endian mode elementary loads and stores that cross a doubleword boundary, and any *lwarx* or *stwcx.* instruction with a misaligned target address causes the system alignment error handler to be invoked.

An unaligned access that does not cause the system alignment error handler to be invoked may cross a page boundary. If this happens, the TLB miss, TLB store fault, or system data storage error handlers can be invoked with the instruction partially completed, but the RT register will not have been altered for elementary fixed-point load instructions. Aligned move assist (*Iswi*, *Iswx*, *stswi*, and *stswx*), *Imw*, and *stmw* instructions that cross page boundaries can also cause these handlers to be invoked with the instruction partially completed.

The  $X^{704}$  does not support direct-store segments or accesses to direct-store segments. All attempts to reference data in a direct-store segment cause either the system data storage error handler or the system alignment error handler to be invoked.

#### 2.1.5.2 Invalid Load/Store Instruction Forms

Attempts to execute load with update instructions with RA = RT cause the system illegal instruction error handler to be invoked.

The execution of load with update or store with update instructions with RA = 0 performs the storage access with an effective address of the contents of RB (for X-form instructions) or of the displacement (for D-form instructions). If the access is successful, r0 is set to the effective address.

Execution of the *Imw*, *Iswi*, and *Iswx* instructions with RA or RB in the range of target registers, including the RA = 0 case, functions correctly, but the instructions cannot be restarted reliably if interrupted because the address value in RA or RB may have been overwritten.

Execution of an *Iswx* instruction specifying a zero-byte transfer causes the contents of RT to become undefined.

Execution of invalid forms of load/store instructions with the Rc bit set does not alter CR0.

Execution of the *stwcx.* instruction with the Rc bit clear sets CR0 as if the Rc bit were set.

#### 2.1.5.3 Reservation Granularity

The storage reservation granularity established by the *lwarx* instruction is 32 bytes—the same size as a cache block.

#### 2.1.5.4 Synchronization Instruction

This instruction causes significant performance penalties and should not be used indiscriminately. See Section 2.2.5 on page 32 for a detailed description of the *sync* instruction.

#### 2.1.5.5 Data Breakpoints

The load store unit includes a Data Address Breakpoint Register (DABR) and a Breakpoint Control register (BPTCTL) that cause a data storage interrupt to occur when a specified address or address range is referenced. See Section 2.3.4.5 on page 41 for more information on BPTCTL, DABR, and breakpoint interrupts.

#### 2.1.6 Fixed-Point Unit

Book I of the architecture specification notes that instructions with the OE bit set or those that are defined to set CA can execute slowly or prevent the execution of subsequent instructions until the operation is complete. With the  $X^{704}$  processor, instructions that set CA never cause performance penalties. The performance of multiply instructions, however, is affected by setting the OE bit.

On the  $X^{704}$ , the **mullwo** and **mullwo**. instructions always require six cycles, as opposed to the three to five cycles required by other fixed-point multiply instructions. The only other performance penalty that may occur for fixed-point instructions occurs when recovering from mispredicted branches based on the value of the SO bit in CR0. In this case, a penalty is incurred only when the branch issues while the instruction with OE set is still in the pipeline.

The performance of the *mtcrf* instruction does not depend on the value of the FXM field in the instruction.

Execution of **mtspr** and **mfspr** instructions with undefined values in the SPR field triggers either the system privileged instruction handler (if SPR(0) is set) or the system illegal instruction interrupt handler (if SPR(0) is clear). The  $X^{704}$  defines additional SPR values beyond those defined in the *PowerPC Architecture Specification*.

The  $X^{704}$  does not support the optional EAR special purpose register. Attempts to reference this register cause the system illegal instruction error handler to be invoked.

### 2.1.6.1 Invalid Fixed-Point Instruction Forms

The X<sup>704</sup> processor ignores the Rc bit value in compare, trap, **mtspr**, **mfspr**, **mcrxr**, and **mfcr** instructions. Execution of those instructions with the Rc bit set will not cause CR0 to be set to an undefined value.

Execution of the *mtcrf* instruction with the Rc bit set may cause CR0 to be set to an undefined value.

Execution of compare instructions with Rc set and with BF not equal to zero will set CR field BF correctly.

Execution of compare instructions is unaffected by the value of either the L bit or bit 9 of the instruction.

Execution of instructions such as **neg** that do not use the RB field is unaffected by the contents of that field.

#### 2.1.7 Floating-Point Unit

The following sections describe the  $X^{704}$  implementation of the floatingpoint unit.

# 2.1.7.1 Conformance with IEEE Standard

The  $X^{704}$  floating-point unit complies with the IEEE-754 floating-point standard while the NI bit in the FPSCR is clear. When FPSCR[NI] is set, the  $X^{704}$  deviates from the standard by replacing denormalized results of floating-point computational instructions with zeros. The check for a denormalized result is made before rounding, so a result that would have been rounded from the largest denormalized number to the smallest normalized number is still forced to zero.

Setting the NI bit does not alter either the definitions of other FPSCR fields or the behavior of floating-point exceptions, including underflow and inexact traps resulting from denormalized results that are forced to zero. Applications that want to suppress all floating-point exceptions should clear all five exception enable bits in the FPSCR.

#### 2.1.7.2 Floating-Point Load/Store Operations

The floating-point register file stores all operands in double-precision format. Single-precision loads and stores perform the appropriate conversions to and from the single-precision memory format. Conversions of singleprecision denormalized values on load instructions cause a performance penalty. See Section 4.9 on page 101 for more information on floatingpoint execution.

#### 2.1.7.3 Floating-Point Arithmetic Instructions

The architecture specification requires operands to single-precision floating-point arithmetic instructions to be representable in single-precision format. If they are not, the results of single-precision arithmetic instructions are undefined. On the  $X^{704}$ , the results are undefined only when one or more operands are not representable in single-precision format and the result is also not representable in single-precision format. The undefined result may not be representable in single-precision format and therefore may not be a valid input for subsequent single-precision computational or store instructions.

## 2.1.7.4 Floating-Point Status and Control Register Instructions

The performance of the *mtfsf* instruction does not depend on the value of the FLM field in the instruction.

## 2.1.7.5 Optional Instructions

The X<sup>704</sup> implements the optional **fsel** and **stfiwx** instructions, but not the optional **fres**, **frsqrte**, **fsqrt**, and **fsqrts** instructions. The hardware never sets FPSCR[VXSQRT] except when one of the floating-point status and control instructions sets that bit explicitly.

## 2.1.7.6 Denormalized Numbers

The X<sup>704</sup> provides complete support for denormalized values in both singleand double-precision formats. When the processor is in non-IEEE mode (FPSCR[NI] is set), denormalized results of floating-point computational instructions, but not floating-point load instructions, are forced to zero. Conversion of single-precision denormalized values on load instructions causes a performance penalty. See Section 4.9 on page 101 for more on floatingpoint execution.

## 2.1.7.7 Floating-Point Exceptions

All floating-point exceptions on the  $X^{704}$  are reported as precise exceptions. The  $X^{704}$  does not use the imprecise recoverable and imprecise non-recoverable exception modes. When a floating-point exception occurs while the processor is not in floating-point interrupts disabled mode, SRRO always points to the instruction that caused the exception, all instructions prior to that instruction have completed, and no instructions following that instruction have caused any architecturally visible effects.

Enabling inexact, overflow, and underflow exceptions degrades performance more than enabling zero divide and invalid operation exceptions. Enabling inexact, overflow, and underflow exceptions does not cause the floating-point operations to take longer, but it does prevent the fixed-point and branch processors from completing instructions and issuing additional instructions for an extended period of time. See Section 4.9 on page 101 for more information.

The X<sup>704</sup> processor does not use the floating-point assist interrupt.

## 2.1.7.8 Invalid Floating-Point Instruction Forms

The execution of floating-point load with update or floating-point store with update instructions with RA = 0 performs the storage access with an effective address of the contents of RB (for X-form instructions) or of the displacement (for D-form instructions). If the access is successful, R0 is set to the effective address.

Execution of floating-point load and store instructions with the Rc bit set does not alter CR1.

The  $X^{704}$  processor ignores the value of the Rc bit in *fcmpo* and *fcmpu*. Execution of those instructions with the Rc bit set does not cause CR1 to be set to an undefined value.

Execution of floating-point compare instructions with Rc set and with BF not equal to one will set CR field BF correctly.

## **2.2** X<sup>704</sup> Virtual Environment Architecture (VEA)

This section follows the structure of Book II of the *PowerPC Architecture Specification*. The reader should be familiar with that book.

#### 2.2.1 Storage Model

The following sections describe the implementation of the storage model for the  $X^{704}$  processor.

## 2.2.1.1 Caches

The X<sup>704</sup> contains three on-chip caches: level 1 data and instruction caches, and a unified level 2 cache. In this document, level 1 is used only when referring to the instruction and data caches as a group; otherwise, mose caches are known simply as the instruction cache and the data cache.

All three caches are made up of 32-byte blocks, are physically addressed, and have physical tags. Cache validity is maintained on a doubleword basis in the level 1 caches. A level 2 cache miss requests all 32 bytes from off chip. This doubleword validity scheme allows partially satisfied level 1 cache misses to be abandoned when a higher-priority miss occurs. For example, if the instruction stream executes a branch from the middle of a cache block, there is no need to supply the remainder of that block to the instruction cache. Instead, the level 2 cache may immediately begin supplying data from the target of the branch if that data is not already present in the instruction cache.

The instruction and data caches are 2KB direct-mapped caches. The level 2 cache is a 32KB, eight-way set-associative cache. The level 2 cache always includes any block that is present in either level 1 cache; this is known as the *inclusion* property. The level 2 cache uses a modified pseudo-LRU algorithm to manage the blocks in an associativity set: a block marked as present in either the data cache or the instruction cache is never considered to be the least-recently-used block and is not replaced in the level 2 cache.

The  $X^{704}$  processor disables the caches when it is reset and must be individually enabled by setting the appropriate bits in the L2CTL register. See Section 2.3.4.6.3 on page 50 and Section 3.10 on page 85.

Level 1 cache blocks can be either valid or invalid. Level 2 cache blocks are each in one of the four MESI cache line states: invalid (I), exclusive clean (E), shared clean (S), and exclusive modified (M).

The data cache is a write through cache. The level 2 cache uses the write through required (W) storage control attribute to determine whether each individual block is write through or copy back. Blocks are treated as copy back unless the W bit is set.

Most memory references are either instruction fetches, data loads, or data stores. When all caches are enabled, those operations have the following effects:

- Instruction fetches read the target storage block into the level 2 cache if it is not already present there, and into the instruction cache if it is not already in that cache.

- Data loads read the target storage block into the level 2 cache if it is not already present there, and into the data cache if it is not already in that cache.

- Data stores read the target storage block into the level 2 cache if it is not already present there. If the block is present in the data cache, the modified data is written to the data cache; if the block is not present, it is not brought into the data cache. The X<sup>704</sup> always writes modified data into the level 2 cache, but never to the instruction cache, even if the target block is present there.

All other memory references are performed either with cache management instructions (described in Section 2.2.3 on page 27) or by other processors referencing coherent storage (described in Section 3.4.6 on page 77).

#### 2.2.1.2 Storage Consistency

In order to maintain sequential consistency for memory operations executed within a single processor, the  $X^{704}$  load/store unit wraps data from the store queue when a load hits a recent store. Store data is not placed in the cache or sent off chip until any possible exceptions caused by the store instruction or any instruction issued before the store instruction have occurred.

## 2.2.2 Effect of Operand Placement on Performance

The alignment of operands in memory affects the performance of load and store instructions. In big-endian mode, the X<sup>704</sup> handles misaligned accesses with minimal performance degradation, and then only when the accesses cross a doubleword boundary. In power-endian mode, misaligned accesses that cross a doubleword boundary always invoke the system alignment error handler, resulting in poor performance.

### 2.2.3 Cache Management Instructions

The X<sup>704</sup> implements all cache management instructions described in Book II.

Execution of all of these instructions except *isync* can update the LRU state of the TLB and level 2 cache. Management of the PTE Reference and Change bits is left to the software interrupt handlers, but the handlers should not be expected to distinguish accesses on behalf of cache management instructions from other storage accesses.

#### 2.2.3.1 Instruction Cache Block Invalidate (icbi)

Execution of the *icbi* instruction invokes the TLB miss handler if data address translation is enabled and no translation for the effective address is found in the TLB or DBAT. If a translation is found in the TLB, but read permission is not allowed, the system data storage error handler is invoked. If data address translation is disabled, or a translation is found and read access is allowed, the addressed block is removed from the instruction cache if it is present there. If the addressed storage is in coherence required mode, the operation is then broadcast on the bus to allow the line to be invalidated in the instruction caches of other processors.

The *icbi* instruction never invalidates a block in the level 2 cache.

The effect of this instruction is the same if the instruction cache is disabled.

#### 2.2.3.2 Instruction Synchronize (*isync*)

Execution of the *isync* instruction flushes any subsequent instructions from the pipeline and causes the fetch unit to invalidate the contents of the instruction buffer and to re-fetch the instruction following the *isync* in the current context. All previously issued instructions complete.

This instruction must be used when changing the processor's endian mode (see Section 2.3.3.2 on page 34).

### 2.2.3.3 Data Cache Block Touch (dcbt)

If data address translation is disabled, or if a translation for the effective address is found, read access is allowed and the addressed storage is not in caching inhibited mode, the  $X^{704}$  may read the addressed block into the level 2 cache. If any of these conditions are not met, if the level 2 cache is disabled, or if processor resources are busy on higher-priority memory operations, the *dcbt* instruction is treated as a *nop*.

Because of resource limitations, the  $X^{704}$  generally performs a read for only the last in a sequence of touch operations. Data references caused by the *dcbt* instruction are treated as prefetches. See Section 3.4.7 on page 78 for more information on prefetching.

## 2.2.3.4 Data Cache Block Touch for Store (dcbtst)

The *dcbtst* instruction is treated as a *nop* when:

- the level 2 cache is disabled

- processor resources are busy on higher-priority memory operations

- data address translation is enabled and no translation for the effective address is found

- read access is not allowed

- the addressed storage is in caching inhibited mode

If none of these conditions are true, and the addressed storage is marked as memory coherence required, the addressed block is read into the level 2 cache with a read with intent to modify bus operation and marked as modified in the cache. If the addressed storage is marked as memory coherence not required, the block is read into the cache with a simple read operation and placed in the exclusive state.

This instruction should be used only when there is a high probability that the target cache block will be modified before it is evicted from the cache. If the line is very likely to be read, but less likely to be modified, the **dcbt** instruc-

tion should be used instead. Because of resource limitations, the  $X^{704}$  generally performs a read for only the last in a sequence of touch operations. Data references caused by the *dcbtst* instruction are treated as prefetches. See Section 3.4.7 on page 78 for more information on prefetching.

## 2.2.3.5 Data Cache Block Zero (dcbz)

Execution of the *dcbz* instruction invokes the TLB miss handler if data address translation is enabled and no translation for the effective address is found in the TLB or DBAT. It also invokes the TLB store handler if a matching TLB entry is found with the C bit clear, and invokes the system data error handler if a translation is found that does not allow write permission.

If the addressed storage is marked as memory coherence required and not caching inhibited, *dcbz* broadcasts an invalidate request that removes the line from the caches of any other processors.

If the addressed storage is caching allowed, *dcbz* zeroes the line in the level 2 cache, allocating a cache block if the line is not already present. No read request will be issued on the bus. If the addressed storage is present in the data cache, *dcbz* invalidates the cache block containing that storage

If the level 2 cache is disabled, or if the storage is marked as either caching inhibited or write through required, the *dcbz* instruction sets each byte of the addressed block in off-chip memory to zero. The *PowerPC Architecture Specification* invokes the system alignment error handler in these cases, but the X<sup>704</sup> implementation does not.

### 2.2.3.6 Data Cache Block Store (dcbst)

Execution of the *dcbst* instruction invokes the TLB miss handler if data address translation is enabled and no translation for the effective address is found in the TLB or DBAT. If a translation is found, but read access is not allowed, the system data storage error handler is invoked.

If data address translation is disabled, or a translation is found and the addressed block is marked as modified in the level 2 cache, the contents of the block are written back to off-chip memory, and the state of the block is changed to exclusive clean. If the addressed storage is marked as memory coherence required, the clean operation is broadcast on the bus.

The operation of this instruction is independent of the state of the cache enables. If the block is not present and modified in any processor's level 2 cache, the instruction is treated as a *nop*.

#### 2.2.3.7 Data Cache Block Flush (dcbf)

Execution of the *dcbf* instruction invokes the TLB miss handler if data address translation is enabled and no translation for the effective address is found in the TLB or DBAT. If a translation is found, but read access is not allowed, the system data error handler is invoked.

If data address translation is disabled or a translation is found, and the addressed block is marked as valid in the level 2 cache, the block is invalidated in the data cache, the instruction cache, and the level 2 cache. The data cache block addressed by bits (21:26) of the effective address is invalidated regardless of whether the addressed storage is present in the cache. If the addressed block is marked as modified in the level 2 cache, the contents of the block is written back to main memory. If the addressed storage is marked as coherence required, the flush operation is broadcast on the bus.

The operation of this instruction is independent of the state of the cache enables. If the block is not present in any processor's level 2 cache, the instruction is treated as a **nop**.

### 2.2.4 Additional Diagnostic Instructions

The  $X^{704}$  implements two diagnostic instructions allowing direct access to the TLB, cache data, cache tags, and other internal processor structures. These instructions use an alternate address space to reference the structures. See Section 3.9 on page 84 for a description of the diagnostic address space.

In the following instruction descriptions, DIAG(X, Y) refers to the contents of Y bytes of diagnostic memory at address X in the diagnostic address space.

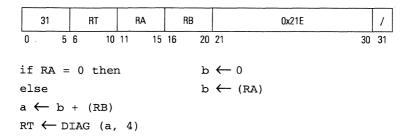

#### Load Word Diagnostic Indexed X-Form

lwdx RT, RA, RB

Let the diagnostic address (a) be the sum (RA | 0) + (RB). The word in diagnostic memory addressed by a is loaded into RT.

This instruction is privileged, and defined only when the DE bit in the MODES register is set. An attempt to execute this instruction with MODES[DE] clear or MSR[PR] set will cause the system illegal instruction error handler to be invoked.

If the instruction references an undefined diagnostic address, the system data storage interrupt handler may be invoked (see Section 3.9 on page 84). The low two bits of the effective address must be zero or the results of executing the instruction are boundedly undefined; this instruction never causes an alignment interrupt.

#### Special Registers Altered: None

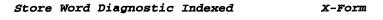

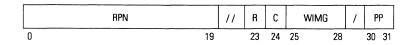

stwdx RS, RA, RB

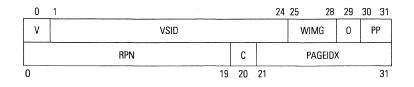

|   | 31             |            |     | RS  |              |    | RA  |    |    | RB |    |    |      |   | 0x29E |        | /  |

|---|----------------|------------|-----|-----|--------------|----|-----|----|----|----|----|----|------|---|-------|--------|----|

|   | )              | 5          | 6   |     | 10           | 11 |     | 15 | 16 |    | 20 | 21 |      |   |       | <br>30 | 31 |

| i | f RA           | =          | 0   | th  | ler          | ı  |     |    |    |    | b  | ←  | 0    |   |       |        |    |

| е | lse            |            |     |     |              |    |     |    |    |    | b  | ←  | (RA) | ) |       |        |    |

| а | $\leftarrow$ k | <b>,</b> . | +   | (RB | )            |    |     |    |    |    |    |    |      |   |       |        |    |

| D | IAG            | (a         | , . | 4)  | <del>(</del> | -  | (RS | )  |    |    |    |    |      |   |       |        |    |

Let the diagnostic address (a) be the sum  $(RA \mid 0) + (RB)$ . (RS) is stored into the word in diagnostic memory addressed by a.

This instruction is privileged, and defined only when the DE bit in the MODES register is set. An attempt to execute this instruction with MODES[DE] clear or MSR[PR] set will cause the system illegal instruction error handler to be invoked.

If the instruction references an undefined diagnostic address, the system data storage interrupt handler may be invoked (see Section 3.9 on page 84). The low two bits of the effective address must be zero or the results of executing the instruction are boundedly undefined; this instruction never causes an alignment interrupt.

#### Special Registers Altered: None

## 2.2.5 Storage Access Ordering

The X<sup>704</sup> implements a weakly consistent storage model. The order in which stores are visible outside the processor may not be the same order in which the stores are performed. For example, multiple stores to the same doubleword can be merged and made visible as a single store operation. If a particular ordering is required, the *eieio* and *sync* instructions can be used to place barriers in the storage access stream.

The *eieio* instruction does not complete until all stores have been removed from the store queue and the level 2 cache has reported that all previous *tlbie* and *tlbsync* operations have been broadcast on the bus. Subsequent load and store instructions are delayed until after the *eieio* completes. The architecture specification defines two sets of operations that are ordered separately by *eieio*, but the X<sup>704</sup> orders all applicable operations as a single set. If synchronization of storage and TLB accesses is all that is required, the *eieio* instruction is preferable to the *sync* instruction.

The **sync** instruction does not complete until the store queue is empty and the level 2 cache reports that no operations are still in progress.

#### 2.2.6 Executing Modified Code

When a program modifies an instruction stream that it wants to execute, cache management instructions must be used to ensure that all updates are visible to the instruction fetch unit. Without the use of these instructions, the  $X^{704}$  does not guarantee coherency between the instruction cache and either the data cache, level 2 cache, or off-chip memory.

After modifying instructions in the block of data addressed by general register RX, the program should execute the following instruction sequence:

| dcbst | RX | ! update cache block in main memory     |

|-------|----|-----------------------------------------|

| sync  |    | ! wait for update to complete           |

| icbi  | RX | ! invalidate block in icache            |

| sync  |    | ! wait for invalidate to complete       |

| isync |    | ! make sure instructions are re-fetched |

Because it appears before the *icbi* instruction, the first *sync* instruction ensures that the fetch unit reads instructions from the modified block after the updates are visible. The second *sync* instruction is necessary only on multiprocessor systems where the block must be flushed from the instruction caches of all processors before execution continues.

## 2.2.7 Atomic Update Primitives

The *lwarx* and *stwcx*. instructions function correctly regardless of the write through required attribute for the addressed storage.

The **stwcx.** instruction performs a store even if its storage address is not identical to the storage address used by the most recent *Iwarx* instruction.

There are no causes of reservation loss other than those listed in Book II. On the  $X^{704}$ , the reservation is lost when another processor executes a *dcbtst* or *dcbi* instruction to the reservation granule, but is not lost when another processor executes a *dcbf* or *dcbst*.

## 2.2.8 Timer Facilities

The X<sup>704</sup> maintains the 64-bit time base register in two parts: the lower 32 bits in the TBL register and the upper 32 bits in the TBU register. These registers can be read separately with the *mftb* and *mftbu* instructions. The X<sup>704</sup> is a 32-bit implementation of the PowerPC architecture and thus does not provide a way to read all 64 bits of the time base in one instruction.

The X<sup>704</sup> increments the time base register every four system bus clock cycles as long as MODES[TBD] is clear. The X<sup>704</sup> also implements the 32-bit decrementer (DEC) register. This register counts down every four system bus clock cycles.

# 2.3 X<sup>704</sup> Operating Environment Architecture (OEA)

This section follows the structure of Book III of the *PowerPC Architecture Specification*. The reader should be familiar with that book.

## 2.3.1 Reserved Fields in Storage Tables

The X<sup>704</sup> hardware does not automatically access the hashed page table and thus does not alter any reserved fields.

## 2.3.2 Exceptions

The X<sup>704</sup> defines two additional interrupts: TLB miss and TLB store. These interrupts manage the software refill and update of the TLB. They are described in detail in Section 2.3.6.2 on page 56.

## 2.3.3 Branch Processor

The following sections describe the  $X^{704}$  implementation of the OEA specification for the branch processor.

#### 2.3.3.1 SRR0 and SRR1

Any instruction fetch when MSR[IR] is set can set SRR0 to the address of the instruction being fetched, and can set SRR1 as described in Section 2.3.6.2.13 on page 61.

The execution of any instruction requiring an address translation when MSR[DR] is set can set SRR0 to the address of the instruction being executed, and can set SRR1 as described in Section 2.3.6.2.13 on page 61 or Section 2.3.6.2.14 on page 62.

#### 2.3.3.2 MSR

The X<sup>704</sup> implements the MSR as described in the *PowerPC Architecture Specification*, including the tracing functions supported by the Branch Trace Enable (BE) and Single-Step Trace Enable (SE) bits. When either of these trace enable bits is set, the processor disables superscalar instruction issue.

Caution: Use of the tracing facilities causes significant performance loss.