Mitsubishi Single Chip Microcomputers

# M16C/62 Group Application Note <Simple I<sup>2</sup>C Bus> (Tentative)

Mitsubishi Electric Corporation, Kitaitami Works Mitsubishi Electric Semiconductor Systems Corporation Mitsubishi Electric System LSI Design Corporation REV.B

## Safety Considerations

Mitsubishi has made every effort to improve the quality and reliability of its products. Nevertheless, a small percentage of semiconductor products can malfunction. Please incorporate redundancy features, fire countermeasures, malfunction prevention features, and other safety measures to prevent bodily injury, fire, or inconvenience to the public.s

#### **Using this Document**

This document is intended to serve as a reference to permit the appropriate use of the Mitsubishi semiconductor products for customer applications. It does not represent consent for the implementation of intellectual property or other rights by Mitsubishi Electric or third-parties.

Mitsubishi Electric takes no responsibility for damage or infringement of third-party rights arising from the use of the data, figures, tables, or circuit charts presented in this document.

The data, figures, tables, and other information are current as of the publication of this document; this information is subject to change without notice as product features are improved by Mitsubishi Electric. Please have your company's technical specialists contact Mitsubishi Electric or your retailer as needed for information about using the products presented here.

Mitsubishi Denki semiconductors are not been designed or manufactured for use in equipment upon which safety and human life depend. Please contact Mitsubishi Denki or your retailer for information regarding transportation, moving vehicle, medical, aerospace, nuclear power control, or sea-floor communications devices and systems, or other special applications.

Written permission must be obtained from Mitsubishi Electric or Mitsubishi Semiconductor Systems prior to excerpting or duplicating this documentation.

Export permits based on all foreign exchange and overseas trade control laws applicable to strategic products and materials described herein must be obtained prior to export.

Please contact Mitsubishi Electric or your retailer with any inquiries or comments you may have about this document.

## Foreword

The "M16C/62 Series Application Notes, "Simple I<sup>2</sup>C Bus Mode" are reference materials intended to help you control the simple I<sup>2</sup>C bus mode which is contained in the Mitsubishi CMOS 16 bit microcomputer M16C/62 series. These materials are not intended to serve as a guarantee of the communications operations of the I<sup>2</sup>C bus. As the user, you are responsible for performing an adequate performance evaluation.

Please use these materials along with the "M16C/60 Series Software Manual" for information about the M16C/62 series command system. Refer to the user manuals appropriate for each of the hardware devices you are using, and see the operating descriptions for information about development support tools.

| Chapter  | Chapter Title                                               | Page Number |

|----------|-------------------------------------------------------------|-------------|

| 1        | Summary of I <sup>2</sup> C Bus Mode Specifications         |             |

| 2        | M16C/62 UART2 Functions                                     |             |

| 3        | Functions of the Simple I <sup>2</sup> C Bus Mode           |             |

| 4        | Precautions Concerning the Simple I <sup>2</sup> C Bus Mode |             |

| Appendix |                                                             |             |

## Summary

The M16C/62 Series has a serial I/O circuit (UART2) which is provided with a simple  $I^2C$  bus circuit. Using a simple  $I^2C$  bus circuit in combination with software enables control of the PC bus interface. This Application Note outlines the  $I^2C$  bus specifications and introduces the various functions and programs that are used to enable the  $I^2C$  bus interface with the simple  $I^2C$  bus function.

To use this document, you need a fundamental knowledge about electrical circuits, logic circuits, and microcomputers.

The document consists of four chapters. You can refer to the appropriate chapters/sections for information responding to the following needs:

| I need to learn about                                                                   | Refer to                                                                 |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| I <sup>2</sup> C bus protocol                                                           | Chapter 1, "Summary of I <sup>2</sup> C Bus Mode Specifications"         |

| M16C/62 serial I/O configuration                                                        | Chapter 2, "M16C/62 UART2 Functions" Section 2.1                         |

| M16C/62 simple I <sup>2</sup> C bus block schematic and the reg-<br>ister configuration | Chapter 2, "M16C/62 UART Functions" Sections 2.2~2.4                     |

| How to use functions of M16C/62 simple I <sup>2</sup> C bus mode                        | Chapter 3, "Functions of the Simple I <sup>2</sup> C Bus Mode"           |

| Precautions regarding use of M16C/62 simple I <sup>2</sup> C bus mode                   | Chapter 4, "Precautions Concerning the Simple I <sup>2</sup> C Bus Mode" |

| Refer to the I <sup>2</sup> C bus mode interface program used by M16C/62                | The reference program                                                    |

## List of Documents for the M16C Family

Applications (Microcomputer development flow)

|                                              |   | Тур      | e of Document                      | Contents                                                                                                                                      |

|----------------------------------------------|---|----------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Microcomputer selection                      |   | are      | Datasheets/<br>Databooks           | Hardware specifications<br>(pin assignment, memory<br>maps, specification of<br>peripheral functions, elec-<br>trical properties, timing)     |

| Schematic design of system                   |   | Hardware | Users' manual                      | Details of hardware<br>specifications, operations,<br>application examples (con-<br>nections with peripherals,<br>relationship with software) |

| <br>Detailed design of system                |   |          | Programming<br>manual              | Assembly language, pro-<br>gramming with C-language                                                                                           |

| Hardware development<br>Software development |   | Software | Software manual                    | Details of each command<br>operation (assembly lan-<br>guage)                                                                                 |

| Software                                     |   |          | Reference<br>program<br>collection | Assembly language refer-<br>ence program collection                                                                                           |

| System evaluation                            | ~ |          |                                    |                                                                                                                                               |

|                                              |   |          |                                    |                                                                                                                                               |

# Chapter 1. Summary of I<sup>2</sup>C Bus Mode Specifications

|     | Chapter 1 Section Title                                   |

|-----|-----------------------------------------------------------|

| 1.1 | I <sup>2</sup> C Bus Mode Features                        |

| 1.2 | II <sup>2</sup> C Bus Mode Concept                        |

| 1.3 | Data Transmission                                         |

| 1.4 | Communication Coordination                                |

| 1.5 | Definition of First Byte                                  |

| 1.6 | Standard Mode and High-Speed Mode                         |

| 1.7 | I <sup>2</sup> C Bus SDA and SCL Bus Line Characteristics |

The I<sup>2</sup>C bus is a multi-master bus communications inter-IC control protocol developed by Philips that is now used by many IC's. Refer to information published by Philips for detailed I<sup>2</sup>C bus specifications.

## 1.1 I<sup>2</sup>C Bus Mode Features

I<sup>2</sup>C bus mode provides efficient control between IC's. It is a two-way bus line with a simple two-wire structure consisting of a serial data line (SDA) and a serial clock line (SCL). I<sup>2</sup>C bus mode also includes the following features:

Each of the devices connected to the bus has its own individual address. A simple master<sup>1</sup> and slave<sup>2</sup> relationship is always established. The master device functions as either a transmitting device or reception device; the slave device functions as either a slave transmitting device or reception device.

Collision detection<sup>3</sup> and communications coordination procedures<sup>4</sup> are incorporated into the device to prevent data destruction in the event that several masters attempt to start data transmission simultaneously, permitting multi-master<sup>5</sup> operations.

Two-way serial data transfer is enabled in high-speed mode.

| Note 1<br>Note 2 | Devices that start data transmission, generate clock signals, and end data transmission.<br>Devices that have addresses designated by the master.                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note 3           | A function that detects data transmitting at levels other than its own when more than one master device transmits data.                                                               |

| Note 4           | A procedure that enables bus control by only one master device when multiple masters attempt to control simultaneously, ensuring that messages are not lost and contents not changed. |

| Note 5           | This feature allows several masters to control the bus simultaneously without losing messages.                                                                                        |

# 1.2 I<sup>2</sup>C Bus Mode Concept

With two wires (SDA and SCL), the I<sup>2</sup>C bus performs data transmission among devices connected to the bus. Each piece of equipment is recognized by its individual address and operated as either a transmitting or receiving device, according to the functions of the equipment. Master devices are those devices that transmit clock signals as they transmit data; slave devices are those devices that designate addresses in response to one or several masters.

When master devices transfer data, the master transmits a clock signal to obtain the data transmission timing and designates the slave address (transmission). The transmitting device then transmits data to the receiving device; data transmission is ended by the master. A clock signal is always generated by the master with the I<sup>2</sup>C bus, so each master generates its own clock signal whenever data exchanges take place at the bus. If the clock signal generated by the master is a for a low-speed slave device that maintains the SCL at "low", then the bus may change to another master during communications coordination procedures. (Refer to 1.4, "Coordinating Procedures Using SCL Synchronization" and "SCL Synchronization".)

Both the SDA and SCL are two-way lines that are connected to the positive power source through parallel resistance. When the bus is free, both lines are put into "high" status. Since the output levels of the devices connected to the bus execute AND connection functions, either an open drain or an open collector are needed. \*

\* The SDA and SCL output terminals of the M16C/62 are N-channel open drain output.

# 1.3 Data Transmission

The  $\mathsf{I}^2\mathsf{C}$  bus data transmission format is defined as follows:

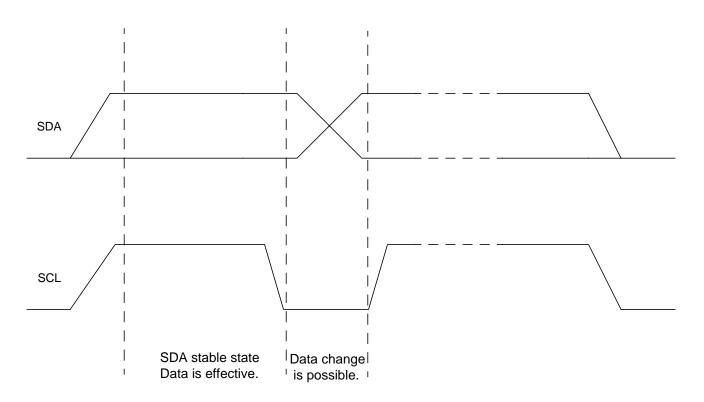

Data effectiveness - SDA status between the SCL highs must remain constant. Changes in SDA level are limited to when the SCL is low.

#### 1.3 Data Transmission

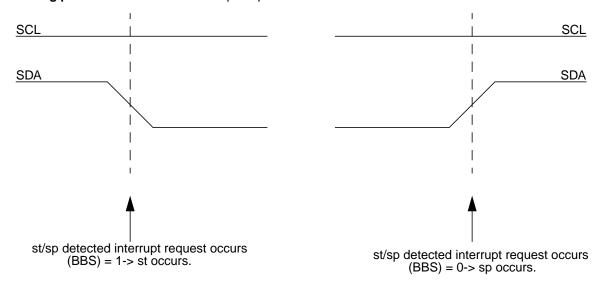

#### **Start and Stop Conditions**

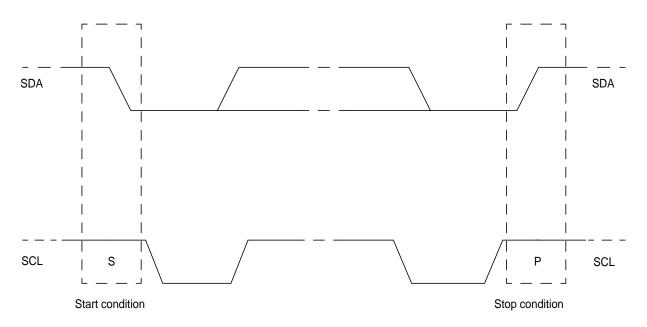

In  $I^2C$  bus communications procedures, data transmission begins with the transmitting of a start condition by the master; data transmission stops with the transmitting of a stop condition.

When the SCL is high, the situation where the SDA changes from high to low is called a start condition.<sup>1</sup> The situation where the SDA changes from low to high is called a stop condition.<sup>2</sup>

Other than start and stop conditions, the SDA level does not change when the SCL is high.

Both start and stop conditions are always generated by the master. The bus goes into busy status after a start condition is generated. The bus goes into free status after a stop condition is generated.<sup>3</sup>

- <sup>1</sup> The M16C/62 simple I<sup>2</sup>C bus mode has a "start condition detection interrupt" designed to detect start conditions. (Refer to Section 3.2, "Start/Stop Condition Detection".)

- <sup>2</sup> The M16C/62 simple I<sup>2</sup>C bus mode has a "stop condition detection interrupt" designed to detect stop conditions. (Refer to Section 3.2, "Start/Stop Condition Detection".)

- <sup>3</sup> The M16C/62 simple I<sup>2</sup>C bus mode has a "bus busy" flag indicating the condition of the bus. (Refer to Section 3.2, "Bus Busy Detection".)

M16C/62 Specification (ABB)

#### **Byte Format**

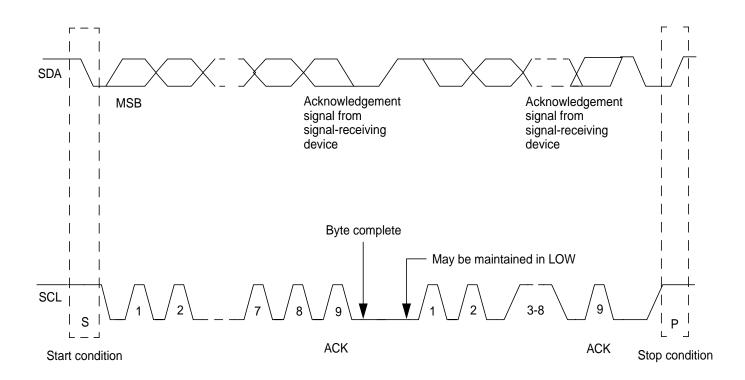

The length of each byte of the data output by the SDA must be eight bits. There is no limit to the number of bytes that can be sent in one transmission (from the time a start condition is generated to the time a stop condition is generated. Any number of bytes can be sent continuously. Data is sent in sequence from the uppermost bit (MSB) and an acknowledge bit is attached after each byte (the ninth bit).

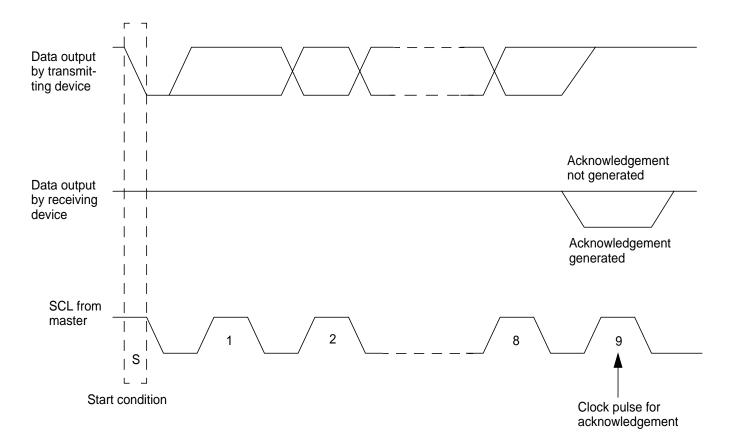

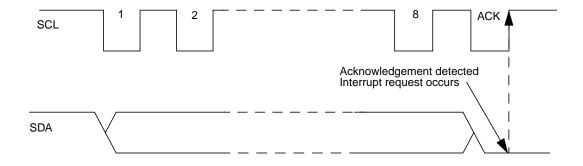

#### Acknowledge

Acknowledgements are needed in data transmission. The clock signal for acknowledgements are generated by the master in the SCL. When the clock signal for acknowledgement (the ninth bit) is generated, the SDA is released on the transmitting device end (high status). When the acknowledgement clock signal rises at each receiving device, an acknowledgement signal is generated because the SDA remains in a stable low status.<sup>1</sup>

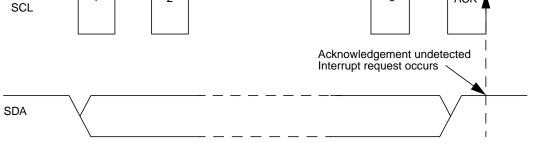

Receiving devices that have had addresses designated must ordinarily generate acknowledgements whenever the completion of each byte is received. If the slave receiver device does not confirm the address, the slave maintains the SDA in high status when the acknowledgement signal rises and does not generate an acknowledgement signal.2 At this time, the master transmits a stop condition and data transmission can be halted. When data cannot be received during a transmission, even if the slave receiving device has confirmed the address, the condition is indicated by the fact that an acknowledgement is not generated. At this time, the slave maintains the SDA in high status and the master generates a stop condition.

When the master becomes a receiving device, it informs the slave transmitting device of the end of the data by not generating an acknowledgement for the last data byte transmitted from the slave. At this time, the slave transmitting device releases the SDA and the master is able to generate a stop condition.,

- <sup>1</sup> The M16C/62 simple I<sup>2</sup>C bus mode has an "acknowledgement detected" interrupt to detect acknowledgement generation conditions. (Refer to Section 3.3, "Acknowledgement Detection".)

- <sup>2</sup> The M16C/62 simple I<sup>2</sup>C bus mode has an "acknowledgement not detected" interrupt to detect when acknowledgements have not been generated. (Refer to Section 3.3, "Acknowledgement Detection".)

## 1.4 Communication Coordination

Communication is performed according to the following procedures for communications among several devices connected through one  $I^2C$  bus.

#### **Communication Enabling Procedures**

The master can only start data transmission when the bus is in a free condition. However, since the  $I^2C$  is a multi-master bus, there are situations in which two or more masters generate a start condition at precisely the same time. Communication enabling procedures exist to prevent confusion when this occurs. These procedures are performed by using the SDA and the AND feature of each device's open drain or the open collector output terminal.

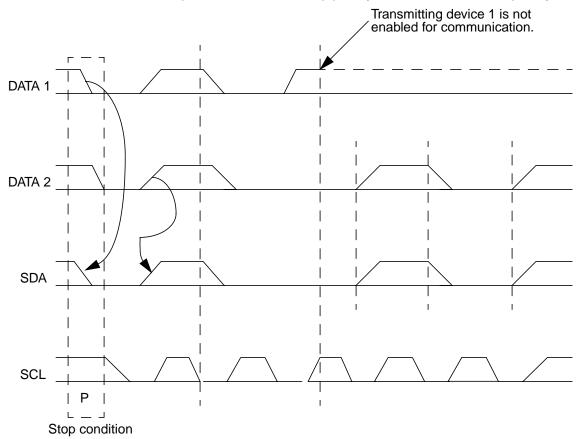

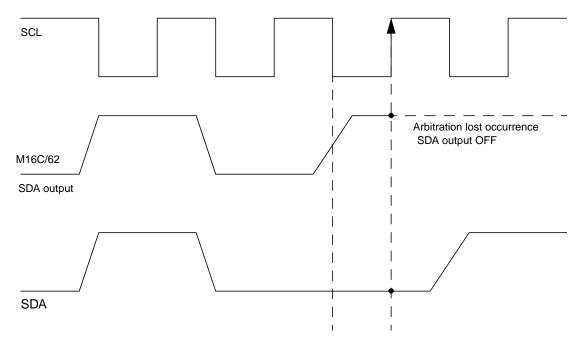

When the SCL is at a high level, masters that are transmitting to the SDA at a high level turn the data output level off, determining that communcation is not enabled when a low SDA level (when an arbitration loss occurs) is detected (since other masters are transmitting with the SDA at a low level.)<sup>1</sup> In this way, communication enabling procedures are executed through the SDA if several masters attempt to transmit their own data. Simultaneous transmissions limit the master that can actually transmit data to another device. The masters that do not receive enabling are immediately switched over to slave signal-receiving mode if they have slave capabilities. The clock signal can be generated until the end of the byte that made the determination not to grant communication enabling is shut off.

The diagram below shows the communication enabling procedures that take place between two masters. When the internal data level and actual SDA levels are different in the master-generating DATA1, the master's data output is turned off. Thus the data transmission that was started by the master that was given communication enabling is not affected in any way. These procdures are used only when many masters start at the same time; the procedures do not set up priority masters or an order of priority.

<sup>1</sup> The M16C/62 simple I<sup>2</sup>C bus mode has a function that detects disparities between internal data levels and the SDA levels timed to the SCL rise (refer to Section 3.5, "Arbitration Loss Detection Function") and a function for turning output level output off (refer to Section 3.5, "SDA Output Prohibition Function when Arbitration Loss Occurs").

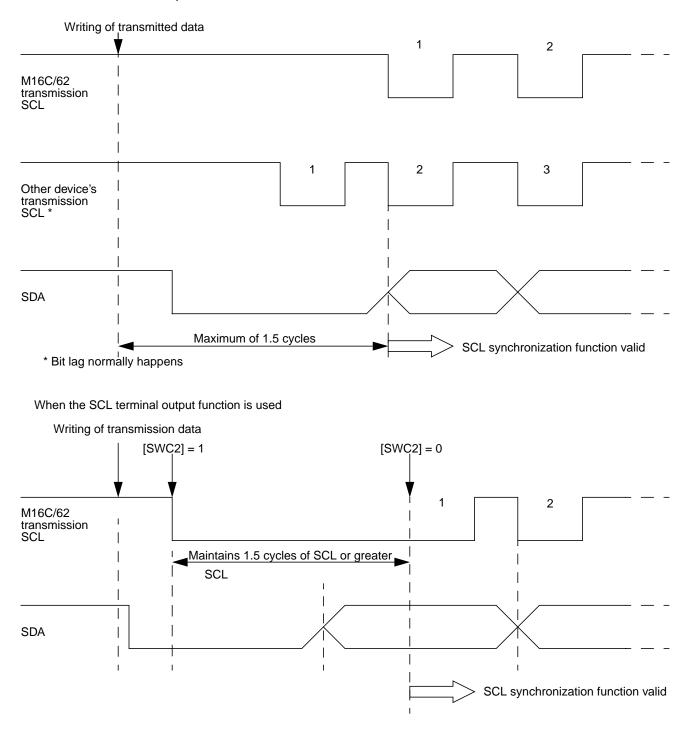

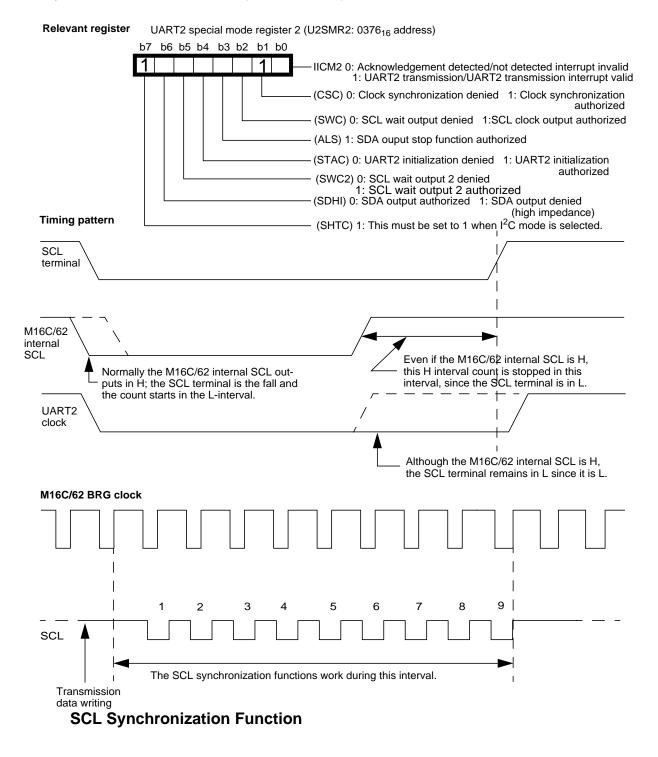

## **SCL Synchronization**

#### The M30622 chip does not have a register for $l^2C$ and does not operate in multimaster environments.

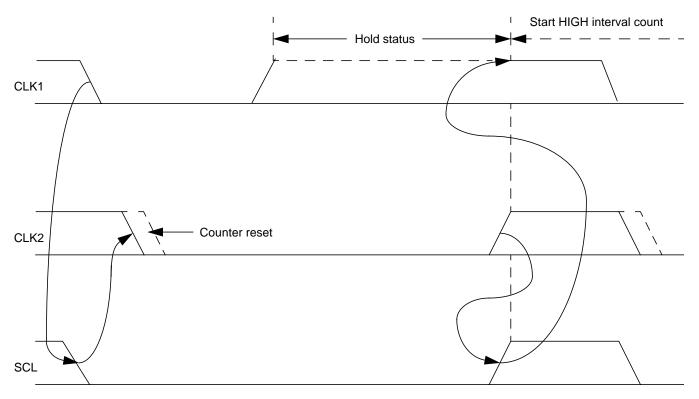

The SCL has procedures to enable communication when several masters attempt to start data transmission at the same time. A clock signal is output until the last byte for masters where communication is not enabled and when arbitration is lost, but among the masters that are each generating their own clock signals occurring at the bus.

Synchronization of the different clock signals can be performed using the SCL and the AND feature of the open drain output or open collector output terminals of each device. If the clock signal of a device is low, the low interval count is started while the SCL is maintained in low. Even if the low interval of the device ends and the clock signal goes from low to high, the SCL does not change if the clock signals of other devices remain in the low interval. The duration of the low interval is actually determined by the device with the longest low interval. During this interval, the clock signal remains high for devices with the shorter low interval (remaining in high-impedance state).

When all the devices finish the low interval, the clock signal is released and the system goes into high interval. The clock signals output by the devices and the SCL are now in the same status and counting begins for the high intervals of each device. The SCL reverts to low status according to the device that first finishes its high interval.

The low interval is determined by the device that has the longest low interval, while the high interval is determined by the device with the shortest high interval, thereby synchronizing the SCL.

<sup>1</sup> The M16C/62 simple I<sup>2</sup>C bus mode has an "SCL Synchronization" function to obtain SCL synchronization. (Refer to Section 3.5, "SCL Synchronization Function.")

## 1.5 Definition of First Byte

In the I<sup>2</sup>C bus, the first byte sent after a start condition contains important data which designates the slave. The following is the definition of the first byte.

#### 7-bit Address Format

In the I<sup>2</sup>C bus, the address with which the master selects the slave is determined by the first byte continuing from the start condition. The following description is an explanation of the seven-bit address format.

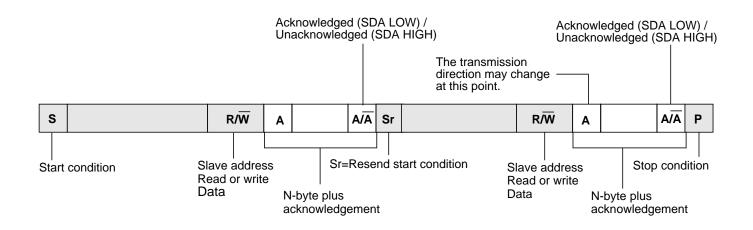

The schematic below shows the data transmission format. The slave address is sent after the start condition (S). This address consists of seven bits, with the eighth bit constituting the data direction bit (R/W). Transmitting to the slave is indicated if this data direction bit is 0; a data request to the slave is indicated if the bit is 1. However, a retransmit start condition (SR) is generated without first generating a stop condition and another address can be designated with the next byte if the master wants to continue communication at the bus. In this case, the slave address is sent with the seventh bit after the retransmit start condition, with the eighth bit serving as the data direction bit (R/W).

## 1.5 Definition of First Byte

## Definitions of Each Bit of the First Byte

After the start condition, the first seven bits of the first byte show the slave address. The eighth bit is the data direction bit (R/W), the bit which determines the direction of the message.

When the address is sent, and after the start condition, each device in the system compares the first seven bits with their own individual addresses. When the addresses agree, the device understands that it has been designated as a slave by the master and puts the SDA line in low in time with the nineth bit clock pulse, returns an acknowledgement signal, and performs data reception (data direction bit "W") or transmitting (data direction bit "R").

The M16C/62 simple I<sup>2</sup>C bus mode has a function that puts the master into standby mode until the address determination processing and acknowledgement transmitting can be completed.

## 1.6 Standard Mode and High-Speed Mode

\*

You can set 7-bit addresses in the standard mode of the  $I^2C$  bus at a maximum data transmitting rate of 100 kilobits/second. By increasing from standard to high-speed mode, 7-bit addresses as well as 10-bit addresses can be set with data transmitting rates of up to 400 kilobits/second. All new devices which have  $I^2C$  bus interfaces can handle high-speed mode.

The M16C/62 simple I<sup>2</sup>C bus mode also supports high-speed mode, with the exception of some restricted items. (Refer to Chapter 4, "Precautions Concerning the Simple I<sup>2</sup>C Bus Mode"). Note,however,that address transmitting and receiving is performed by software. (Refer to "Example of Auto Address Determination".)

# 1.7 I<sup>2</sup>C Bus SDA and SCL Bus Line Characteristics

The following table presents the I<sup>2</sup>C bus standard and high-speed mode electrical characteristics and the SDA and SCA bus line definitions:

| Parameters                                                     | Symbol           | Standar            | d Mode             | High-Spee                           | d Mode             | Units |

|----------------------------------------------------------------|------------------|--------------------|--------------------|-------------------------------------|--------------------|-------|

|                                                                | -                | Min.               | Max.               | Min.                                | Max.               |       |

| Low level input voltage:                                       |                  |                    |                    |                                     |                    |       |

| When input level is constant                                   | V <sub>IL</sub>  | -0.5               | 1.5                | -0.5                                | 1.5                | V     |

| When input level varies according to                           |                  | -0.5               | 0.3V <sub>DD</sub> | -0.5                                | 0.3V <sub>DD</sub> |       |

| V <sub>DD</sub>                                                |                  |                    |                    |                                     |                    |       |

| High level input voltage:                                      |                  |                    |                    |                                     |                    |       |

| When input level is constant                                   | V <sub>IH</sub>  | 3.0                |                    | 3.0                                 |                    | V     |

| When input level varies according to                           |                  | 0.7V <sub>DD</sub> | (1)                | 0.7V <sub>DD</sub>                  | (1)                |       |

| V <sub>DD</sub>                                                |                  |                    | (1)                |                                     | (1)                |       |

| Input hysteresis is a Schmidt trigger:                         |                  |                    |                    |                                     |                    |       |

| When input level is constant                                   | V <sub>hys</sub> | n/a                | n/a                | 0.2                                 |                    | V     |

| When input level varies according to                           | ,                | n/a                | n/a                | 0.05V <sub>DD</sub>                 |                    |       |

| V <sub>DD</sub>                                                |                  |                    |                    |                                     |                    |       |

| Spike pulse width controlled by input                          | t <sub>SP</sub>  | n/a                | n/a                | 0                                   | 50                 | ns    |

| filter                                                         |                  |                    |                    |                                     |                    |       |

| Low level output voltage (open drain or                        |                  |                    |                    |                                     |                    |       |

| open collector:                                                |                  |                    |                    |                                     |                    |       |

| When sink current is 3mA                                       | V <sub>OL1</sub> | 0                  | 0.4                | 0                                   | 0.4                | V     |

| When sink current is 6mA                                       | V <sub>OL2</sub> | n/a                | n/a                | 0                                   | 0.6                |       |

| Output fall time from V <sub>Ihmin</sub> to V <sub>Ilmax</sub> |                  |                    |                    |                                     |                    |       |

| when the bus capacitance is from                               |                  |                    |                    |                                     |                    |       |

| 10pF to 400pF (up to maximum 6mA                               | t <sub>OF</sub>  |                    |                    |                                     |                    | ns    |

| through $V_{OL2}$ parallel resistance):                        | -OF              |                    |                    |                                     |                    | ne    |

|                                                                |                  |                    | 050(2)             | 00,040 (2)                          | 250                |       |

| Maximum sink current 3mA at V <sub>OL1</sub>                   |                  | n/a                | 250 <sup>(2)</sup> | 20+0.1C <sub>b</sub> <sup>(2)</sup> |                    |       |

| Maximum sink current 6mA at V <sub>OL2</sub>                   |                  | n/a                | n/a                | 20+0.1C <sub>b</sub> <sup>(2)</sup> | 250 <sup>(3)</sup> |       |

| Input current at each VO pin when                              |                  |                    |                    | -                                   |                    |       |

| input current is 0.4 V~ 0.9 $V_{DDmax}$ .                      | li               | -10                | 10                 | -10 <sup>(3)</sup>                  | 10 <sup>(3)</sup>  | μa    |

| Capacitance of each VO pin                                     | Ci               |                    | 10                 |                                     | 10                 | pF    |

#### **Electrical Characteristics**

n/a = not applicable

**Note 1**  $Max V_{IH} = V_{DD} " 0.5V.$

Note 2 Cb = Capacitance (units: pF) of 1 bus line. The maximum  $t_F$  of the SDA and SCL bus lines (200 ns) greater than the maximum  $t_{OF}$  (250ns) at the output step.

Thus, a series protector resistor ( $R_S$ ) can be connected between the SDA/SCL pins and the SDA/SCL bus line without exceeding the maximum rated  $I_F$ .

Note 3 There can be no interference by the I/O pin with the SDA and the SCL lines when the V<sub>DD</sub> supply is cut.

**Related Note:** The electrical properties of the M16C/62 are different from the standards for the I<sup>2</sup>C bus. (Refer to 4.1, "Electrical Characteristics".)

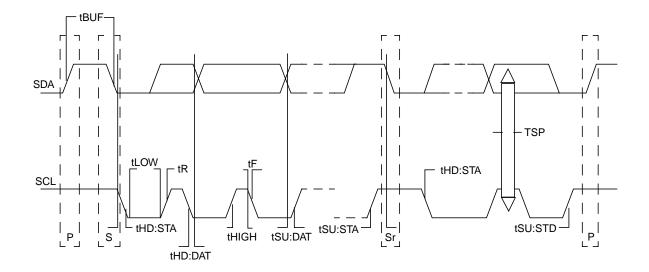

## **Timing Definitions**

| Parameters                                                                            | Symbol              | Standard I <sup>2</sup> C Mode Bus |      | High-Speed Standard<br>I <sup>2</sup> C Mode Bus |               | Units  |

|---------------------------------------------------------------------------------------|---------------------|------------------------------------|------|--------------------------------------------------|---------------|--------|

|                                                                                       |                     | Min.                               | Max. | Min.                                             | Max.          |        |

| SCL clock frequency                                                                   | f <sub>SCL</sub>    | 0                                  | 100  | 0                                                | 400           | KHz    |

| Bus free time between start and stop conditions                                       | t <sub>BUF</sub>    | 4.7                                |      | 1.3                                              |               | μ secs |

| Hold time (retransmit) "start". Initial clock pulse<br>generated after this interval. | <sup>t</sup> HDSTA  | 4.0                                |      | 0.6                                              |               | μ secs |

| SCL clock "low"status hold time                                                       | t <sub>LOW</sub>    | 4.7                                |      | 1.3                                              |               | μ secs |

| SCL clock "high" status hold time                                                     | t <sub>HIGH</sub>   | 4.0                                |      | 0.6                                              |               | μ secs |

| Retransmit "start" condition setup time                                               | t <sub>SU-STA</sub> | 4.7                                |      | 0.6                                              |               | μ secs |

| Data hold time:<br>For the CBUS compatibility master (see 9.3,<br>"Precautions")      | t <sub>HD-DAT</sub> | 5.0                                |      |                                                  |               | μ secs |

| For the I <sup>2</sup> C bus                                                          |                     | 0<br>Note 1                        |      | 0<br>Note 1                                      | 0.9<br>Note 2 | μ secs |

| Data setup time                                                                       | t <sub>SU-DAT</sub> | 250                                |      | 100<br>Note 3                                    |               | n secs |

| SDA and SCL signal rise times                                                         | t <sub>R</sub>      |                                    | 1000 | 20 + 0.1<br>C <sub>b</sub><br>Note 4             | 300           | n secs |

| SDA and SCL signal fall times                                                         | t <sub>F</sub>      |                                    | 300  | 20 + 0.1<br>C <sub>b</sub><br>Note 4             | 300           | n secs |

| "Stop" condition setup time                                                           | t <sub>SU-STD</sub> | 4.0                                |      | 0.6                                              |               | μ secs |

| Load capacity of each bus line                                                        | Cb                  |                                    | 400  |                                                  | 400           | pF     |

The above values all correspond to  $V_{IH max}$  or  $V_{IL min}$  levels.

Note 1 To fill the undefined region of the SCL fall end, a 300-ns minimum hold time for the SDA signal (at SCL signal V<sub>IH min</sub>) must be provided internally.

- Note 2 When the device does not extend the SCL signal "low" (t<sub>LOW</sub>) hold time, only the maximum data hold time t<sub>HD:DAT</sub> must be met.

- **Note 3** Although the high-speed mode of the  $I^2C$  bus can be used in the standard mode  $I^2C$  bus system,  $t_{SU:DAT}>250$ ns is a condition that must be satisfied. If the device does not extend the SCL signal's "low" (tLOW) hold time, the satisfaction of this condition is requested to be a non-condition. If the device does extend the SCL signal's "low status hold time, the following data bits need to be sent to the SDA line before t <sub>Rmax.</sub> +  $t_{su:dat} = 1000 + 250 = 1250$  nx, releasing the SCL line (according to specifications of standard  $I^2C$  mode bus.

**Note 5** The electrical properties of the M16C/62 are different from the standards for the I<sup>2</sup>C bus. Refer to 4.1, "Electrical Characteristics".

**Note 4** C<sub>b</sub> = 1 bus line total capacitance (units: pF)

## Chapter 2. M16C/62 UART2 Functions

The M16C/62 serial I/O consists of five channels, UART0, UART1, UART2, as well as S I/O3 and S I/O4. Each of these channels has its own timer for generating dedicated transmitting clocks, and these timers function independently. In this chapter, we discuss detailed settings for the simple  $I^2C$  bus mode, which is one of the UART2.

|     | Chapter 2 Section Title                                                          |

|-----|----------------------------------------------------------------------------------|

| 2.1 | Functions of the UART2                                                           |

| 2.2 | Block Diagram of the Simple I <sup>2</sup> C Bus Mode                            |

| 2.3 | Terminal Functions That Change in I <sup>2</sup> C Bus Mode and Interrupt Causes |

| 2.4 | Register Setup When in Simple I <sup>2</sup> C Bus Mode                          |

## 2.1 Functions of the UART2

With the exception of some different functions, the functions of the UART0~ UART2 channels are essentially the same. Of these channels, UART2 in particular makes use of modes which can handle a SIM interface, an IE bus interface, and an  $I^2C$  bus interface.

UART0~ UART2 make selective use of either a clock synchronization-type serial I/O mode or a clock non-synchronization-type serial I/O mode.

The clock non-synchronization-type serial I/O mode in particular can handle an IE bus interface and a SIM interface. The M16C/62 has a serial data switching function and a bus collision detection function in order to enable IE bus interface and SIM interface. See the M16C/62 data sheets for detailed information about these functions.

Further, the UART2 clock synchronization-type serial I/O mode makes it possible to handle the I<sup>2</sup>C bus interface.

In this chapter, we present the M16C/62 simple  $I^2C$  bus mode block diagrams and each type of relevant register. In the next chapter, we discuss the functions needed to make the  $I^2C$  bus interface work with the M16C/62.

The IE bus interface, SIM interface, and  $I^2C$  bus interface are the functions which are limited to UART2.

M16C/62 serial I/O configuration:

| UART0          | Clock synchronization-type serial I/O     |

|----------------|-------------------------------------------|

|                | Clock non-synchronization-type serial I/O |

| UART1          | Clock synchronization-type serial I/O     |

|                | Clock non-synchronization-type serial I/O |

| UART2          | Clock synchronization-type serial I/O     |

|                | For the I <sup>2</sup> C bus interface    |

| non-synchroniz | zation-type serial I/O                    |

|                | For the IE bus interface                  |

|                | For the SIM interface                     |

- S I/O3 Clock synchronization-type serial I/O

- S I/O4 Clock non-synchronization-type serial I/O

Clock

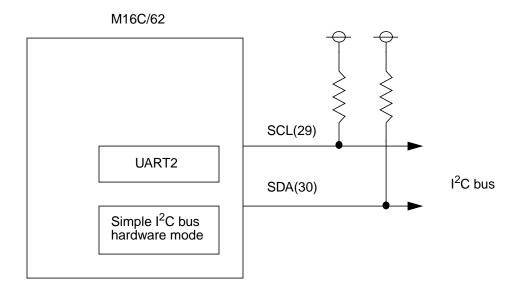

# 2.2 Block Diagram of the Simple I<sup>2</sup>C Bus Mode

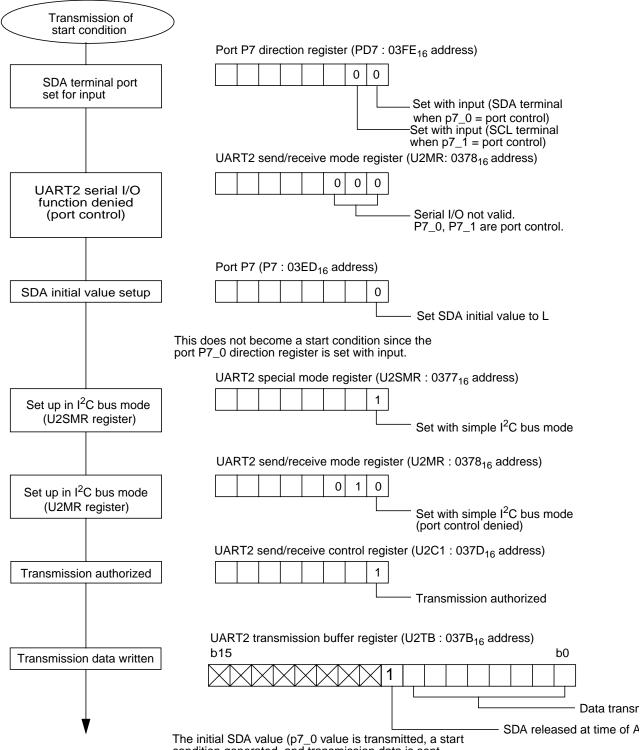

The M16C/62 simple I<sup>2</sup>C bus mode is used to enable the I<sup>2</sup>C bus interface. The simple I<sup>2</sup>C bus mode effectuates the circuit for the I<sup>2</sup>C bus interface by setting the I<sup>2</sup>C selector bit (IICM) to "1."

The following is the  $I^2C$  bus mode block diagram.

# 2.3 Terminal Functions That Change in I<sup>2</sup>C Bus Mode and Interrupt Causes

The M16C/62 simple  $I^2C$  bus mode is put into effect by setting the  $I^2C$  mode selector bit (IICM). The following tables show each function when the simple  $I^2C$  bus mode is selected.

|                           | (IICM) =1 (Simple I <sup>2</sup> C bus mode) | (IICM) = 0 (Common S I/O mode)     |

|---------------------------|----------------------------------------------|------------------------------------|

| P7_0 terminal function    | SDA (input/output)                           | TxD2 (output)                      |

| P7_0 output initial value | Set value in P7_0 when the serial I/O is     | Hlevel                             |

|                           | not valid                                    |                                    |

| P7_1 terminal function    | SCL (input/output)                           | RxD1 (input)                       |

| P7_1 terminal read        | The terminal reads, regardless of the        | In accordance with the directional |

|                           | directional register                         | register settings                  |

| P7_2 terminal function    | Port P7_2                                    | CLK2                               |

#### **Terminal Functions**

#### Main Interrupt Causes

|                                          | (IICM) = 1 (Simple I <sup>2</sup> C bus mode) |                 | (IICM) = 0 (Common S I/<br>O mode) |  |

|------------------------------------------|-----------------------------------------------|-----------------|------------------------------------|--|

|                                          | (IICM2) = 0                                   | (IICM2) = 0     |                                    |  |

| Cause: interrupt no. 10                  |                                               | dition detected | Bus collision detected             |  |

| Cause: interrupt no. 15                  | Acknowledge not UART2 transmission            |                 | UART2 transmission                 |  |

|                                          | detected                                      |                 |                                    |  |

| Cause: interrupt no. 16                  | Acknowledge detected                          | UART2 reception | UART2 reception                    |  |

| DMA1 cause when the Acknowledge detected |                                               | UART2 reception | UART2 reception                    |  |

| DMA request factor                       | _                                             |                 |                                    |  |

| selector bit = "1101"                    |                                               |                 |                                    |  |

#### Precautions concerning bit processing commands for the port:

When the input/output port data register (port latch), is rewritten using bit processing commands, the bits which do not have values designated for them may change.

#### Reason:

Bit processing commands are read-modify-write commands which perform reading and writing in bit units. Therefore, when these commands are executed in relation to certain bits of the input/output ports of the data register, the following processing takes place in relation to the entire data register:

Bits set with input The terminal value is read by the CPU, and this bit is read in after bit processing. Bits for which values have been set

The data register bit values are read by the CPU, and these bits are written in after bit processing.

\* Please note that the SCL and SDA output values may be changed when read-modify-write commands are executed for port P7.

# 2.4 Register Setup When in Simple I<sup>2</sup>C Bus Mode

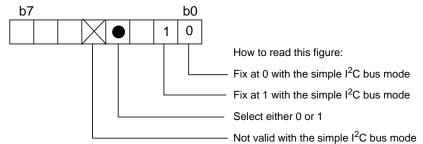

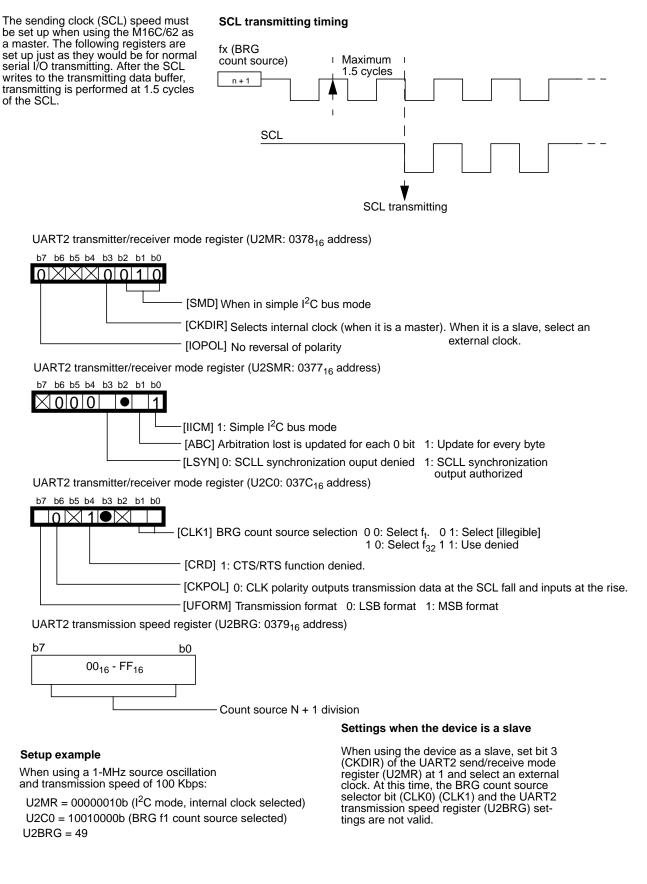

Registered are configured as follows when using the simple I<sup>2</sup>C bus mode in the M16C/62 UART2: UART2-relevant register

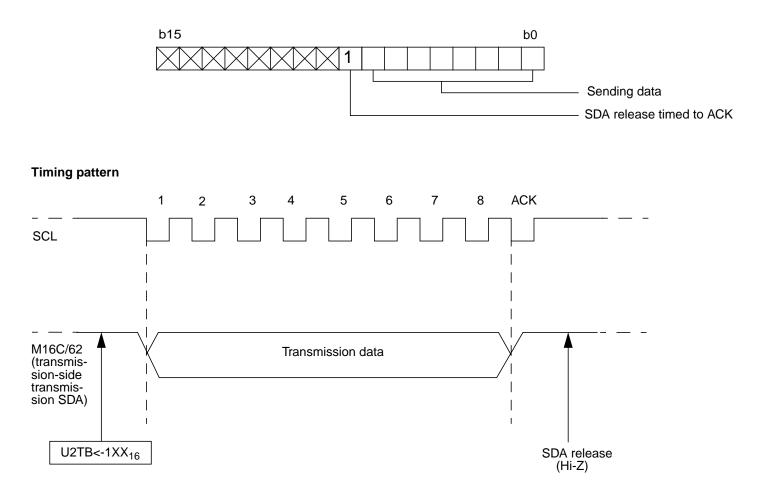

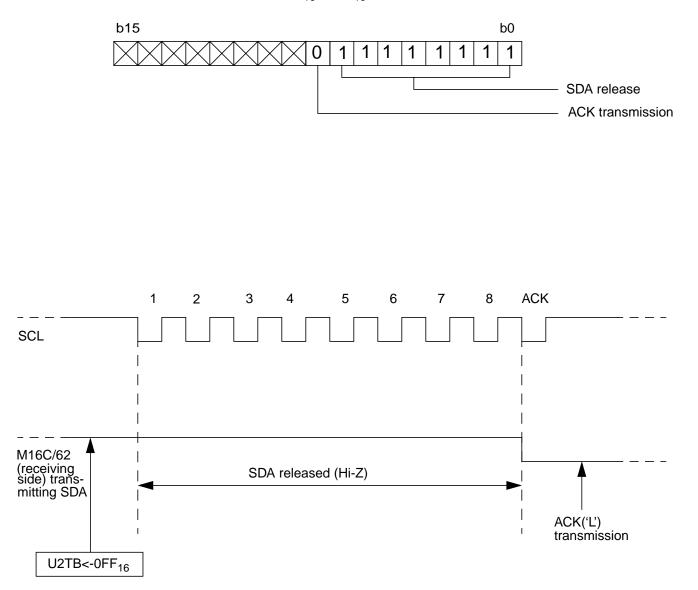

| UART2 transmitting buffer register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Function                                  | Values that can be set                                               | R | w |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|---|---|

| (b15)<br>(b15)<br>(b15)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b10)<br>(b | Symbol = U2TB Address                     | = 037B <sub>16</sub> , 037E <sub>16</sub> <b>At reset</b> = Undefine |   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Transmitting data (bit 8 is ACK)          | 00 <sub>16</sub> ~ FF <sub>16</sub>                                  | x | 0 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Nothing located here. Put in 0 wher readi | 0                                                                    |   |   |

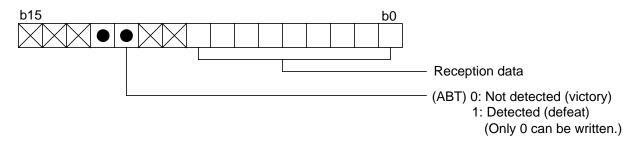

| UART2 reception buffer register | Bit                                                                           | Bit Name                             | Function                                           | R     | w    |

|---------------------------------|-------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|-------|------|

|                                 | Symbol =                                                                      | : U2RB Address =                     | 037F <sub>16</sub> , 037E <sub>16</sub> At reset = | Undef | ined |

|                                 |                                                                               |                                      | Reception data                                     | 0     | x    |

|                                 | Nothing located here. Put in 0 when writing. Value is undefined when reading. |                                      |                                                    |       |      |

|                                 | ABT                                                                           | Arbitration lost detec-<br>tion flag | 0: Not detected (success)<br>1: Detected (defeat)  | 0     | 0    |

|                                 | OER                                                                           | Overrun error flag                   | 0: No overrun<br>1: Overrun                        | 0     | х    |

|                                 | FER                                                                           | Framing error flag                   | Not valid in I <sup>2</sup> C bus mode             | 0     | х    |

|                                 | PER                                                                           | Parity error flag                    | Not valid in I <sup>2</sup> C bus mode             | 0     | х    |

|                                 | SUM                                                                           | Error sum flag                       | Not valid in I <sup>2</sup> C bus mode             | 0     | х    |

|                                 |                                                                               | L                                    | 1                                                  | 1     | 1    |

| UART2 transmitting speed register | Function                                                         | Values that can be set              |      | w     |

|-----------------------------------|------------------------------------------------------------------|-------------------------------------|------|-------|

| b7 b0                             | Symbol = U2BRG Addre                                             | ess = 0379 <sub>16</sub> At reset = | Unde | fined |

|                                   | If the set value is n, BRG2 will n+1<br>divide the count source. | 00 <sub>16</sub> ~ FF <sub>16</sub> | х    | 0     |

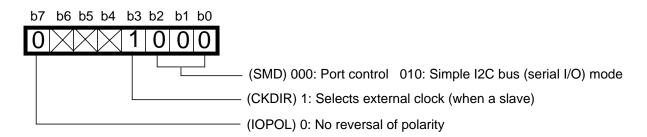

| UART2 transmit/receive mode register                   | Bit   | Bit Name                                        | Function                                                                                                              |                            | w  |

|--------------------------------------------------------|-------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------|----|

| b7 b6 b5 b4 b3 b2 b1 b0 $0 \times \times \times 0 1 0$ | Symbo | ol = U2MR Ad                                    | ldress = 0378 <sub>16</sub> At rese                                                                                   | <b>t =</b> 00 <sub>1</sub> | 16 |

|                                                        | SMD0  | Serial i/o mode                                 | b2=0 b1=0 b0=0: serial I/O not<br>valid (port control)<br>b2=0 b1=1 b0=0: simple I <sup>2</sup> C bus<br>mode         |                            | 0  |

|                                                        | SMD1  | selector bit                                    |                                                                                                                       |                            | 0  |

|                                                        | SMD2  |                                                 |                                                                                                                       |                            | 0  |

|                                                        | CKDIR | Internal clock<br>selector bit                  | <ul> <li>0: Internal clock<br/>(set at 0 when master)</li> <li>1: External clock<br/>(set at 1 when slave)</li> </ul> | 0                          | 0  |

|                                                        | STPS  | Stop bit length selector bit                    | Not valid in I <sup>2</sup> C bus mode                                                                                | 0                          | 0  |

|                                                        | PRY   | Parity odd/even selector bit                    | Not valid in I <sup>2</sup> C bus mode                                                                                | 0                          | 0  |

|                                                        | PRYE  | Parity authorization bit                        | Not valid in I <sup>2</sup> C bus mode                                                                                | 0                          | 0  |

|                                                        | IOPOL | TxD, RxD input/output<br>polarity switching bit | 0: Reversal 1: No reversal<br>(set at 0 when in I <sup>2</sup> C mode)                                                | 0                          | 0  |

| UART2 transmit/receive<br>control register 0 | Bit        | Bit Name                            | Function                                                                                                                                                                                                                               | R                 | w |

|----------------------------------------------|------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---|

| b7 b6 b5 b4 b3 b2 b1 b0                      | Symbo      | ol = U2C0 Add                       | iress = 037C <sub>16</sub> At reset                                                                                                                                                                                                    | = 08 <sub>1</sub> | 6 |

|                                              | CLK0       | BRG count source selector bit       | b1=0 b0=0: $f_1$ selected<br>b1=0 b0=1: $f_8$ selected<br>b1=1 b0=0: $f_{32}$ selected<br>b1=1 b0=1: Use is not permitted.                                                                                                             | 0                 | 0 |

|                                              | CLK1       |                                     |                                                                                                                                                                                                                                        | 0                 | 0 |

|                                              | CRS        | CTS/RTS function selector bit       | Not valid when bit 4=1                                                                                                                                                                                                                 | 0                 | 0 |

|                                              | TXEPT      | Transmitting register<br>blank flag | <ul><li>0: Data in transmitting register</li><li>1: No data in transmitting register</li></ul>                                                                                                                                         | 0                 | х |

|                                              | CRD        | CTS/RTS prohibition bit             | <ul> <li>0: CTS/RTS function allowed</li> <li>1: CTS/RTS function prohibited.</li> <li>(set at 1 when in I<sup>2</sup>C mode)</li> </ul>                                                                                               | 0                 | 0 |

|                                              | Nothing Ic | ocated here. Put in a 0 whe         | en writing. Value is 0 when reading.                                                                                                                                                                                                   |                   |   |

|                                              | CKPOL      | Clock polarity<br>selection bit     | <ol> <li>O: Transmitting data output at<br/>fall of transmitting clock and<br/>reception data output at rise.</li> <li>1: Transmitting data output at<br/>rise of transmitting clock and<br/>reception data output at fall.</li> </ol> | 0                 | 0 |

|                                              | UFORM      | Transmitting format selector bit    | 0: LSB format<br>1: MSB format                                                                                                                                                                                                         | 0                 | 0 |

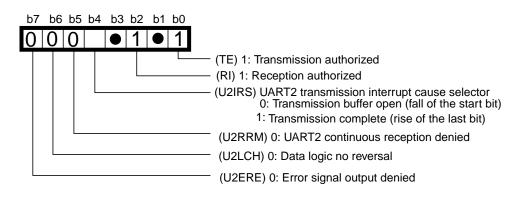

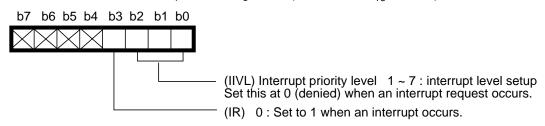

| UART2 transmit/receive<br>control register 1 | Bit   | Bit Name                                                                                                                 | Function                                                                                                             | R                  | w |

|----------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------|---|

| b7 b6 b5 b4 b3 b2 b1 b0                      | Symb  | ol = U2C1 Add                                                                                                            | Iress = 037D <sub>16</sub> At reset                                                                                  | = 02 <sub>16</sub> | 5 |

|                                              | TE    | Transmitting<br>authorization bit                                                                                        | 0: Transmitting denied<br>1: Transmitting authorized                                                                 | 0                  | 0 |

|                                              | TI    | Transmitting buffer open flag                                                                                            | <ul><li>0: Data in transmitting<br/>buffer register</li><li>1: No data in transmitting<br/>buffer register</li></ul> | 0                  | х |

|                                              | RE    | Reception authoriza-<br>tion bit                                                                                         | <ul><li>0: Reception denied</li><li>1: Reception authorized</li></ul>                                                | 0                  | 0 |

|                                              | RI    | Reception completed flag                                                                                                 | <ul><li>0: Data in transmitting<br/>buffer register</li><li>1: No data in transmitting<br/>buffer register</li></ul> | 0                  | х |

|                                              | U2IRS | UART2 transmit/<br>receive interrupt cause<br>selector bit (Note:<br>U2IRS is not valid<br>when (IICM)-1 and<br>(IICM2). | <ul> <li>0: Transmitting buffer open<br/>(TI=1)</li> <li>1: Transmitting complete<br/>(TXEPT=1)</li> </ul>           | 0                  | 0 |

|                                              | U2RRM | UART2 continuous<br>reception mode<br>authorization bit                                                                  | 0: UART2 clock 1: 0 output                                                                                           | 0                  | 0 |

|                                              | U2LCH | Data logic selector bit                                                                                                  | 0: No reversal 1: Reversal (set at 0 in simple I <sup>2</sup> C bus mode)                                            | 0                  | 0 |

|                                              | U2ERE | Error signal output authorization bit                                                                                    | Set at 0 in simple I <sup>2</sup> C bus mode.                                                                        | 0                  | 0 |

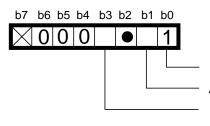

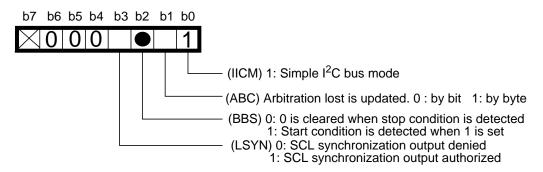

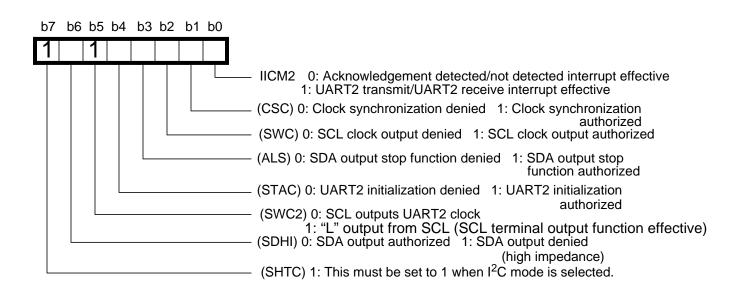

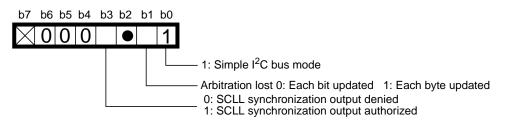

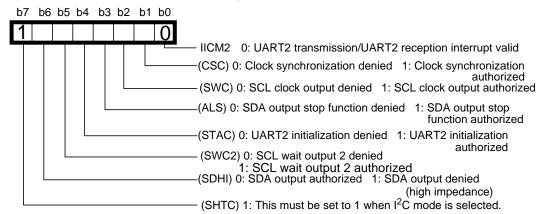

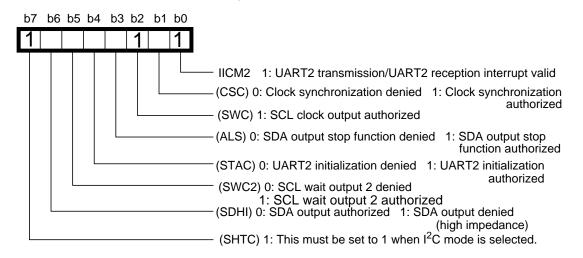

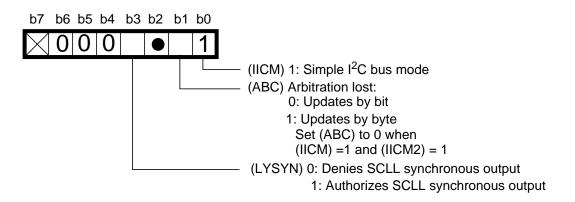

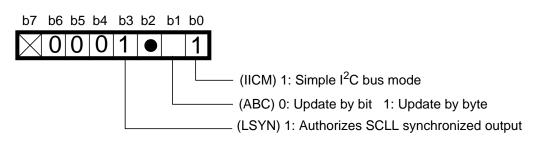

| UART2 special mode register                | Bit        | Bit Name                                                                                                                                        | Function                                                                 | R              | w  |

|--------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|----|

| b7 b6 b5 b4 b3 b2 b1 b0 $\times$ 0 0 0 0 1 | Symbo      | I = U2SMR A                                                                                                                                     | ddress = 0377 <sub>16</sub> At rese                                      | <b>≥t</b> = 00 | 16 |

|                                            | IICM       | I <sup>2</sup> C mode selector bit<br>(Note: Set serial I/O<br>mode selector bit at<br>0 1 0 when in simple<br>I <sup>2</sup> C mode.)          | 0: Normal mode<br>1: Simple I <sup>2</sup> C bus mode                    | 0              | 0  |

|                                            | ABC        | Arbitration lost detec-<br>tion flag control (Note:<br>Set at 0 when (IICM) -1<br>and (IICM2).                                                  | <ul><li>0: Update for each bit</li><li>1: Update for each byte</li></ul> | 0              | 0  |

|                                            | BBS        | Bus busy flag (can be written as 0)                                                                                                             | 0: Stop condition detected<br>1: Start condition detected                | 0              | 0  |

|                                            | LSYN       | SCLL synchronization<br>output authorization bit<br>(Note: Valid only when<br>in port control; this bit<br>is not valid when in<br>serial I/O). | 0: Denied<br>1: Authorized                                               | 0              | 0  |

|                                            | ABSCS      | Bus collision detection<br>sampling clock selec-<br>tor bit                                                                                     | Fix at 0.                                                                | 0              | 0  |

|                                            | ACSE       | Transmitting authoriza-<br>tion bit and automatic<br>clearing function selec-<br>tor bit                                                        | Fix at 0.                                                                | 0              | 0  |

|                                            | SSS        | Transmitting start condition selector bit                                                                                                       | Fix at 0.                                                                | 0              | 0  |

|                                            | Nothing lo | bcated here. Put in a 0 whe                                                                                                                     | n writing. Value is 0 when reading.                                      |                |    |

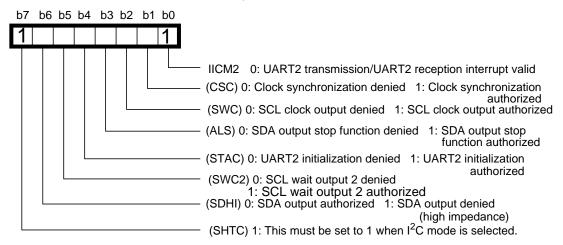

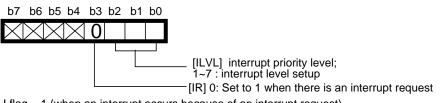

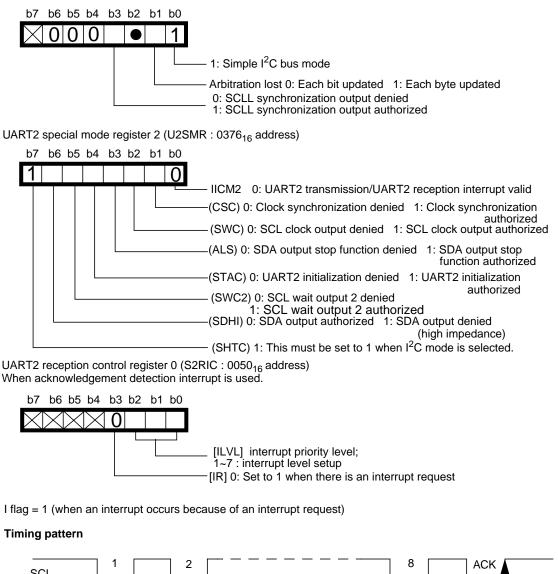

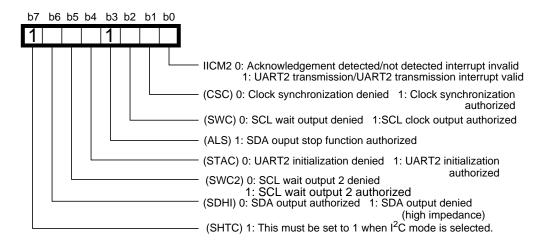

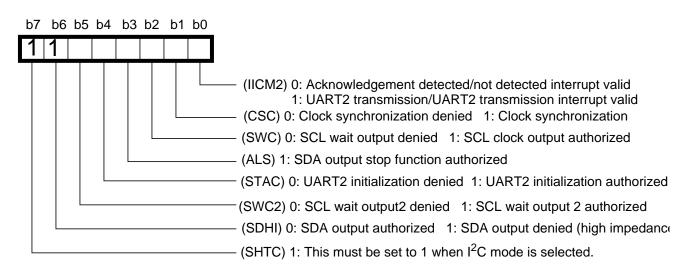

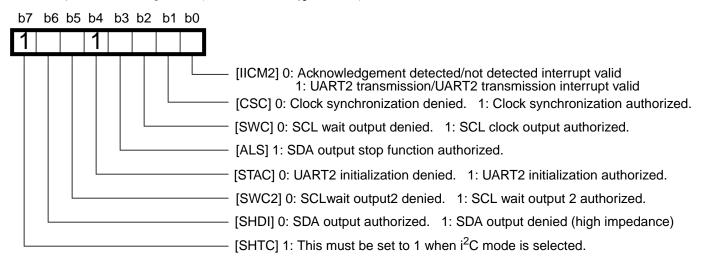

| UART2 special mode register 2 | Bit   | Bit Name                                   | Function                                                  | R | w       | Chapter<br>explain-<br>ing bits |

|-------------------------------|-------|--------------------------------------------|-----------------------------------------------------------|---|---------|---------------------------------|

| b7 b6 b5 b4 b3 b2 b1 b0       | Symb  | <b>ol =</b> U2SMR2                         | <b>Address =</b> 0376 <sub>16</sub>                       | ļ | At rese | et = 00 <sub>16</sub>           |

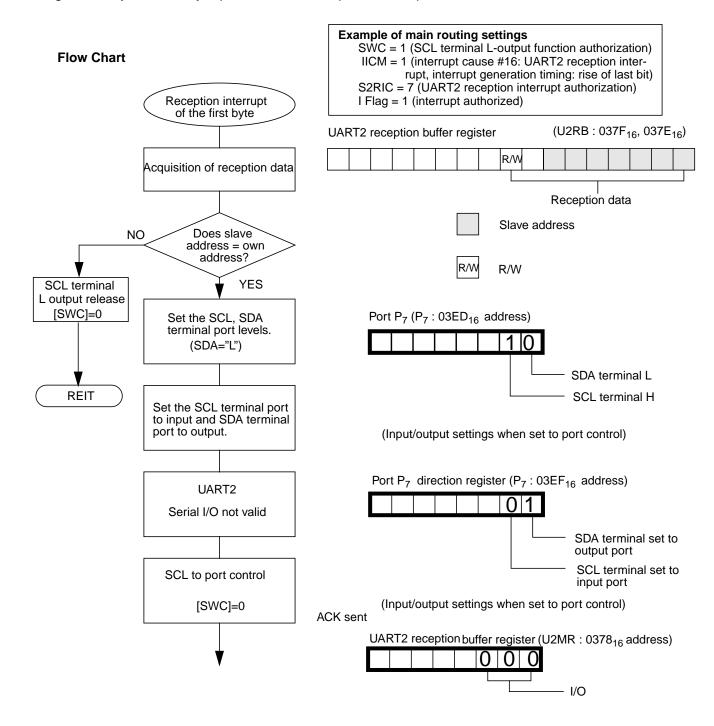

|                               | IICM2 | I <sup>2</sup> C mode selector bit         | See Table 1.                                              | 0 | 0       | 2.3                             |

|                               | CSC   | Clock synchronization bit                  | 0: Denied<br>1: Authorized                                | 0 | 0       | 3.5                             |

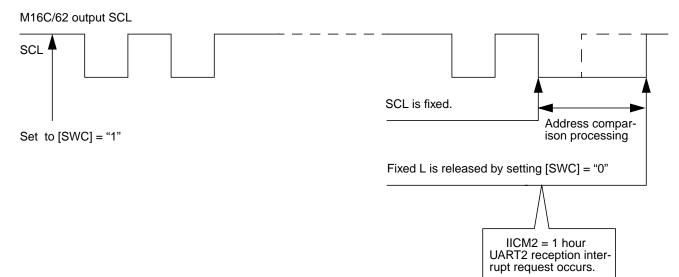

|                               | SWC   | SCL wait output bit                        | 0: Denied<br>1: Authorized                                | 0 | 0       | 3.4                             |

|                               | ALS   | SDA output stop bit                        | 0: Denied<br>1: Authorized                                | 0 | 0       | 3.5                             |

|                               | STAC  | UART2 initialization bit                   | 0: Denied<br>1: Authorized                                | 0 | 0       | 3.6                             |

|                               | SWC2  | SCL wait output bit 2                      | 0: UART2 clock<br>1: 0 output                             | 0 | 0       | 3.2                             |

|                               | SDHI  | SDA output prohibition<br>bit              | 0: Denied<br>1: Authorized (high<br>impedance)            | 0 | 0       | 3.6                             |

|                               | SHTC  | Start/stop condition control bit (Table 2) | 1: This must be set to<br>1 when in I <sup>2</sup> C mode | 0 | 0       |                                 |

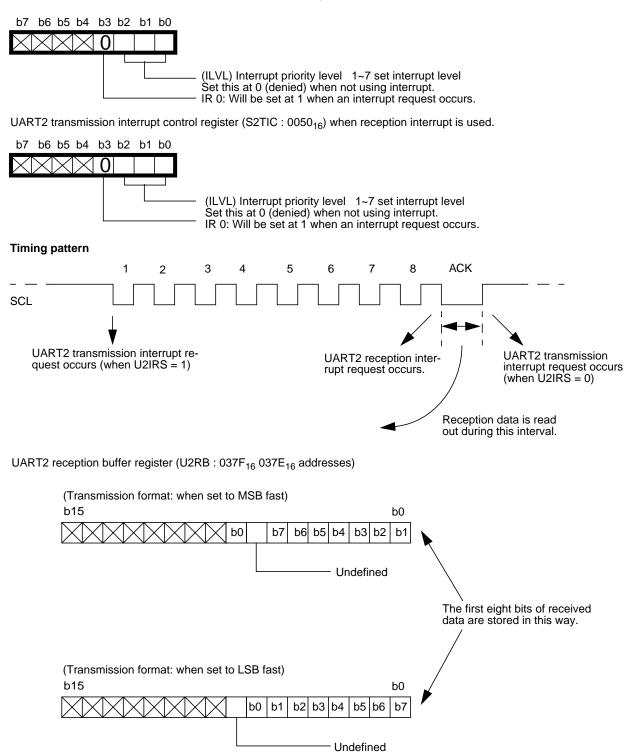

### Table 1

|   | Function                                                                              | IICM2 = 0                                                      | IICM2 = 1                                                           |

|---|---------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------|

| 1 | Interrupt signal cause 15                                                             | No acknowledgement detected (NACK)                             | UART2 transmitting (rise of the last bit of the transmitting clock) |

| 2 | Interrupt signal cause 16                                                             | Acknowledgement detected (ACK)                                 | UART2 reception (fall of the last bit of the reception clock)       |

| 3 | DMA cause when DMA request<br>cause selector bit = 1 1 0 1                            | Acknowledgement detected (ACK)                                 | UART2 reception (fall of the last bit of the reception clock)       |

| 4 | Timing of data transmitting from UART2 reception shift register to reception buffer   | Rise of last bit of reception clock                            | Fall of last bit of reception clock                                 |

| 5 | Timing of UART2 reception/acknowledge-<br>ment detection interrupt request generation | Rise of last bit of reception clock (acknowledgement detected) | Fall of last bit of reception clock (UART2 reception)               |

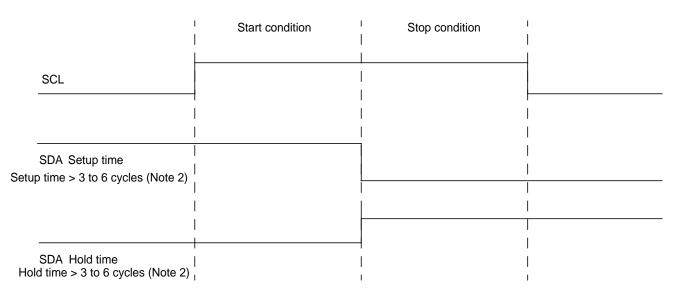

#### Table 2. Start/stop condition detection timing characteristics (Note 1)

## I Setup time Т Hold time SCL SDA Start condition

T

Note 1; When the start/stop condition control bit SHTC=1. Note 2: The number of cycles indicates the main clock in-put oscillation frequency (XIN) number of cycles.

3~6 cycles < setup time (Note 2)

3~6 cycles < hold time (Note 2)

SDA Stop condition

# Chapter 3 Functions of the Simple I<sup>2</sup>C Bus Mode

In this chapter, we discuss methods for using the hardware functions when the M16C/62 uses the simple  $I^2C$  bus mode to realize the  $I^2C$  bus interface.

|     | Chapter 3 Section Title                  |

|-----|------------------------------------------|

| 3.1 | Byte-Data Transmission/Reception Methods |

| 3.2 | Start/Stop Conditions                    |

| 3.3 | Acknowledgement                          |