# THEORY OF OPERATION

**OF**

# **DISPLAY SYSTEM**

**FOR**

AN/FSQ-7 COMBAT DIRECTION CENTRAL AND AN/FSQ-8 COMBAT CONTROL CENTRAL

#### VOLUME I

1 August 1958

This document contains information of a proprietary nature. Any use or reproduction of this document for other than government purposes is subject to the prior consent of International Business Machines Corporation.

MILITARY PRODUCTS DIVISION

INTERNATIONAL BUSINESS MACHINES CORPORATION

KINGSTON, NEW YORK

# Reproduction for non-military use of the information or illustrations contained in this publication is not permitted without specific approval of the issuing service (BuAer or USAF). The policy for use of classified publications is established for the Air Force in AFR 205-1 and for the Navy in Navy Regulations, Article 1509. LIST OF REVISED PAGES INSERT LATEST REVISED PAGES. DESTROY SUPERSEDED PAGES. NOTE: The portion of the text affected by the current revision is indicated by a vertical rule in the left margin of a left-hand page and in the right margin of a right-hand page.

\*The asterisk indicates pages revised, added or deleted by the current revision.

#### **CONTENTS**

| Head | ling    |                                                     | Page |

|------|---------|-----------------------------------------------------|------|

| PA   | RT 1    | INTRODUCTION                                        | 1    |

| C    | HAPTI   | ER 1 PURPOSE AND SCOPE OF MANUAL                    | 1    |

|      | 1.1     | Purpose                                             | 1    |

|      | 1.2     | Scope                                               | 1    |

|      | 1.2.1   | Scope of Equipment Differences                      | 1    |

|      | 1.2.2   | Division of Contents                                | 1    |

|      | 1.3     | Relationship to Other Manuals                       | 1    |

|      | 1.4     | List of Nomenclature                                | 1    |

| C    | HAPTI   | ER 2 DISPLAY SYSTEM IN THE AN/FSQ-7 AND AN/FSQ-8    | 17   |

|      | SECTIO  | ON 1 SCOPE                                          | 17   |

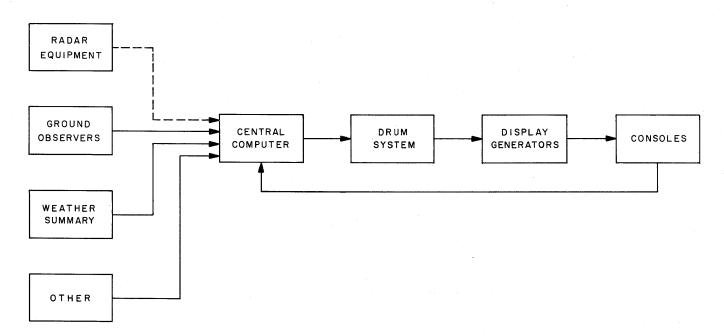

|      | 1.1     | Relation of Display System to AN/FSQ-7 and AN/FSQ-8 | 17   |

|      | 1.2     | Types of Displays                                   | 17   |

|      | 1.2.1   | Digital Display Elements                            | 18   |

|      | 1.2.2   | Situation Display Elements                          | 18   |

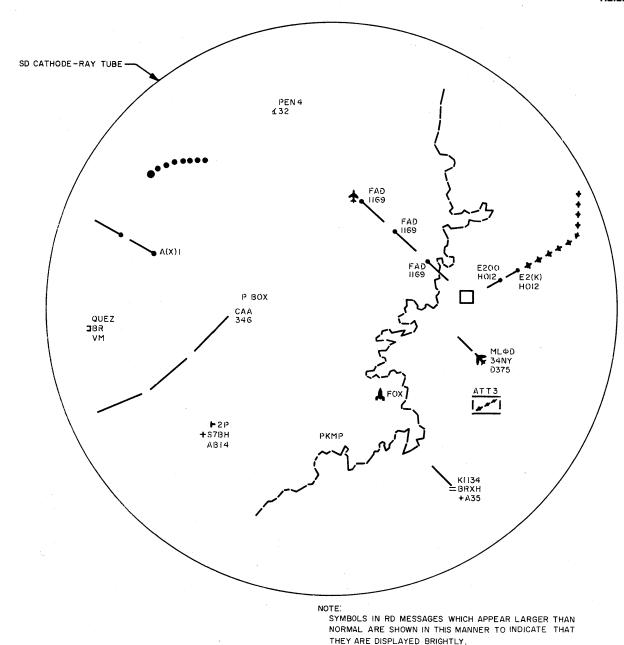

|      | 1.2.2.1 | The SD Message                                      | 19   |

|      | 1.2.2.2 | Individual Console Routing                          | 20   |

|      | 1.3     | Display Information Signals                         | 21   |

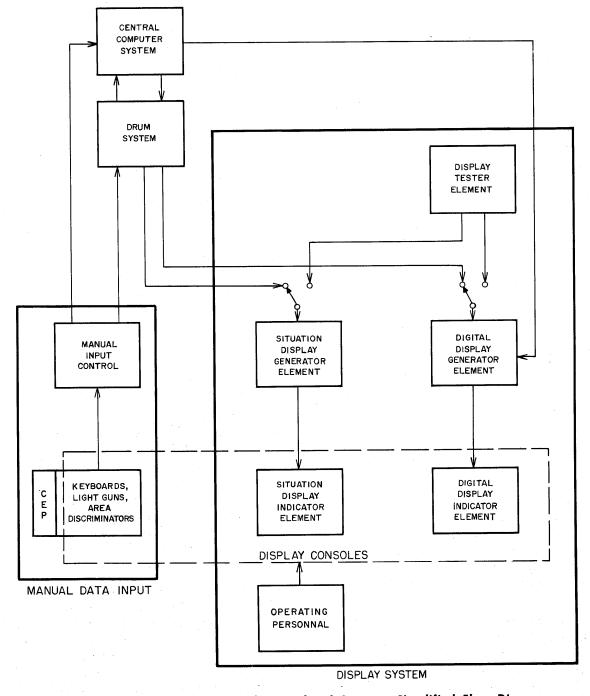

|      | 1.4     | Logical Organization of Display System              | 23   |

|      | 1.5     | Equipment Reliability                               | 23   |

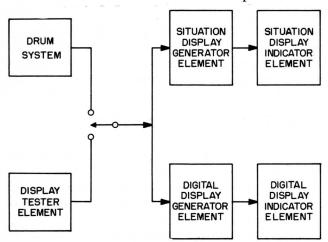

|      | 1.6     | Duplex Operation in Display System                  | 23   |

|      | 1.7     | Checking the Display System                         | 24   |

|      | SECTIO  | ON 2 FUNCTIONAL OPERATION OF DISPLAY SYSTEM         | 25   |

|      | 2.1     | Display System Function                             | 25   |

|      | 2.2     | Display System Breakdown                            | 25   |

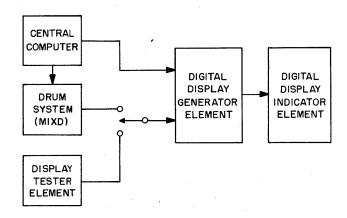

|      | SECTIO  | ON 3 OVERALL FUNCTION OF DD ELEMENTS                | 26   |

|      | 3.1     | Scope                                               | 26   |

|      | 3.2     | Digital Display Instructions                        | 26   |

| Head | ling    |                                              | Page |

|------|---------|----------------------------------------------|------|

|      | 3.3     | Digital Display Elements                     | 26   |

|      | 3.4     | Timing of a DD Cycle                         | 27   |

|      | SECTIO  | N 4 OVERALL FUNCTION OF SD ELEMENTS          | 27   |

|      | 4.1     | Scope                                        | 27   |

|      | 4.2     | SD Information                               | 27   |

|      | 4.3     | SD Message Presentation                      | 27   |

|      | 4.4     | Situation Display Elements                   | 27   |

|      | 4.5     | SD Signal Flow and Timing                    | 27   |

|      | 4.6     | SDIS Selection                               |      |

|      | 4.6.1   | Message Category                             | 28   |

|      | 4.6.2   | Display Assignment Bit                       | 28   |

|      | 4.6.3   | Optional Message Display                     | 28   |

|      | SECTIO  | N 5 OVERALL FUNCTION OF ASSOCIATED EQUIPMENT | 29   |

| *.   | 5.1     | Scope                                        | 29   |

|      | 5.2     | Supporting Components                        | 29   |

|      | 5.2.1   | Audible Alarms and Warning Lights            | 29   |

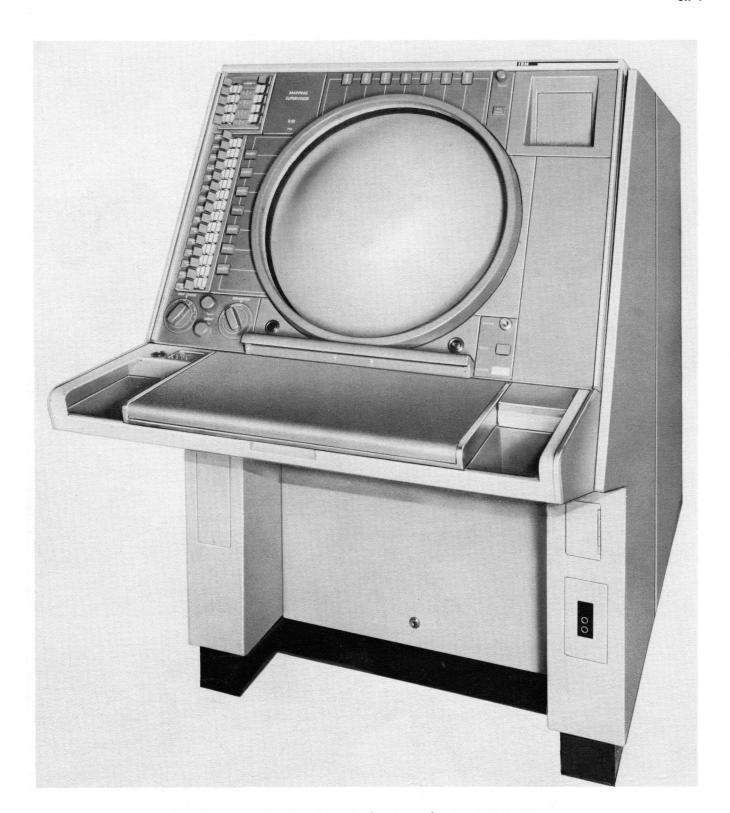

|      | 5.2.2   | SD Console                                   | 29   |

|      | 5.2.3   | Auxiliary Console                            | 29   |

|      | 5.2.4   | Command Post Console                         | 29   |

|      | 5.2.5   | Communication Equipment                      | 29   |

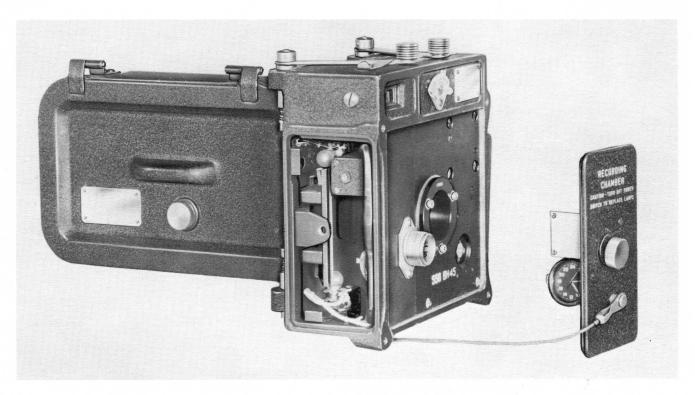

|      | 5.2.6   | Photographic Recorder-Reproducer Element     | . 29 |

|      | 5.2.7   | Situation Display Camera Element             | . 30 |

|      | 5.2.8   | Display Tester Element                       | 30   |

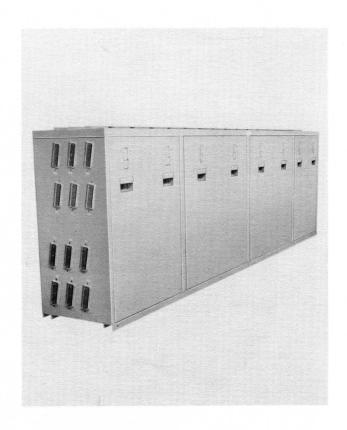

|      | 5.2.9   | Distribution Element                         | . 30 |

|      | 5.2.9.1 | Distribution Boxes                           | . 30 |

|      | 5.2.9.2 | Signal Data Patching Panel                   |      |

|      | SECTIO  | ON 6 OVERALL FUNCTION OF MANUAL DATA         |      |

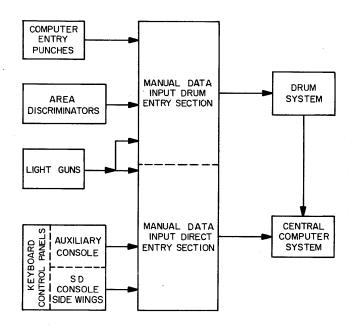

|      | 6.1     | Scope                                        | . 31 |

|      | 6.2     | MDI Devices                                  | . 31 |

|      | 6.2.1   | Keyboard Control Panel                       | . 31 |

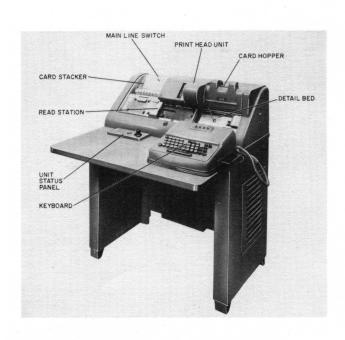

|      | 622     | Computer Entry Punch                         | . 31 |

| Heading |                                            | Page |

|---------|--------------------------------------------|------|

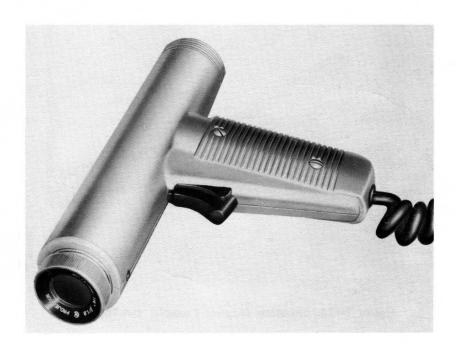

| 6.2.3   | Light Gun                                  | . 31 |

| 6.2.4   | Area Discriminator                         | . 31 |

| PART 2  | CRT'S IN DISPLAY SYSTEM                    | . 33 |

| CHAPTER | 1 GENERAL THEORY OF CRT'S                  | . 33 |

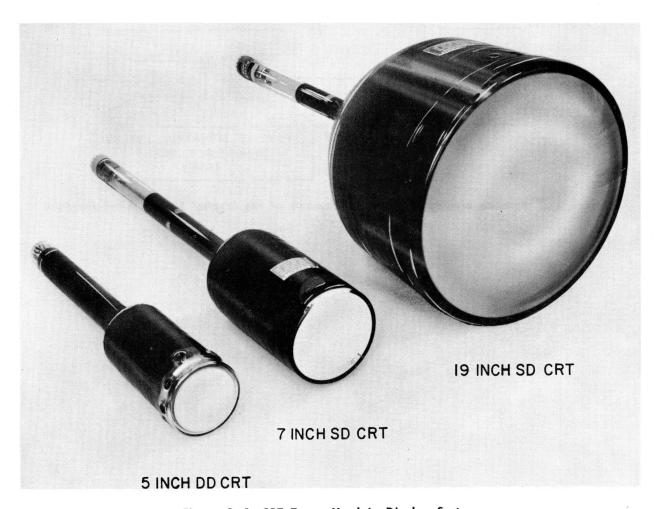

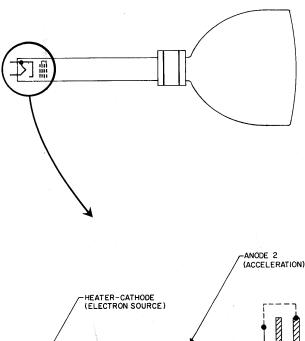

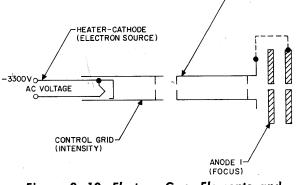

| 1.1     | Introduction to CRT's                      | . 33 |

| 1.2     | Display System CRT's                       | . 34 |

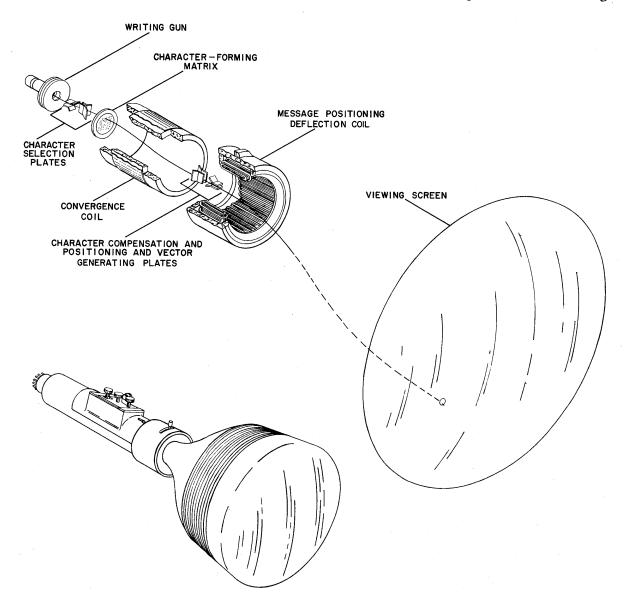

| 1.2.1   | Electron Gun                               | . 34 |

| 1.2.2   | Screen Phosphors                           | . 35 |

| 1.2.3   | Persistence of Phosphors                   | . 35 |

| 1.2.4   | Envelope Coating                           | . 35 |

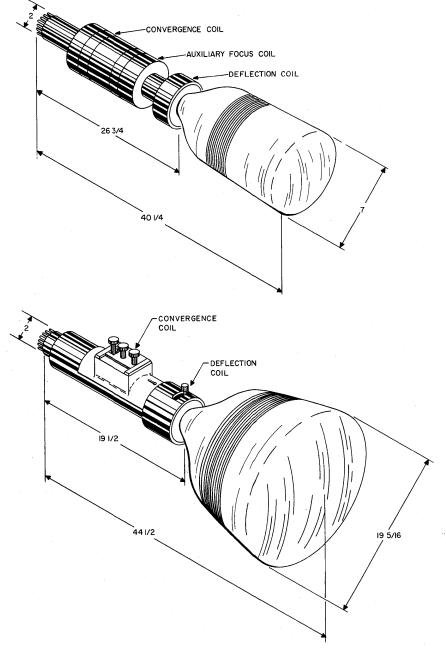

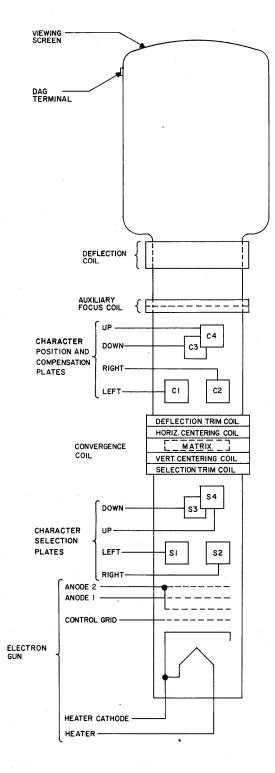

| CHAPTER | 2 19-INCH SD CRT'S                         | . 37 |

| 2.1     | General                                    | . 37 |

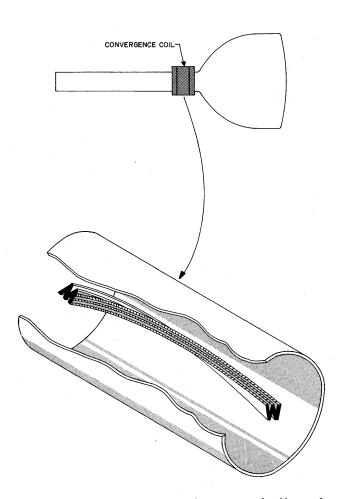

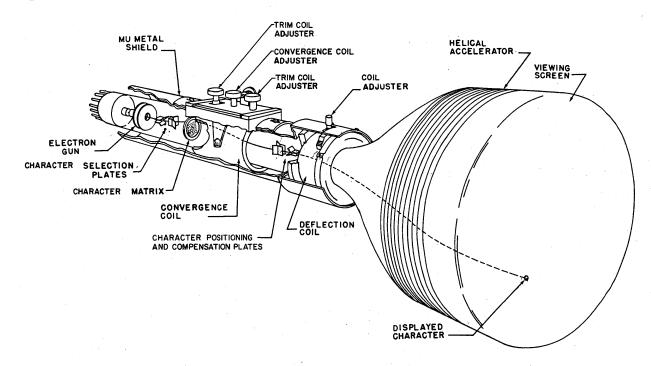

| 2.1.1   | Convergence Coil                           | . 37 |

| 2.1.2   | Trim Coils                                 | . 37 |

| 2.1.3   | Character Position and Compensation Plates | . 37 |

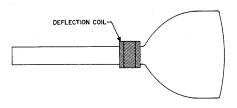

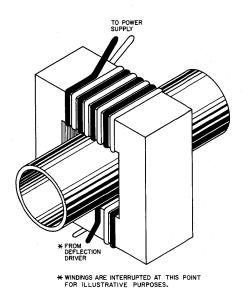

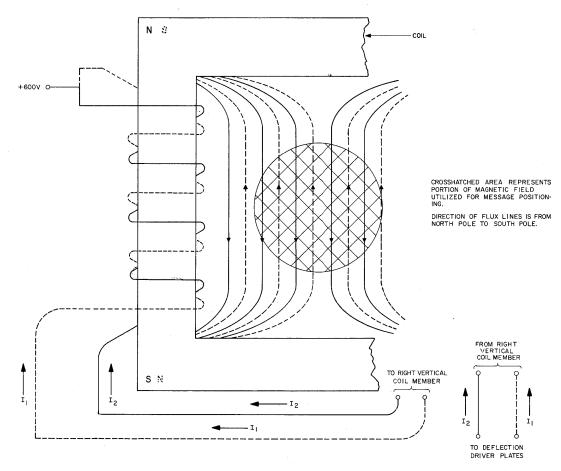

| 2.1.4   | Deflection Coil                            | . 37 |

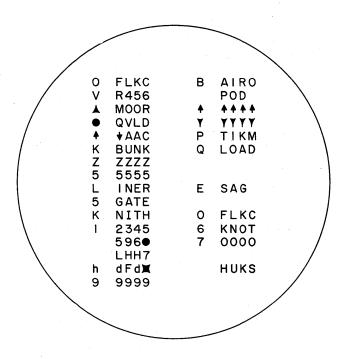

| 2.1.5   | Viewing Screen and Message Format          | . 38 |

| 2.1.6   | Post-Acceleration Coating                  | . 39 |

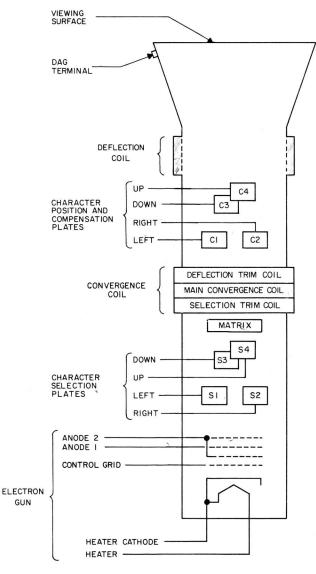

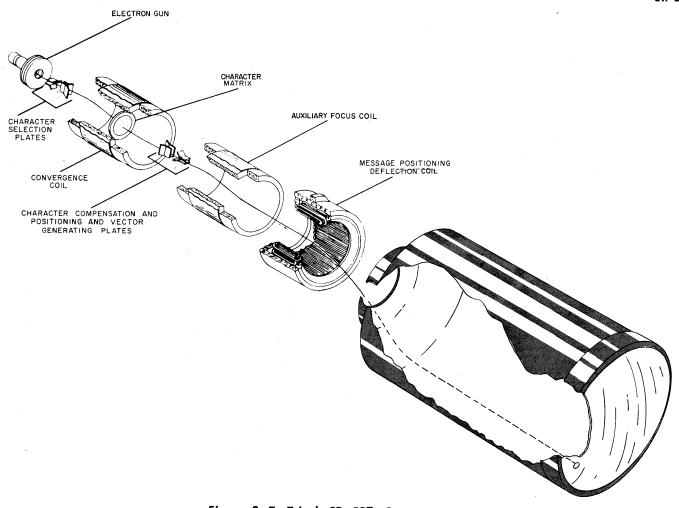

| 2.2     | SD CRT Functional Operation                | . 39 |

| 2.2.1   | Character Display, Detailed Operation      | . 41 |

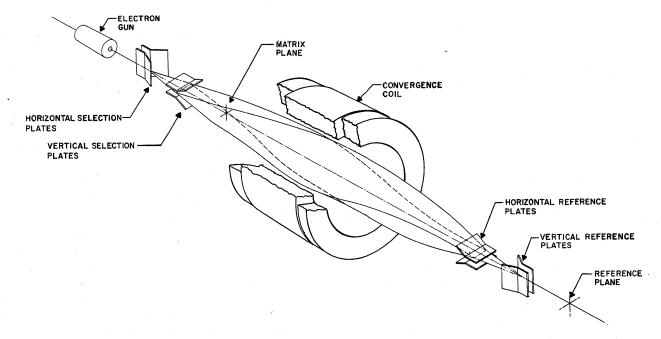

| 2.2.1.1 | Electron Beam Generation                   | . 41 |

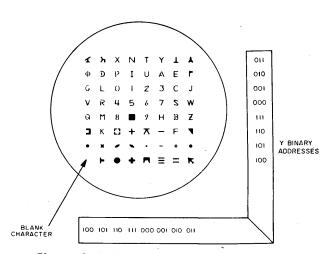

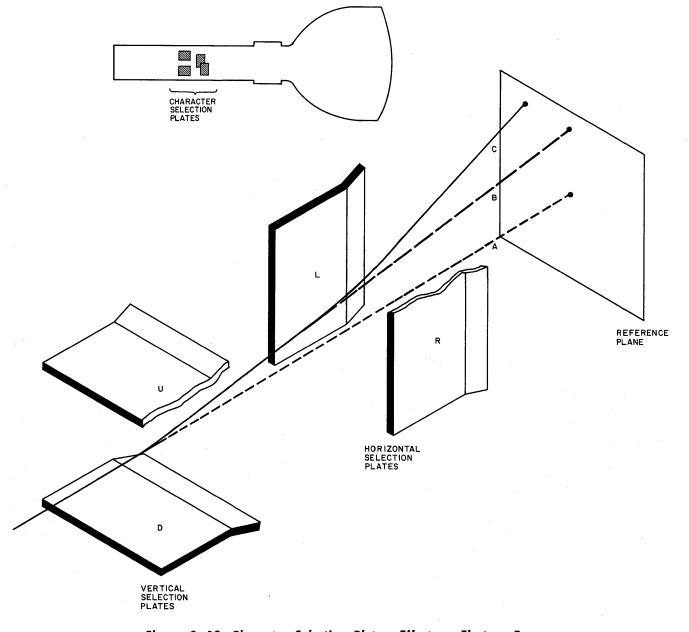

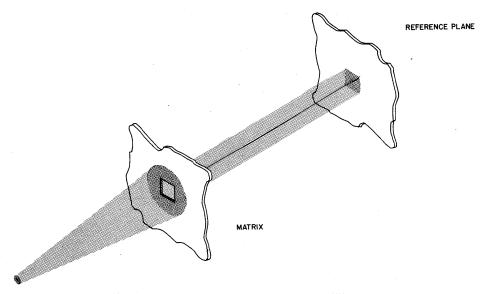

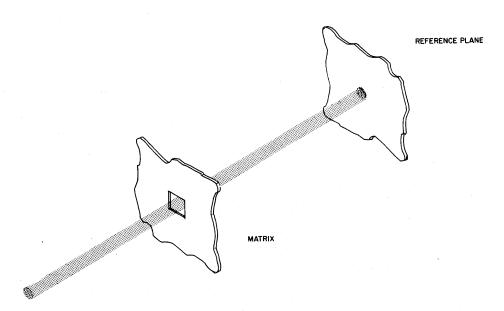

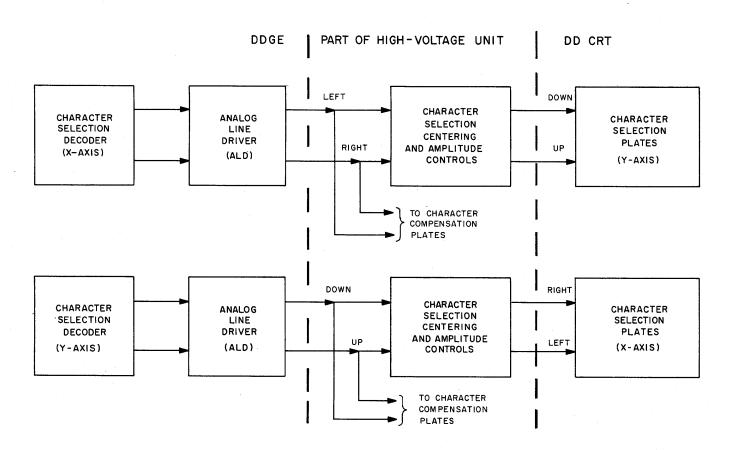

| 2.2.1.2 | Character Selection                        | . 42 |

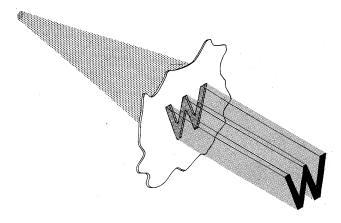

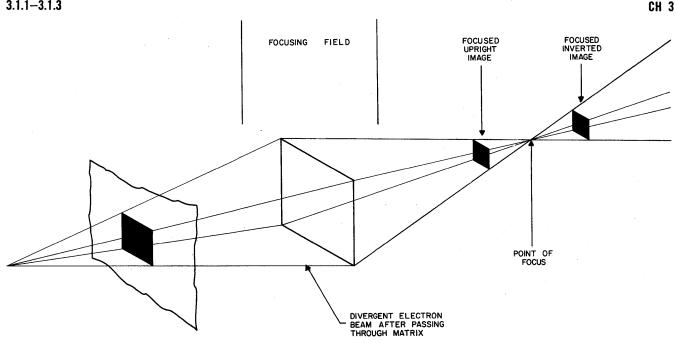

| 2.2.1.3 | Electron Beam Shaping                      | . 44 |

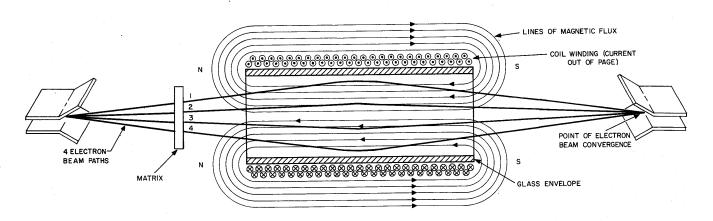

| 2.2.1.4 | Electron Beam Convergence                  | . 44 |

| 2.2.1.5 | Character Compensation and Positioning     | 48   |

| 2.2.1.6 | Message Deflection                         | 48   |

| 2.2.1.7 | Character Display Summary                  | . 50 |

| 2.2.2   | Vector Display, Detailed Operation         | . 50 |

| CHAPTER | 2 3 7-INCH SD CRT                          | . 53 |

| 3.1     | General                                    | 53   |

| Heading |                                              | Page |

|---------|----------------------------------------------|------|

| 3.1.1   | Auxiliary Focus Coil                         | 53   |

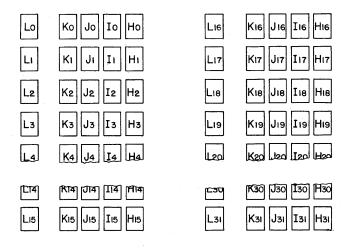

| 3.1.2   | Character Matrix Location                    | 54   |

| 3.1.3   | Convergence Coil                             | 54   |

|         |                                              |      |

| CHAPTE  | R 4 5-INCH DD CRT                            | . 55 |

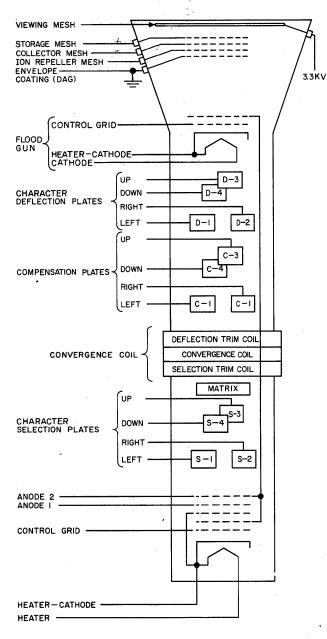

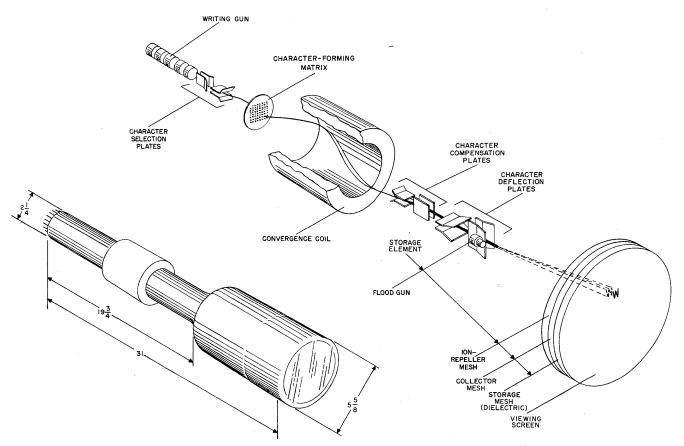

| 4.1     | General                                      | 55   |

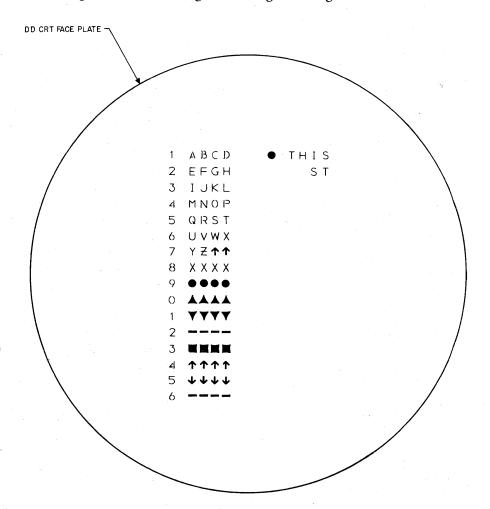

| 4.1.1   | Basic Operation                              | 56   |

| 4.1.2   | Detailed Operation                           | . 56 |

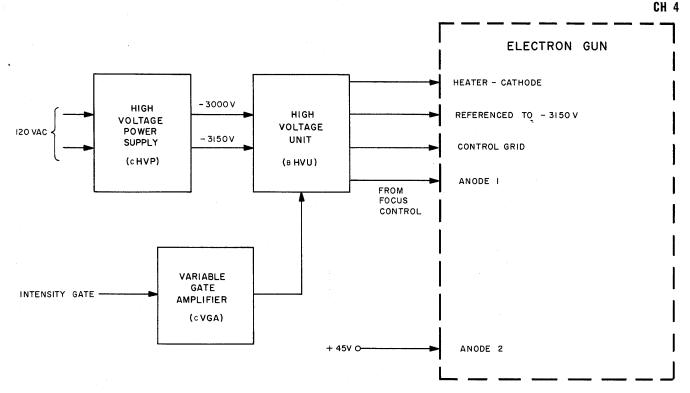

| 4.1.2.1 | Electron Gun                                 | 56   |

| 4.1.2.2 | Character Selection                          | 56   |

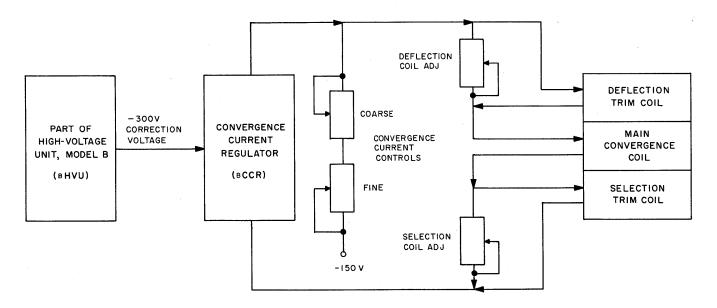

| 4.1.2.3 | Electron Beam Convergence                    | 57   |

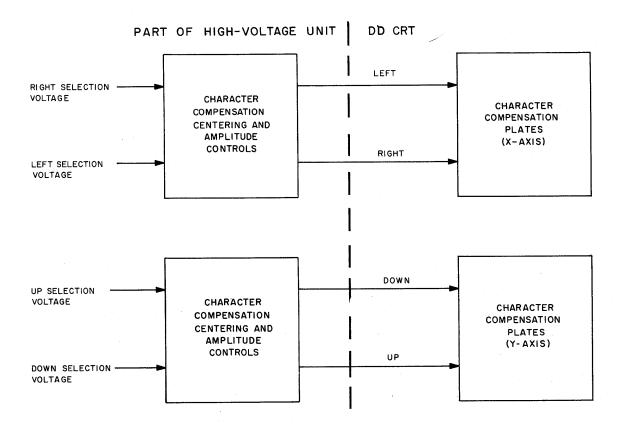

| 4.1.2.4 | Electron Beam Compensation                   | -57  |

| 4.1.2.5 | Character Message Deflection                 | 58   |

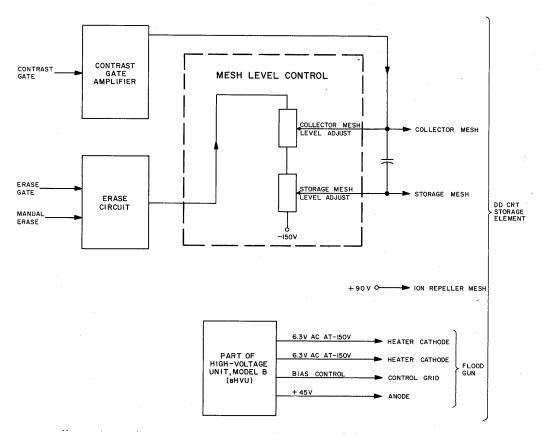

| 4.1.2.6 | Flood Gun                                    | 58   |

| 4.1.2.7 | Collector Mesh                               | . 59 |

| 4.1.2.8 | Storage Mesh                                 | . 59 |

| 4.1.2.9 | Ion Repeller Mesh                            | . 59 |

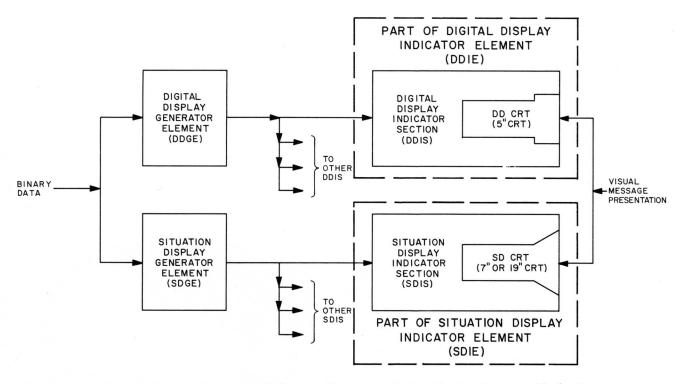

| PART 3  | DIGITAL DISPLAY ELEMENTS                     | . 63 |

| СНАРТЕ  | R 1 INTRODUCTION TO DIGITAL DISPLAY ELEMENTS | 63   |

| 1.1     | General                                      | . 63 |

| 1.2     | Purpose of Digital Display Elements          | 63   |

| 1.3     | Type of Display                              |      |

| 1.4     | MIXD Drum Operation                          |      |

| 1.4.1   | Timing and Control Signals                   |      |

| 1.4.2   | Information Signals                          |      |

| 1.5     | Message Format                               |      |

| 1.6     | DD Sequence of Operation                     |      |

| 1.6.1   | Initial Period                               |      |

| 1.6.1.1 | Synchronization Phase                        |      |

| 1.6.1.2 | Delay Phase                                  |      |

| 1.6.1.3 | Display Phase                                | . 65 |

| Head | ding    |                                                | Page |

|------|---------|------------------------------------------------|------|

|      | 1.6.2   | Display Period                                 | 66   |

|      | 1.6.3   | Retention Period                               | 66   |

|      | 1.6.4   | Erase Period                                   | 66   |

| C    | HAPTER  | 2 DIGITAL DISPLAY INDICATOR ELEMENT            | . 67 |

|      | 2.1     | General                                        | 67   |

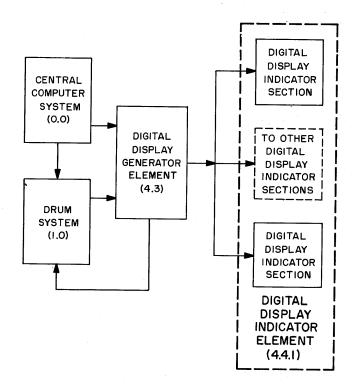

|      | 2.2     | Information Flow to DDIE                       | 67   |

|      | 2.3     | Digital Display Indicator Section              | 67   |

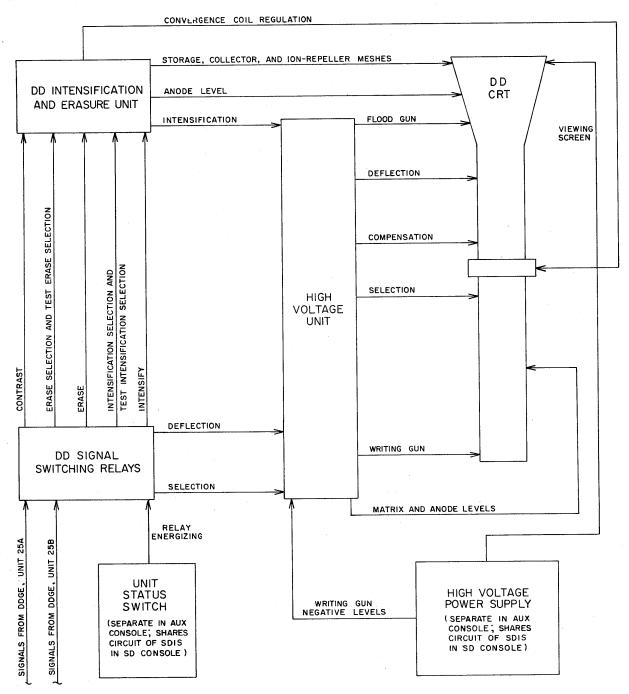

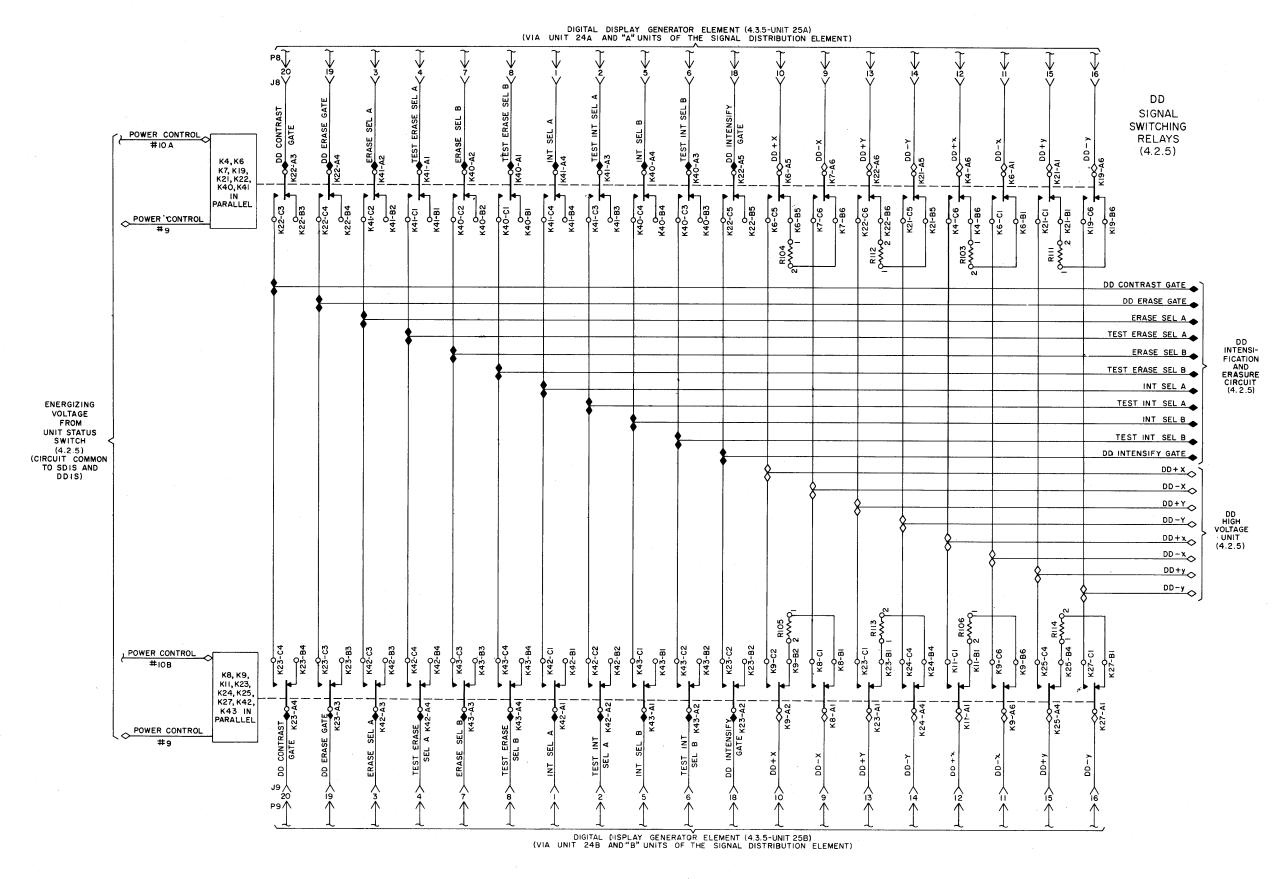

|      | 2.3.1   | Unit Status Switch and Signal Switching Relays | 69   |

|      | 2.3.2   | Intensification and Erasure Circuit            | 69   |

|      | 2.3.2.1 | Normal Intensification Selection               | 69   |

|      | 2.3.2.2 | Intensification in Test 1                      | 69   |

|      | 2.3.2.3 | Intensification in Test 2                      | 69   |

|      | 2.3.2.4 | Normal Erase Selection                         | 69   |

|      | 2.3.2.5 | Erasure in Test 1                              | 69   |

|      | 2.3.2.6 | Erasure in Test 2                              | 69   |

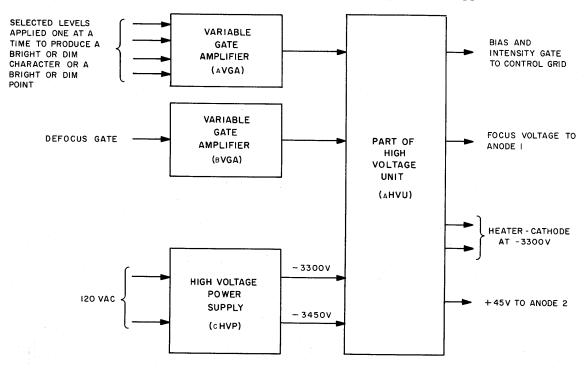

| *    | 2.3.3   | High-Voltage Unit                              | 70   |

|      | 2.3.4   | High-Voltage Power Supply                      | 70   |

|      | 2.3.5   | DD Cathode-Ray Tube                            | 72   |

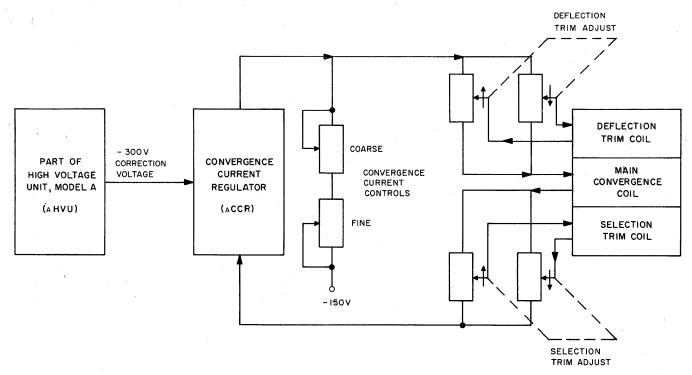

|      | 2.3.6   | Convergence Current Regulator                  | 72   |

|      | 2.3.7   | Contrast Gate                                  | 72   |

|      | 2.4     | DDIS Marginal Checking                         | 72   |

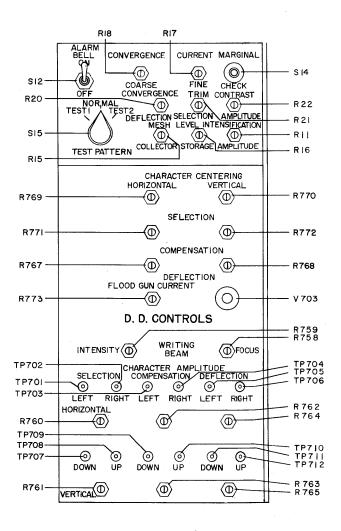

|      | 2.5     | DDIS Controls                                  | 72   |

| C    | HAPTER  | 3 DIGITAL DISPLAY GENERATOR ELEMENT            | 77   |

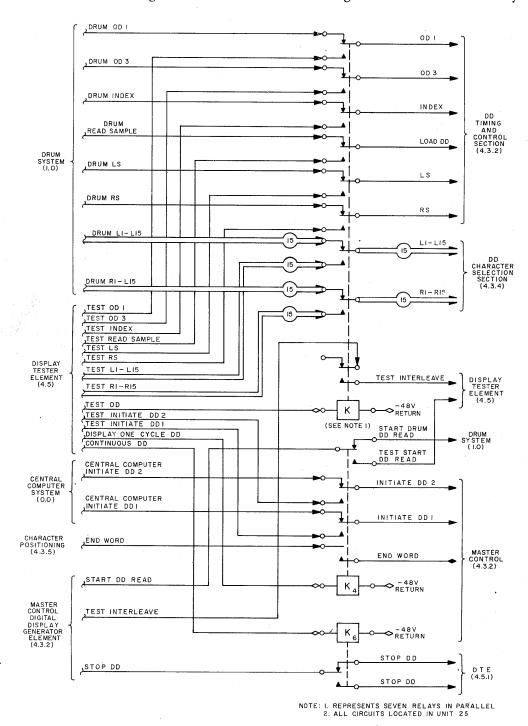

|      | SECTION | I FUNCTIONAL OPERATION OF DD GENERATOR ELEMENT | 77   |

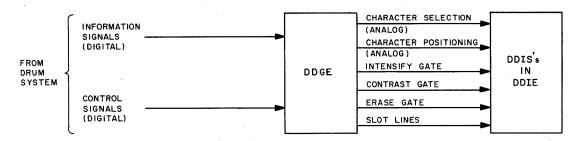

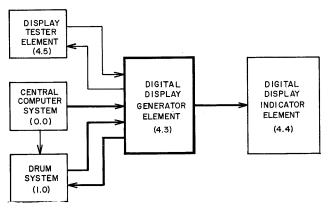

|      | 1.1     | Purpose of Digital Display Generator Element   | 77   |

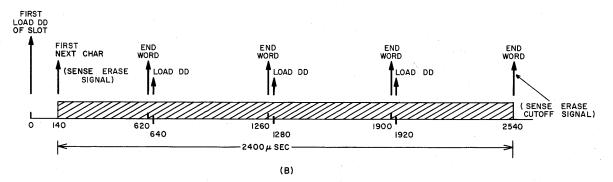

|      | 1.2     | DDGE Logic-Block Function                      | 77   |

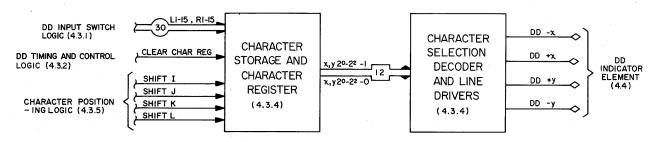

|      | 1.2.1   | DD Input Switch Section                        | 77   |

|      | 1.2.2   | DD Indicator Selection Section                 | 77   |

|      | 1.2.3   | DD Character Selection Section                 | 77   |

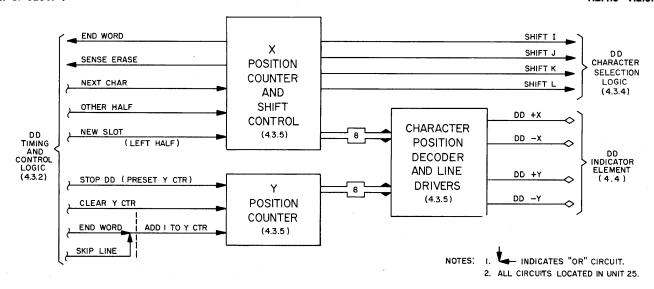

|      | 1.2.4   | DD Character Positioning Section               | 79   |

|      | 1.2.4.1 | X-Position Counter and Shift Control           | 80   |

|      | 1242    | Y-Position Counter                             | 80   |

| Head | ling    |                                                    | Page |

|------|---------|----------------------------------------------------|------|

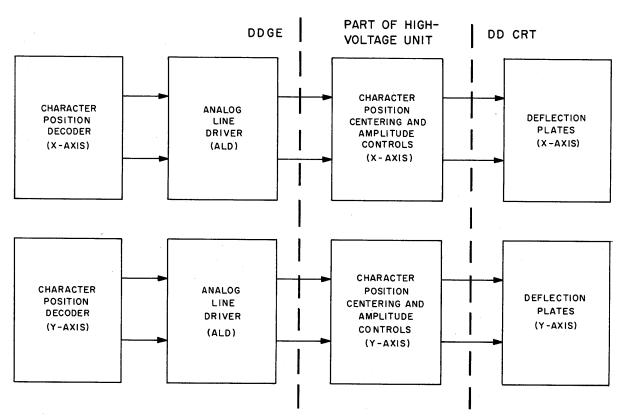

|      | 1.2.4.3 | Character Position Decoder and Line Drivers        | 80   |

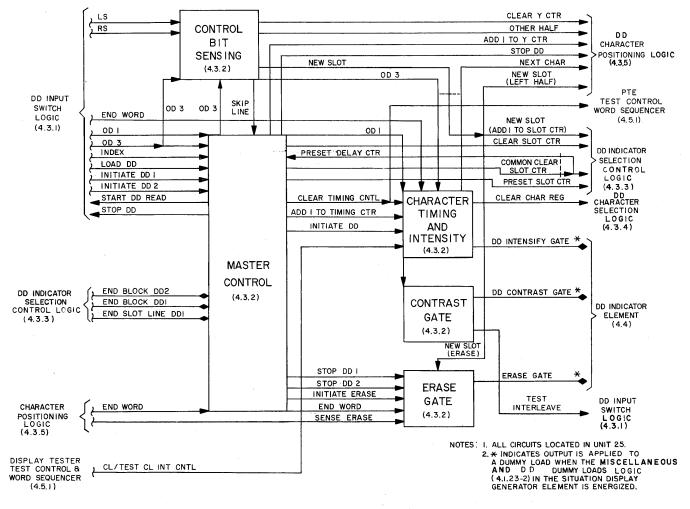

|      | 1.2.5   | DD Timing and Control Section                      | 81   |

|      | 1.2.5.1 | Overall Timing and Control Functions               | 81   |

|      | 1.2.5.2 | Master Control Circuit                             | 81   |

|      | 1.2.5.3 | Character Timing and Intensity Circuit             | 82   |

|      | 1.2.5.4 | Control Bit Sensing Circuit                        | 82   |

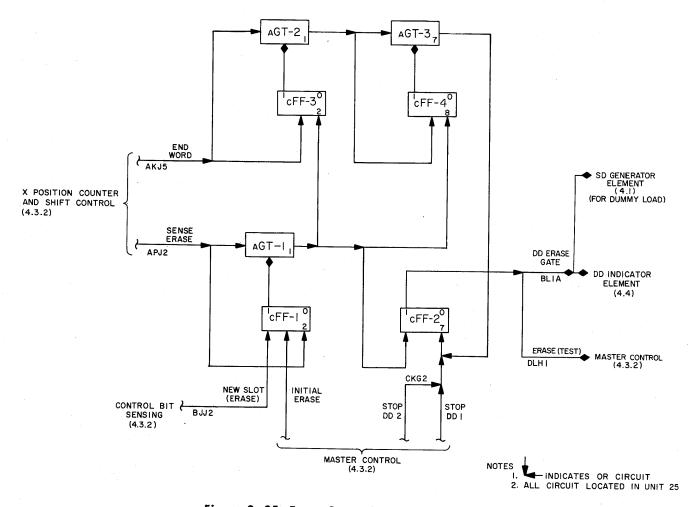

|      | 1.2.5.5 | Erase Gate Circuit                                 | 83   |

|      | 1.2.5.6 | Contrast Gate Circuit                              | 83   |

|      | 1.2.6   | DD Timing and Control Inputs                       | 83   |

|      | 1.2.7   | DD Timing and Control Outputs                      | 83   |

|      | SECTIO  | N 2 LOGIC OPERATION OF DD GENERATOR ELEMENT        | 84   |

|      | 2.1     | DD Input Switch                                    | 84   |

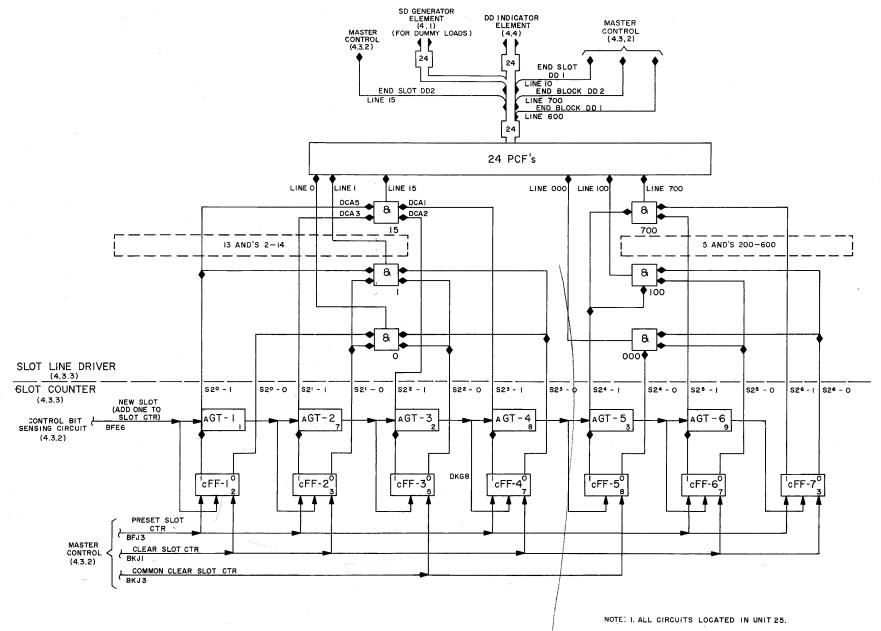

| - 21 | 2.2     | DD Indicator Selection Section                     | 84   |

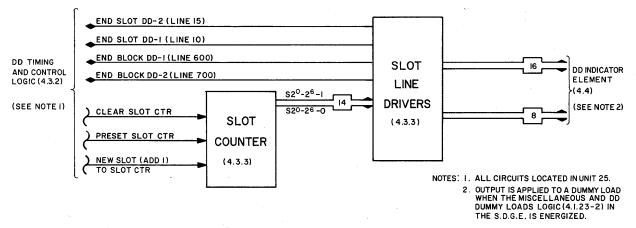

|      | 2.2.1   | Slot Counter Circuit                               | 84   |

|      | 2.2.2   | Slot Line Driver Circuit                           | 87   |

|      | 2,2.3   | Intensification and Erase Gate Distribution        | 87   |

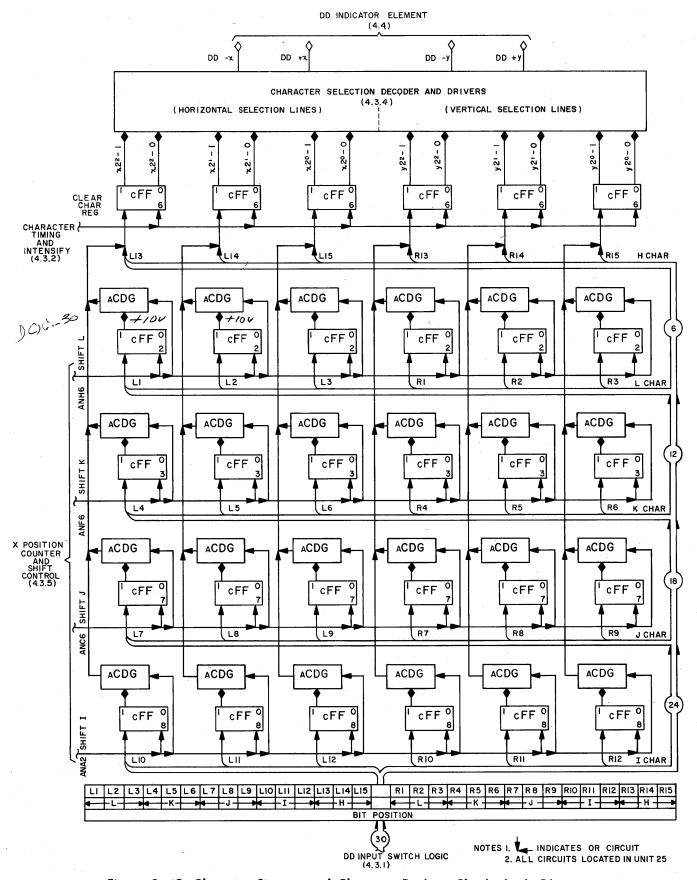

|      | 2.3     | DD Character Selection Section                     | 87   |

|      | 2.3.1   | Character Storage and Character Register Circuit   | 87   |

|      | 2.3.2   | Character Selection Decoder and Drivers Circuit    | 89   |

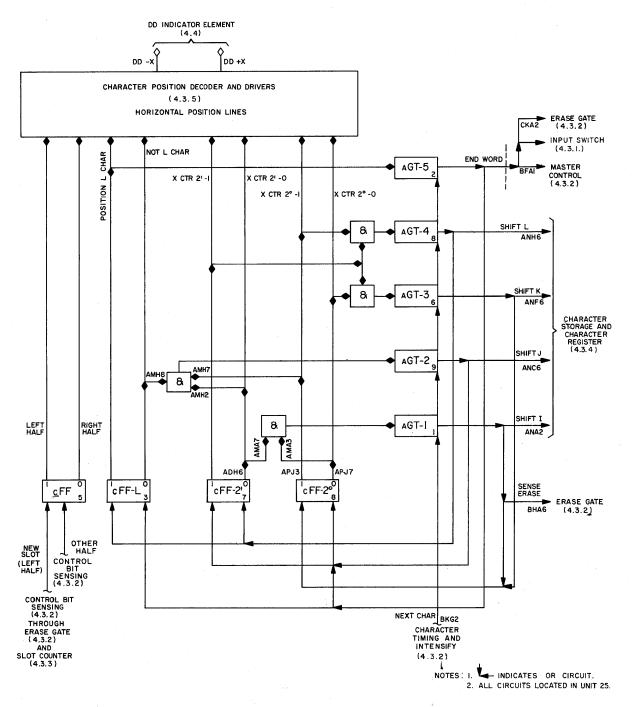

|      | 2.4     | Character Positioning Section                      | 89   |

|      | 2.4.1   | X-Position Counter and Shift Control Circuit       | 89   |

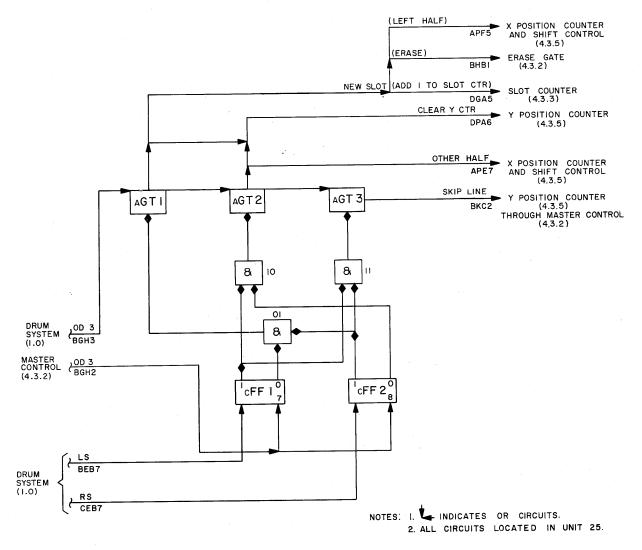

|      | 2.4.1.1 | Counting and Shift Control                         | 89   |

|      | 2.4.1.2 | Left-Half or Other-Half Flip-Flop                  | 91   |

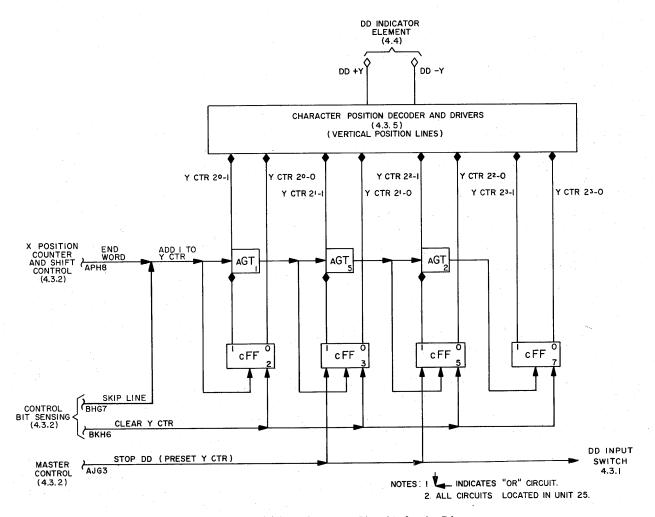

|      | 2.4.2   | Y-Position Counter                                 | 91   |

|      | 2.4.2.1 | Y-Counter Operation                                | 91   |

|      | 2.4.2.2 | Character Position Decoder and Line Driver Circuit | . 92 |

|      | 2.5     | Digital Display Timing and Control Section         | . 92 |

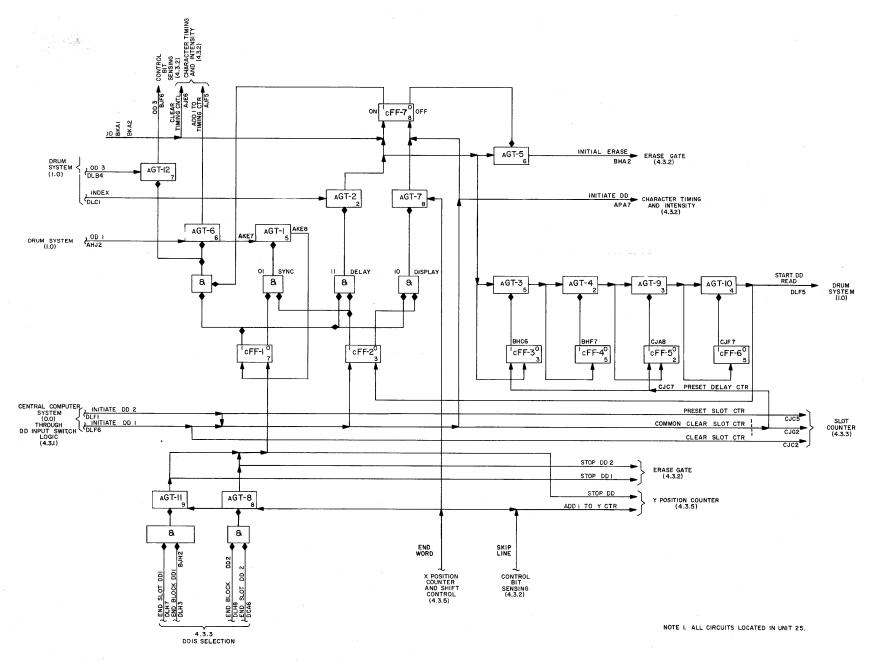

|      | 2.5.1   | Master Control Circuit                             | . 92 |

|      | 2.5.1.1 | Phase Counter                                      | . 92 |

|      | 2.5.1.2 | On-Off Flip-Flop                                   |      |

|      | 2.5.1.3 | Delay Counter                                      | 94   |

|      | 2.5.1.4 | Display Period Operation                           | 94   |

|      | 2.5.1.5 | End Display                                        | . 94 |

| Head | ding     | •                                             | Page |

|------|----------|-----------------------------------------------|------|

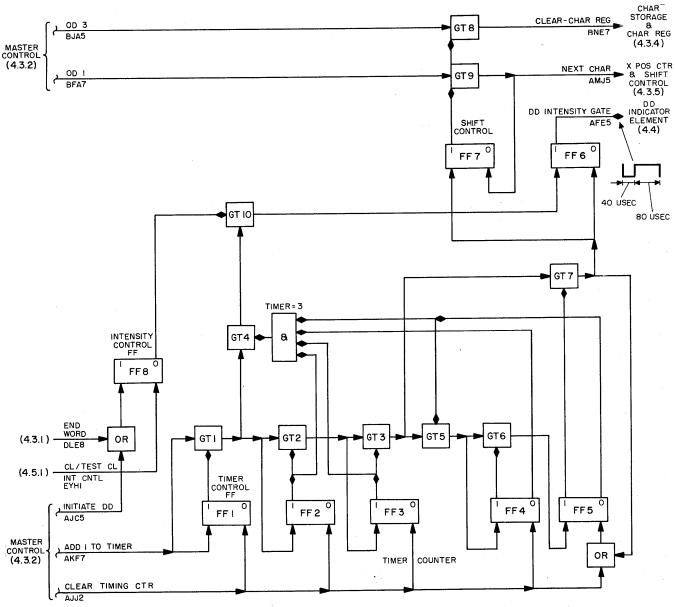

|      | 2.5.2    | Character Timing and Intensity Circuit        | 94   |

|      | 2.5.2.1  | Intensification Gate Generation               | 94   |

|      | 2.5.2.2  | Intensification Gate Cutoff                   | 95   |

|      | 2.5.3    | Control Bit Sensing Circuit                   | 96   |

|      | 2.5.3.1  | New-Slot Operation                            | 96   |

|      | 2.5.3.2  | Other-Half Operation                          | 97   |

|      | 2.5.3.3  | Skip-Line Operation                           | 97   |

|      | 2.5.4    | Erase Gate Circuit                            | 97   |

|      | 2.5.4.1  | Erase Gate Generation                         | 98   |

|      | 2.5.4.2  | Erase Gate Cutoff                             | 98   |

|      | 2.5.5    | Contrast Gate Circuit                         | 99   |

|      | SECTION  | 3 OVERALL TIMING OF DD ELEMENTS               | 100  |

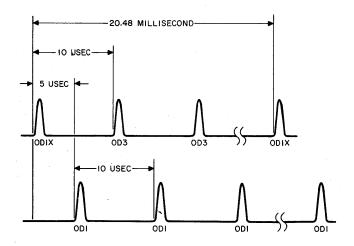

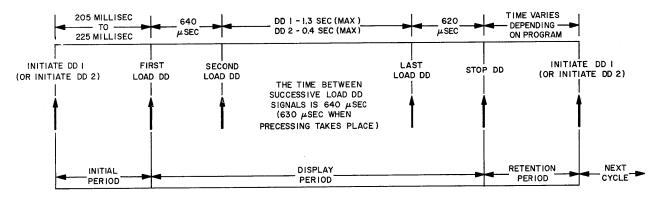

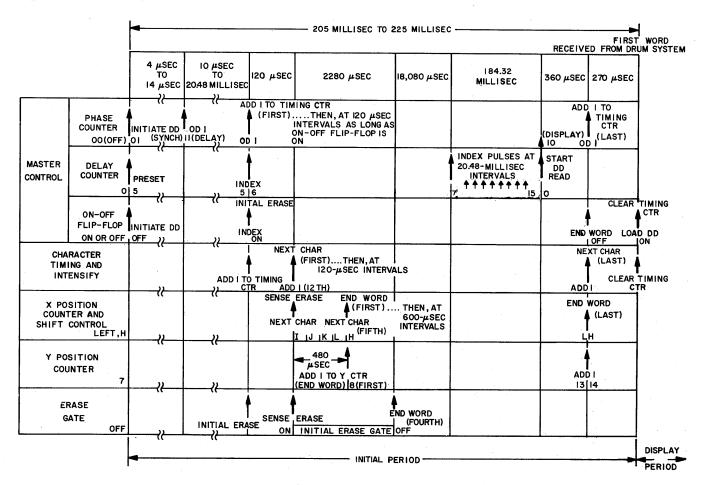

|      | 3.1      | Timing and Control of DD Elements             | 100  |

|      | 3.2      | Character Processing                          | 100  |

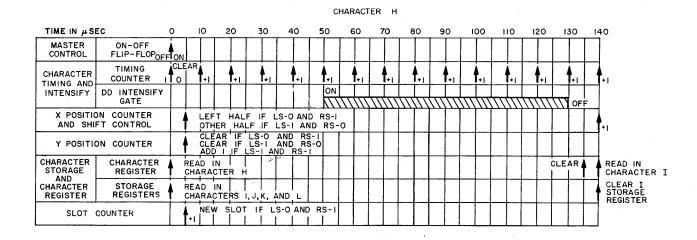

|      | 3.2.1    | Character Timing, Display Period              | 100  |

|      | 3.2.2    | Character Timing, Initial Period              | 100  |

|      | 3.3      | Word Processing                               | 101  |

|      | 3.4      | Slot Processing                               | 101  |

|      | 3.5      | Cycle Processing                              | 102  |

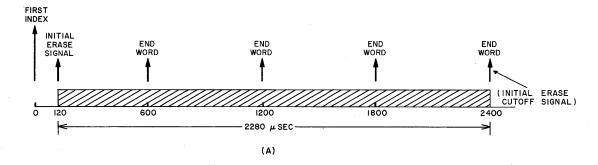

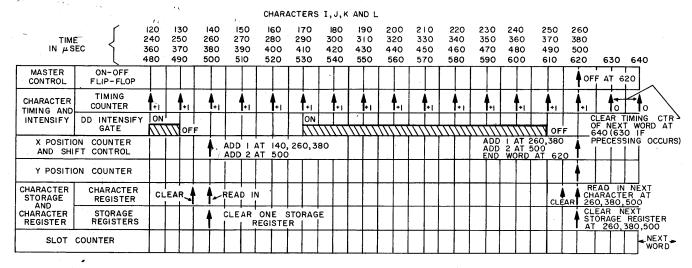

|      | 3.5.1    | Timing of Initial Period                      | 102  |

|      | 3.5.2    | Timing of Display Period                      | 103  |

|      | <b>D</b> |                                               |      |

| PA   | KI 4 :   | SITUATION DISPLAY ELEMENTS                    | 105  |

| C    | HAPTER   | 1 SITUATION DISPLAY PRESENTATION              | 105  |

|      | 1.1      | General                                       | 105  |

|      | 1.2      | Types of Messages                             | 105  |

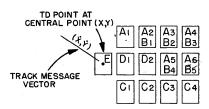

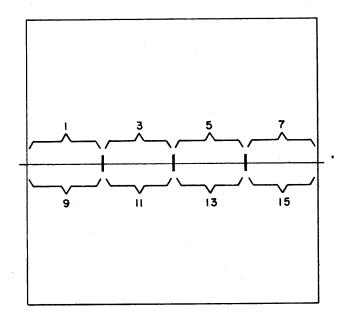

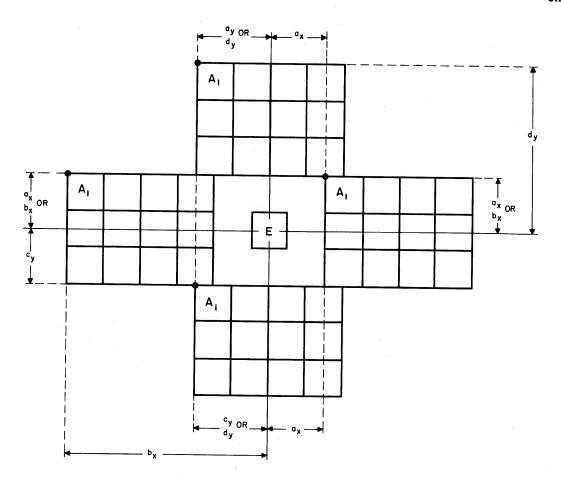

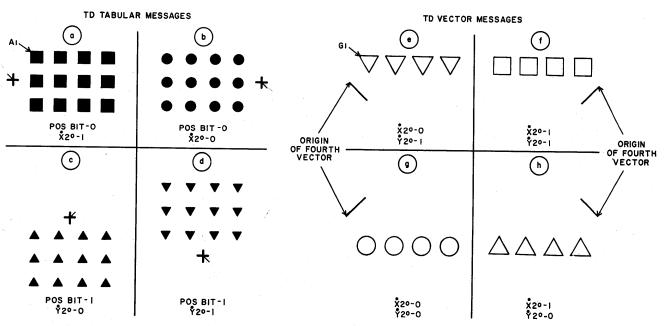

|      | 1.3      | TD Tabular Track Message Display Format       | 105  |

|      | 1.4      | TD Tabular Information Message Display Format | 107  |

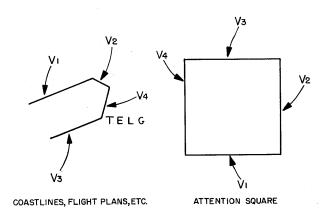

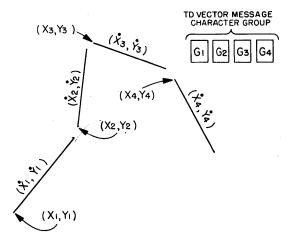

|      | 1.5      | TD Vector Message Display Format              | 107  |

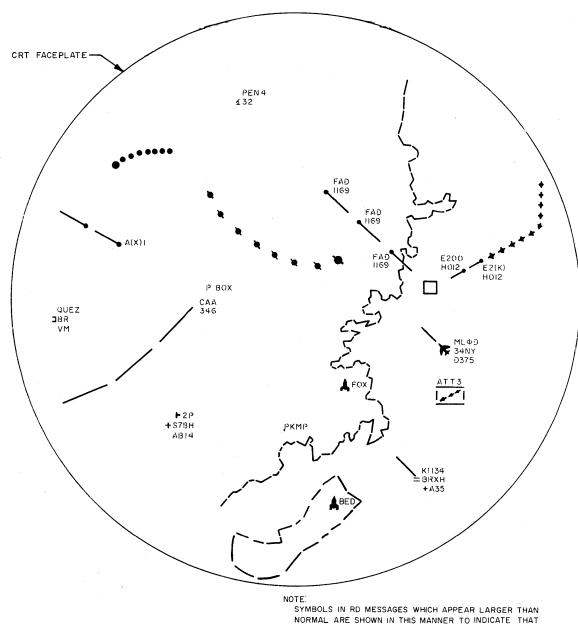

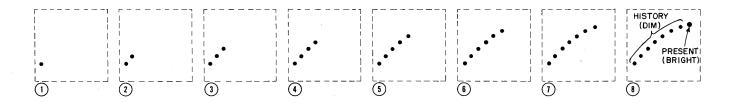

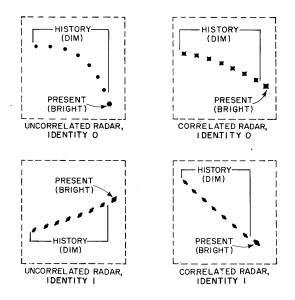

|      | 1.6      | Radar Data Message Display                    | 108  |

|      | 1.6.1    | RD Message Contents                           | 108  |

|      | 1.6.2    | RD Message Categories                         | 109  |

| Heading |                                              | Page |

|---------|----------------------------------------------|------|

| CHAPTER | 2 SITUATION DISPLAY INDICATOR ELEMENT        | 111  |

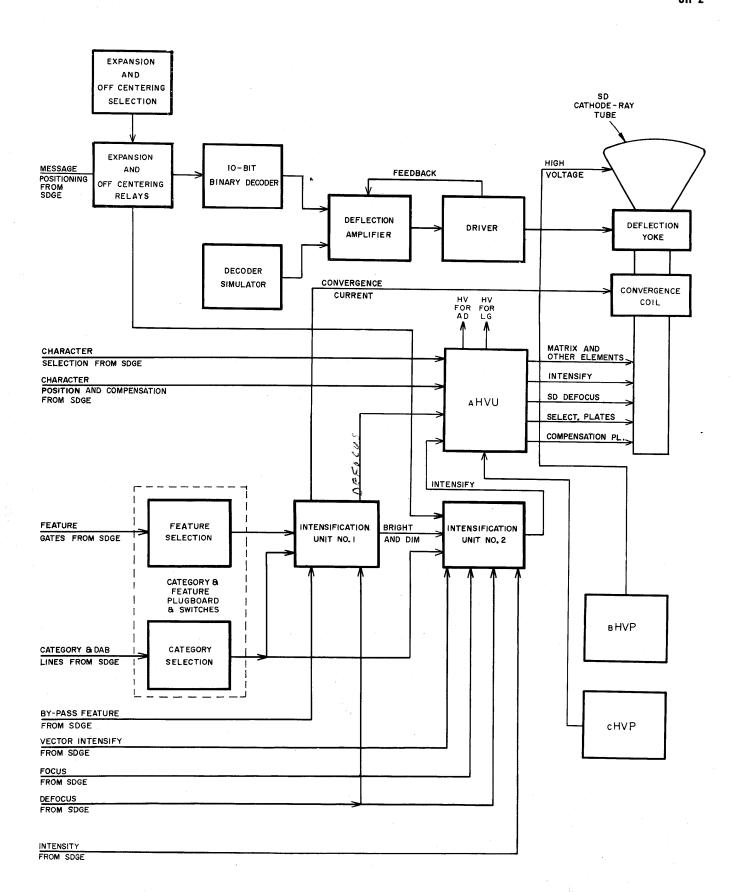

| 2.1     | Introduction                                 | 111  |

| 2.1.1   | SDIS Inputs                                  | 111  |

| 2.1.2   | SDIS Outputs                                 | 111  |

| 2.1.3   | Situation Display CRT                        | 111  |

| 2.2     | Theory of Operation                          | 111  |

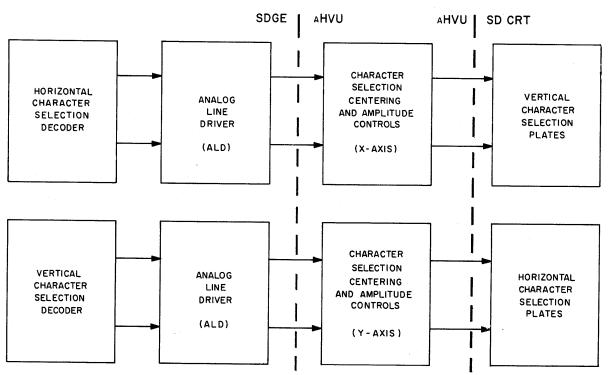

| 2.2.1   | Character Selection                          | 111  |

| 2.2.2   | Character Positioning and Compensation       | 113  |

| 2.2.3   | Message Positioning                          | 113  |

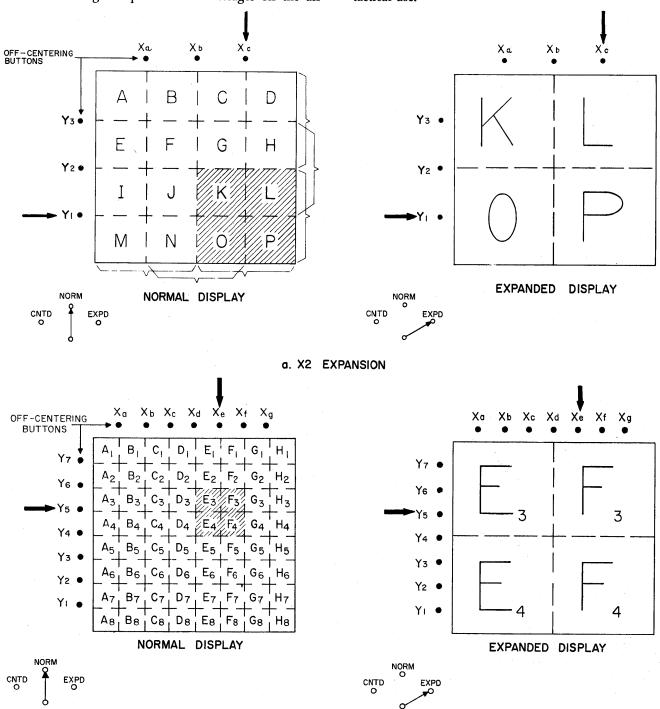

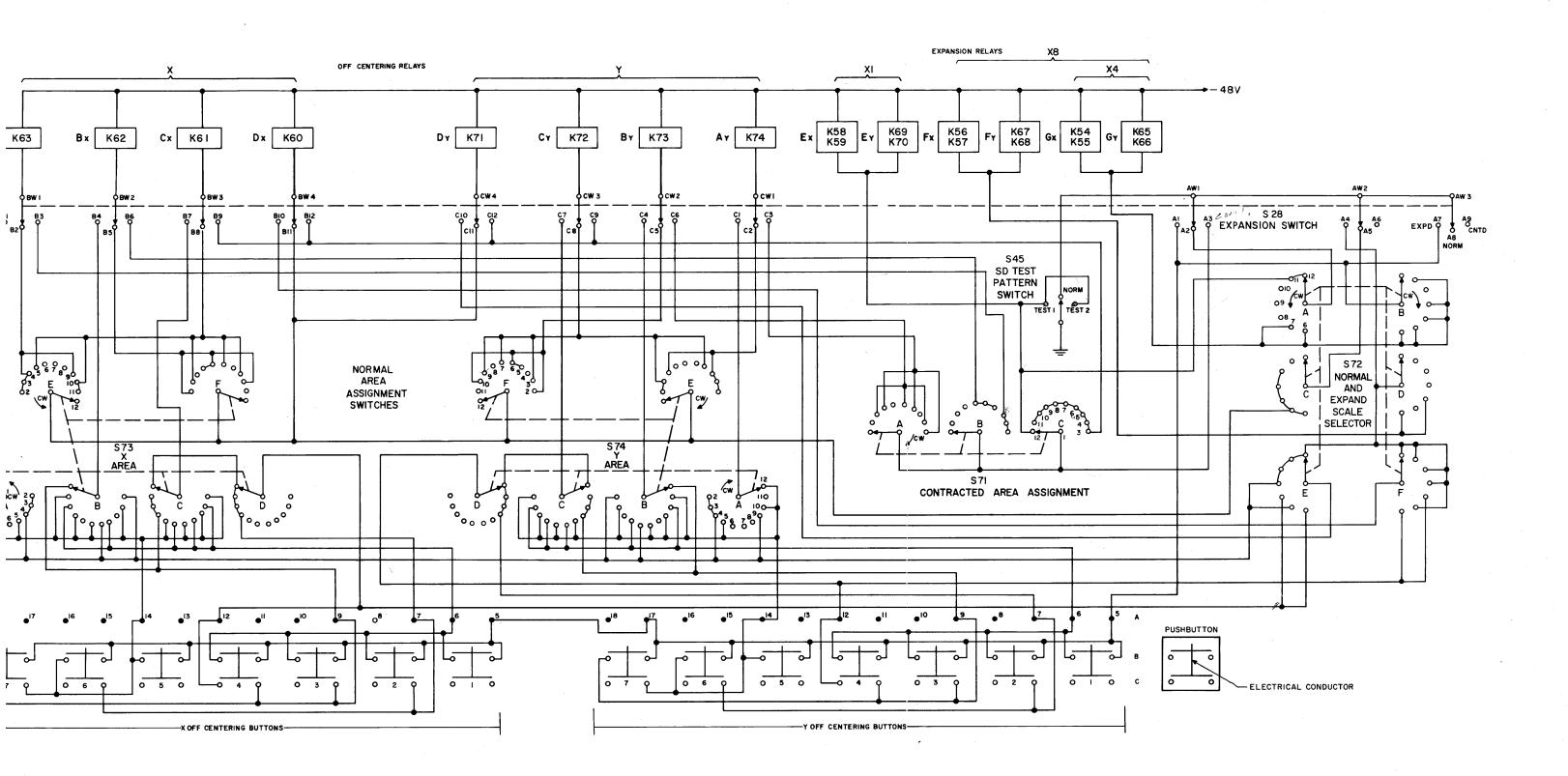

| 2.2.3.1 | Expansion Scales                             | 113  |

| 2.2.3.2 | Off-Centering                                | 113  |

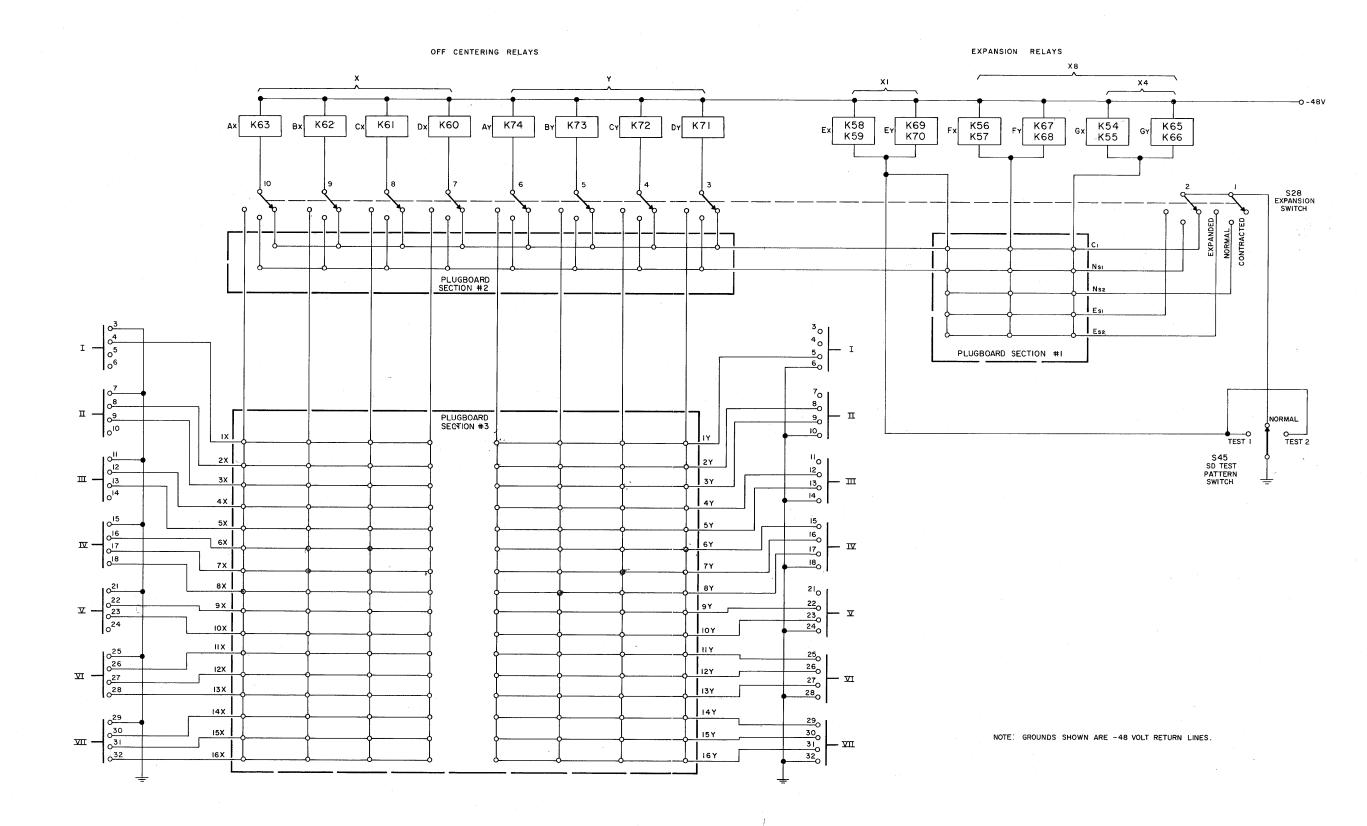

| 2,2.3.3 | Expansion Relays                             |      |

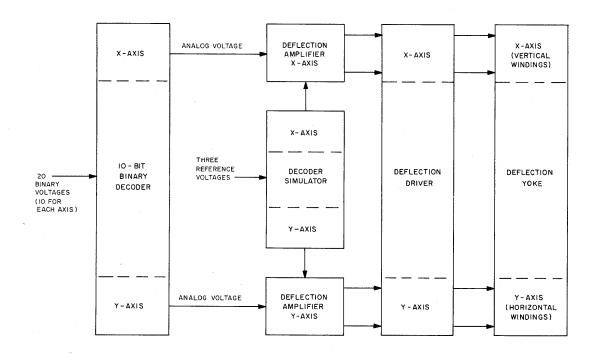

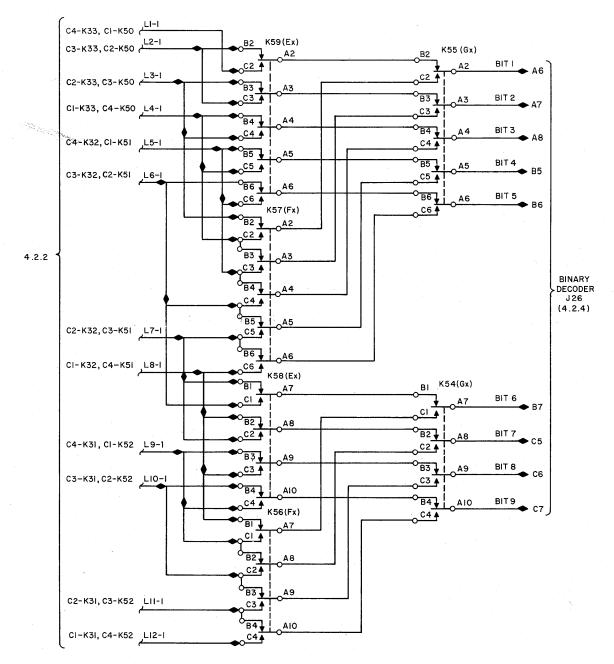

| 2.2.3.4 | Ten-Bit Binary Decoder                       | 115  |

| 2.2.3.5 | Deflection Amplifiers and Deflection Drivers | 115  |

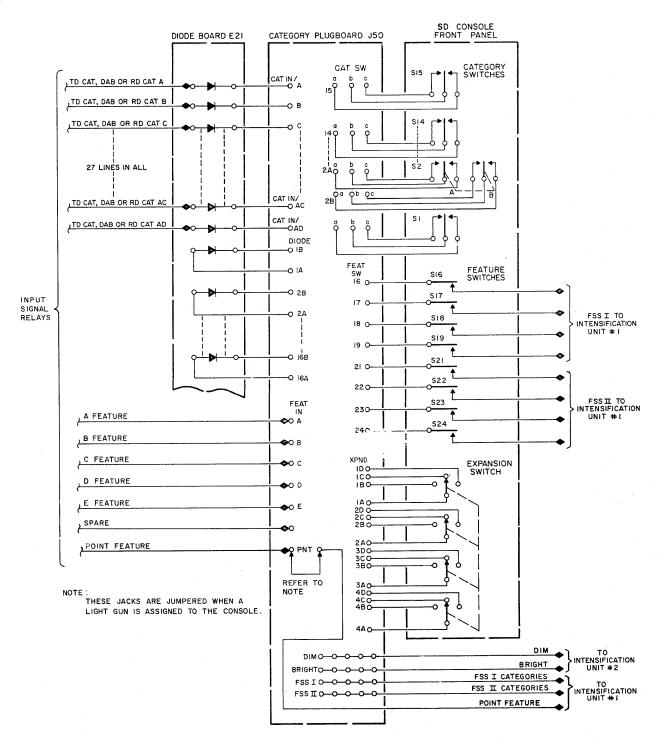

| 2.2.4   | SDIS Selection                               | 116  |

| 2.2.4.1 | Categories                                   | 117  |

| 2.2.4.2 | Display Assignment Bits                      | 118  |

| 2.2.4.3 | Mixed DAB's and CAT's                        | 118  |

| 2.2.4.4 | DAB and CAT Inputs to Consoles               | 118  |

| 2.2.4.5 | Feature Selection                            | 118  |

| 2.2.5   | Intensification                              | 118  |

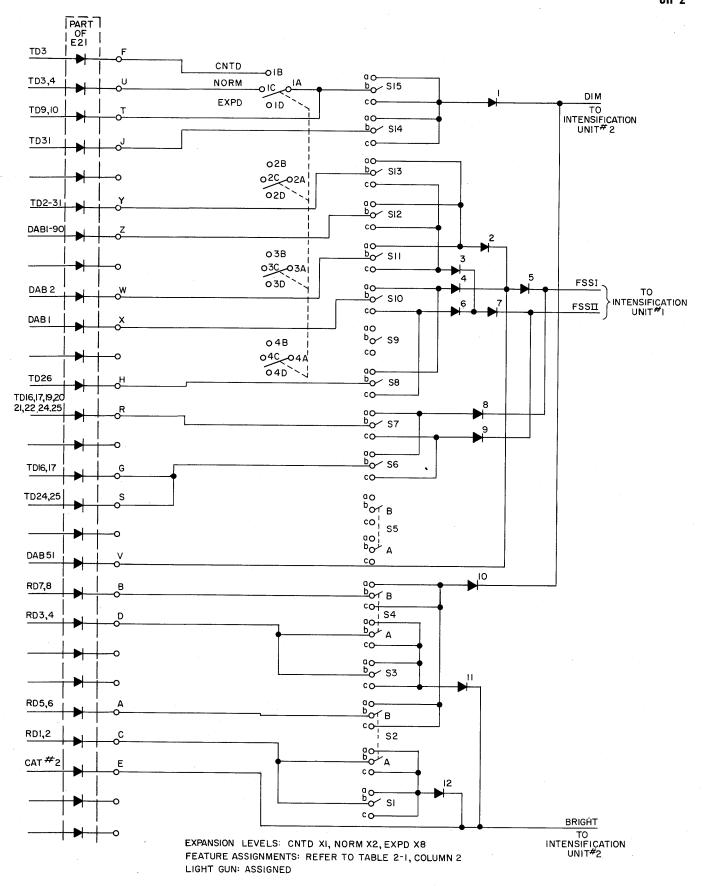

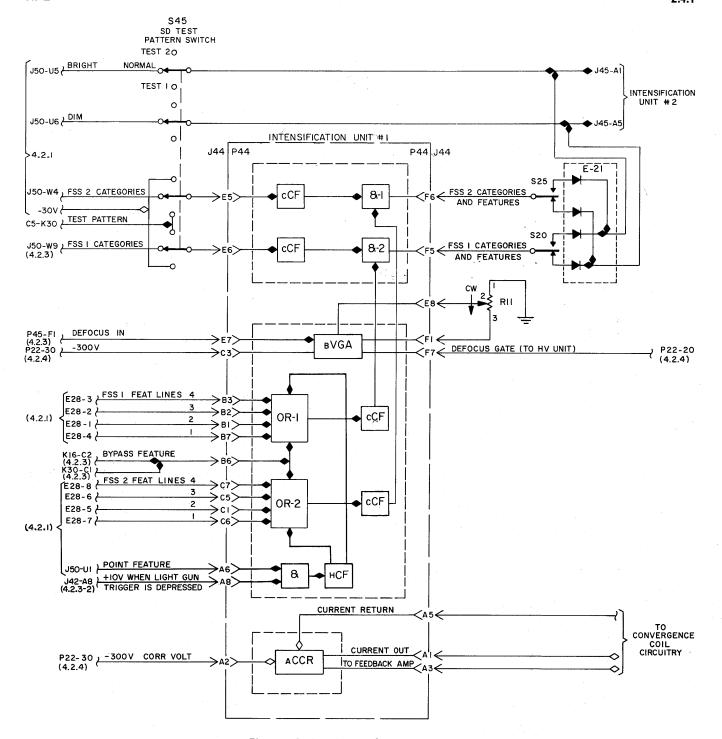

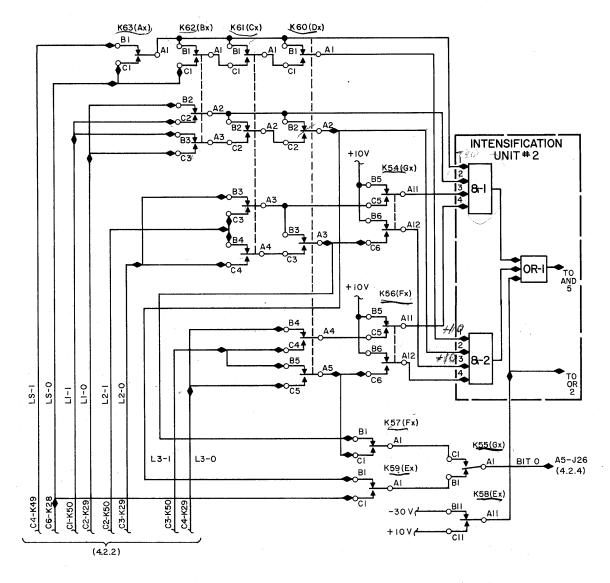

| 2.2.5.1 | Intensification Unit 1                       | 118  |

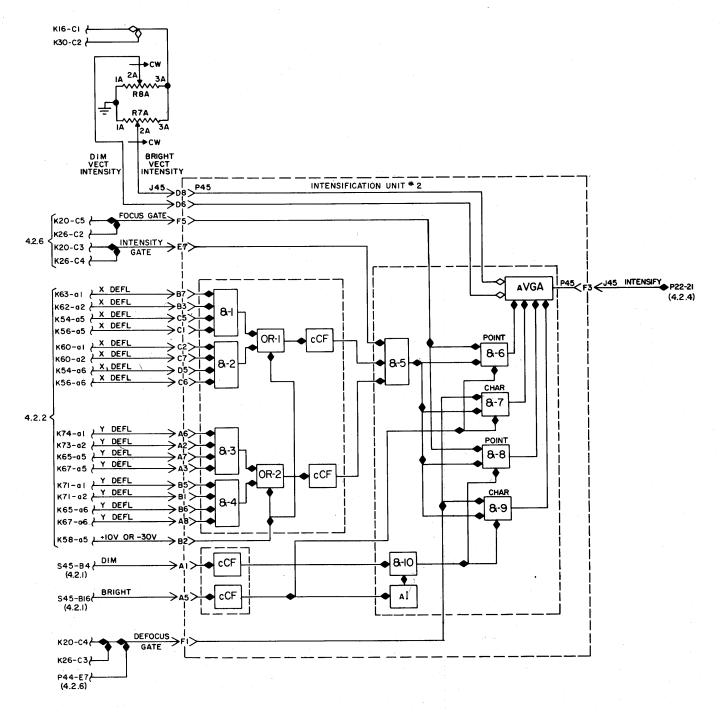

| 2.2.5.2 | Intensification Unit 2                       | 118  |

| 2.2.6   | High-Voltage Power Supplies                  | 119  |

| 2.2.7   | High-Voltage Units                           | 119  |

| 2.3     | Detailed Operation                           | 119  |

| 2.3.1   | Character Selection                          | 119  |

| 2.3.2   | Character Compensation                       | 119  |

| 2.3.3   | SDIS Selection                               | 119  |

| 2.3.4   | CAT and DAB Switches                         | 119  |

| 2.3.5   | RD CAT Switches                              | 120  |

| 2.3.6   | Feature Selection Switches                   |      |

| 2.3.7   | Interaction of Feature and CAT Switches      |      |

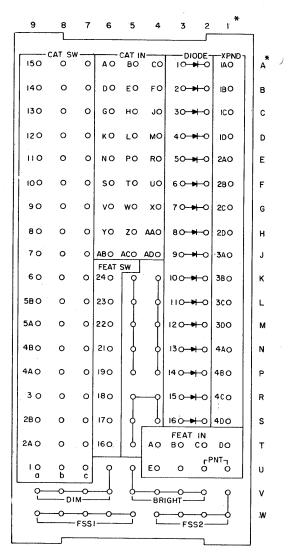

| 2.3.8   | Category Control Panel                       | 120  |

| Неас | ding    |                                                | Page |

|------|---------|------------------------------------------------|------|

|      | 2.3.8.1 | CAT IN                                         | 121  |

|      | 2.3.8.2 | CAT SW                                         | 123  |

|      | 2.3.8.3 | DIODE                                          | 123  |

|      | 2.3.8.4 | EXPD                                           | 123  |

|      | 2.3.8.5 | FEAT IN                                        | 123  |

|      | 2.3.8.6 | FEAT SW                                        | 123  |

|      | 2.3.8.7 | Output Jacks                                   | 123  |

|      | 2.3.9   | Intensity Levels                               | 123  |

|      | 2.3.10  | Patching Procedure                             | 123  |

|      | 2.4     | Intensification                                | 124  |

|      | 2.4.1   | Intensification Unit 1                         | 124  |

|      | 2.4.2   | Intensification Unit 2                         | 126  |

|      | 2.5     | Message-Positioning                            | 127  |

|      | 2.6     | Rotary Switch and Plugboard Control            | 129  |

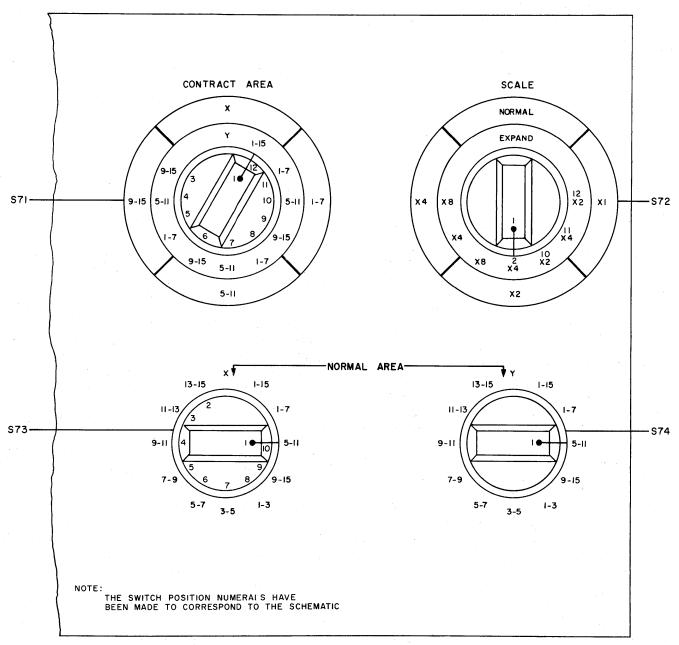

|      | 2.6.1   | Expansion and Off-Centering Rotary Switches    | 129  |

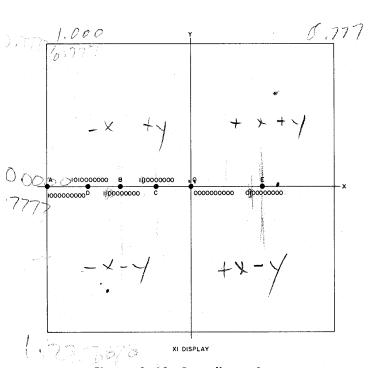

|      | 2.6.1.1 | Contracted Expansion Level and Area Assignment | 130  |

|      | 2.6.1.2 | Normal and Expanded Expansion Level Selections | 131  |

|      | 2.6.1.3 | Normal Area Off-Centering Selections           | 132  |

|      | 2.6.1.4 | Expanded Area Off-Centering Selections         | 132  |

|      | 2.6.1.5 | Incorrect Combinations                         | 132  |

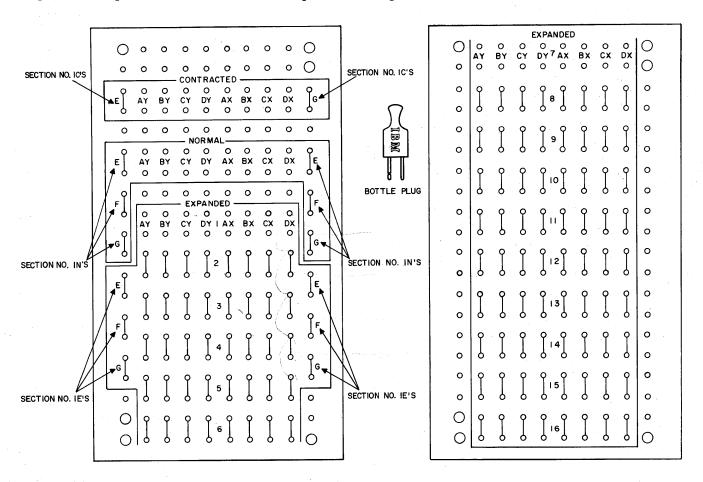

|      | 2.6.2   | Plugboard                                      | 133  |

|      | 2.6.2.1 | Plugboard Section 1                            | 134  |

|      | 2.6.2.2 | Plugboard Section 2                            | 135  |

|      | 2.6.2.3 | Plugboard Section 3                            | 135  |

|      | 2.6.2.4 | Situation Display Test Pattern Switch          | 136  |

|      | 2.6.2.5 | Control Panel Layout                           | 136  |

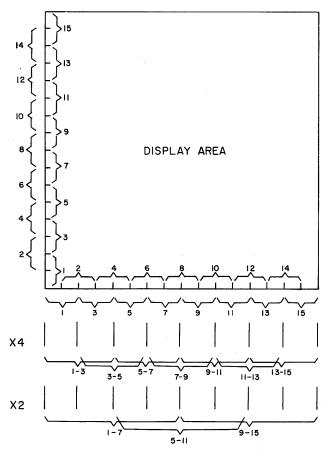

|      | 2.6.3   | Magnitude Bit Selection                        | 138  |

|      | 2.6.4   | Digit 0 Selection, X2 Expansion                | 138  |

|      | 2.6.5   | Digit 0 Selection, X4 Expansion                | 141  |

|      | 2.6.6   | Digit 0 Selection, X8 Expansion                | 142  |

|      | 2.6.7   | Intensification Selection                      | 142  |

|      | 2.6.7.1 | Intensification of X1 Displays                 | 142  |

|      | 2.6.7.2 | Intensification of X2, X4, and X8 Displays     | 142  |

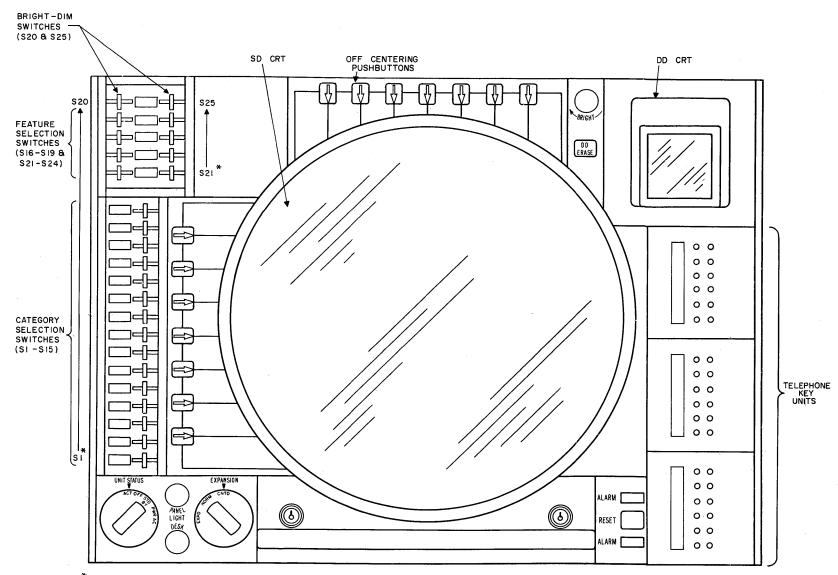

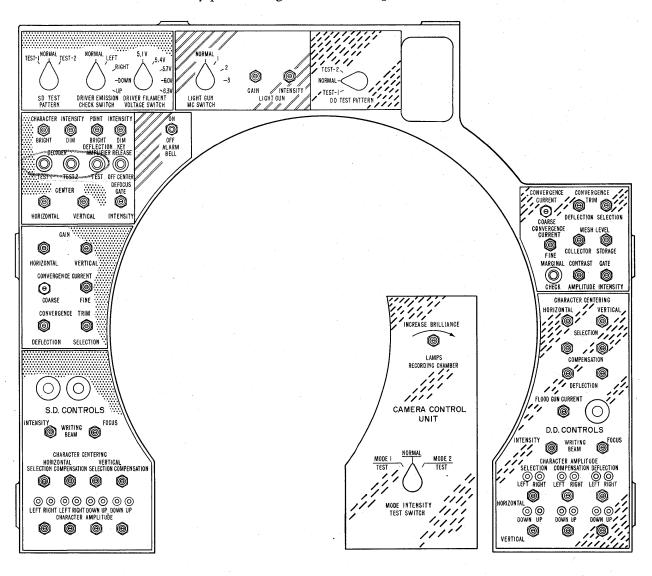

|      | 2.7     | SD Console Subpanel Controls                   | 145  |

| Heading |                                                       | Page  |

|---------|-------------------------------------------------------|-------|

| 2.7.1   | Situation Display Controls                            | 145   |

| 2.7.2   | Light Gun Controls                                    | 146   |

| 2.7.3   | Alarm Bell Control                                    | 146   |

| СНАРТЕ  | R 3 DRUM INPUTS TO SITUATION DISPLAY ELEMENTS         | 147   |

| 3.1     | General                                               | . 147 |

| 3.2     | Timing and Control Signals                            | 147   |

| 3.3     | Display Information Signals                           | . 147 |

| 3.3.1   | TD Tabular Track Message Drum Layout                  | . 147 |

| 3.3.2   | TD Tabular Information Message Drum Layout            | 148   |

| 3.3.3   | TD Vector Message Drum Layout                         | 148   |

| 3.3.4   | RD Message Drum Layout                                | 148   |

| СНАРТЕ  | R 4 SITUATION DISPLAY GENERATOR ELEMENT               | . 151 |

| SECTIO  | ON 1 SCOPE                                            | . 151 |

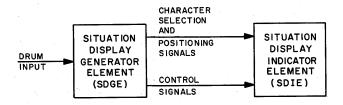

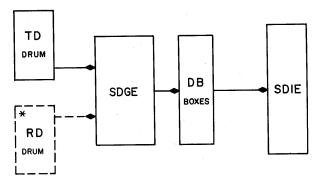

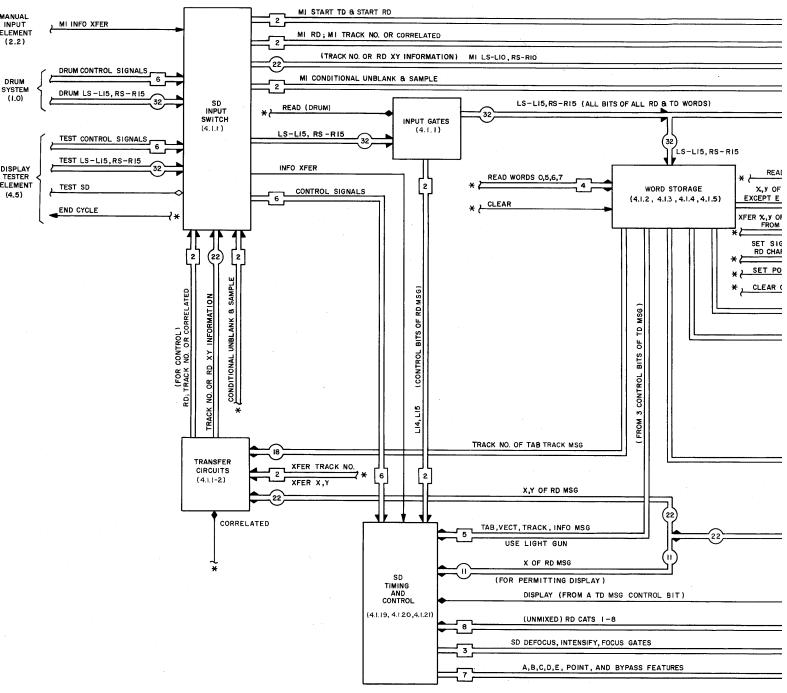

| 1.1     | Objective                                             | . 151 |

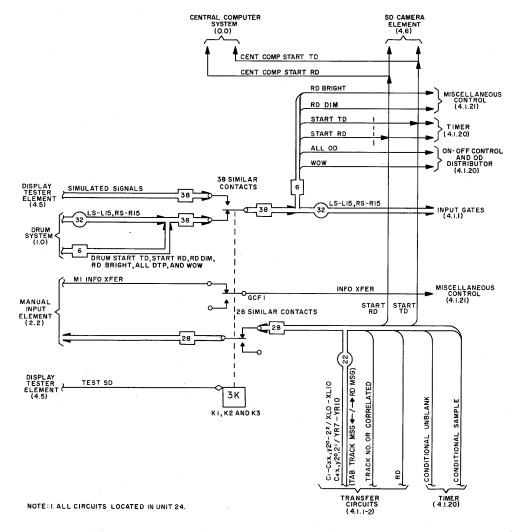

| 1.2     | Inputs to the SDGE                                    | . 151 |

| 1.2.1   | Information and Control Signals from the Drum         | . 151 |

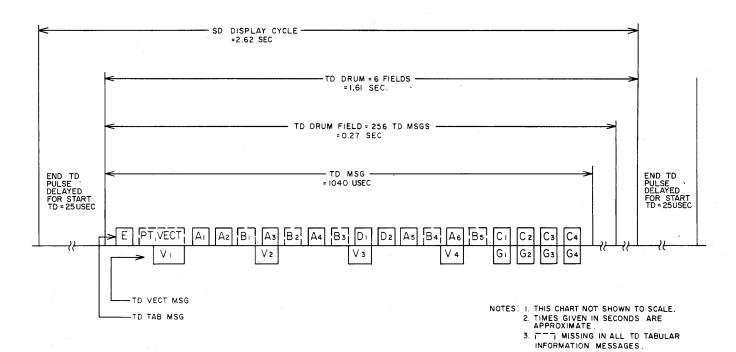

| 1.2.2   | Drum Message Arrangement                              | . 151 |

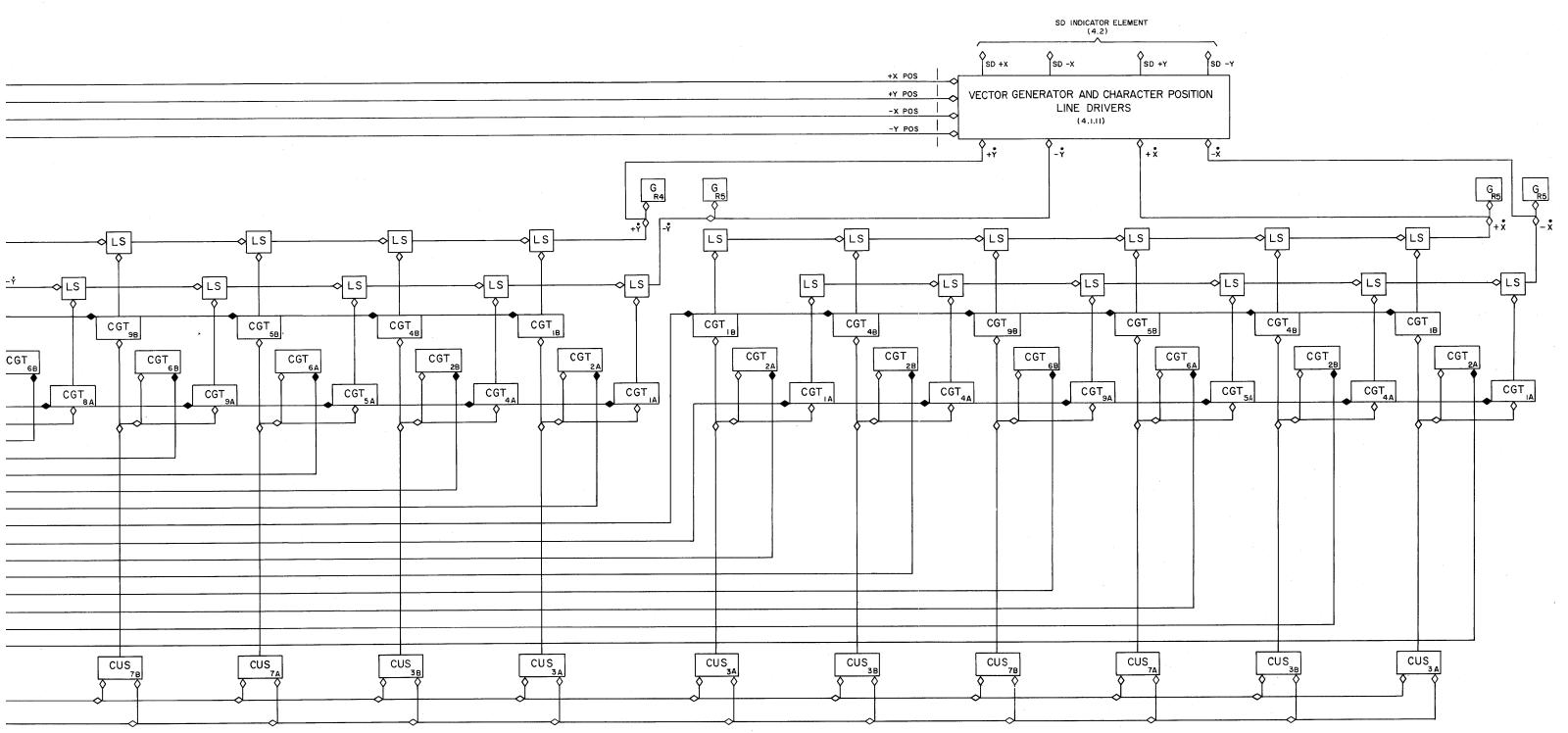

| 1.3     | Outputs from the SDGE                                 | . 151 |

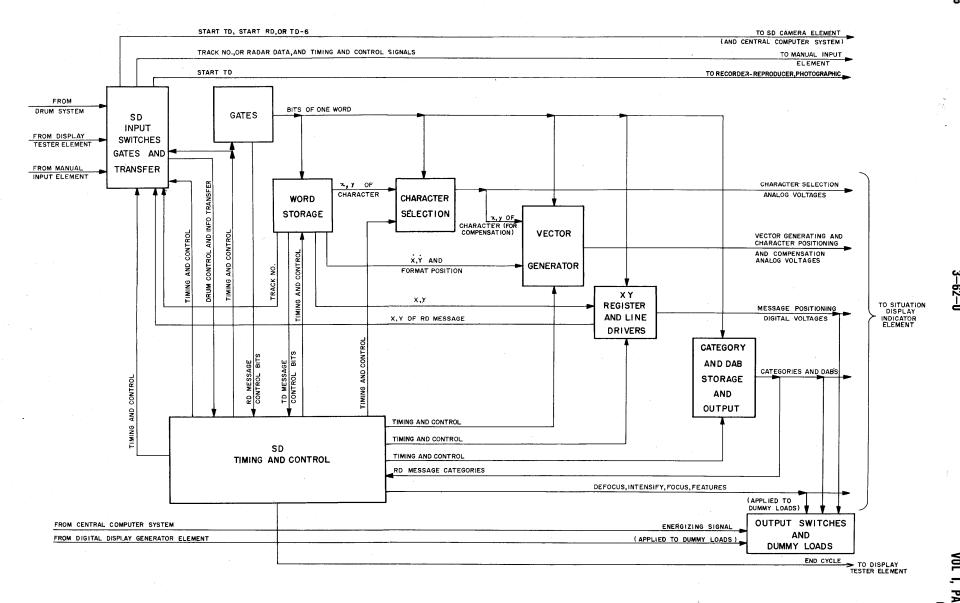

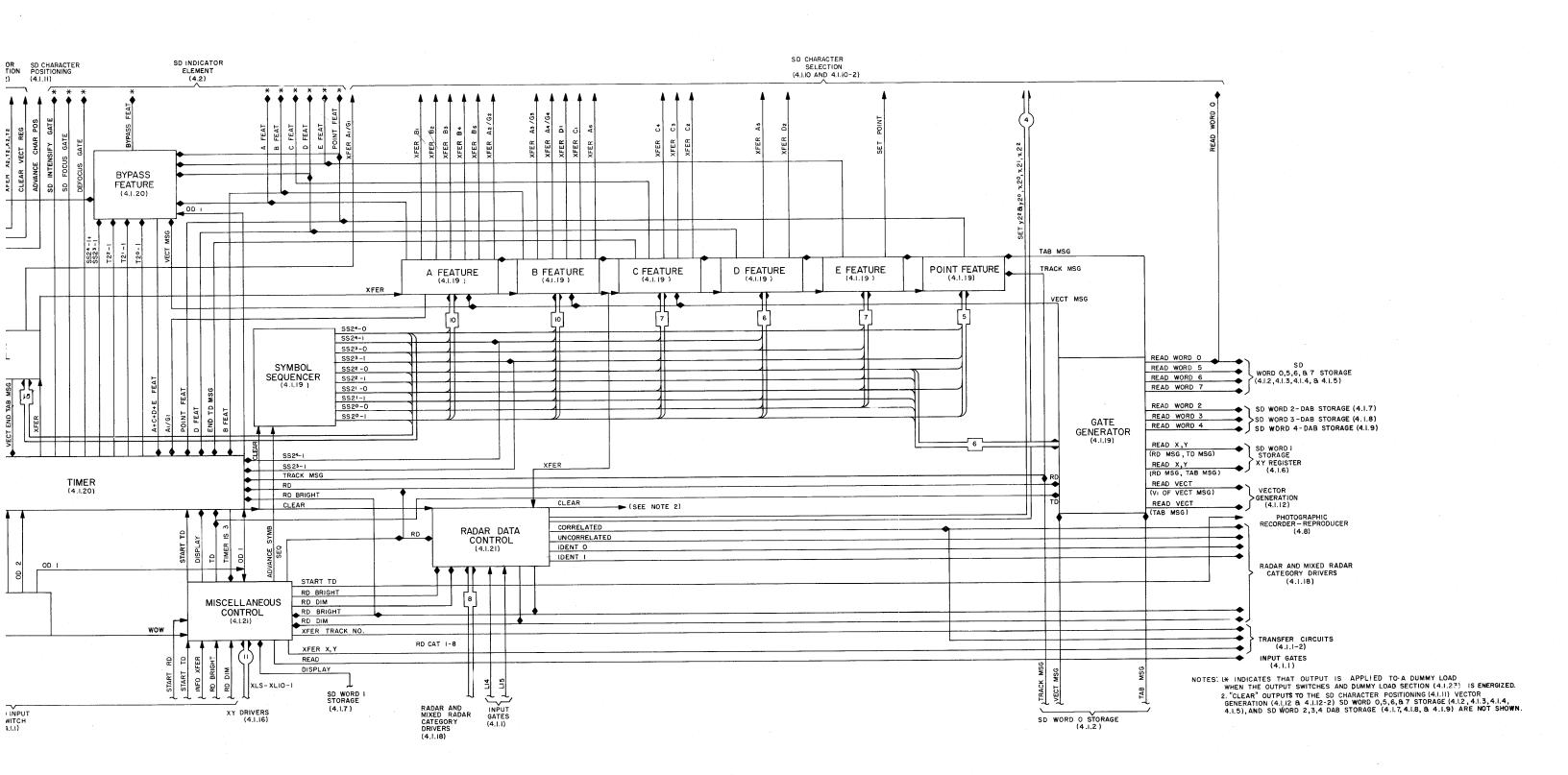

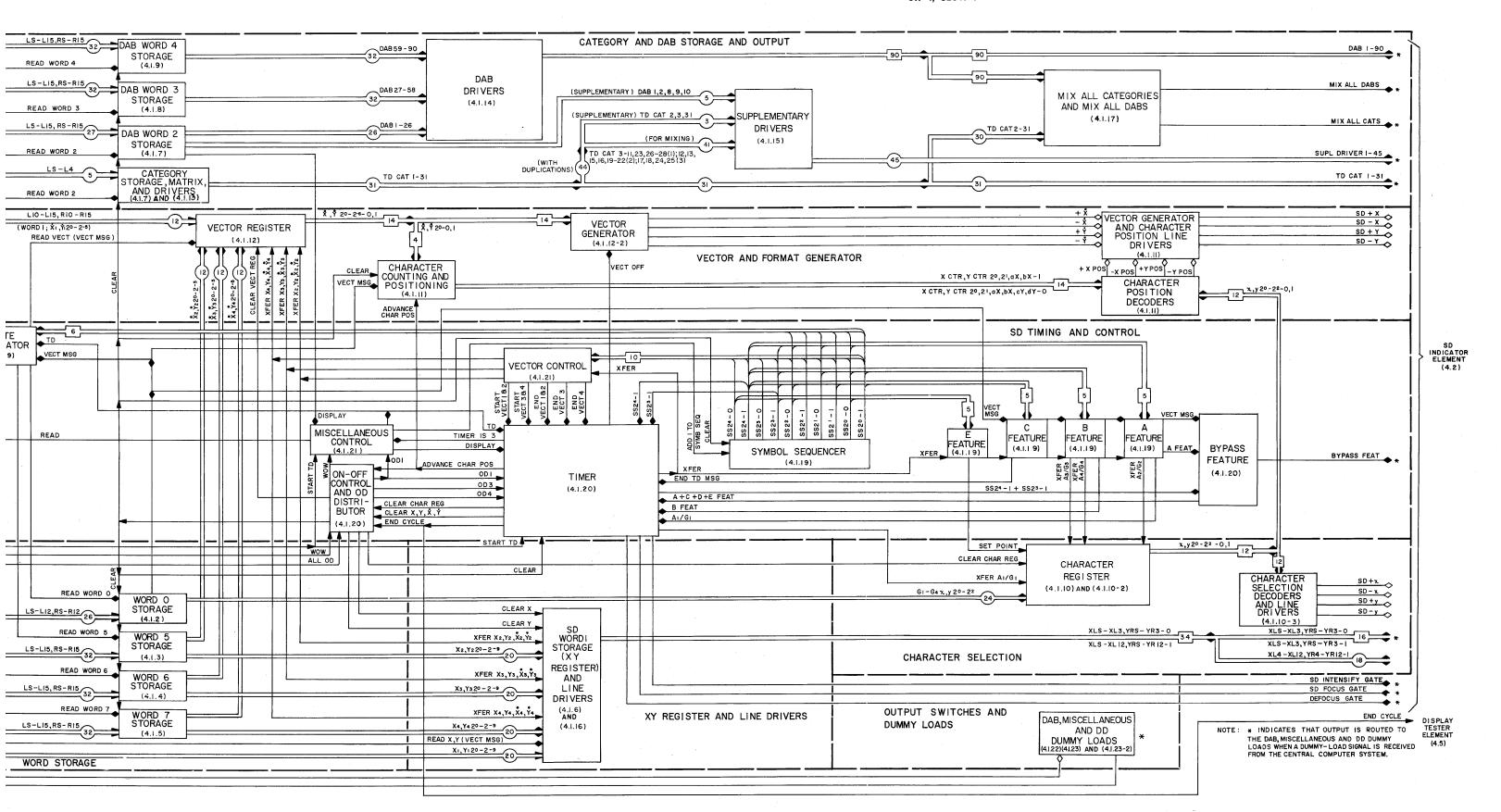

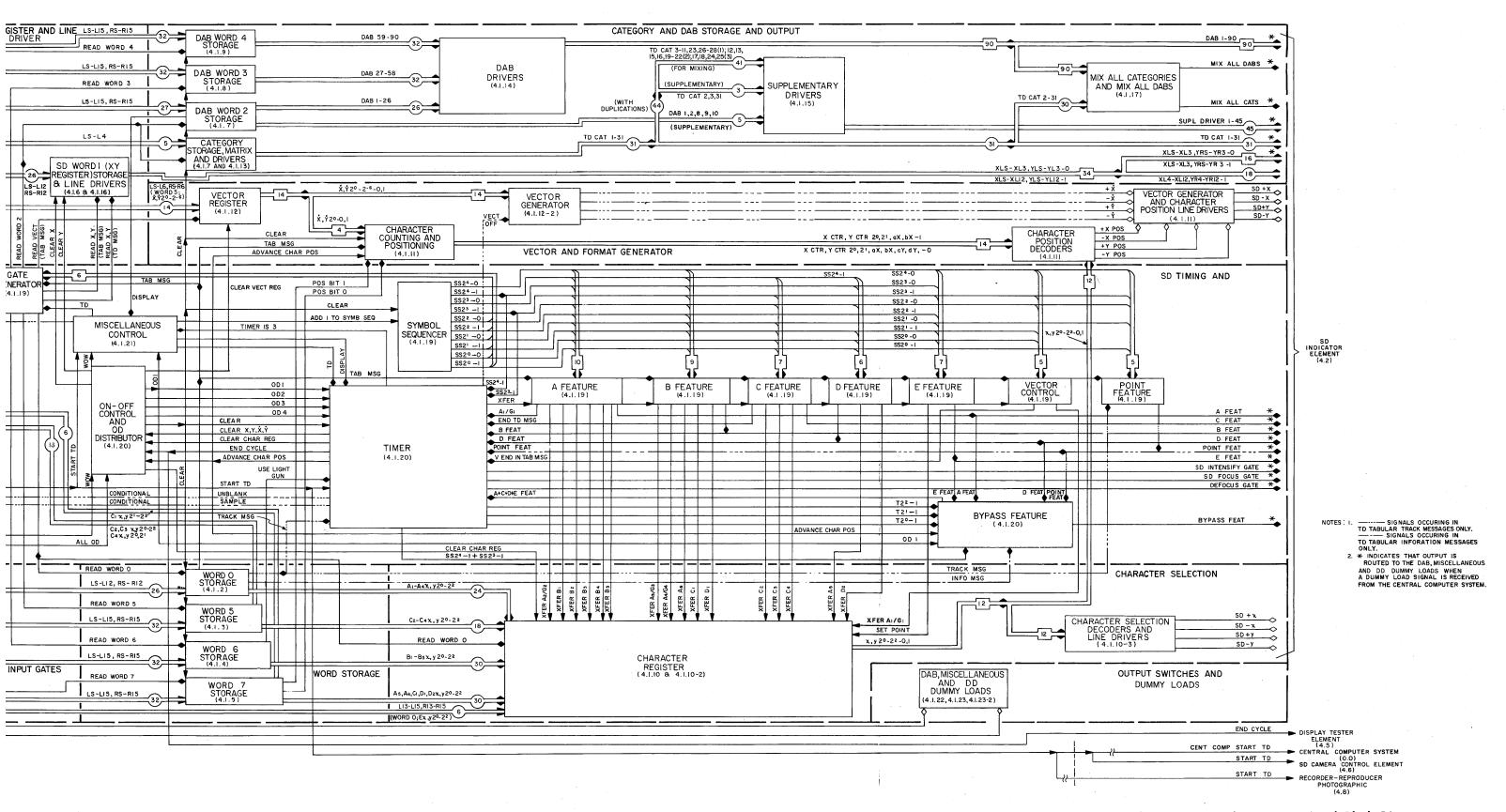

| 1.4     | SDGE Functional Operation                             | 151   |

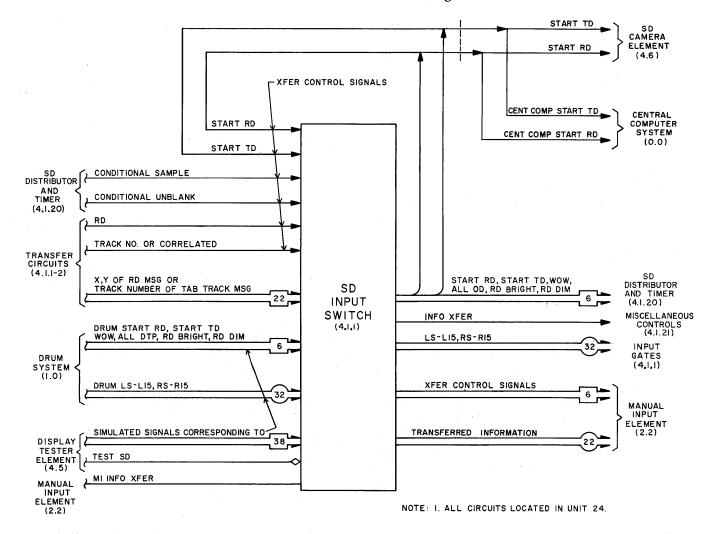

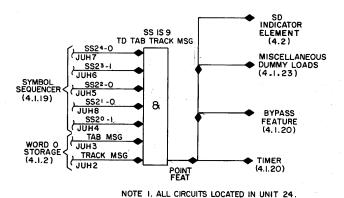

| 1.4.1   | SD Input Switch Section                               | . 151 |

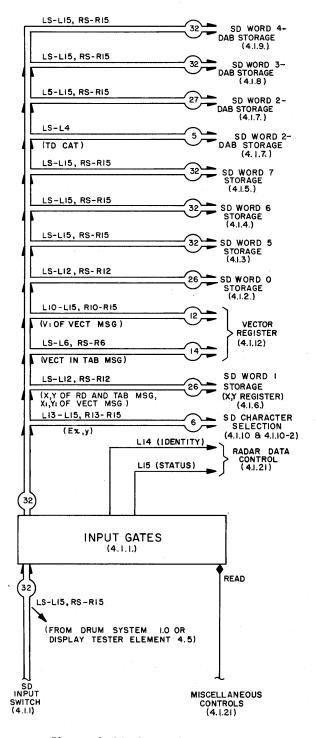

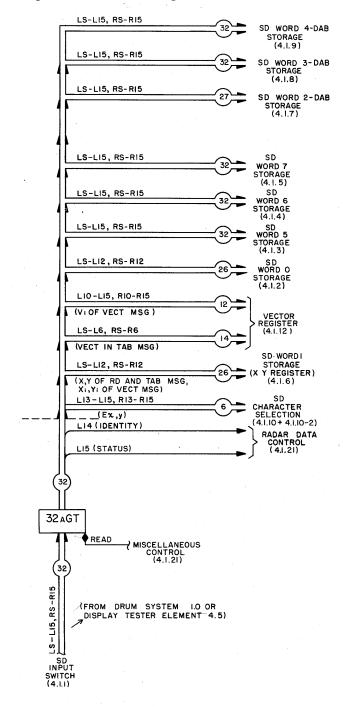

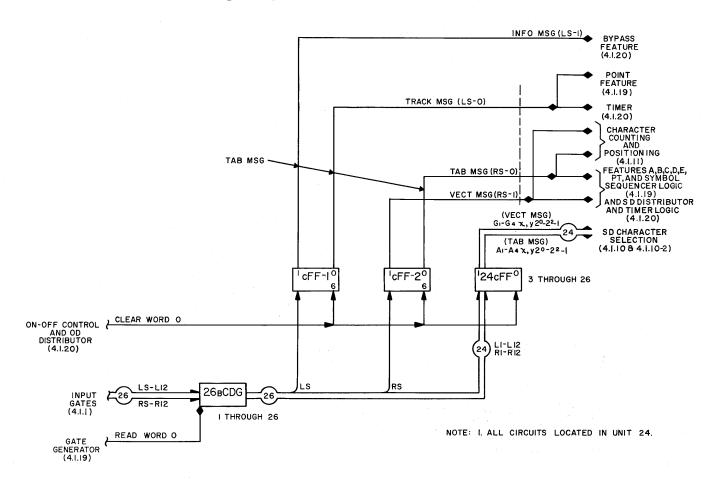

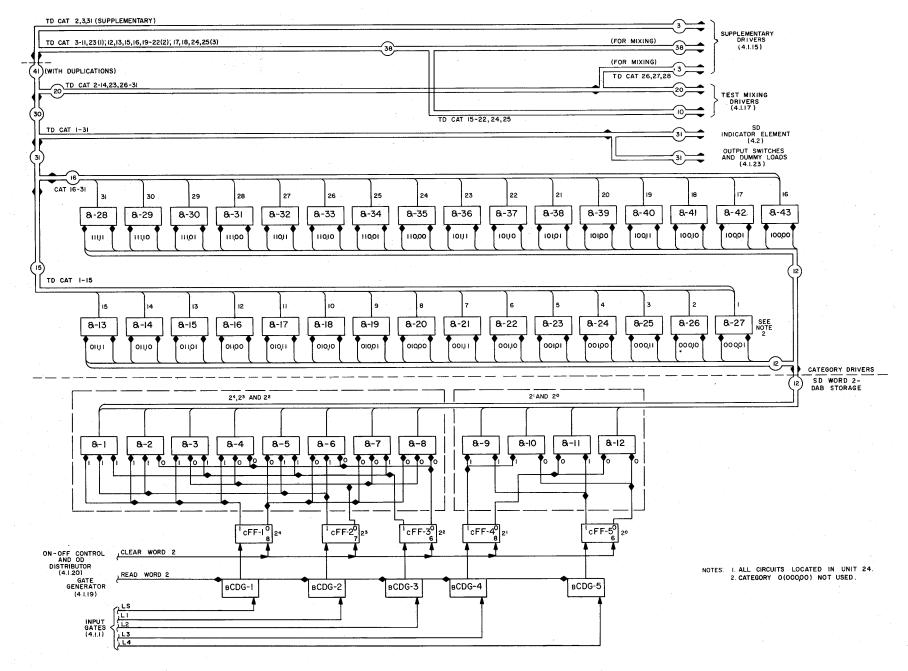

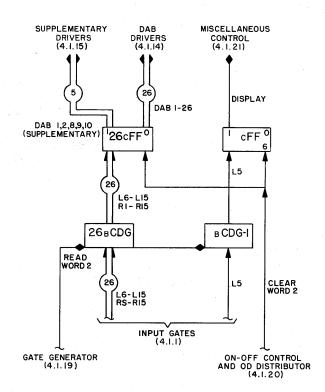

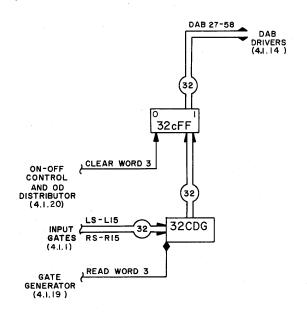

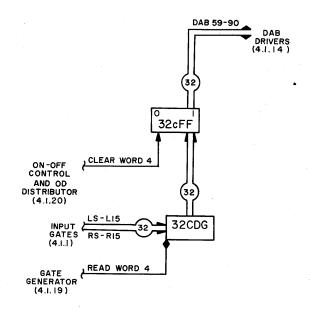

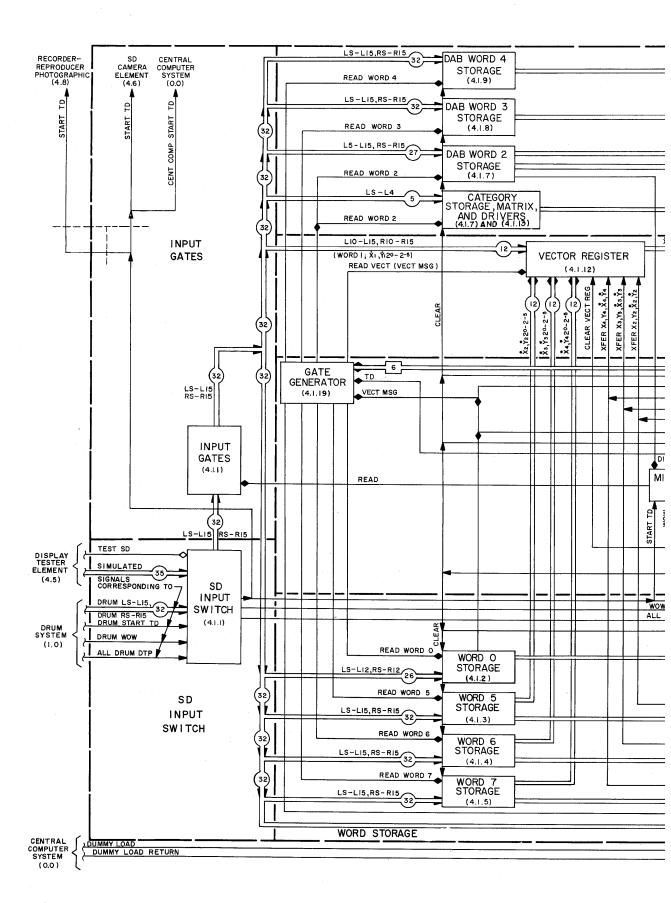

| 1.4.2   | Input Gates and Word Storage Section                  | 152   |

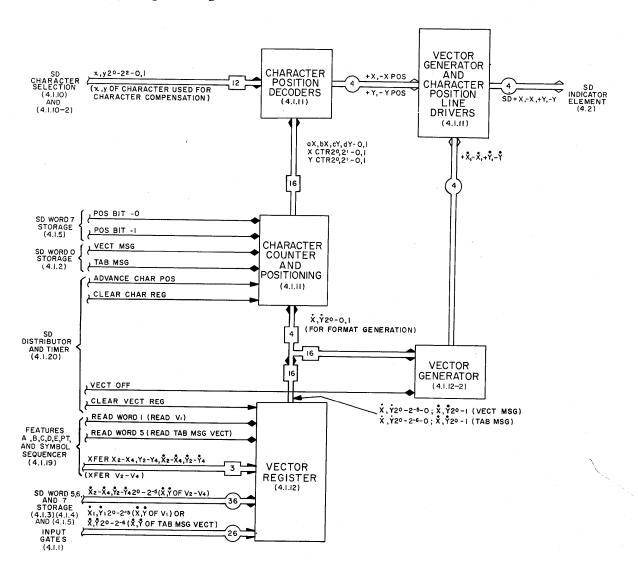

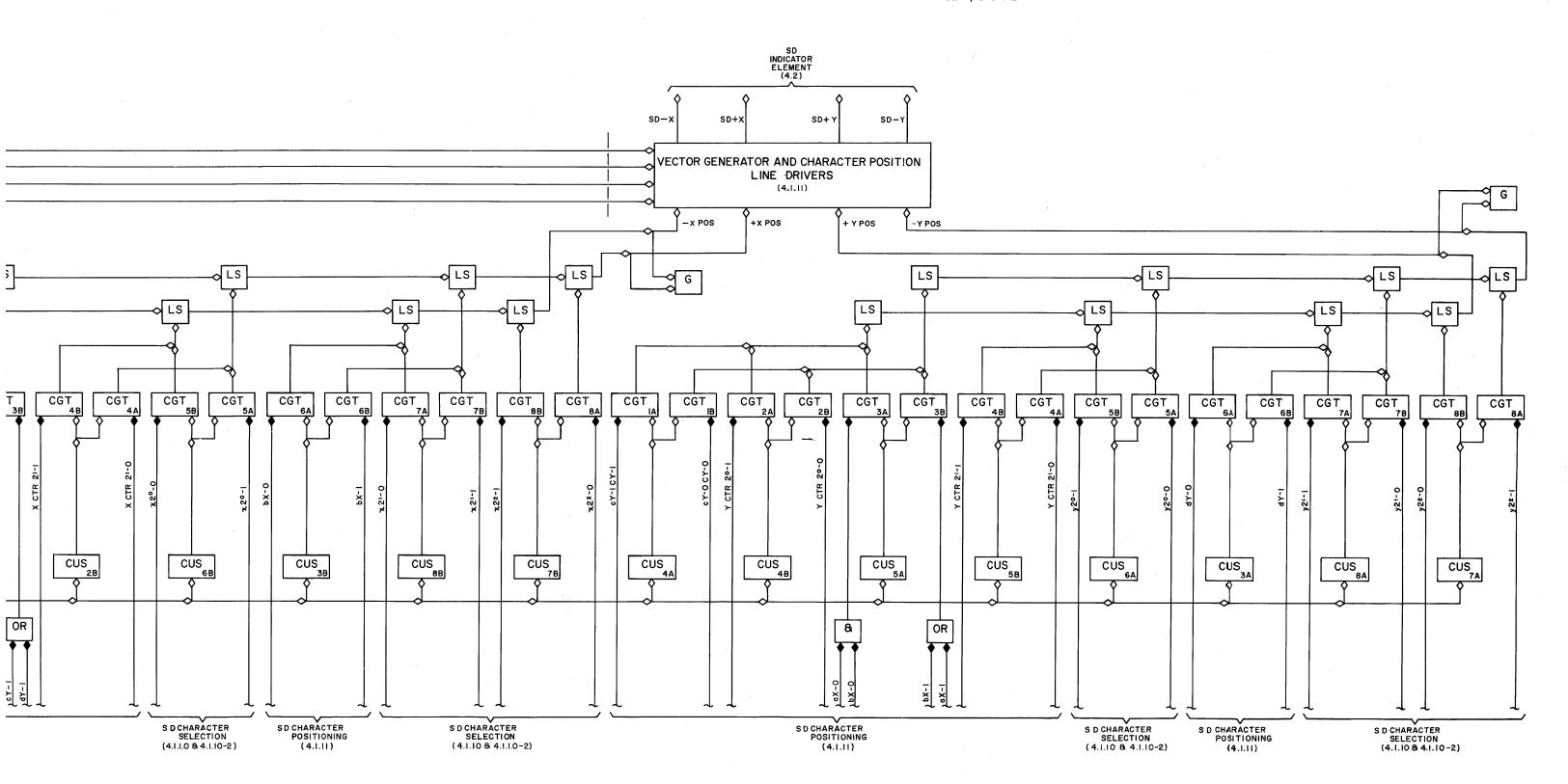

| 1.4.3   | Character Selection Section                           | 153   |

| 1.4.4   | Character Compensation and Positioning, and Vector    |       |

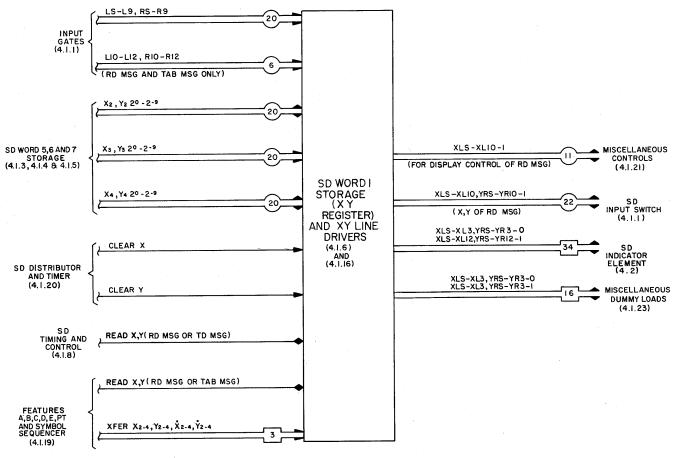

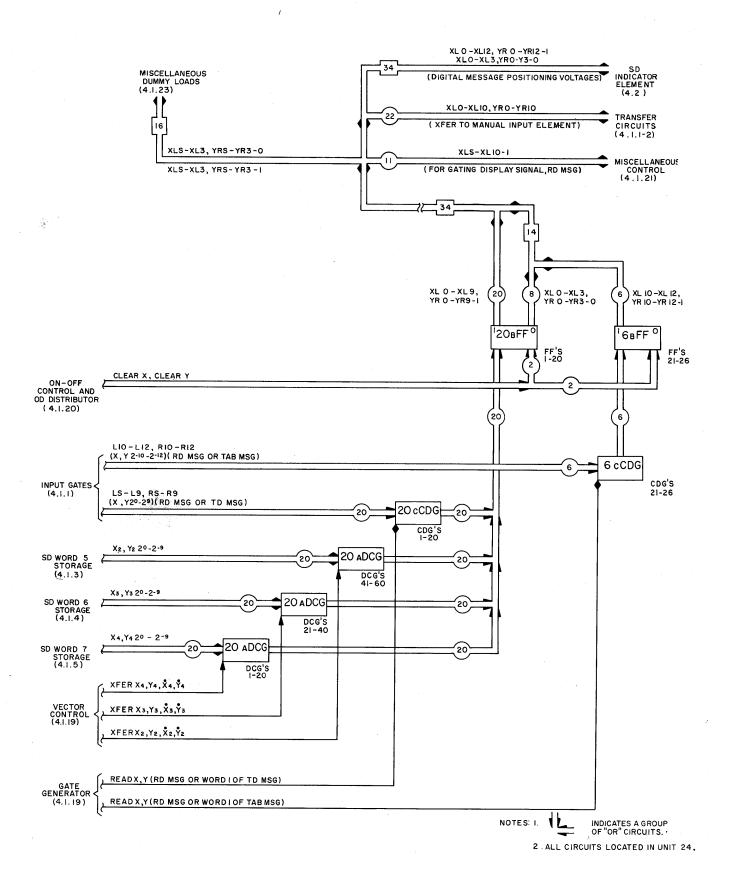

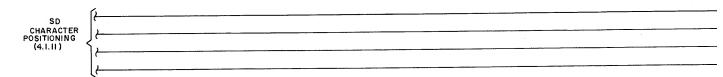

| 1.4.5   | Message Positioning (XY Register and Drivers Section) | 155   |

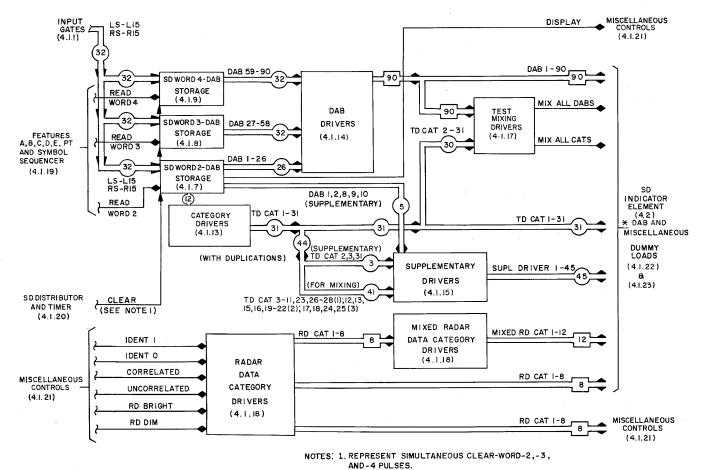

| 1.4.6   | Category and DAB Storage and Output Section           | 156   |

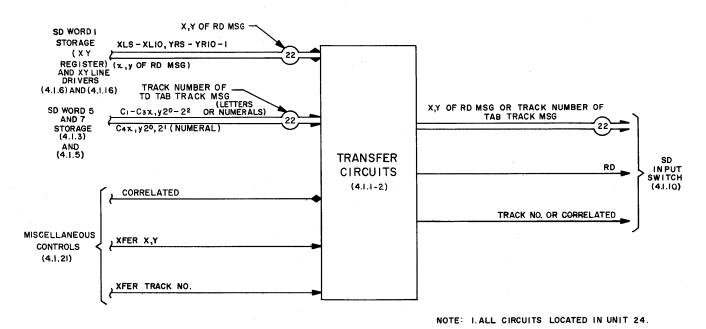

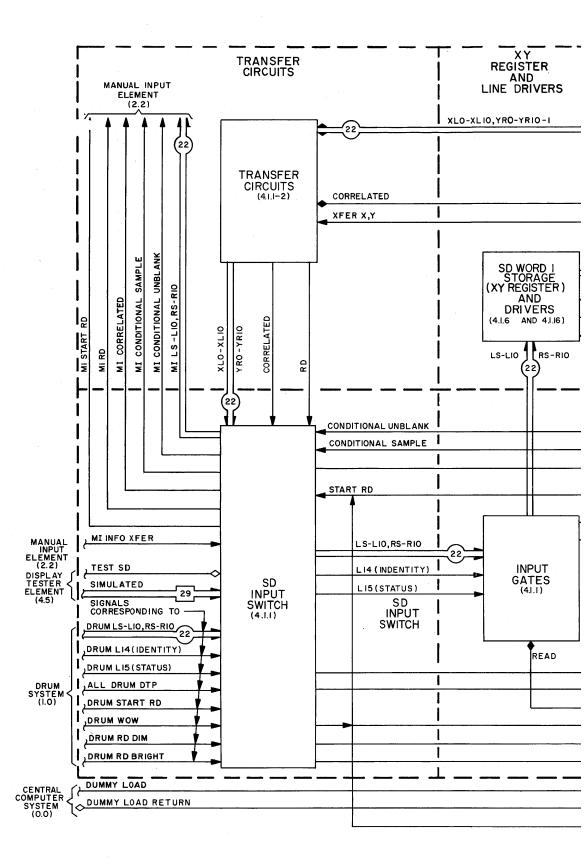

| 1.4.7   | Transfer Circuits Section                             | . 157 |

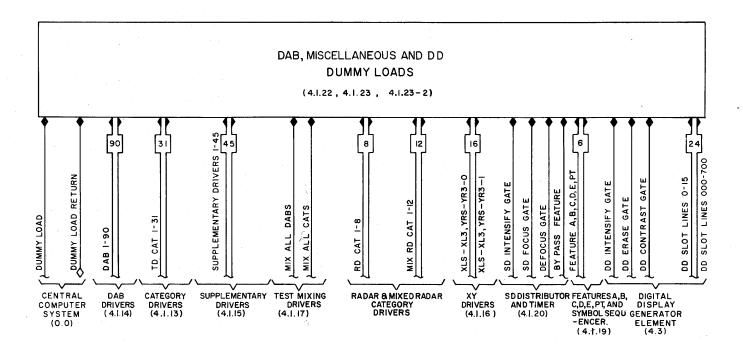

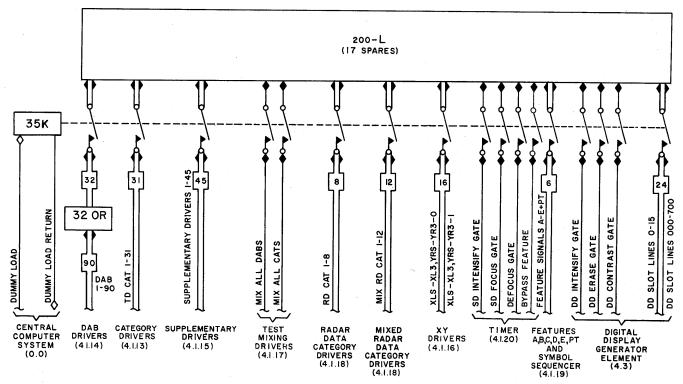

| 1.4.8   | Dummy Load Section                                    | . 157 |

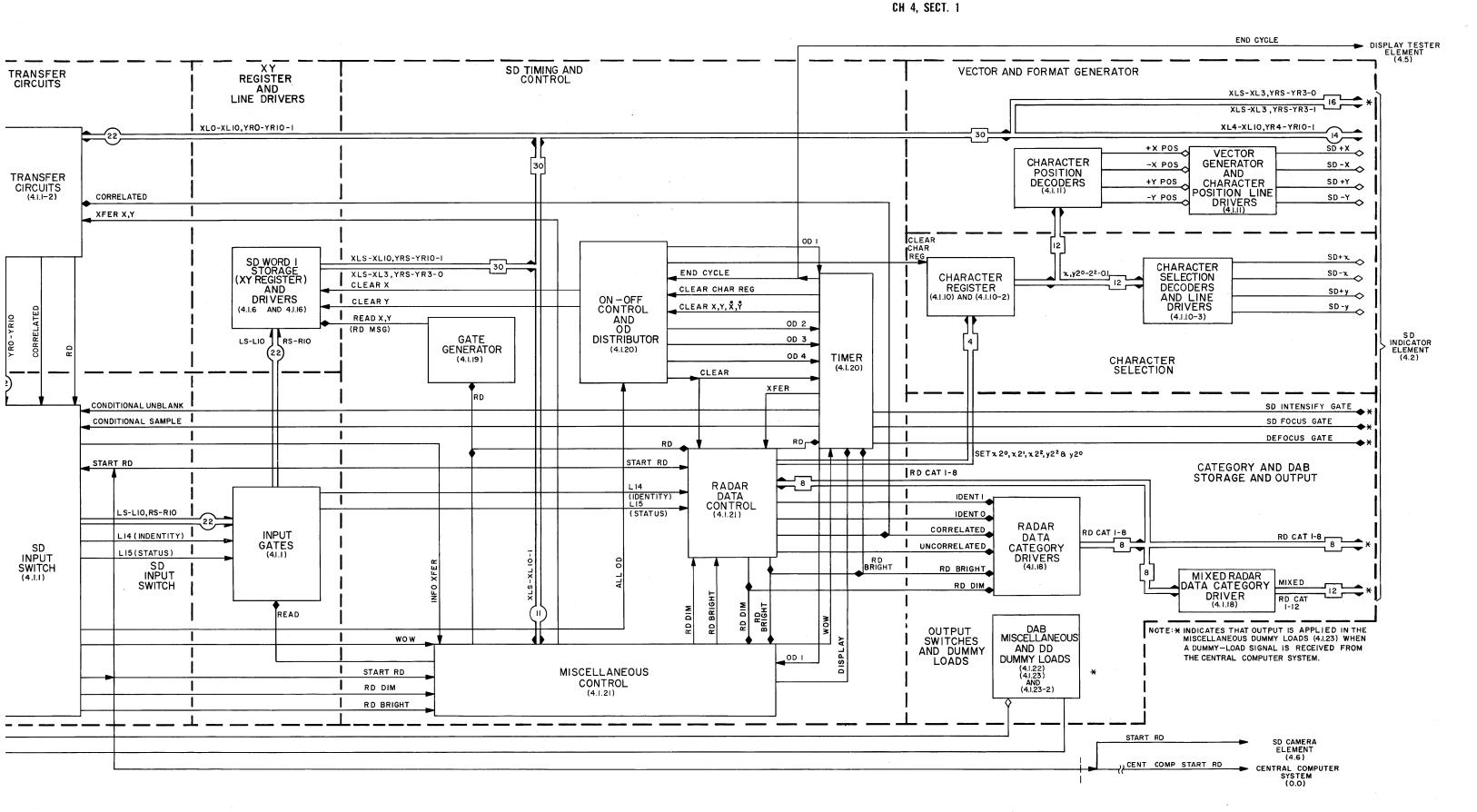

| 1.4.9   | SD Timing and Control Section                         | 159   |

| 1.4.9.1 | RD Message                                            | 160   |

| 1.4.9.2 | TD Vector Message                                     |       |

| 1 4 0 3 | TD Tabular Messages                                   | 160   |

| Head | ling    |                                                           | Page |

|------|---------|-----------------------------------------------------------|------|

|      | SECTION | V 2 SDGE, DETAILED THEORY OF OPERATION                    | 161  |

|      | 2.1     | Introduction                                              | 161  |

|      | 2.2     | SD Input Switch and Drum Signals                          | 161  |

|      | 2.2.1   | Drum System Signals                                       | 161  |

|      | 2.2.2   | RD Messages                                               | 161  |

|      | 2.2.3   | TD Messages                                               | 161  |

|      | 2.3     | Information Transfer to the MI Element and Test Operation | 161  |

|      | 2.3.1   | RD Message                                                | 161  |

|      | 2.3.2   | TD Vector Message                                         | 161  |

|      | 2.3.3   | TD Tabular Track Message                                  | 161  |

|      | 2.3.4   | TD Tabular Information Message                            | 162  |

|      | 2.3.5   | Test Operation                                            | 162  |

|      | 2.4     | Input Gates Section                                       | 162  |

|      | 2.4.1   | RD Message                                                | 163  |

|      | 2.4.2   | TD Messages                                               | 163  |

|      | 2.4.2.1 | TD Vector and Tabular Messages                            | 163  |

|      | 2.4.2.2 | TD Vector Messages                                        | 163  |

|      | 2.4.2.3 | TD Tabular Messages                                       | 163  |

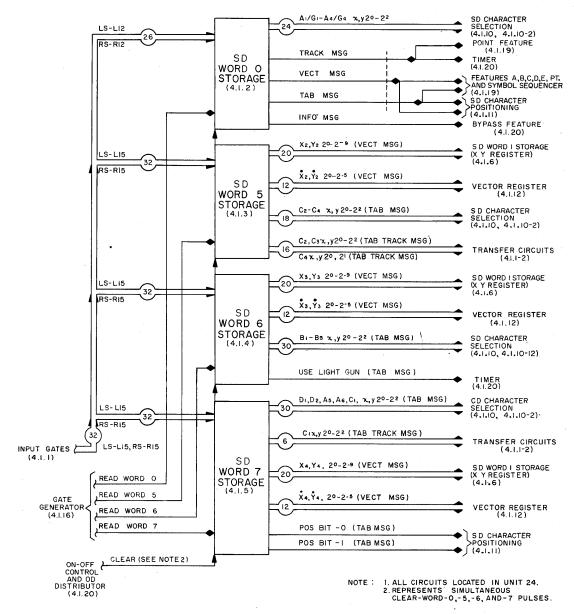

|      | 2.5     | Word Storage                                              | 164  |

|      | 2.5.1   | Word 0 Storage                                            | 164  |

|      | 2.5.1.1 | TD Tabular Message                                        | 164  |

|      | 2.5.1.2 | TD Vector Message                                         | 165  |

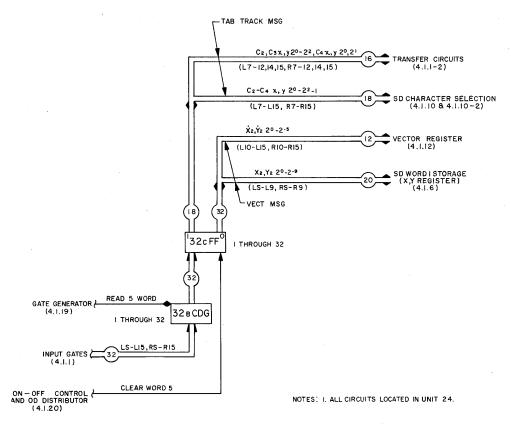

|      | 2.5.2   | Word 5 Storage                                            | 165  |

|      | 2.5.2.1 | TD Tabular Message                                        | 165  |

|      | 2.5.2.2 | TD Vector Message                                         | 167  |

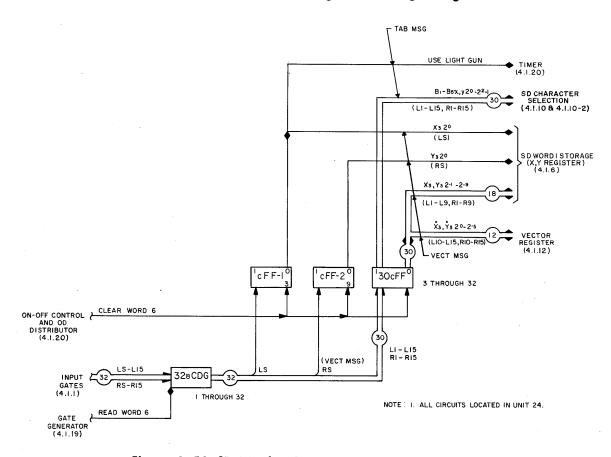

|      | 2.5.3   | Word 6 Storage                                            | 167  |

|      | 2.5.3.1 | TD Tabular Message                                        | 167  |

|      | 2.5.3.2 | TD Vector Message                                         | 167  |

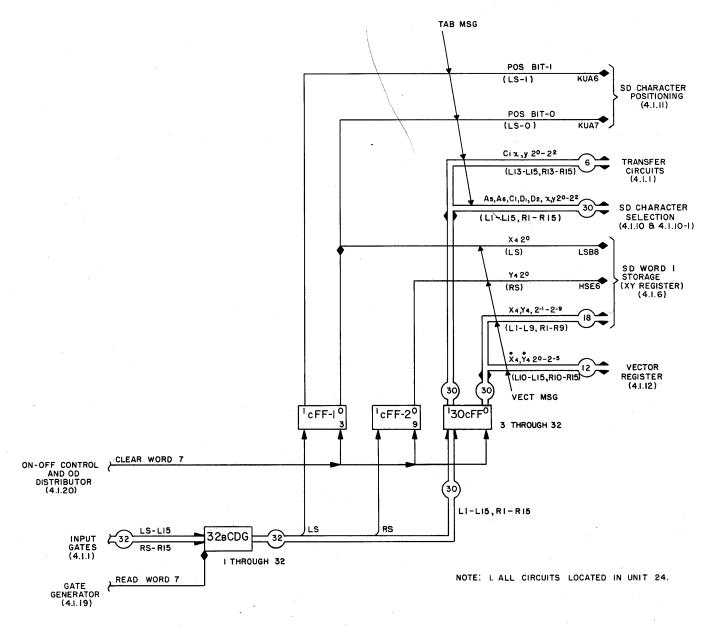

|      | 2.5.4   | Word 7 Storage                                            | 167  |

|      | 2.5.4.1 | TD Tabular Message                                        | 167  |

|      | 2.5.4.2 | TD Vector Message                                         |      |

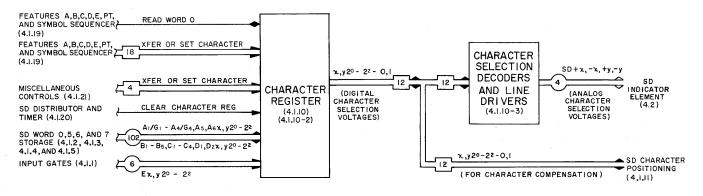

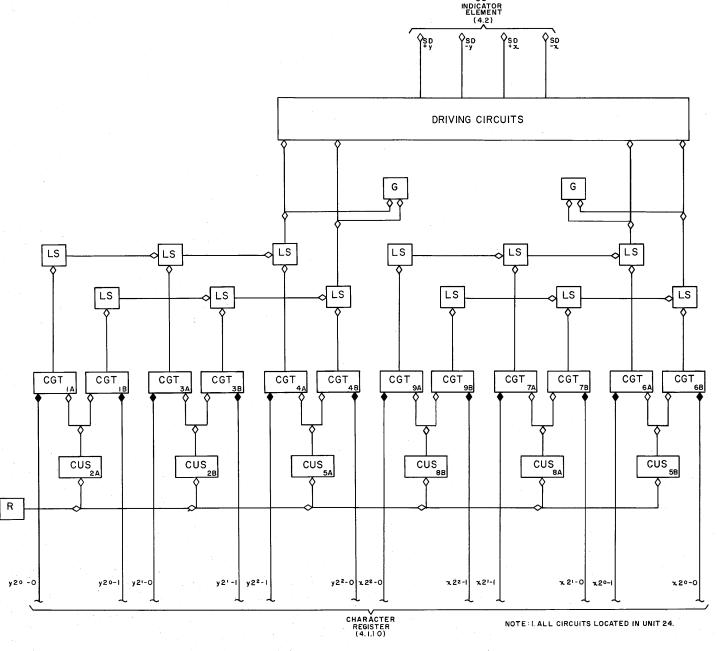

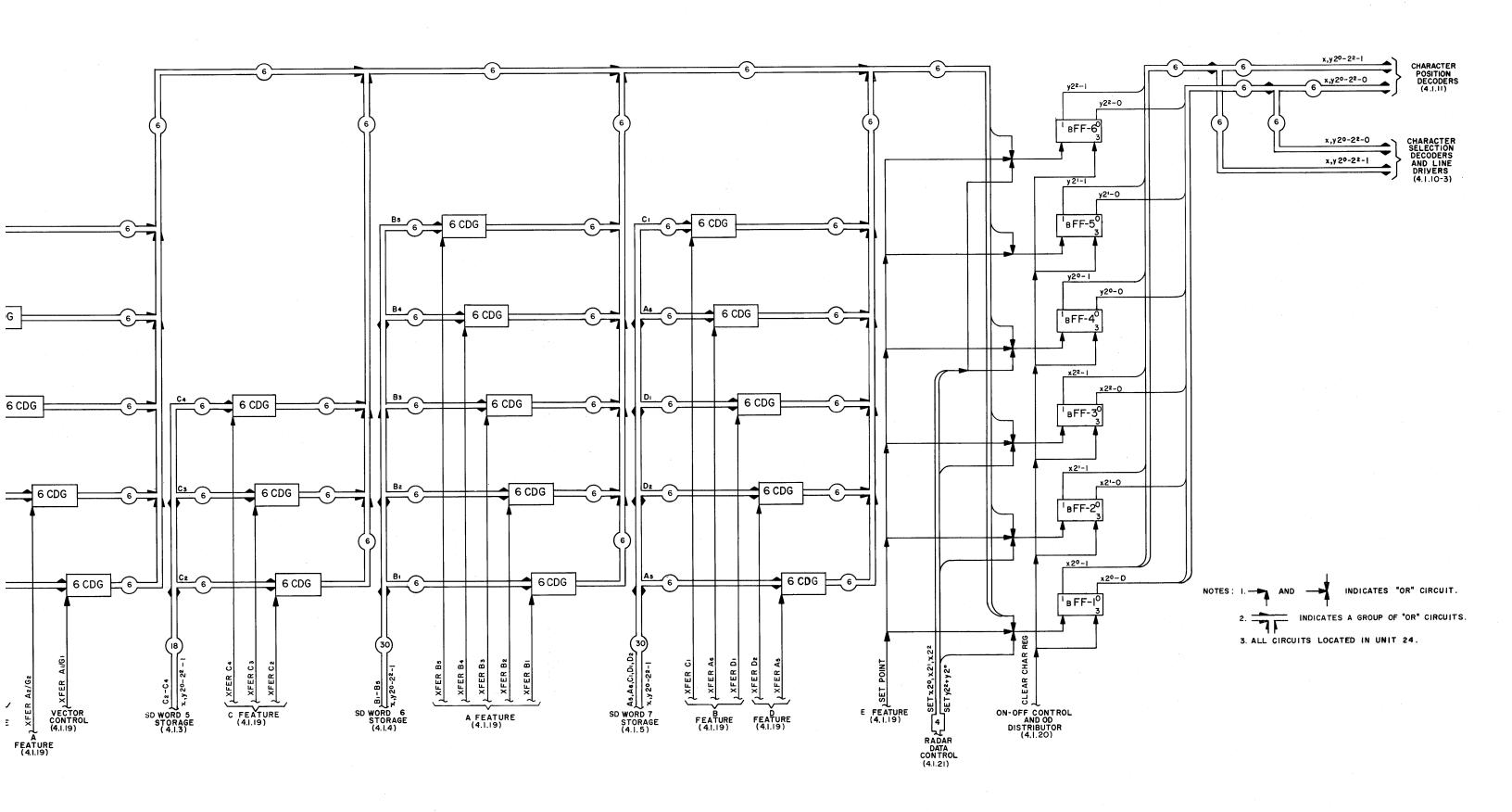

|      | 2.6     | Character Selection Register                              |      |

|      | 2.6.1   | Character Register                                        |      |

|      | 2.6.1.1 | TD Tabular Message                                        | 169  |

| Heading |                                                                                  | Page |

|---------|----------------------------------------------------------------------------------|------|

| 2.6.1.2 | TD Vector Message                                                                | 169  |

| 2.6.1.3 | Radar Message                                                                    | 169  |

| 2.6.2   | Character Selection Decoders and Line Drivers                                    | 169  |

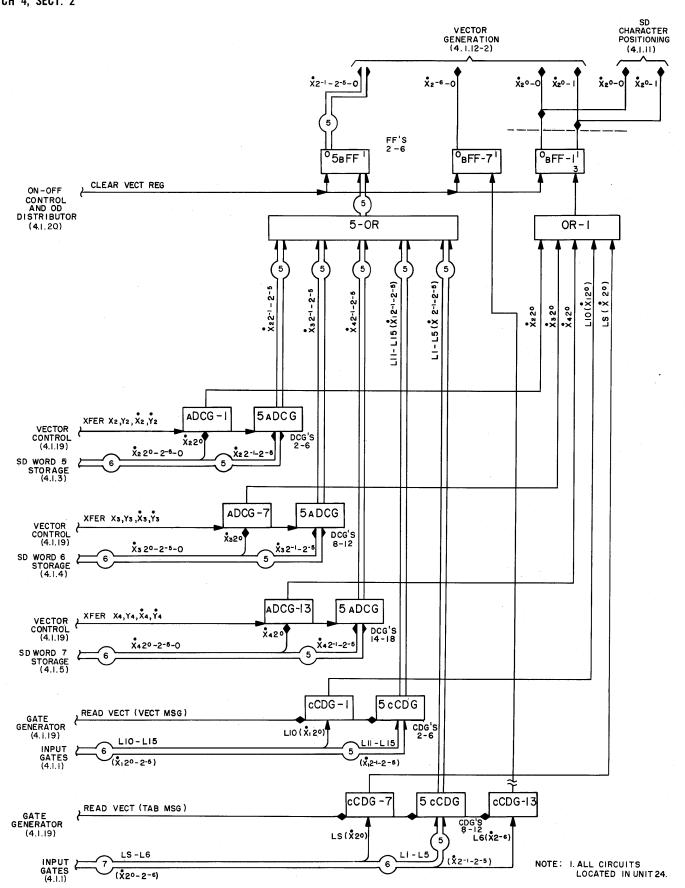

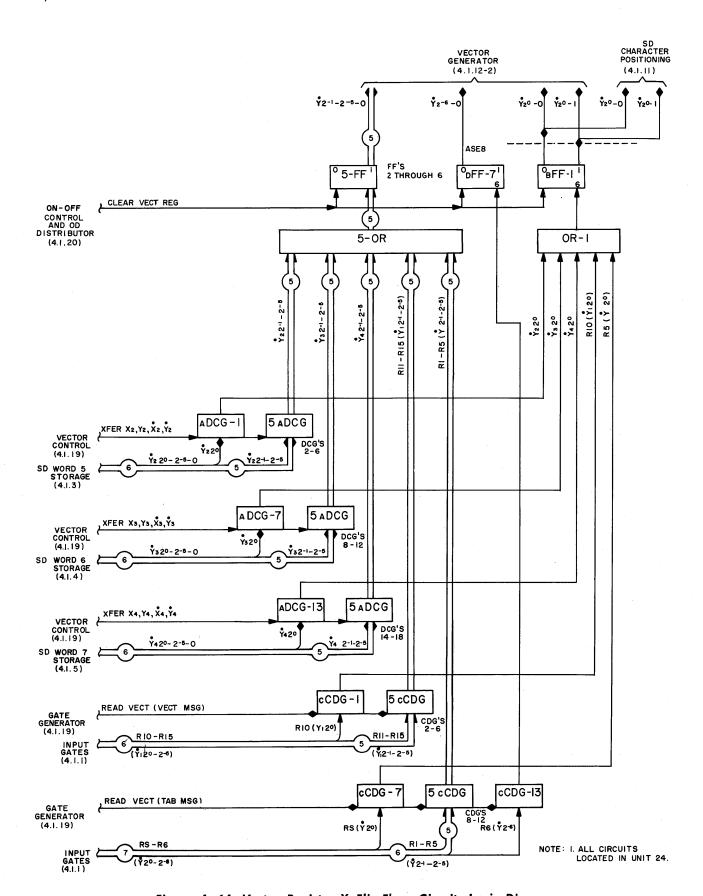

| 2.7     | Character Compensation and Positioning and Vector<br>Generation                  |      |

| 2.7.1   | Character Compensation                                                           | 171  |

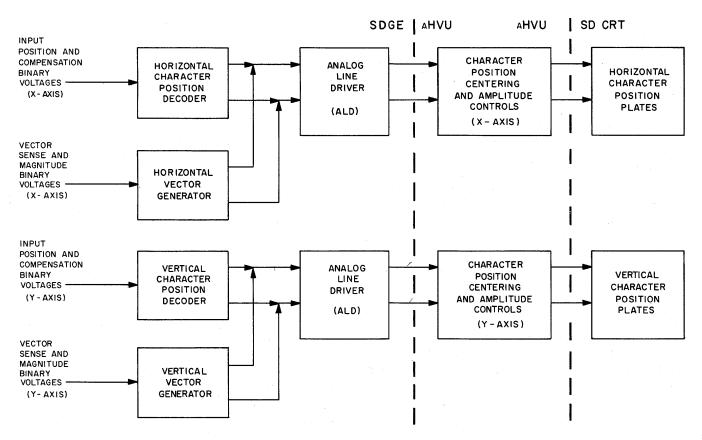

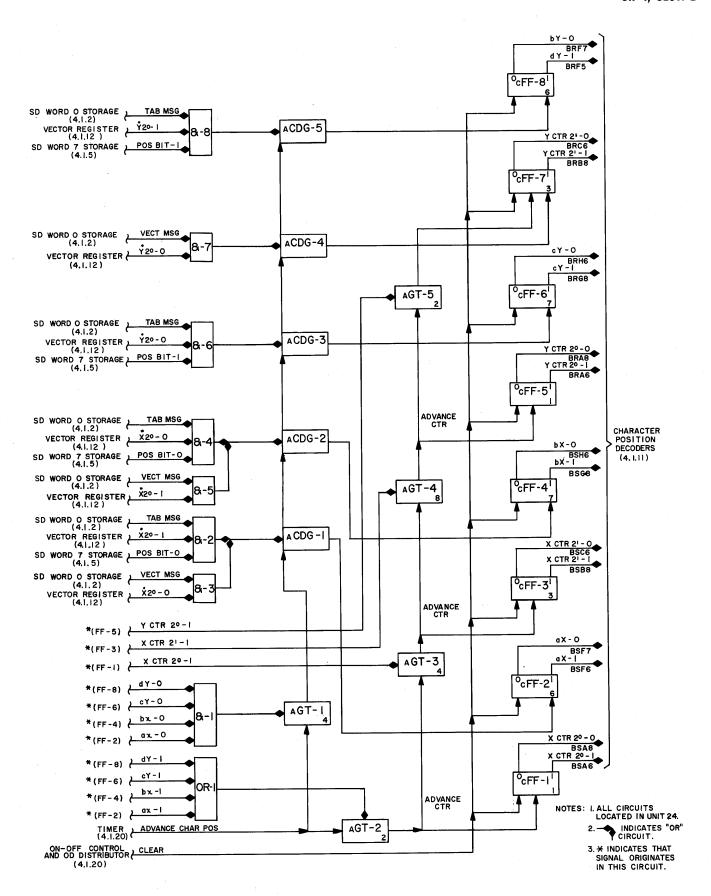

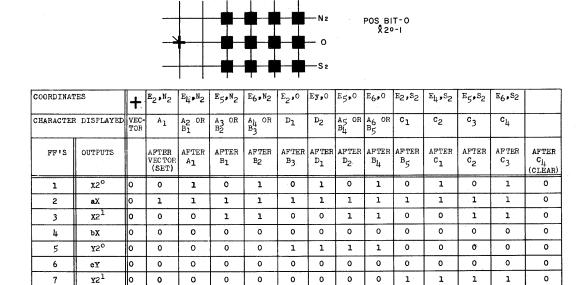

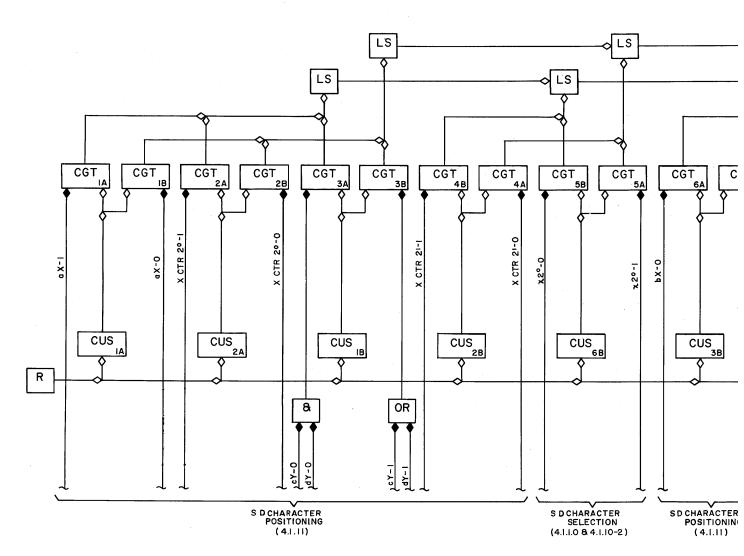

| 2.7.2   | Character Positioning                                                            | 171  |

| 2.7.2.1 | Character Counting and Positioning Circuit (TD Tabular Message)                  |      |

| 2.7.2.2 | Character Counting and Positioning Circuit (TD Vector Message)                   |      |

| 2.7.2.3 | Character Position and Compensation Decoder and Line<br>Drivers                  | 175  |

| 2.7.2.4 | Vector Generator and Character Position Line Drivers                             | 176  |

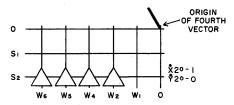

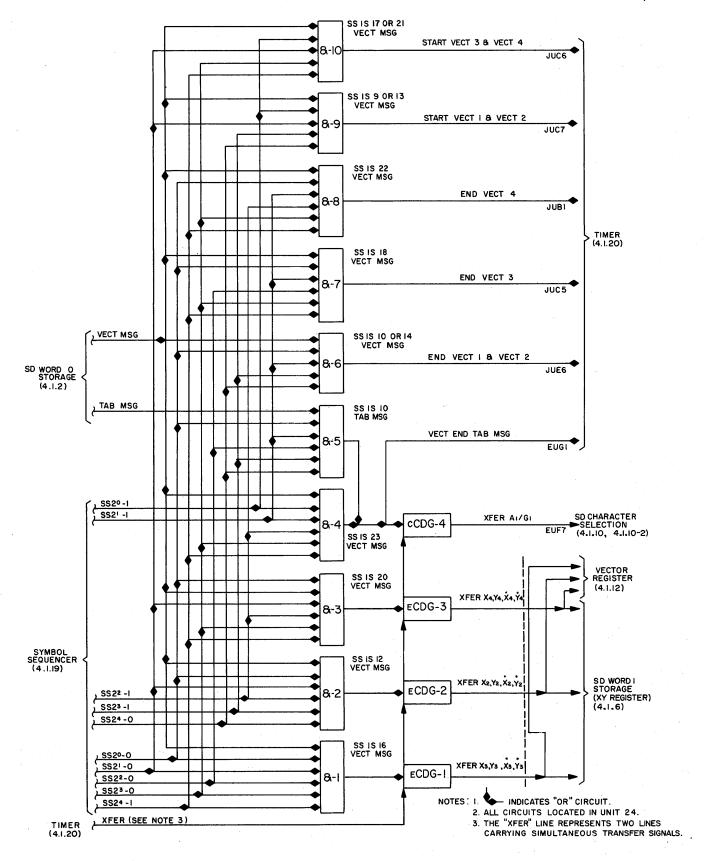

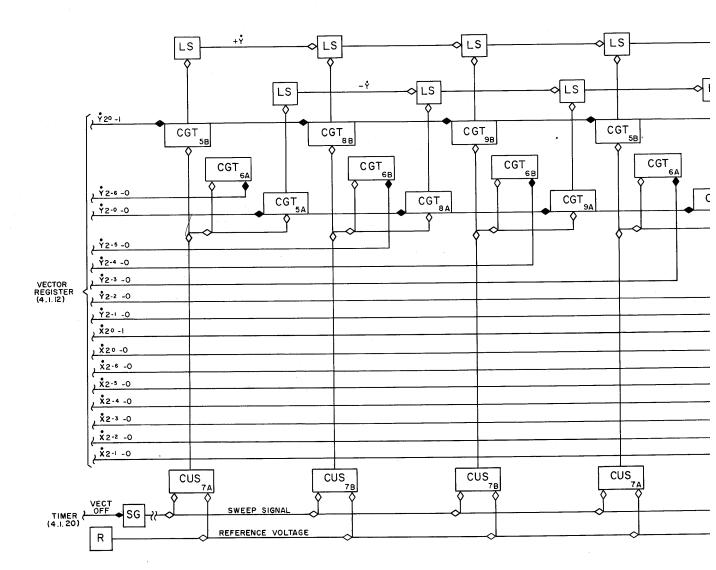

| 2.8     | Vector Generation                                                                | 176  |

| 2.8.1   | Vector Register (TD Tabular Track Message)                                       | 176  |

| 2.8.2   | Vector Register (TD Vector Message)                                              | 178  |

| 2.8.3   | Vector Generator                                                                 | 178  |

| 2.9     | Message Positioning (XY Register SD Word 1 and Storage<br>XY Line Drivers Logic) |      |

| 2.9.1   | TD Tabular Message                                                               | 181  |

| 2.9.2   | TD Vector Message                                                                | 182  |

| 2.9.3   | RD Message                                                                       | 182  |

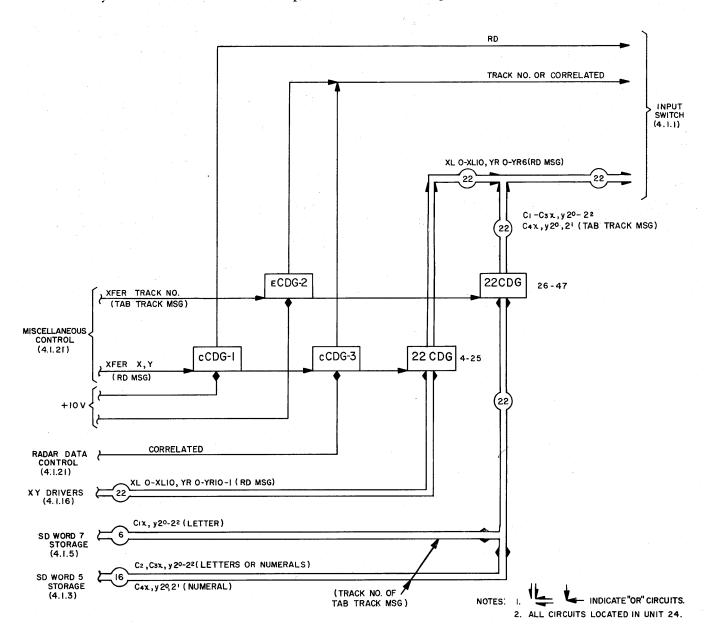

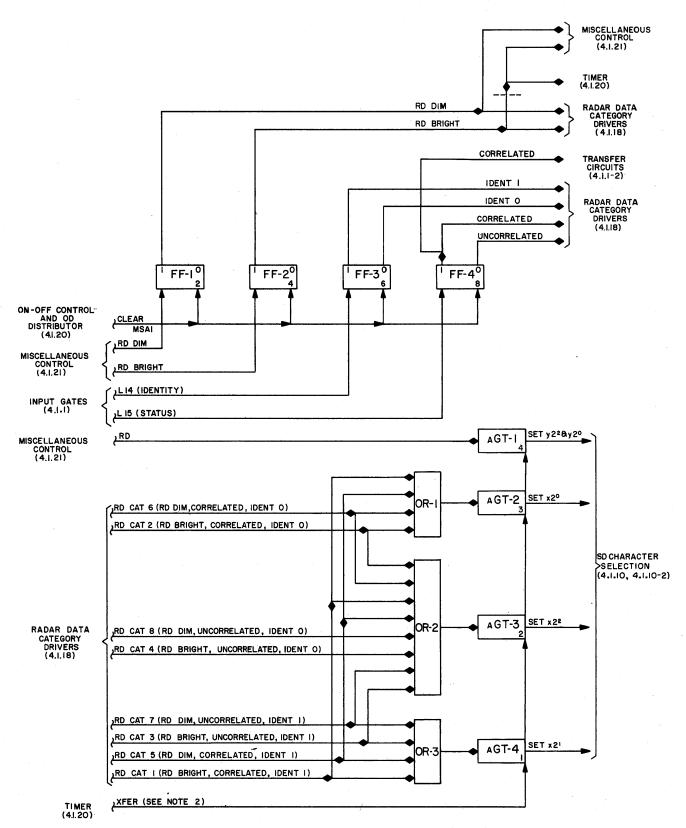

| 2.10    | Category and DAB Storage and Output                                              | 182  |

| 2.10.1  | Category Storage, Matrix and Drivers (TD Messages Only)                          | 183  |

| 2.10.2  | TD Category Generation                                                           | 183  |

| 2.10.3  | TD Category Output Signals                                                       | 185  |

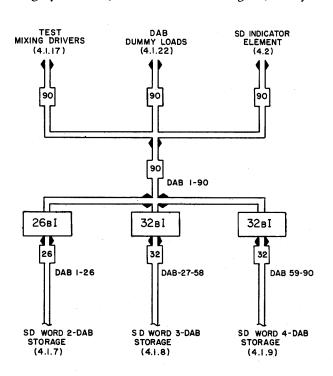

| 2.10.4  | DAB Word 2 Storage Circuit (TD Messages Only)                                    | 185  |

| 2.10.5  | DAB Word 3 Storage Circuit (TD Messages Only)                                    | 185  |

| 2.10.6  | DAB Word 4 Storage Circuit (TD Messages Only)                                    | 186  |

| 2.10.7  | DAB Drivers                                                                      | 186  |

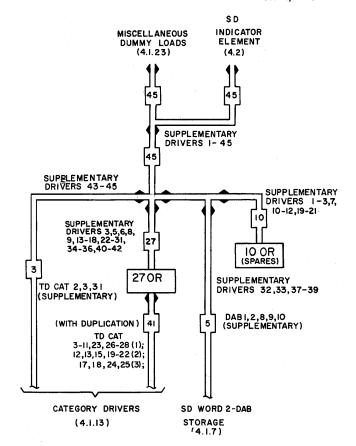

| 2.10.8  | Supplementary Drivers                                                            | 186  |

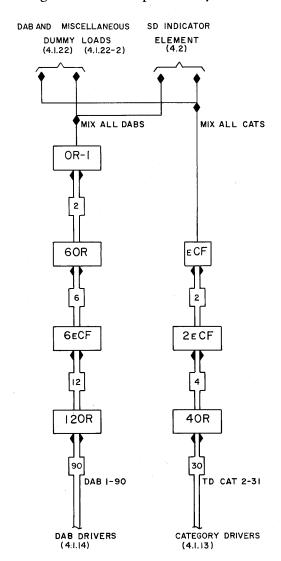

| 2.10.9  | Mix All CAT's and Mix All DAB's                                                  | 188  |

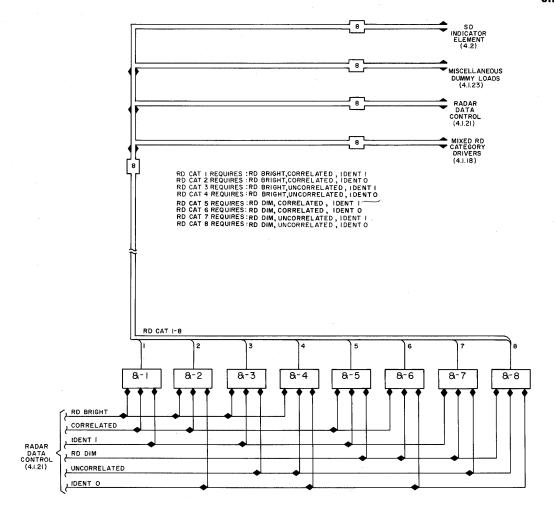

| 2.10.10 | Radar Data Category Drivers (RD Messages Only)                                   | 188  |

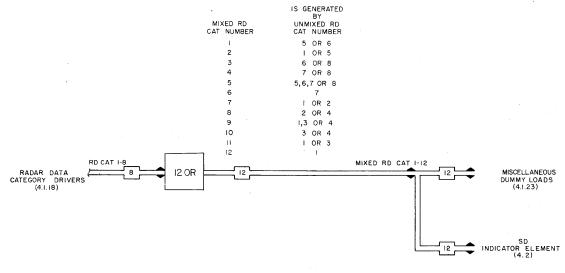

| 2.10.11 | Mixed RD Category Drivers (RD Messages Only)                                     | 188  |

| 2.11    | Transfer Circuits Section                                                        | 189  |

| Head | ding     |                                                     | Page |

|------|----------|-----------------------------------------------------|------|

|      | 2.11.1   | Transfer of Track Number (TD Tabular Track Message) | 189  |

|      | 2.11.2   | Transfer of X,Y Information (RD Message)            | 189  |

|      | 2.11.3   | Generation of Message-Identifying Signals           | 189  |

|      | 2.11.3.1 | TD Tabular Track Message                            | 191  |

|      | 2.11.3.2 | RD Message                                          | 191  |

|      | 2.12     | Dummy Load Section                                  | 192  |

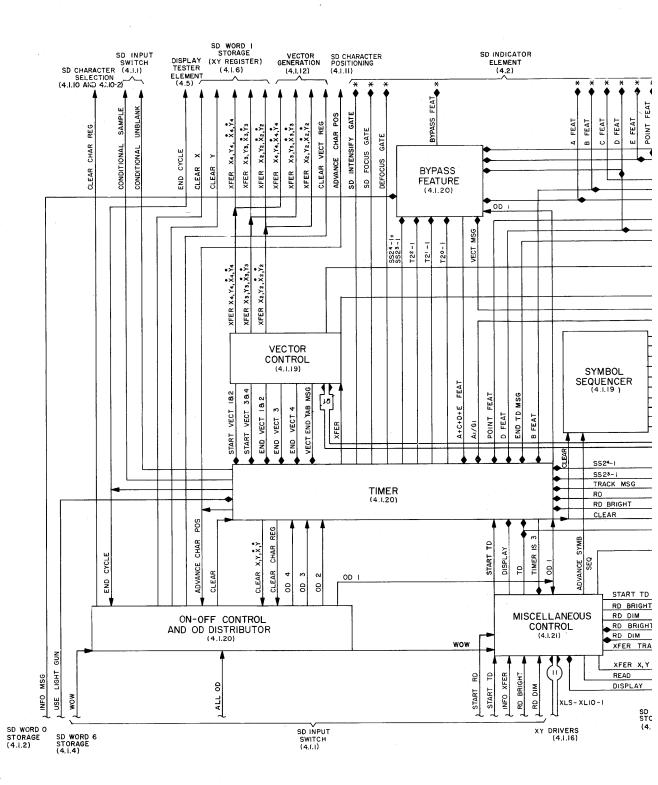

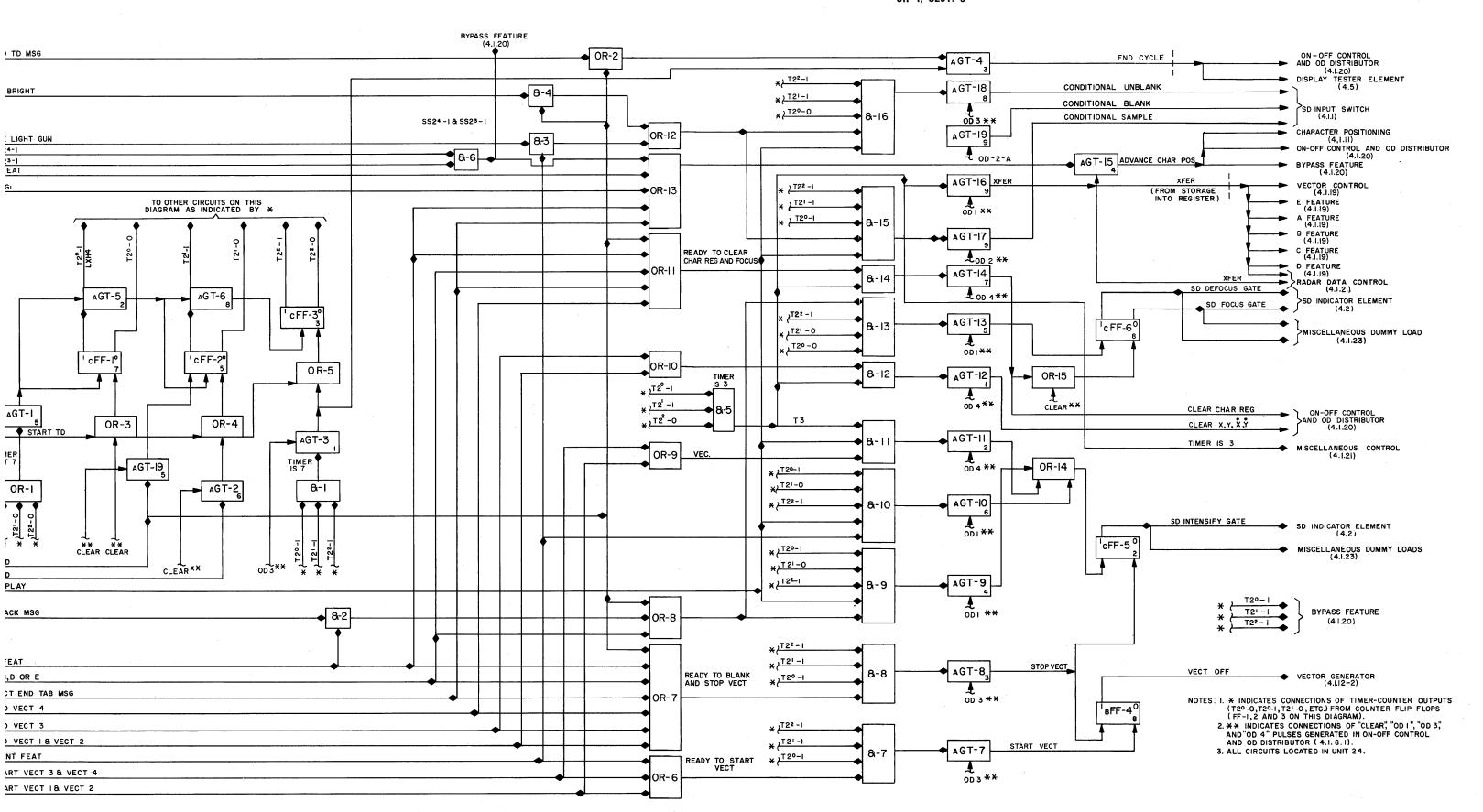

|      | SECTION  | N 3 SD TIMING AND CONTROL                           | 193  |

|      | 3.1      | Introduction                                        | 193  |

|      | 3.2      | Timing, Control, Circuits, and Signals              | 193  |

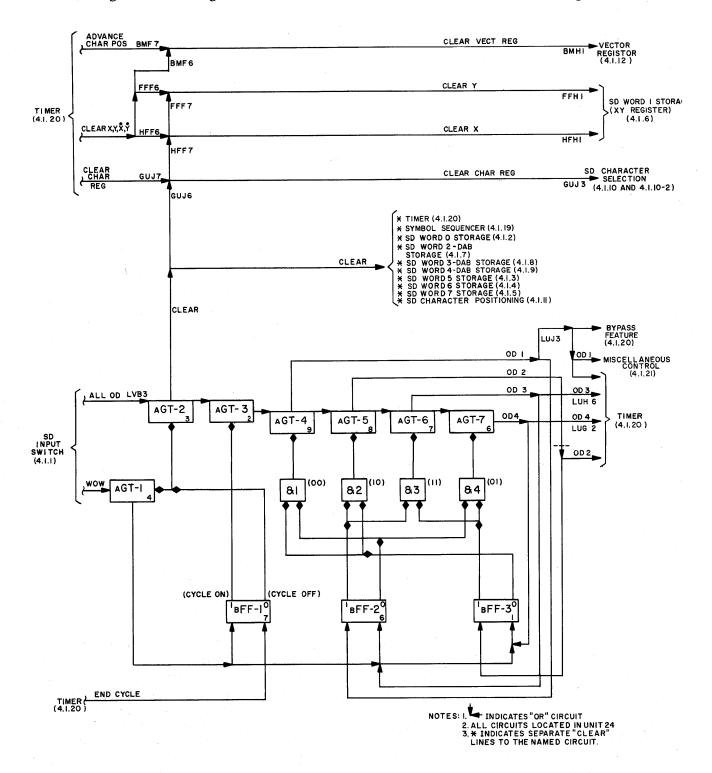

|      | 3.2.1    | On-Off Control and OD Distributor                   | 195  |

|      | 3.2.1.1  | On-Off Control                                      | 195  |

|      | 3.2.1.2  | OD Distributor                                      | 195  |

|      | 3.2.1.3  | Clear Signals                                       | 196  |

|      | 3.2.2    | Miscellaneous Control Circuit                       | 196  |

|      | 3.2.2.1  | TD Tabular Message                                  | 197  |

|      | 3.2.2.2  | TD Vector Message                                   | 197  |

|      | 3.2.2.3  | RD Message                                          | 197  |

|      | 3.2.3    | Symbol Sequencer (TD Messages)                      | 199  |

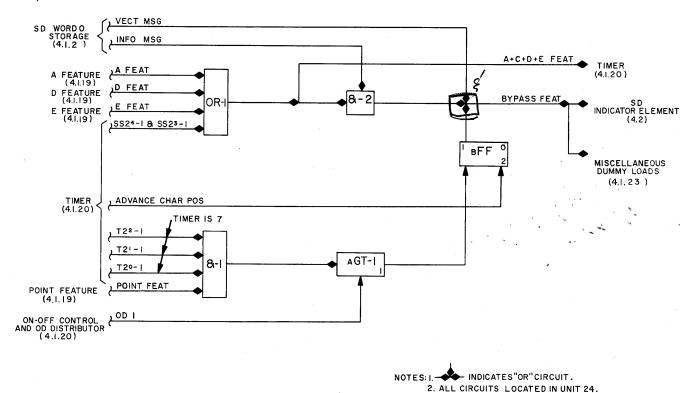

|      | 3.2.4    | Gate Generator                                      | 199  |

|      | 3.2.4.1  | TD Messages                                         | 199  |

|      | 3.2.4.2  | TD Tabular Message                                  | 201  |

|      | 3.2.4.3  | TD Vector Message                                   | 201  |

|      | 3.2.4.4  | RD Message                                          | 201  |

|      | 3.2.5    | A Feature Circuit                                   | 201  |

|      | 3.2.5.1  | TD Tabular Message                                  | 201  |

|      | 3.2.5.2  | TD Tabular Track Message                            | 201  |

|      | 3.2.5.3  | TD Tabular Information Message                      | 201  |

|      | 3.2.5.4  | TD Vector Message                                   | 203  |

|      | 3.2.6    | B Feature Circuit                                   | 203  |

|      | 3.2.6.1  | TD Tabular Message                                  | 203  |

|      | 3.2.6.2  | TD Tabular Track Message                            | 203  |

|      | 3.2.6.3  | TD Tabular Information Message                      | 203  |

|      | 3.2.6.4  | TD Vector Message                                   | 203  |

|      | 3.2.7    | C Feature Circuit                                   | 205  |

| Heading  |                                                                   | Page |

|----------|-------------------------------------------------------------------|------|

| 3.2.7.1  | TD Tabular Message                                                | 205  |

| 3.2.7.2  | TD Tabular Track Message                                          | 206  |

| 3.2.7.3  | TD Tabular Information Message                                    | 206  |

| 3.2.7.4  | TD Vector Message                                                 | 206  |

| 3.2.8    | D Feature Circuit (TD Tabular Message)                            | 207  |

| 3.2.8.1  | TD Tabular Track Message                                          | 207  |

| 3.2.8.2  | TD Tabular Information Message                                    | 207  |

| 3.2.9    | E Feature Circuit                                                 | 207  |

| 3.2.9.1  | TD Tabular Message                                                | 207  |

| 3.2.9.2  | TD Tabular Track Message                                          | 208  |

| 3.2.9.3  | TD Tabular Information Message                                    | 208  |

| 3.2.9.4  | TD Vector Message                                                 | 208  |

| 3.2.10   | Point Feature Circuit (TD Tabular Message)                        | 208  |

| 3.2.11   | Bypass Feature Circuit                                            | 208  |

| 3.2.11.1 | TD Tabular Message                                                | 209  |

| 3.2.11.2 | TD Tabular Track Message                                          | 209  |

| 3.2.11.3 | TD Tabular Information Message                                    | 209  |

| 3.2.11.4 | TD Vector Message                                                 | 209  |

| 3.2.12   | Vector Control Circuit                                            | 209  |

| 3.2.12.1 | TD Tabular Message                                                | 211  |

| 3.2.12.2 | TD Vector Message                                                 | 211  |

| 3.2.13   | RD Control Circuit                                                | 211  |

| 3.2.13.1 | Radar Data Message Control Signals                                | 213  |

| 3.2.13.2 | RD Message Character Selection Signals                            |      |

| 3.2.13.3 | Other Outputs                                                     | 214  |

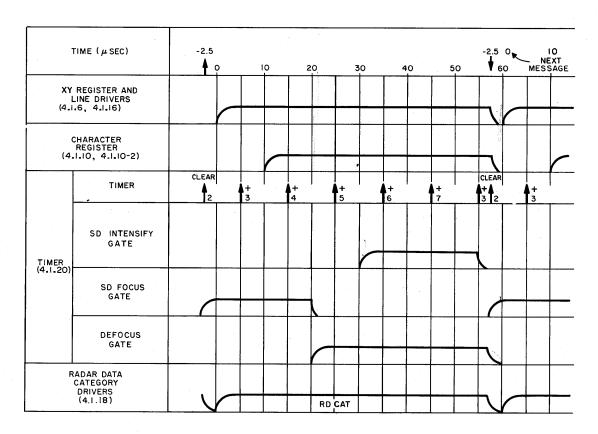

| 3.2.14   | Timer Circuit                                                     | 214  |

| 3.2.14.1 | TD Tabular Message                                                | 214  |

| 3.2.14.2 | Timer Counter, TD Tabular Message                                 |      |

| 3.2.14.3 | Vector-Off Signal (TD Tabular Message)                            | 216  |

| 3.2.14.4 | SD Intensify Gate (TD Tabular Message)                            |      |

| 3.2.14.5 | Clear-XY-Register-and-Vector-Register Signal (TD Tabular Message) | 217  |

| 3.2.14.6 | Advance-Character-Position Signal (TD Tabular Message)            | 217  |

| 3.2.14.7 | Transfer (from-Storage-into-Register) Signal (TD Tabular Message) |      |

| Head | ding      |                                                                                             | Page |

|------|-----------|---------------------------------------------------------------------------------------------|------|

|      | 3.2.14.8  | SD Focus and Defocus Gates (TD Tabular Message)                                             | 218  |

|      | 3.2.14.9  | Clear-Character-Register Signal (TD Tabular Message)                                        | 218  |

|      | 3.2.14.10 | Timer-is-3 Signal (TD Tabular Message)                                                      | 219  |

|      | 3.2.14.11 | Conditional-Unblank, Conditional-Blank, and Conditional-Sample Signals (TD Tabular Message) |      |

|      | 3.2.14.12 | End-Cycle Signal (TD Tabular Message)                                                       | 219  |

|      | 3.2.14.13 | TD Vector Message                                                                           | 219  |

|      | 3.2.14.14 | Timer Counter (TD Vector Message)                                                           | 219  |

|      | 3.2.14.15 | Vector-Off Signal (TD Vector Message)                                                       | 219  |

|      | 3.2.14.16 | SD Intensify Gate (TD Vector Message)                                                       | 219  |

|      | 3.2.14.17 | Clear XY-Register-and-Vector-Register Signal (TD Vector Message)                            |      |

|      | 3.2.14.18 | Advance-Character-Position Signal (TD Vector Message)                                       | 220  |

|      | 3.2.14.19 | Transfer (from-Storage-into-Register) Signal (TD Vector Message)                            |      |

|      | 3.2.14.20 | SD Focus and Defocus Gates (TD Vector Message)                                              | 221  |

|      | 3.2.14.21 | Clear-Character-Register Signal (TD Vector Message)                                         | 221  |

|      | 3.2.14.22 | Conditional-Unblank, Conditional-Blank, and Conditional-Sample Signals (TD Vector Message)  |      |

|      | 3.2.14.23 | Timer-is-3 and End-Cycle Signals (TD Vector Message)                                        | 221  |

|      | 3.2.14.24 | RD Message                                                                                  | 221  |

|      | 3.2.14.25 | Timer Counter (RD Message)                                                                  | 221  |

|      | 3.2.14.26 | SD Intensity Gate (RD Message)                                                              | 221  |

|      | 3.2.14.27 | Transfer (from-Storage-into-Register) Signal (RD Message)                                   | 221  |

|      | 3.2.14.28 | SD Focus and Defocus Gates and Clear-Character-Register Signals                             |      |

|      | 3.2.14.29 | Conditional-Unblank, Conditional-Blank, and Conditional-Sample Signals (RD Message)         |      |

|      | 3.2.14.30 | Timer-is-3 End-Cycle Signals (RD Message)                                                   | 222  |

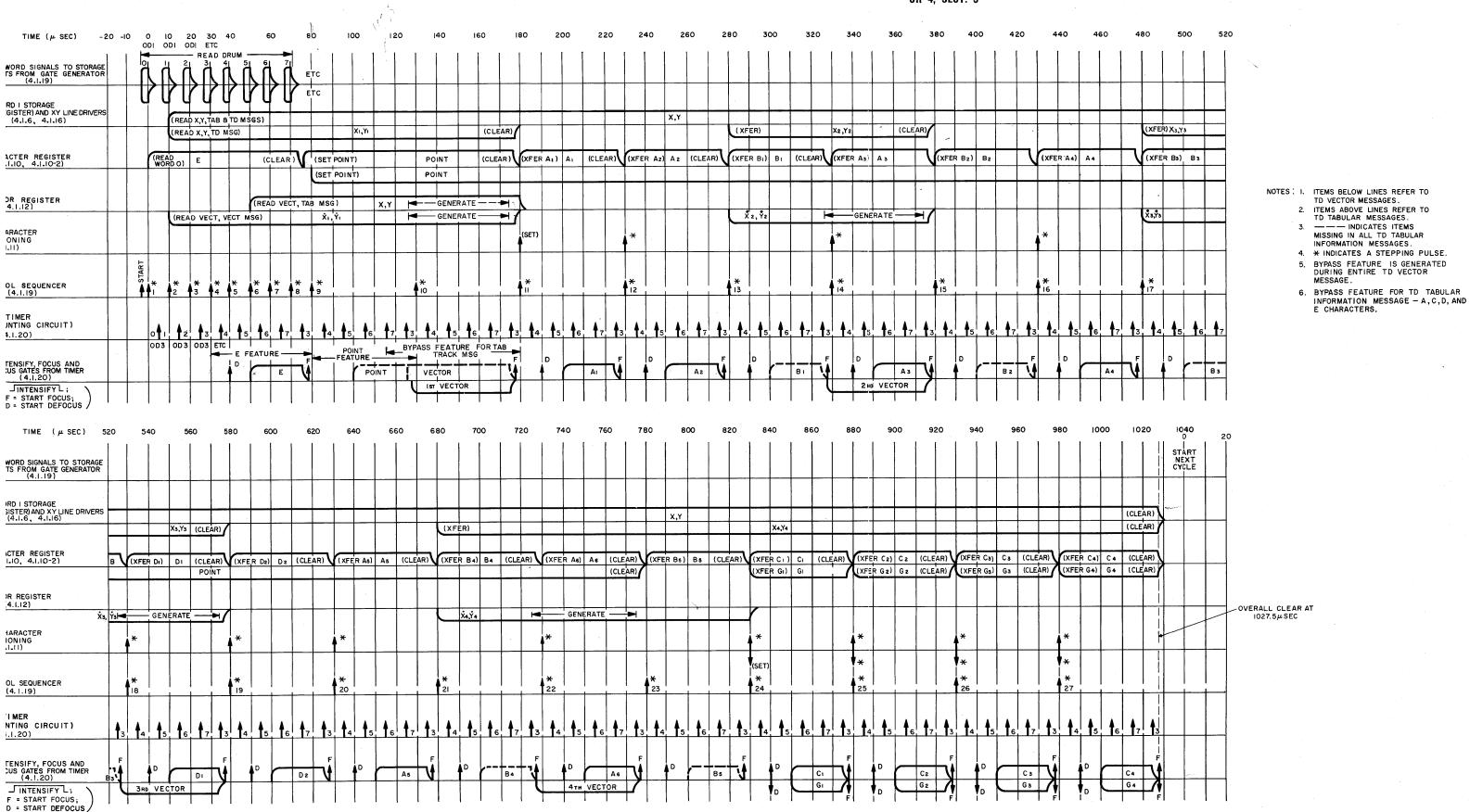

|      | 3.3       | Overall Timing of SD Cycle                                                                  | 223  |

|      | 3.3.1     | RD Messages                                                                                 | 223  |

|      | 3.3.2     | TD Messages                                                                                 | 223  |

|      | 3.3.2.1   | TD Vector Message                                                                           | 223  |

|      | 3.3.2.2   | TD Tabular Message                                                                          | 223  |

|      | 3.4       | Detailed Timing of SD Cycle                                                                 | 223  |

|      | 3.5       | TD Messages                                                                                 | 223  |

|      | 3.5.1     | TD Tabular Message                                                                          | 223  |

| Heading |                                              | Page |

|---------|----------------------------------------------|------|

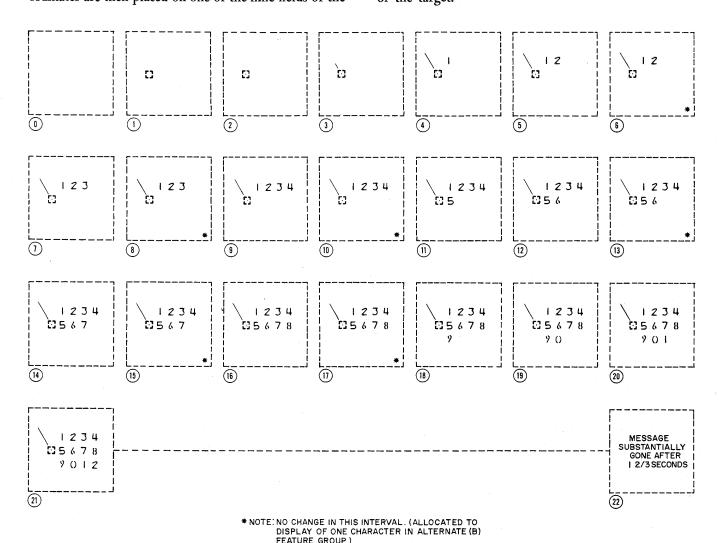

| 3.5.1.1 | Display of a TD Tabular Track Message        | 224  |

| 3.5.1.2 | Display of a TD Tabular Information Message  | 224  |

| 3.5.2   | TD Vector Message                            | 224  |

| 3.5.3   | RD Message                                   | 225  |

|         |                                              |      |

|         | VOLUME II                                    |      |

| PART 5  | ASSOCIATED EQUIPMENT                         | 1    |

| CHAPTE  | R 1 SCOPE                                    | 1    |

| 1.1     | General                                      | 1    |

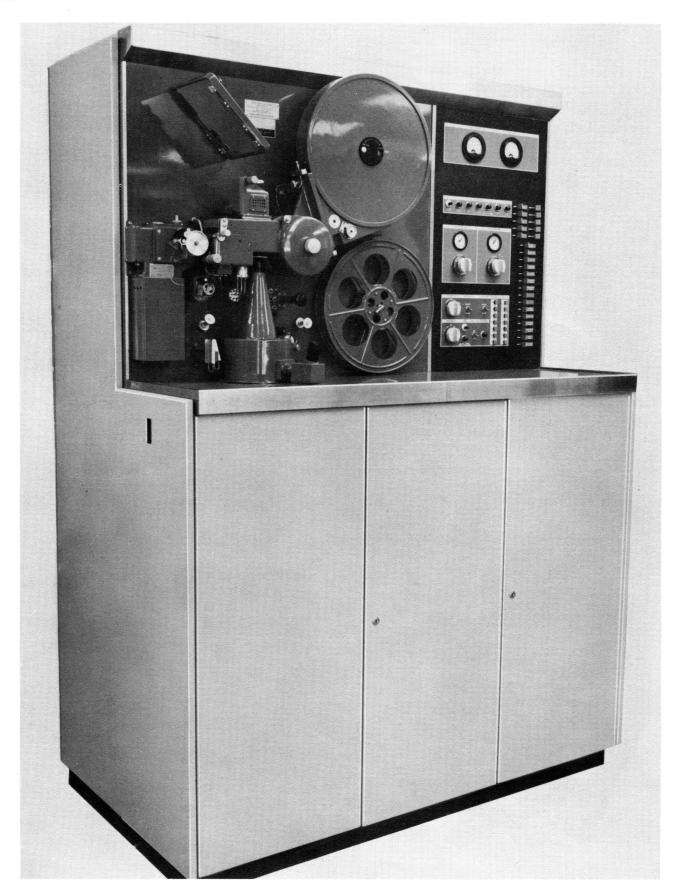

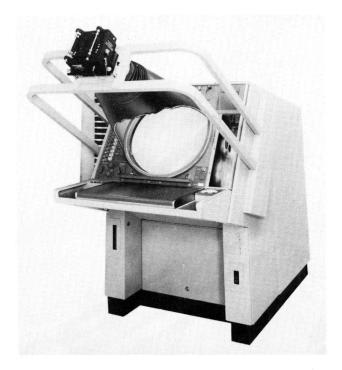

| 1.2     | Photographic Recorder-Reproducer Element     | 1    |

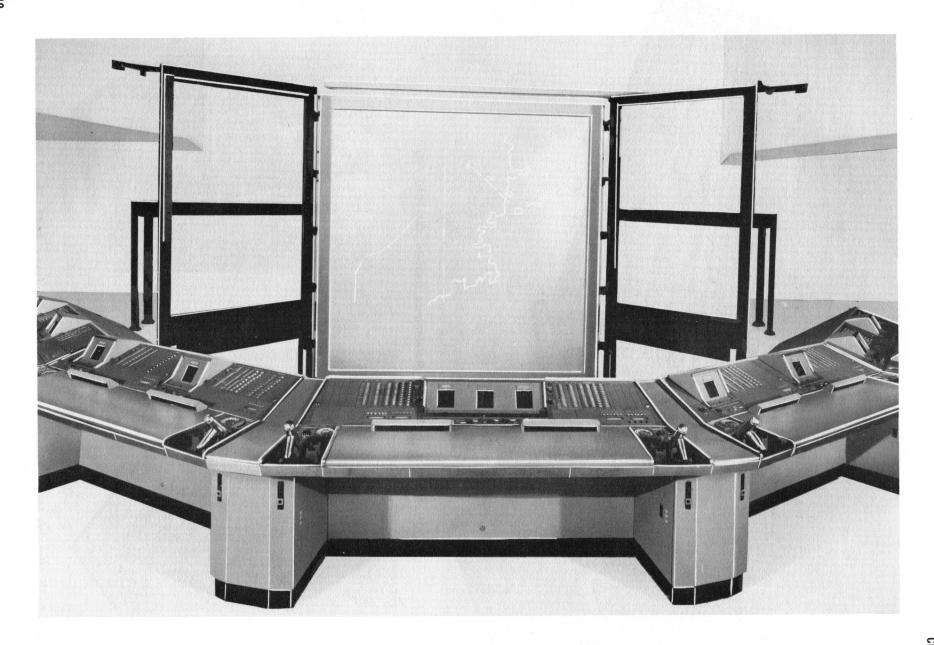

| 1.3     | Situation Display Consoles                   | 1    |

| 1.4     | Situation Display Camera Element             | 1    |

| 1.5     | Command Post Console                         | 1    |

| 1.6     | Distribution Elements                        | 1    |

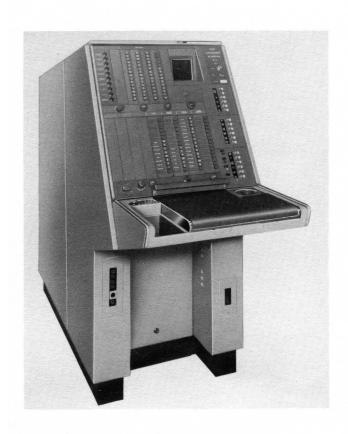

| 1.7     | Supporting Components                        | 1    |

| 1.8     | Display Tester Element                       |      |

| a       | R 2 PHOTOGRAPHIC RECORDER-REPRODUCER ELEMENT |      |

| SECTIO  | ON 1 INTRODUCTION                            |      |

| 1.1     | Scope                                        |      |

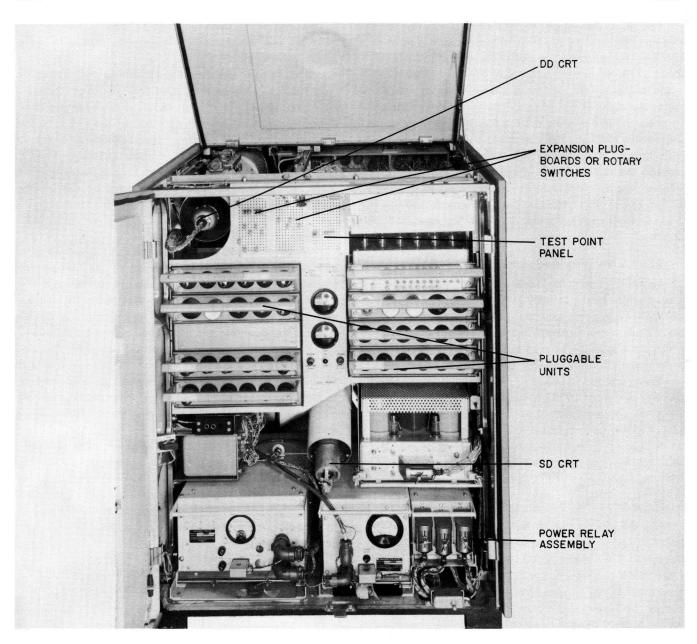

| 1.2     | Physical Description                         |      |

| 1.3     | Location of Units                            | -    |

| 1.4     | SDS Differences                              |      |

| 1.4.1   | Request Display Gate Generator               |      |

| 1.4.2   | Display Assignment Bits                      |      |

| 1.4.3   | B Feature                                    |      |

| 1.4.4   | Radar Data Messages                          |      |

| 1.4.5   | Remote Control                               |      |

| 1.4.6   | Expansion Input Panel                        |      |

| 1.5     | Logical Relationship                         | 4    |

| 1.6     | Sovion Inch SIII I K I                       | 7.   |

| Hea | ding    |                                              | Page |

|-----|---------|----------------------------------------------|------|

|     | SECTIO  | N 2 THEORY OF OPERATION                      | 8    |

|     | 2.1     | Introduction                                 | 8    |

|     | 2.2     | General                                      | 8    |

|     | 2.3     | Expansion and Off-Centering Selection        | 8    |

|     | 2.3.1   | Expansion                                    | 8    |

|     | 2.3.2   | Off-Centering                                | 10   |

|     | 2.4     | Expansion and Off-Centering Relays           | 12   |

|     | 2.5     | Ten-Bit Binary Decoder                       | 12   |

|     | 2.6     | Decoder Simulator                            | 12   |

|     | 2.7     | Deflection Amplifiers and Deflection Drivers | 14   |

|     | 2.8     | High-Voltage Unit                            | 14   |

|     | 2.8.1   | Character Selection                          | 14   |

|     | 2.8.2   | Character-Positioning and Compensation       | 14   |

|     | 2.8.3   | High-Voltage Power Supplies                  | 14   |

|     | 2.9     | Feature Selection                            | 14   |

|     | 2.10    | Display Selection                            | 14   |

|     | 2.10.1  | Categories                                   | 15   |

|     | 2.10.2  | Display Assignment Bits                      | 15   |

|     | 2.10.3  | Supplemental Drivers                         | 15   |

|     | 2.10.4  | Selection Inputs                             | 15   |

|     | 2.11    | Intensification                              | 15   |

| ,   | 2.11.1  | Request Display Gate Generator               | 15   |

|     | 2.11.2  | Intensification Unit 1                       | 15   |

|     | 2.11.3  | Intensification Unit 2                       | 17   |

|     | 2.12    | Seven-Inch SD CRT Circuits                   | 19   |

|     | SECTIO  | N 3 DETAILED EXPLANATION OF CONSOLE CIRCUITS | 20   |

|     | 3.1     | Introduction                                 | 20   |

|     | 3.2     | UNIT STATUS Switch                           | 20   |

|     | 3.3     | Intensification Circuits                     | 20   |

|     | 3.4     | Message-Positioning Circuits                 | 24   |

|     | 3.4.1   | Rotary Switches                              | 26   |

|     | 3.4.1.1 | Expansion Levels                             | 26   |

|     | 2 1 1 2 | Expension on CNTD Position                   | 26   |

| Hea | ıding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    | Page |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|

|     | 3.4.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Expansion on NORM Position                         | 26   |

|     | 3.4.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Expansion of EXP Position                          | . 26 |

|     | 3.4.1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Off-Centering                                      | . 26 |

|     | 3.4.1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Off-Centering Relays                               | . 26 |

|     | 3.4.1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Actuation of Off-Centering Relays on CNTD Position | . 27 |

|     | 3.4.1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Actuation of Off-Centering Relays on NORM Position | . 27 |

|     | 3.4.1.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Actuation of Off-Centering Relays on EXP Position  | . 27 |

|     | 3.4.1.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SD Test Pattern Switch                             | . 27 |

|     | 3.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Magnitude Bit Selection                            | 27   |

|     | 3.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Digit 0 Selection, X2, X4, and X8 Expansion        | . 28 |

|     | 3.4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Intensification Selection                          | . 28 |

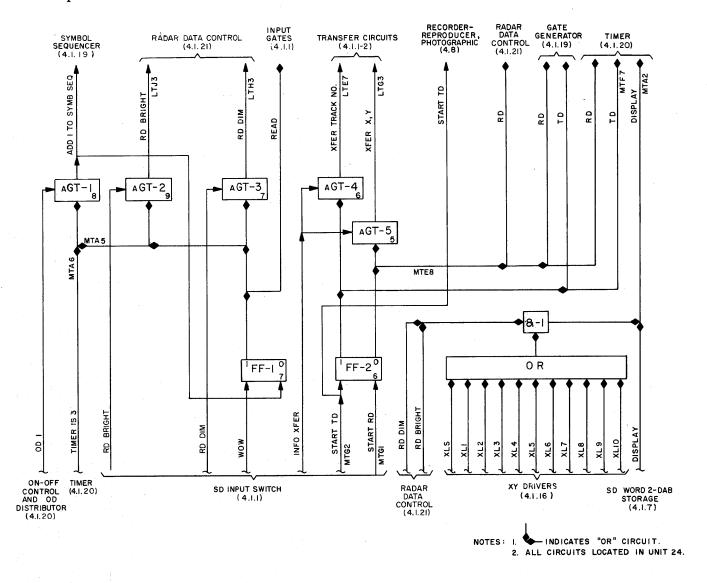

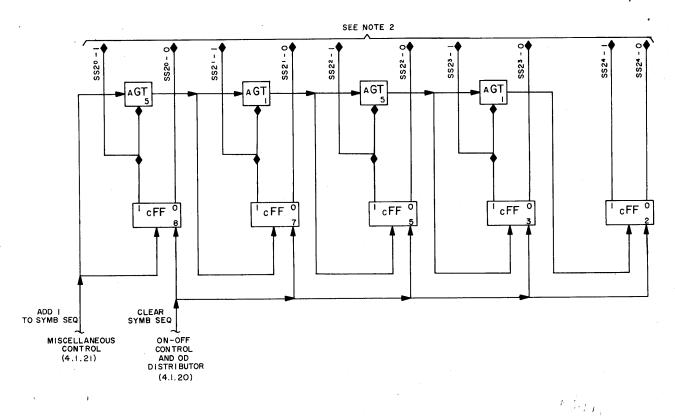

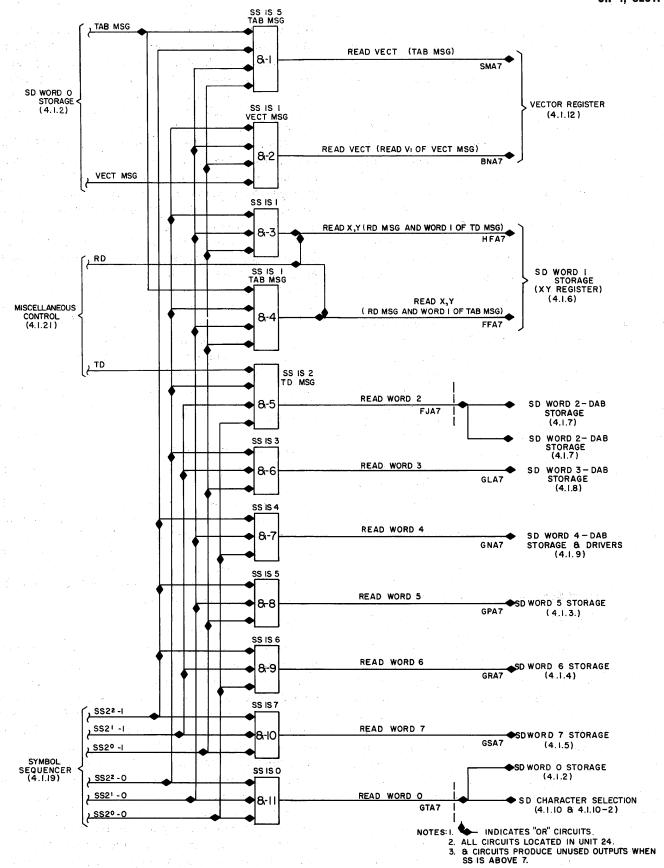

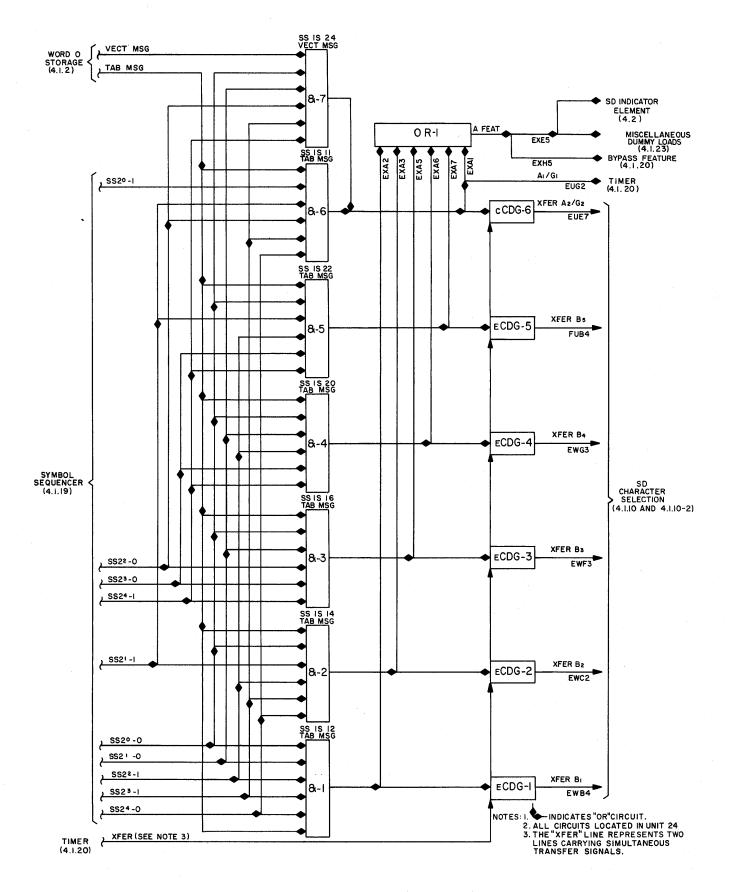

|     | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Remote Control Circuits                            | 28   |