# 92/93 Data Book

### 92/93 Data Book

Printed in U.Ş.A. ©1992 by Catalyst Semiconductor, Inc. "All Rights Reserved"

### **Corporate Message**

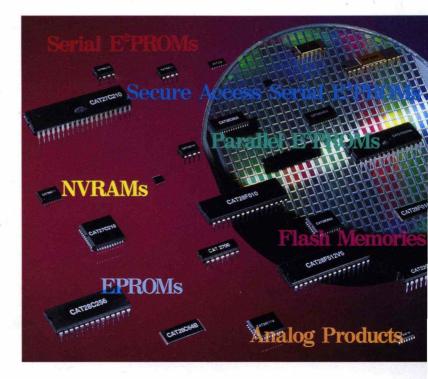

Catalyst Semiconductor, Inc. is a technology leader in CMOS nonvolatile memories and is dedicated to the development of next generation memory products and their applications.

The Catalyst Corporate Mission Statement is:

- Use state of the art nonvolatile memory technology to produce innovative leading edge products and obtain a leadership position in all reprogrammable product markets.

- Adopt a global manufacturing strategy by using strategic partners to produce cost-effective, high quality products.

- Provide excellent service to customers worldwide and enter into mutually beneficial, long-term partnership agreements.

Catalyst Semiconductor is in the business of providing integrated circuits which enhance your electronic systems' performance, thereby giving you a competitive edge in your marketplace. In our view, you, our customer, have not simply purchased ICs; you've secured our commitment to your company and your business. Since our inception in 1985, we have found that relationships based on this commitment result in the development of trust, support and mutual prosperity. Such is the foundation of long-term corporate partnerships, and these are what the future of Catalyst is being designed to secure.

Thank you for considering Catalyst memory products.

David W. Sear President & C.O.O.

B.K. Marya Chairman of the Board & C.E.O.

Catalyst Semiconductor is licensed by Philips Corporation to carry the I<sup>2</sup>C Bus Protocol. Intelligent Programming, Quick-Erase Programming and Quick-Pulse Programming are trademarks of Intel Corporation.

Power Miser<sup>™</sup>, ZERO Power<sup>™</sup> and DACpot<sup>™</sup> are trademarks of Catalyst Semiconductor, Inc.

#### LIMITED WARRANTY

Devices sold by Catalyst Semiconductor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Catalyst Semiconductor makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Catalyst Semiconductor makes no warranty of merchantability or fitness for any purpose. Catalyst Semiconductor reserves the right to discontinue production and change specifications and prices at any time and without notice.

Catalyst Semiconductor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Catalyst Semiconductor product. No other circuits, patents, licenses are implied.

#### LIFE RELATED POLICY

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurence.

Catalyst Semiconductor's products are not authorized for use as critical components in life support devices or systems.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labelling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## **Table of Contents**

| SECTION 1 | PRODUCT INFORMATION Alpha-Numeric Index |                   |         |      |

|-----------|-----------------------------------------|-------------------|---------|------|

|           | •                                       |                   |         |      |

|           | Product Selection Guide                 |                   |         |      |

|           | Ordering Information (Part Number Desc  | ription)          |         | 1-11 |

| SECTION 2 | 2-WIRE BUS SERIAL E <sup>2</sup> PROMS  |                   |         |      |

|           | CAT24C02/CAT24C02I                      |                   | 2K-Bit  | 2-1  |

|           | CAT24LC02/CAT24LC02I                    |                   | 2K-Bit  | 2-9  |

|           | CAT24C02A/CAT24C02AI                    |                   | 2K-Bit  | 2-17 |

|           | CAT24LC02A/CAT24LC02AI                  | 256 x 8           | 2K-Bit  | 2-25 |

|           | CAT24C04/CAT24C04I                      | 512 x 8           | 4K-Bit  | 2-33 |

|           | CAT24LC04/CAT24LC04I                    | 512 x 8           | 4K-Bit  | 2-41 |

|           | CAT24C08/CAT24C08I                      | 1024 x 8          | 8K-Bit  | 2-49 |

|           | CAT24LC08/CAT24LC08l                    |                   | 8K-Bit  | 2-57 |

|           | CAT24C16/CAT24C16I                      |                   | 16K-Bit | 2-65 |

|           | CAT24LC16/CAT24LC16l                    |                   | 16K-Bit | 2-73 |

|           | CAT24C32/CAT24C32                       | 4096 x 8          | 32K-Bit | 2-81 |

| SECTION 3 | 3-WIRE BUS SERIAL E <sup>2</sup> PROMS  |                   |         |      |

|           | CAT93C46/CAT93C46I                      | 64 x 16, 128 x 8  | 1K-Bit  | 3-1  |

|           | CAT93C46A/CAT93C46AI                    | 64 x 16           | 1K-Bit  | 3-9  |

|           | CAT93C46B/CAT93C46BI                    | 64 x 16, 128 x 8  | 1K-Bit  | 3-17 |

|           | CAT33C101/CAT33C1011                    | 64 x 16, 128 x 8  | 1K-Bit  | 3-25 |

|           | CAT32C101                               | 64 x 16, 128 x 8  | 1K-Bit  | 3-33 |

|           | CAT93C56/CAT93C56I                      |                   | 2K-Bit  | 3-41 |

|           | CAT93LC56/CAT93LC56I                    |                   | 2K-Bit  | 3-49 |

|           | CAT35C102/CAT35C102I                    |                   | 2K-Bit  | 3-57 |

|           | CAT33C104/CAT33C104I                    | 256 x 16, 512 x 8 | 4K-Bit  | 3-65 |

|           | CAT35C104/CAT35C104I                    |                   | 4K-Bit  | 3-73 |

|           | CAT33C108/CAT33C108I                    |                   | 8K-Bit  | 3-81 |

| SECTION 3 | 3 3-WIRE BUS SERIAL E <sup>2</sup> PROMS (CONT'D) |                     |              |

|-----------|---------------------------------------------------|---------------------|--------------|

|           | CAT35C108/CAT35C108I                              | 512 x 16, 1024 x 8  | 8K-Bit3-89   |

|           | CAT33C116/CAT33C116!                              | 1024 x 16, 2048 x 8 | 16K-Bit3-97  |

|           | CAT35C116/CAT35C116I                              | 1024 x 16, 2048 x 8 | 16K-Bit3-105 |

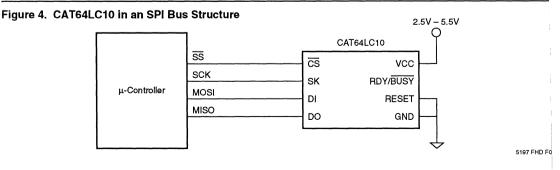

#### SECTION 4 SPI BUS SERIAL E<sup>2</sup>PROMS

| CAT64LC10/CAT64LC10I | 64 x 16  | 1K-Bit | 4-1  |

|----------------------|----------|--------|------|

| CAT64LC20/CAT64LC20I | 128 x 16 | 2K-Bit | 4-11 |

| CAT64LC40/CAT64LC40I | 256 x 16 | 4K-Bit | 4-21 |

#### SECTION 5 4-WIRE BUS SERIAL E<sup>2</sup>PROMS

| CAT59C11/CAT59C11I   | 64 x 16, 128 x 8  | 1K-Bit | 5-1 |

|----------------------|-------------------|--------|-----|

| CAT35C202/CAT35C202I | 128 x 16, 256 x 8 | 2K-Bit | 5-7 |

#### SECTION 6 SECURE ACCESS SERIAL E<sup>2</sup>PROMS

| CAT33C704/CAT33C704I       | 256 x 16, 512 x 8 | 4K-Bit | 6-1           |

|----------------------------|-------------------|--------|---------------|

| CAT35C704/CAT35C704I       | 256 x 16, 512 x 8 | 4K-Bit | 6-15          |

| CAT33C804A-B/CAT33C804A-BI | 256 x 16, 512 x 8 | 4K-Bit | 6 <b>-</b> 29 |

| CAT35C804A-B/CAT35C804A-BI | 256 x 16, 512 x 8 | 4K-Bit | 6-43          |

#### SECTION 7 PARALLEL E<sup>2</sup>PROMS

| CAT28C16A/CAT28C16AI | 2K x 8  | 16K-Bit  | 7-1  |

|----------------------|---------|----------|------|

| CAT28C16V3           | 2K x 8  | 16K-Bit  | 7-9  |

| CAT28C17A/CAT28C17AI | 2K x 8  | 16K-Bit  | 7-17 |

| CAT28C64A/CAT28C64AI | 8K x 8  | 64K-Bit  | 7-25 |

| CAT28C65A/CAT28C65AI | 8K x 8  | 64K-Bit  | 7-33 |

| CAT28C64B/CAT28C64BI | 8K x 8  | 64K-Bit  | 7-41 |

| CAT28C65B/CAT28C65BI | 8K x 8  | 64K-Bit  | 7-51 |

| CAT28C256/CAT28C256I | 32K x 8 | 256K-Bit | 7-61 |

#### SECTION 8 FLASH MEMORIES

| CAT28F512/CAT28F512I     | 64K x 8  | 512K-Bit | 8-1  |

|--------------------------|----------|----------|------|

| CAT28F512V5/CAT28F512V5I | 64K x 8  | 512K-Bit | 8-19 |

| CAT28F010/CAT28F010I     | 128K x 8 | 1M-Bit   | 8-37 |

| CAT28F010V5/CAT28F010V5I | 128K x 8 | 1M-Bit   | 8-55 |

| SECTION 8 | FLASH MEMORIES (CONT'D)<br>CAT28F020/CAT28F020I | 256K x 8 | 2M-Bit   | 8-73 |

|-----------|-------------------------------------------------|----------|----------|------|

| SECTION 9 | EPROMS<br>CAT27HC256L/CAT27HC256LI              | 32K x 8  | 256K-Bit | 9-1  |

| SECTION 10 | NVRAMS |

|------------|--------|

| CAT22C10/CAT22C10I | 64 x 4  | 256-Bit | 10-1    |

|--------------------|---------|---------|---------|

| CAT22C12/CAT22C12I | 256 x 4 | 1K-Bit  | 10-9    |

| CAT24C44/CAT24C44I | 16 x 16 | 256-Bit | . 10-17 |

#### SECTION 11 ANALOG PRODUCTS

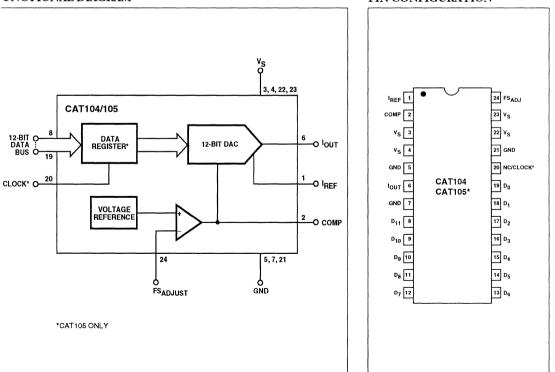

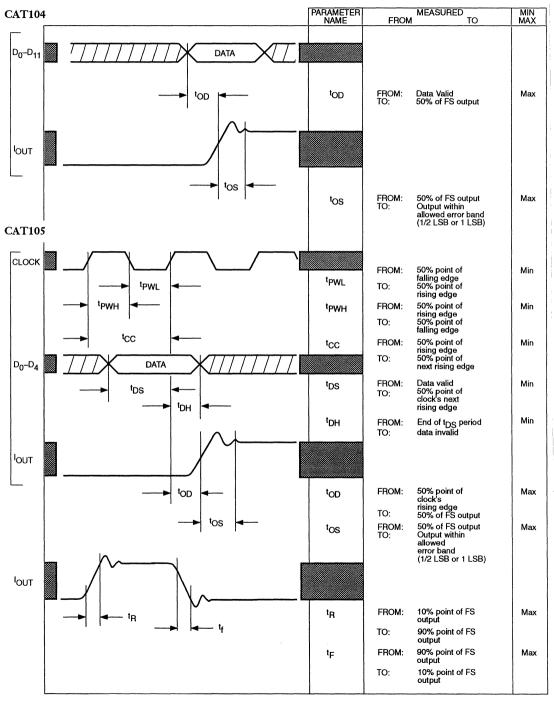

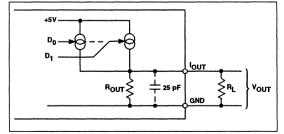

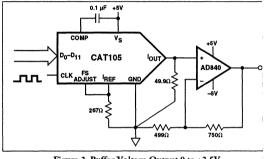

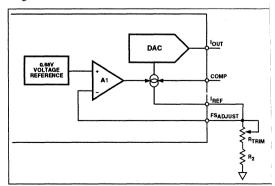

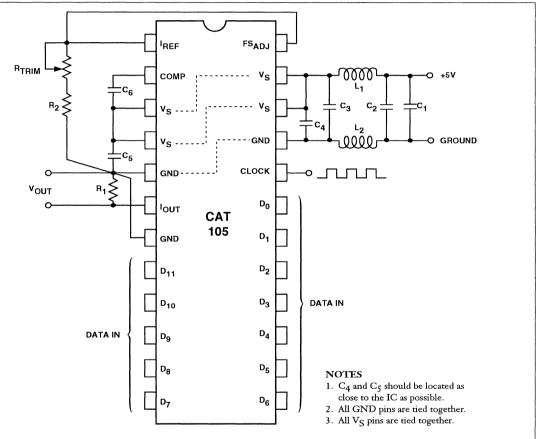

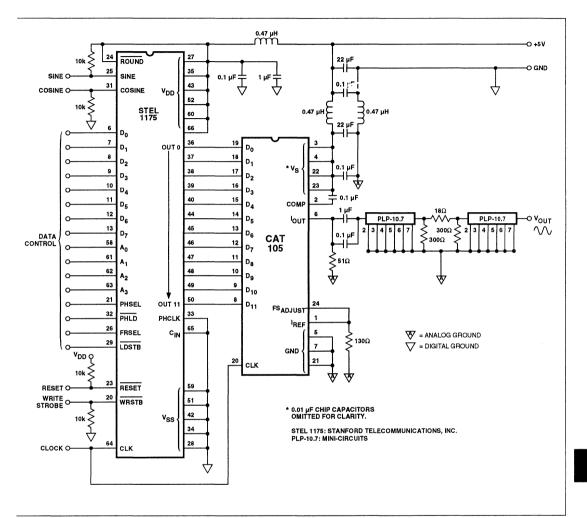

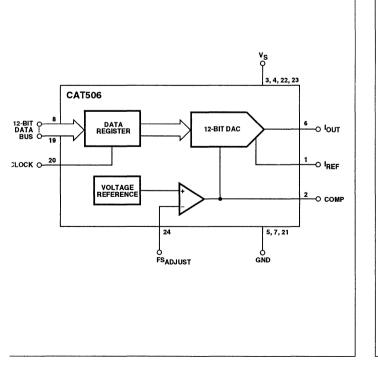

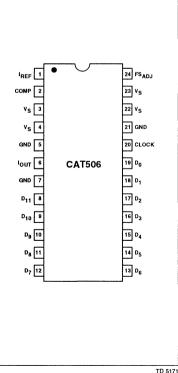

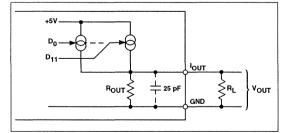

| CAT104/105   | 12 Bit, 25MHz D/A Converter11-           |

|--------------|------------------------------------------|

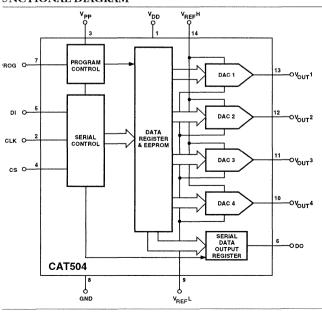

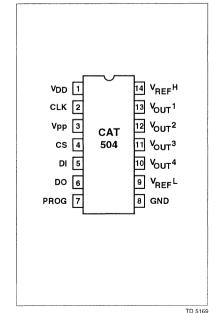

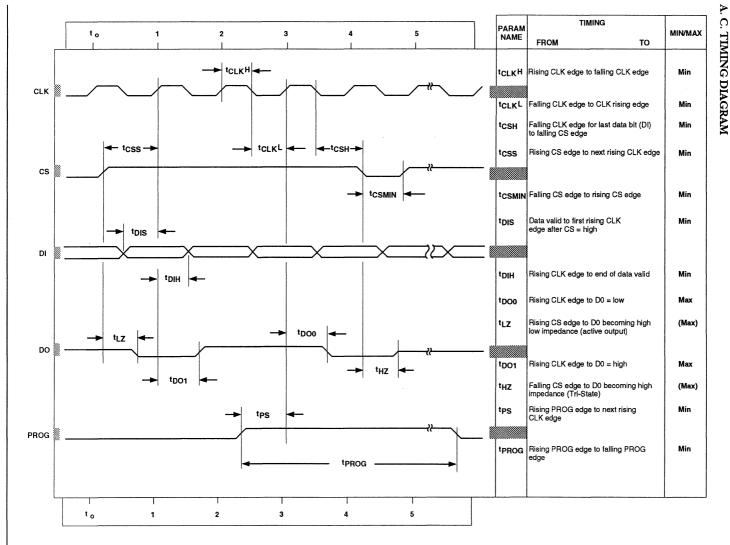

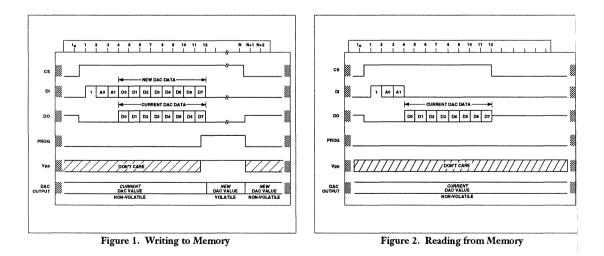

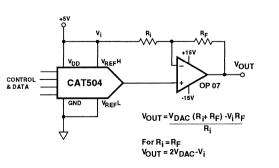

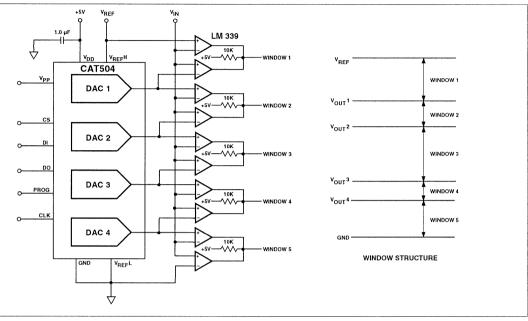

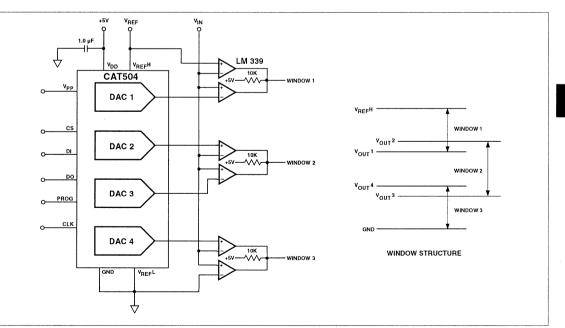

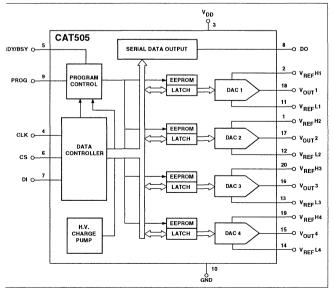

| CAT504       | Quad DACpot, 8 Bit D/A Converter11-13    |

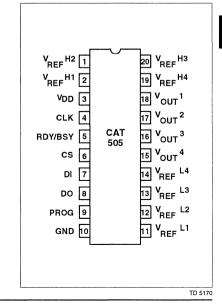

| CAT505       | Quad DACpot, 8 Bit D/A Converter, 5V11-2 |

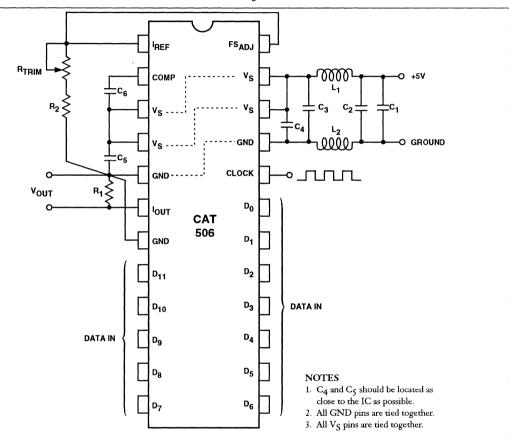

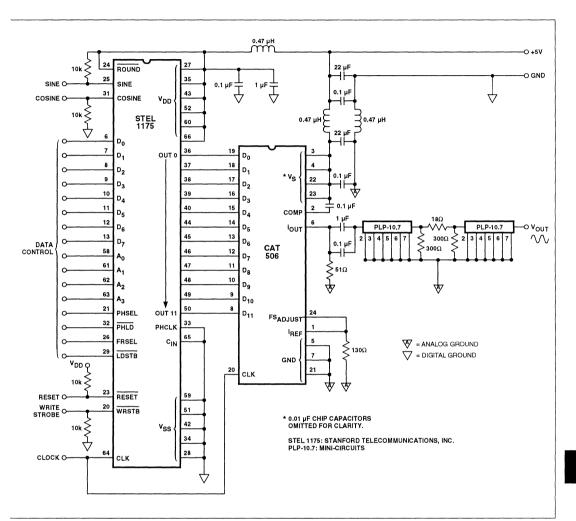

| CAT506       | 12 Bit, 40MHz D/A Converter11-3          |

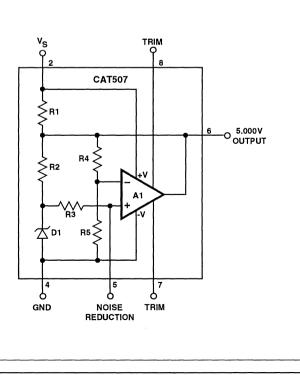

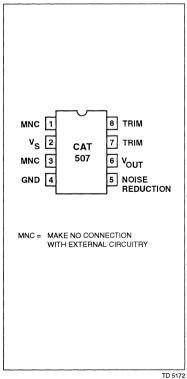

| CAT507       | Precision +5.000V Reference              |

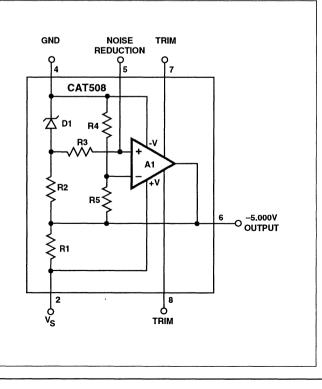

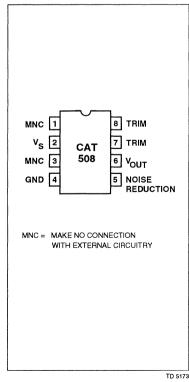

| CAT508       | Precision -5.000V Reference              |

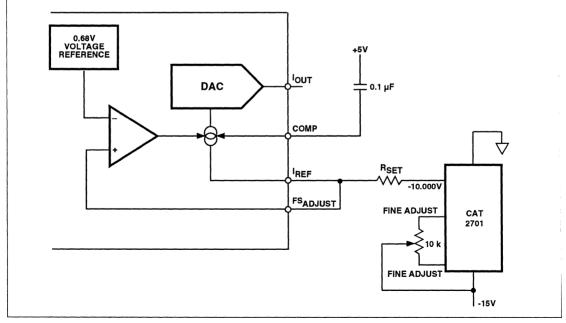

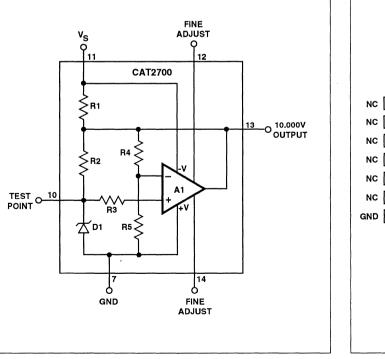

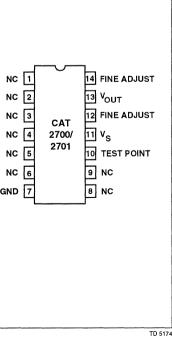

| CAT2700/2701 | Precision +10.000V Reference             |

#### SECTION 12 APPLICATION NOTES

| Using Catalyst's Serial E <sup>2</sup> PROMs in Shared Input/Out Configuration |       |

|--------------------------------------------------------------------------------|-------|

| The CAT93C46 Start-Bit Timing                                                  | 12-5  |

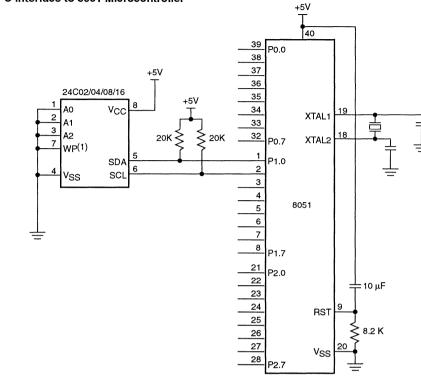

| I <sup>2</sup> C Interface to 8051 Microcontroller                             | 12-7  |

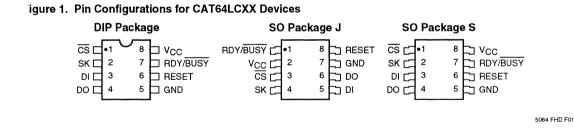

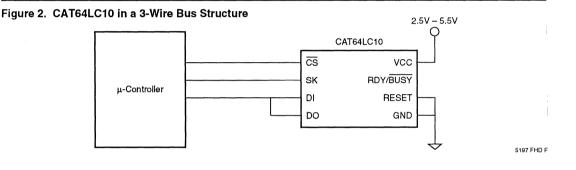

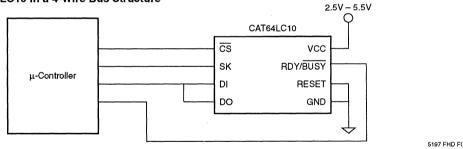

| CAT64LC10: A User-Friendly Serial E <sup>2</sup> PROM                          | 12-17 |

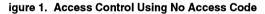

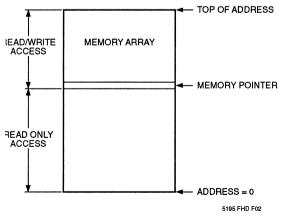

| How to Use Catalyst Secure Access Serial E <sup>2</sup> PROMs                  |       |

| Catalyst Parallel E <sup>2</sup> PROMs Feature Software Data Protection        |       |

| Advantages of 5V Flash Memories                                                |       |

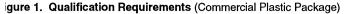

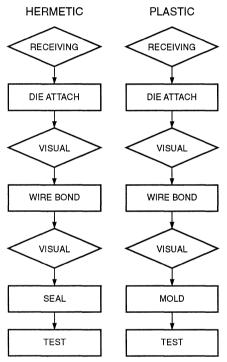

#### SECTION 13 QUALITY AND RELIABILITY

| Catalyst Quality and Reliability                                                        | 13-1  |

|-----------------------------------------------------------------------------------------|-------|

| Warranty Procedure                                                                      |       |

| Reliability Considerations for E <sup>2</sup> PROMs                                     | 13-19 |

| E <sup>2</sup> PROM Reliability: On-Chip Error Code Correction for E <sup>2</sup> PROMs | 13-23 |

| <b>SECTION 13</b> | QUALITY AND RELIABILITY (CONT'D)                                                |       |

|-------------------|---------------------------------------------------------------------------------|-------|

|                   | Procurement Considerations for Reprogrammable Nonvolatile Microcircuit Memories | 13-27 |

|                   | Full-Featured E <sup>2</sup> PROM Cell Operation                                | 13-35 |

|                   | Flash Memory Cell Operation                                                     | 13-37 |

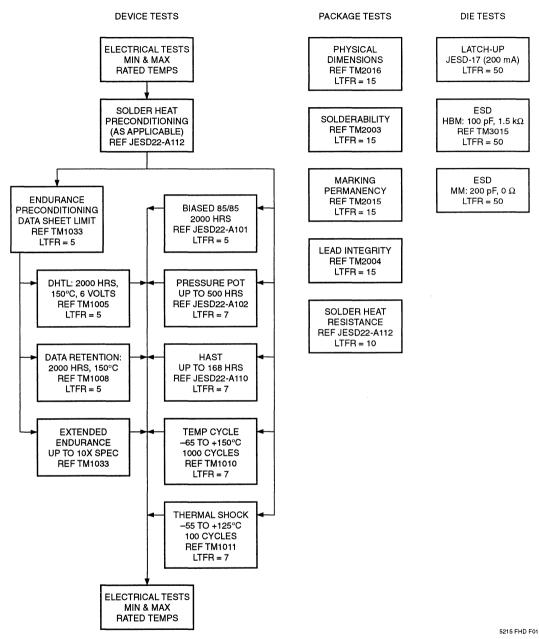

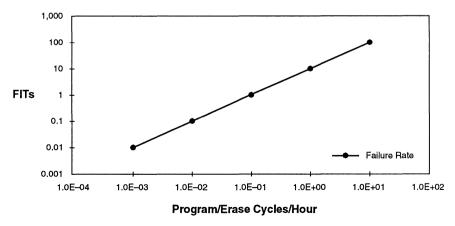

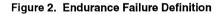

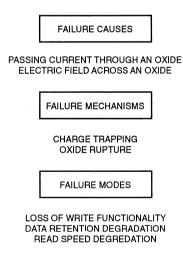

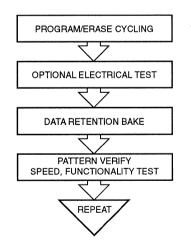

|                   | Failure Rate Prediction                                                         | 13-39 |

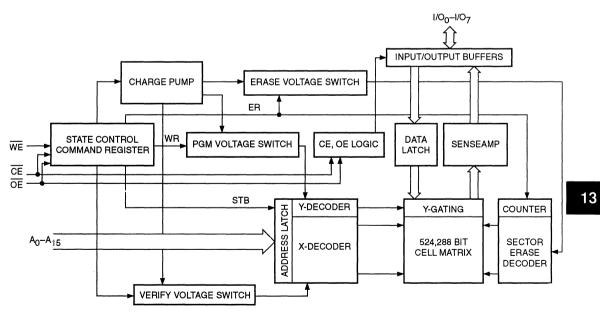

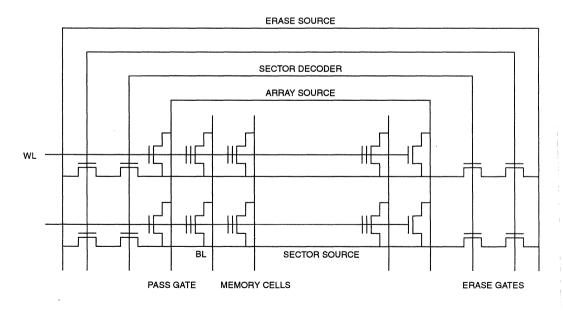

|                   | Single Transistor 5V Flash Technology, with Sector Erase                        | 13-41 |

|                   | Features and Performance of Reprogrammable Nonvolatile Floating Gate Memories   | 13-45 |

|                   |                                                                                 |       |

| <b>SECTION 14</b> | DIE PRODUCTS                                                                    |       |

|                   | Catalyst Die Products                                                           | 14-1  |

| SECTION 15        | GENERAL INFORMATION                                                             |       |

| SECTION 15        | Ordering Information                                                            | 15-1  |

|                   | 2-Wire Bus Structure Serial E <sup>2</sup> PROMs                                |       |

|                   | 3-Wire Bus Structure Serial E <sup>2</sup> PROMs                                | 15-8  |

|                   | SPI Bus Structure Serial E <sup>2</sup> PROMs                                   | 15-14 |

|                   | 4-Wire Bus Structure Serial E <sup>2</sup> PROMs                                | 15-16 |

|                   | Secure Access Serial E <sup>2</sup> PROMs                                       | 15-17 |

|                   | Parallel E <sup>2</sup> PROMs                                                   | 15-19 |

|                   | Flash Memories                                                                  | 15-23 |

|                   | EPROMs                                                                          | 15-26 |

|                   | NVRAMs                                                                          | 15-28 |

|                   | DACs-High Speed                                                                 | 15-29 |

|                   | DACs-Low Speed DACpot                                                           | 15-29 |

|                   | Voltage References                                                              | 15-30 |

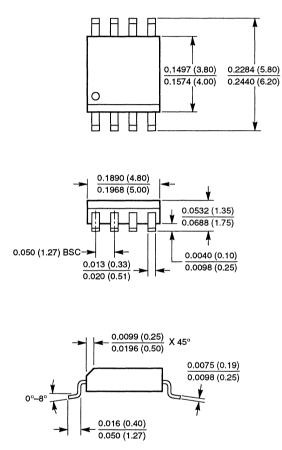

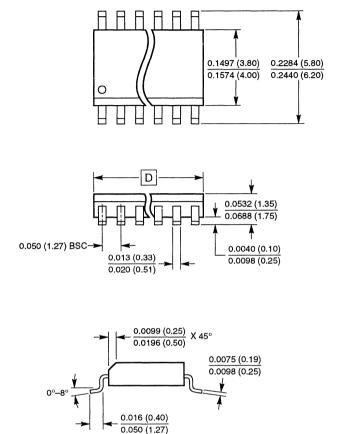

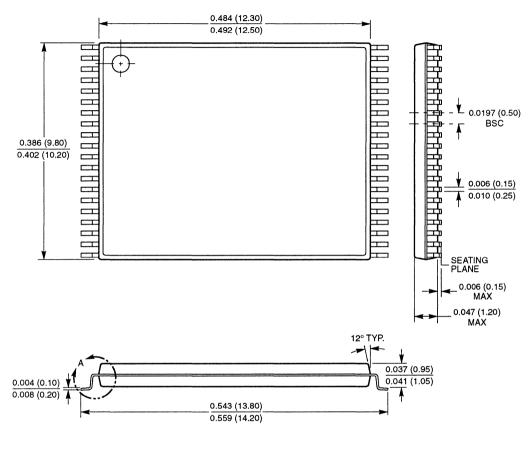

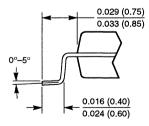

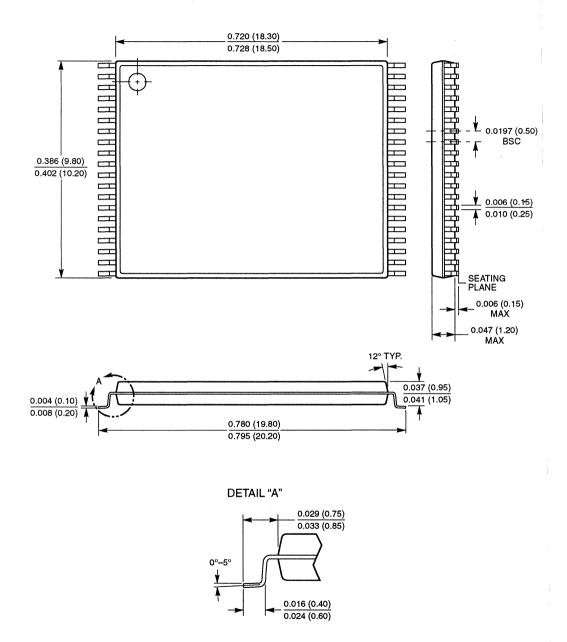

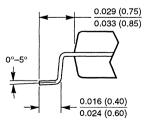

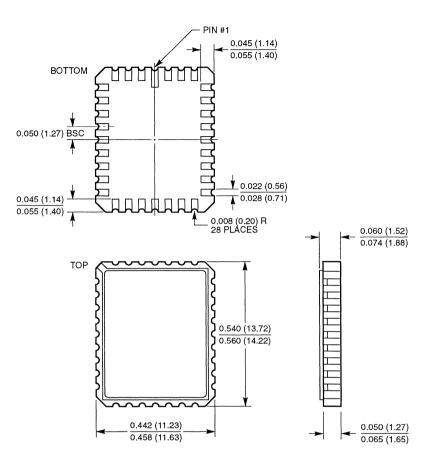

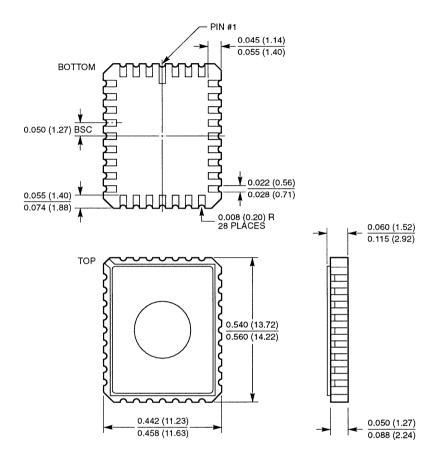

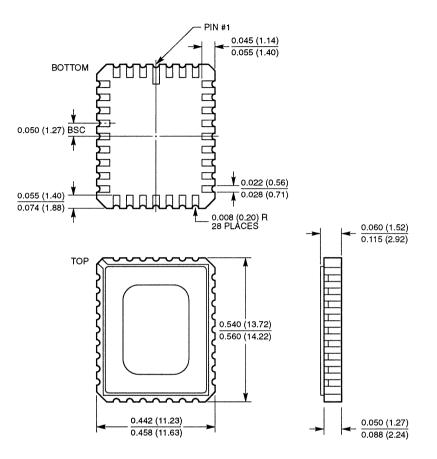

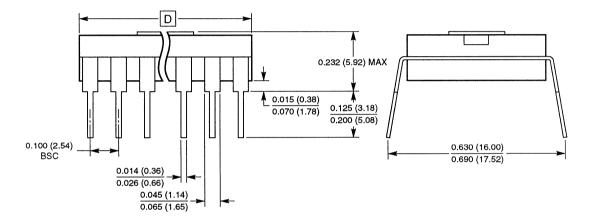

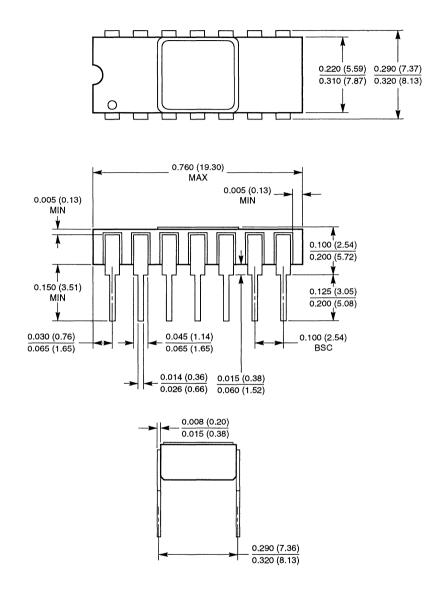

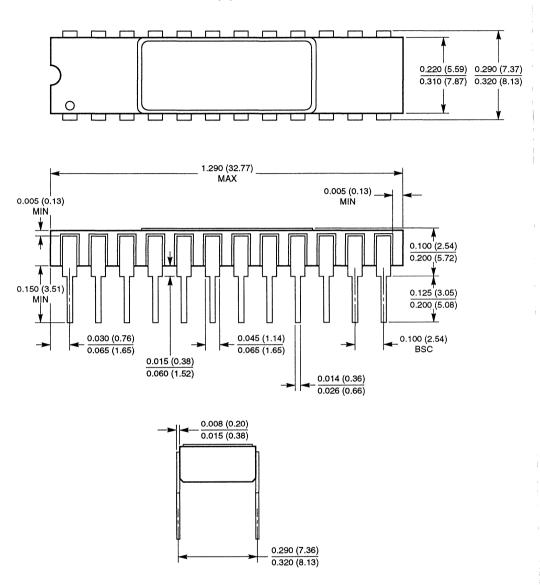

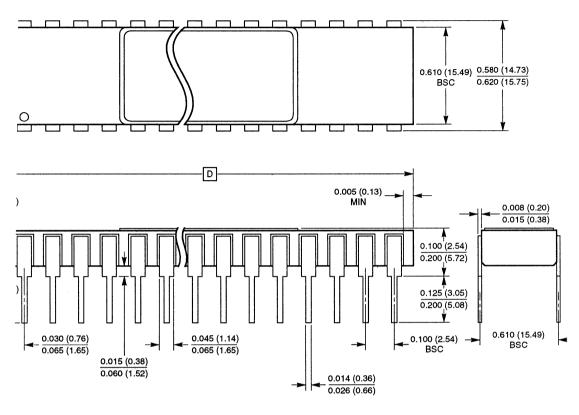

|                   | Packaging Information                                                           | 15-31 |

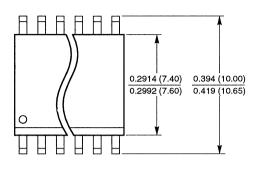

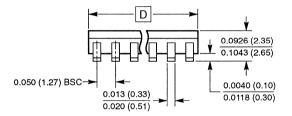

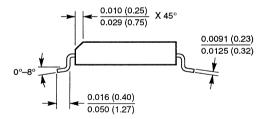

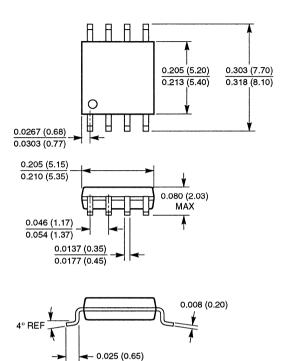

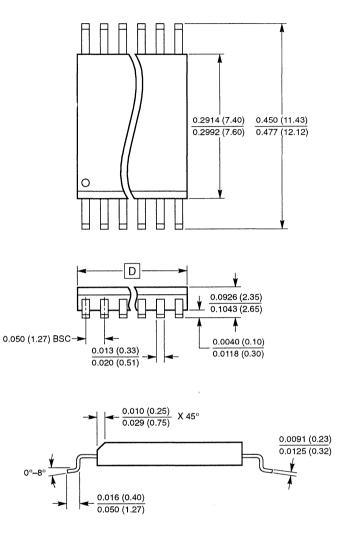

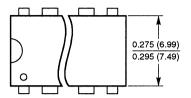

|                   | SOIC                                                                            | 15-31 |

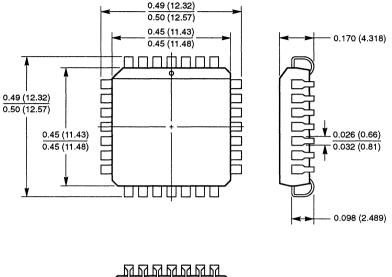

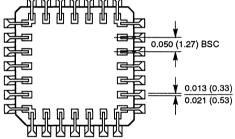

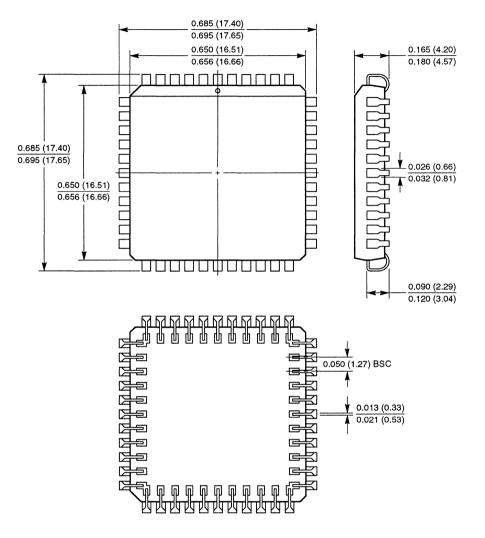

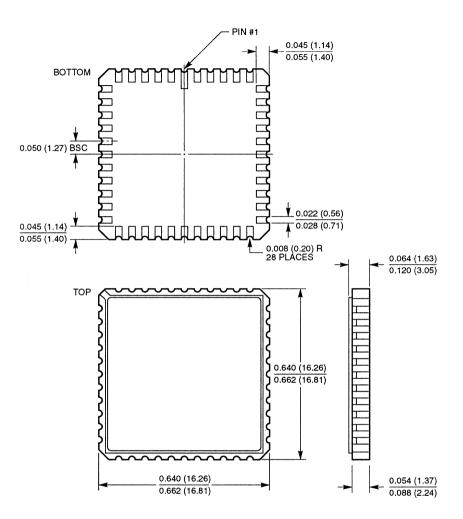

|                   | PLCC                                                                            | 15-36 |

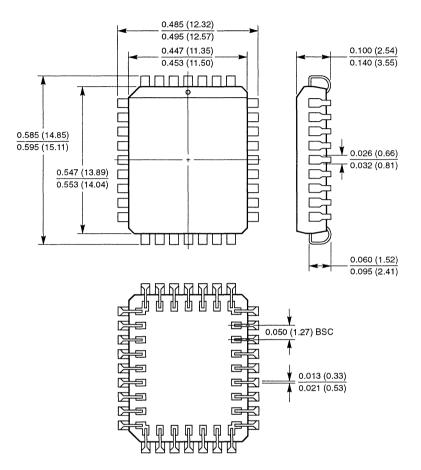

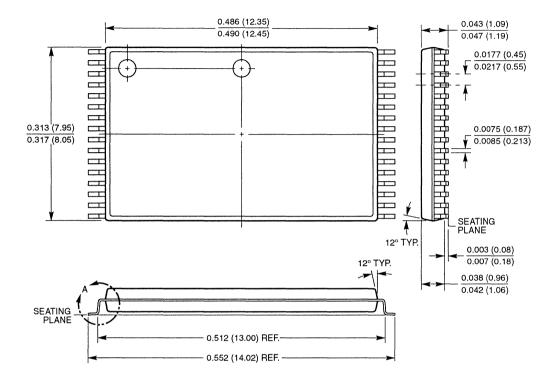

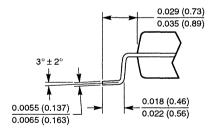

|                   | TSOP                                                                            | 15-39 |

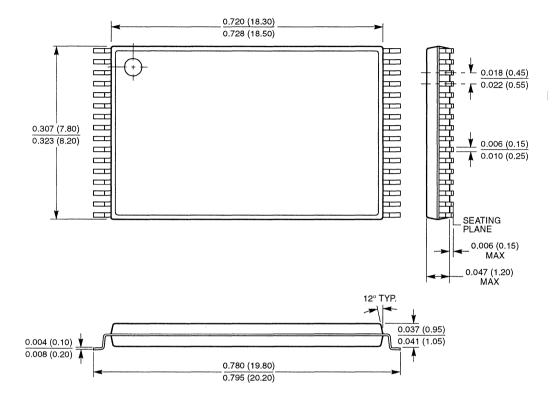

|                   | LCC                                                                             | 15-44 |

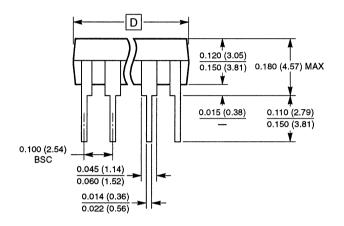

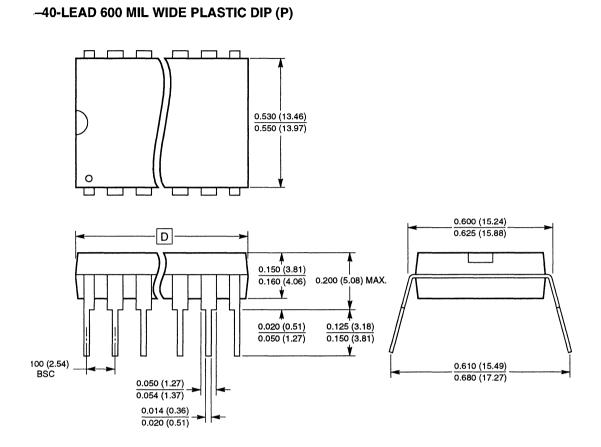

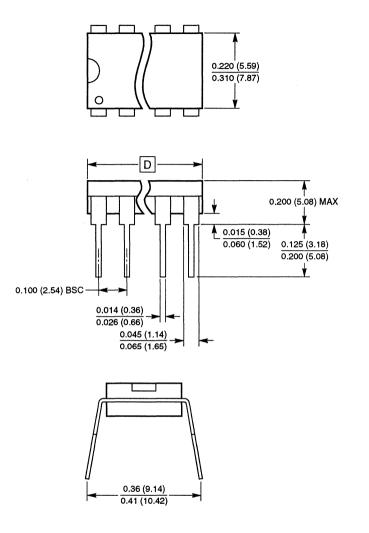

|                   | Plastic DIP                                                                     | 15-48 |

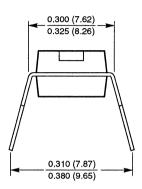

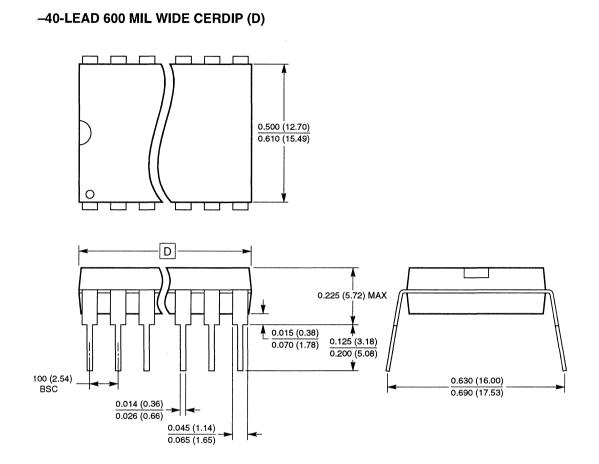

|                   | CERDIP                                                                          | 15-50 |

|                   | Sidebraze                                                                       | 15-53 |

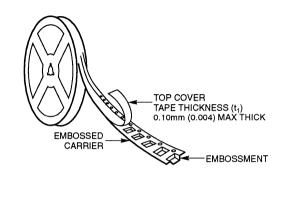

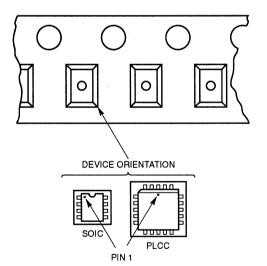

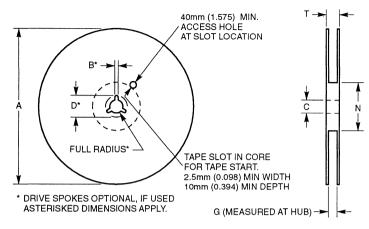

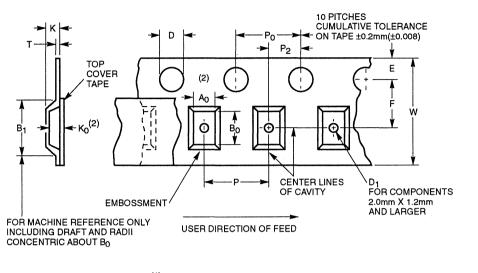

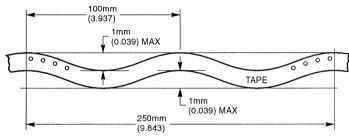

|                   | Tape and Reel                                                                   | 15-56 |

|                   | Sales Offices                                                                   | 15-61 |

# **IIIII CATALYST**

| Product Information                       | 1  |

|-------------------------------------------|----|

| 2-Wire Bus Serial E <sup>2</sup> PROMs    | 2  |

| 3-Wire Bus Serial E <sup>2</sup> PROMs    | 3  |

| SPI Bus Serial E <sup>2</sup> PROMs       | 4  |

| 4-Wire Bus Serial E <sup>2</sup> PROMs    | 5  |

| Secure Access Serial E <sup>2</sup> PROMs | 6  |

| Parallel E <sup>2</sup> PROMs             | 7  |

| Flash Memories                            | 8  |

| EPROMs                                    | 9  |

| NVRAMs                                    | 10 |

| Analog Products                           | 11 |

| Application Notes                         | 12 |

| Quality and Reliability                   | 13 |

| Die Products                              | 14 |

| General Information                       | 15 |

ix

| Product Information                       | 1  |

|-------------------------------------------|----|

| 2-Wire Bus Serial E <sup>2</sup> PROMs    | 2  |

| 3-Wire Bus Serial E <sup>2</sup> PROMs    | 3  |

| SPI Bus Serial E <sup>2</sup> PROMs       | 4  |

| 4-Wire Bus Serial E <sup>2</sup> PROMs    | 5  |

| Secure Access Serial E <sup>2</sup> PROMs | 6  |

| Parallel E <sup>2</sup> PROMs             | 7  |

| Flash Memories                            | 8  |

| EPROMs                                    | 9  |

| NVRAMS                                    | 10 |

| Analog Products                           | 11 |

| Application Notes                         | 12 |

| Quality and Reliability                   | 13 |

| Die Products                              | 14 |

| General Information                       | 15 |

## Contents

| SECTION 1 | PRODUCT INFORMATION                            |      |

|-----------|------------------------------------------------|------|

|           | Alpha-Numeric Index                            | 1-1  |

|           | Product Selection Guide                        | 1-5  |

|           | Ordering Information (Part Number Description) | 1-11 |

1

# Alpha-Numeric Index

| PART NO.                 | ORGANIZATION | DESCRIPTION                                                                                                   | PAGE           |

|--------------------------|--------------|---------------------------------------------------------------------------------------------------------------|----------------|

| CAT104/105               |              | .12 Bit, 25MHz D/A Converter                                                                                  | 11-1           |

| CAT22C10/CAT22C10I       | .64 x 4      | .256-Bit NVRAM                                                                                                | 10-1           |

| CAT22C12/CAT22C12I       | .256 x 4     | .1K NVRAM                                                                                                     | 10-9           |

| CAT24C02/CAT24C02I       | .256 x 8     | .2K 2-Wire Bus Serial E <sup>2</sup> PROM<br>with Hardware Write Protection                                   | 2-1            |

| CAT24C02A/CAT24C02AI     | .256 x 8     | .2K 2-Wire Bus Serial E <sup>2</sup> PROM                                                                     | 2-17           |

| CAT24C04/CAT24C04I       | .512 x 8     | .4K 2-Wire Bus Serial E <sup>2</sup> PROM                                                                     | 2-33           |

| CAT24C08/CAT24C08I       | . 1024 x 8   | .8K 2-Wire Bus Serial E <sup>2</sup> PROM                                                                     | 2-49           |

| CAT24C16/CAT24C16I       | .2048 x 8    | .16K 2-Wire Bus Serial E <sup>2</sup> PROM                                                                    | 2-65           |

| CAT24C32/CAT24C32I       | .4096 x 8    | .32K, 2-Wire Bus Serial E <sup>2</sup> PROM                                                                   | 2-81           |

| CAT24C44/CAT24C44I       | . 16 x 16    | .256-Bit Serial NVRAM                                                                                         | . 10-17        |

| CAT24LC02/CAT24LC02I     | .256 x 8     | .2K, 3–6 Volt, 2-Wire Bus Serial E <sup>2</sup> PROM with Hardware Write Protection                           | 2-9            |

| CAT24LC02A/CAT24LC02AI   | .256 x 8     | .2K, 3–6 Volt, 2-Wire Bus Serial E <sup>2</sup> PROM                                                          | 2 <b>-</b> 25  |

| CAT24LC04/CAT24LC04I     | .512 x 8     | .4K, 3–6 Volt, 2-Wire Bus Serial E <sup>2</sup> PROM                                                          | 2-41           |

| CAT24LC08/CAT24LC08I     | . 1024 x 8   | .8K, 3–6 Volt, 2-Wire Bus Serial E <sup>2</sup> PROM                                                          | 2-57           |

| CAT24LC16/CAT24LC16I     | .2048 x 8    | .16K, 3–6 Volt, 2-Wire Bus Serial E <sup>2</sup> PROM                                                         | 2-73           |

| CAT2700/2701             |              | Precision +10.000V Reference                                                                                  | . 11-51        |

| CAT27C210/CAT27C210I     | .64K x 16    | .1M, High Speed, Low Power UV EPROM                                                                           | 9-13           |

| CAT27HC256L/CAT27HC256LI | .32K x 8     | .256K, High Speed, Low Power UV EPROM                                                                         | 9-1            |

| CAT28C16A/CAT28C16AI     | .2K x 8      | . 16K Parallel E <sup>2</sup> PROM with $\overline{DATA}$ Polling                                             | 7-1            |

| CAT28C16V3               | .2K x 8      | . 16K, 3 Volt, Parallel E <sup>2</sup> PROM with $\overline{DATA}$ Pollir                                     | ıg <b>7-</b> 9 |

| CAT28C17A/CAT28C17AI     | .2K x 8      | .16K Parallel E <sup>2</sup> PROM with DATA Polling,<br>RDY/BUSY                                              | 7-17           |

| CAT28C64A/CAT28C64AI     | .8K x 8      | .64K Parallel E <sup>2</sup> PROM with DATA Polling,<br>Hardware Write Protection                             | 7-25           |

| CAT28C64B/CAT28C64BI     | .8K x 8      | .64K Parallel E <sup>2</sup> PROM with DATA Polling,<br>Toggle Bit, Hardware and Software Write<br>Protection | 7-41           |

| CAT28C65A/CAT28C65AI     | .8K x 8      | .64K Parallel E <sup>2</sup> PROM with DATA Polling,<br>RDY/BUSY, Hardware Write Protection                   | 7-33           |

#### **Alpha-Numeric Index** PART NO. ORGANIZATION DESCRIPTION ..64K Parallel E<sup>2</sup>PROM with DATA Polling, CAT28C65B/CAT28C65BI ......8K x 8 ..... Toggle Bit, RDY/BUSY, Hardware and Toggle Bit, Hardware and Software Write

PAGE

| CAT33C704/CAT33C704I256 x 16, 512 x 84K, 3 Volt, Secure Access Serial E <sup>2</sup> PROM<br>with High Speed Synchronous Protocol6-1 |

|--------------------------------------------------------------------------------------------------------------------------------------|

| CAT33C804A-B<br>CAT33C804A-BI                                                                                                        |

| CAT35C102/CAT35C102I                                                                                                                 |

| CAT35C104/CAT35C104I256 x 16, 512 x 84K 3-Wire Bus Serial E <sup>2</sup> PROM                                                        |

| CAT35C108/CAT35C108I512 x 16, 1024 x 88K 3-Wire Bus Serial E <sup>2</sup> PROM<br>with Sequential Read, Write Protect3-89            |

| CAT35C116/CAT35C116I                                                                                                                 |

| CAT35C202/CAT35C202I                                                                                                                 |

| CAT35C704/CAT35C704I256 x 16, 512 x 84K Secure Access Serial E <sup>2</sup> PROM<br>with High Speed Synchronous Protocol6-15         |

| CAT35C804A-B<br>CAT35C804A-Bl                                                                                                        |

|                                                                                                                                      |

| CAT504 Quad DACpot, 8 Bit D/A Converter                                                                                              |

|                                                                                                                                      |

CAT33C104/CAT33C104I ......256 x 16, 512 x 8 .......4K, 3 Volt, 3-Wire Bus Serial E<sup>2</sup>PROM ......3-65

CAT33C108/CAT33C108l ......512 x 16, 1024 x 8 ......8K, 3 Volt, 3-Wire Bus Serial E<sup>2</sup>PROM

CAT33C116/CAT33C116I ......1024 x 16, 2048 x 8 ......16K, 3 Volt, 3-Wire Bus Serial E<sup>2</sup>PROM

#### Alpha-Numeric Index

| PART NO.             | ORGANIZATION        | DESCRIPTION                                                          | PAGE  |

|----------------------|---------------------|----------------------------------------------------------------------|-------|

| CAT507               |                     | . Precision +5.000V Reference                                        | 11-47 |

| CAT508               |                     | Precision –5.000V Reference                                          | 11-49 |

| CAT59C11/CAT59C11I   | .64 x 16, 128 x 8   | .1K 4-Wire Bus Serial E <sup>2</sup> PROM<br>with RDY/BUSY           | 5-1   |

| CAT64LC10/CAT64LC10I | .64 x 16            | . 1K, 2.5V–5.5V, SPI Bus Serial E <sup>2</sup> PROM<br>with RDY/BUSY | 4-1   |

| CAT64LC20/CAT64LC20I | . 128 x 16          | .2K, 2.5V–5.5V, SPI Bus Serial E <sup>2</sup> PROM<br>with RDY/BUSY  | 4-11  |

| CAT64LC40/CAT64LC40I | .256 x 16           | .4K, 2.5V–5.5V, SPI Bus Serial E <sup>2</sup> PROM<br>with RDY/BUSY  | 4-21  |

| CAT93C46/CAT93C46I   | .64 x 16, 128 x 8   | .1K 3-Wire Bus Serial E <sup>2</sup> PROM                            | 3-1   |

| CAT93C46A/CAT93C46AI | .64 x 16            | .1K 3-Wire Bus Serial E <sup>2</sup> PROM                            | 3-9   |

| CAT93C46B/CAT93C46BI | .64 x 16, 128 x 8   | .1K 3-Wire Bus Serial E <sup>2</sup> PROM                            | 3-17  |

| CAT93C56/CAT93C56I   | . 128 x 16, 256 x 8 | .2K 3-Wire Bus Serial E <sup>2</sup> PROM                            | 3-41  |

| CAT93LC56/CAT93LC56I | . 128 x 16, 256 x 8 | .2K, 3 Volt, 3-Wire Bus Serial E <sup>2</sup> PROM                   | 3-49  |

## **Product Selection Guide**

### SERIAL E<sup>2</sup>PROMs

#### 2-Wire Bus Structure (Data Book Section 2)

| Device     | Temp.<br>Range | Compatibility          | Size<br>(Organization) | I <sub>CC</sub><br>(Max/<br>Standby) | Max<br>Clock<br>Freq. | #<br>Pins | Pkg<br>Types | Voltage |

|------------|----------------|------------------------|------------------------|--------------------------------------|-----------------------|-----------|--------------|---------|

| CAT24C02   | C, I           | Xicor                  | 2K Bit<br>(256 x 8)    | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 5 V     |

| CAT24LC02  | C, I           | Xicor                  | 2K Bit<br>(256 x 8)    | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 3–6 V   |

| CAT24C02A  | C, I           | Xicor                  | 2K Bit<br>(256 x 8)    | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 5 V     |

| CAT24LC02A | C, I           | Xicor                  | 2K Bit<br>(256 x 8)    | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 3–6 V   |

| CAT24C04   | C, I           | Xicor                  | 4K Bit<br>(512 x 8)    | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 5 V     |

| CAT24LC04  | C, I           | Xicor                  | 4K Bit<br>(512 x 8)    | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 3–6 V   |

| CAT24C08   | C, I           | Xicor                  | 8K Bit<br>(1024 x 8)   | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 5 V     |

| CAT24LC08  | C, I           | Xicor                  | 8K Bit<br>(1024 x 8)   | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 3–6 V   |

| CAT24C16   | C, I           | Xicor                  | 16K Bit<br>(2048 x 8)  | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 5 V     |

| CAT24LC16  | C, I           | Xicor                  | 16K Bit<br>(2048 x 8)  | 3mA/4µA                              | 100kHz                | 8<br>14   | P, J<br>J    | 3–6 V   |

| CAT24C32   | C, I           | Xicor<br>24C16 UPGRADE | 32K Bit<br>(4096 x 8)  | 3mA/4µA                              | 100kHz                | 8<br>14   | P<br>J       | 5 V     |

Note:

(1) All I<sup>2</sup>C devices offered in ZERO Power™ (I<sub>SBZ</sub> = 0µA) version.

(2) Catalyst Semiconductor is licenced by Philips Corporation to carry the I<sup>2</sup>C Bus Protocol.

(3) All Serial E<sup>2</sup>PROMs offered in High Endurance Version ("H").

(4) For information on military temperature devices, please contact the factory.

#### SERIAL E<sup>2</sup>PROMs

#### 3-Wire Bus Structure (Data Book Section 3)

| Device    | Temp.<br>Range | Compatibility             | Size<br>(Organization) | I <sub>CC</sub><br>(Max/<br>Standby) | Max<br>Clock<br>Freq. | #<br>Pins | Pkg<br>Types | Voltage |

|-----------|----------------|---------------------------|------------------------|--------------------------------------|-----------------------|-----------|--------------|---------|

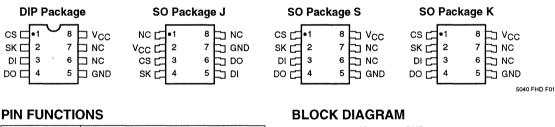

| CAT93C46A | C, I           | National 93C46            | 1K Bit<br>(64x16)      | 3mA/100μA                            | 1 MHz                 | 8         | P, K, J, S   | 5 V     |

| CAT93C46B | C, I           | National 93C46            | 1K Bit<br>(x8 or x16)  | 3mA/100μA                            | 1MHz                  | 8         | P, K, J, S   | 5 V     |

| CAT93C46  | C, I           | National 93C46            | 1K Bit<br>(x8 or x16)  | 3mA/100μA                            | 1 MHz                 | 8         | P, K, J, S   | 5 V     |

| CAT33C101 | C, I           | National 93C46<br>UPGRADE | 1K Bit<br>(x8 or x16)  | 2mA/50µA                             | 250kHz                | 8         | P, K, J, S   | 3 V     |

| CAT32C101 | с              | National 93C46<br>UPGRADE | 1K Bit<br>(x8 or x16)  | 2mA/2µA                              | 250kHz                | 8         | P, K, J      | 2.2 V   |

| CAT93C56  | C, I           | National 93C56            | 2K Bit<br>(x8 or x16)  | 3mA/100μA                            | 1MHz                  | 8         | P, K, S      | 5 V     |

| CAT93LC56 | C, I           | National 93C56<br>UPGRADE | 2K Bit<br>(x8 or x16)  | 2mA/50μA                             | 250kHz                | 8         | P, K, S      | 3 V     |

| CAT35C102 | C, I           | National 93C46<br>UPGRADE | 2K Bit<br>(x8 or x16)  | 3mA/100μA                            | 1MHz                  | 8         | P, K, S      | 5 V     |

| CAT33C104 | C, I           | National 93C66<br>UPGRADE | 4K Bit<br>(x8 or x16)  | 2mA/50μA                             | 250kHz                | 8         | P, K, S      | 3 V     |

| CAT35C104 | C, I           | National 93C66            | 4K Bit<br>(x8 or x16)  | 3mA/100μA                            | 1MHz                  | 8         | P, K, S      | 5 V     |

| CAT33C108 | C<br>I         | National 93C66<br>UPGRADE | 8K Bit<br>(x8 or x16)  | 2mA/10μA<br>3mA/10μA                 | 1MHz                  | 8         | P, K, S      | 3 V     |

| CAT35C108 | C<br>I         | National 93C66<br>UPGRADE | 8K Bit<br>(x8 or x16)  | 3mA/10μA<br>4mA/10μA                 | ЗMHz                  | 8         | P, K, S      | 5 V     |

| CAT33C116 | C<br>I         | National 93C66<br>UPGRADE | 16K Bit<br>(x8 or x16) | 2mA/10μA<br>3mA/10μA                 | 1MHz                  | 8         | P, K, S      | 3 V     |

| CAT35C116 | C<br>I         | National 93C66<br>UPGRADE | 16K Bit<br>(x8 or x16) | 3mA/10μA<br>4mA/10μA                 | ЗMHz                  | 8         | P, K, S      | 5 V     |

#### SERIAL E<sup>2</sup>PROMs

#### SPI Bus Structure (Data Book Section 4)

| Device    | Temp.<br>Range | Compatibility | Size<br>(Organization) | I <sub>CC</sub><br>(Max/<br>Standby) | Max<br>Clock<br>Freq. | #<br>Pins | Pkg<br>Types | Voltage   |

|-----------|----------------|---------------|------------------------|--------------------------------------|-----------------------|-----------|--------------|-----------|

| CAT64LC10 | C, I           | Asahi         | 1K Bit<br>(64 x 16)    | 1mA/3µА                              | 1MHz                  | 8         | P, J, S      | 2.5–5.5 V |

| CAT64LC20 | C, I           | Asahi         | 2K Bit<br>(128 x 16)   | 1mA/3µA                              | 1 MHz                 | 8         | P, J, S      | 2.5–5.5 V |

| CAT64LC40 | C, I           | Asahi         | 4K Bit<br>(256 x 16)   | 1mA/3µА                              | 1 MHz                 | 8         | P, J, S      | 2.5–5.5 V |

Note:

All SPI devices offered in ZERO Power™ (I<sub>SBZ</sub> = 0µA) Version.

All Serial E<sup>2</sup>PROMs offered in High Endurance Version ("H").

(3) For information on military temperature devices, please contact the factory.

#### SERIAL E<sup>2</sup>PROMs

#### 4-Wire Bus Structure (Data Book Section 5)

| Device    | Temp.<br>Range | Compatibility             | Size<br>(Organization) | I <sub>CC</sub><br>(Max/<br>Standby) | Max<br>Clock<br>Freq. | #<br>Pins | Pkg<br>Types | Voltage |

|-----------|----------------|---------------------------|------------------------|--------------------------------------|-----------------------|-----------|--------------|---------|

| CAT59C11  | C, I           | Microchip 5911            | 1K Bit<br>(x8 or x16)  | 5mA/100µA                            | 1MHz                  | 8         | Р, К         | 5 V     |

| CAT35C202 | C<br>I         | Microchip 5911<br>UPGRADE | 2K Bit<br>(x8 or x16)  | 3mA/100μA<br>4mA/100μA               | 1MHz                  | 8         | Р, К         | 5 V     |

#### SECURE ACCESS SERIAL E<sup>2</sup>PROMs (Data Book Section 6)

| Device       | Temp.<br>Range | Protocol    | Size<br>(Organization) | I <sub>CC</sub><br>(Max/<br>Standby) | Max<br>Clock<br>Freq. | #<br>Pins | Pkg<br>Types | Voltage |

|--------------|----------------|-------------|------------------------|--------------------------------------|-----------------------|-----------|--------------|---------|

| CAT33C704    | C, I           | 0           |                        | 3mA/250µA                            | 1MHz                  |           |              | 3 V     |

| CAT35C704    | C, I           | Synchronous | 4K Bit                 | 3mA/250µA                            | ЗMHz                  | 8         | Р            | 5 V     |

| CAT33C804A-B | C, I           | VART        | (x8 or x16)            | 3mA/250µA                            | 5MHz                  | 16        | J            | 3 V     |

| CAT35C804A-B | C, I           | Compatible  |                        | 3mA/250µA                            | 5MHz                  |           |              | 5 V     |

#### PARALLEL E<sup>2</sup>PROMs (Data Book Section 7)

| Device     | Temp.<br>Range | Size<br>(Organization) | Access<br>Time (ns)    | I <sub>CC</sub><br>(Max/<br>Standby) | #<br>Pins | Pkg<br>Types | Voltage |

|------------|----------------|------------------------|------------------------|--------------------------------------|-----------|--------------|---------|

| CAT28C16A  | C, I           | 16K Bit (2Kx8)         | 200                    | 25mA/100µA                           | 24<br>24  | P<br>K, J    | 5 V     |

| CAT28C16V3 | С              | 16K Bit (2Kx8)         | 700                    | 10mA/50µA                            | 32        | N            | 3 V     |

| CAT28C17A  | C, I           | 16K Bit (2Kx8)         | 200                    | 25mA/100µA                           | 28<br>32  | P, K, J<br>N | 5 V     |

| CAT28C64A  | C, I           | 64K Bit (8Kx8)         | 150/200/250            | 30mA/100µA                           | 28        | P, J, K      | 5V      |

| CAT28C65A  | C, I           | 64K Bit (8Kx8)         | 150/200/250            | 30mA/100µA                           | 32        | N            | 5 V     |

| CAT28C64B  | C<br>I         | 64K Bit (8Kx8)         | 120/150/200<br>150/200 | 25mA/100µA                           | 28        | P, J, K      | 5 V     |

| CAT28C65B  | C<br>I         | 64K Bit (8Kx8)         | 120/150/200<br>150/200 | 25mA/100µA                           | 32        | Ν, Τ         | 5 V     |

| CAT28C256  | C, I           | 256K Bit (32Kx8)       | 200/250/300            | 30mA/150µA                           | 28<br>32  | P<br>N       | 5 V     |

Note:

(1) All Serial E<sup>2</sup>PROMs offered in High Endurance version ("H").

(2) For information on military temperature devices, please contact the factory.

#### FLASH MEMORIES (Data Book Section 8)

| Device      | Temp.<br>Range | Size<br>(Organization) | Access<br>Time (ns) | I <sub>CC</sub><br>(Max/<br>Standby) | #<br>Pins | Pkg<br>Types | Voltage |

|-------------|----------------|------------------------|---------------------|--------------------------------------|-----------|--------------|---------|

| CAT28F512   | C, I           | 512K Bit (64Kx8)       | 120/150/200         | 30mA/100µA                           | 32        | P, N, T      | 12 V    |

| CAT28F512V5 | C, I           | 512K Bit (64Kx8)       | 120/150/200         | 120mA/100µA                          | 32        | P, N, T      | 5 V     |

| CAT28F010   | C, I           | 1M Bit (128Kx8)        | 120/150/200         | 30mA/100µA                           | 32        | P, N, T      | 12 V    |

| CAT28F010V5 | C, I           | 1M Bit (128Kx8)        | 120/150/200         | 120mA/100µA                          | 32        | P, N, T      | 5 V     |

| CAT28F020   | C, I           | 2M Bit (256Kx8)        | 120/150/200         | 30mA/100µA                           | 32        | P, N, T      | 12 V    |

#### EPROMS (Data Book Section 9)

| Device      | Temp.<br>Range | Size<br>(Organization) | Access<br>Time (ns)            | I <sub>CC</sub><br>(Max/<br>Standby) | #<br>Pins | Pkg<br>Types             | Programming<br>Voltage |

|-------------|----------------|------------------------|--------------------------------|--------------------------------------|-----------|--------------------------|------------------------|

| CAT27HC256L | C<br>I         | 256K Bit (32Kx8)       | 55/70/90/120<br>70/90/120      | 50mA/100μA<br>60mA/100μA             | 28<br>32  | D, P (OTP)<br>E, N (OTP) | 12.5 V                 |

| CAT27C210   | C<br>I         | 1M Bit (64Kx16)        | 150/170/200/250<br>170/200/250 | 50mA/100μA<br>60mA/100μA             | 40<br>44  | D, P (OTP)<br>N (OTP)    | 12.5 V                 |

#### NVRAMS (Data Book Section 10)

| Device   | Temp.<br>Range | Compatibility | Size<br>(Organization)    | I <sub>CC</sub><br>(Max/<br>Standby | Access<br>Time (ns) | #<br>Pins | Pkg<br>Types |

|----------|----------------|---------------|---------------------------|-------------------------------------|---------------------|-----------|--------------|

| CAT22C10 | C, I           | Xicor         | 256 Bit (64x4)            | 40mA/30μA                           | 200/300             | 18<br>20  | P<br>J       |

| CAT22C12 | C, I           | Xicor         | 1K Bit (256x4)            | 50mA/30µA                           | 200/300             | 18        | Р            |

| CAT24C44 | C, I           | Xicor         | 256 Bit (16x16)<br>Serial | 20mA/30µA                           | 1MHz                | 8<br>8    | P<br>J       |

Note:

(1) For information on military temperature devices, please contact the factory.

#### ANALOG PRODUCTS (Data Book Section 11)

#### DACs

| Device  | Temp.<br>Range | Bits<br>Resolution | Settling<br>Time (ns) | Linearity<br>Error (LSB) | Data<br>Latch | NV<br>Mem. | # DACs<br>/Pkg | Pkg<br>Types |

|---------|----------------|--------------------|-----------------------|--------------------------|---------------|------------|----------------|--------------|

| CAT104A | С              | 12                 | 40                    | 0.5                      | No            | No         | 1              | С            |

| CAT104B | С              | 12                 | 40                    | 1.0                      | No            | No         | 1              | С            |

| CAT105A | С              | 12                 | 40                    | 0.5                      | Yes           | No         | 1              | С            |

| CAT105B | С              | 12                 | 40                    | 1.0                      | Yes           | No         | 1              | С            |

| CAT504  | C, I           | 8                  | 10 (μs)               | 1.0                      | Yes           | Yes        | 4              | P, J         |

| CAT505  | C, I           | 8                  | 10 (µs)               | 1.0                      | Yes           | Yes        | 4              | P, J         |

| CAT506A | С              | 12                 | 25                    | 0.5                      | Yes           | No         | 1              | С            |

| CAT506B | С              | 12                 | 25                    | 1.0                      | Yes           | No         | 1              | С            |

#### VOLTAGE REFERENCES

| Device  | Temp.<br>Range | Output<br>Voltage | Output<br>Error (mV) | Adjustment<br>Range (%) | Drift with<br>Temp. (ppm/°C) | Pkg<br>Types |

|---------|----------------|-------------------|----------------------|-------------------------|------------------------------|--------------|

| CAT507  | C, I           | +5                | 15                   | 6                       | 3                            | P, D         |

| CAT508  | C, I           | -5                | 15                   | 6                       | 3                            | P, D         |

| CAT2700 | C, I           | +10               | 2.5                  | 0.2                     | 3                            | P, D         |

| CAT2701 | C, I           | -10               | 2.5                  | 0.2                     | 3                            | P, D         |

#### Note:

(1) For information on military temperature devices, please contact the factory.

#### Product Selection Guide

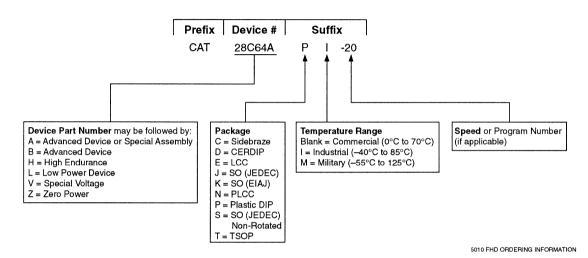

### **Ordering Tree (Part Number Description)**

#### **Explanation of Catalyst's Part Number Code**

Note:

(1) Refer to Section 15 for a detailed listing of Catalyst part numbers by product type.

(2) The device used in the above example is a CAT28C64API-20 (Plastic DIP, Industrial temperature, 200ns Access Time).

#### Ordering Tree

# **IIIII <u>CATALY</u>ST**

| Product Information                       | 1  |

|-------------------------------------------|----|

| 2-Wire Bus Serial E <sup>2</sup> PROMs    | 2  |

| 3-Wire Bus Serial E <sup>2</sup> PROMs    | 3  |

| SPI Bus Serial E <sup>2</sup> PROMs       | 4  |

| 4-Wire Bus Serial E <sup>2</sup> PROMs    | 5  |

| Secure Access Serial E <sup>2</sup> PROMs | 6  |

| Parallel E <sup>2</sup> PROMs             | 7  |

| Flash Memories                            | 8  |

| EPROMs                                    | 9  |

| NVRAMs                                    | 10 |

| Analog Products                           | 11 |

| Application Notes                         | 12 |

| Quality and Reliability                   | 13 |

| Die Products                              | 14 |

| General Information                       | 15 |

### Contents

| SECTION 2 | 2-WIRE BUS SERIAL E <sup>2</sup> PROMS |          |         |      |

|-----------|----------------------------------------|----------|---------|------|

|           | CAT24C02/CAT24C02I                     |          | 2K-Bit  | 2-1  |

|           | CAT24LC02/CAT24LC02I                   |          | 2K-Bit  | 2-9  |

|           | CAT24C02A/CAT24C02AI                   |          | 2K-Bit  | 2-17 |

|           | CAT24LC02A/CAT24LC02AI                 |          | 2K-Bit  | 2-25 |

|           | CAT24C04/CAT24C04I                     | 512 x 8  | 4K-Bit  | 2-33 |

|           | CAT24LC04/CAT24LC04I                   | 512 x 8  | 4K-Bit  | 2-41 |

|           | CAT24C08/CAT24C08I                     | 1024 x 8 | 8K-Bit  | 2-49 |

|           | CAT24LC08/CAT24LC08I                   |          | 8K-Bit  | 2-57 |

|           | CAT24C16/CAT24C16I                     | 2048 x 8 | 16K-Bit | 2-65 |

|           | CAT24LC16/CAT24LC16I                   |          | 16K-Bit | 2-73 |

|           | CAT24C32/CAT24C32                      | 4096 x 8 | 32K-Bit | 2-81 |

# CAT24C02/CAT24C02I

2K-Bit SERIAL E<sup>2</sup>PROM

#### **FEATURES**

- I<sup>2</sup>C Bus Compatible\*

- Low Power CMOS Technology

- Hardware Write Protect

- 8 Byte Page Write Buffer

- Self-Timed Write Cycle with Auto-Clear

- 100,000 Program/Erase Cycles

- 100 Year Data Retention

- 8 pin DIP, 8 pin SO or 14 pin SO Package

- ZERO Power<sup>™</sup> Version (CAT24C02Z) Available

- Optional High Endurance Device Available

#### DESCRIPTION

The CAT24C02/CAT24C02I is a 2K bit Serial CMOS E<sup>2</sup>PROM internally organized as 256 x 8 bits. Catalyst's advanced CMOS technology substantially reduces device power requirements. The CAT24C02/CAT24C021 features an 8-byte page write buffer and a special write protection feature. The device operates via the I<sup>2</sup>C bus serial interface and is available in 8 pin DIP. 8 pin SO or 14 pin SO packages.

\* Catalyst Semiconductor is licensed by Philips Corporation to carry the I<sup>2</sup>C Bus Protocol.

TD 5020

2

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias55°C to +125°C                                                        |

|---------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                           |

| Voltage on Any Pin with<br>Respect to Ground <sup>(1)</sup> 2.0V to +V <sub>CC</sub> + 2.0V |

| $V_{CC}$ with Respect to Ground–2.0V to +7.0V                                               |

| Package Power Dissipation<br>Capability (Ta = 25°C)1.0W                                     |

| Lead Soldering Temperature (10 secs)                                                        |

| Output Short Circuit Current <sup>(2)</sup> 100mA                                           |

**\*COMMENT**

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

#### **RELIABILITY CHARACTERISTICS**

| Symbol                         | Parameter          | Min.    | Max. | Units       | Reference Test Method         |

|--------------------------------|--------------------|---------|------|-------------|-------------------------------|

| NEND <sup>(3)</sup>            | Endurance          | 100,000 |      | Cycles/Byte | MIL-STD-883, Test Method 1033 |

| T <sub>DR</sub> <sup>(3)</sup> | Data Retention     | 100     |      | Years       | MIL-STD-883, Test Method 1008 |

| Vzap <sup>(3)</sup>            | ESD Susceptibility | 2000    |      | Volts       | MIL-STD-883, Test Method 3015 |

| ILTH <sup>(3)(4)</sup>         | Latch-up           | 100     |      | mA          | JEDEC Standard 17             |

#### D.C. OPERATING CHARACTERISTICS

CAT24C02 T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = +5V ±10%, unless otherwise specified. CAT24C02I T<sub>A</sub> = -40°C to +85°C, V<sub>CC</sub> = +5V ±10%, unless otherwise specified.

|                      |                                        |                       | Limits |                       |       |                                          |

|----------------------|----------------------------------------|-----------------------|--------|-----------------------|-------|------------------------------------------|

| Symbol               | Parameter                              | Min.                  | Тур.   | Max.                  | Units | Test Conditions                          |

| lcc                  | Power Supply Current                   |                       |        | 3                     | mA    | f <sub>SCL</sub> = 100 KHz               |

| I <sub>SB</sub>      | Standby Current V <sub>CC</sub> = 5.5V |                       |        | 4                     | μΑ    | $V_{IN} = GND \text{ or } V_{CC}$        |

| I <sub>SBZ</sub> (5) | Standby Current $V_{CC} = 5.5V$        |                       |        | 0                     | μA    | $V_{IN} = GND \text{ or } V_{CC}$        |

| ILI                  | Input Leakage Current                  |                       |        | 10                    | μA    | V <sub>IN</sub> = GND to V <sub>CC</sub> |

| Ilo                  | Output Leakage Current                 |                       |        | 10                    | μA    | $V_{OUT} = GND$ to $V_{CC}$              |

| VIL                  | Input Low Voltage                      | -1.0                  |        | V <sub>CC</sub> x 0.3 | V     |                                          |

| VIH                  | Input High Voltage                     | V <sub>CC</sub> x 0.7 |        | V <sub>CC</sub> + 0.5 | V     |                                          |

| VoL                  | Output Low Voltage                     |                       |        | 0.4                   | V     | I <sub>OL</sub> = 3 mA                   |

#### **CAPACITANCE** $T_A = 25^{\circ}C$ , f = 1.0 MHz, $V_{CC} = 5V$

| Symbol                          | Test                                | Max. | Units | Conditions           |

|---------------------------------|-------------------------------------|------|-------|----------------------|

| C <sub>I/O</sub> <sup>(3)</sup> | Input/Output Capacitance (SDA)      | 8    | pF    | $V_{I/O} = 0V$       |

| CIN <sup>(3)</sup>              | Input Capacitance (A0, A1, A2, SCL) | 6    | pF    | V <sub>IN</sub> = 0V |

Note:

(1) The minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> +0.5V, which may overshoot to V<sub>CC</sub> + 2.0V for periods of less than 20ns.

(2) Output shorted for no more than one second. No more than one output shorted at a time.

(3) This parameter is tested initially and after a design or process change that affects the parameter.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1V to V<sub>CC</sub> +1V.

(5) Standby Current ( $I_{SBZ}$ ) = 0 $\mu$ A (<900nA) for the CAT24C02Z.

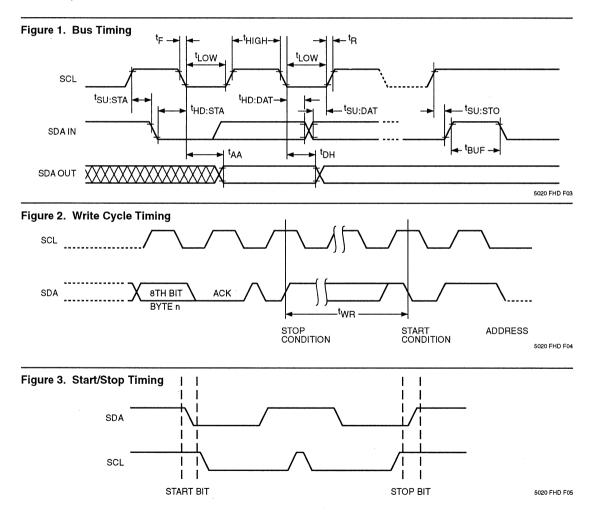

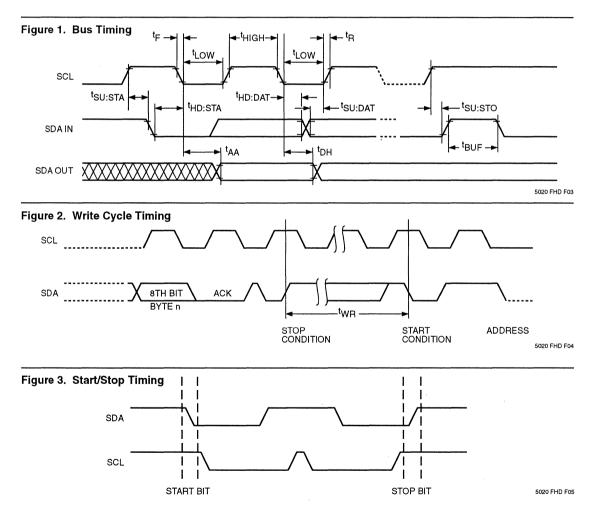

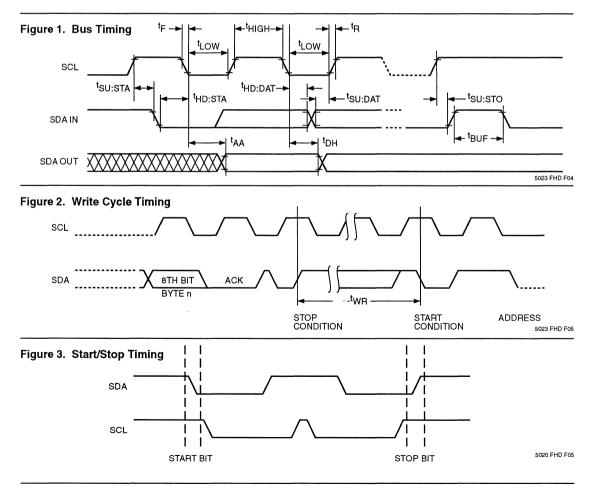

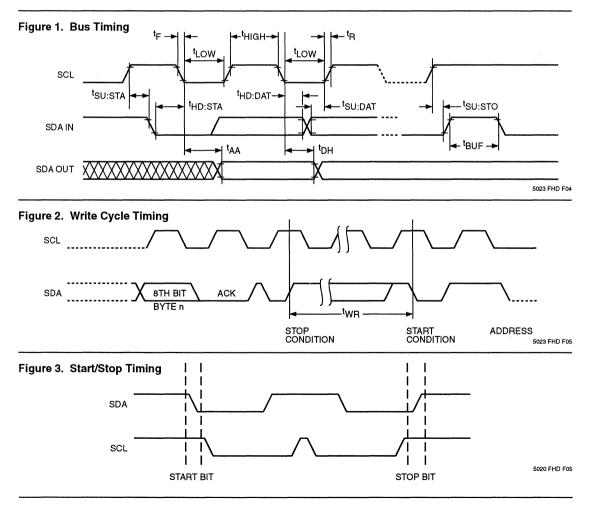

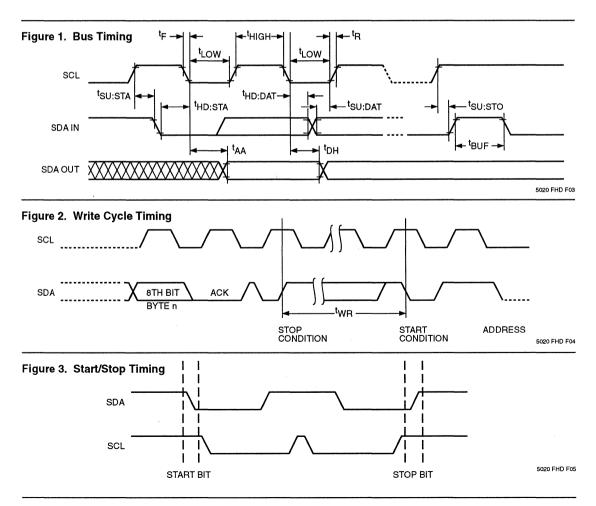

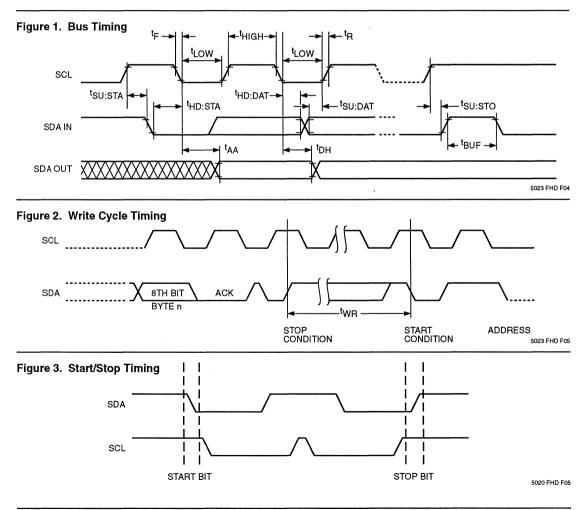

#### A.C. CHARACTERISTICS

CAT24C02 T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = +5V ±10%, unless otherwise specified. CAT24C02I T<sub>A</sub> = -40°C to +85°C, V<sub>CC</sub> = +5V ±10%, unless otherwise specified.

#### **Read & Write Cycle Limits**

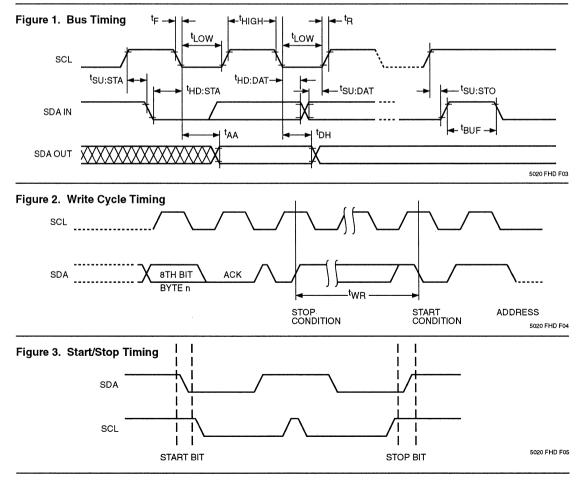

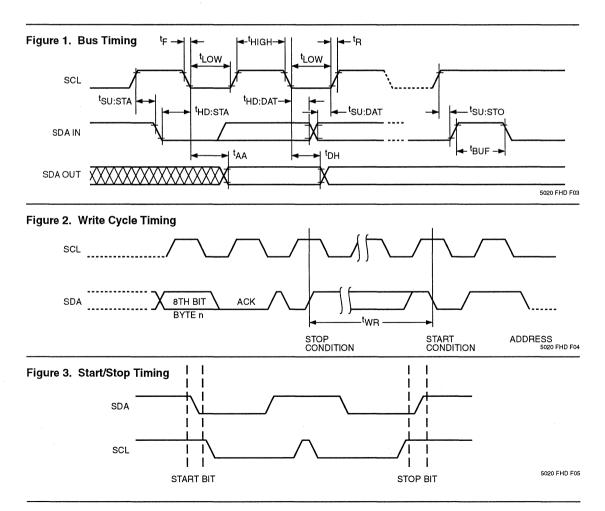

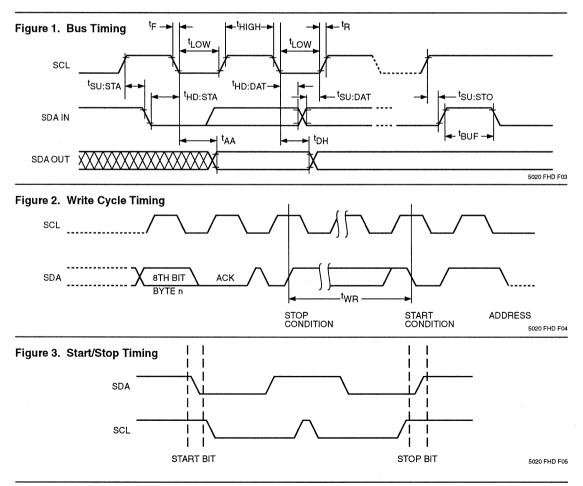

| Symbol                          | Parameter                                                        | Min. | Max | Units |

|---------------------------------|------------------------------------------------------------------|------|-----|-------|

| F <sub>SCL</sub>                | Clock Frequency                                                  |      | 100 | KHz   |

| Tı <sup>(3)</sup>               | Noise Suppression Time<br>Constant at SCL, SDA Inputs            |      | 100 | ns    |

| t <sub>AA</sub>                 | SCL Low to SDA Data Out<br>and ACK Out                           |      | 3.5 | μs    |

| t <sub>BUF</sub> <sup>(3)</sup> | Time the Bus Must be Free Before<br>a New Transmission Can Start | 4.7  |     | μs    |

| thd:sta                         | Start Condition Hold Time                                        | 4.0  |     | μs    |

| tLOW                            | Clock Low Period                                                 | 4.7  |     | μs    |

| thigh                           | Clock High Period                                                | 4.0  |     | μs    |

| tsu:sta                         | Start Condition Setup Time<br>(for a Repeated Start Condition)   | 4.7  |     | μs    |

| thd:dat                         | Data In Hold Time                                                | 0    |     | ns    |

| tsu:dat                         | Data In Setup Time                                               | 250  |     | ns    |

| t <sub>R</sub> <sup>(3)</sup>   | SDA and SCL Rise Time                                            |      | 1   | μs    |

| t <sub>F</sub> <sup>(3)</sup>   | SDA and SCL Fall Time                                            |      | 300 | ns    |

| tsu:sto                         | Stop Condition Setup Time                                        | 4.7  |     | μs    |

| tDH                             | Data Out Hold Time                                               | 300  |     | ns    |

#### Power-Up Timing<sup>(3)(6)</sup>

| Symbol | Parameter                   | Max. | Units |

|--------|-----------------------------|------|-------|

| tpur   | Power-up to Read Operation  | 1 .  | ms    |

| tpuw   | Power-up to Write Operation | 1    | ms    |

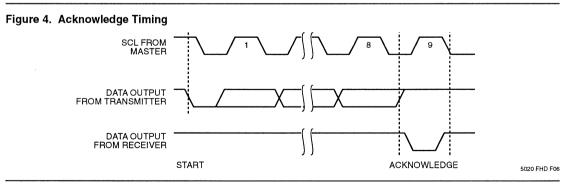

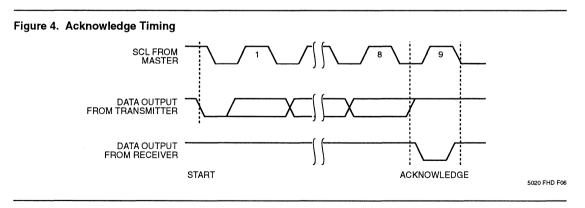

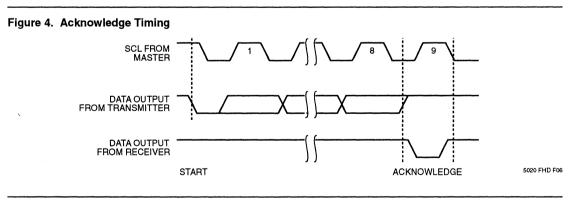

#### Write Cycle Limits

| Symbol | Parameter        | Min. | Тур. | Max | Units |

|--------|------------------|------|------|-----|-------|

| twR    | Write Cycle Time |      |      | 10  | ms    |

The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the bus interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.

Note:

(6) t<sub>PUR</sub> and t<sub>PUW</sub> are the delays required from the time V<sub>CC</sub> is stable until the specified operation can be initiated.

<sup>(3)</sup> This parameter is tested initially and after a design or process change that affects the parameter.

#### FUNCTIONAL DESCRIPTION

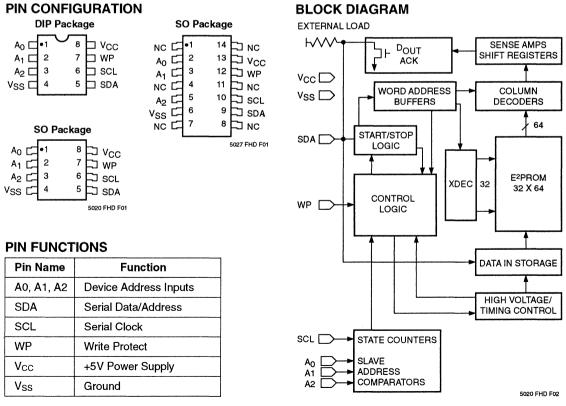

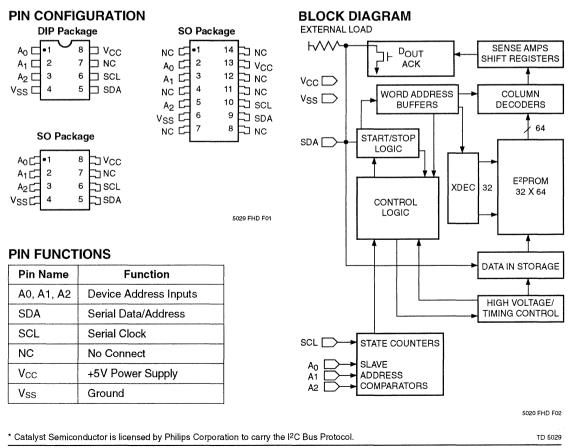

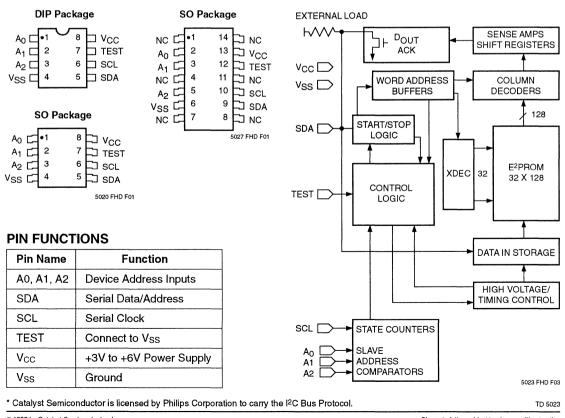

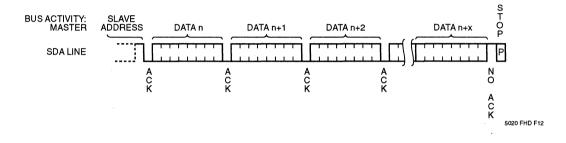

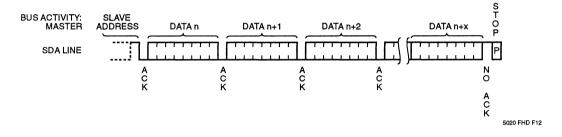

The CAT24C02/CAT24C02I supports the I<sup>2</sup>C Bus data transmission protocol. This Inter-Integrated Circuit Bus protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. The transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The CAT24C02/CAT24C02I operates as a Slave device. Both the Master device and Slave device can operate as either transmitter or receiver, but the Master device controls which mode is activated. A maximum of 8 devices may be connected to the bus as determined by the device address inputs A0, A1, and A2.

#### **PIN DESCRIPTIONS**

#### SCL: Serial Clock

The serial clock input clocks all data transferred into or out of the device.

#### SDA: Serial Data/Address

The bidirectional serial data/address pin is used to transfer all data into and out of the device. The SDA pin is an open drain output and can be wire-ORed with other open drain or open collector outputs.

#### A0, A1, A2: Device Address Inputs

These inputs set the device address within the slave address. They must be connected to either  $V_{SS}$  or  $V_{CC}$ .

#### WP: Write Protect

If the WP pin is tied to  $V_{CC}$  the entire memory array becomes READ only. If the WP pin is tied to  $V_{SS}$  normal read/write operations are allowed to the device. This feature protects the device from inadvertent programming.

#### **I<sup>2</sup>C BUS PROTOCOL**

The following defines the features of the  $I^2C$  bus protocol:

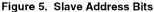

(1) Data transfer may be initiated only when the bus is not busy.

(2) During a data transfer, the data line must remain stable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.

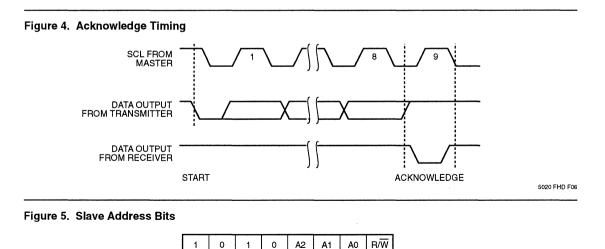

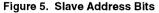

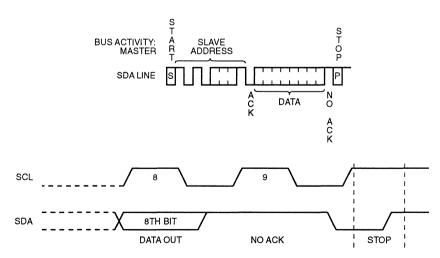

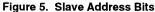

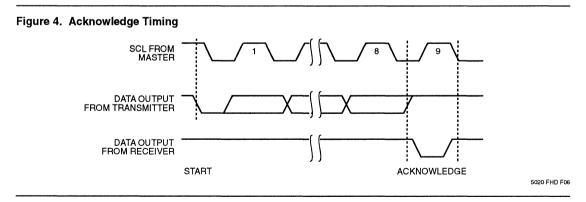

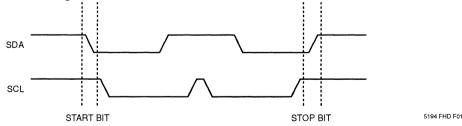

#### START Condition

The START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The CAT24C02/CAT24C02I monitors the SDA and SCL lines and will not respond until this condition is met.

#### **STOP Condition**

A LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.

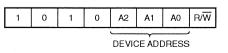

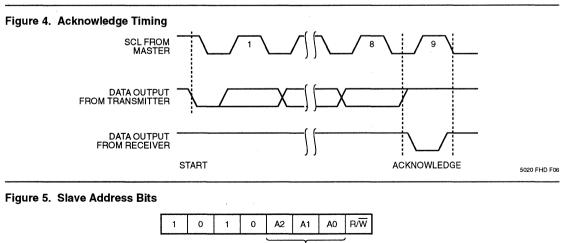

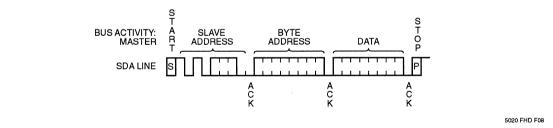

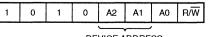

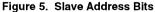

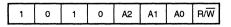

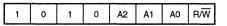

#### DEVICE ADDRESSING

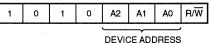

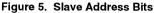

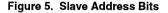

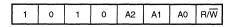

The bus Master begins a transmission by sending a START condition. The Master then sends the address of the particular slave device it is requesting. The four most significant bits of the 8-bit slave address are fixed as 1010 for the CAT24C02/CAT24C02I (see Fig. 5). The next three significant bits (A2, A1, A0) are the device address bits and define which device the Master is

accessing. Up to eight CAT24C02/CAT24C02I devices may be individually addressed by the system. The last bit of the slave address specifies whether a Read or Write operation is to be performed. When this bit is set to 1, a Read operation is selected, and when set to 0, a Write operation is selected.

After the Master sends a START condition, the CAT24C02/CAT24C02I monitors the bus and responds with an acknowledge (on the SDA line) when its address matches the transmitted slave address. The CAT24C02/CAT24C02I then performs a Read or Write operation depending on the state of the R/W bit.

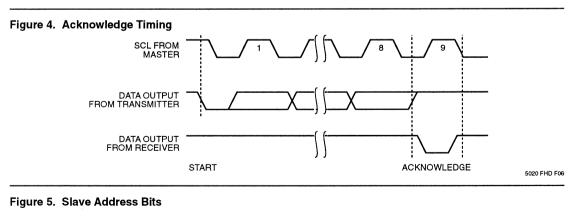

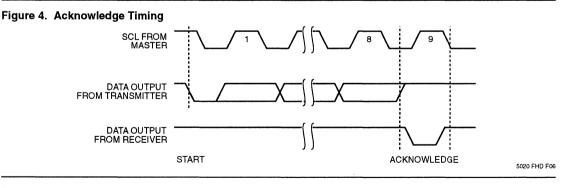

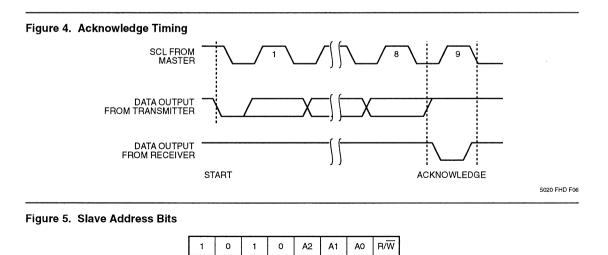

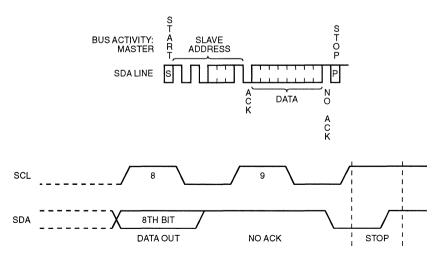

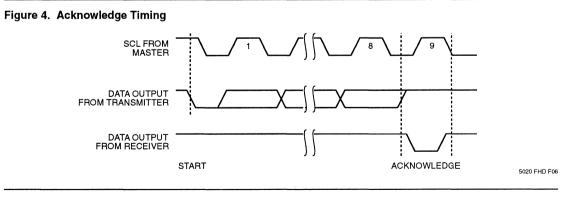

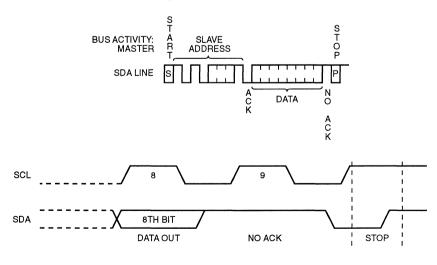

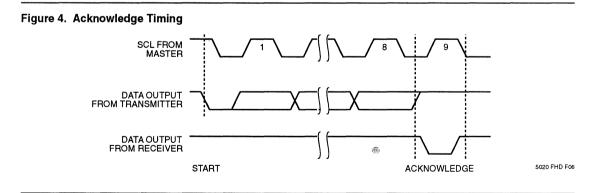

#### Acknowledge

After a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledging device pulls down the SDA line during the ninth clock cycle, signaling that it received the eight bits of data.

The CAT24C02/CAT24C02I responds with an acknowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation, it responds with an acknowledge after receiving each eight bit byte.

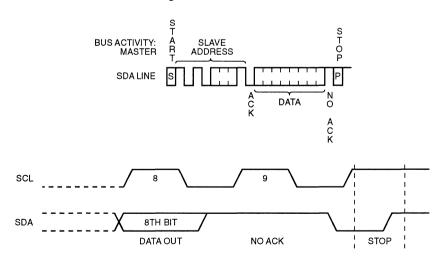

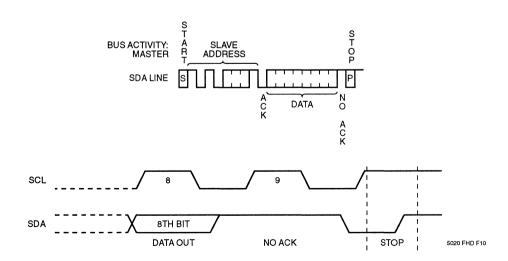

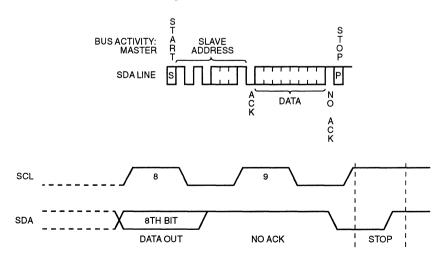

When the CAT24C02/CAT24C02l begins a READ mode it transmits eight bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowledge, the CAT24C02/CAT24C02l will continue to transmit data. If no acknowledge is sent by the Master, the device terminates data transmission and waits for a STOP condition.

5022 FHD F07

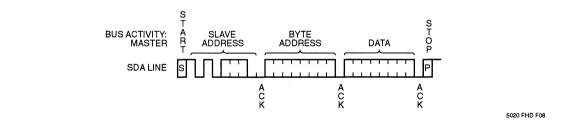

## WRITE OPERATIONS

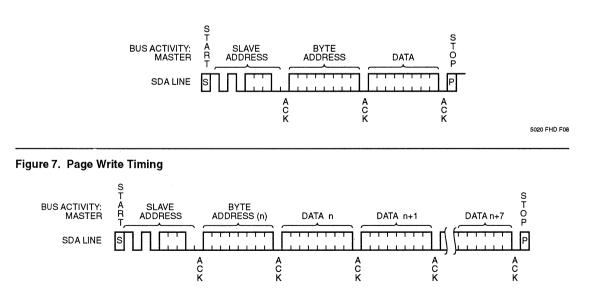

#### Byte Write

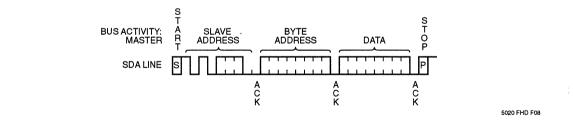

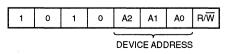

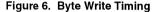

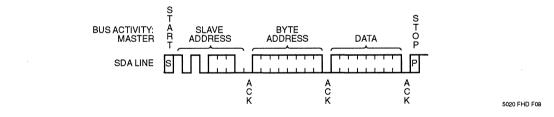

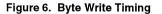

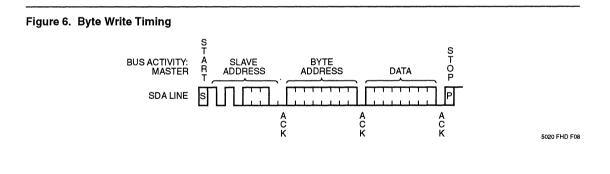

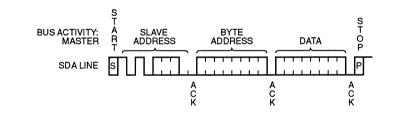

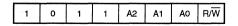

In the Byte Write mode, the Master device sends the START condition and the slave address information (with the R/W bit set to zero) to the Slave device. After the Slave generates an acknowledge, the Master sends the byte address that is to be written into the address pointer of the CAT24C02/CAT24C02I. After receiving another acknowledge from the Slave, the Master device transmits the data byte to be written into the addressed memory location. The CAT24C02/CAT24C02I acknowledges once more and the Master generates the STOP condition, at which time the device begins its internal programming cycle to nonvolatile memory. While this internal cycle is in progress, the device will not respond to any request from the Master device.

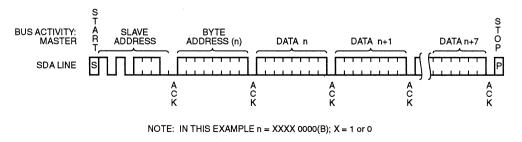

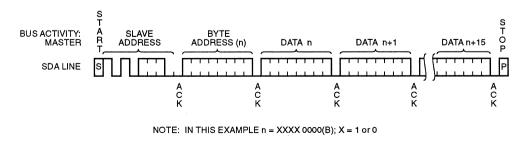

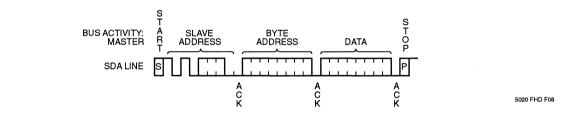

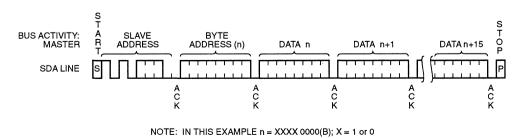

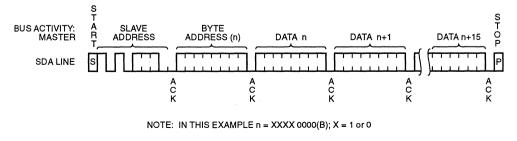

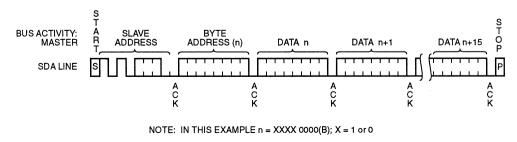

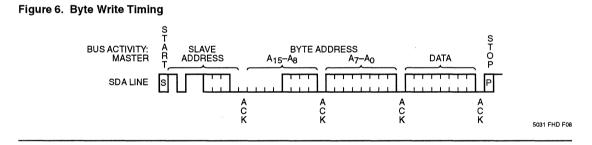

#### Page Write

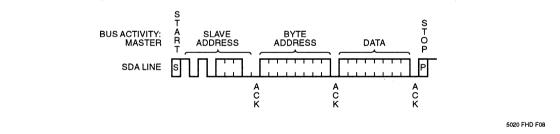

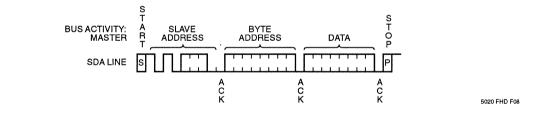

The CAT24C02/CAT24C02l writes up to 8 bytes of data, in a single write cycle, using the Page Write operation. The page write operation is initiated in the same manner as the byte write operation, however instead of terminating after the initial word is transmitted, the Master is allowed to send up to 7 additional bytes. After each byte has been transmitted the CAT24C02/CAT24C02l will respond with an acknowledge, and internally increment the three low order address bits by one. The high order bits remain unchanged.

If the Master transmits more than 8 bytes prior to sending the STOP condition, the address counter 'wraps around', and previously transmitted data will be overwritten.

Once all eight bytes are received and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point all received data is written to the CAT24C02/CAT24C02I in a single write cycle.

#### **Acknowledge Polling**

The disabling of the inputs can be used to take advantage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host's write operation, the CAT24C02/CAT24C02I initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address for a write operation. If the CAT24C02/CAT24C02I is still busy with the write operation, no ACK will be returned. If the CAT24C02/ CAT24C02I has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.

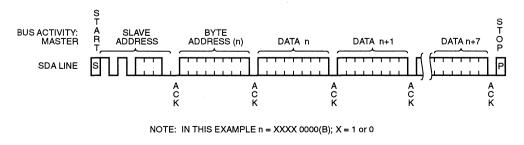

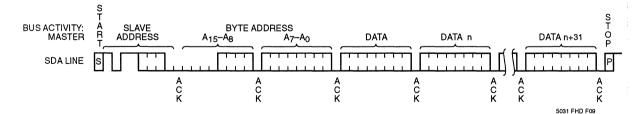

#### Figure 6. Byte Write Timing

#### Figure 7. Page Write Timing

5020 FHD F09

## WRITE PROTECTION

The Write Protection feature allows the user to protect against inadvertent programming of the memory array. If the WP pin is tied to  $V_{CC}$ , the entire memory array is protected and becomes read only. The CAT24C02/CAT24C02I will accept both slave and byte addresses, but the memory location accessed is protected from programming by the device's failure to send an acknowledge after the first byte of data is received.

# **READ OPERATIONS**

The READ operation for the CAT24C02/CAT24C02I is initiated in the same manner as the write operation with the one exception that the R/W bit is set to a one. Three different READ operations are possible: Immediate Address READ, Selective READ and Sequential READ.

#### **Immediate Address Read**

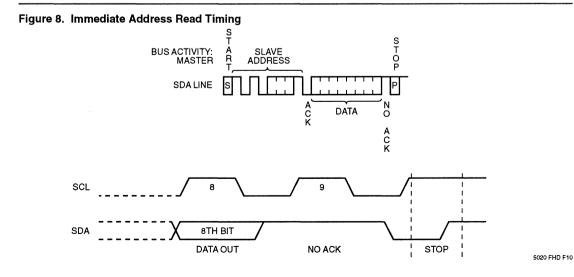

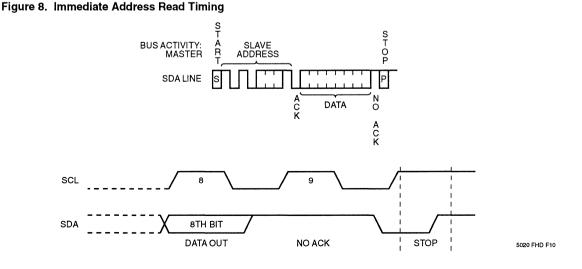

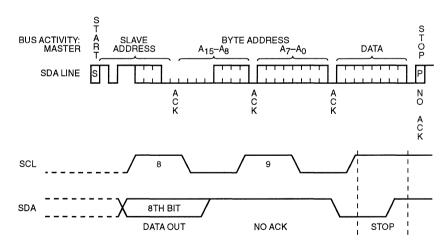

The CAT24C02/CAT24C02I's address counter contains the address of the last byte accessed, incremented by one. In other words, if the last READ or WRITE access was to address N, the READ immediately following would access data from address N+1. If N=255, then the counter will 'wrap around' to address 0 and continue to clock out data. After the CAT24C02/CAT24C02I receives its slave address information (with the R/W bit set to one), it issues an acknowledge, then transmits the eight bit byte requested. The master device does not send an acknowledge but will generate a STOP condition.

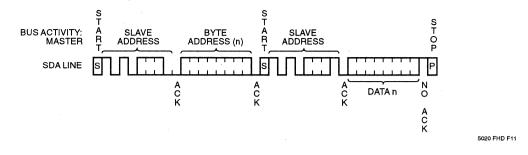

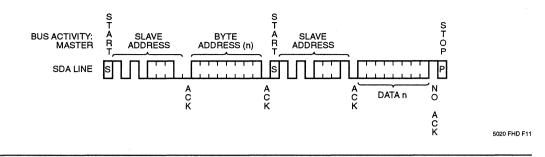

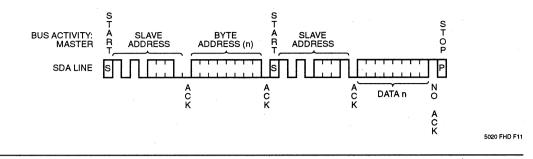

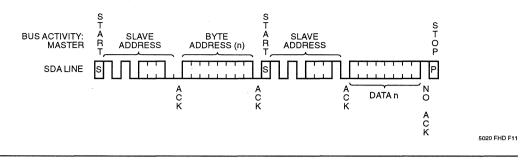

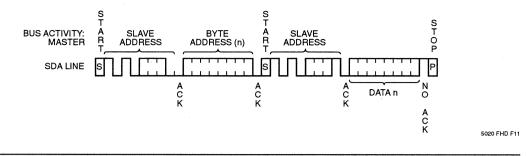

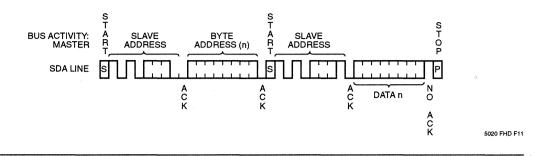

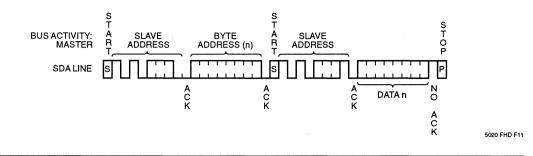

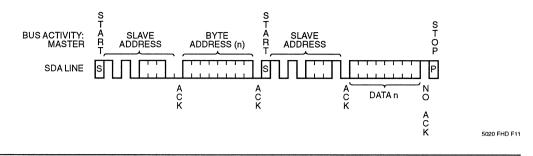

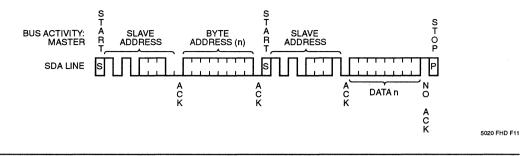

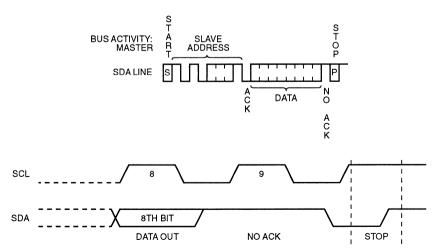

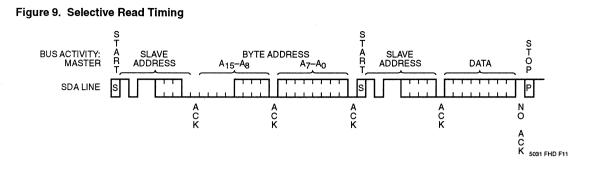

## Selective Read

Selective READ operations allow the Master device to select at random any memory location for a READ operation. The Master device first performs a 'dummy' write operation by sending the START condition, slave address and byte address of the location it wishes to read. After the CAT24C02/CAT24C02I acknowledges the word address, the Master device resends the START condition and the slave address, this time with the R/W bit set to one. The CAT24C02/CAT24C02I then responds with its acknowledge and sends the eight bit byte requested. The master device does not send an acknowledge but will generate a STOP condition.

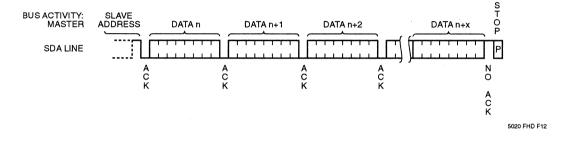

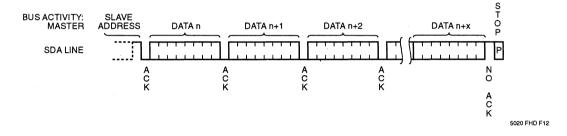

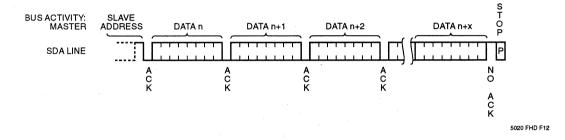

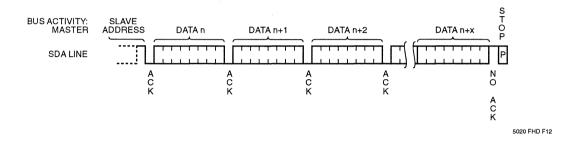

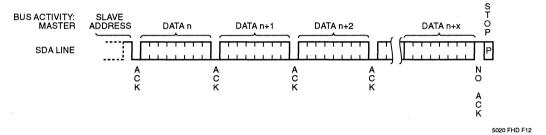

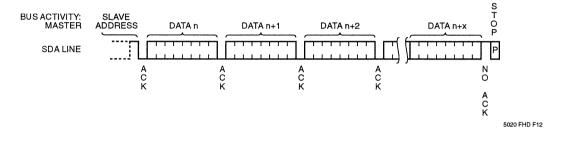

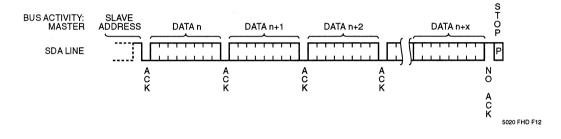

#### Sequential Read

The Sequential READ operation can be initiated by either the Immediate Address READ or Selective READ operations. After the CAT24C02/CAT24C02I sends the initial eight bit byte requested, the Master will respond with an acknowledge which tells the device it requires more data. The CAT24C02/CAT24C02I will continue to output an eight bit byte for each acknowledge sent by the Master. The operation will terminate operation when the Master fails to respond with an acknowledge, thus sending the STOP condition.

The data being transmitted from the CAT24C02/ CAT24C02I is outputted sequentially with data from address N followed by data from address N+1. The READ operation address counter increments all of the CAT24C02/CAT24C02I address bits so that the entire memory array can be read during one operation. If more than the 256 bytes are read out, the counter will "wrap around" and continue to clock out data bytes.

# CAT24C02/CAT24C02I

## Preliminary

## Figure 9. Selective Read Timing

Figure 10. Sequential Read Timing

Preliminary

# CAT24LC02/CAT24LC02I

2K-Bit SERIAL E<sup>2</sup>PROM

# FEATURES

- I<sup>2</sup>C Bus Compatible\*

- Low Power CMOS Technology

- Hardware Write Protect

- 8 Byte Page Write Buffer

- Self-Timed Write Cycle with Auto-Clear

- 100,000 Program/Erase Cycles

- 100 Year Data Retention

- 8 pin DIP, 8 pin SO or 14 pin SO Package

- 3 to 6 Volt Operation

- ZERO Power<sup>™</sup> Version (CAT24LC02Z) Available

- Optional High Endurance Device Available

# DESCRIPTION

The CAT24LC02/CAT24LC02I is a 2K bit Serial CMOS  $E^{2}PROM$  internally organized as 256 x 8 bits. Catalyst's advanced CMOS technology substantially reduces device power requirements. The CAT24LC02/CAT24LC02I

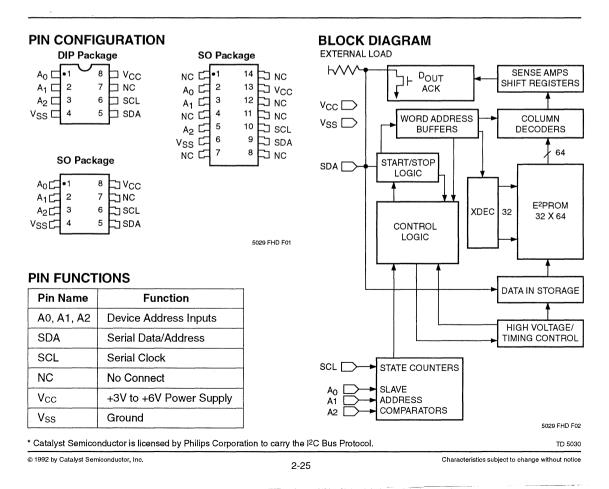

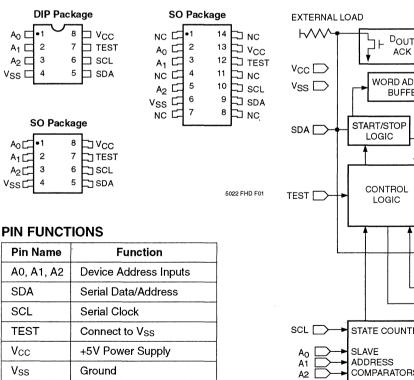

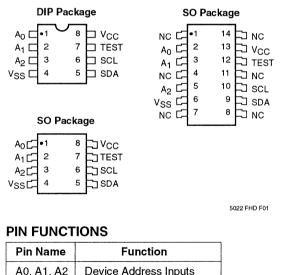

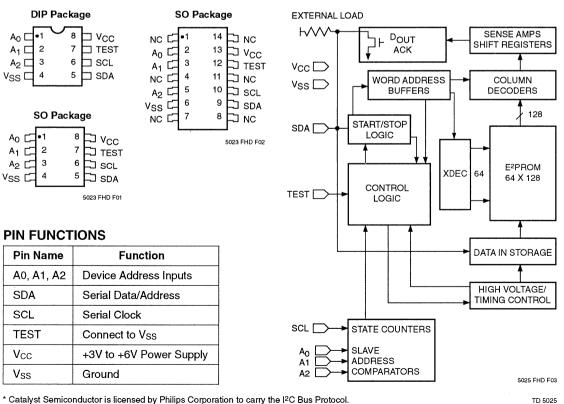

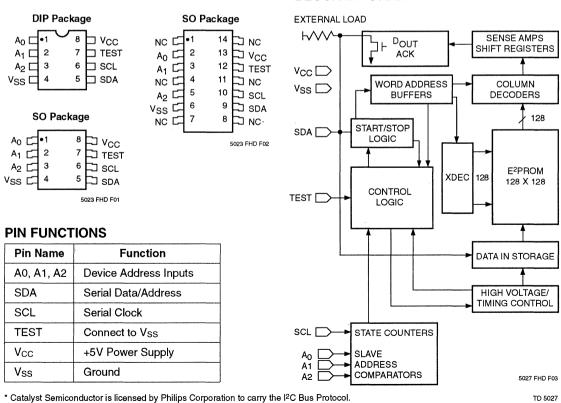

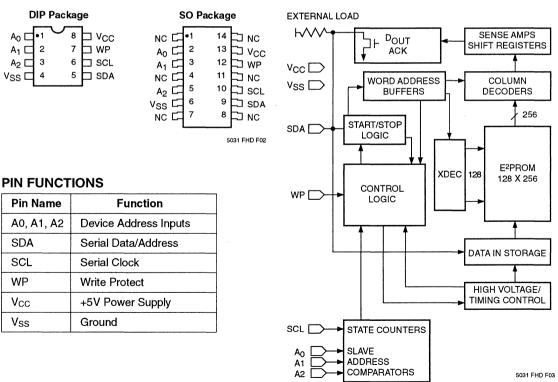

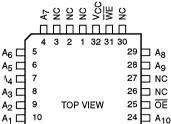

# **PIN CONFIGURATION**

**DIP Package** SO Package A0 -1 •1 8 ⊐ Vcc 14 NC L С ИС A1 🗆 7 2 b wp 2 13 ⊐ v<sub>cc</sub> 占 SCL A2 [ з 6 з 12 C) WP 4 5 ⊐ SDA 4 11 Vss 🗆 NC L Л ИС 5 10 LI SCI A2 [-6 9 v<sub>ss</sub> ⊏ 🗅 SDA 7 8 NC Э NC SO Package •1 8 A<sub>0</sub> JVcc 2 7 - WP 3 6 SCL A2 4 5 SDAC VssE 5021 FHD F01

# **PIN FUNCTIONS**

| Pin Name   | Function                |

|------------|-------------------------|

| A0, A1, A2 | Device Address Inputs   |

| SDA        | Serial Data/Address     |

| SCL        | Serial Clock            |

| WP         | Write Protect           |

| Vcc        | +3V to +6V Power Supply |

| Vss        | Ground                  |

features an 8-byte page write buffer and a special write protection feature. The device operates via the  $l^2C$  bus serial interface and is available in 8 pin DIP, 8 pin SO or 14 pin SO packages.

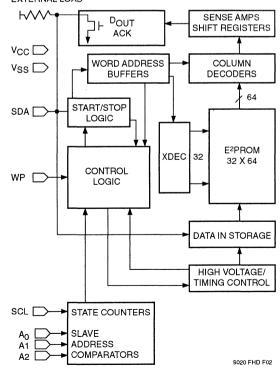

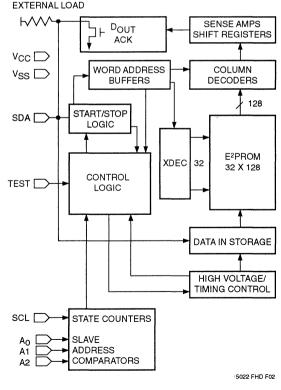

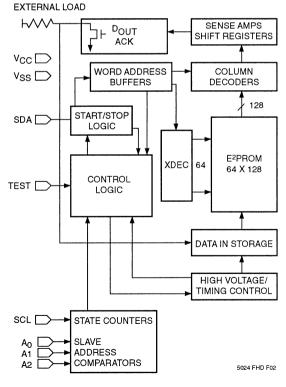

# **BLOCK DIAGRAM**

EXTERNAL LOAD

\* Catalyst Semiconductor is licensed by Philips Corporation to carry the I<sup>2</sup>C Bus Protocol.

2

# **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias55°C to +125°C                                                         |

|----------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                            |

| Voltage on Any Pin with<br>Respect to Ground <sup>(1)</sup> –2.0V to +V <sub>CC</sub> + 2.0V |

| $V_{CC}$ with Respect to Ground–2.0V to +7.0V                                                |

| Package Power Dissipation<br>Capability (Ta = 25°C)1.0W                                      |

| Lead Soldering Temperature (10 secs)                                                         |

| Output Short Circuit Current <sup>(2)</sup>                                                  |

## \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

## **RELIABILITY CHARACTERISTICS**

| Symbol                             | Parameter          | Min.    | Max. | Units       | Reference Test Method         |

|------------------------------------|--------------------|---------|------|-------------|-------------------------------|

| N <sub>END</sub> <sup>(3)</sup>    | Endurance          | 100,000 |      | Cycles/Byte | MIL-STD-883, Test Method 1033 |

| T <sub>DR</sub> <sup>(3)</sup>     | Data Retention     | 100     |      | Years       | MIL-STD-883, Test Method 1008 |

| VZAP <sup>(3)</sup>                | ESD Susceptibility | 2000    |      | Volts       | MIL-STD-883, Test Method 3015 |

| I <sub>LTH</sub> <sup>(3)(4)</sup> | Latch-up           | 100     |      | mA          | JEDEC Standard 17             |

## D.C. OPERATING CHARACTERISTICS

CAT24LC02 T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = +3V to +6V, unless otherwise specified. CAT24LC02I T<sub>A</sub> = -40°C to +85°C, V<sub>CC</sub> = +3V to +6V, unless otherwise specified.

|                     |                                      |                       | Limits |                       |       |                                          |

|---------------------|--------------------------------------|-----------------------|--------|-----------------------|-------|------------------------------------------|

| Symbol              | Parameter                            | Min.                  | Тур.   | Max.                  | Units | Test Conditions                          |

| lcc                 | Power Supply Current                 |                       |        | 3                     | mA    | f <sub>SCL</sub> = 100 KHz               |

| I <sub>SB</sub>     | Standby Current V <sub>CC</sub> = 6V |                       |        | 4                     | μA    | V <sub>IN</sub> = GND or V <sub>CC</sub> |

| Isbz <sup>(5)</sup> | Standby Current V <sub>CC</sub> = 6V |                       |        | 0                     | μA    | $V_{IN} = GND \text{ or } V_{CC}$        |

| ILI                 | Input Leakage Current                |                       |        | 10                    | μA    | $V_{IN} = GND$ to $V_{CC}$               |

| ILO                 | Output Leakage Current               |                       |        | 10                    | μA    | $V_{OUT} = GND$ to $V_{CC}$              |

| VIL                 | Input Low Voltage                    | -1.0                  |        | V <sub>CC</sub> x 0.3 | V     |                                          |

| VIH                 | Input High Voltage                   | V <sub>CC</sub> x 0.7 |        | V <sub>CC</sub> + 0.5 | V     |                                          |

| V <sub>OL</sub>     | Output Low Voltage                   |                       |        | 0.4                   | V     | l <sub>OL</sub> = 3 mA                   |

## **CAPACITANCE** $T_A = 25^{\circ}C$ , f = 1.0 MHz, $V_{CC} = 5V$

| Symbol                          | Test                                | Max. | Units | Conditions     |

|---------------------------------|-------------------------------------|------|-------|----------------|

| C <sub>I/O</sub> <sup>(3)</sup> | Input/Output Capacitance (SDA)      | 8    | pF    | $V_{I/O} = 0V$ |

| C <sub>IN</sub> <sup>(3)</sup>  | Input Capacitance (A0, A1, A2, SCL) | 6    | pF    | $V_{IN} = 0V$  |

Note:

(1) The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> +0.5V, which may overshoot to V<sub>CC</sub> + 2.0V for periods of less than 20ns.

(2) Output shorted for no more than one second. No more than one output shorted at a time.

(3) This parameter is tested initially and after a design or process change that affects the parameter.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1V to V<sub>CC</sub> +1V.

(5) Standby Current ( $I_{SBZ}$ ) = 0µA (<900nA) for the CAT24LC02Z.

## A.C. CHARACTERISTICS

CAT24LC02 T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = +3V to +6V, unless otherwise specified. CAT24LC02I T<sub>A</sub> = -40°C to +85°C, V<sub>CC</sub> = +3V to +6V, unless otherwise specified.

#### Read & Write Cycle Limits

| Symbol                          | Parameter                                                                           | Min. | Max | Units |

|---------------------------------|-------------------------------------------------------------------------------------|------|-----|-------|

| F <sub>SCL</sub>                | Clock Frequency                                                                     |      | 100 | KHz   |

| Tı <sup>(3)</sup>               | T <sub>I</sub> <sup>(3)</sup> Noise Suppression Time<br>Constant at SCL, SDA Inputs |      | 100 | ns    |

| t <sub>AA</sub>                 | AA SCL Low to SDA Data Out<br>and ACK Out                                           |      | 3.5 | μs    |

| t <sub>BUF</sub> <sup>(3)</sup> | Time the Bus Must be Free Before<br>a New Transmission Can Start                    | 4.7  |     | μs    |

| tHD:STA                         | Start Condition Hold Time                                                           | 4.0  |     | μs    |

| tLOW                            | tLOW Clock Low Period                                                               |      |     | μs    |

| thigh                           | Clock High Period                                                                   | 4.0  |     | μs    |

| tsu:sta                         | t <sub>SU:STA</sub> Start Condition Setup Time<br>(for a Repeated Start Condition)  |      |     | μs    |

| tHD:DAT                         | Data In Hold Time                                                                   | 0    |     | ns    |

| tsu:DAT                         | Data In Setup Time                                                                  | 250  |     | ns    |

| t <sub>R</sub> <sup>(3)</sup>   | SDA and SCL Rise Time                                                               |      | 1   | μs    |

| t <sub>F</sub> <sup>(3)</sup>   | t <sub>F</sub> <sup>(3)</sup> SDA and SCL Fall Time                                 |      | 300 | ns    |

| tsu:sto                         | Stop Condition Setup Time                                                           | 4.7  |     | μs    |

| t <sub>DH</sub>                 | Data Out Hold Time                                                                  | 300  |     | ns    |

# Power-Up Timing<sup>(3)(6)</sup>

| Symbol | Parameter                   | Max. | Units |

|--------|-----------------------------|------|-------|

| tpur   | Power-up to Read Operation  | 1    | ms    |

| tPUW   | Power-up to Write Operation | 1    | ms    |

#### Write Cycle Limits

| Symbol          | Parameter        | Min. | Тур. | Max | Units |

|-----------------|------------------|------|------|-----|-------|

| t <sub>WR</sub> | Write Cycle Time |      |      | 10  | ms    |

The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the bus interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.

Note:

<sup>(3)</sup> This parameter is tested initially and after a design or process change that affects the parameter.

<sup>(6)</sup> t<sub>PUR</sub> and t<sub>PUW</sub> are the delays required from the time V<sub>CC</sub> is stable until the specified operation can be initiated.

# FUNCTIONAL DESCRIPTION

The CAT24LC02/CAT24LC02I supports the I<sup>2</sup>C Bus data transmission protocol. This Inter-Integrated Circuit Bus protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. The transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The CAT24LC02/CAT24LC02I operates as a Slave device. Both the Master device and Slave device can operate as either transmitter or receiver, but the Master device controls which mode is activated. A maximum of 8 devices may be connected to the bus as determined by the device address inputs A0, A1, and A2.

# **PIN DESCRIPTIONS**

#### SCL: Serial Clock

The serial clock input clocks all data transferred into or out of the device.

#### SDA: Serial Data/Address

The bidirectional serial data/address pin is used to transfer all data into and out of the device. The SDA pin is an open drain output and can be wire-ORed with other open drain or open collector outputs.

#### A0, A1, A2: Device Address Inputs

These inputs set the device address within the slave address. They must be connected to either  $V_{SS}$  or  $V_{CC}$ .

#### WP: Write Protect

If the WP pin is tied to  $V_{CC}$  the entire memory array becomes READ only. If the WP pin is tied to  $V_{SS}$  normal read/write operations are allowed to the device. This feature protects the device from inadvertent programming.

# I<sup>2</sup>C BUS PROTOCOL

The following defines the features of the  $l^2C$  bus protocol:

(1) Data transfer may be initiated only when the bus is not busy.

(2) During a data transfer, the data line must remain stable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.

#### **START Condition**

The START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The CAT24LC02/CAT24LC02I monitors the SDA and SCL lines and will not respond until this condition is met.

## **STOP Condition**

A LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.

# **DEVICE ADDRESSING**