# VHDL Development System User's Guide

Cypress Semiconductor 3901 North First Street San Jose, CA 95134 (408) 943-2600 April 1996 The following are trademarks or registered trademarks of Cypress Semiconductor Corporation: Warp, .Warp2, Warp3, Nova, Galaxy, Flash370, UltraLogic, Impuise3, UltraGen, pASIC380, ISR, MAX340.

The following are trademarks or registered trademarks of Viewlogic Systems: Powerview, Workview, Workview PLUS, ViewDraw, ViewSim, ViewTrace, ViewText, Cockpit, VCS.

The following are trademarks or registered trademarks of Microsoft Corporation: Microsoft, Windows, Windows 3.1, Windows 3.1, Windows NT, Windows 95.

The following are trademarks or registered trademarks of QuickLogic Corporation: SpDE, pASIC.

The following is a registered trademark of Intel Corporation: Pentium.

The following is a trademark of Hewlett Packard Corporation: HP-UX.

The following are trademarks of Mentor Graphics Corporation: QuickHDL, V-System.

The following is a trademark of Veribest, Inc.: Veribest.

The following is a registered trademark of AT&T: UNIX.

The following are trademarks or registered trademarks of Synopsys, Inc.: Synopsys, Design Compiler, VSS.

The following are trademarks or registered trademarks of Cadence Design Systems Inc.: Verilog, Leapfrog, Verilog-XL.

The following are trademarks or registered trademarks of Sun Microsystems, Inc.: Sun SparcStation, SunOS, Solaris.

The following is a registered trademark of Open Software Foundation: Motif.

Cypress Semiconductor Corporation may revise this publication from time to time without notice. Some states or jurisdictions do not allow disclaimer of express or implied warranties in certain transactions; therefore, this statement may not apply to you.

All other brand or product names are trademarks or registered trademarks of their respective companies or organizations.

Copyright © 1996 Cypress Semiconductor Corporation. All rights reserved.

# **Cypress Software License Agreement**

LICENSE. Cypress Semiconductor Corporation ("Cypress") hereby grants you, as a Customer and Licensee, a single-user, non-exclusive license to use the enclosed Cypress software program ("Program") on a single CPU at any given point in time. Cypress authorizes you to make archival copies of the software for the sole purpose of backing up your software and protecting your investment from loss.

**TERM AND TERMINATION.** This Agreement is effective from the date the diskettes are received until this Agreement is terminated. The unauthorized reproduction or use of the Program and/or documentation will immediately terminate this Agreement without notice. Upon termination you are to destroy both the Program and the documentation.

**COPYRIGHT AND PROPRIETARY RIGHTS**. The Program and documentation are protected by both United States Copyright Law and International Treaty provisions. This means that you must treat the documentation and Program just like a book, with the exception of making archival copies for the sole purpose of protecting your investment from loss. The Program may be used by any number of people, and may be moved from one computer to another, so long as there is **No Possibility** of its being used by two people at the same time.

DISCLAIMER. THIS PROGRAM AND DOCUMENTATION ARE LICENSED "AS-IS," WITHOUT WARRANTY AS TO PERFORMANCE. CYPRESS EXPRESSLY DISCLAIMS ALL WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS OF THIS PROGRAM FOR A PARTICULAR PURPOSE.

**LIMITED WARRANTY**. The diskette on which this Program is recorded is guaranteed for 90 days from date of purchase. If a defect occurs within 90 days, contact the representative at the place of purchase to arrange for a replacement.

**RESELLING.** The reselling or distribution of this product can be done by Cypress authorized distributors only.

**BENCHMARKING.** This license Agreement does not convey to you the right to publish performance benchmarking results involving any Cypress *Warp* products. Permission to publish performance benchmarking results involving any Cypress *Warp* products must be received in writing from Cypress Semiconductor prior to publishing.

LIMITATION OF REMEDIES AND LIABILITY. IN NO EVENT SHALL CYPRESS BE LIABLE FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM PROGRAM USE, EVEN IF CYPRESS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. CYPRESS'S EXCLUSIVE LIABILITY AND YOUR EXCLUSIVE REMEDY WILL BE IN THE REPLACEMENT OF ANY DEFECTIVE DISKETTE AS PROVIDED ABOVE. IN NO EVENT SHALL CYPRESS'S LIABILITY HEREUNDER EXCEED THE PURCHASE PRICE OF THE SOFTWARE.

**ENTIRE AGREEMENT**. This Agreement constitutes the sole and complete Agreement between Cypress and the Customer for use of the Program and documentation. Changes to this Agreement may be made only by written mutual consent.

**GOVERNING LAW**. This Agreement shall be governed by the laws of the State of California. Should you have any question concerning this Agreement, please contact:

Cypress Semiconductor Corporation Attn: Legal Counsel 3901 N. First Street San Jose, CA 95134-1599

408-943-2600

# Contents

Warp User's Guide

#### Contents

| Chapter 1    | Installation                            |     |

|--------------|-----------------------------------------|-----|

| PC Installat | tion                                    | 1   |

|              | laris/HP Installation                   |     |

| 50100/000    |                                         |     |

| Chapter 2    | Overview                                | 15  |

| Chapter 3    | Tutorials                               | 21  |

| Introduction | n                                       | 22  |

| Designing a  | a Soda Machine                          | 27  |

| Starting Wa  | arp                                     |     |

| Creating A   | New Project                             |     |

| Creating the | e VHDL File                             | 32  |

| Verifying th | ne VHDL Syntax                          | 38  |

| Creating a   | Top-Level Description                   | 40  |

| Compiling a  | and Synthesizing a Top-Level File       | 43  |

| Simulating   | the Behavior of the Design with Nova    | 49  |

| Retargeting  | g the Design to an FPGA                 | 58  |

| Back-Annot   | tating Pin Assignment Information       | 66  |

| Simulating   | the Behavior of the Design with ViewSim | 67  |

| Designing a  | a Parking Garage Monitor                | 70  |

| Starting Ga  | alaxy                                   | 72  |

| Creating a   | Project                                 | 73  |

| Writing the  | VHDL File                               | 74  |

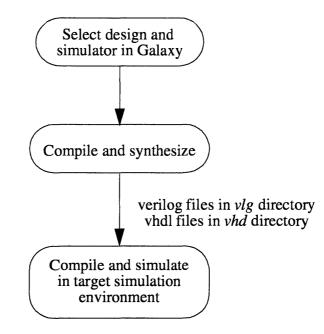

| Compiling a  | and Synthesizing the Design             | 88  |

| Simulating   | the Behavior of the Design with Nova    | 92  |

| Back-Annot   | tating Pin Assignment Information       | 105 |

| Simulating   | the Behavior of the Design with ViewSim | 106 |

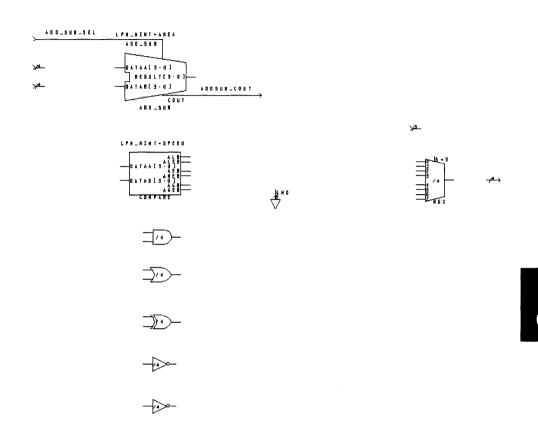

| Designing a  | an ALU Circuit                          | 110 |

| Starting Wa  | arp3                                    | 110 |

| Creating a   | Project                                 | 111 |

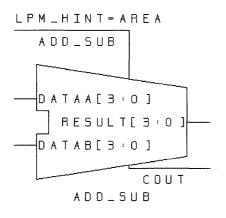

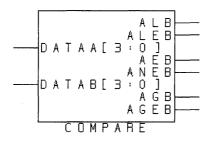

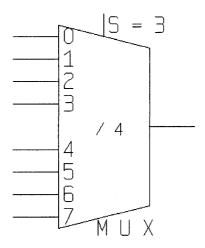

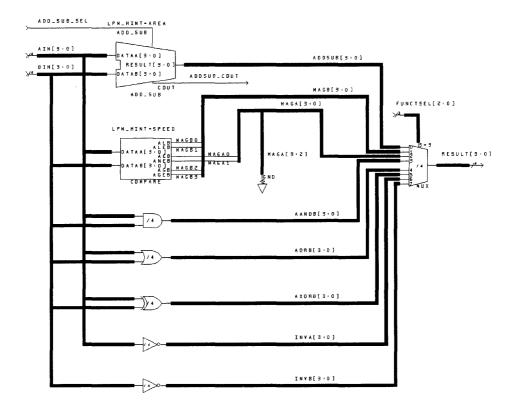

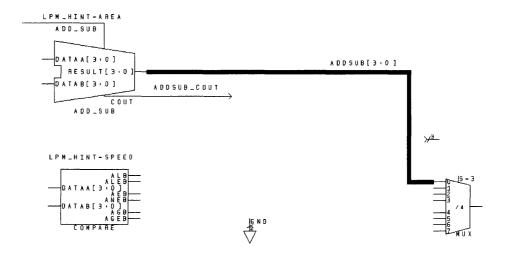

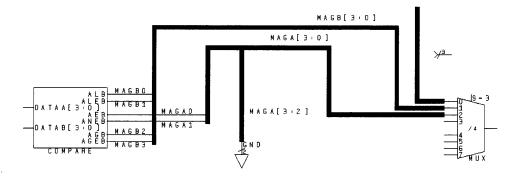

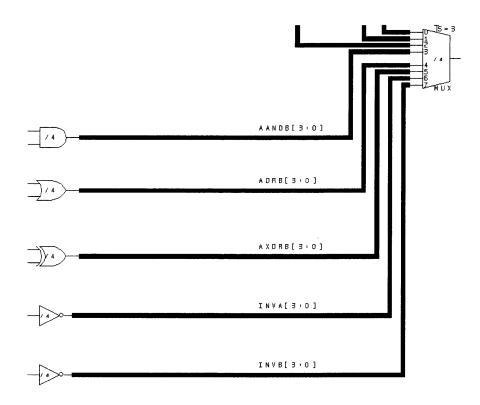

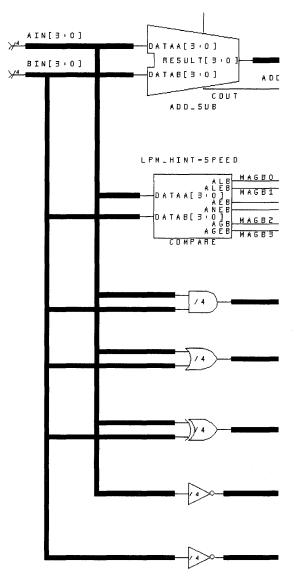

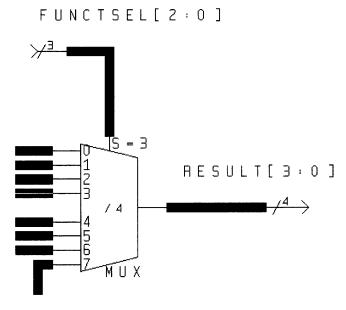

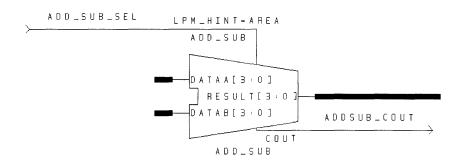

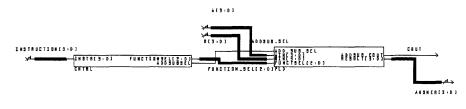

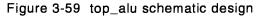

| Creating the | e Schematic                             | 112 |

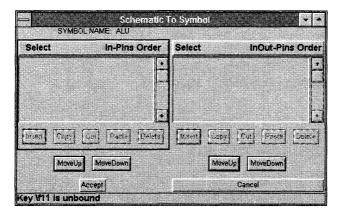

| Generating   | a Symbol from the Schematic             | 143 |

| Writing the  | VHDL File                               | 143 |

| Verifying the VHDL File                            | 148 |

|----------------------------------------------------|-----|

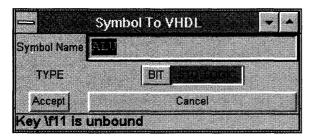

| Generating a Symbol for the VHDL File              | 149 |

| Creating a Top-Level Schematic                     | 150 |

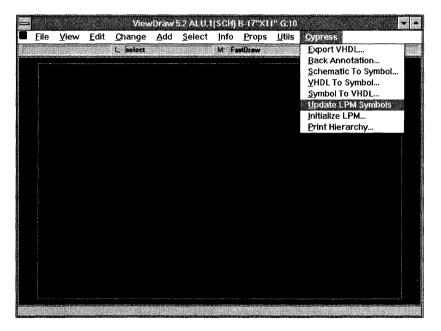

| Exporting the Top-Level Schematic                  | 158 |

| Compiling and Synthesizing the Top-Level Schematic | 159 |

| Placing and Routing the Design                     | 159 |

| Simulating the Behavior of the Design with ViewSim | 162 |

| Back-Annotating Pin Assignments                    | 167 |

| Conclusion                                         | 167 |

| Chapter 4  | Galaxy     | <br>69 |

|------------|------------|--------|

| Overview   |            | <br>70 |

| Starting G | alaxy      | <br>71 |

| Project Ma | anagement  | <br>71 |

| Targeting  | a Device   | <br>77 |

| Generic O  | ptions     | <br>84 |

| Compiling  | a Design . | <br>87 |

| Library Ma | nagement   | <br>89 |

| Integrated | Editor     | <br>91 |

| Simulation |            | <br>94 |

| Back-Anno  | otation    | <br>94 |

|            |            |        |

| Chapter 5  | SpDE                                        |  |

|------------|---------------------------------------------|--|

| Introducti | on                                          |  |

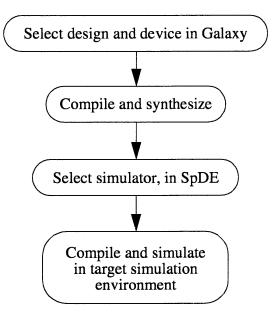

| SpDE De    | sign Flow                                   |  |

| SpDE Gra   | aphical Interface: The SpDE Window          |  |

| SpDE De    | sign Tools                                  |  |

| SpDE An    | alysis Tools                                |  |

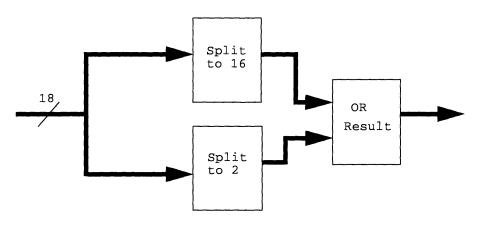

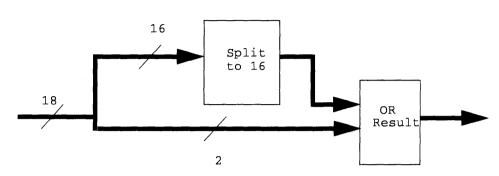

| Design C   | onsiderations: Speeding Up High-Fanout Nets |  |

| Chapter 6      | Nova.    |                           |  |

|----------------|----------|---------------------------|--|

| -<br>1-1 1 - 1 |          |                           |  |

|                |          |                           |  |

| Starting No    | va       |                           |  |

| The Nova V     | Vindow   |                           |  |

| The File Me    | enu      |                           |  |

| The Edit Me    | enu      |                           |  |

| The Simula     | te Menu  |                           |  |

| The Views      | Menu     |                           |  |

| The Option     | s Menu   |                           |  |

| Nova JEDE      | C Simula | tor Quick Reference Sheet |  |

| Creating Bu    | uses     |                           |  |

| Miscellaneo    | ous      |                           |  |

| Chapter 7     | Schematic Entry                 |     |

|---------------|---------------------------------|-----|

| Overview      |                                 |     |

| LPM Library   |                                 |     |

| Exporting th  | e Schematic                     |     |

| Back-Annota   | ation                           |     |

| Using the So  | chematic Libraries from Release | 3.5 |

| Schematic to  | o Symbol                        |     |

| VHDL To Sy    | /mbol                           |     |

| Symbol to V   | 'HDL                            |     |

| Update Libra  | ary                             |     |

| Print Hierard | chy                             |     |

| Chapter 8    | Simulation                                      |     |

|--------------|-------------------------------------------------|-----|

| Introduction | n                                               |     |

| Pre-synthe   | sis Simulation                                  |     |

| Post-synth   | esis Simulation Design Flow for PLDs and CPLDs  | 301 |

| Post-synth   | esis Simulation Design Flow for FPGAs           | 305 |

| Post-synth   | esis VHDL Simulation in ModeIT Environment      | 307 |

| Post-synth   | esis Verilog Simulation In VeriBest Environment |     |

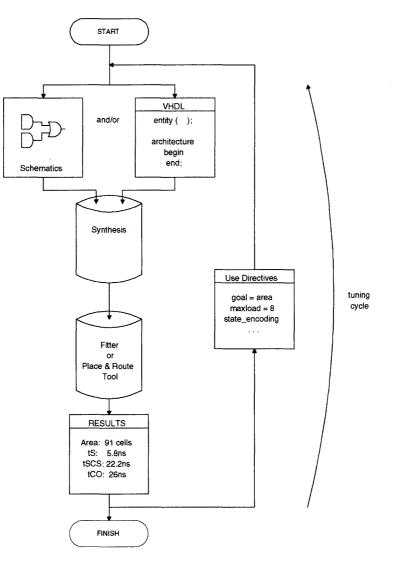

| Chapter 9  | Synthesis                         |  |

|------------|-----------------------------------|--|

| Synthesis  | s Directives                      |  |

| Example    | 1-DRAM Controller                 |  |

| Example    | 2Multiply and Accumulate Function |  |

| Area Opti  | mization                          |  |

| Specific C | Control                           |  |

| Speed Op   | otimization                       |  |

| Documen    | Itation Directives                |  |

| Directive  | Format Summary                    |  |

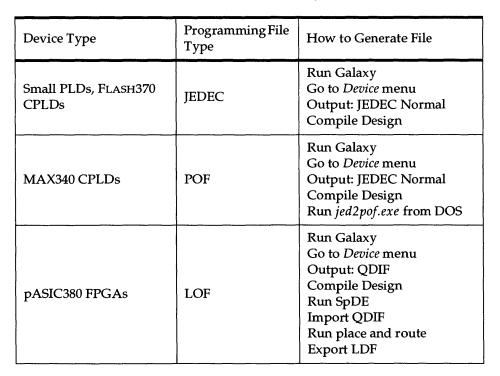

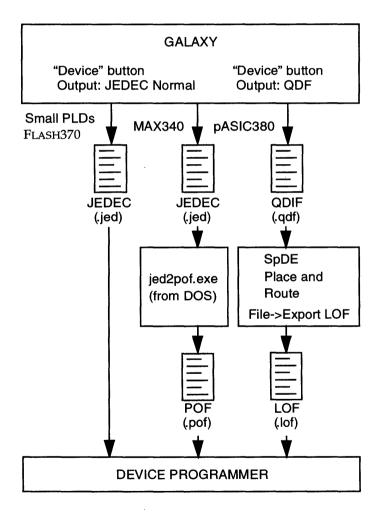

| Chapter 10 | Device Programming             |  |

|------------|--------------------------------|--|

| Generating | g a JEDEC File                 |  |

| Generating | g POF Files for MAX340 CPLDs   |  |

| Generating | g LOF Files for pASIC380 FPGAs |  |

| Device Pro | ogrammers                      |  |

# Installation

# 1

# **PC Installation**

To install  $Warp^{TM}$ , insert the CD-ROM and using the File Manager in Windows<sup>TM</sup>, locate *pc\setup.exe* on the CD-ROM. Double click your left mouse button on this file. Cypress recommends that you close all your applications (except for the File Manager and the Program Manager) before running the *Warp* installation program. *Warp* Release 4.0 is a major release and should not be installed on a previous version of *Warp*. Cypress recommends installing *Warp* Release 4.0 in a new directory. If you have deleted a version of *Warp* (for *Warp3<sup>TM</sup>* customers), entering Windows after doing so might give you some messages about missing device files: this is harmless. You will have to edit the *c:\windows\system.ini* file manually to remove these devices from the file.

Warp is a 32-bit program and requires that Microsoft's® Win32s subsystem be loaded for Windows 3.1<sup>TM</sup> or Windows 3.11<sup>TM</sup>. This is not required for Windows 95<sup>TM</sup> or Windows NT<sup>TM</sup>. The first part of the Windows installation routine will check for the existence of Win32s and offer to install it for you.

For previous *Warp3* customers, Viewlogic tools required BIGWIN in order to run. The current Viewlogic tools shipped with *Warp* no longer require this. The *Warp* installation program does not automatically remove this device from your *system.ini* file because you may have other applications that might require BIGWIN. To remove BIGWIN, you must edit the *system.ini* file in your Windows directory manually.

The following are the approximate disk space requirements for the various *Warp* products:

- 1. Warp2 60Mbytes

- 2. *Warp3* 110Mbytes (150 with on-line Documentation)

You may also need extra disk space for your designs.

Cypress also recommends that you run *Warp* on at least a 486-66 or a Pentium<sup>®</sup>, with at least 16MB of RAM and an additional 16MB of virtual memory.

The Warp2<sup>™</sup> product is also capable of integrating itself with the Viewlogic WorkView<sup>®</sup> PLUS environment if you already have this. Warp2 has been tested with WorkView PLUS<sup>®</sup> version 5.2.

#### Warp On-line Documents

*Warp* documentation is available on-line and it can be viewed using the **Adobe Acrobat Reader**, shipped with the CD-ROM. To install the Acrobat Reader, insert the CD-ROM and using the File Manager in Windows, locate \pc\acroread\disk1\setup.exe and double-click your left mouse button on this file. These files can also be installed into the c:\warp\docs directory during installation.

#### PLD Data Book

The Cypress *Programmable Logic Data Book* is also available on-line. It can be viewed using the **Acrobat Reader**, shipped with the CD-ROM. To access the databook, insert the CD-ROM and use the File Manager in Windows to locate the \*doc*\*databook* directory.

#### PC License Issues for Viewlogic Tools (Warp3 Customers)

PC Warp3 customers require a hardware key as well as a license file in order to use the software. This key and license file are used solely for the Viewlogic tools within the Warp3 environment. To obtain a license file for your Warp3 software, please fill out the registration form that was included with your Warp3 software kit, and fax it to the number shown on the form. The HOSTID is specified on the key itself and the license file is generated based on that number. You will receive your license file within 24 hours of Cypress receiving the registration form.

# PC - Known Installation Problems

**Problem**: *Warp* installation sometimes aborts, giving a "Divide by 0" error.

**Solution**: Please try installing *Warp* again. This problem will be fixed in the next update and involves the calculation of free disk space. Installing a second time changes the free disk space situation and thus avoids the error.

**Problem**: *Warp* installation does not work, or Viewlogic tools do not work properly.

**Solution**: Some newer PCs with SCSI drives must run SMARTDRIVE. Without this, some 32-bit applications have trouble accessing the disk. To avoid this problem, please make sure that you are running SMARTDRIVE. The following command in your *autoexec.bat* or *config.sys* is recommended:

#### c:\windows\smartdrive.exe /double\_buffer

Running SMARTDRIVE even on non-SCSI machines is also a good idea, since it improves the performance of your computer.

Problem: Windows fails to come up after Warp installation.

**Solution**: Rare as this is, some configurations of Windows do this. To solve this problem, please check your *c:\windows\system.ini* file for any duplicate device drivers. If any are found, please remove the duplication, leaving only one instance of each device driver.

**Problem**: *Warp* fails to install.

**Solution**: Certain power management tools and screen savers might conflict with the installation program. Temporarily disable the screen saver during installation. If *power.exe* is being run from your *autoexec.bat* or *config.sys*, please disable this.

# **Commonly Asked Questions About PC Installation**

What is BIGWIN, and why do I no longer need it?

Windows is essentially a 16-bit environment. The previous version of Viewlogic (5.1) used a Windows extender called BIGWIN to allow 32-bit access. All Viewlogic tools which formerly used BIGWIN have now been ported to use Microsoft's recommended extender, Win32s.

Do I need to change any settings in my config.sys?

Please check the settings for FILES and BUFFERS. Cypress recommends a setting of 60 for FILES and 15 for BUFFERS.

Which mice are supported?

For *Warp2* customers, a generic 2-button mouse will suffice. However, if you have configured *Warp2* to run with Viewlogic or if you are a *Warp3* customer, Cypress recommends a 3-button mouse. Although a 2-button mouse will work, many of the WorkView PLUS functions require a middle mouse button. A 2-button mouse can be made to emulate a 3-button mouse within the Viewlogic tools by using the F2, F3, F4 function keys for the left, middle and the right mouse buttons, but the user must first click the left mouse button to use these function keys. For example, to emulate the middle button, you have to single-click the left mouse button of your 2-button mouse and then press F3.

Which files are modified by the Warp installation?

The files *autoexec.bat*, *c*:\*windows*\*win.ini* and *c*:\*windows*\*system.ini* are always modified. A detailed description of the exact changes that are made to these files is listed in the file *warppc.txt* (available at the end of the installation or with the Release Notes icon within the *Warp R4* program group). The changes vary depending upon the product that you have installed.

# SunOS/Solaris/HP Installation

The following steps show how to install *Warp* Release 4 on a SUN Sparc station running SunOS<sup>™</sup> 4.1.x/Solaris<sup>™</sup> 2.5 or on an HP 9000 (700 series) workstation running HP-UX<sup>™</sup> 9.05. The following are the disk space requirements depending on the product you have purchased:

- 1. Warp2 60Mbytes

- 2. *Warp3* 160Mbytes (260 with on-line Documentation)

*Warp* Release 4.0 is a major release and should not be installed over a previous version of *Warp*. Cypress recommends installing *Warp* Release 4.0 in a new directory.

The *Warp2* product is also capable of integrating itself with the Viewlogic Powerview<sup>®</sup> environment if you already have this. *Warp2* has been tested with Powerview version 5.3.2.

*Warp* documentation is available on-line and can be viewed using the **Adobe Acrobat Reader**, shipped with the CD-ROM. The Acrobat reader can be installed during *Warp* installation or separately after completing *Warp* installation.

## **PLD Data Book**

The Cypress *Programmable Logic Data Book* is available on-line. It can be viewed using the **Acrobat Reader**, shipped with the CD-ROM. To access the data book, mount the CD-ROM on */cdrom* and view the databook located in the directory */cdrom/doc/databook*. Refer to the following steps to mount the CD-ROM.

#### Step 1: Mount the CD-ROM

#### On SunOS 4.1.x

Login as super user on a machine that has a CD-ROM drive. Run the following commands to create and mount the */cdrom* directory.

```

mkdir /cdrom

mount -rt hsfs /dev/sr0 /cdrom

```

#### **On Solaris 2.5**

If the Volume Manager is running, it will automatically mount the CD-ROM. Otherwise, login as super user on a machine that has a CD-ROM drive. Run the following commands to create and mount the */cdrom* directory:

```

mkdir /cdrom

mount -F ufs -r /dev/dsk/c0t6d0s2 /cdrom

```

#### **On HP-UX 9.05**

Login as super user on a machine that has a CD-ROM drive. Run the following commands to create and mount the */cdrom* directory:

```

mkdir /cdrom

mount -o ro /dev/dsk/c201d3s0 /cdrom

```

In the above procedure, it is assumed that the CD-ROM drive has a SCSI ID of 6 (for Solaris) and 3 (for HP-UX). Make sure that you specify the correct ID in the above mount commands.

## Step 2: Local Installation

If you are installing from a CD-ROM that is on a remote machine, skip to Step 3.

#### On SunOS 4.1.x

cd /cdrom/sunos ./install.wr4

To install the Acrobat Reader separately, run the following commands instead of the above commands:

```

cd /cdrom/sunos/acroread

./install

```

#### On Solaris 2.5

```

cd /cdrom/w3r40fcs/solaris

./install.wr4

```

To install the Acrobat Reader separately, run the following commands instead of the above commands:

```

cd /cdrom/w3r40fcs/solaris/acroread

./install

```

#### On HP-UX 9.05

cd /cdrom/HP ./INSTALL.WR4

The above program will guide you through the rest of the installation process.

To install the Acrobat Reader separately, run the following commands instead of the above commands:

cd /cdrom/HP/ACROREAD ./INSTALL

After this step is completed, please skip to Step 4.

# Step 3: Remote Installation

#### On SunOS 4.1.x

If you are installing from a CD-ROM that is on a remote machine, export the */cdrom* directory. Add the following line:

```

/cdrom -ro

```

to the file */etc/exports* on the remote machine, if the line does not already exist. If you are modifying an existing */etc/exports*, run the following command:

```

/usr/etc/exportfs -a

```

If */etc/exports* does not exist and you have had to create it to enter the above line, run the following commands:

sync reboot

If your sync command also reboots the machine, you do not need to run the above reboot command.

Remote login to the install machine (where you want to install the software) using the following commands:

rlogin <install machine> -1 root

If */cdrom* does not exist, run the following command:

mkdir /cdrom.

Mount the remote CD-ROM on the install machine, change the directory to the CD-ROM, and run the installation script by using the following commands:

```

mount -r <remote-machine-name>:/cdrom /cdrom

cd /cdrom/sunos

./install.wr4

```

The above program will walk you through the rest of the installation process.

To install the Acrobat Reader separately, run the following commands instead of the above commands:

```

mount -r <remote-machine-name>:/cdrom /cdrom

cd /cdrom/sunos/acroread

./install

```

#### On Solaris 2.5

If you are installing from a CD-ROM that is on a remote machine, export the */cdrom* directory. Add the following line:

share -F nfs -o ro /cdrom/warp

to the file /etc/dfs/dfstab on the remote machine, if the line does not already exist. If nfsd is not running, reboot the machine.

Run the following command to export /cdrom/warp:

```

shareall

```

Remote login to the install machine (where you want to install the software) using the following commands:

rlogin <install machine> -1 root

If */cdrom* does not exist, run the following command:

mkdir /cdrom

Mount the remote CD-ROM on the install machine, change the directory to the CD-ROM, and run the installation script by using the following commands:

```

mount -r <remote-machine-name>:/cdrom/warp3r40 /cdrom

cd /cdrom/solaris

./install.wr4

```

The above program will walk you through the rest of the installation process.

To install the Acrobat Reader separately, run the following commands instead of the above commands:

```

mount -r <remote-machine-name>:/cdrom/warp3r40 /cdrom

cd /cdrom/solaris/acroread

./install

```

#### On HP-UX 9.05

If you are installing from a CD-ROM that is on a remote machine, export the */cdrom* directory. Add the following line:

```

/cdrom -ro

```

to the file */etc/exports* on the remote machine, if the line does not already exist. If you are modifying an existing */etc/exports*, run the following command:

```

/usr/etc/exportfs -a

```

If */etc/exports* does not exist and you have had to create it to enter the above line, reboot the machine.

Remote login to the install machine (where you want to install the software) by using the following commands:

```

rlogin <install machine> -l root

```

If /cdrom does not exist, run the following command:

```

mkdir /cdrom

```

Mount the remote CD-ROM on the install machine, change the directory to the CD-ROM, and run the installation script by using the following commands:

```

mount -o ro <remote-machine-name>:/cdrom /cdrom

cd /cdrom/HP

./INSTALL.WR4

```

The above program will walk you through the rest of the installation process.

To install the Acrobat Reader separately, run the following commands instead of the above commands:

```

mount ~o ro <remote-machine-name>:/cdrom /cdrom

cd /cdrom/HP/ACROREAD

./INSTALL

```

#### On all platforms:

Unmount the CD-ROM and come back to <CD-ROM\_drive host> machine.

```

cd /

umount /cdrom

exit

```

# Step 4: Unmount the CD-ROM

Type in these commands:

cd / umount /cdrom

# Update User's Login Start Up File

To run *Warp*, you need to set some environment variables in the user's login start up file.

#### For C Shell users:

If you are using *C* shell, add the following lines to your ~/.cshrc file:

```

setenv CYPRESS_DIR <Warp installation directory>

set path = ($CYPRESS_DIR/bin $path)

setenv SPDE_ROOT $CYPRESS_DIR/spde

setenv XVTPATH $SPDE_ROOT/print

setenv UIDPATH $SPDE_ROOT/%N.uid

set path = ($SPDE_ROOT $path)

```

On Sun/Solaris, also include the following line:

setenv LD\_LIBRARY\_PATH \${LD\_LIBRARY\_PATH}:\${SPDE\_ROOT}

On HP, also include the following line:

setenv SHLIB\_PATH \${SPDE\_ROOT}

On all platforms, copy the pASIC® control file (*\$CYPRESS\_DIR/spde/.spderc*) into your home directory.

If you have purchased the *Warp2* product and would like to configure *Warp* to run with Viewlogic tools, in addition to the above lines, add/replace the WDIR environment variable in your ~/.cshrc file:

```

setenv WDIR ~/<pvlocal>:$CYPRESS_DIR/warpstd:<PowerView-

Install-Dir>/standard

```

It is important that the *\$CYPRESS\_DIR/warpstd* directory appear before the Powerview directory.

If you have purchased the *Warp3* product, add the following lines to your ~/.*cshrc* file:

```

setenv WDIR ~/<pvlocal>:$CYPRESS_DIR/warpstd:$CYPRESS_DIR

/pv/standard

set path = ($CYPRESS_DIR/pv $path)

```

As noted above, *<pvlocal>* is a local directory where user specific Powerview files and user design files can be stored.

If you have installed the **Acrobat Reader**, add the following lines to your ~/.*cshrc* file:

```

setenv ACROBAT_DIR <Acrobat Reader installation

directory>

set path = ($ACROBAT_DIR/bin $path)

```

Source the ~/.*cshrc* file.

#### For Bourne shell users:

If you are using *Bourne shell*, add the following lines to *\$HOME/.profile* file in the same order.

```

CYPRESS_DIR=<Warp installation directory>

PATH=$CYPRESS_DIR/bin:$PATH

export CYPRESS_DIR PATH

SPDE_ROOT=$CYPRESS_DIR/spde

XVTPATH=$SPDE_ROOT/print

UIDPATH=$SPDE_ROOT/%N.uid

PATH=$SPDE_ROOT:$PATH

```

On Sun/Solaris, also include the following lines:

```

LD_LIBRARY_PATH=$LD_LIBRARY_PATH:$SPDE_ROOT

export SPDE_ROOT XVTPATH UIDPATH PATH LD_LIBRARY_PATH

```

On HP, also include the following lines:

SHLIB\_PATH=\$SPDE\_ROOT export SPDE\_ROOT XVTPATH UIDPATH PATH SHLIB\_PATH

On all platforms, copy the pASIC control file (*\$CYPRESS\_DIR/spde/.spderc*) into your home directory.

If you have purchased the *Warp2* product and would like to configure *Warp* to run with Viewlogic tools, add/replace the WDIR environment variable in your *\$HOME/.profile* file:

```

WDIR=$HOME/<pvlocal>:$CYPRESS_DIR/warpstd:<PowerView-

Install-Dir>/standard

export WDIR

```

It is important that the *\$CYPRESS\_DIR/warpstd* directory appear before the Powerview directory.

If you have purchased the *Warp3* product, add the following lines to your *\$HOME/.profile* file:

```

WDIR=$HOME/<pvlocal>:$CYPRESS_DIR/warpstd:$CYPRESS_DIR/

pv/standard

PATH=$CYPRESS_DIR/pv:$PATH

export WDIR PATH

```

As noted above, *<pvlocal>* is a local directory where user specific Powerview files and user design files can be stored.

If you have installed the **Acrobat Reader**, add the following lines to your *\$HOME/.profile* file:

```

ACROBAT_DIR=<Acrobat Reader installation directory>

PATH=$ACROBAT_DIR/bin:$PATH

export ACROBAT_DIR PATH

```

Source the \$HOME/.profile file.

#### For both C-shell and Bourne shell users:

If you are running **SunOS 4.1.***x*, make sure that */usr/openwin/lib* and */usr/motif/lib* are included in the LD\_LIBRARY\_PATH before running *Warp*.

If you are running **Solaris 2.5**, make sure that */usr/openwin/lib* is included in the LD\_LIBRARY\_PATH before running *Warp*.

If you have configured *Warp* to run with Viewlogic tools, also make sure that the WDIR path includes a writable directory (*<pvlocal>* above).

# License Issues for Viewlogic Tools (Warp3 Customers)

*Warp3* customers on the workstation platforms also require a license file. Again, this license file enables the Viewlogic Powerview tools. However, for the workstation environment there are two types of license files available: node-locked and floating. For more information on these types of license files, please refer to the Viewlogic on-line documentation. Your *Warp3* registration form should already specify the type of license that was purchased. If this is not correct, please contact the sales office through which your software was purchased. Workstation license files are specified via the HOSTID which is unique to each workstation as opposed to a hardware key in the PC environment. Please make sure you specify your HOSTID on the registration form correctly.

# Run Warp

If you have purchased the *Warp3* product or configured the *Warp2* product to run with Viewlogic tools, run the following command:

#### powerview

If you have purchased the Warp2 product, run the following command:

galaxy

### To Read the On-line Documentation

To read the on-line User's Guide, run the following command:

acroread <Warp Installation directory>/doc/usguide.pdf

To read the on-line *Reference Manual*, run the following command:

acroread <Warp Installation directory>/doc/refman.pdf

On-line documentation files can also be opened from the Acrobat Reader's file selection dialog box. The files are in *<Warp Installation directory*/*doc>*.

On-line documentation can also be found on your CD-ROM in the /docs directory.

For more information on the Acrobat Reader, read the *ReadMe-Reader.txt* and *Help-Reader.pdf* files in the *<Acrobat Reader Installation directory>/Help* directory.

# Chapter 2

# **Overview**

2

Welcome to the *Warp* programmable logic design tool. *Warp* offers unparalleled performance and flexibility with a user-friendly GUI. *Warp* leads the programmable logic industry in device resource utilization and speed optimization for programmable logic. Thus, designs can be tuned to have the fastest performance with smallest area utilization. *Warp's* flexibility means flexibility of design entry methods: schematic capture, industry standard VHDL entry, or a combination of both; moreover, *Warp* is independent of device architecture, which means one design format can target all Cypress programmable logic devices. *Warp* is a fully integrated EDA tool, fully IEEE VHDL compliant, and available to run on many computer platforms.

*Warp* is available for all of the popular computer platforms available:

| Computer | Operating System                                                                    |

|----------|-------------------------------------------------------------------------------------|

| PC       | Windows 3.1<br>Windows 95 ( <i>Warp</i> 2 only)<br>Windows NT ( <i>Warp</i> 2 only) |

| Sun      | Solaris<br>SunOS                                                                    |

| HP       | HP-UX                                                                               |

| Тε | ıble | 2-1 |

|----|------|-----|

|----|------|-----|

Table 2-2 lists the parts for which *Warp* can target designs. These parts can be divided into three families:

- 1. PLDs: these are industry standard devices such as 22V10s, 16V8s, and 20v8s. They are both high performance and low cost.

- 2. CPLDs: the Cypress FLASH370<sup>™</sup> high-density CPLD family and the Cypress MAX340<sup>™</sup> multiple-array matrix, high-density CPLD family.

- 3. FPGAs: the Cypress pASIC380<sup>™</sup> high-speed CMOS FPGA family.

|        |   | _ |   |  |

|--------|---|---|---|--|

| Part # |   |   |   |  |

|        | _ |   | _ |  |

|        |   |   |   |  |

| Table | 2-2 |

|-------|-----|

|-------|-----|

| ſ | PLDs  | PALC16V8, 20V8, 22V10, CY7C335 |

|---|-------|--------------------------------|

|   | CPLDs | FLASH370, MAX340               |

|   | FPGAs | pASIC380 family                |

Family

# **Streamlined Design Process**

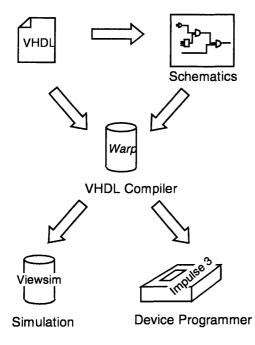

*Warp*'s design process is intuitive and straightforward. The fully integrated *Warp* comes with all the necessary tools for design entry, design synthesis, fitting, place and route, and design verification. *Warp3* integrates the Cypress VHDL synthesis, fitting, and place and route technology with the Viewlogic Powerview or Workview PLUS environment. The Viewlogic Cockpit<sup>TM</sup> facilitates project management and intertool communication.

# **Project Management**

The Viewlogic Cockpit provides an easy point-and-click interface for starting the design tools and design project management within the *Warp3* design flow. Tools run from within the Cockpit pass the current design name and project directory from one tool to the next.

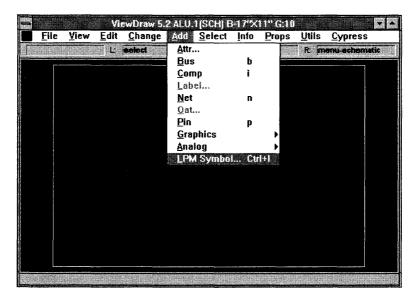

# **Design Entry**

The ViewDraw<sup>®</sup> tool within the *Warp3* environment is used to capture designs graphically using schematics. This tool allows the user to choose elements from a Library of Parameterized Modules (LPM) as well as create graphical symbols from lower-level VHDL blocks. The user can thus capture designs in the manner that he or she prefers.

# **Generating a VHDL Netlist**

The *Warp3* tool converts schematic designs into an IEEE compliant VHDL netlist for synthesis. This VHDL netlist combines the schematic portion of the design with the lower-level VHDL blocks while retaining the hierarchy created by the designer.

### Synthesis, Fitting, and Place and Route

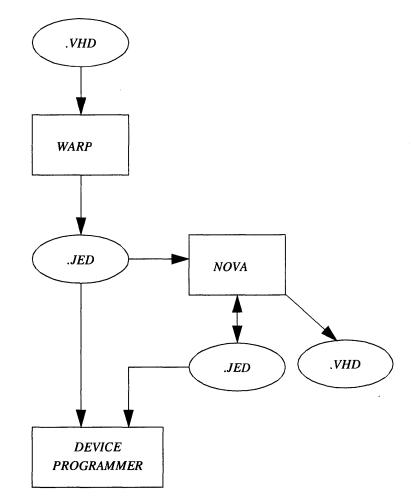

Galaxy<sup>TM</sup> is the name of the Graphical User Interface (GUI) for the *Warp* VHDL compiler. *Warp* accepts VHDL as input, checks the design for proper VHDL syntax, and synthesizes the design into logic equations for a target device.

Warp features the UltraGen<sup>™</sup> module generation technology. This technology allows the user to write VHDL code using high-level datapath operators in a truly behavioral fashion. The UltraGen technology then maps each of these high-level operators to an architecture specific module pre-optimized for area or speed, depending on the user's directive. Each portion of VHDL code, via a control file, can accept a different synthesis goal which allows for fine tuning of critical paths within a design. For PLDs and CPLDs, the logic equations produced by the synthesis are automatically passed to the fitter, which fits the logic into a particular device. The output of the fitter is a JEDEC map which can be used to program the device using the Cypress *Impulse*<sup>3™</sup> programmer.

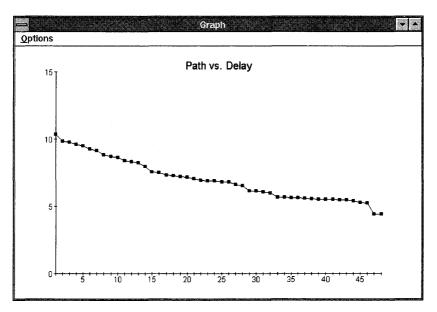

For FPGAs, *Warp* translates the design into a netlist specific to the FPGA architecture. This netlist describes the interconnection of logic elements that can map directly to logic cells of the FPGA device. The place and route tool takes the FPGA netlist generated by the *Warp* compiler, places the logic equations within the logic cells, and routes the necessary signals between logic cells and I/O pins. A static timing analyzer (path analyzer) is available to evaluate worst-case delays and allows for timing-constrained placement and routing as well.

## **Design Verification**

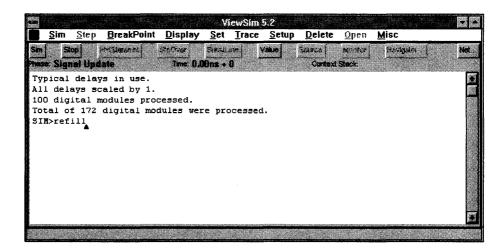

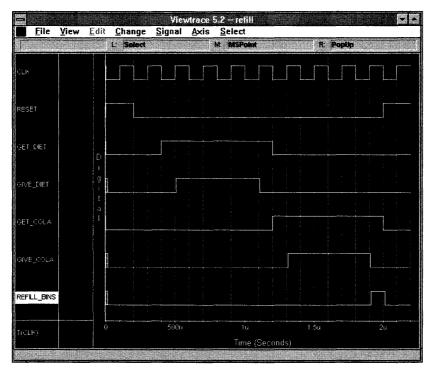

Nova<sup>™</sup> is a very convenient tool for PLD or CPLD design simulation. During the initial design stage, Nova can be valuable in obtaining simulation results quickly. For full timing information and verification, Cypress offers the Viewlogic ViewSim® simulator.

ViewSim simulates the design with full timing information. With ViewSim, one can verify the functionality of the design and determine if the design meets the timing requirements of the specific system. ViewSim provides an interface to ViewTrace®, which displays waveforms and allows direct interaction with the simulator.

#### What's in This Manual?

Besides the Tutorials chapter, this *User's Guide* is meant more as a guide to using *Warp* and less as a reference book, and would be best digested in complete chapters.

Chapter 1 covered all of the necessary information required to get the software installed and up and running.

Chapter 3 is the Tutorials chapter. This section demonstrates the design process via a well-tailored design exercise, which illustrates the *Warp2* and *Warp3* tools respectively.

Chapter 4 contains a description of the Galaxy user interface.

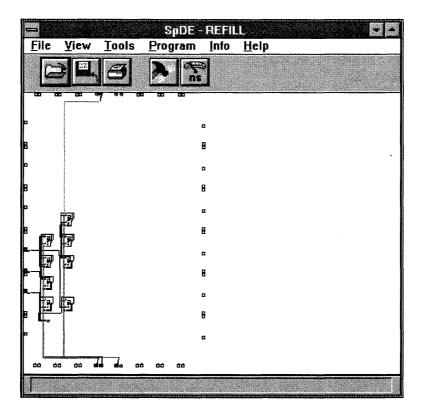

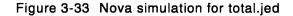

Chapter 5 focuses on the SpDE place and route toolkit.

Chapter 6 discusses the Nova functional simulator used for simulating simple PLD and CPLD devices.

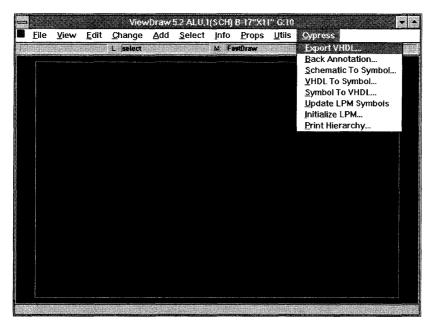

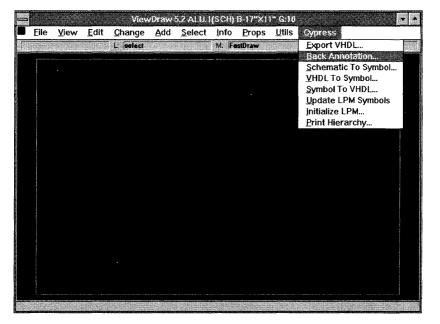

Chapter 7 contains valuable information regarding the use of ViewDraw for schematic and mixed-mode designs.

Chapter 8 includes information regarding simulation interfaces within the *Warp* environment as well as how to interface with third party simulators.

Chapter 9 culminates much of the information presented within this book into a guide to synthesis using *Warp*. This chapter focuses on how to get the most out of your VHDL designs.

Chapter 10 is a brief description of the device programming portion of the flow as it contains information regarding file types and device programmers.

2

Warp User's Guide

# Chapter 3

# **Tutorials**

3

### 3.1 Introduction

The *Warp* tutorials demonstrate a common sequence of operations in *Warp2* and *Warp3*. The tutorials show the user how to create, compile, synthesize, and simulate designs.

This section presents:

- product descriptions of Warp2 and Warp3

- some conventions about typography, wording, and illustrations used in this manual

- the objectives of the tutorial

- the contents of the tutorial

## 3.1.1 Product Descriptions

#### Warp2

*Warp2* allows users to describe electronic designs using VHDL and then to compile and synthesize those descriptions to program Cypress devices, such as small PLDs, MAX340 EPLDs, FLASH370 CPLDs, and pASIC380 FPGAs.

Warp2 consists of three major components:

- The *Warp* VHDL compiler which is IEEE 1076/1164 compliant and translates VHDL text descriptions into JEDEC and QDIF (for pASIC380 FPGAs only) files that can be mapped onto programmable devices.

- The Nova JEDEC functional simulator which allows you to verify the correctness of a design by simulating its behavior.

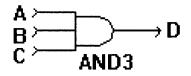

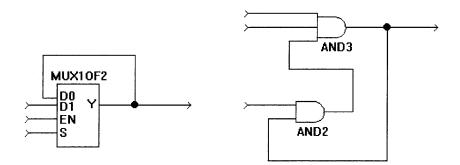

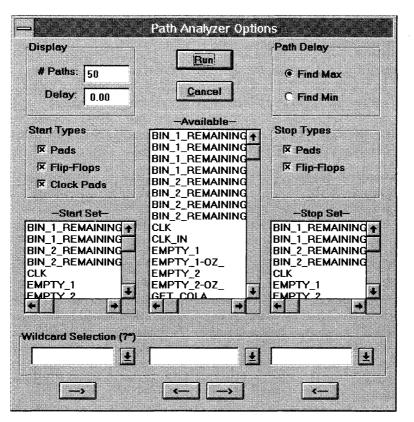

- The SpDE<sup>™</sup> toolkit which contains a set of tools for fitting designs into pASIC380 FPGAs. This tool set includes a placer, router, logic optimizer, and a path analyzer, among others.

#### Warp3

*Warp3* enables users to define, compile and synthesize VHDL descriptions, schematic descriptions, or a combination of VHDL (text-based) descriptions with schematic drawings of electronic designs into Cypress programmable logic devices.

Finished files can be synthesized into (i.e., used to program) Cypress devices, such as small PLDs, MAX340 EPLDs, FLASH370 CPLDs, and pASIC380 FPGAs.

*Warp3* integrates all of the components from the *Warp2* software with the Viewlogic Workview PLUS and Powerview CAE environments. Included with *Warp3* are the following:

- The *Warp* VHDL compiler which is IEEE 1076/1164 compliant and translates VHDL text descriptions into JEDEC and QDIF (for pASIC380 FPGAs only) files that can be mapped onto programmable devices.

- The Nova JEDEC functional simulator which allows you to verify the correctness of a design by simulating its behavior.

- The SpDE toolkit which contains a set of tools for fitting designs into pASIC380 FPGAs. This tool set includes a placer, router, logic optimizer, and a path analyzer, among others.

- Viewlogic's Workview PLUS design environment (for IBM PCs and compatibles) and the Powerview design environment (for UNIX workstations). Viewlogic provides the Cockpit, which is the central access point for all tools in the *Warp3* system. The Cockpit contains icons that bring up any tool the user needs. Viewlogic's design environments provide a large set of design tools in and of themselves. Among them are ViewDraw, a hierarchical schematic and symbol editor; ViewSim, a full-featured simulator that accurately models timing delays; ViewTrace, a waveform viewing tool that helps you analyze simulator results; and numerous other tools for special needs.

Warp User's Guide

# 3.1.2 Conventions

The following conventions are used throughout this manual:

| Menu items | Whenever an item from a menu is referenced, the ref-<br>erence takes the form <i>menu-name-&gt;item-name-&gt;item-name</i> The first entry in the reference is the name of<br>the menu; the second is the name of the menu item;<br>the third and succeeding entries indicate choices from<br>sub-menus. Example: Select <i>File-&gt;Open</i> tells you to<br>pull down the <i>File</i> menu and select the <i>Open</i> item<br>from it. |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Path names | Italics are also used to designate path names and file<br>names.<br>Words are <b>bolded</b> for emphasis or to draw attention to<br>new terms.                                                                                                                                                                                                                                                                                           |  |

| Bold       |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Courier    | Denotes signal names and other VHDL constructs as well as system output.                                                                                                                                                                                                                                                                                                                                                                 |  |

| Courier    | Denotes the contents of a text file and also indicates the text of typed commands.                                                                                                                                                                                                                                                                                                                                                       |  |

Table 3-1 Notational Conventions

# File Naming Conventions

*Warp* runs on many different platforms: IBM PCs and compatible computers, Sun workstations, and HP workstations.

IBM PCs and compatible computers specify file locations by designating a disk drive and using a backslash (\) character to distinguish directory levels, e.g., *c:\level1\level2\myfile*.

Sun and HP workstations specify file locations using a forward slash (/) and no disk drive designator, e.g., */level1/level2/myfile*.

For consistency and brevity, this manual uses the same notation as IBM PCs and compatibles when referring to file locations. UNIX platform users are asked to make appropriate translations.

# **Mouse Conventions**

The following terms describe common actions you might perform in using this manual:

| Tab | le | 3-2 |

|-----|----|-----|

|-----|----|-----|

| Click        | Place the mouse cursor over an object, then press and release the appropriate mouse button.                                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Double-click | Position the mouse cursor over an object, then press<br>and release the appropriate mouse button twice in<br>rapid succession.                                                                                                               |

| Drag         | Position the mouse cursor over an object or at a speci-<br>fied location. Press and hold the appropriate mouse<br>button. While holding down the mouse button, move<br>the cursor to the new location. Finally, release the<br>mouse button. |

| Select       | When you are instructed to "select" an option, move<br>the cursor over the option, then click the appropriate<br>mouse button.                                                                                                               |

# **Other Conventions**

The following visual indicators denote special situations you may encounter while using this manual.

**Note** – This icon indicates a *note*: a point in the tutorial where you must exercise special caution, or where the procedure might vary depending upon the platform you're using, or where there's something else you should know about that doesn't fit into the main flow of the text.

农

**Hint** – This icon indicates a *hint*: a point in the tutorial where you could save a little time, a few keystrokes, or much frustration if you follow the hint that's being explained.

## 3.1.3 Differences between Operating Systems

*Warp* operates identically on both UNIX and Windows systems except for start-up procedure and the appearance of some objects in the display.

## Naming Restrictions

In the Windows environment, file names **must** be eight or fewer alpha-numeric characters plus a file extension of up to three characters (e.g., *.exe*, *.vhd*, etc.). This is important to remember for transferring data between Windows and UNIX/Windows 95 implementations of *Warp*.

R-

**Note** – Keep in mind that some UNIX systems have trouble with spaces embedded in file names. That can be true for IBM PCs and compatible systems, too. Cypress recommends not using embedded spaces in file names.

**Note** – If you are working in a system with PCs (running under Windows) and UNIX workstations connected to the same network, Cypress advises you to name all VHDL files with lower case characters.

#### **Differences in Display**

Although dialog boxes and prompts may differ in appearance between the two platforms, their functionality is identical. Screen captures in this manual are taken from the Windows version of *Warp*. Differences in the UNIX version are identified when necessary. In most cases, any adjustments needed to go from Windows to UNIX versions of *Warp* displays are obvious.

#### For Warp3 Users Only

There are minor differences between the Windows and UNIX versions of *Warp3* in the appearance of the Cockpit, the dialog boxes, and the prompt boxes. Besides these minor differences, the operation of the *Warp3* software is virtually identical among all platforms.

# 3.2 Designing a Soda Machine

This section takes you step-by-step through a tutorial example using a low-level VHDL behavioral description and a high-level VHDL file that instantiates the component contained in the lower level VHDL file. When you complete this section, you will know how to:

- write an entity declaration, architecture, component and package declaration for a VHDL behavioral description of a simple circuit

- write an entity declaration and architecture that instantiates the simple circuit in a VHDL description of a higher-level circuit

- run Warp to compile and synthesize the design's VHDL description

- run Nova to simulate the behavior of the design

- for Warp3 users only: simulate the design with ViewSim

# 3.2.1 Design Description

In this example, you will design a controller for a soft-drink dispensing machine. The machine has two bins to dispense regular cola and diet cola. Each bin holds three cans of soft drink. (This could be any value, but three is an easy number to simulate.)

The circuit should dispense a beverage if the user presses a button for that beverage and one or more cans of the beverage are available. The circuit should not dispense a beverage if no cans of that beverage are available. A refill signal should appear when both bins are empty. Finally, pressing a reset signal should tell the circuit that the machine has been replenished and that the bins are full again.

# 3.2.2 Design Solution

The solution presented in this section will proceed as follows:

First, this tutorial will describe a circuit in IEEE standard VHDL that controls the operation of one bin. It will respond appropriately to a get\_drink signal (i.e., by giving a drink when one is available), keep count of the number of cans left in the bin, and set an empty signal when its bin becomes empty and is in need of resetting. This circuit will be named *binctr*. You will also add appropriate VHDL to declare this circuit a component and define a package that contains that component, which will allow you to use the circuit in higher-level designs.

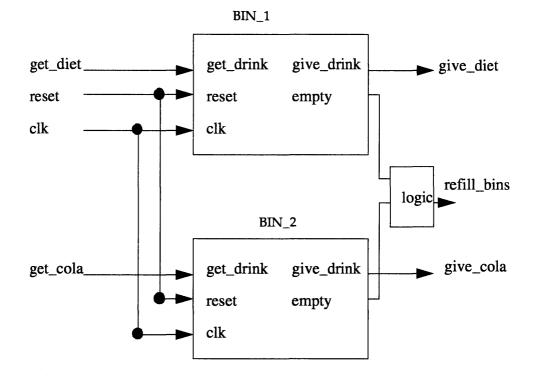

27

Then, you will write a top-level description of a circuit that instantiates two *binctrs* and other logic as appropriate to describe the larger design described above. The larger design will be called *refill*.

After that, you'll compile and synthesize the *binctr* and *refill* VHDL descriptions into a CY7C371 JEDEC file and simulate the behavior of the resulting design using the Nova functional simulator.

## 3.3 Starting Warp

#### For Warp2 Users

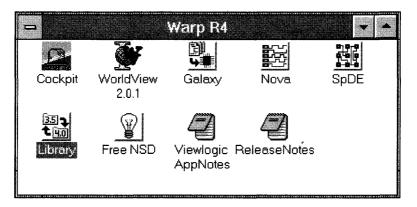

- => On Windows systems, start *Warp2* by double-clicking on the *Galaxy* icon from the *Warp R4* program group.

- => On UNIX systems, start *Warp2* by typing **galaxy<CR>** from within a shell window.

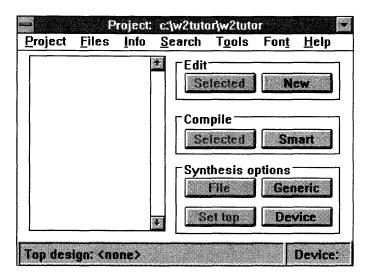

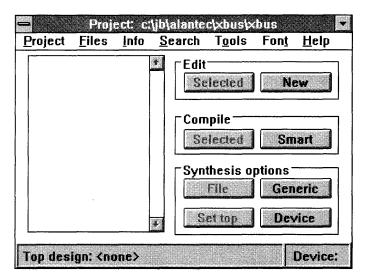

In both systems, the Galaxy window should appear as shown in Figure 3-2.

#### For Warp3 Users

- => On Windows systems, you start *Warp3* by double-clicking on the *Cockpit* icon from the *Warp R4* program group.

- => On UNIX systems, you start *Warp3* by typing **powerview<CR>** from within a shell window.

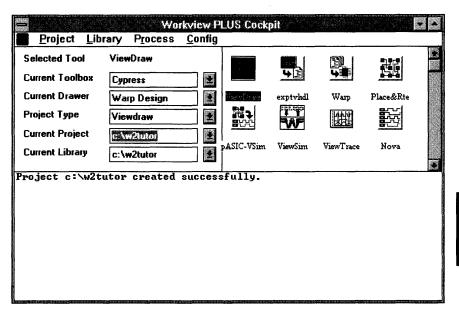

On both platforms, the Cockpit should be displayed immediately after you start *Warp3*. The Cockpit is labeled "Workview PLUS Cockpit" on Windows systems, "Powerview Cockpit" on UNIX systems, and should appear as shown in Figure 3-3.

Figure 3-1 The Warp R4 Program Group

## 3.4 Creating A New Project

#### For Warp2 Users

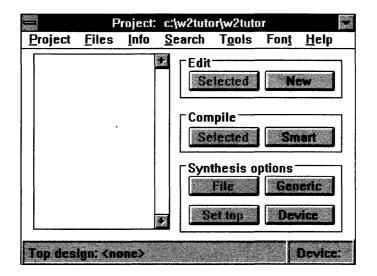

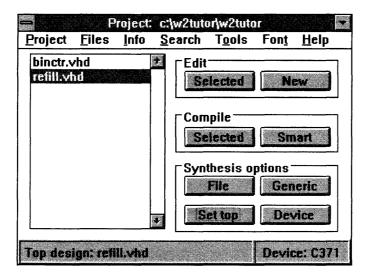

=> Under the Project menu, choose New. A new Galaxy window will appear, prompting you for a new name. On the PC, enter c:\w2tutor\w2tutor and on UNIX systems, enter <user home directory path>/w2tutor/w2tutor.

You should now see a Galaxy window identical to the one that appeared when you started *Warp*, except that it is named *c*:\w2tutor\w2tutor.

You have now created a project directory for your designs and called it *w2tutor*. All files pertinent to this tutorial need to be placed in this project directory. You have also created a project file called *w2tutor.wpr* which is now located in the  $c:\w2tutor$  directory.

Figure 3-2 Galaxy window named c:\w2tutor\w2tutor

#### For Warp3 Users

=> Select Project->Create from the Cockpit menu bar. When a dialog box

appears, on the PC type the pathname c:\w2tutor and on UNIX

systems, type <user home directory path>/w2tutor and then

click OK

Figure 3-3 Warp3 cockpit

When doing the tutorial exercises (or any other time, for that matter), **don't write anything into the** *Warp* **directory**. Instead, create a separate directory to practice in, such as the  $c: \w2tutor$  directory you have just created above.

By default, the *Warp3* installation procedure for IBM PCs and compatible computers installs *Warp3* software into a directory named *c:\warp*. On UNIX workstations, the user needs to point the CYPRESS\_DIR environment variable to point to the location of the *Warp3* software.

3

# 3.5 Creating the VHDL File

#### For Warp2 Users

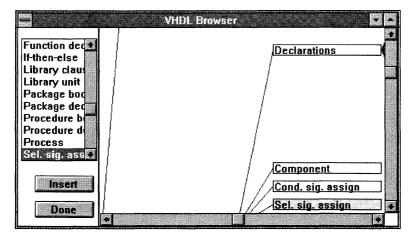

=> In your Galaxy window, click on *New* in the *Edit* button section on the right.

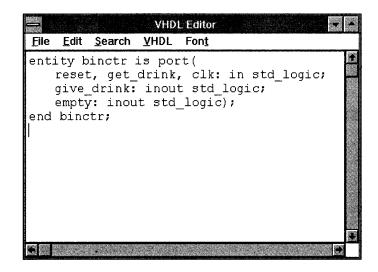

This will bring up a VHDL text editor (Figure 3-4), in which you can enter your VHDL code.

| -            |              |                | VHDL E       |  | - |   |

|--------------|--------------|----------------|--------------|--|---|---|

| <u>F</u> ile | <u>E</u> dit | <u>S</u> earch | <u>v</u> hdl |  |   |   |

|              |              |                |              |  |   | * |

| •            |              |                |              |  | • |   |

Figure 3-4 VHDL Editor

#### For Warp3 Users

=> From the Cockpit window, click on the *Warp* icon. After the Galaxy window appears, click on *New* in the *Edit* button section.

This will bring up the VHDL editor in which you can enter your VHDL code.

3

The *binctr* VHDL description will be written in three parts:

- the entity declaration declares the name, direction, and data type of each port of the component

- the architecture describes the behavior of the component

- the **package** declaration provides the information to *Warp* to allow *binctr* to be used as a component in a higher-level design

The following pages briefly discuss the contents of each of these sections of the VHDL description. For a detailed explanation on these VHDL constructs, please refer to the text book which was included in your software kit entitled VHDL for Programmable Logic.

#### 3.5.1 Writing the Entity Declaration

=> Copy the following lines into your VHDL text editor:

```

entity binctr is port(

```

```

reset, get_drink, clk: in std_logic;

give_drink: inout std_logic;

empty: inout std_logic);

end binctr;

```

The entity declaration declares the name, direction, and data type of each port of the component. The entity declaration declares that entity binctr has five external interfaces, or ports. It has three input ports of type std\_logic, named reset, get\_drink, and clk, respectively. It has two input/output (inout) ports, also of type std\_logic, named give\_drink and empty, respectively.

```

3

```

The signals give\_drink and empty are of mode inout and represent the various states that the state machine can assume. The architecture definition for the entity binctr requires that signals give\_drink and empty retain their values when all other state transition conditions are untrue. This forces give\_drink and empty to feed back on themselves apart from being outputs of the state machine. Hence the signals give\_drink and empty are declared with mode inout.

Figure 3-5 The VHDL editor with the entity description

## 3.5.2 Writing the Architecture

=> Copy the following lines into your VHDL text editor *below* your entity declaration:

```

architecture archbinctr of binctr is

constant full: std_logic_vector(1 downto 0):= "11";

-- max of 3 drinks/bin

signal remaining: std_logic_vector(1 downto 0);

begin

proc_label: process (clk,reset)

begin

if (reset = 1') then

remaining <= full;</pre>

empty <= `0';</pre>

give_drink <= `0';

elsif (clk'event and clk = '1') then

if (remaining = 00'') then

empty <= 1';

give_drink <= `0';

elsif (get drink = 1') then

remaining <= remaining - 1;

give_drink <= `1';

elsif (get_drink = `0') then

give_drink <= `0';

else

give_drink <= give_drink;

remaining <= remaining;

empty <= empty;</pre>

end if;

end if:

end process;

end archbinctr;

```

The architecture portion of a VHDL description describes the behavior of the component and always appears *after* the entity description.

The first line declares an architecture named archbinctr of entity binctr.

The next two lines declare a constant and a signal, respectively.

- The constant, named full, determines how many drinks are in a full bin.

- Signal remaining, of type std\_logic\_vector keeps track of how many drinks are left in the bin.

The begin that follows the signal declaration marks the start of the architecture body. All constant and signal declarations in the architecture of the VHDL code should precede the begin statement.

A process declaration follows, marked by the keyword process and an ensuing begin. The process declaration ends with the end process; statement.

The last line end archbinctr; denotes the end of the architecture declaration.

You can add comment lines to your VHDL code by placing "--" before the text on a line that you want commented. All or part of a line can be commented out as shown on the line that defines the constant full.

The architecture defines a process which is activated by any changes to the clk or the reset signal. The process definition shown here is a VHDL template for describing a synchronous circuit with an asynchronous reset.

Signal activity is handled in the following sequential order:

- The process within the architecture is triggered only if there is a change in the logic levels of the signals clk and reset. These signals are therefore included in the process sensitivity list. The signal order in the sensitivity list is arbitrary.

- If signal reset is '1', then signal remaining is set to full, signal empty is set to '0', and signal give\_drink is set to '0'. (Notice that this means reset has priority over all other signal declarations in the architecture definition. This forces the compiler to define the reset as an asynchronous reset for the design.

- The reset signal needs to be false to initiate the execution of the rest of the statements in the process declaration.

- The clock definition statement indicates to the compiler that all registered equations in the architecture definition are to be synthesized into rising edge triggered flip-flops. The process can be changed to be falling edge sensitive by altering the clock definition statement to look like this:

(if clk'event and clk = `0').

- If signal remaining has a value of "00", then signal empty is set to '1' and signal give\_drink is set to '0'.

- If signal remaining is not a '0' and signal get\_drink is '1', then signal remaining is decremented by one and signal give\_drink is set to '1'.

- If signal remaining is not "00" and signal get\_drink is '0', then signal give\_drink is set to '0'.

- If the if-then-elsif conditions are false, give\_drink, remaining and empty retain the current value of give\_drink, remaining and empty respectively.

Several lines ending the if statement, process, and architecture follow. Note that the end statement of the architecture must be accompanied by the name of the architecture, which **must** match the name shown on the first line of the architecture.

## 3.5.3 Writing the Package Declaration

=> Copy the following lines into your VHDL text editor *before* the entity declaration:

```

package binctr_pkg is

component binctr

port(reset, get_drink, clk: in std_logic;

give_drink: inout std_logic;

empty: inout std_logic);

end component;

end binctr_pkg;

```

The package declaration provides the information to the *Warp* compiler to allow *binctr* to be used as a component in a higher-level design.

## 农

**Note** – The package declaration **must** appear before the entity declaration and architecture in the *.vhd* file.

The first line in the above package declaration names the package. The name of the package must be distinct from the name of any component declared within that package. Using the convention <*entity*\_pkg works nicely.

The second line declares a component named binctr. The component name that appears on this line must match the name of an accompanying entity.

The port statement declares the name, direction, and type of each port in the component. You can copy the port statement from the entity declaration for this purpose.

An end component and end binctr\_pkg statement conclude the package declaration. Note that the package named in the end package statement must match that shown in the first line of the package declaration.

At this point, save the file as c:\w2tutor\binctr.vhd.

### 3.5.4 Including the Libraries

=> Insert the following three lines of VHDL code *before* the package declaration *and* also *before* the entity declaration:

```

library ieee;

use ieee.std_logic_1164.all;

use work.std_arith.all;

```

These two lines advise the compiler to link to the IEEE VHDL library, and the Cypress UltraGen module generation library. The compiler finds definitions for the various types, modes, and VHDL constructs defined in the user's VHDL code. In general, the **library** and **use** VHDL reserved words instruct the compiler to include pre-defined libraries and user created VHDL files, in compiling the selected VHDL code. For more information on the std\_logic\_1164 and std\_arith packages, see Chapter 4, "VHDL," in the *Reference Manual*.

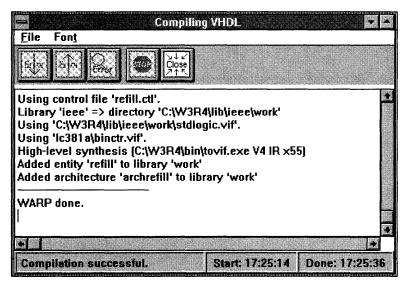

# 3.6 Verifying the VHDL Syntax

=> First, save your VHDL file by clicking on Save under the File menu.

=> Then under the VHDL menu, select Compile.

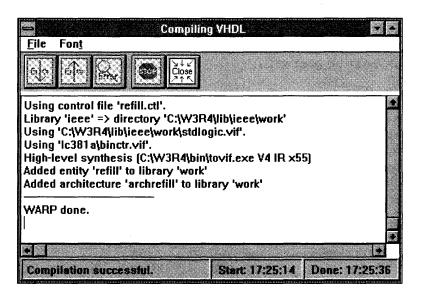

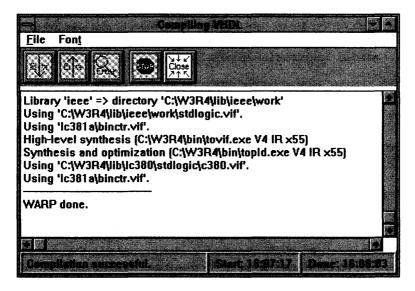

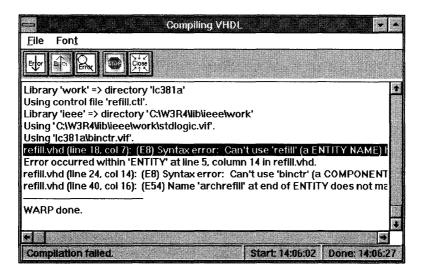

*Warp* runs, printing messages to keep you appraised of its progress. The verification process should run to completion without any error messages. A snapshot of this window is shown in Figure 3-6.

=> Close your VHDL file by clicking on the close box, or selecting Close under the File menu. You have just used *Warp* to verify that the *binctr.vhd* file is syntactically correct. This step isn't strictly necessary, but it's always a good idea to compile any VHDL description once it's completed. That way, you can spot problems in your VHDL description when they are easiest to identify and correct. Later, should you encounter problems with the larger circuit, you can at least be assured that you have taken care of any errors in the lower levels of the hierarchy.

Figure 3-6 A successful Warp compilation

**Note** – If you do get error messages, check to make sure that the various parts of the *binctr.vhd* file read **exactly** as they are listed on the preceding pages. Better yet, copy the *binctr.vhd* file from the *c:\warp\examples\wtutor* directory of the *Warp* installation, then try compiling the design again.

# 3.7 Creating a Top-Level Description

Now that you have defined the behavior of the lower level of the circuitry, you can describe the upper level by instantiating two components and connecting them with appropriate internal signals.

=> Open your VHDL editor by clicking on *New* in the *Edit* section of the Galaxy window. Copy the following lines into the *new* VHDL file.

```

library ieee;

use ieee.std_logic_1164.all;

use work.binctr_pkg.all;

entity REFILL is port (

GIVE_cola: INOUT std_logic;

GIVE_diet: INOUT std_logic;

REFILL_BINS: OUT std_logic;

RESET: IN std_logic;

CLK: IN std_logic;

GET_diet: IN std_logic;

GET_cola: IN std_logic);

attribute pin_numbers of refill:entity is

" GIVE_cola:2 GIVE_diet:3 REFILL_BINS:4 RESET:10 CLK:13" &

" GET_diet:11 GET_cola:35" ;

```

#### end REFILL;

The first three lines advise the compiler to link to the IEEE VHDL library and the user created binctr\_pkg VHDL package. The compiler finds definitions for the various types, modes, and VHDL constructs defined in the user's VHDL code. In general, the **library** and **use** VHDL reserved words instruct the compiler to include pre-defined libraries and user created VHDL files, in compiling the selected VHDL code. For more information on the std\_logic\_1164 and std\_arith packages, see Chapter 4, "VHDL," in the *Reference Manual*.

The entity declaration declares an entity named refill and defines the names, types, and mode (direction) of its seven input and output ports.

There is also a pin\_numbers assignment attribute which assigns all the signals declared within the entity port map declaration to user specified pin numbers. Refer to Chapter 3, "Synthesis Directives," in the *Reference Manual* for more information on the pin\_numbers attribute.

**Note** – The pin numbers assigned to the signals in this design are specific to the CY7C371 in the PLCC package. If a different package or device is targeted, the numbers would have to be changed appropriately. Alternatively, the pin\_numbers attribute and the pin\_number assignments can be removed.

=> Copy the following lines into your VHDL editor *below* the entity declaration.

```

architecture archREFILL of REFILL is

signal empty_1: std_logic;

signal empty_2: std_logic;

```

begin

```

bin_1: BINCTR

port map(RESET => RESET,

GET_DRINK => GET_cola,

CLK => CLK,

GIVE_DRINK => GIVE_cola,

EMPTY => empty_1);

bin_2: BINCTR

port map(RESET => RESET,

GET_DRINK => GET_diet ,

CLR => CLK,

GIVE_DRINK => GIVE_diet ,

EMPTY => empty_2);

refill_bins <= `1' when ((empty_1 = `1') and (empty_2 = `1'))

else `0';</pre>

```

end archREFILL;

=> Now, save your top-level VHDL file by choosing *Save As* in the *File* menu. Enter **refill.vhd** as the name, then close the file.

The architecture starts by declaring two internal signals, empty\_1 and empty\_2. These are used to connect the outputs of the two binctr components to create the functionality for refill\_bins.

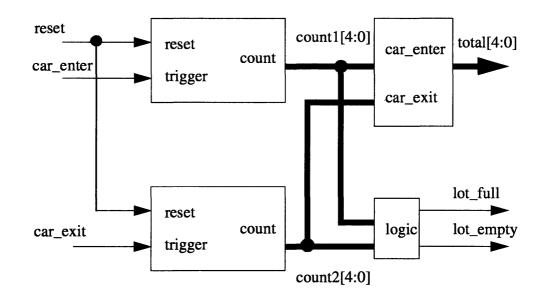

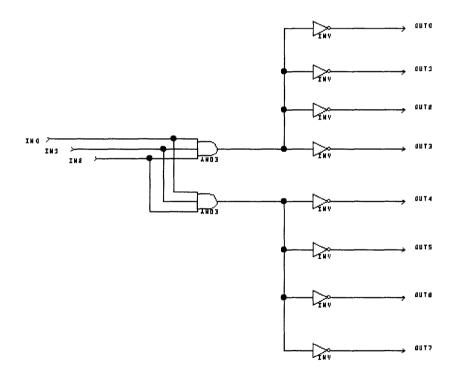

The two instantiations of binctr and the creation of the refill\_bins equation complete the VHDL description of this circuit. With this implementation, you have translated the original vending machine problem into a VHDL design that can be synthesized into any Cypress programmable logic device. The block diagram for *refill.vhd* is shown here:

Figure 3-7 Block Diagram for refill.vhd

The final VHDL window for *refill.vhd* should look as follows:

| c:wv2tutor/refill.vhd                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------|

| library ieee;<br>use ieee.std_logic_1164.all;                                                                                          |

| use work.binctr_pkg.all;<br>entity REFILL is port (                                                                                    |

| GIVE_cola: INOUT std_logic;<br>GIVE_diet: INOUT std_logic;<br>REFILL_BINS: OUT std_logic;                                              |

| RESET: IN std_logic;<br>CLK: IN std_logic;<br>GET_diet: IN std_logic;<br>GET_cola: IN std_logic);                                      |

| attribute pin_numbers of refill:entity is<br>" GIVE_cola:2 GIVE_diet:3 REFILL_BINS:4 RESET:10 CLK:13" &<br>" GET_diet:11 GET_cola:35"; |

| end REFILL;                                                                                                                            |

| architecture archREFILL of REFILL is signal empty_1: std_logic;                                                                        |

|                                                                                                                                        |

Figure 3-8 Final VHDL window for refill.vhd

# 3.8 Compiling and Synthesizing a Top-Level File

The first time you ran *Warp*, earlier in the tutorial, it was simply to verify that the *binctr.vhd* file was syntactically correct.

In the following pages, you'll run *Warp* to produce a JEDEC file for a specific target device (in this case, a CY7C371 - 32 macrocell CPLD).

## 3.8.1 Selecting Files for Compilation

First, you need to add the files you will compile to your project.

=> In your Galaxy window labeled *w2tutor*, click on the *Files* menu and choose the *Add all* option.

Since the only files currently in this project directory are *binctr.vhd* and *refill.vhd*, the two files needed for this tutorial, the *Add all* option is a quick way to add them to the compilation list.

3

If there are other VHDL files in the same directory, you need to do something slightly different:

=> Click on the *Files* menu and choose the *Add* option.

The ensuing dialog box lists the VHDL files available in the current directory on the left side, and the VHDL files selected for compilation or synthesis on the right side (Figure 3-8).

=> Highlight the VHDL file in the left-hand list, and double-click on it or choose and click on the "-->" button. To deselect a file for compilation or synthesis, highlight the VHDL file in the right-hand list and double-click on it or choose and click on the "<--" button. Click on *binctr.vhd* and *refill.vhd* until they are the only files in the right-hand list, then click OK.

|                  | ected:<br>ctr.vhd |

|------------------|-------------------|

| Sel              |                   |

|                  |                   |

| refill.vhd Z bin | ctr.vhd 🗶         |

|                  |                   |

| OK               |                   |

Figure 3-9 Dialog box to add files to your Galaxy window

Back in the main Galaxy window, both *binctr.vhd* and *refill.vhd* should be listed.

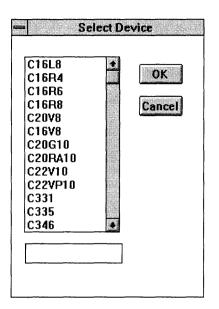

# 3.8.2 Selecting a Device

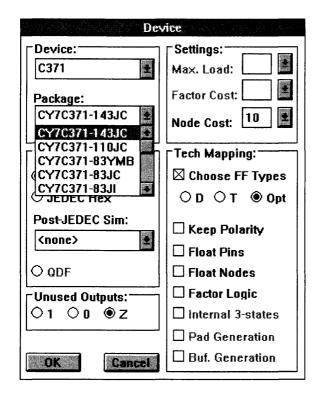

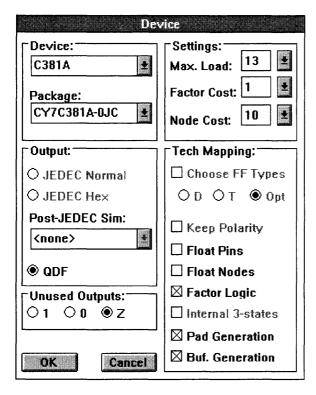

=> Click on the Device button from within the Synthesis options section.

The Device window should appear (Figure 3-9).

=> Click on the down-pointing arrow next to the *Device* label to activate the pull-down menu. Scroll down the menu and select the C371 by clicking on it.

C371 should appear as the targeted device in the lower righthand corner of the main Galaxy window.

# 3.8.3 Selecting a Package and Speed Bin

In addition to selecting the device you wish to target, you can also choose a package type and a speed bin from the list of available packages (Figure 3-10).

Click on the arrow next to the *Package* label to activate the scroll down menu. Scroll down the menu until the your desired package is visible. Select the desired package by clicking on it. For this exercise you should choose the default package and speed bin CY7C371-143JC.

Figure 3-10 Available Package and Speed Bin list

# 3.8.4 Resolving Unused Outputs

*Warp* gives you the option of turning all of your unused output pins that have unused macrocells into '1's, '0's, or 'Z's. This is a global option and cannot be applied on a signal-by-signal basis. This option is useful for driving all unused pins to a certain logic level.

=> Under the *Unused Outputs* options of the Device window, choose *Z*, the default option of leaving all unused I/O pins to be three-stated.

**Note** – When using MAX340 EPLDs and FLASH370 CPLDs, it is a recommended practice to use external pull-ups for unused I/O pins.

# 3.8.5 Choosing Tech Mapping Options

While compiling registered equations, the fitter will use the directive from *Choose FF types* to synthesize equations. Leaving the option *Opt* selected is the best choice. This enables the fitter to make the choice between a D-FF and a T-FF implementation and then choose the implementation that uses the least number of product terms.

=> Under Tech Mapping options in the Device window, choose the Opt option.

There are a few other useful options in the *Tech Mapping* options and the *Settings* options. Refer to Chapter 4, "Galaxy," of this *User's Guide* for a detailed description of each option.

=> Click on the OK button to dismiss the Device window.

# 3.8.6 Setting the Top-Level File

=> Highlight *refill.vhd* by clicking on it.

=> Click on the *Set Top* button in the *Synthesis options* section to assign your top-level VHDL file.

Figure 3-11 Galaxy window showing refill.vhd as the top-level design

*Refill.vhd* should be listed as the top file in the lower left-hand corner of your Galaxy window.

# 3.8.7 Compiling and Synthesizing the File

=> In your Galaxy window, click on the *Smart* button in the *Compile* button group to begin compilation.

*Warp* starts the compilation and synthesis of the design into a CY7C371 and prints messages to keep you appraised of its progress in a pop-up window. The *Smart* compile option automatically recompiles only those files which have been modified since the last compilation.

This operation generates two files of particular interest:

- The first is named *refill.jed*. The *.jed* file can be used to program a CY7C371 device. It is also used as the input to the Nova functional simulator.

- The second file is named *refill.rpt*. It contains pinout and timing information, along with other information about the final synthesized design. You can see the *.rpt* file by pulling down the *Info* menu from the Galaxy window and clicking on *Report*. For more information on what is contained in a report file, refer to Chapter 6, "Report File," in the *Reference Manual*.

- => Close the Galaxy compilation window by clicking on the *Close* button located at the top of the Galaxy compilation window.

**Note** – If compilation errors occur, do the following: make sure the text of your *binctr.vhd* file is entered **exactly** as shown earlier in this chapter -- or better yet, copy it from the *c:\warp\examples\wtutor* directory -- and then run *Warp* again.

If error messages appear in the pop-up window:

- => Highlight the error message by clicking on it.

- => Click on the *Error* button (the icon that looks like a magnifying glass) located at the top of the Galaxy compilation window.

This opens the VHDL editor with the cursor on the line number that contains the error. Check the code you have entered against the text shown earlier in this chapter.

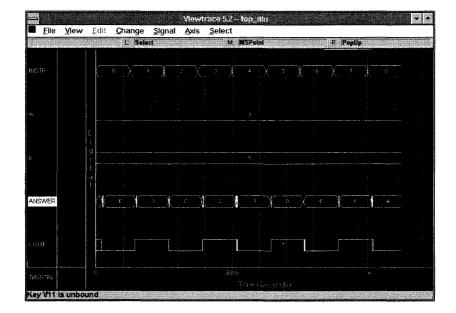

# 3.9 Simulating the Behavior of the Design with Nova

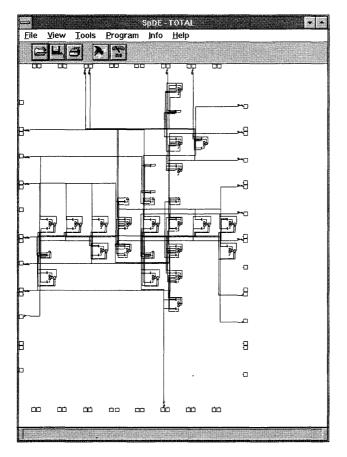

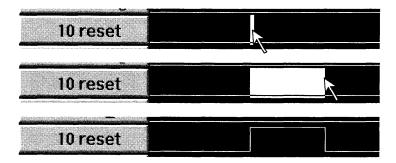

Once the design is synthesized, you must simulate it to verify that it functions as intended. You'll use the Nova simulator to test the behavior of the design. Nova is a simple JEDEC functional simulator. In this tutorial, you'll perform the following steps:

- start Nova

- open the *refill.jed* file

- create a new view and populate it with the signals you're interested in (and only those signals). Typically you would retain and modify the default view

- designate and edit a clock signal

- set the values of the stimulus signals in the simulation

- simulate the design

- examine results to figure out what happened

## 3.9.1 Starting Nova

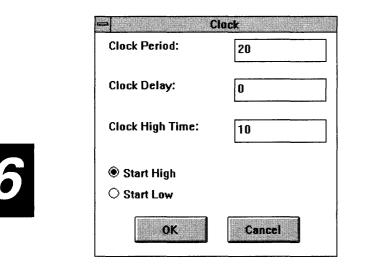

#### For Warp2 Users