# **RISC Family Users Guide**

.

RISC CY7C600 FAMILY USERS GUIDE

# CY7C600 RISC FAMILY USERS GUIDE

# CYPRESS SEMICONDUCTOR

3901 North First St., San Jose, CA 95134 (408) 943-2600 Telex: 821032 CYPRESS SNJ UD, TWX: 910 997 0753, FAX (408) 943-2741

Published June 3, 1988

Cypress Semiconductor and the Cypress logo are trademarks of Cypress Semiconductor Corporation.

SPARC is a trademark of Sun Microsystems, Inc.

UNIX is a registered trademark of AT&T Bell Laboratories.

The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no liability or responsibility for the correctness of any circuitry set forth herein other than circuitry embodied in a Cypress Semiconductor Corporation product. Neither Cypress Semiconductor Corporation nor Sun Microsystems conveys or implies any license under patent, copyright, trademark, or other proprietary rights in conjunction with the use of this User's Guide.

Portions of this manual are reproduced from Sun Microsystems, Inc. documentation, with the permission of Sun Microsystems, Inc.

- © Cypress Semiconductor Corporation, 1988.

- © Sun Microsystems, Inc., 1988. All rights reserved.

| Chapter 1: Introduction                                     | 1–1 |

|-------------------------------------------------------------|-----|

| Scalable Processor Architecture                             | 1–1 |

| What is RISC?                                               | 1–1 |

| RISC Architecture                                           | 1–2 |

| Single-cycle execution                                      | 1–2 |

| Hardwired control with no microcode                         | 1–2 |

| Load/Store, register-to-register design                     | 1–2 |

| Simple fixed-format instructions with few addressing modes  | 1–2 |

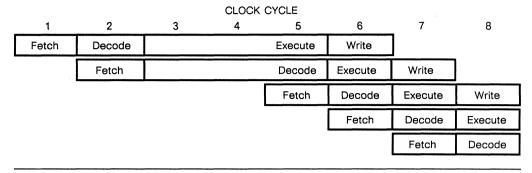

| Pipelining                                                  | 1–2 |

| High-performance memory                                     | 1–2 |

| Migration of functions to software                          | 1–2 |

| Simple, Efficient Instruction Pipeline Visible to Compliers | 1–2 |

| RISC's Speed Advantage                                      | 1-3 |

| CY7C600 Architecture                                        | 1–4 |

| Instruction Categories                                      | 1–4 |

| Load and store instructions (the only way to access memory) | 1–4 |

| Arithmetic/logical/shift instructions                       | 1–4 |

| Floating-Point and Coprocessor nstructions                  | 1-4 |

| Control-transfer instructions                               | 1–4 |

| Read/write control register instructions                    | 1–4 |

| Artificial Intelligence Instructions                        | 1–4 |

| Multiprocessing Instructions                                | 1-5 |

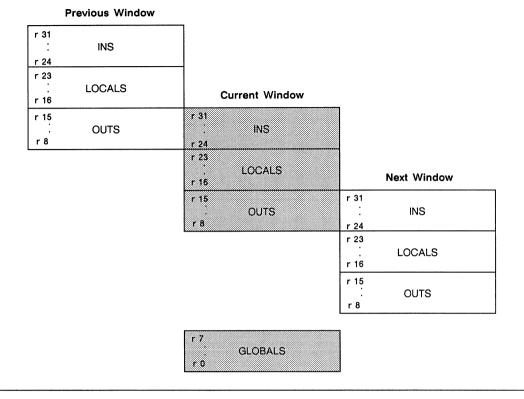

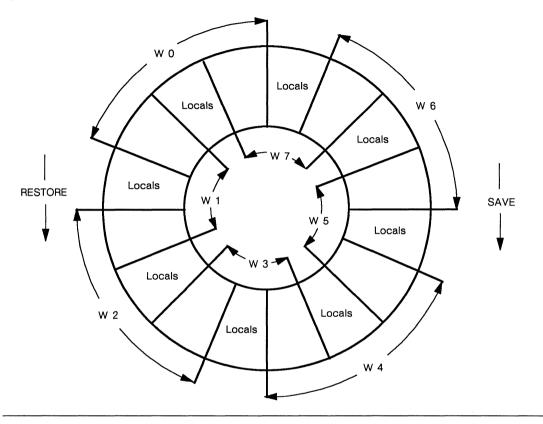

| Register Windows                                            | 1-5 |

| Traps and Interrupts                                        | 1-5 |

| Protection                                                  | 1-5 |

| An Open Architecture                                        | 1-5 |

| Advantages of Open Architecture                             | 1-5 |

| CY7C600 Machines and Other RISC Machines                    | 1-6 |

| CY7C600 Product Family                                      | 1–7 |

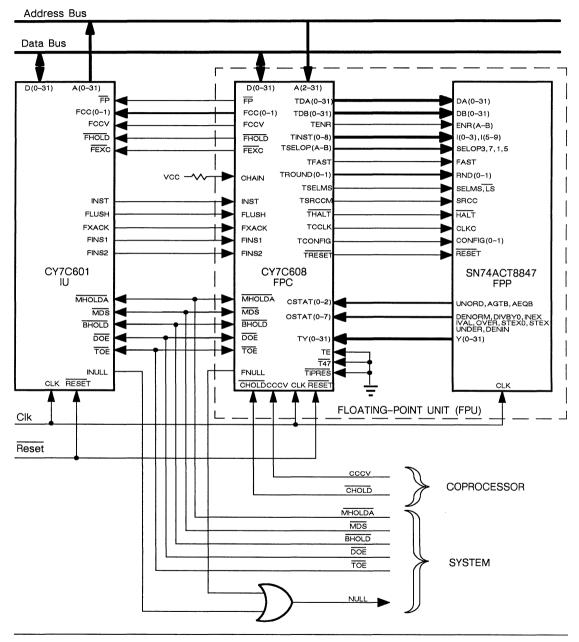

| CY7C601 Integer Unit                                        | 1–7 |

| CY7C603 Memory Management Unit                              | 1–7 |

| CY7C608 Floating-Point Controller                           | 1-8 |

| SN74ACT8847 Floating-Point Processor                        | 1–8 |

| CY7C181 Cache Tag RAM                                       | 1-8 |

| CY7C153 Cache Data RAM                                      | 1–9 |

| Chapter 2. CV7C601 Architecture                             | 0 1 |

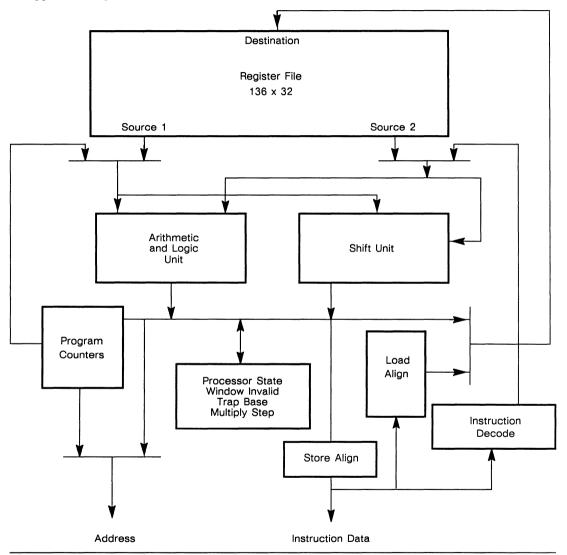

| Chapter 2: CY7C601 Architecture                             |     |

| Overview                                                    |     |

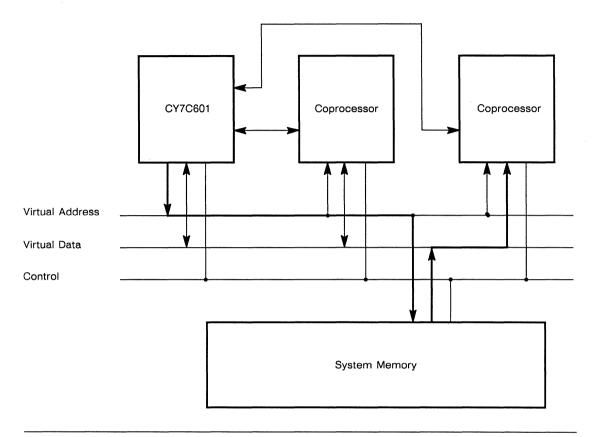

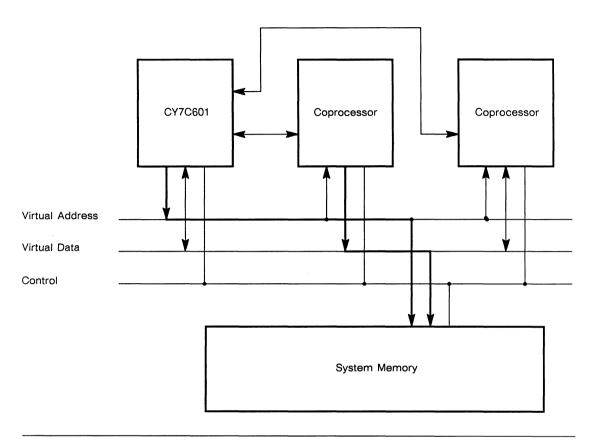

| Integer Unit, Floating-Point Unit, and Coprocessor          |     |

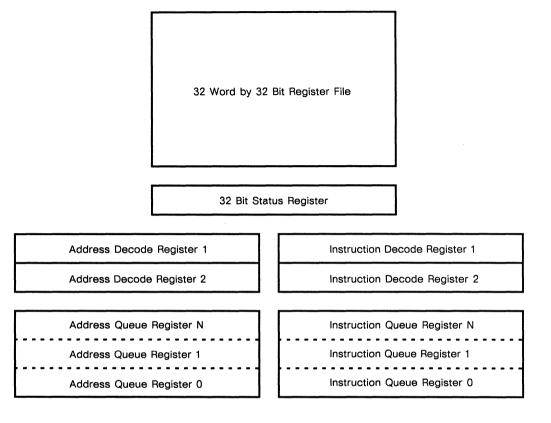

| Registers                                                   | 2-4 |

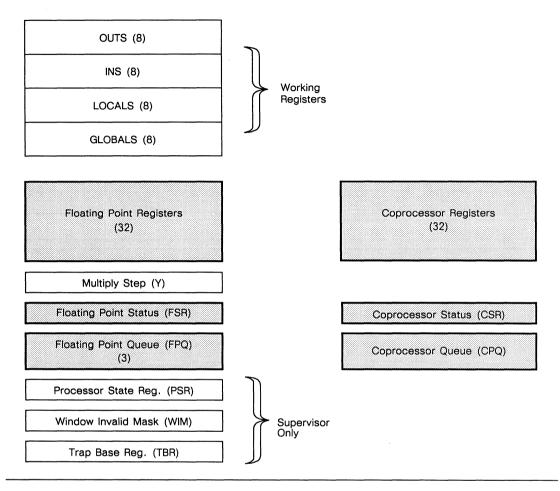

| Integer Unit Registers                              | 2-5  |

|-----------------------------------------------------|------|

| Special r Registers                                 | 2–7  |

| Integer Unit Control/Status Registers               | 2-8  |

| Integer Program Counters (PC and nPC)               | 2-8  |

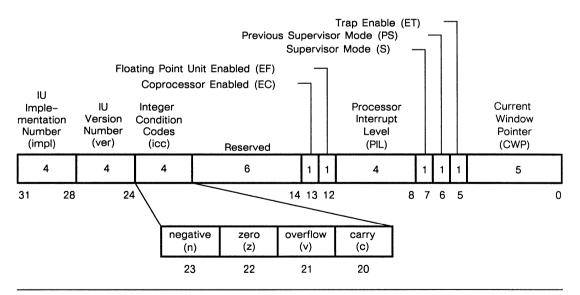

| Processor State Register (PSR)                      | 2–8  |

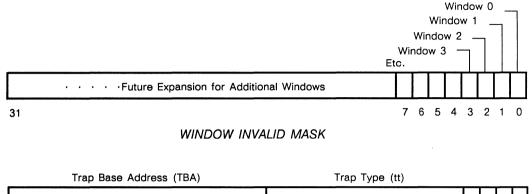

| Window Invalid Mask Register (WIM)                  | 2-10 |

| Trap Base Register (TBR)                            | 2–11 |

| Y Register                                          | 2-11 |

| Floating-Point Registers                            | 2-11 |

| Floating-Point f registers                          | 2-12 |

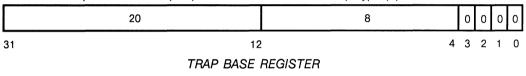

| Floating-Point State Register (FSR)                 | 2-12 |

| Floating-Point Queue (FQ)                           | 2-15 |

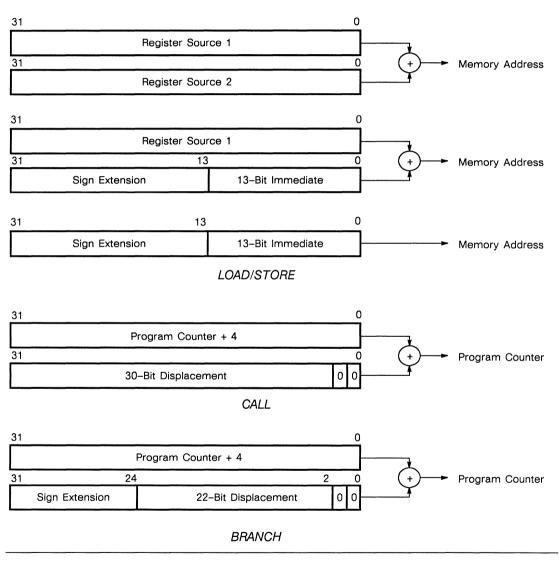

| Addressing                                          | 2-16 |

| Instruction Set                                     | 2-18 |

| Instruction Format                                  | 2-18 |

| Load and Store Instructions                         | 2-20 |

| Address Space Identifier                            | 2-20 |

| Arithmetic/Logical/Shift                            | 2–21 |

| Register 0                                          | 2–21 |

| Shift                                               | 2-21 |

| SETHI                                               | 2–21 |

| Tagged Arithmetic                                   | 2-21 |

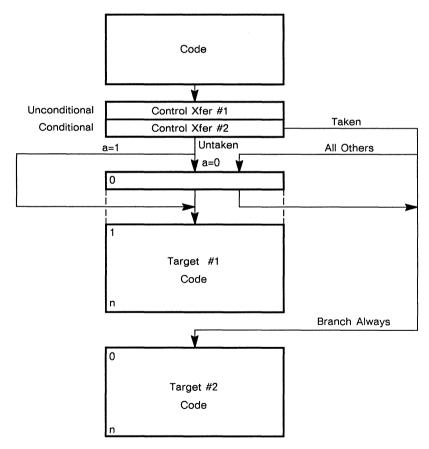

| Control-Transfer Instructions                       | 2–22 |

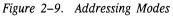

| Delayed Control Transfer                            | 2–23 |

| PC and nPC                                          | 2-23 |

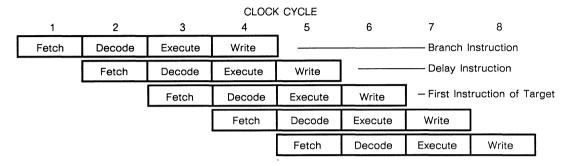

| Delay Instruction                                   | 2-23 |

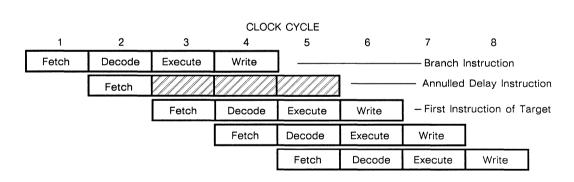

| Annul Bit                                           | 2-24 |

| Calls and Returns                                   | 2–26 |

| Trap Instruction                                    | 2–27 |

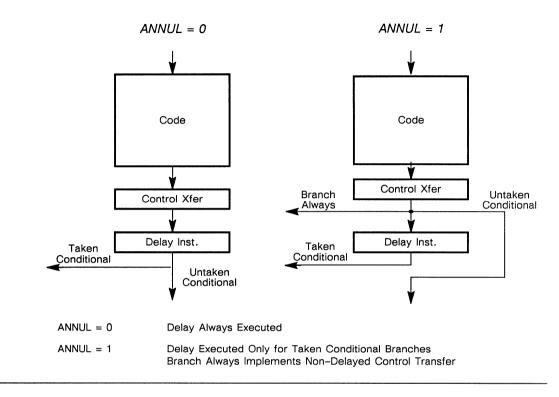

| Delayed Control Transfer Couples                    | 2-27 |

| Read/Write Control Registers                        | 2–29 |

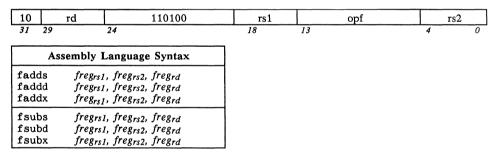

| Floating-point and Coprocessor Operate Instructions | 2–29 |

| Condition Codes                                     | 2–29 |

| Processor Pipeline                                  | 2-33 |

| Processor Data Types                                | 2-34 |

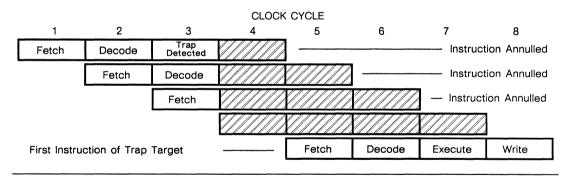

| Traps                                               | 2-35 |

| Chapter 3: Pipeline Operation                       | 3–1  |

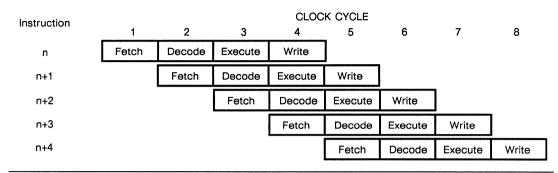

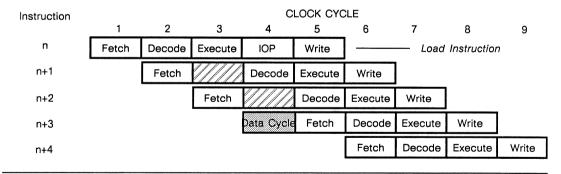

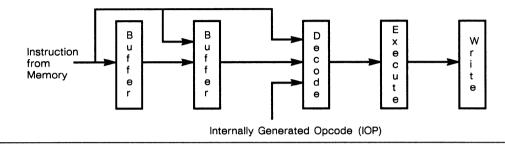

| Pipeline Stages                                     | 3–1  |

| Single Cycle Instructions                           |      |

| Internally Generated Opcodes                 | 3-2<br>3-2<br>3-4<br>3-4<br>3-5 |

|----------------------------------------------|---------------------------------|

| Traps                                        | 3–6                             |

| Chapter 4: Interrupts, Traps, and Exceptions | 4–1                             |

| Trap Categories                              | 4–1                             |

| Synchronous Traps                            | 4–1                             |

| Asynchronous Traps                           | 4–1                             |

| Trap Addressing                              | 4–2                             |

| Trap Types and Priorities                    | 4–2                             |

| Trap Operation                               | 4-3                             |

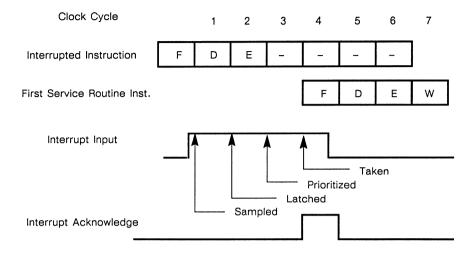

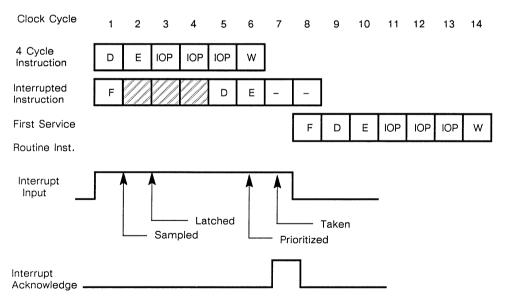

| Interrupt Detection                          | 4-3                             |

| Interrupt Response Timing                    | 4-3                             |

| Interrupt Acknowledge                        | 4–5                             |

| Floating-Point/Coprocessor Exception Traps   | 4-5                             |

| Trap Descriptions                            | 4–5                             |

| Reset                                        | 4–5                             |

| Illegal Instruction                          | 4-6                             |

| Privileged Instruction                       | 4-6                             |

| Floating-Point Disabled                      | 4-6                             |

| Coprocessor Disabled                         | 4-6                             |

| Window Overflow                              | 4-6                             |

| Window Underflow                             | 4–6                             |

| Memory Address not Aligned                   | 4–7                             |

| Floating-Point Exception                     | 4–7                             |

| Coprocessor Exception                        | 4-7                             |

| Data Access Exception                        | 4-7                             |

| Tag Overflow                                 | 4–7                             |

| Trap Instruction                             | 4-7                             |

| Interrupt Level                              | 4–7                             |

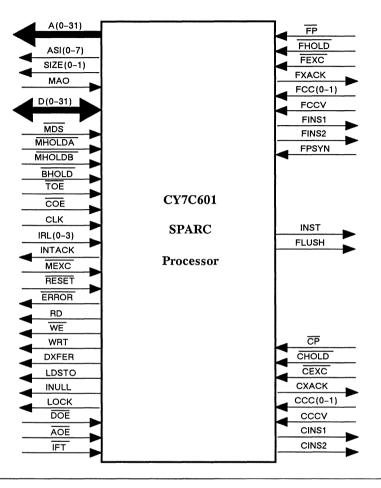

| Chapter 5: Pin Description                   | 5-1                             |

| Memory Subsystem Interface Signals           | 5-1                             |

|                                              | 5-1                             |

| ASI[7:0] Address Space Identifier            | 5-1                             |

| D[31:0] Data Bus                             | 5-2                             |

|                                              | 5-3                             |

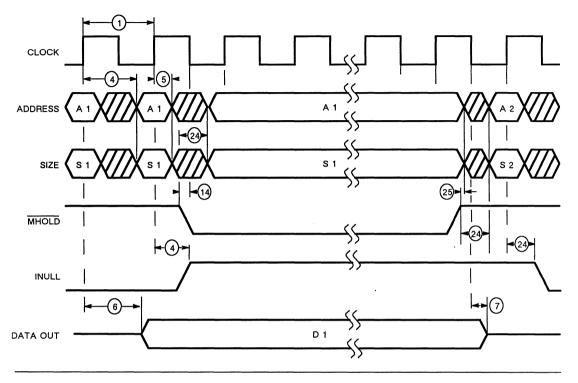

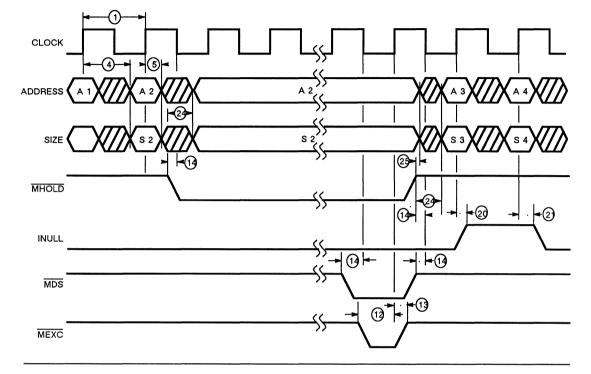

| MHOLD (A/B) Memory Holds                           | . 5–3 |

|----------------------------------------------------|-------|

| BHOLD Bus Hold                                     |       |

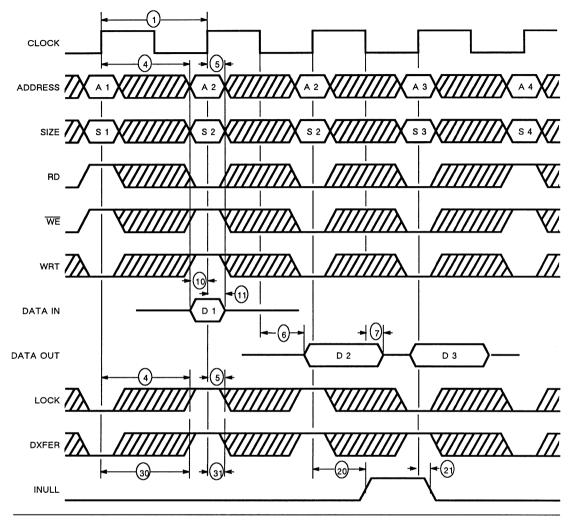

| MDS Memory Data Strobe                             |       |

| MEXC Memory Exception                              |       |

| MAO Memory Address Output                          |       |

| AOE Address Output Enable                          |       |

| DOE Data Output Enable                             |       |

| COE Control Output Enable                          |       |

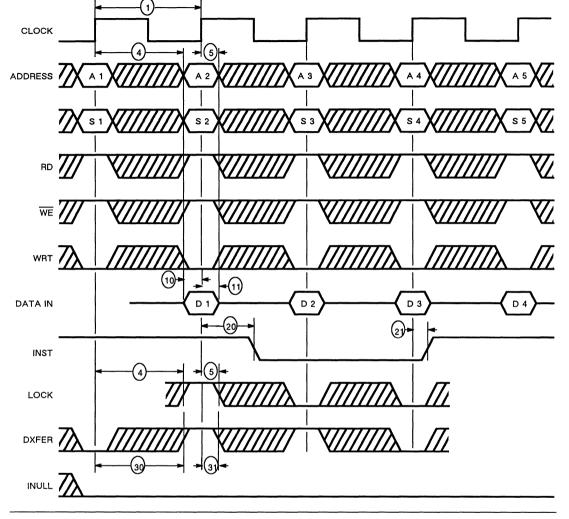

| RD Read                                            |       |

| WE Write Enable                                    |       |

| WRT Advanced Write                                 |       |

| LDSTO Load/Store                                   |       |

| LOCK                                               |       |

| DXFER Data Transfer                                | . 5–5 |

| INULL Integer Unit Nullify Cycle                   | . 5–6 |

| IFT Instruction Cache Flush Trap                   |       |

| Floating-Point/Coprocessor Interface Signals       |       |

| FP Floating-Point Unit Present                     |       |

| CP Coprocessor Unit Present                        |       |

| FCC[1:0] Floating-Point Condition Codes            |       |

| CCC[1:0] Coprocessor Condition Codes               |       |

| FCCV Floating-Point Condition Codes Valid          |       |

| CCCV Coprocessor Condition Codes Valid             |       |

| FHOLD Floating-Point Hold                          |       |

| CHOLD Coprocessor Hold                             |       |

| FEXC Floating-Point Exception                      |       |

| CEXC Coprocessor Exception                         |       |

| INST Instruction Fetch                             |       |

| FLUSH Floating-Point/Coprocessor Instruction Flush |       |

| FINS1 Floating-Point Instruction in Buffer 1       |       |

| FINS2 Floating-Point Instruction in Buffer 2       |       |

| CINS1 Coprocessor Instruction in Buffer 1          |       |

| CINS2 Coprocessor Instruction in Buffer 2          |       |

| FXACK Floating-Point Exception Acknowledge         |       |

| CXACK Coprocessor Exception Acknowledge            |       |

| Miscellaneous I/O Signals                          |       |

| IRL[3:0] Interrupt Request Level                   |       |

| INTACK Interrupt Acknowledge                       | . 5–9 |

-

| RESET Integer Unit Reset       Integer Unit Reset         ERROR Error State       Integer Unit Enable         TOE Test Mode Output Enable       Integer Unit Synonym Mode         FPSYN Floating-Point Synonym Mode       Integer Unit Synonym Mode         CLK Clock       Integer Unit Synonym Mode | 5-9<br>5-9<br>5-9<br>5-9<br>5-9 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

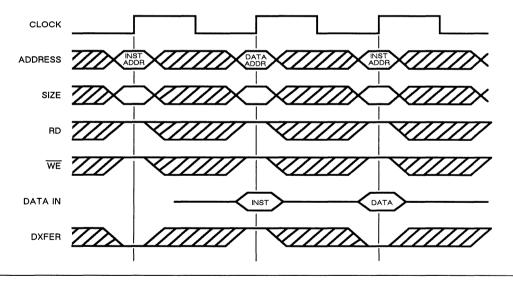

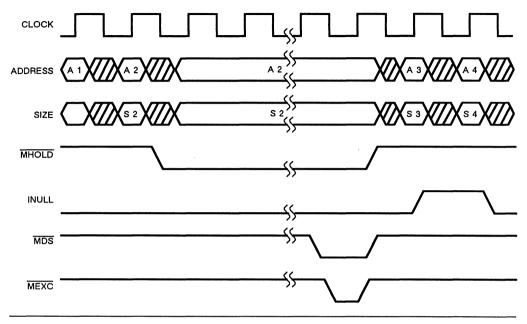

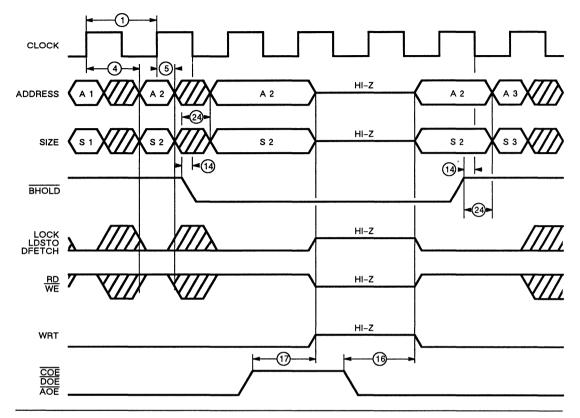

| Chapter 6: Bus Operation                                                                                                                                                                                                                                                                              | 6–1                             |  |

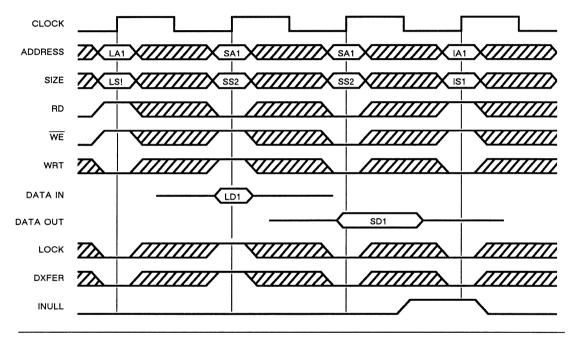

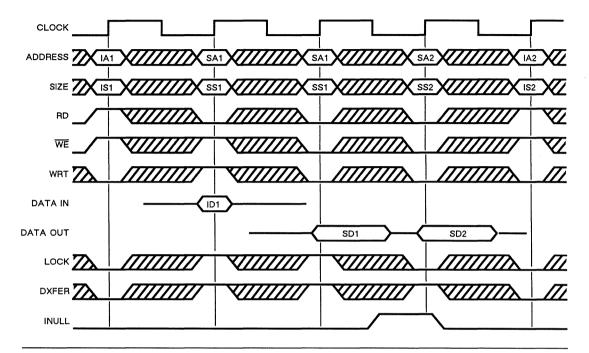

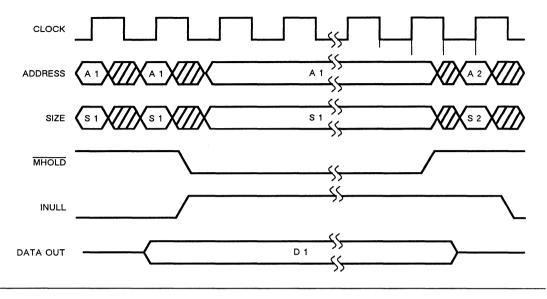

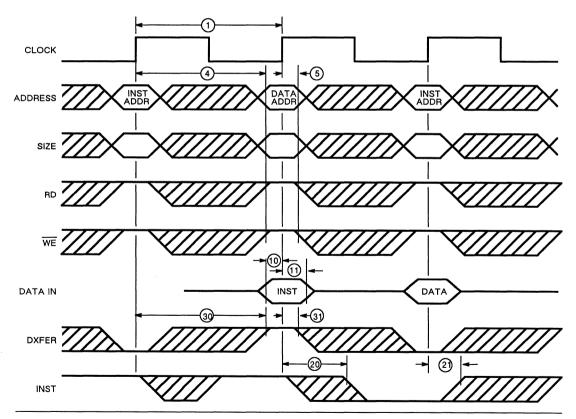

| Instruction Fetch                                                                                                                                                                                                                                                                                     | 6-1                             |  |

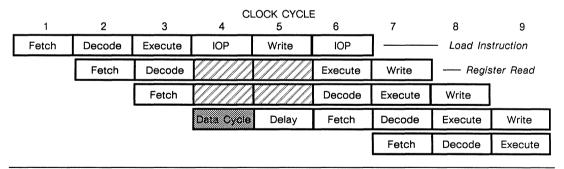

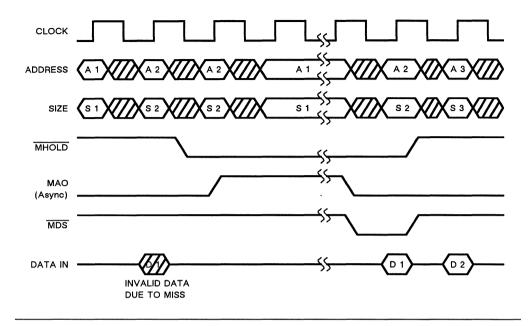

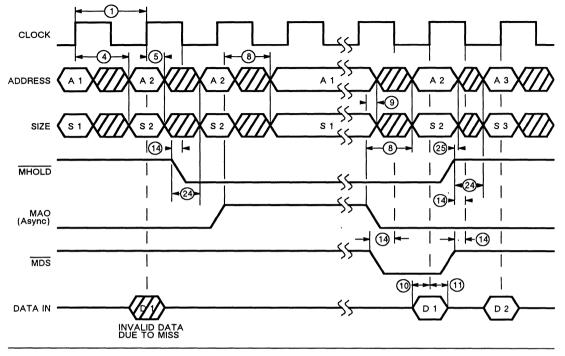

| Load Transactions                                                                                                                                                                                                                                                                                     | 6-2                             |  |

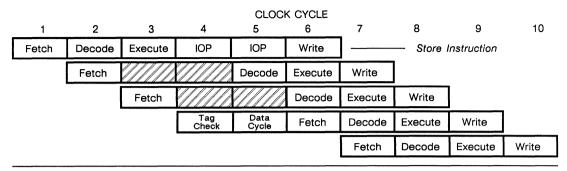

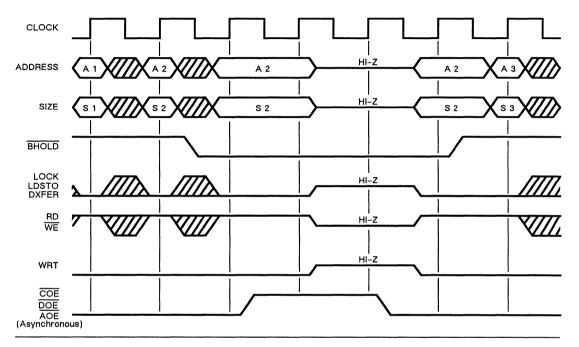

| Store Transactions                                                                                                                                                                                                                                                                                    | 6-2                             |  |

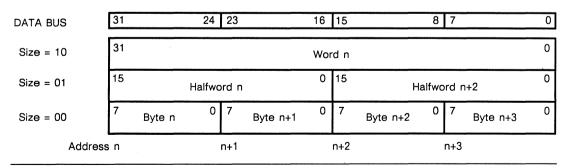

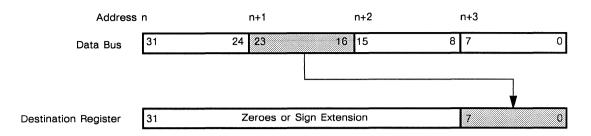

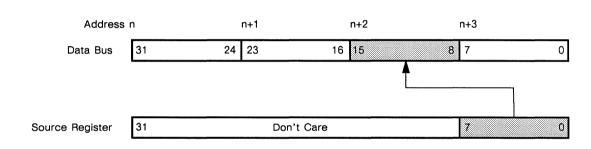

| Data Bus Contents                                                                                                                                                                                                                                                                                     | 6-4                             |  |

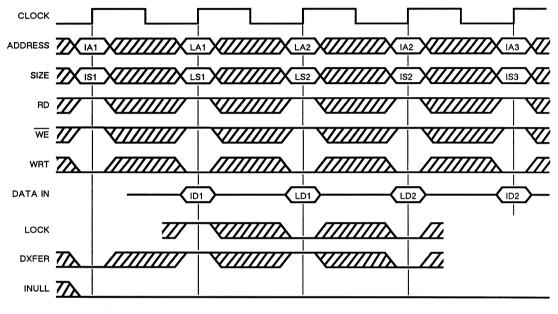

| Atomic Transactions                                                                                                                                                                                                                                                                                   | 6–5                             |  |

| Floating-Point Operations                                                                                                                                                                                                                                                                             | 6-6                             |  |

| Bus Arbitration                                                                                                                                                                                                                                                                                       | 6-6                             |  |

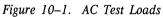

| Reset Operation                                                                                                                                                                                                                                                                                       | 6–7                             |  |

|                                                                                                                                                                                                                                                                                                       |                                 |  |

| Chapter 7: Memory Interface                                                                                                                                                                                                                                                                           | 7–1                             |  |

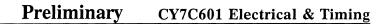

| Memory Wait States                                                                                                                                                                                                                                                                                    | 7–1                             |  |

| Cache Memory Systems                                                                                                                                                                                                                                                                                  |                                 |  |

| Memory Exceptions                                                                                                                                                                                                                                                                                     | 7–3                             |  |

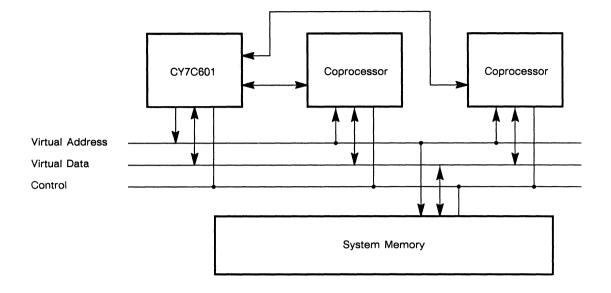

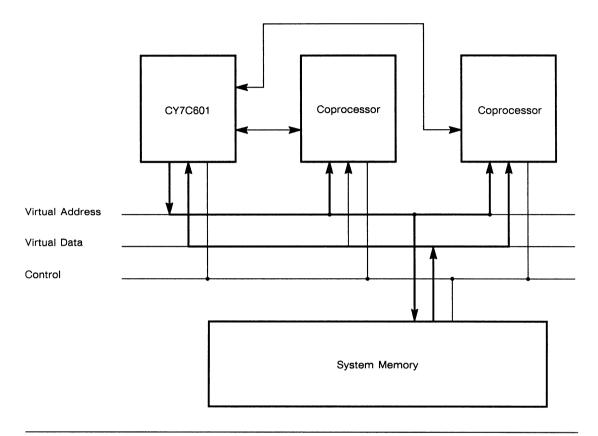

| Chapter 8: CY7C601 Coprocessor Interface                                                                                                                                                                                                                                                              | 8-1                             |  |

| Concept of a Coprocessor                                                                                                                                                                                                                                                                              | 8-1                             |  |

| Concurrency                                                                                                                                                                                                                                                                                           | 8-1                             |  |

| Synchronization                                                                                                                                                                                                                                                                                       | 8-1                             |  |

| Coprocessor Interface                                                                                                                                                                                                                                                                                 | 8-1                             |  |

| Coprocessor Operations                                                                                                                                                                                                                                                                                | 8-6                             |  |

| Coprocessor Compare Operations                                                                                                                                                                                                                                                                        | 8-7                             |  |

| Unimplemented Coprocessor Instructions                                                                                                                                                                                                                                                                | 8-8                             |  |

| Unfinished Coprocessor instruction                                                                                                                                                                                                                                                                    | 8-8                             |  |

| Chapter 9: CY7C601 Design Examples                                                                                                                                                                                                                                                                    | 9-1                             |  |

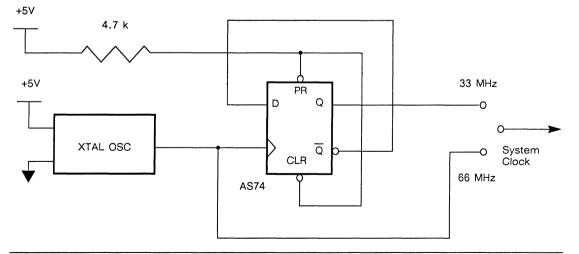

| Clocking The CY7C601 IU                                                                                                                                                                                                                                                                               | 9–1                             |  |

| Clock Parameters                                                                                                                                                                                                                                                                                      |                                 |  |

|                                                                                                                                                                                                                                                                                                       | 9-1                             |  |

| Clock Generation                                                                                                                                                                                                                                                                                      | 9–1<br>9–2                      |  |

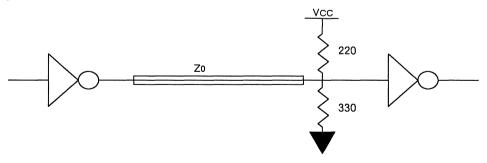

| Parallel Termination                                                                                                                                                                                                                                                                                  |                                 |  |

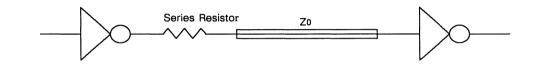

| Series Termination                                                                                                                                                                                                                                                                                    |                                 |  |

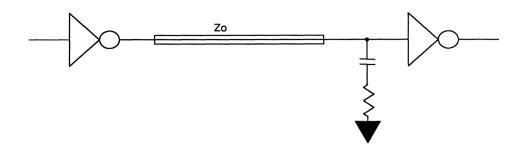

| AC Termination                                                                                                                                                                                                                                                                                        | 9-3<br>9-3                      |  |

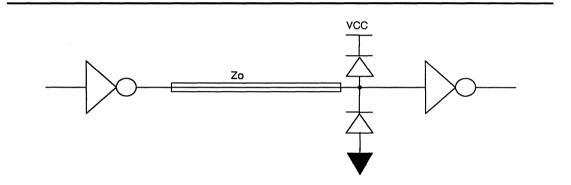

| Diode Termination                                                                                                                                                                                                                                                                                     |                                 |  |

|                                                                                                                                                                                                                                                                                                       | フーゴ                             |  |

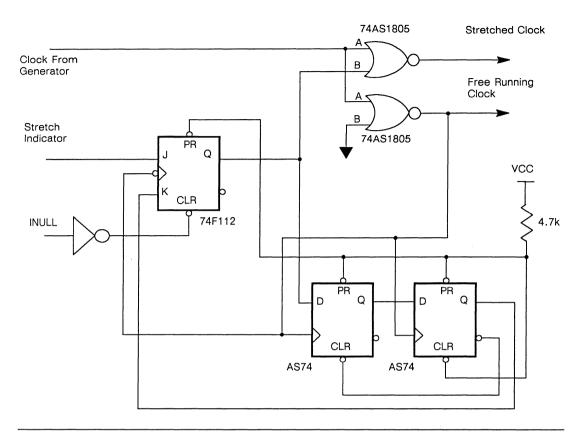

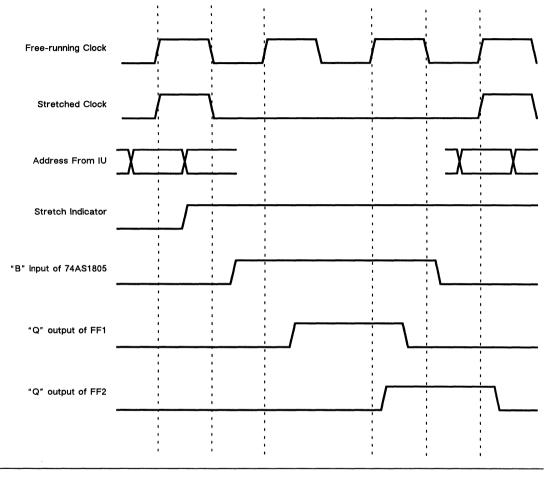

| Clock Stretching                         | 9–3   |

|------------------------------------------|-------|

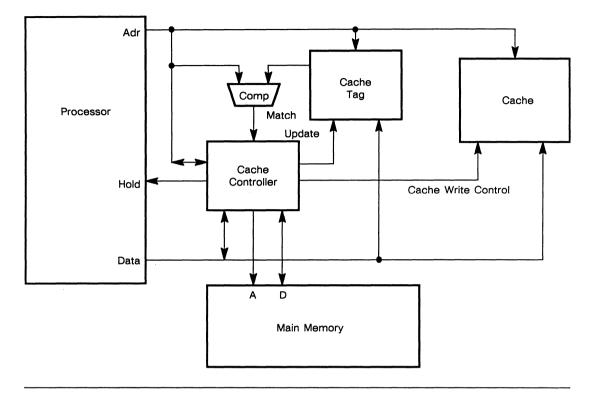

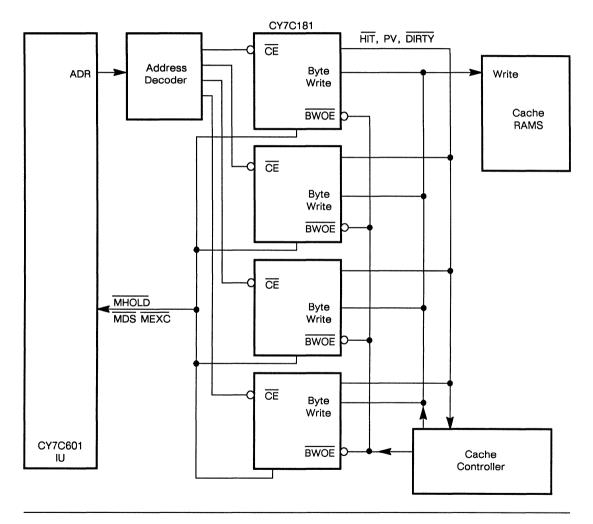

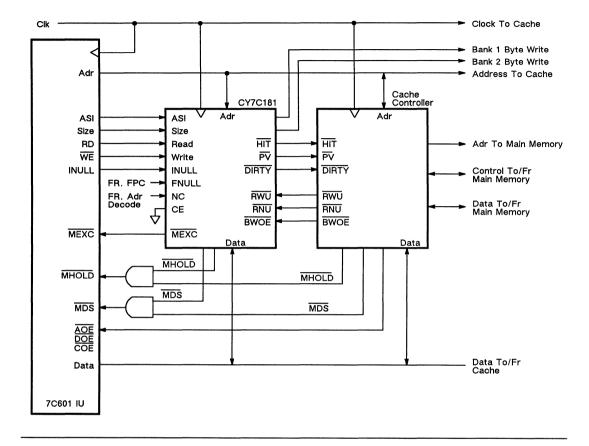

| Cache Design in a CY7C601 System         | 9–7   |

| Building Blocks of a Cache System        | 9–7   |

| Cache Memory Operations                  | 9–8   |

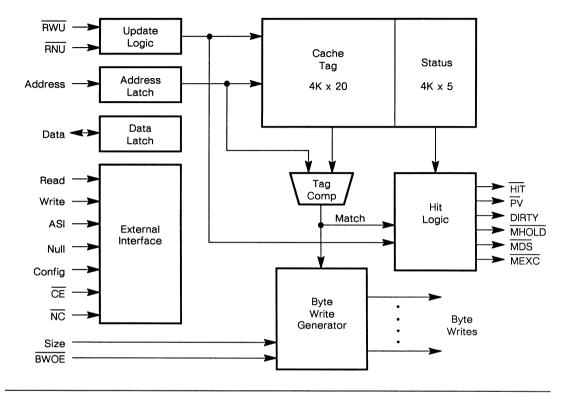

| Cypress Cache Support Chips              | 9–9   |

| The CY7C181 Cache Tag RAM                | 9–9   |

| Processing an IU Cache Memory Access     | 9–10  |

| Access Protection                        | 9–11  |

| Caching Policy                           | 9–11  |

| Tag Invalidation                         | 9–11  |

| Byte Write Generation                    | 9–11  |

| Cascading the CY7C181                    | 9–12  |

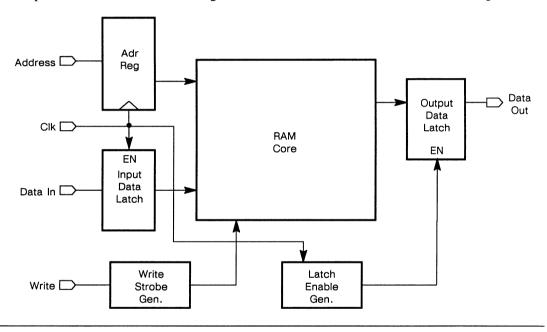

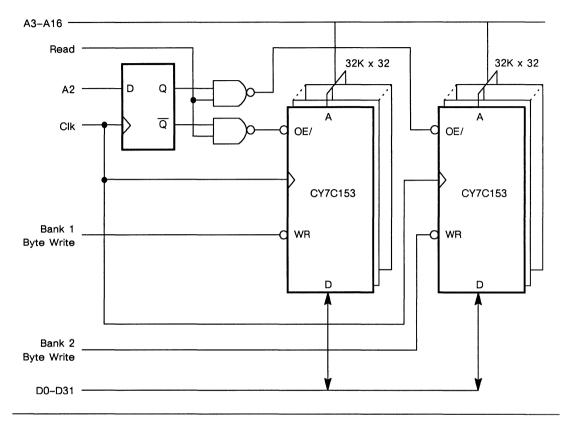

| The CY7C153 Cache RAM                    | 9–13  |

| Functional Description of a Sample Cache | 9–13  |

|                                          | 9-15  |

| Read Accesses                            | 9–15  |

| Write Accesses                           | 9–16  |

| Summary                                  | 9–17  |

| Memory Design                            | 9–    |

|                                          | 9–    |

| Eprom Section                            | 9-    |

| Static RAM Second Edition                | 9–    |

| Dynamic RAM Second Edition               | 9-    |

|                                          | 9-    |

| I/O Design Second Edition                |       |

| Timer Counter Second Edition             | 9-    |

|                                          |       |

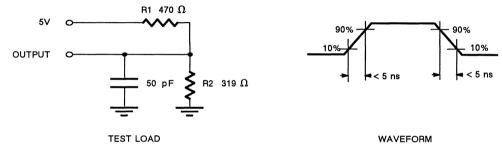

| Chapter 10: CY7C601 Electrical & Timing  | 10-1  |

| Operating Range                          | 10-1  |

| Maximum Ratings                          | 10-1  |

| Electrical Characteristics               | 10-1  |

|                                          | 10-2  |

|                                          | 10-2  |

|                                          | 10-2  |

|                                          | 10-3  |

| Switching Characteristics Continued      | 10-4  |

| Military Specifications                  | 10-12 |

| Group A Subgroup Testing                 | 10-12 |

| Switching Characteristics                | 10-12 |

|                                          | 10-12 |

.....

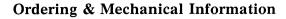

| Chapter 11: Ordering and Mechanical Information       | 11–1 |  |  |

|-------------------------------------------------------|------|--|--|

| Chapter 12: Programming Considerations Second Edition | 12–1 |  |  |

| Chapter 13: Development Environment Second Edition    | 13–1 |  |  |

| Appendix A: Assemby Language Syntax                   |      |  |  |

| Register Names                                        | A-1  |  |  |

| Special Symbol Names                                  | A-2  |  |  |

| Values                                                | A-2  |  |  |

| Label                                                 | A-2  |  |  |

| Appendix B: Instruction Definitions                   |      |  |  |

| Load Integer Instructions                             | B-3  |  |  |

| Load Floating-Point Instructions                      | B-4  |  |  |

| Load Coprocessor Instructions                         | B-6  |  |  |

| Store Integer Instructions                            | B7   |  |  |

| Store Floating-Point Instructions                     | B-8  |  |  |

| Store Coprocessor Instructions                        | B-9  |  |  |

| Atomic Load-Store Unsigned Byte Instructions          |      |  |  |

| SWAP r Register with Memory                           |      |  |  |

| Add Instructions                                      |      |  |  |

| Tagged Add Instructions                               |      |  |  |

| Subtract Instructions                                 |      |  |  |

| Multiply Step Instruction                             |      |  |  |

| Logical Instructions                                  |      |  |  |

| Shift Instructions                                    | B-17 |  |  |

| SETHI Instruction                                     | B-18 |  |  |

| SAVE and RESTORE Instructions                         | B-19 |  |  |

| Branch on Integer Condition Instructions              | B-20 |  |  |

| Floating-Point Branch on Condition Instructions       | B-21 |  |  |

| Coprocessor Branch on Condition Instructions          |      |  |  |

| CALL Instruction                                      |      |  |  |

| Jump and Link Instruction                             |      |  |  |

| Return from Trap Instruction                          |      |  |  |

| Trap on Integer Condition Instruction                 | B-27 |  |  |

| Read State Register Instructions                      | B-28 |  |  |

| Write State Register Instructions                     | B-29 |  |  |

| Unimplemented Instruction                             |      |  |  |

| Instruction Cache Flush Instruction I                 |      |  |  |

\_\_\_\_

| Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Traps       C-11         Instruction Definitions       C-13         Load Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-19         Swap r Register with Memory Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-22         Tagged Subtract Instructions       C-22         Multiply Step Instruction       C-23         Logical Instructions       C-23         Shift Instructions       C-23         Shift Instructions       C-24                                                                                                                                                                                                                                                                                                                                                                     |                                                 |      |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|--|--|

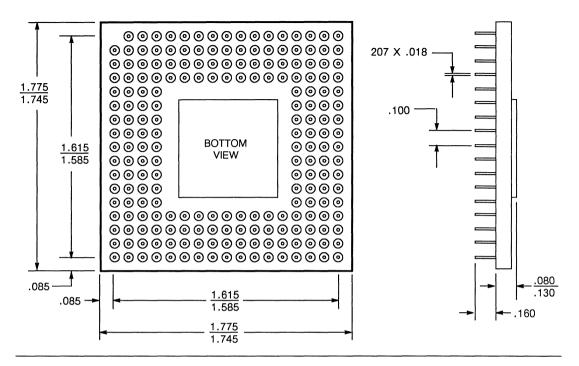

| Convert Floating-Point to IntegerB-33Convert Between Floating-Point Formats InstructionsB-34Floating-Point Move InstructionsB-35Floating-Point Add and Subtract InstructionsB-36Floating-Point Multiply and Divide InstructionsB-37Floating-Point Compare InstructionsB-37Coprocessor Operate InstructionsB-37Coprocessor Operate InstructionsC-1Register DefinitionsC-2System Interface DefinitionsC-4Instruction FieldsC-4Instruction FieldsC-4Instruction FieldsC-4Instruction DispatchC-6Floating-Point Queue (FQ)C-9FQ_Front_DoneC-10FPU StatesC-10Coprocessor Instruction ExecutionC-11Instruction DefinitionsC-11Instruction DefinitionsC-12System Interface DefinitionsC-22YatesC-10Processor States and Instruction FetchC-4Instruction DispatchC-6Floating-Point Queue (FQ)C-9FQ_Front_DoneC-10Coprocessor Instruction ExecutionC-11Instruction DefinitionsC-14Store InstructionsC-14Store InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Shift InstructionsC-22Shift InstructionsC-23Shift Instructions <t< td=""><td>Floating-Point Operate (FPop) Instructions</td><td>B-31</td></t<>                                             | Floating-Point Operate (FPop) Instructions      | B-31 |  |  |

| Convert Between Floating-Point Formats Instructions       B-34         Floating-Point Move Instructions       B-35         Floating-Point Add and Subtract Instructions       B-35         Floating-Point Multiply and Divide Instructions       B-37         Floating-Point Compare Instructions       B-37         Floating-Point Compare Instructions       B-37         Coprocessor Operate Instructions       B-37         Coprocessor Operate Instructions       B-38         Appendix C: ISP Descriptions       C-4         Register Definitions       C-4         Instruction Fields       C-4         Instruction Fields       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Instruction Execution       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-14         Store Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-20         Atomic Load-Store Unsigned Byte Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-21         Subtract Instructions       C-22 | Convert Integer to Floating-Point Instructions  |      |  |  |

| Floating-Point Move Instructions       B-35         Floating-Point Square Root Instructions       B-35         Floating-Point Add and Subtract Instructions       B-36         Floating-Point Multiply and Divide Instructions       B-37         Floating-Point Compare Instructions       B-37         Coprocessor Operate Instructions       B-37         Coprocessor Operate Instructions       B-38         Appendix C: ISP Descriptions       C-1         Register Definitions       C-2         System Interface Definitions       C-4         Instruction Fields       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         Coprocessor Instruction Execution       C-11         Instruction Definitions       C-11         Instructions       C-14         Store Instructions       C-10         Coprocessor Instructions       C-10         Store Instructions       C-10         Store Instructions       C-20         Add Instructions       C-20      <                        | Convert Floating-Point to Integer               | B-33 |  |  |

| Floating-Point Square Root Instructions       B-35         Floating-Point Add and Subtract Instructions       B-36         Floating-Point Multiply and Divide Instructions       B-37         Floating-Point Compare Instructions       B-37         Coprocessor Operate Instructions       B-37         Appendix C: ISP Descriptions       C-1         Register Definitions       C-2         System Interface Definitions       C-4         Instruction Fields       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-6         Floating-Point Instruction Execution       C-7         FPU States       C-10         Coprocessor Instruction Execution       C-10         FU States       C-10         Coprocessor Instruction Execution       C-10         FU States       C-10         Coprocessor Instructions       C-11         Instruction Definitions       C-13         Load Instructions       C-14         Store Instructions       C-10         Codd Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-22         Tagged Subt                                    |                                                 |      |  |  |

| Floating-Point Add and Subtract Instructions       B-36         Floating-Point Multiply and Divide Instructions       B-37         Floating-Point Compare Instructions       B-37         Coprocessor Operate Instructions       B-38         Appendix C: ISP Descriptions       C-1         Register Definitions       C-2         System Interface Definitions       C-4         Instruction Fields       C-4         Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         Coprocessor Instruction Execution       C-11         Traps       C-11         Instruction Definitions       C-14         Store Instructions       C-10         Coprocessor Instructions       C-11         Traps       C-11         Store Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-22         Multiply Step Instructions       C-22         Auditipl                                    | Floating-Point Move Instructions                | B-35 |  |  |

| Floating-Point Multiply and Divide Instructions       B-37         Floating-Point Compare Instructions       B-37         Coprocessor Operate Instructions       B-38         Appendix C: ISP Descriptions       C-1         Register Definitions       C-2         System Interface Definitions       C-4         Instruction Fields       C-4         Instruction Dispatch       C-4         Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Traps       C-10         Load Instructions       C-12         Atomic Load-Store Unsigned Byte Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-21         Tagged Subtract Instructions       C-22         Multiply Step Instructions       C-22         Multiply Step Instructions       C-22         Shift Instructions       C-23         Shift Instruc                                    | Floating-Point Square Root Instructions         | B-35 |  |  |

| Floating-Point Compare Instructions       B-37         Coprocessor Operate Instructions       B-38         Appendix C: ISP Descriptions       C-1         Register Definitions       C-2         System Interface Definitions       C-4         Instruction Fields       C-4         Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-11         Coprocessor Instruction Execution       C-11         Traps       C-10         Coprocessor Instructions       C-10         Store Instructions       C-14         Store Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Tagged Subtract Instructions       C-22         Multiply Step Instructions       C-22         Multiply Step Instructions       C-22         Shift Instructions       C-23         Shift Instructions       C-24                                                                                             | Floating-Point Add and Subtract Instructions    | B-36 |  |  |

| Coprocessor Operate Instructions       B-38         Appendix C: ISP Descriptions       C-1         Register Definitions       C-2         System Interface Definitions       C-4         Instruction Fields       C-4         Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Instruction Execution       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instructions       C-11         Instruction Definitions       C-11         Instruction Definitions       C-10         Coprocessor Instructions       C-10         Coprocessor Instructions       C-11         Instruction Definitions       C-11         Instructions       C-12         Add Instructions       C-14         Store Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-22         Tagged Subtract Instructions       C-22         Multiply Step Instruction       C-23         Logical Instructions       C-23                                                                          | Floating-Point Multiply and Divide Instructions | B-37 |  |  |

| Appendix C: ISP Descriptions       C-1         Register Definitions       C-2         System Interface Definitions       C-4         Instruction Fields       C-4         Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-4         Floating-Point Instruction Execution       C-6         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Instruction Definitions       C-13         Load Instructions       C-14         Store Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-21         Tagged Subtract Instructions       C-22         Tagged Subtract Instructions       C-22         Multiply Step Instruction       C-22         Shift Instructions       C-22         Shift Instructions       C-22                                                                                                                                                                                         | Floating-Point Compare Instructions             | B-37 |  |  |

| Register Definitions       C-2         System Interface Definitions       C-4         Instruction Fields       C-4         Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-4         Instruction Definition Execution       C-6         Floating-Point Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Traps       C-11         Instruction Definitions       C-13         Load Instructions       C-14         Store Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Tagged Subtract Instructions       C-22         Multiply Step Instruction       C-23         Logical Instructions       C-23         Shift Instructions       C-24                                                                                        | Coprocessor Operate Instructions                | B-38 |  |  |

| System Interface Definitions       C-4         Instruction Fields       C-4         Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Instruction Definitions       C-13         Load Instructions       C-14         Store Instructions       C-19         Swap r Register with Memory Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-22         Tagged Subtract Instructions       C-22         Multiply Step Instruction       C-23         Logical Instructions       C-22         Shift Instructions       C-22                                                                                                                                                                                                                                                                                                                                 | Appendix C: ISP Descriptions                    | C-1  |  |  |

| Instruction Fields       C-4         Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Traps       C-11         Instruction Definitions       C-13         Load Instructions       C-14         Store Instructions       C-19         Swap r Register with Memory Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-22         Tagged Subtract Instructions       C-22         Multiply Step Instruction       C-23         Logical Instructions       C-22                                                                                                                                                                                                                                                                                                                                                                                             | Register Definitions                            | C-2  |  |  |

| Processor States and Instruction Fetch       C-4         Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Traps       C-11         Instruction Definitions       C-13         Load Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-19         Swap r Register with Memory Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-22         Tagged Subtract Instructions       C-22         Multiply Step Instruction       C-23         Logical Instructions       C-23         Shift Instructions       C-23         Shift Instructions       C-24                                                                                                                                                                                                                                                                                                                                                                     | System Interface Definitions                    | C-4  |  |  |

| Instruction Dispatch       C-6         Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Traps       C-11         Instruction Definitions       C-13         Load Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-20         Add Instructions       C-21         Swap r Register with Memory Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-22         Tagged Subtract Instructions       C-23         Logical Instructions       C-23         Shift Instructions       C-23         Shift Instructions       C-24                                                                                                                                                                                                                                                      | Instruction Fields                              | C-4  |  |  |

| Floating-Point Instruction Execution       C-8         Floating-Point Queue (FQ)       C-9         FQ_Front_Done       C-10         FPU States       C-10         Coprocessor Instruction Execution       C-11         Traps       C-11         Instruction Definitions       C-13         Load Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-21         Subtract Instructions       C-22         Tagged Subtract Instructions       C-22         Multiply Step Instructions       C-23         Logical Instructions       C-23         Shift Instructions       C-23         Shift Instructions       C-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Processor States and Instruction Fetch          | C-4  |  |  |

| Floating-Point Queue (FQ)C-9FQ_Front_DoneC-10FPU StatesC-10Coprocessor Instruction ExecutionC-11TrapsC-11Instruction DefinitionsC-13Load InstructionsC-14Store InstructionsC-16Atomic Load-Store Unsigned Byte InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-23Logical InstructionsC-23Shift InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Instruction Dispatch                            | C-6  |  |  |

| FQ_Front_DoneC-10FPU StatesC-10Coprocessor Instruction ExecutionC-11TrapsC-11Instruction DefinitionsC-13Load InstructionsC-14Store InstructionsC-16Atomic Load-Store Unsigned Byte InstructionsC-19Swap r Register with Memory InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-23Logical InstructionsC-23Shift InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Floating-Point Instruction Execution            | C-8  |  |  |

| FPU States       C-10         Coprocessor Instruction Execution       C-11         Traps       C-11         Instruction Definitions       C-13         Load Instructions       C-14         Store Instructions       C-16         Atomic Load-Store Unsigned Byte Instructions       C-19         Swap r Register with Memory Instructions       C-20         Add Instructions       C-21         Tagged Add Instructions       C-22         Tagged Subtract Instructions       C-22         Multiply Step Instructions       C-23         Logical Instructions       C-23         Shift Instructions       C-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Floating-Point Queue (FQ)                       | C-9  |  |  |

| Coprocessor Instruction ExecutionC-11TrapsC-11Instruction DefinitionsC-13Load InstructionsC-14Store InstructionsC-16Atomic Load-Store Unsigned Byte InstructionsC-19Swap r Register with Memory InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionsC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FQ_Front_Done                                   | C-10 |  |  |

| TrapsC-11Instruction DefinitionsC-13Load InstructionsC-14Store InstructionsC-16Atomic Load-Store Unsigned Byte InstructionsC-19Swap r Register with Memory InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionsC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FPU States                                      | C-10 |  |  |

| Instruction DefinitionsC-13Load InstructionsC-14Store InstructionsC-16Atomic Load-Store Unsigned Byte InstructionsC-19Swap r Register with Memory InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionsC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Coprocessor Instruction Execution               | C-11 |  |  |

| Load InstructionsC-14Store InstructionsC-16Atomic Load-Store Unsigned Byte InstructionsC-19Swap r Register with Memory InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Traps                                           | C-11 |  |  |

| Store InstructionsC-16Atomic Load-Store Unsigned Byte InstructionsC-19Swap r Register with Memory InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Instruction Definitions                         | C-13 |  |  |

| Atomic Load-Store Unsigned Byte InstructionsC-19Swap r Register with Memory InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Load Instructions                               | C-14 |  |  |

| Swap r Register with Memory InstructionsC-20Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Store Instructions                              | C-16 |  |  |

| Add InstructionsC-21Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Atomic Load-Store Unsigned Byte Instructions    | C-19 |  |  |

| Tagged Add InstructionsC-21Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Swap r Register with Memory Instructions        | C-20 |  |  |

| Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Add Instructions                                | C-21 |  |  |

| Subtract InstructionsC-22Tagged Subtract InstructionsC-22Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Tagged Add Instructions                         | C-21 |  |  |

| Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |      |  |  |

| Multiply Step InstructionC-23Logical InstructionsC-23Shift InstructionsC-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Tagged Subtract Instructions                    | C-22 |  |  |

| Logical Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Shift Instructions                              | C-24 |  |  |

| SETHI Instruction C-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SETHI Instruction                               | C-24 |  |  |

| SAVE and RESTORE Instructions C-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SAVE and RESTORE Instructions                   | C-24 |  |  |

| Branch on Integer Condition Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |      |  |  |

| Floating-Point Branch on Condition Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |      |  |  |