# 8-Bit Embedded Controller Handbook

#### LITERATURE

To order Intel Literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your local sales office or distributor.

INTEL LITERATURE SALES P.O. BOX 58130 SANTA CLARA, CA 95052-8130 In the U.S. and Canada call toll free (800) 548-4725

#### **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| TITLE                                                                                    | LITERATURE<br>ORDER NUMBER |

|------------------------------------------------------------------------------------------|----------------------------|

| COMPLETE SET OF HANDBOOKS (Available in U.S. and Canada only)                            | 231003                     |

| AUTOMOTIVE PRODUCTS HANDBOOK (Not included in handbook set)                              | 231792                     |

| COMPONENTS QUALITY/RELIABILITY HANDBOOK                                                  | 210997                     |

| EMBEDDED CONTROL APPLICATIONS HANDBOOK                                                   | 270648                     |

| 8-BIT EMBEDDED CONTROLLER HANDBOOK                                                       | 270645                     |

| 16-BIT EMBEDDED CONTROLLER HANDBOOK                                                      | 270646                     |

| 32-BIT EMBEDDED CONTROLLER HANDBOOK                                                      | 270647                     |

| MEMORY COMPONENTS HANDBOOK                                                               | 210830                     |

| MICROCOMMUNICATIONS HANDBOOK                                                             | 231658                     |

| MICROCOMPUTER PROGRAMMABLE LOGIC HANDBOOK                                                | 296083                     |

| MICROPROCESSOR AND PERIPHERAL HANDBOOK (2 volume set)                                    | 230843                     |

| MILITARY PRODUCTS HANDBOOK (2 volume set. Not included in handbook set)                  | 210461                     |

| OEM BOARDS AND SYSTEMS HANDBOOK                                                          | 280407                     |

| PRODUCT GUIDE (Overview of Intel's complete product lines)                               | 210846                     |

| SYSTEMS QUALITY/RELIABILITY HANDBOOK                                                     | 231762                     |

| INTEL PACKAGING OUTLINES AND DIMENSIONS (Packaging types, number of leads, etc.)         | 231369                     |

| LITERATURE PRICE LIST (U.S. and Canada) (Comprehensive list of current Intel Literature) | 210620                     |

| INTERNATIONAL LITERATURE GUIDE                                                           | E00029                     |

CG/LIT/100188

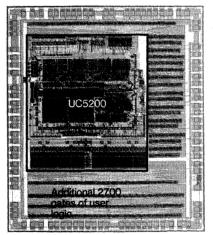

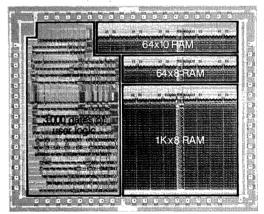

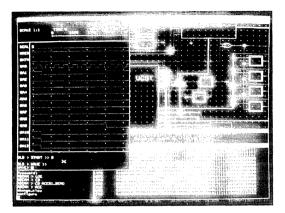

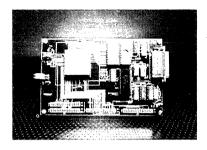

About Our Cover:

As the inventor of the 8-bit embedded architecture that leads the market, Intel has provided the basis for over 50% of all 8-bit embedded controllers today. From simple consumer products to complex peripherals, our 8-bit controllers provide new venues for mold-breaking technological development.

### U.S. and CANADA LITERATURE ORDER FORM

| NAME:                                                                    |                                                                                                                |                                                                                            |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| COMPANY:                                                                 |                                                                                                                |                                                                                            |

| ADDRESS:                                                                 |                                                                                                                |                                                                                            |

| CITY:                                                                    | ST/                                                                                                            | ATE: ZIP:                                                                                  |

| COUNTRY:                                                                 |                                                                                                                |                                                                                            |

| PHONE NO.: ( )                                                           |                                                                                                                |                                                                                            |

| ORDER NO.                                                                | TITLE                                                                                                          | QTY. PRICE TOTAL                                                                           |

|                                                                          |                                                                                                                | ×=-                                                                                        |

|                                                                          |                                                                                                                | ×=                                                                                         |

|                                                                          |                                                                                                                | ×=                                                                                         |

|                                                                          | ·                                                                                                              | ×=                                                                                         |

|                                                                          | gana and a state of the state of | X=                                                                                         |

|                                                                          |                                                                                                                | ×=                                                                                         |

|                                                                          |                                                                                                                | ×=                                                                                         |

|                                                                          |                                                                                                                | ×=                                                                                         |

|                                                                          | ·                                                                                                              | ×=                                                                                         |

|                                                                          |                                                                                                                | ×=                                                                                         |

|                                                                          |                                                                                                                | Subtotal                                                                                   |

| <b></b>                                                                  |                                                                                                                | Must Add Your<br>Local Sales Tax                                                           |

| Postage: add 10% of st                                                   | ubtotal                                                                                                        | Postage                                                                                    |

| accept VISA, MasterCard or Alfor delivery.                               | r include company purchase order w<br>merican Express. Make payment to I<br>erican Express Expiration Date     | Total<br>vith this form (\$100 minimum).We also<br>intel Literature Sales. Allow 2-4 weeks |

|                                                                          | ZAPITATION DATE                                                                                                |                                                                                            |

| Signature                                                                |                                                                                                                |                                                                                            |

| Mail To: Intel Literature Sales<br>P.O. Box 58130<br>Santa Clara, CA 950 | should use the Intern                                                                                          | tomers outside the U.S. and Canada national order form or contact their local ibutor.      |

For phone orders in the U.S. and Canada Call Toll Free: (800) 548-4725

Prices good until 12/31/89. Source HB

### INTERNATIONAL LITERATURE ORDER FORM

| NAME:           |                               |

|-----------------|-------------------------------|

| ÇOMPANY:        |                               |

| ADDRESS:        |                               |

| CITY:           | STATE: ZIP:                   |

| COUNTRY:        |                               |

| PHONE NO.: ( )  |                               |

| ORDER NO. TITLE | QTY. PRICE TOTAL              |

|                 | ×=_                           |

|                 | ×=                            |

|                 | =_                            |

|                 |                               |

|                 | X=                            |

|                 |                               |

|                 |                               |

|                 | X=                            |

|                 |                               |

|                 | X=                            |

|                 | X=                            |

| •               | Subtotal                      |

|                 | Must Add Your Local Sales Tax |

|                 | Total                         |

#### **PAYMENT**

Cheques should be made payable to your local Intel Sales Office (see inside back cover.)

Other forms of payment may be available in your country. Please contact the Literature Coordinator at your local Intel Sales Office for details.

The completed form should be marked to the attention of the LITERATURE COORDINATOR and returned to your local Intel Sales Office.

Intel the Microcomputer Company:

When Intel invented the microprocessor in 1971, it created the era of microcomputers. Whether used as microcontrollers in automobiles or microwave ovens, or as personal computers or supercomputers, Intel's microcomputers have always offered leading-edge technology. In the second half of the 1980s, Intel architectures have held at least a 75% market share of microprocessors at 16 bits and above. Intel continues to strive for the highest standards in memory, microcomputer components, modules, and systems to give its customers the best possible competitive advantages.

## 8-BIT EMBEDDED CONTROLLER HANDBOOK

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, ETOX, FASTPATH, Genius, i,  $\hat{i}$ , ICE, iCEL, iCS, iDBP, iDIS, I2ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Inboard, Insite, Intel, int<sub>e</sub>l, Intel376, Intel386, Intel486, int<sub>e</sub>IBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, OTP, PC BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Erase, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM. MCS. or UPI and a numerical suffix, 4-SITE, 376, 386, 486.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

#### **CUSTOMER SUPPORT**

#### INTEL'S COMPLETE SUPPORT SOLUTION WORLDWIDE

Customer Support is Intel's complete support service that provides Intel customers with hardware support, software support, customer training, consulting services and network management services. For detailed information contact your local sales offices.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. As you might expect, Intel's customer support is quite extensive. It can start with assistance during your development effort to network management. 100 Intel sales and service offices are located worldwide — in the U.S., Canada, Europe and the Far East. So wherever you're using Intel technology, our professional staff is within close reach.

#### HARDWARE SUPPORT SERVICES

Intel's hardware maintenance service, starting with complete on-site installation will boost your productivity from the start and keep you running at maximum efficiency. Support for system or board level products can be tailored to match your needs, from complete on-site repair and maintenance support economical carry-in or mail-in factory service.

Intel can provide support service for not only Intel systems and emulators, but also support for equipment in your development lab or provide service on your product to your end-user/customer.

#### SOFTWARE SUPPORT SERVICES

Software products are supported by our Technical Information Phone Service (TIPS) that has a special toll free number to provide you with direct, ready information on known, documented problems and deficiencies, as well as work-arounds, patches and other solutions.

Intel's software support consists of two levels of contracts. Standard support includes TIPS (Technical Information Phone Service), updates and subscription service (product-specific troubleshooting guides and; *COMMENTS Magazine*). Basic support consists of updates and the subscription service. Contracts are sold in environments which represent product groupings (e.g., iRMX® environment).

#### **CONSULTING SERVICES**

Intel provides field system engineering consulting services for any phase of your development or application effort. You can use our system engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training and customizing an Intel product to providing technical and management consulting. Systems Engineers are well versed in technical areas such as microcommunications, real-time applications, embedded microcontrollers, and network services. You know your application needs; we know our products. Working together we can help you get a successful product to market in the least possible time.

#### CUSTOMER TRAINING

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to ten days a limited number of individuals learn more in a single workshop than in weeks of self-study. For optimum convenience, workshops are scheduled regularly at Training Centers worldwide or we can take our workshops to you for on-site instruction. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>TM</sup> and LAN applications.

#### NETWORK MANAGEMENT SERVICES

Today's networking products are powerful and extremely flexible. The return they can provide on your investment via increased productivity and reduced costs can be very substantial.

Intel offers complete network support, from definition of your network's physical and functional design, to implementation, installation and maintenance. Whether installing your first network or adding to an existing one, Intel's Networking Specialists can optimize network performance for you.

### **Table of Contents**

| Alphanumeric Index                                                | ×            |

|-------------------------------------------------------------------|--------------|

| MCS®-48 FAMILY                                                    |              |

| Chapter 1                                                         |              |

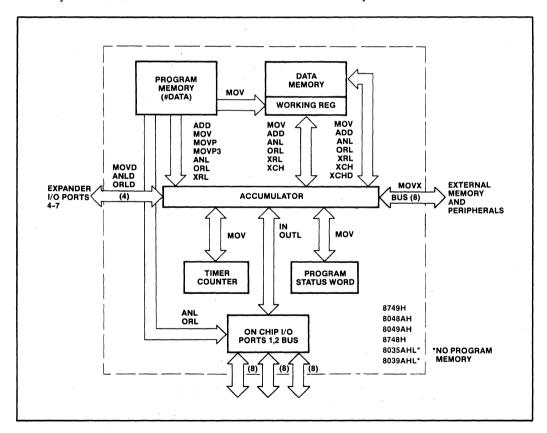

| MCS®-48 Single Component System                                   | 1-1          |

| Chapter 2                                                         |              |

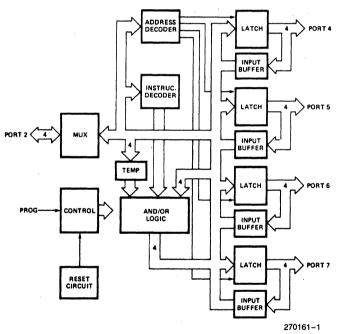

| MCS®-48 Expanded System                                           | 2-1          |

| Chapter 3                                                         |              |

| MCS®-48 Instruction Set                                           | 3-1          |

| Chapter 4                                                         |              |

| MCS®-48 DATA SHEETS                                               |              |

| 8243 MCS®-48 Input/Output Expander                                | 4-1          |

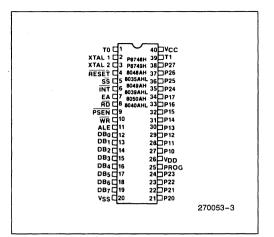

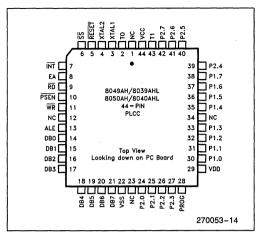

| P8748H/P8749H/8048AH/8035AHL/8049AH/8039AHL/8050AH/8040AHL        |              |

| HMOS 8-Bit Microcontroller                                        | 4-8          |

| D8748H/8749H HMOS-E Single-Component 8-Bit Microcomputer          | 4-21         |

| MCS®-48 Express                                                   | 4-33         |

| MCS®-51 FAMILY                                                    |              |

| Chapter 5                                                         |              |

| MCS®-51 Architectural Overview                                    | 5-1          |

| Chapter 6                                                         |              |

| MCS®-51 Programmer's Guide and Instruction Set                    | 6-1          |

| Chapter 7                                                         |              |

| Using the Intel MCS®-51 Boolean Processing Capabilities           | 7-1          |

| Chapter 8                                                         |              |

| Hardware Description of the 8051, 8052 and 80C51                  | 8-1          |

| DATA SHEETS                                                       |              |

| 8031/8051/8031AH/8051AH/8032AH/8052AH/8751H/8751-8 8-Bit HMOS and |              |

| HMOS EPROM Microcontroller                                        | 8-35         |

| 8051AHP 8-Bit Microcontroller with Protected ROM                  | 8-49         |

| 8031AH/8051AH/8032AH/8751H/8751H-8 Express                        | 8-59         |

| 8751BH 8-Bit HMOS EPROM Microcontroller                           | 8-61<br>8-73 |

| 8752BH Express                                                    | 8-85         |

| 80C31BH/80C51BH 8-Bit CHMOS Microcontroller                       | 8-87         |

| 80C31BH/80C51BH Express                                           | 8-100        |

| 80C51 BHP 8-Bit CHMOS Microcontroller with Protected ROM          | 8-102        |

| 87C51 8-Bit CHMOS EPROM Microcontroller                           | 8-115        |

| 87C51 Express                                                     | 8-129        |

| Chapter 9                                                         |              |

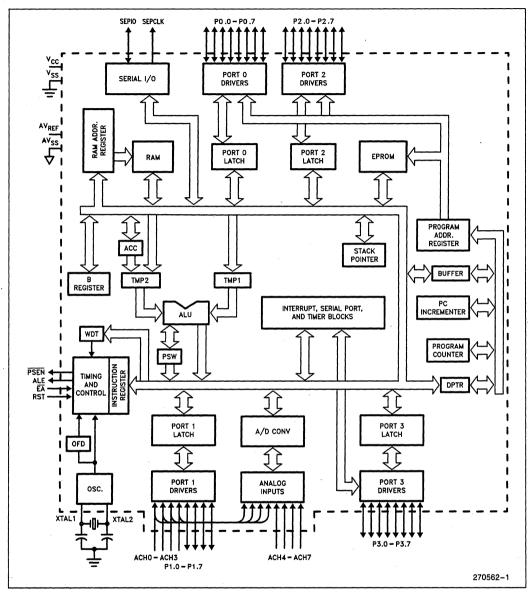

| Hardware Description of the 83C51FA/FB                            | 9-1          |

| DATA SHEETS                                                       |              |

| 83C51FA 8-Bit CHMOS Microcontroller                               | 9-43         |

| 83C51FA Express                                                   | 9-57         |

| 87C51FA 8-Bit CHMOS Microcontroller                               | 9-59<br>9-75 |

| 83C51FB 8-Bit CHMOS Microcontroller                               | 9-75<br>9-78 |

| 87C51FB 8-Bit CHMOS Microcontroller                               | 9-91         |

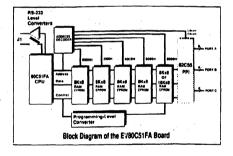

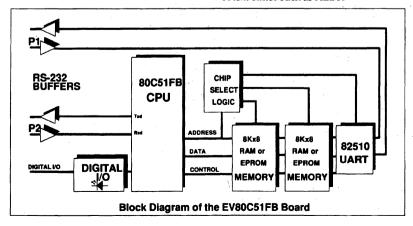

| EV80C51FA Microcontroller Evaluation Board Fact Sheet             | 9-107        |

| EV80C51FB Microcontroller Evaluation Board Fact Sheet             | 9-109        |

| Chapter 10                                                        |              |

| Hardware Description of the 8XC51GA                               | 10-1         |

| DATA SHEET                                                        |              |

| 87C51GA 8-Bit CHMOS Microcontroller                               | 10-12        |

# Table of Contents (Continued)

| DATA SHEETS 8XC152 JA/JB/JC/JD Communication Controller 18XC152 JA/JB/JC/JD Express 1  Chapter 12 Hardware Description of the 8XC451 DATA SHEET 8XC451 8-Bit CHMOS Microcontroller  Chapter 13 UPITM-452 CHMOS Programmable I/O Processor  Chapter 14 DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 87C75PF Microcontroller Peripheral I/O Port Expander  1 Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages | 11-1<br>11-69<br>11-85<br>12-1<br>12-5<br>13-1<br>14-1<br>4-25<br>15-1 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 8XC152 JA/JB/JC/JD Communication Controller 8XC152 JA/JB/JC/JD Express 1  Chapter 12 Hardware Description of the 8XC451 DATA SHEET 8XC451 8-Bit CHMOS Microcontroller  Chapter 13 UPITM-452 CHMOS Programmable I/O Processor  Chapter 14 DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 87C75PF Microcontroller Peripheral I/O Port Expander  1 Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages              | 12-1<br>12-5<br>13-1<br>14-1<br>14-25                                  |

| 8XC152 JA/JB/JC/JD Express 1  Chapter 12 Hardware Description of the 8XC451 DATA SHEET 8XC451 8-Bit CHMOS Microcontroller  Chapter 13 UPITM-452 CHMOS Programmable I/O Processor  Chapter 14 DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 187C75PF Microcontroller Peripheral I/O Port Expander  Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                           | 12-1<br>12-5<br>13-1<br>14-1<br>14-25                                  |

| Chapter 12 Hardware Description of the 8XC451 DATA SHEET 8XC451 8-Bit CHMOS Microcontroller  Chapter 13 UPITM-452 CHMOS Programmable I/O Processor  Chapter 14 DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 187C75PF Microcontroller Peripheral I/O Port Expander  1 Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                                                       | 12-1<br>12-5<br>13-1<br>14-1<br>4-14<br>4-25                           |

| Hardware Description of the 8XC451 DATA SHEET 8XC451 8-Bit CHMOS Microcontroller  Chapter 13 UPITM-452 CHMOS Programmable I/O Processor  Chapter 14 DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 1 87C75PF Microcontroller Peripheral I/O Port Expander 1 Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                                                                  | 12-5<br>13-1<br>14-1<br>4-14<br>4-25                                   |

| Hardware Description of the 8XC451 DATA SHEET 8XC451 8-Bit CHMOS Microcontroller  Chapter 13 UPITM-452 CHMOS Programmable I/O Processor  Chapter 14 DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 1 87C75PF Microcontroller Peripheral I/O Port Expander 1 Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                                                                  | 12-5<br>13-1<br>14-1<br>4-14<br>4-25                                   |

| DATA SHEET 8XC451 8-Bit CHMOS Microcontroller  Chapter 13 UPITM-452 CHMOS Programmable I/O Processor  Chapter 14 DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 1 87C75PF Microcontroller Peripheral I/O Port Expander 1 Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                                                                                                     | 12-5<br>13-1<br>14-1<br>4-14<br>4-25                                   |

| 8XC451 8-Bit CHMOS Microcontroller  Chapter 13     UPITM-452 CHMOS Programmable I/O Processor  Chapter 14     DATA SHEETS     27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM     87C257 256K (32K x 8) CHMOS UV Erasable PROM     87C75PF Microcontroller Peripheral I/O Port Expander  1 Chapter 15     MCS®-51 DEVELOPMENT SUPPORT TOOLS     8051 Software Packages                                                                                                                     | 13-1<br>14-1<br>4-14<br>4-25                                           |

| Chapter 13     UPITM-452 CHMOS Programmable I/O Processor  Chapter 14     DATA SHEETS     27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM     87C257 256K (32K x 8) CHMOS UV Erasable PROM     87C75PF Microcontroller Peripheral I/O Port Expander  1 Chapter 15     MCS®-51 DEVELOPMENT SUPPORT TOOLS     8051 Software Packages                                                                                                                                                         | 13-1<br>14-1<br>4-14<br>4-25                                           |

| UPITM-452 CHMOS Programmable I/O Processor  Chapter 14  DATA SHEETS  27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM  87C257 256K (32K x 8) CHMOS UV Erasable PROM  1 87C75PF Microcontroller Peripheral I/O Port Expander  1 Chapter 15  MCS®-51 DEVELOPMENT SUPPORT TOOLS  8051 Software Packages                                                                                                                                                                                        | 14-14<br> 4-14<br> 4-25                                                |

| Chapter 14 DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 1 87C75PF Microcontroller Peripheral I/O Port Expander 1 Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                                                                                                                                                                                                           | 14-14<br> 4-14<br> 4-25                                                |

| DATA SHEETS 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 1 87C75PF Microcontroller Peripheral I/O Port Expander 1 Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                                                                                                                                                                                                                      | 4-14<br> 4-25                                                          |

| 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM 87C257 256K (32K x 8) CHMOS UV Erasable PROM 1 87C75PF Microcontroller Peripheral I/O Port Expander 1  Chapter 15 MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                                                                                                                                                                                                                                 | 4-14<br> 4-25                                                          |

| 87C257 256K (32K x 8) CHMOS UV Erasable PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-14<br> 4-25                                                          |

| 87C75PF Microcontroller Peripheral I/O Port Expander                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-25                                                                   |

| Chapter 15  MCS®-51 DEVELOPMENT SUPPORT TOOLS  8051 Software Packages                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |

| MCS®-51 DEVELOPMENT SUPPORT TOOLS 8051 Software Packages                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15-1                                                                   |

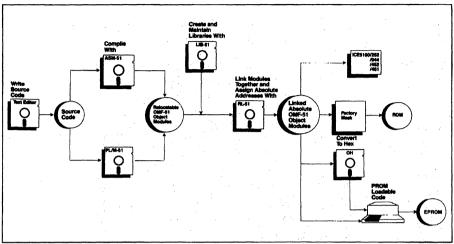

| 8051 Software Packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15-1                                                                   |

| 8051 Software Packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15-1                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-1                                                                   |

| AEDIT Text Editor Fact Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15-4                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15-6                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-10                                                                   |

| ICETM-5100/452 In-Circuit Emulator Fact Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-14                                                                   |

| Chapter 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

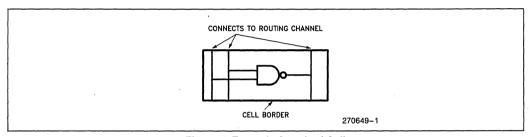

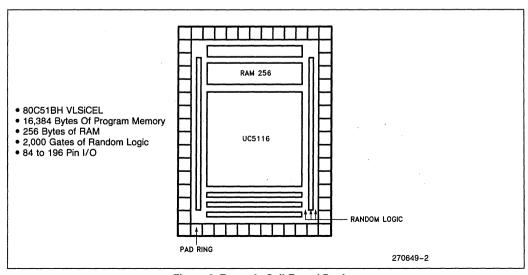

| ASIC: INTEL CELL-BASED DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16-1                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

| DATA SHEETS 1.5 Micron CHMOS III Cell Library                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-12                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-23                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-25                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-27                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-29                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

| MCS®-96/8098 FAMILY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                        |

| Chapter 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17-1                                                                   |

| DATA SHEET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

| 8098/8398 Advanced 8-Bit Microcontroller with 16-Bit CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-43                                                                   |

| THE RUPITM FAMILY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        |

| Chanter 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

| The RUPITM-44 Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18-1                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-1                                                                   |

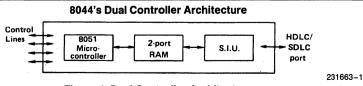

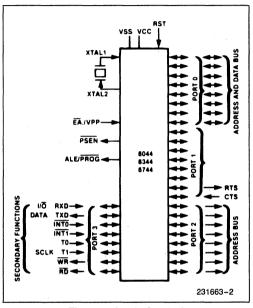

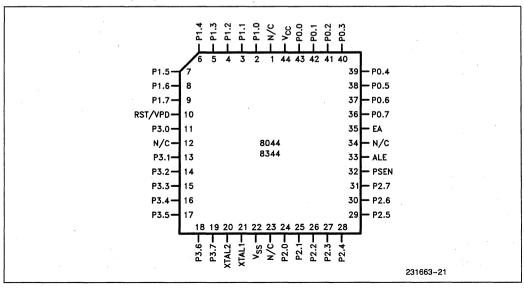

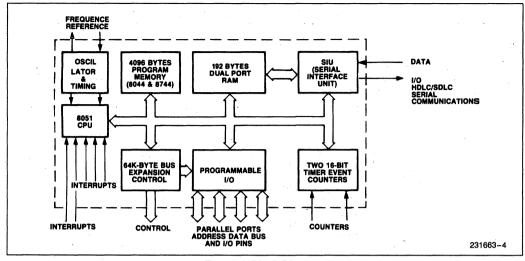

| Chapter 19 8044 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19-1                                                                   |

| Chapter 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

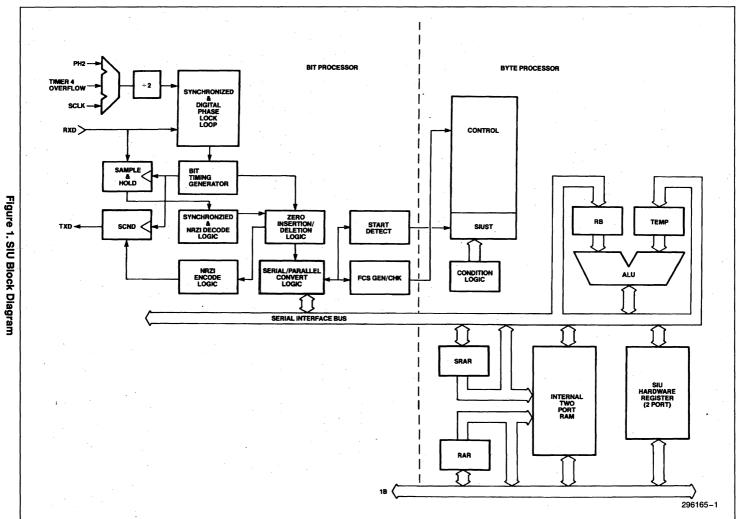

| 8044 Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20-1                                                                   |

| Chapter 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21-1                                                                   |

| Chapter 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

| 8044 DATA SHEET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

| 8044AH/8344AH/8744H High Performance 8-Bit Microcontroller with On-Chip                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                        |

# Table of Contents (Continued)

| Chapter 23                                                              |       |

|-------------------------------------------------------------------------|-------|

| RUPI™ DEVELOPMENT SUPPORT TOOL                                          |       |

| ICE™-5100/044 In-Circuit Emulator Fact Sheet                            | 23-1  |

| MCS®-80/85 FAMILY                                                       |       |

| Chapter 24                                                              |       |

| 80/85 DATA SHEETS                                                       |       |

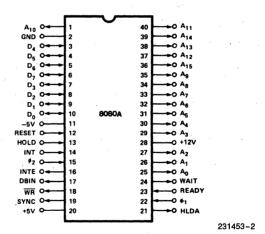

| 8080A/8080A-1/8080A-2 8-Bit N-Channel Microprocessor                    | 24-1  |

|                                                                         | 24-11 |

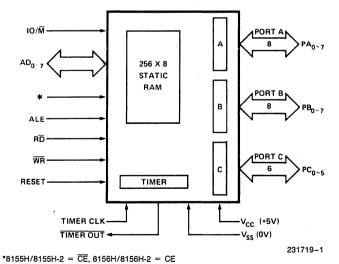

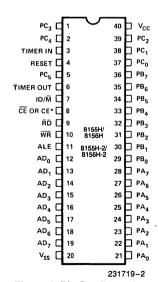

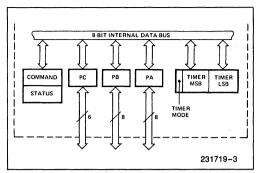

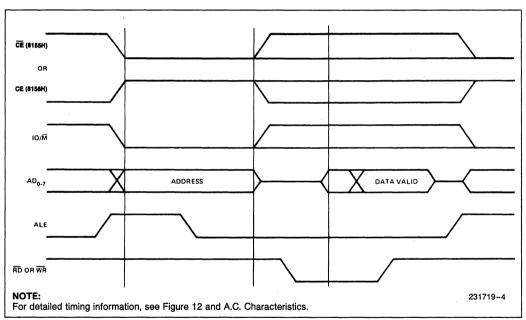

| 8155H/8156H/8155H-2/8156H-2 2048-Bit Static HMOS RAM with I/O Ports and |       |

|                                                                         | 24-31 |

|                                                                         | 24-45 |

|                                                                         | 24-50 |

|                                                                         | 24-55 |

|                                                                         | 24-59 |

| Indexes                                                                 |       |

| MCS®-48 Index                                                           | 25-1  |

| MCS®-51 Architectural Index                                             | 25-3  |

| 8XC451 Architectural Index                                              | 25-5  |

# Alphanumeric Index

| 1.5 Micron CHMOS III Cell Library                                              | 16-12 |

|--------------------------------------------------------------------------------|-------|

| 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROM                 | 14-1  |

| 8031AH/8051AH/8032AH/8751H/8751H-8 Express                                     | 8-59  |

| 8031/8051/8031AH/8051AH/8032AH/8052AH/8751H/8751-8 8-Bit HMOS and HMOS         | 0-09  |

|                                                                                | 0.05  |

| EPROM Microcontroller                                                          | 8-35  |

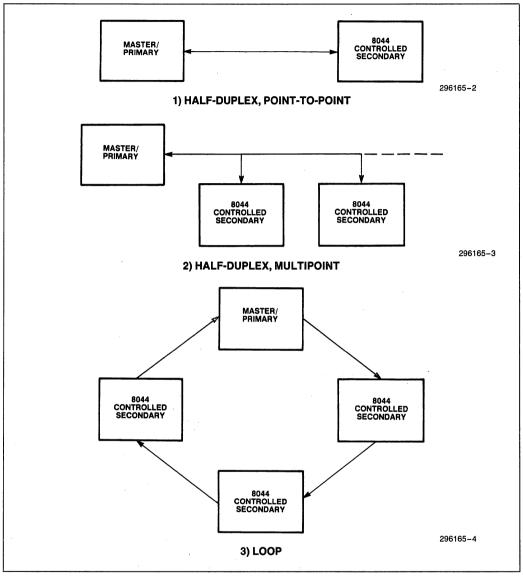

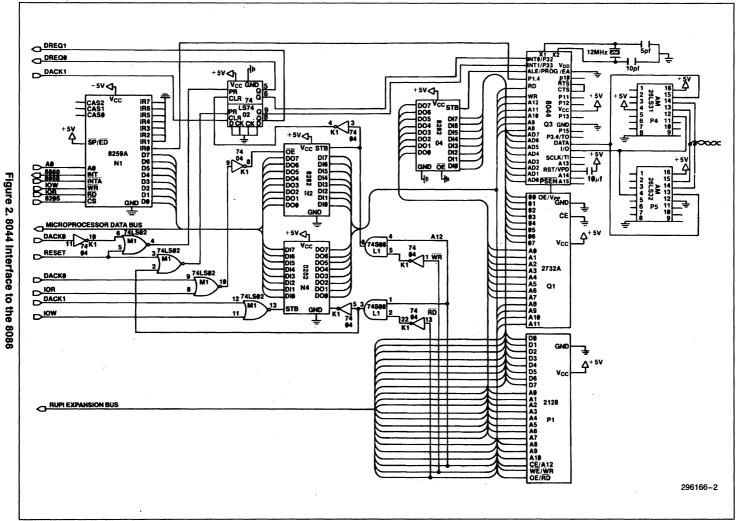

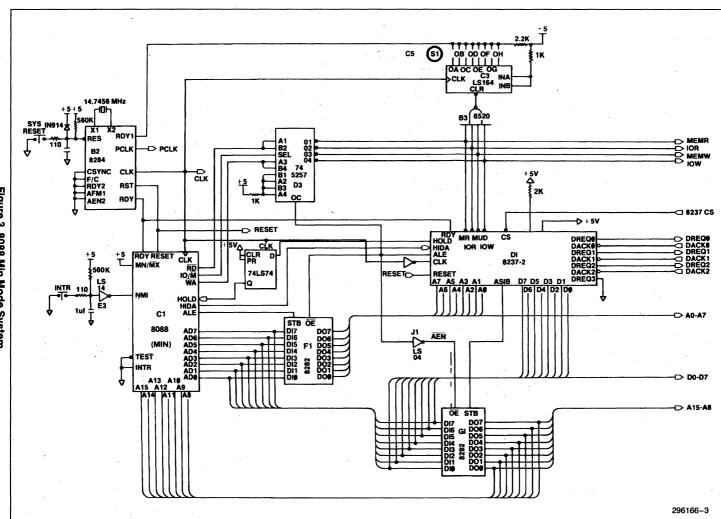

| 8044 Application Examples                                                      | 21-1  |

| 8044 Architecture                                                              | 19-1  |

| 8044 Serial Interface                                                          | 20-1  |

| 8044AH/8344AH/8744H High Performance 8-Bit Microcontroller with On-Chip Serial |       |

| Communication Controller                                                       | 22-1  |

| 8051 Software Packages                                                         | 15-1  |

| 8051AHP 8-Bit Microcontroller with Protected ROM                               | 8-49  |

| 8080A/8080A-1/8080A-2 8-Bit N-Channel Microprocessor                           | 24-1  |

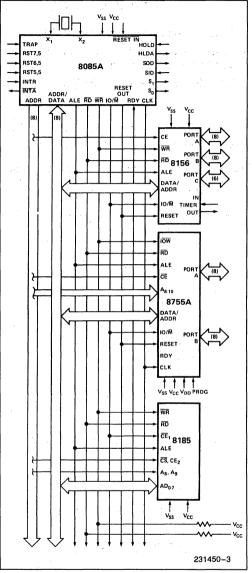

| 8085AH/8085AH-2/8085AH-1 8-Bit HMOS Microprocessor                             | 24-11 |

| 8098/8398 Advanced 8-Bit Microcontroller with 16-Bit CPU                       | 17-43 |

| 80C31BH/80C51BH 8-Bit CHMOS Microcontroller                                    | 8-87  |

| 80C31BH/80C51BH Express                                                        | 8-100 |

| 80C51 BHP 8-Bit CHMOS Microcontroller with Protected ROM                       | 8-102 |

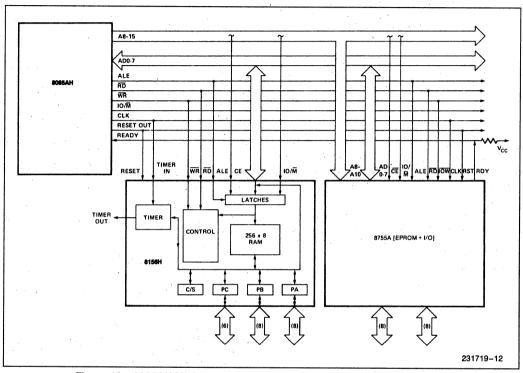

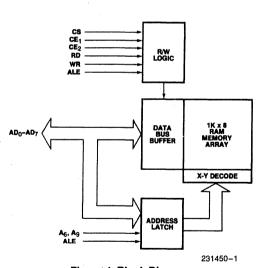

| 8155H/8156H/8155H-2/8156H-2 2048-Bit Static HMOS RAM with I/O Ports and Timer  | 24-31 |

| 8185/8185-2 1024 x 8-Bit Static RAM for MCS®-85                                | 24-45 |

| 8224 Clock Generator and Driver for 8080A CPU                                  | 24-50 |

| 8228 System Controller and Bus Driver for 8080A CPU                            | 24-55 |

| 8243 MCS®-48 Input/Output Expander                                             | 4-1   |

| 83C51FA 8-Bit CHMOS Microcontroller                                            | 9-43  |

| 83C51FA Express                                                                | 9-57  |

| 83C51FB 8-Bit CHMOS Microcontroller                                            | 9-78  |

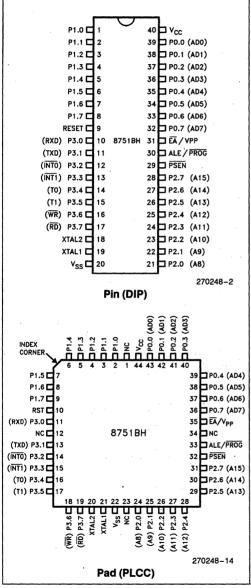

| 8751BH 8-Bit HMOS EPROM Microcontroller                                        |       |

| 8752BH 8-Bit HMOS EPROM Microcontroller                                        | 8-73  |

| 8752BH Express                                                                 | 8-85  |

| 8755A 16,384-Bit EPROM with I/O                                                | 24-59 |

| 87C257 256K (32K x 8) CHMOS UV Erasable PROM                                   | 14-14 |

| 87C51 8-Bit CHMOS EPROM Microcontroller                                        | 8-115 |

| 87C51 Express                                                                  | 8-129 |

| 87C51FA 8-Bit CHMOS Microcontroller                                            | 9-59  |

| 87C51FA 6-bit CHIMOS MICrocontroller                                           | 9-75  |

| 87C51FB 8-Bit CHMOS Microcontroller                                            | 9-75  |

|                                                                                | 10-12 |

| 87C51GA 8-Bit CHMOS Microcontroller                                            |       |

| 87C75PF Microcontroller Peripheral I/O Port Expander                           | 14-25 |

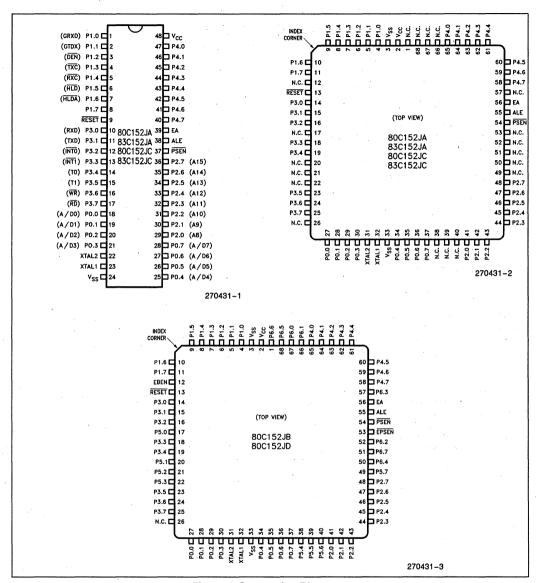

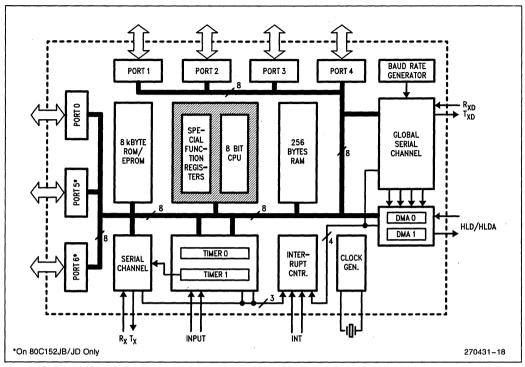

| 8XC152 JA/JB/JC/JD Communication Controller                                    | 11-69 |

| 8XC152 JA/JB/JC/JD Express                                                     | 11-85 |

| 8XC451 8-Bit CHMOS Microcontroller                                             | 12-5  |

| AEDIT Text Editor Fact Sheet                                                   | 15-4  |

| ASIC Tools and Services                                                        | 16-25 |

| D8748H/8749H HMOS-E Single-Component 8-Bit Microcomputer                       | 4-21  |

| Daisy-Based ASIC Libraries                                                     | 16-29 |

|                                                                                | 9-107 |

| EV80C51FB Microcontroller Evaluation Board Fact Sheet                          | 9-109 |

| Hardware Description of the 8XC51GA                                            | 10-1  |

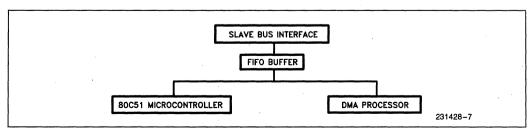

| Hardware Description of the 83C152                                             | 11-1  |

| Hardware Description of the 83C51FA/FB                                         | 9-1   |

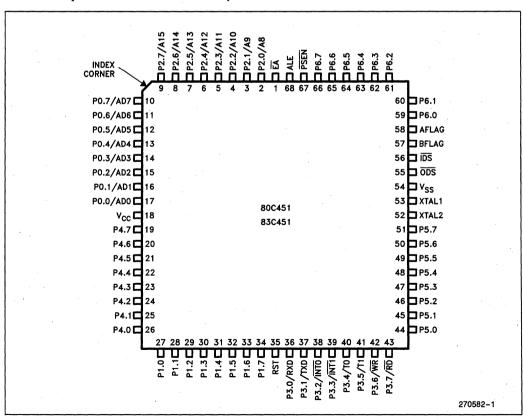

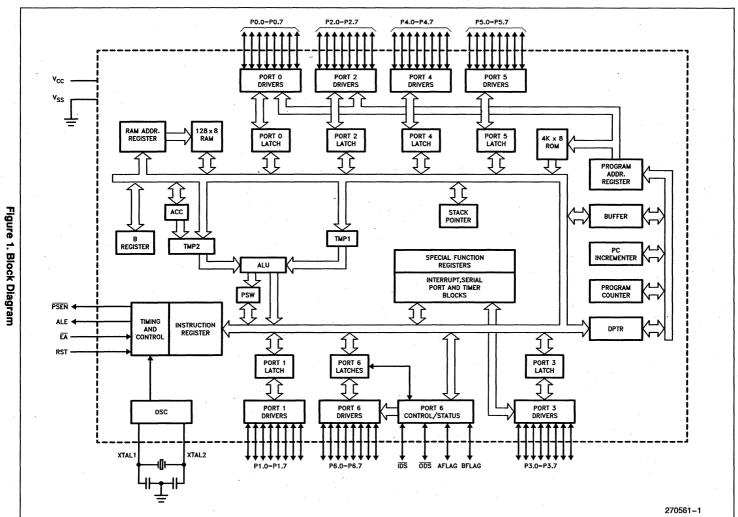

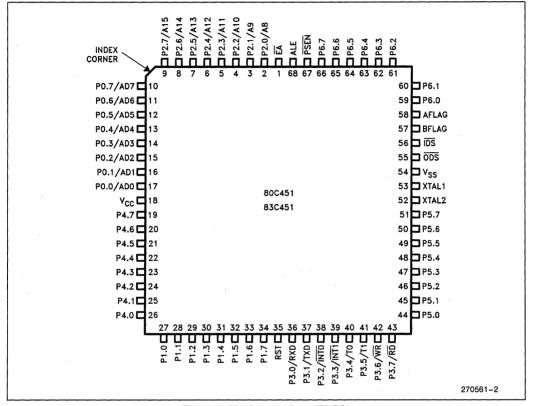

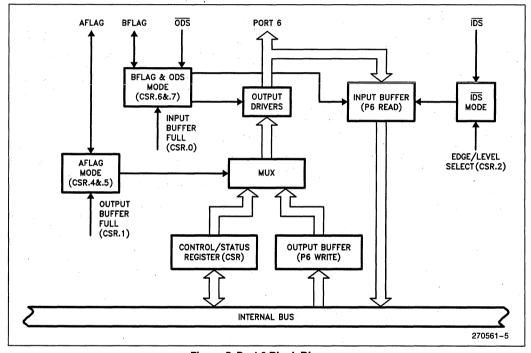

| Hardware Description of the 8XC451                                             | 12-1  |

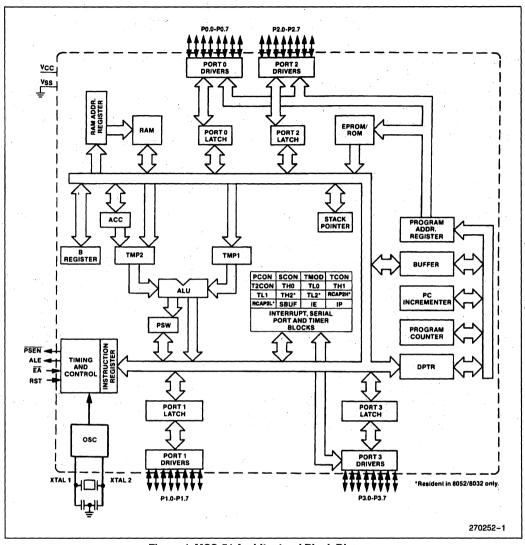

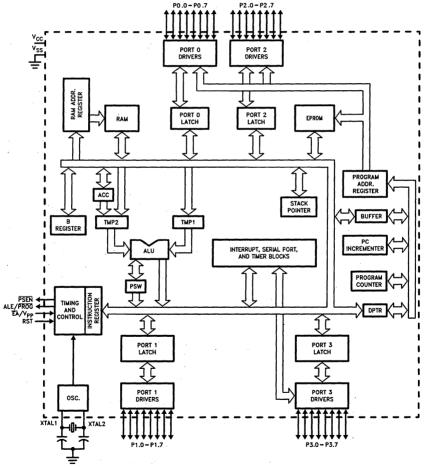

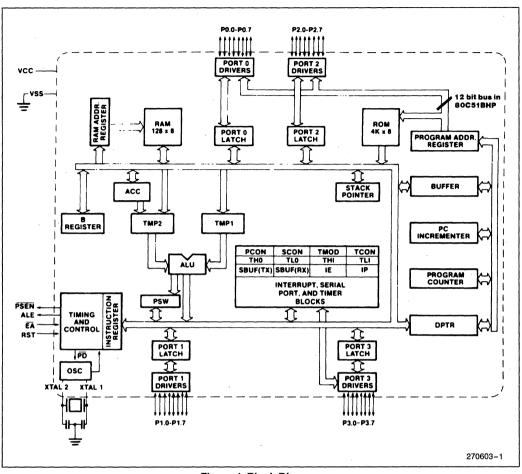

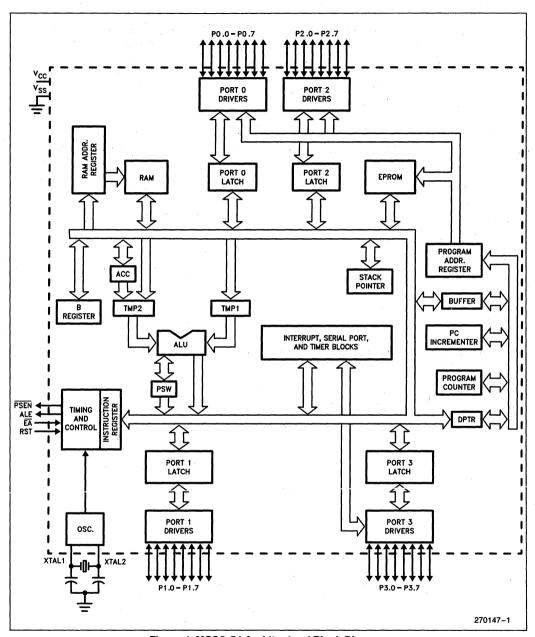

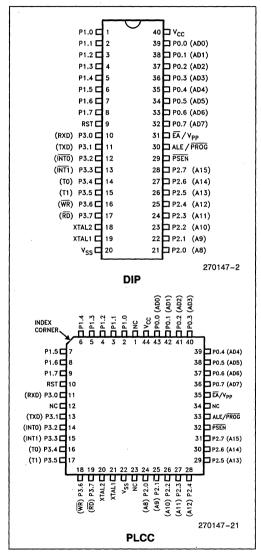

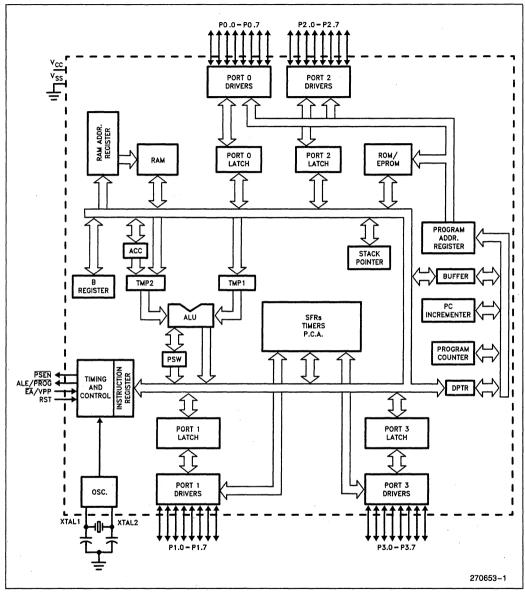

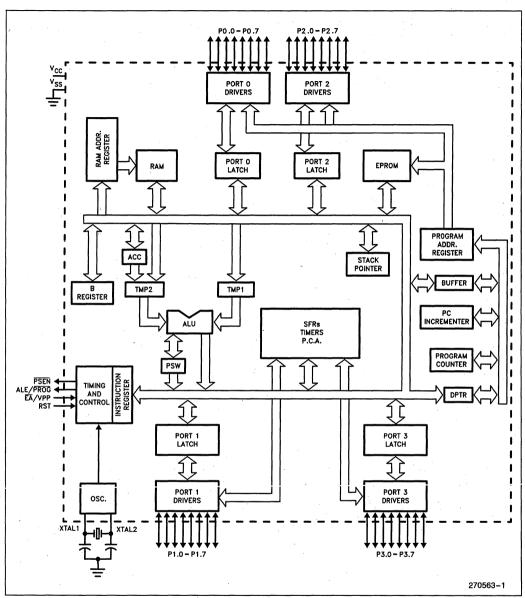

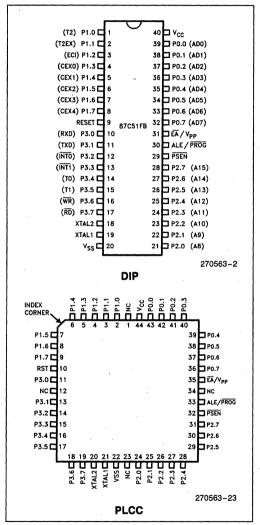

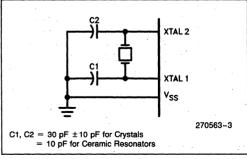

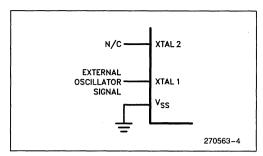

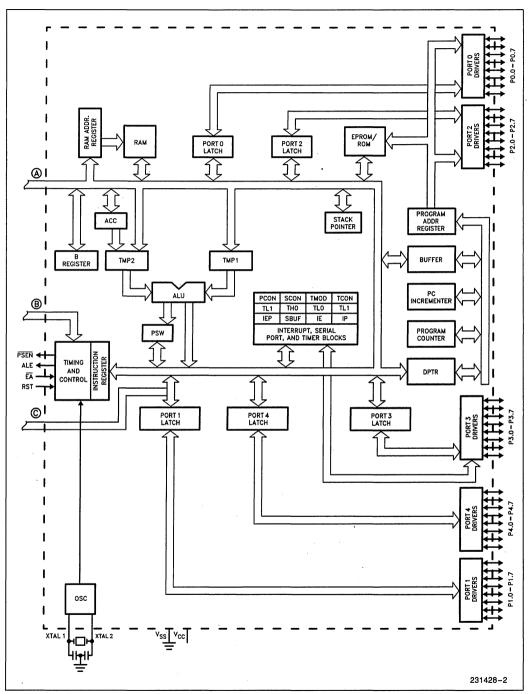

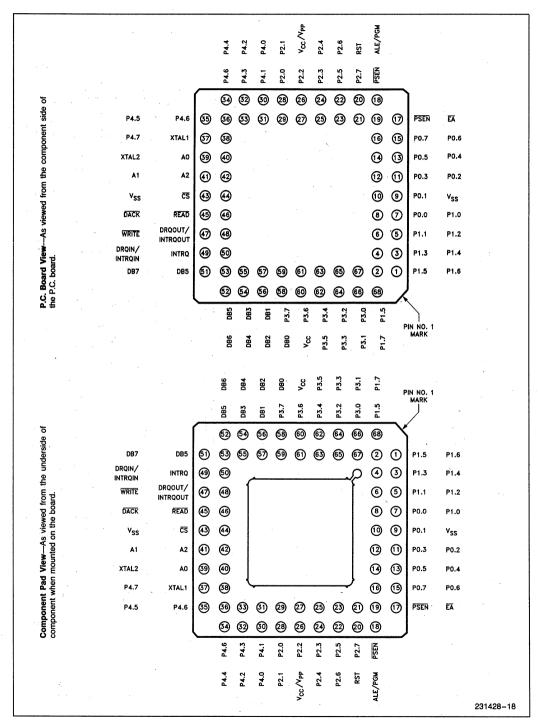

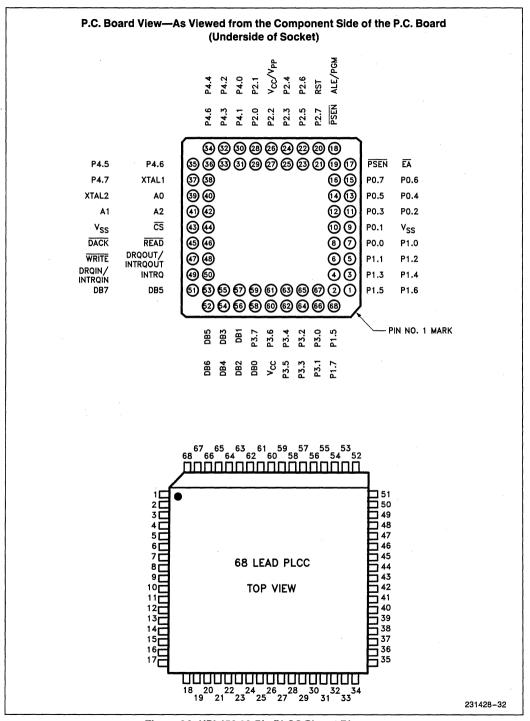

| Hardware Description of the 8051, 8052 and 80C51                               | 8-1   |

| ICETM-5100/252 Fact Sheet                                                      | 15-6  |

| ICETM-5100/451 Fact Sheet                                                      | 15-10 |

# Alphanumeric Index (Continued)

| ICETM-5100/452 In-Circuit Emulator Fact Sheet                         | 15-14 |

|-----------------------------------------------------------------------|-------|

| ICETM-5100/044 In-Circuit Emulator Fact Sheet                         | 23-1  |

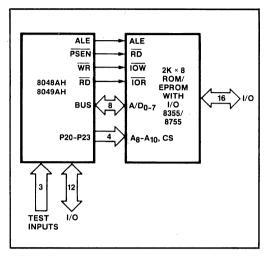

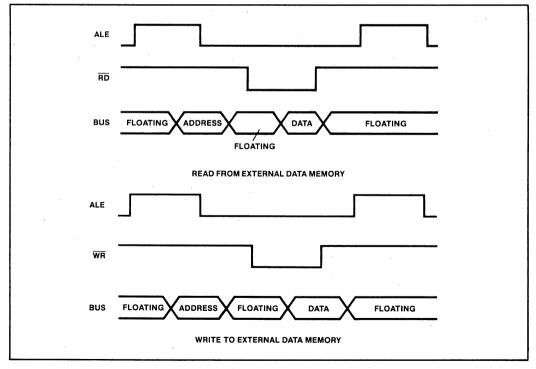

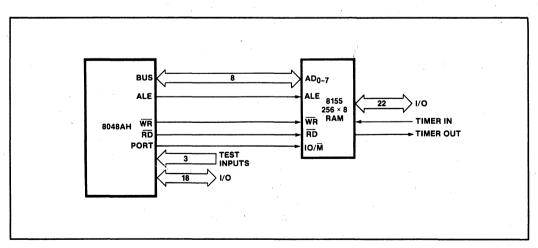

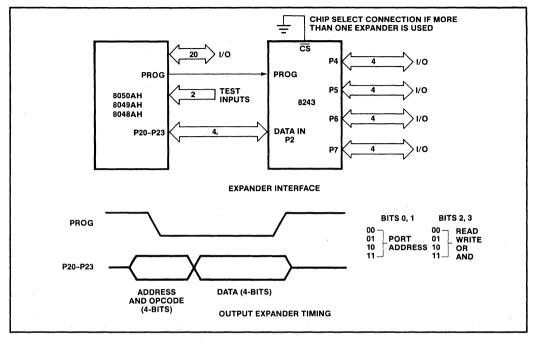

| MCS®-48 Expanded System                                               | 2-1   |

| MCS®-48 Express                                                       | 4-33  |

| MCS®-48 Instruction Set                                               | 3-1   |

| MCS®-48 Single Component System                                       | 1-1   |

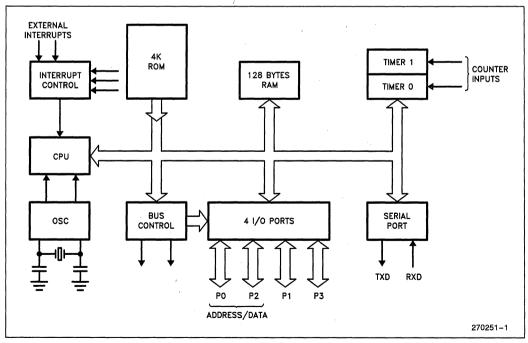

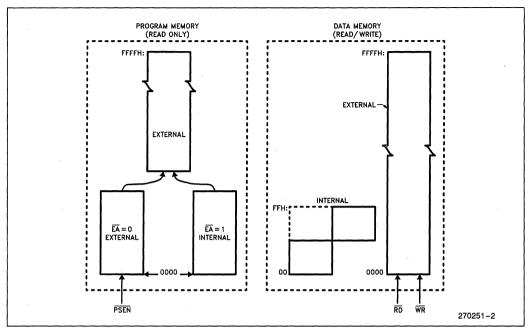

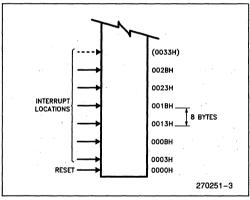

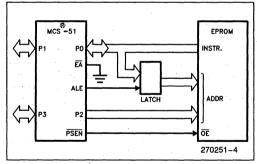

| MCS®-51 Architectural Overview                                        | 5-1   |

| MCS®-96 8098 Architectural Overview                                   | 17-1  |

| Mentor-Based ASIC Libraries                                           | 16-27 |

| P8748H/P8749H/8048AH/8035AHL/8049AH/8039AHL/8050AH/8040AHL HMOS 8-Bit |       |

| Microcontroller                                                       | 4-8   |

| UC51 Timing Calculation Package Fact Sheet                            | 16-23 |

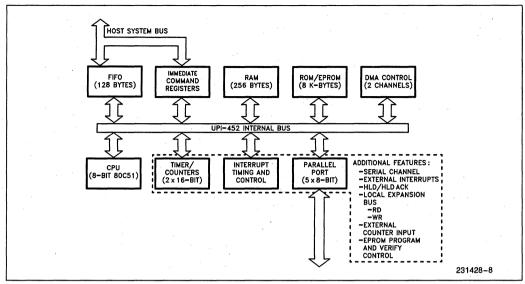

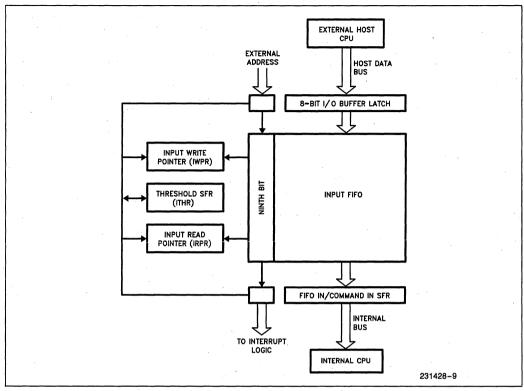

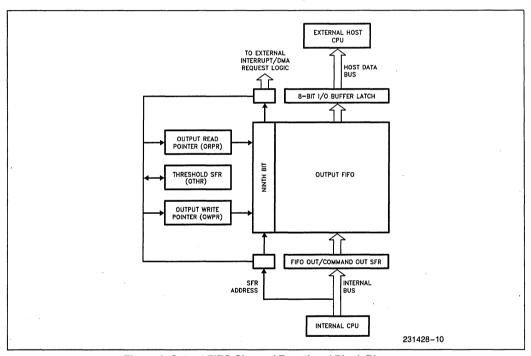

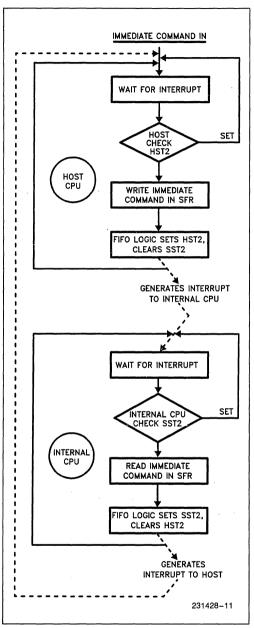

| UPITM-452 CHMOS Programmable I/O Processor                            | 13-1  |

| Using the Intel MCS®-51 Boolean Processing Capabilities               | 7-1   |

Any of the following products may appear in this publication. If so, it must be noted that such products have counterparts manufactured by Intel Puerto Rico, Inc., Intel Puerto Rico II, Inc., and/or Intel Singapore, Ltd. The product codes/part numbers of these counterpart products are listed below next to the corresponding Intel Corporation product codes/part numbers.

| Intel Corporation<br>Product Codes/<br>Part Numbers | Intel Puerto Rico, Inc.<br>Intel Puerto Rico II, Inc.<br>Product Codes/<br>Part Numbers | Intel Singapore, Ltd .<br>Product Codes/<br>Part Numbers | Intel Corporation<br>Product Codes/<br>Part Numbers | Intel Puerto Rico, Inc.<br>Intel Puerto Rico II, Inc.<br>Product Codes/<br>Part Numbers | Intel Singapore, Ltd .<br>Product Codes/<br>Part Numbers |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------|

| 376SKIT                                             | p376SKIT                                                                                |                                                          | KM2                                                 | pKM2                                                                                    |                                                          |

| 903                                                 | p903                                                                                    |                                                          | KM4                                                 | pKM4                                                                                    | 4                                                        |

| 904                                                 | p904                                                                                    |                                                          | KM8                                                 | pKM8                                                                                    |                                                          |

| 913                                                 | p913                                                                                    |                                                          | KNLAN                                               | pKNLAN                                                                                  |                                                          |

| 914                                                 | p914                                                                                    |                                                          | KT60                                                | pKT60                                                                                   |                                                          |

| 923                                                 | p923                                                                                    |                                                          | KW140                                               | pKW140                                                                                  |                                                          |

| 924                                                 | p924                                                                                    |                                                          | KW40                                                | pKW40                                                                                   |                                                          |

| 952                                                 | p952                                                                                    |                                                          | KW80                                                | pKW80                                                                                   |                                                          |

| 953                                                 | p953                                                                                    |                                                          | M1.                                                 | pM1                                                                                     |                                                          |

| 954                                                 | p954                                                                                    |                                                          | M2                                                  | pM2                                                                                     |                                                          |

| ADAICE                                              | pADAICE                                                                                 | •                                                        | M4                                                  | pM4                                                                                     |                                                          |

| B386M1                                              | pB386M1                                                                                 |                                                          | M8                                                  | pM8                                                                                     |                                                          |

| B386M2                                              | pB386M2                                                                                 |                                                          | MDS610                                              | pMDS610                                                                                 |                                                          |

| B386M4                                              | pB386M4                                                                                 |                                                          | MDX3015                                             | pMDX3015                                                                                |                                                          |

| B386M8                                              | pB386M8                                                                                 |                                                          | MDX3015                                             | pMDX3015                                                                                |                                                          |

| C044KIT                                             | pC044KIT                                                                                | -                                                        | MDX3016                                             | pMDX3016                                                                                |                                                          |

| C252KIT                                             | pC252KIT                                                                                |                                                          | MDX3016                                             | pMDX3016                                                                                |                                                          |

| C28                                                 | pC28                                                                                    |                                                          | MDX457                                              | pMDX457                                                                                 |                                                          |

| C32                                                 | pC32                                                                                    |                                                          | MDX457                                              | pMDX457                                                                                 |                                                          |

| C452KIT                                             | pC452KIT                                                                                | \$                                                       | MDX458                                              | pMDX458                                                                                 | *                                                        |

| D86ASM                                              | pD86ASM                                                                                 |                                                          | MDX458                                              | pMDX458                                                                                 |                                                          |

| D86C86                                              | pD86C86                                                                                 |                                                          | MSA96                                               | pMSA96                                                                                  |                                                          |

| D86EDI                                              | pD86EDI                                                                                 |                                                          | NLAN                                                | pNLAN                                                                                   |                                                          |

| DCM9111                                             | pDCM9111                                                                                |                                                          | PCLINK                                              | •                                                                                       | <b>sPCLINK</b>                                           |

| DOSNET                                              | pDOSNET                                                                                 |                                                          | PCX344A                                             | pPCX344A                                                                                |                                                          |

| FI .                                                | pF1                                                                                     |                                                          | R286ASM                                             | pR286ASM                                                                                |                                                          |

| GUPILOGICIID                                        | pGUPILOGICIID                                                                           |                                                          | R286EDI                                             | pR286EDI                                                                                |                                                          |

| H4                                                  | pH4                                                                                     |                                                          | R286PLM                                             | pR286PLM                                                                                |                                                          |

| I044                                                | pI044                                                                                   |                                                          | R286SSC                                             | pR286SSC                                                                                |                                                          |

| I252KIT                                             | pI252KIT                                                                                |                                                          | R86FOR                                              | pR86FOR                                                                                 |                                                          |

| I452KIT                                             | pI452KIT                                                                                |                                                          | RCB4410                                             |                                                                                         | sRCB4410                                                 |

| I86ASM                                              | pI86ASM                                                                                 |                                                          | RCX920                                              | pRCX920                                                                                 |                                                          |

| ICE386                                              | pICE386                                                                                 |                                                          | RMX286                                              | pRMX286                                                                                 |                                                          |

| III010                                              | pIII010                                                                                 |                                                          | RMXNET                                              | pRMXNET                                                                                 |                                                          |

| 111086                                              | pIII086                                                                                 |                                                          | S301 ·                                              | pS301                                                                                   |                                                          |

| III086                                              | TIII086                                                                                 |                                                          | S386                                                | pS386                                                                                   |                                                          |

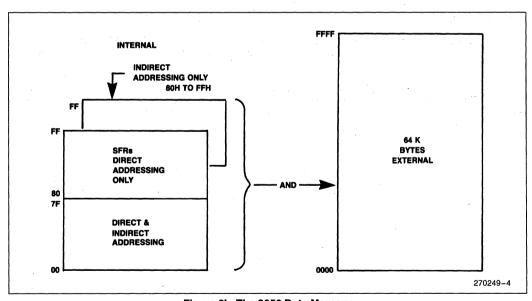

| III111                                              | pIII111                                                                                 |                                                          | SBC010                                              | pSBC010                                                                                 |                                                          |