# 82430FX PCIset DATASHEET 82437FX SYSTEM CONTROLLER (TSC) AND 82438FX DATA PATH UNIT (TDP)

- Supports all 3V Pentium<sup>®</sup> Processors

- Integrated Second Level Cache Controller

- Direct Mapped Organization

- Write-Back Cache Policy

- Cacheless, 256-Kbyte, and 512-Kbyte

- Standard Burst and Pipelined Burst SRAMs

- Cache Hit Read/Write Cycle Timings at 3-1-1-1 with Burst or Pipelined Burst SRAMs

- Back-to-Back Read Cycles at 3-1-1-1-1-1-1-1 with Burst or Pipelined Burst SRAMs

- Integrated Tag/Valid Status Bits for Cost Savings and Performance

- Supports 5V SRAMs for Tag Address

- Integrated DRAM Controller

- 64-Bit Data Path to Memory

- 4 Mbytes to 128 Mbytes Main Memory

- EDO/Hyper Page Mode DRAM (x-2-2-2 Reads) or Standard Page Mode DRAMs

- 5 RAS Lines

- 4 Qword Deep Buffer for 3-1-1-1 Posted Write Cycles

- Symmetrical and Asymmetrical DRAMs

- 3V or 5V DRAMs

- EDO DRAM Support

- Highest Performance with Burst or Pipelined Burst SRAMs

- Superior Cacheless Designs

- Fully Synchronous 25/30/33 MHz PCI Bus Interface

- 100 MB/s Instant Access Enables Native Signal Processing (NSP) on Pentium Processors

- Synchronized CPU-to-PCI Interface for High Performance Graphics

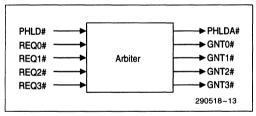

- PCI Bus Arbiter: PIIX and Four PCI Bus Masters Supported

- CPU-to-PCI Memory Write Posting with 4 Dword Deep Buffers

- Converts Back-to-Back Sequential CPU to PCI Memory Writes to PCI Burst Writes

- PCI-to-DRAM Posting of 12 Dwords

- PCI-to-DRAM up to 120 Mbytes/Sec Bandwidth Utilizing Snoop Ahead Feature

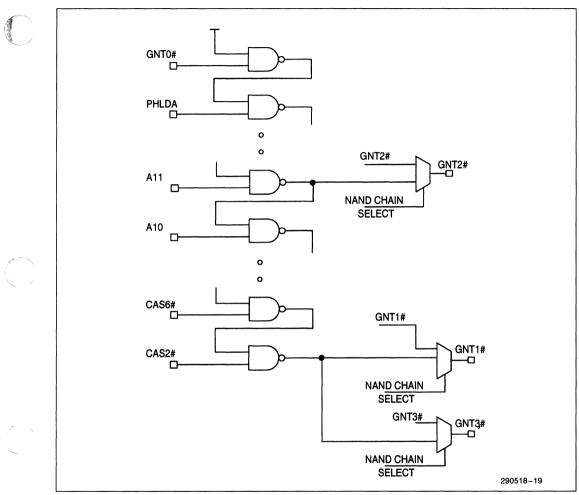

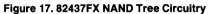

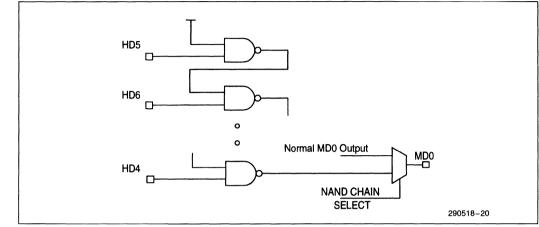

- NAND Tree for Board-Level ATE Testing

- 208 Pin QFP for the 82437FX System Controller (TSC); 100 Pin QFP for Each 82438FX Data Path (TDP)

- Supported Kits

82437FX ISA Kit (TSC, TDPs, PIIX)

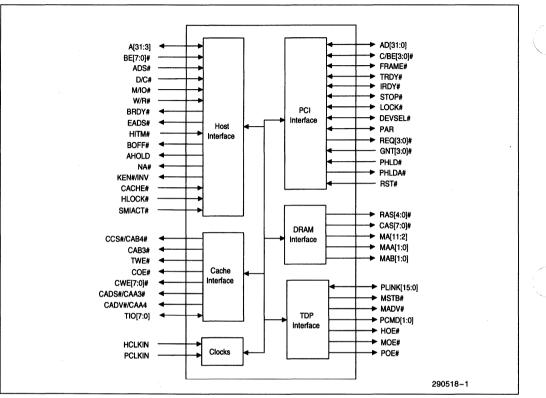

The 82430FX PCIset consists of the 82437FX System Controller (TSC), two 82438FX Data Paths (TDP), and the 82371FB PCI ISA IDE Xcelerator (PIIX). The PCIset forms a Host-to-PCI bridge and provides the second level cache control and a full function 64-bit data path to main memory. The TSC integrates the cache and main memory DRAM control functions and provides bus control for transfers between the CPU, cache, main memory, and the PCI Bus. The second level (L2) cache controller supports a write-back cache policy for cache sizes of 256 Kbytes and 512 Kbytes. Cacheless designs are also supported. The cache memory can be implemented with either standard, burst, or pipelined burst SRAMs. An external Tag RAM is used for the address tag and an internal Tag RAM for the cache line status bits. For the TSC's DRAM controller, five rows are supported for up to 128 Mbytes of main memory. The TSC's optimized PCI interface allows the CPU to sustain the highest possible bandwidth to the graphics frame buffer at all frequencies. Using the snoop ahead feature, the TSC allows PCI masters to achieve full PCI bandwidth. The TDPs provide the data paths between the CPU/cache, main memory, and PCI. For increased system performance, the TDPs contain read prefetch and posted write buffers.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by the sale of Intel products. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel relatins the relatings to sale contains and product descriptions at any time. The relating to sale and/or use of Intellectual property right. Intel products in without notice. The Intel 430FX PCIset may contain design defects or errors known as errata. Current characterized errata are available on request. "Third-party brands and names are the property of their respective owners."

© INTEL CORPORATION 1996

82437FX TSC AND 82438FX TDP

# intel

82437FX TSC Simplified Block Diagram

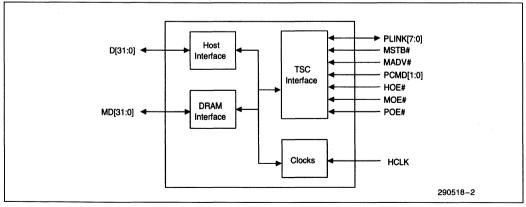

82438FX TDP Simplified Block Diagram

# 82430FX PCIset DATASHEET 82437FX SYSTEM CONTROLLER (TSC) AND 82438FX DATA PATH UNIT (TDP) CONTENTS PAGE

| 1.0 ARCHITECTURE OVERVIEW OF TSC/TDP                       |

|------------------------------------------------------------|

| 2.0 SIGNAL DESCRIPTION                                     |

| 2.1 TSC Signals                                            |

| 2.1.1 HOST INTERFACE (TSC)                                 |

| 2.1.2 DRAM INTERFACE (TSC)                                 |

| 2.1.3 SECONDARY CACHE INTERFACE (TSC)                      |

| 2.1.4 PCI INTERFACE (TSC)                                  |

| 2.1.5 TDP INTERFACE (TSC)                                  |

| 2.1.6 CLOCKS (TSC)                                         |

| 2.2 TDP Signals                                            |

| 2.2.1 DATA INTERFACE SIGNALS (TDP)12                       |

| 2.2.2 TSC INTERFACE SIGNALS (TDP) 12                       |

| 2.2.3 CLOCK SIGNAL (TDP) 12                                |

| 2.3 Signal State During Reset                              |

| 3.0 REGISTER DESCRIPTION                                   |

| 3.1 Control Registers                                      |

| 3.1.1 CONFADD—CONFIGURATION ADDRESS REGISTER               |

| 3.1.2 CONFDATA—CONFIGURATION DATA REGISTER                 |

| 3.2 PCI Configuration Registers                            |

| 3.2.1 VID—VENDOR IDENTIFICATION REGISTER                   |

| 3.2.2 DID—DEVICE IDENTIFICATION REGISTER                   |

| 3.2.3 PCICMD—PCI COMMAND REGISTER                          |

| 3.2.4 PCISTS—PCI STATUS REGISTER                           |

| 3.2.5 RID—REVISION IDENTIFICATION REGISTER                 |

| 3.2.6 SUBC—SUB-CLASS CODE REGISTER                         |

| 3.2.7 BCC—BASE CLASS CODE REGISTER 20                      |

| 3.2.8 MLT—MASTER LATENCY TIMER REGISTER                    |

| 3.2.9 BIST—BIST REGISTER                                   |

| 3.2.10 PCON—PCI CONTROL REGISTER                           |

| 3.2.11 CC—CACHE CONTROL REGISTER 22                        |

| 3.2.12 DRAMC—DRAM CONTROL REGISTER 23                      |

| 3.2.13 DRAMT—DRAM TIMING REGISTER 24                       |

| 3.2.14 PAM—PROGRAMMABLE ATTRIBUTE MAP REGISTERS (PAM[6:0]) |

| 3.2.15 DRB—DRAM ROW BOUNDARY REGISTERS                     |

| CONTENTS PAGE                                       |                     |

|-----------------------------------------------------|---------------------|

| 3.2.16 DRT—DRAM ROW TYPE REGISTER                   |                     |

| 3.2.17 SMRAM—SYSTEM MANAGEMENT RAM CONTROL REGISTER | N.                  |

| 4.0 FUNCTIONAL DESCRIPTION                          |                     |

| 4.1 Host Interface                                  |                     |

| 4.2 PCI Interface                                   |                     |

| 4.3 Secondary Cache Interface                       |                     |

| 4.3.1 CLOCK LATENCIES                               |                     |

| 4.3.2 SNOOP CYCLES                                  |                     |

| 4.3.3 CACHE ORGANIZATION                            |                     |

| 4.3.4 CLARIFICATION ON HOW TO FLUSH THE L2 CACHE    |                     |

| 4.4 DRAM Interface                                  |                     |

| 4.4.1 DRAM ORGANIZATION 41                          |                     |

| 4.4.2 MAIN MEMORY ADDRESS MAP 42                    |                     |

| 4.4.3 DRAM ADDRESS TRANSLATION 42                   |                     |

| 4.4.4 DRAM PAGE MODE 44                             | $\langle \ \rangle$ |

| 4.4.5 EDO MODE                                      | $\sim$              |

| 4.4.6 DRAM PERFORMANCE 46                           |                     |

| 4.4.7 DRAM REFRESH 46                               |                     |

| 4.4.8 SYSTEM MANAGEMENT RAM 46                      |                     |

| 4.5 82438FX Data Path (TDP) 46                      |                     |

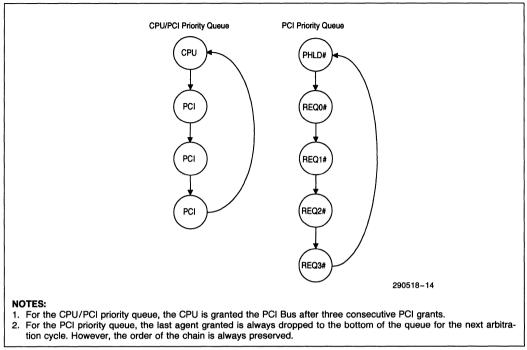

| 4.6 PCI Bus Arbitration                             |                     |

| 4.6.1 PRIORITY SCHEME AND BUS GRANT 47              |                     |

| 4.6.2 CPU POLICIES                                  |                     |

| 4.7 Clock Generation and Distribution               | 1 .                 |

| 4.7.1 RESET SEQUENCING 48                           |                     |

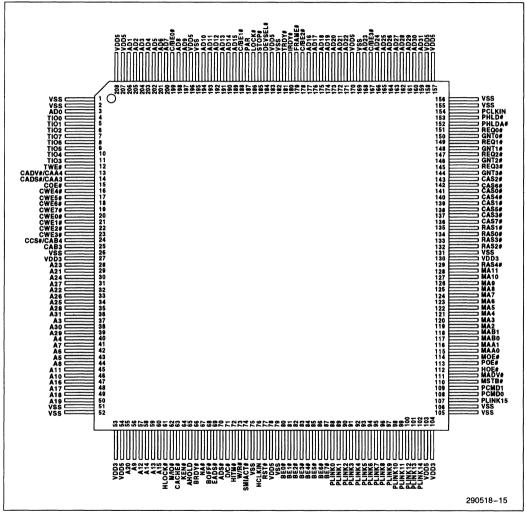

| 5.0 PINOUT AND PACKAGE INFORMATION                  | ×                   |

| 5.1 82437FX Pinout                                  |                     |

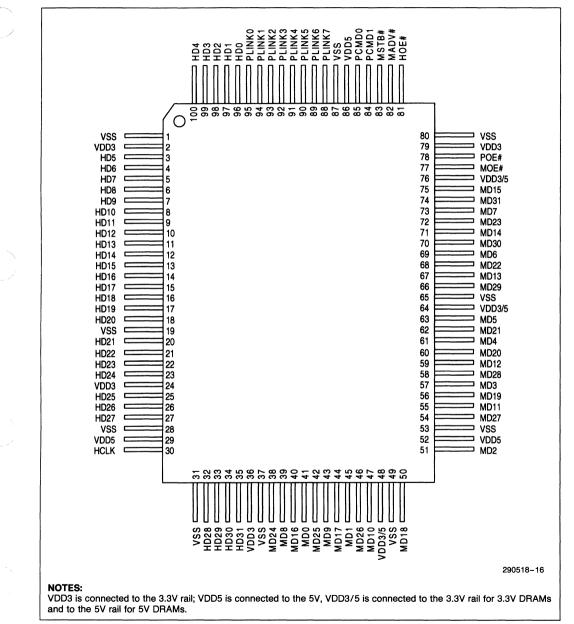

| 5.2 82438FX Pinout                                  |                     |

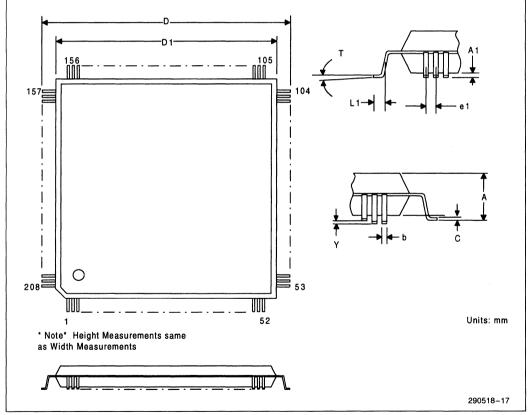

| 5.3 82437FX Package Dimensions 55                   |                     |

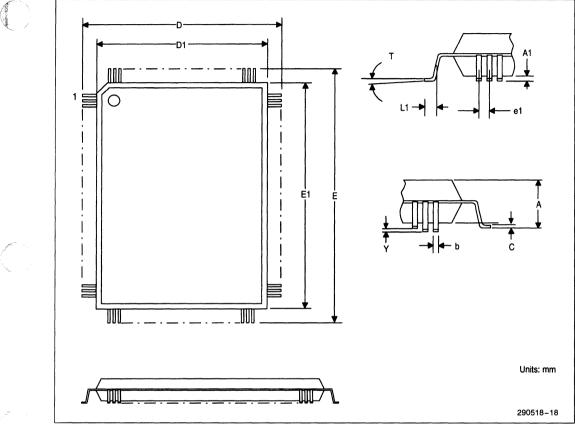

| 5.4 82438FX Package Dimensions 57                   |                     |

| 6.0 82437FX TSC TESTABILITY                         |                     |

| 6.1 Test Mode Description                           |                     |

| 6.2 NAND Tree Mode                                  |                     |

| 7.0 82438FX TDP TESTABILITY                         | Se d                |

| 7.1 Test Mode Description                           |                     |

| 7.2 NAND Tree Mode                                  |                     |

# 1.0 ARCHITECTURE OVERVIEW OF TSC/TDP

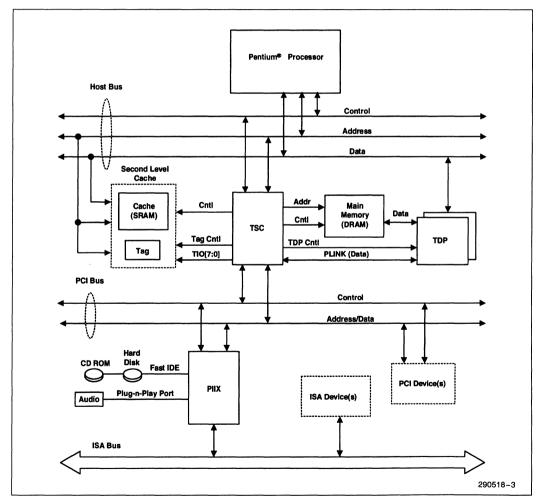

The 82430FX PCIset (Figure 1) consists of the 82437FX System Controller (TSC), two 82438FX Data Path (TDP) units, and the 82371FB PCI IDE ISA Xcelerator (PIIX). The TSC and two TDPs form a Host-to-PCI bridge. The PIIX is a multi-function PCI device providing a PCI-to-ISA bridge and a fast IDE interface. The PIIX also provides power management and has a plug and play port.

The two TDPs provide a 64-bit data path to the host and to main memory and provide a 16-bit data path (PLINK) between the TSC and TDP. PLINK provides the data path for CPU to PCI accesses and for PCI to main memory accesses. The TSC and TDP bus interfaces are designed for 3V and 5V busses. The TSC/TDP connect directly to the Pentium<sup>®</sup> processor 3V host bus; The TSC/TDP connect directly to 5V or 3V main memory DRAMs; and the TSC connects directly to the 5V PCI Bus.

Figure 1. 82430FX PCIset System

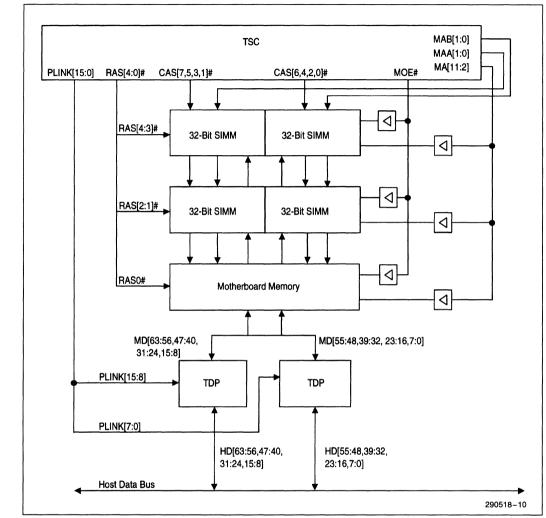

### **DRAM Interface**

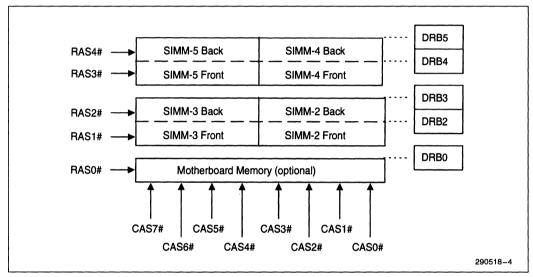

The DRAM interface is a 64-bit data path that supports both standard page mode and Extended Data Out (EDO) (also known as Hyper Page Mode) memory. The DRAM interface supports 4 Mbytes to 128 Mbytes with five RAS lines available and also supports symmetrical and asymmetrical addressing for 512K, 1M, 2M, and 4M deep DRAMs.

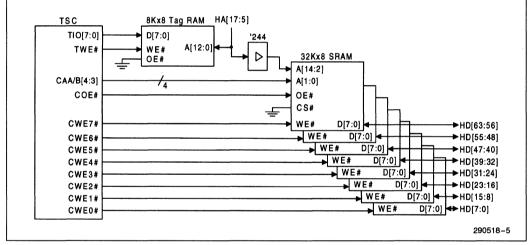

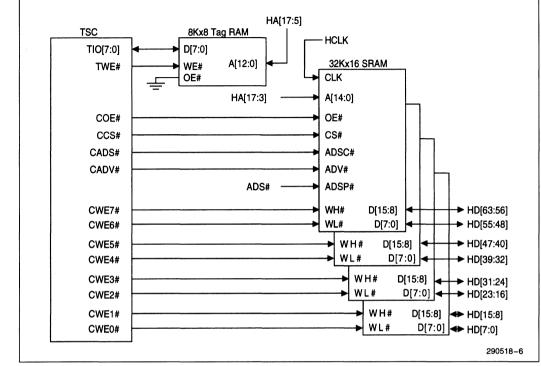

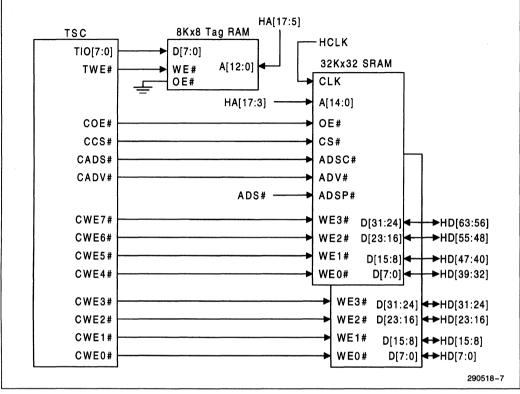

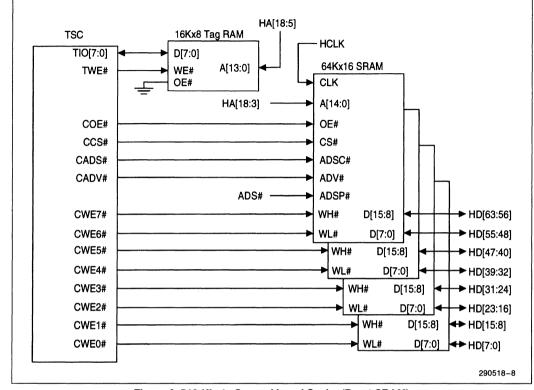

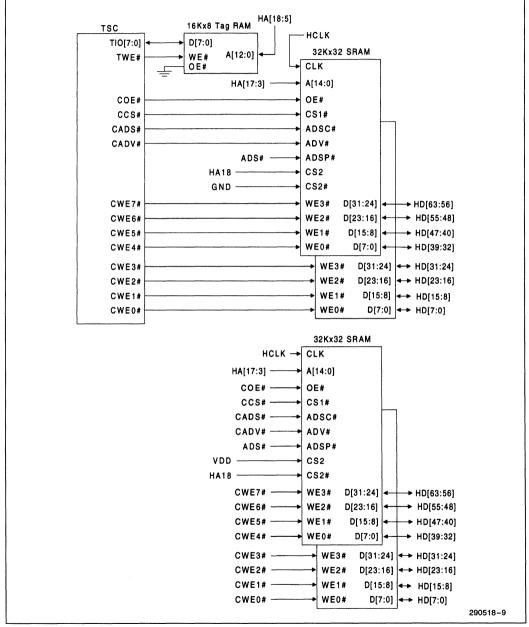

### Second Level Cache

The TSC supports a write-back cache policy providing all necessary snoop functions and inquire cycles. The second level cache is direct mapped and supports both a 256-Kbyte or 512-Kbyte SRAM configuration using either burst, pipelined burst, or standard SRAMs. The burst 256-Kbyte configuration performance is 3-1-1-1 for read/write cycles; pipelined backto-back reads can maintain a 3-1-1-1-1-1-1 transfer rate.

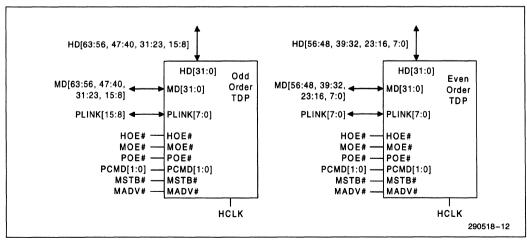

#### TDP

Two TDPs create a 64-bit CPU and main memory data path. The TDP's also interface to the TSC's 16-bit PLINK inter-chip bus for PCI transactions. The combination of the 64-bit memory path and the 16-bit PLINK bus make the TDP's a cost effective solution, providing optimal CPU-to-main memory performance while maintaining a small package footprint (100 pins each).

### **PCI Interface**

The PCI interface is 2.0 compliant and supports up to 4 PCI bus masters in addition to the PIIX bus master requests. While the TSC and TDP's together provide the interface between PCI and main memory, only the TSC connects to the PCI Bus.

### Buffers

The TSC and TDP's together contain buffers for optimizing data flow. A four Qword deep buffer is provided for CPU-to-main memory writes, second level cache write back cycles, and PCI-to-main memory transfers. This buffer is used to achieve 3-1-1-1 posted writes to main memory. A four Dword buffer is used for CPU-to-PCI writes. In addition, a four Dword PCI Write Buffer is provided which is combined with the DRAM Write Buffer to supply a 12 Dword deep buffering for PCI to main memory writes.

### System Clocking

The processor, second level cache, main memory subsystem, and PLINK bus all run synchronous to the host clock. The PCI clock runs synchronously at half the host clock frequency. The TSC and TDP's have a host clock input and the TSC has a PCI clock input. These clocks are derived from an external source and have a maximum clock skew requirement with respect to each other.

# 2.0 SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The following notations are used to describe the signal type.

- I Input is a standard input-only signal.

- O Totem pole output is a standard active driver.

- o/d Open drain.

- t/s Tri-State is a bi-directional, tri-state input/output pin.

- **s/t/s** Sustained tri-state is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tristates it. An external pull-up is required to sustain the inactive state until another agent drives it and must be provided by the central resource.

Ē

3

# 2.1 TSC Signals

# 2.1.1 HOST INTERFACE (TSC)

| Signal<br>Name       | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[31:3]              | I/O 3V | <b>ADDRESS BUS:</b> A[31:3] connect to the address bus of the CPU. During CPU cycles A[31:3] are inputs. These signals are driven by the TSC during cache snoop operations. Note that A[31:28] provide poweron/reset strapping options for the second level cache.                                                                                                                            |

| BE[7:0] <i>#</i>     | 13V    | <b>BYTE ENABLES:</b> The CPU byte enables indicate which byte lane the current CPU cycle is accessing. All eight byte lanes are provided to the CPU if the cycle is a cacheable read regardless of the state of $BE[7:0] #$ .                                                                                                                                                                 |

| ADS#                 | 13V    | ADDRESS STATUS: The CPU asserts ADS # to indicate that a new bus cycle is being driven.                                                                                                                                                                                                                                                                                                       |

| BRDY#                | O 3V   | <b>BUS READY:</b> The TSC asserts BRDY # to indicate to the CPU that data is available on reads or has been received on writes.                                                                                                                                                                                                                                                               |

| NA#                  | O 3V   | <b>NEXT ADDRESS:</b> When burst SRAMs are used in the second level cache or the second level cache is disabled, the TSC asserts NA# in T2 during CPU write cycles and with the first assertion of BRDY# during CPU linefills. NA# is never asserted if the second level cache is enabled with asynchronous SRAMs. NA# on the TSC must be connected to the CPU NA# pin for all configurations. |

| AHOLD                | O 3V   | <b>ADDRESS HOLD:</b> The TSC asserts AHOLD when a PCI master is accessing main memory. AHOLD is held for the duration of the PCI burst transfer. The TSC negates AHOLD when the PCI to main memory read/write cycles complete and during PCI peer transfers.                                                                                                                                  |

| EADS#                | O 3V   | <b>EXTERNAL ADDRESS STROBE:</b> Asserted by the TSC to inquire the first level cache when servicing PCI master accesses to main memory.                                                                                                                                                                                                                                                       |

| BOFF#                | O 3V   | <b>BACK OFF:</b> Asserted by the TSC when required to terminate a CPU cycle that was in progress.                                                                                                                                                                                                                                                                                             |

| HITM#                | 13V    | <b>HIT MODIFIED:</b> Asserted by the CPU to indicate that the address presented with the last assertion of EADS# is modified in the first level cache and needs to be written back.                                                                                                                                                                                                           |

| M/IO#, D/C#,<br>W/R# | 13V    | <b>MEMORY/IO; DATA/CONTROL; WRITE/READ:</b> Asserted by the CPU with ADS # to indicate the type of cycle on the host bus.                                                                                                                                                                                                                                                                     |

| HLOCK #              | 13V    | <b>HOST LOCK:</b> All CPU cycles sampled with the assertion of HLOCK# and ADS#, until the negation of HLOCK# must be atomic (i.e., no PCI activity to main memory is allowed).                                                                                                                                                                                                                |

| CACHE#               | 13V    | <b>CACHEABLE:</b> Asserted by the CPU during a read cycle to indicate the CPU can perform a burst line fill. Asserted by the CPU during a write cycle to indicate that the CPU will perform a burst write-back cycle. If CACHE# is asserted to indicate cacheability, the TSC asserts KEN# either with the first BRDY#, or with NA#, if NA# is asserted before the first BRDY#.               |

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KEN#/INV       | O 3V | CACHE ENABLE/INVALIDATE: KEN#/INV functions as both the KEN# signal<br>during CPU read cycles and the INV signal during first level cache snoop cycles.<br>During CPU cycles, KEN#/INV is normally low. The TSC drives KEN# high during the<br>first BRDY# or NA# assertion of a non-cacheable (in first level cache) CPU read<br>cycle.<br>The TSC drives INV high during the EADS# assertion of a PCI master DRAM write<br>snoop cycle and low during the EADS# assertion of a PCI master DRAM read snoop<br>cycle. |

| SMIACT#        | 1 3V | SYSTEM MANAGEMENT INTERRUPT ACTIVE: The CPU asserts SMIACT# when it<br>is in system management mode as a result of an SMI. After SMM space (located at<br>A0000h) is loaded and locked by BIOS, this signal must be sampled active with ADS#<br>for the processor to access the SMM space of DRAM.                                                                                                                                                                                                                    |

# 2.1.2 DRAM INTERFACE (TSC)

| Signal<br>Name | Туре | Description                                                                                              |

|----------------|------|----------------------------------------------------------------------------------------------------------|

| RAS[4:0]#      | O 3V | ROW ADDRESS STROBE: These pins select the DRAM row.                                                      |

| CAS[7:0]#      | O 3V | <b>COLUMN ADDRESS STROBE:</b> These pins always select which bytes are affected by a DRAM cycle.         |

| MA[11:2]       | O 3V | MEMORY ADDRESS: This is the row and column address for DRAM.                                             |

| MAA[1:0]       | O 3V | <b>MEMORY ADDRESS COPY A</b> : One copy of the MAs that change during a burst read or write of DRAM.     |

| MAB[1:0]       | O 3V | <b>MEMORY ADDRESS COPY B:</b> A second copy of the MAs that change during a burst read or write of DRAM. |

Concession of the local diversion of the loca

# 2.1.3 SECONDARY CACHE INTERFACE (TSC)

| Signal<br>Name | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CADV#/<br>CAA4 | O 3V   | <b>CACHE ADVANCE/CACHE ADDRESS 4 (COPY A):</b> This pin has two modes of operation depending on the type of SRAMs selected via hardware strapping options or programming the CC Register. The CAA4 mode is used when the L2 cache consists of asynchronous SRAMs. CAA4 is used to sequence through the Qwords in a cache line during a burst operation.                                                                                                         |

|                |        | CADV # mode is used when the L2 cache consists of burst SRAMs. In this mode, assertion causes the burst SRAM in the L2 cache to advance to the next Qword in the cache line.                                                                                                                                                                                                                                                                                    |

| CADS#/CAA3     | O 3V   | <b>CACHE ADDRESS STROBE/CACHE ADDRESS 3 (COPY A):</b> This pin has two modes of operation depending on the type of SRAMs selected via hardware strapping options or programming the CC Register. The CAA3 mode is used when the L2 cache consists of asynchronous SRAMs. CAA3 is used to sequence through the Qwords in a cache line during a burst operation.                                                                                                  |

|                |        | CADS # mode is used when the L2 cache consists of burst SRAMs. In this mode assertion causes the burst SRAM in the L2 cache to load the BSRAM address register from the BSRAM address pins.                                                                                                                                                                                                                                                                     |

| CAB3           | O 3V   | <b>CACHE ADDRESS 3 (COPY B):</b> CAB3 is used when the L2 cache consists of asynchronous SRAMs. CAB3 is used to sequence through the Qwords in a cache line during a burst operation                                                                                                                                                                                                                                                                            |

| CCS#/CAB4      | O 3V   | <b>CACHE CHIP SELECT/CACHE ADDRESS (COPY B):</b> This pin has two modes of operation depending on the type of SRAMs selected via hardware strapping options or programming the CC Register. The CAB4 mode is used when the L2 cache consists of asynchronous SRAMs. CAB4 is used to sequence through the Qwords in a cache line during a burst operation.                                                                                                       |

|                |        | A L2 cache consisting of burst SRAMs will power up, if necessary, and perform<br>an access if CCS# is asserted when CADS# is asserted. A L2 cache consisting<br>of burst SRAMs will power down if CCS# is negated when CADS# is asserted.<br>When CCS# is negated, a L2 cache consisting of burst SRAMs ignores ADS#. If<br>CCS# is asserted when ADS# is asserted, a L2 cache consisting of burst<br>SRAMs will power up, if necessary, and perform an access. |

| COE#           | O 3V   | <b>CACHE OUTPUT ENABLE</b> : The secondary cache data RAMs drive the CPU's data bus when COE# is asserted.                                                                                                                                                                                                                                                                                                                                                      |

| CWE[7:0]#      | O 3V   | <b>CACHE WRITE ENABLE:</b> Each CWE # corresponds to one byte lane. Assertion causes the byte lane to be written into the secondary cache data RAMs if they are powered up.                                                                                                                                                                                                                                                                                     |

| TIO[7:0]       | I/O 5V | <b>TAG ADDRESS:</b> These are inputs during CPU accesses and outputs during L2 cache line fills and L2 cache line invalidates due to inquire cycles. TIO[7:0] contain the L2 tag address for 256-Kbyte L2 caches. TIO[6:0] contains the L2 tag address and TIO7 contains the L2 cache valid bit for 512-Kbyte caches.                                                                                                                                           |

| TWE#           | O 5V   | TAG WRITE ENABLE: When asserted, new state and tag addresses are written into the external tag.                                                                                                                                                                                                                                                                                                                                                                 |

# 2.1.4 PCI INTERFACE (TSC)

| Signal<br>Name | Туре   | Description                                                                                                                                                                                                                                                          |

|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]       | 1/O 5V | <b>ADDRESS DATA BUS:</b> The standard PCI address and data lines. The address is driven with FRAME # assertion and data is driven or received in following clocks.                                                                                                   |

| C/BE[3:0] #    | I/O 5V | <b>COMMAND, BYTE ENABLE:</b> The command is driven with FRAME # assertion.<br>Byte enables corresponding to supplied or requested data are driven on following clocks.                                                                                               |

| FRAME#         | 1/O 5V | <b>FRAME:</b> Assertion indicates the address phase of a PCI transfer. Negation indicates that one more data transfer is desired by the cycle initiator.                                                                                                             |

| DEVSEL#        | 1/O 5V | <b>DEVICE SELECT:</b> The TSC drvies DEVSEL # when a PCI initiator attempts to access main memory. DEVSEL # is asserted at medium decode time.                                                                                                                       |

| IRDY#          | 1/O 5V | INITIATOR READY: Asserted when the initiator is ready for a data transfer.                                                                                                                                                                                           |

| TRDY#          | 1/O 5V | TARGET READY: Asserted when the target is ready for a data transfer.                                                                                                                                                                                                 |

| STOP#          | 1/O 5V | STOP: Asserted by the target to request the master to stop the current transaction.                                                                                                                                                                                  |

| LOCK#          | 1/O 5V | LOCK: Used to establish, maintain, and release resource locks on PCI.                                                                                                                                                                                                |

| REQ[3:0] #     | 15V    | REQUEST: PCI master requests for PCI.                                                                                                                                                                                                                                |

| GNT[3:0]#      | O 5V   | GRANT: Permission is given to the master to use PCI.                                                                                                                                                                                                                 |

| PHLD#          | I 5V   | <b>PCI HOLD</b> : This signal comes from the PIIX. PHLD# is the PIIX request for the PCI Bus. The TSC flushes the DRAM Write Buffers and acquires the host bus before granting PIIX via PHLDA#. This ensures that the guaranteed access time is met for ISA masters. |

| PHLDA#         | O 5V   | PCI HOLD ACKNOWLEDGE: This signal is driven by the TSC to grant PCI to the PIIX.                                                                                                                                                                                     |

| PAR            | 1/O 5V | PARITY: A single parity bit is provided over AD[31:0] and C/BE[3:0].                                                                                                                                                                                                 |

| RST#           | 15V    | <b>RESET:</b> When asserted, RST # resets the TSC and sets all register bits to the default value.                                                                                                                                                                   |

# 2.1.5 TDP INTERFACE (TSC)

| Signal<br>Name | Туре   | Description                                                                                                                                                                                                                                                                     |

|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLINK[15:0]    | I/O 3V | <b>PCI LINK:</b> These signals are connected to the PLINK data bus on the TDP. This is the data path between the TSC and TDP. Each TDP connects to one byte of the 16-bit bus.                                                                                                  |

| MSTB#          | O 3V   | MEMORY STROBE: Assertion causes data to be posted in the DRAM Write Buffer.                                                                                                                                                                                                     |

| MADV #         | O 3V   | <b>MEMORY ADVANCE:</b> For memory write cycles, assertion causes a Qword to be drained from the DRAM Write Buffer and the next data to be made available to the MD pins of the TDPs. For memory read cycles, assertion causes a Qword to be latched in the DRAM Input Register. |

| PCMD[1:0]      | O 3V   | PLINK COMMAND: This field controls how data is loaded into the PLINK input and output registers.                                                                                                                                                                                |

| HOE#           | O 3V   | HOST OUTPUT ENABLE: This signal is used as the output enable for the Host Data Bus.                                                                                                                                                                                             |

| MOE#           | O 3V   | <b>MEMORY OUTPUT ENABLE:</b> This signal is used as the output enable for the memory data bus. A buffered copy of MOE # also serves as a WE # select for the DRAM array.                                                                                                        |

| POE#           | O 3V   | <b>PLINK OUTPUT ENABLE:</b> This signal is used as the output enable for the PLINK Data Bus.                                                                                                                                                                                    |

# 2.1.6 CLOCKS (TSC)

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLKIN         | I 5V | <b>HOST CLOCK IN:</b> This pin receives a buffered host clock. This clock is used by all of the TSC logic that is in the Host clock domain. This should be the same clock net that is delivered to the CPU. The net should tee and have equal lengths from the tee to the CPU and the TSC. |

| PCLKIN         | 15V  | <b>PCI CLOCK IN:</b> This pin receives a buffered divide-by-2 host clock. This clock is used by all of the TSC logic that is in the PCI clock domain.                                                                                                                                      |

intel.

# 2.2 TDP Signals

# 2.2.1 DATA INTERFACE SIGNALS (TDP)

| Signal<br>Name | Туре      | Description                                                                                                                                                                              |

|----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HD[31:0]       | I/O 3V    | <b>HOST DATA</b> : These signals are connected to the CPU data bus. The CPU data bus is interleaved between the two TDPs for every byte, effectively creating an even and an odd TDP.    |

| MD[31:0]       | I/O 3V/5V | <b>MEMORY DATA:</b> These signals are connected to the DRAM data bus. The DRAM data bus is interleaved between the two TDPs for every byte, effectively creating an even and an odd TDP. |

| PLINK[7:0]     | I/O 3V    | <b>PCI LINK:</b> These signals are connected to the PLINK data bus on the TSC. This is the data path between the TSC and TDP. Each TDP connects to one byte of the 16-bit bus.           |

# 2.2.2 TSC INTERFACE SIGNALS (TDP)

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                     |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSTB#          | 1 3V | MEMORY STROBE: Assertion causes data to be posted in the DRAM Write Buffer.                                                                                                                                                                                                     |

| MADV#          | 13V  | <b>MEMORY ADVANCE:</b> For memory write cycles, assertion causes a Qword to be flushed from the DRAM Write Buffer and the next data to be made available to the MD pins of the TDPs. For memory read cycles, assertion causes a Qword to be latched in the DRAM Input register. |

| PCMD[1:0]      | 1 3V | PLINK COMMAND: This field controls how data is loaded into the PLINK input and output registers.                                                                                                                                                                                |

| HOE#           | 1 3V | HOST OUTPUT ENABLE: This signal is used as the output enable for the Host Data Bus.                                                                                                                                                                                             |

| MOE#           | 1 3V | <b>MEMORY OUTPUT ENABLE:</b> This signal is used as the output enable for the Memory Data Bus.                                                                                                                                                                                  |

| POE#           | 1 3V | <b>PLINK OUTPUT ENABLE:</b> This signal is used as the output enable for the PLINK Data Bus.                                                                                                                                                                                    |

# 2.2.3 CLOCK SIGNAL (TDP)

| Signal<br>Name | Туре | Description                                             |

|----------------|------|---------------------------------------------------------|

| HCLK           | I 5V | HOST CLOCK: Primary clock input used to drive the part. |

# 2.3 Signal State During Reset

Table 1 shows the state of all TSC and TDP output and bi-directional signals during a hard reset (RST# asserted). The TSC samples the strapping options on the A[31:28] signal lines on the rising edge of RST#. When RST# is asserted, the TSC enables the TDP outputs via the HOE#, MOE#, and POE# TSC/TDP interface signals. When RST# is negated, the TSC resets the TDP logic by driving HOE#, MOE#, and POE# inactive for two HCLKs.

| Signal     | State |

|------------|-------|

| TSC        |       |

| A[31:28]   | Input |

| A[27:3]    | Low   |

| BRDY#      | High  |

| NA#        | High  |

| AHOLD      | High  |

| EADS#      | High  |

| BOFF#      | High  |

| KEN#/INV   | Low   |

| RAS[4:0] # | Low   |

| CAS[7:0]#  | Low   |

| MA[11:2]   | Low   |

| MAA[1:0]   | Low   |

| MAB[1:0]   | Low   |

| CADV#/CAA4 | High  |

| CADS#/CAA3 | High  |

| Table 1. Output | t and I/O Signa | al States Duri | ng Hard Reset |

|-----------------|-----------------|----------------|---------------|

| Tuble II output |                 |                | ig hala hooot |

| Jų | tput and 1/O Signal States During |           |  |

|----|-----------------------------------|-----------|--|

|    | Signal                            | State     |  |

|    | CCS#/CAB4                         | High      |  |

|    | CAB3                              | High      |  |

|    | COE#                              | High      |  |

|    | CWE[7:0] #                        | High      |  |

|    | TIO[7:0] #                        | Tri-state |  |

|    | TWE#                              | High      |  |

|    | AD[31:0]                          | Low       |  |

|    | C/BE[3:0] #                       | Low       |  |

|    | FRAME#                            | Tri-state |  |

|    | DEVSEL#                           | Tri-state |  |

|    | IRDY#                             | Tri-state |  |

|    | TRDY#                             | Tri-state |  |

|    | STOP#                             | Tri-state |  |

|    | LOCK#                             | Tri-state |  |

|    | GNT[3:0]#                         | Tri-state |  |

|    | PHLDA#                            | Tri-state |  |

|    |                                   |           |  |

| d Heset     |           |  |

|-------------|-----------|--|

| Signal      | State     |  |

| PAR         | Low       |  |

| PLINK[15:0] | Low       |  |

| MSTB#       | High      |  |

| MADV#       | High      |  |

| PCMD[1:0]   | High      |  |

| HOE#        | High      |  |

| MOE#        | Low       |  |

| POE#        | Low       |  |

| TDP         |           |  |

| HD[31:0]    | Low       |  |

| MD[31:1]    | Low       |  |

| MD0         | NAND Tree |  |

|             | Output    |  |

| PLINK[7:0]  | Low       |  |

# 3.0 REGISTER DESCRIPTION

The TSC contains two sets of software accessible registers (Control and Configuration registers), accessed via the Host CPU I/O address space. Control Registers control access to PCI configuration space. Configuration Registers reside in PCI configuration space and specify PCI configuration, DRAM configuration, cache configuration, operating parameters, and optional system features.

The TSC internal registers (both I/O Mapped and Configuration registers) are only accessible by the Host CPU and cannot be accessed by PCI masters. The registers can be accessed as Byte, Word (16-bit), or Dword (32-bit) quantities, with the exception of CONFADD which can only be accessed as a Dword. All multi-byte numeric fields use "little-endian" ordering (i.e., lower addresses contain the least significant parts of the field). The following nomenclature is used for access attributes.

- **RO Read Only**. If a register is read only, writes to this register have no effect.

- **R/W Read/Write.** A register with this attribute can be read and written.

- R/WC Read/Write Clear. A register bit with this attribute can be read and written. However, a write of 1 clears (sets to 0) the corresponding bit and a write of 0 has no effect.

Some of the TSC registers described in this section contain reserved bits. Software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back.

In addition to reserved bits within a register, the TSC contains address locations in the PCI configuration space that are marked "Reserved" (Table 2). The TSC responds to accesses to these address locations by completing the Host cycle. Software should not write to reserved TSC configuration locations in the device-specific region (above address offset 3Fh).

During a hard reset (RST# asserted), the TSC sets its internal configuration registers to predetermined **default** states. The default state represents the minimum functionality feature set required to successfully bring up the system. Hence, it does not represent the optimal system configuration. It is the responsibility of the system initialization software (usually BIOS) to properly determine the DRAM configurations, cache configuration, operating parameters and optional system features that are applicable, and to program the TSC registers accordingly.

# 3.1 Control Registers

The TSC contains two registers that reside in the CPU I/O address space—the Configuration Address (CONFADD) Register and the Configuration Data (CONFDATA) Register. These registers can not reside in PCI configuration space because of the special functions they perform. The Configuration Address Register enables/disables the configuration space and determines what portion of configuration space is visible through the Configuration Data window.

## 3.1.1 CONFADD—CONFIGURATION ADDRESS REGISTER

I/O Address: 0CF8h (Dword access only)

Default Value: 00000000h

Access: Read/Write

CONFADD is a 32-bit register accessed only when referenced as a Dword. A Byte or Word reference will "pass through" the Configuration Address Register to the PCI Bus. The CONFADD Register contains the Bus Number, Device Number, Function Number, and Register Number for which a subsequent configuration access is intended.

| Bit   | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Configuration Enable (CONE): 1 = Enable; 0 = Disable.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 30:24 | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 23:16 | <b>Bus Number (BUSNUM):</b> When BUSNUM is programmed to 00h, the target of the configuration cycle is either the TSC or the PCI Bus that is directly connected to the TSC, depending on the Device Number field. If the Bus Number is programmed to 00h and the TSC is not the target, a type 0 configuration cycle is generated on PCI. If the Bus Number is non-zero, a type 1 configuration cycle is generated on PCI with the Bus Number mapped to AD[23:16] during the address phase.              |

| 15:11 | <b>Device Number (DEVNUM):</b> This field selects one agent on the PCI Bus selected by the Bus Number. During a Type 1 Configuration cycle, this field is mapped to AD[15:11]. During a Type 0 configuration cycle, this field is decoded and one of AD[31:11] is driven to 1. The TSC is always Device Number 0.                                                                                                                                                                                        |

| 10:8  | <b>Function Number (FUNCNUM):</b> This field is mapped to AD[10:8] during PCI configuration cycles. This allows the configuration registers of a particular function in a multi-function device to be accessed. The TSC responds to configuration cycles with a function number of 000b; all other function number values attempting access to the TSC (Device Number = 0, Bus Number = 0) generate a type 0 configuration cycle on the PCI Bus with no IDSEL asserted, which results in a master abort. |

| 7:2   | <b>Register Number (REGNUM):</b> This field selects one register within a particular bus, device, and function as specified by the other fields in the Configuration Address Register. This field is mapped to AD[7:2] during PCI configuration cycles.                                                                                                                                                                                                                                                  |

| 1:0   | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# 3.1.2 CONFDATA—CONFIGURATION DATA REGISTER

I/O Address: CFCh Default Value: 0000000h Access: Read/Write

CONFDATA is a 32-bit read/write window into configuration space. The portion of configuration space that is referenced by CONFDATA is determined by the contents of CONFADD.

| Bit | Descriptions                                                                                                                                                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | <b>Configuration Data Window (CDW):</b> If bit 31 of CONFADD is 1, any I/O reference in the CONFDATA I/O space is mapped to configuration space using the contents of CONFADD. |

# 3.2 PCI Configuration Registers

The PCI Bus defines a slot based "configuration space" that allows each device to contain up to 256 8-bit configuration registers. The PCI specification defines two bus cycles to access the PCI configuration space—**Configuration Read** and **Configuration Write**. While memory and I/O spaces are supported by the Pentium microprocessor, configuration space is not supported. The PCI specification defines two mechanisms to access configuration space, Mechanism #1 and Mechanism #2. The TSC only supports Mechanism #1. Table 2 shows the TSC configuration space.

The configuration access mechanism makes use of the CONFADD Register and CONFDATA Register. To reference a configuration register, a Dword I/O write cycle is used to place a value into CONFADD that specifies the PCI Bus, the device on that bus, the function within the device, and a specific configuration register of the device function being accessed. CONFADD[31] must be 1 to enable a configuration cycle. Then, CONFDATA becomes a window onto four bytes of configuration space specified by the contents of CONFADD. Read/write accesses to CONFDATA generates a PCI configuration cycle to the address specified by CONFADD.

## **Type 0 Access**

If the Bus Number field of CONFADD is 0, a type 0 configuration cycle is generated on PCI. CONFADD[10:2] is mapped directly to AD[10:2]. The Device Number field of CONFADD is decoded onto AD[31:11]. The TSC is Device #0 and does not pass its configuration cycles to PCI. Thus, AD11 is never asserted. (For accesses to device #1, AD12 is asserted, etc., to Device #20 which asserts AD31.) Only one AD line is asserted at a time. All device numbers higher than 20 cause a type 0 configuration access with no IDSEL asserted, which results in a master abort.

### **Type 1 Access**

If the Bus Number field of CONFADD is non-zero, a type 1 configuration cycle is generated on PCI. CONFADD[23:2] are mapped directly to AD[23:2]. AD[1:0] are driven to 01 to indicate a Type 1 Configuration cycle. All other lines are driven to 0.

# 82437FX TSC AND 82438FX TDP

r

| Address Offset | Symbol   | Register Name                            | Access   |

|----------------|----------|------------------------------------------|----------|

| 00–01h         | VID      | Vendor Identification                    | RO       |

| 02-03h         | DID      | Device Identification                    | RO       |

| 04–05h         | PCICMD   | Command Register                         | R/W      |

| 06–07h         | PCISTS   | Status Register                          | RO, R/WC |

| 08h            | RID      | Revision Identification                  | RO       |

| 09h            |          | Reserved                                 |          |

| 0Ah            | SUBC     | Sub-Class Code                           | RO       |

| 0Bh            | BCC      | Base Class Code                          | RO       |

| 0Ch            |          | Reserved                                 |          |

| 0Dh            | MLT      | Master Latency Timer                     | R/W      |

| 0Eh            |          | Reserved                                 |          |

| 0Fh            | BIST     | BIST Register                            | R/W      |

| 10-49h         |          | Reserved                                 |          |

| 50h            | PCON     | PCI Control Register                     | R/W      |

| 51h            |          | Reserved                                 |          |

| 52h            | CC       | Cache Control                            | R/W      |

| 53–56h         |          | Reserved                                 |          |

| 57h            | DRAMC    | DRAM Control                             | R/W      |

| 58h            | DRAMT    | DRAM Timing                              | R/W      |

| 59–5Fh         | PAM[6:0] | Programmable Attribute Map (7 registers) | R/W      |

| 60-64h         | DRB[4:0] | DRAM Row Boundary (5 registers)          | R/W      |

| 65–67h         |          | Reserved                                 |          |

| 68h            | DRT      | DRAM Row Type                            | R/W      |

| 69–71h         |          | Reserved                                 |          |

| 72h            | SMRAM    | System Management RAM Control            | R/W      |

| 73-FFh         |          | Reserved                                 |          |

# Table 2. TSC Configuration Space

# 3.2.1 VID-VENDOR IDENTIFICATION REGISTER

Address Offset: 00–01h Default Value: 8086h Attribute: Read Only

The VID Register contains the vendor identification number. This 16-bit register combined with the Device Identification Register uniquely identify any PCI device. Writes to this register have no effect.

| Bit  | Description                                                             |

|------|-------------------------------------------------------------------------|

| 15:0 | Vendor Identification Number: This is a 16-bit value assigned to Intel. |

## 3.2.2 DID-DEVICE IDENTIFICATION REGISTER

Address Offset: 02–03h Default Value: 122Dh Attribute: Read Only

This 16-bit register combined with the Vendor Identification register uniquely identifies any PCI device. Writes to this register have no effect.

| Bit  | Description                                                               |

|------|---------------------------------------------------------------------------|

| 15:0 | Device Identification Number. This is a 16-bit value assigned to the TSC. |

### 3.2.3 PCICMD—PCI COMMAND REGISTER

Address Offset: 04–05h Default: 06h Access: Read/Write

This register controls the TSC's ability to respond to PCI cycles.

| Bit   | Descriptions                                                                                                                                                                               |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:10 | Reserved.                                                                                                                                                                                  |

| 9     | Fast Back-to-Back: (Not Implemented) This bit is hardwired to 0.                                                                                                                           |

| 8     | SERR# Enable (SERRE): (Not Implemented) This bit is hardwired to 0.                                                                                                                        |

| 7     | Address/Data Stepping: (Not Implemented) This bit is hardwired to 0.                                                                                                                       |

| 6     | Parity Error Enable (PERRE): (Not Implemented) This bit is hardwired to 0.                                                                                                                 |

| 5:3   | Reserved: These bits are hardwired to 0.                                                                                                                                                   |

| 2     | Bus Master Enable (BME): (Not Implemented) The TSC does not support disabling of its bus master capability on the PCI Bus. This bit is hardwired to 1.                                     |

| 1     | <b>Memory Access Enable (MAE):</b> 1 = Enable PCI master access to main memory, if the PCI address selects enabled DRAM space; 0 = Disable (TSC does not respond to main memory accesses). |

| 0     | I/O Access Enable (IOAE): (Not Implemented) This bit is hardwired to 0. The TSC does not respond to PCI I/O cycles.                                                                        |

# 3.2.4 PCISTS—PCI STATUS REGISTER

Address Offset: 06-07h

Default Value: 0200h

Access: Read Only, Read/Write Clear

PCISTS reports the occurrence of a PCI master abort and PCI target abort. PCISTS also indicates the DEVSEL# timing that has been set by the TSC hardware.

| Bit  | Descriptions                                                                                                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Detected Parity Error (DPE): (Not Implemented) This bit is hardwired to 0.                                                                                                                                                             |

| 14   | Signaled System Error (SSE)R/WC: This bit is hardwired to 0.                                                                                                                                                                           |

| 13   | <b>Received Master Abort Status (RMAS)—R/WC:</b> When the TSC terminates a Host-to-PCI transaction (TSC is a PCI master) with an unexpected master abort, this bit is set to 1.                                                        |

|      | NOTE:                                                                                                                                                                                                                                  |

|      | Master abort is the normal and expected termination of PCI special cycles. Software sets this<br>bit to 0 by writing 1 to it.                                                                                                          |

| 12   | <b>Received Target Abort Status (RTAS)—R/WC:</b> When a TSC-initiated PCI transaction is terminated with a target abort, RTAS is set to 1. Software sets RTAS to 0 by writing 1 to it.                                                 |

| 11   | Signaled Target Abort Status (STAS): This bit is hardwired to 0. The TSC never terminates a PCI cycle with a target abort.                                                                                                             |

| 10:9 | <b>DEVSEL # Timing (DEVT)—RO:</b> This 2-bit field indicates the timing of the DEVSEL # signal when the TSC responds as a target, and is hard-wired to the value 01b (medium) to indicate the slowest time that DEVSEL # is generated. |

| 8    | Data Parity Detected (DPD)-R/WC: This bit is hardwired to 0                                                                                                                                                                            |

| 7    | Fast Back-to-Back (FB2B): (Not Implemented) This bit is hardwired to 0.                                                                                                                                                                |

| 6:0  | Reserved.                                                                                                                                                                                                                              |

# 3.2.5 RID-REVISION IDENTIFICATION REGISTER

Address Offset:08hDefault Value:See stepping information documentAccess:Read Only

This register contains the revision number of the TSC.

| Bit | Description                                                                                                                  |

|-----|------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | <b>Revision Identification Number:</b> This is an 8-bit value that indicates the revision identification number for the TSC. |

# 82437FX TSC AND 82438FX TDP

# intel

### 3.2.6 SUBC-SUB-CLASS CODE REGISTER

Address Offset: 0Ah Default Value: 00h Access: Read Only

This register indicates the function sub-class in relation to the Base Class Code.

| Bit | Description                               |  |  |  |  |  |

|-----|-------------------------------------------|--|--|--|--|--|

| 7:0 | Sub-Class Code (SUBC): 00h = Host bridge. |  |  |  |  |  |

# 3.2.7 BCC-BASE CLASS CODE REGISTER

Address Offset: 0Bh Default Value: 06h Access: Read Only

This register contains the Base Class Code of the TSC.

|   | Bit | Description                                   |

|---|-----|-----------------------------------------------|

| Γ | 7:0 | Base Class Code (BASEC): 06h = Bridge device. |

#### 3.2.8 MLT-MASTER LATENCY TIMER REGISTER

Address Offset: 0Dh

Default Value: 00h

Access: Read/Write

MLT is an 8-bit register that controls the amount of time the TSC, as a bus master, can burst data on the PCI Bus. The Count Value is an 8-bit quantity. However, MLT[2:0] are hardwired to 0. MLT is also used to guarantee the host CPU a minimum amount of the system resources as described in the PCI Bus Arbitration section.

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | <b>Master Latency Timer Count Value:</b> The number of clocks programmed in the MLT represents the minimum guaranteed time slice (measured in PCI clocks) allotted to the TSC, after which it must surrender the bus as soon as other PCI masters are granted the bus. The default value of MLT is 00h or 0 PCI clocks. The MLT should always be programmed to a non-zero value. |

| 2:0 | Reserved: Hardwired to 0.                                                                                                                                                                                                                                                                                                                                                        |

# 3.2.9 BIST-BIST REGISTER

| Address Offset: | 0Fh        |

|-----------------|------------|

| Default:        | 00h        |

| Access:         | Read/Write |

The Built In Self Test (BIST) function is not supported by the TSC. Writes to this register have no affect.

| Bit | Descriptions                                                                         |  |  |

|-----|--------------------------------------------------------------------------------------|--|--|

| 7   | ST Supported—RO: 00h = Disable BIST function.                                        |  |  |

| 6   | start BIST: This function is not supported and writes have no affect.                |  |  |

| 5:4 | Reserved.                                                                            |  |  |

| 3:0 | Completion Code—RO: This field always returns 0 when read and writes have no affect. |  |  |

# 3.2.10 PCON-PCI CONTROL REGISTER

| Address Offset: | 50h        |

|-----------------|------------|

| Default:        | 00h        |

| Access:         | Read/Write |

The PCON Register enables and disables features related to the PCI unit operation not already covered in the PCI required configuration space.

| Bit | Descriptions                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:5 | <b>CPU Inactivity Timer Bits:</b> This field selects the value used in the CPU Inactivity Timer. This timer counts CPU inactivity in PCI clocks. The inactivity window is defined as the last BRDY # to the next ADS #. When active, the CPU is default owner of the PCI Bus. If the CPU is inactive, PHOLD and the REQx # lines are given priority. |  |  |  |  |

|     | Bits[7:5] PCI Clocks                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|     | 000 1                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|     | 001 2                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|     | 010 3*                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|     | 011 4                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|     | 100 5*                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|     | 101 6                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|     | 110 7                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|     | 111 8                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|     | * Recommended settings                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 4   | Reserved.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 3   | <b>Peer Concurrency Enable Bit (PCE):</b> 1 = Peer Concurrency enabled. 0 = Peer Concurrency disabled. This bit is normally programmed to 1.                                                                                                                                                                                                         |  |  |  |  |

| 2   | <b>CPU-to-PCI Write Bursting Disable Bit:</b> 0 = CPU-to-PCI Write bursting enabled. 1 = CPU-to-PCI Write bursting disabled.                                                                                                                                                                                                                         |  |  |  |  |

| 1   | PCI Streaming Bit: 0 = PCI streaming enabled. 1 = PCI streaming disabled.                                                                                                                                                                                                                                                                            |  |  |  |  |

| 0   | Bus Concurrency Disable Bit: 0 = Bus concurrency enabled. 1 = Bus concurrency disabled.                                                                                                                                                                                                                                                              |  |  |  |  |

inte

# 3.2.11 CC-CACHE CONTROL REGISTER

Address Offset: 52h

Default: SSSS0010 (S = Strapping option) Access: Read/Write

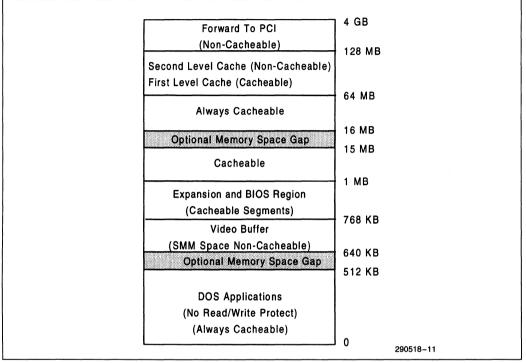

The CC Register selects the secondary cache operations. This register enables/disables the L2 cache, adjusts cache size, defines the cache SRAM type, and controls tag initialization. After a hard reset, CC[7:4] reflect the inverted signal levels on the host address lines A[31:28].