# **User's Manual**

# $\mu$ PD720101

**USB 2.0 Host Controller**

# [MEMO]

#### NOTES FOR CMOS DEVICES —

#### (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### ③ PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### (5) POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### **(6)** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

USB logo is a trademark of USB Implementers Forum, Inc.

Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

- The information in this document is current as of September, 2004. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# Main Revisions in this Edition

| Page         | Description                                             |

|--------------|---------------------------------------------------------|

| pp. 69 to 73 | Change of <b>Note</b>                                   |

| p. 125       | Change of Table 8-1 Semantics for Each Byte/Bit in Page |

The mark ★ shows major revised points.

#### **PREFACE**

Readers This manual is intended for engineers who need to be familiar with the capability of

the  $\mu$ PD720101 in order to develop application systems based on it.

Purpose The purpose of this manual is to help users understand the hardware capabilities

(listed below) of the  $\mu$ PD720101.

**Configuration** This manual consists of the following chapters:

Introduction

- Pin functions

- Information for NAND-tree test mode

- · Register information

- · OHCI host controller

- EHCI host controller

- Power management

- · How to write external serial ROM

- · How to connect to external elements

- Product specifications

Guidance Readers of this manual should already have a general knowledge of electronics, logic

circuits, and microcomputers.

**Notation** This manual uses the following conventions:

Data bit significance: High-order bits on the left side;

low-order bits on the right side

Active low: XXXX0 (Pin and signal names are suffixed with 0.)

**Note**: Explanation of an indicated part of text

**Caution**: Information requiring the user's special attention

**Remark**: Supplementary information Numerical value: Binary ... xxxx or xxxxb

Decimal ... xxxx

Hexadecimal ... xxxxh

The related documents indicated in this publication may include preliminary versions.

However, preliminary versions are not marked as such.

• μPD720101 Data Sheet: S16265E

# **CONTENTS**

| CHAPTER 1 INTRODUCTION                                                         | 13 |

|--------------------------------------------------------------------------------|----|

| 1.1 Features                                                                   | 13 |

| 1.2 Ordering Information                                                       | 13 |

| 1.3 Block Diagram                                                              | 14 |

| 1.4 Pin Configuration                                                          | 16 |

| CHAPTER 2 PIN FUNCTIONS                                                        | 22 |

| 2.1 Pin Functions for 144-pin LQFP                                             | 22 |

| 2.1.1 Power supply                                                             | 22 |

| 2.1.2 Analog signaling                                                         | 22 |

| 2.1.3 PCI interface                                                            | 23 |

| 2.1.4 System clock & reset for power management                                | 23 |

| 2.1.5 USB interface                                                            | 24 |

| 2.1.6 Legacy support interface                                                 |    |

| 2.1.7 Serial ROM interface                                                     | 25 |

| 2.1.8 Test signals                                                             | 25 |

| 2.2 Pin Functions for 144-pin FBGA                                             |    |

| 2.2.1 Power supply                                                             |    |

| 2.2.2 Analog signaling                                                         |    |

| 2.2.3 PCI interface                                                            |    |

| 2.2.4 System clock & reset for power management                                | 28 |

| 2.2.5 USB interface                                                            |    |

| 2.2.6 Legacy support interface                                                 |    |

| 2.2.7 Serial ROM interface                                                     |    |

| 2.2.8 Test signals                                                             | 29 |

| CHAPTER 3 INFORMATION FOR NAND-TREE TEST MODE                                  | 30 |

|                                                                                |    |

| CHAPTER 4 REGISTER INFORMATION                                                 | 32 |

| 4.1 PCI Configuration Space                                                    | 32 |

| 4.1.1 PCI configuration space for OHCI host controller #1                      |    |

| 4.1.2 PCI configuration space for OHCI host controller #2                      |    |

| 4.1.3 PCI configuration space for EHCI host controller                         |    |

| 4.2 OHCI Operational Registers                                                 |    |

| 4.2.1 Mapping of operational registers for OHCl host controller #1             | 58 |

| 4.2.2 Mapping of operational registers for OHCI host controller #2             |    |

| 4.2.3 Overview of OHCI operational registers                                   |    |

| 4.3 EHCI Capability and Operational Registers                                  |    |

| 4.3.1 Mapping of capability and operational registers for EHCl host controller |    |

| 4.3.2 Overview of EHCI capability and operational registers                    |    |

| 4.4 Legacy Function Registers                                                  |    |

| 4.4.1 Overview of legacy function registers                                    |    |

|                                                                                |    |

| CHAPTER 5 OHCI HOST CONTROLLER                                                 | 92 |

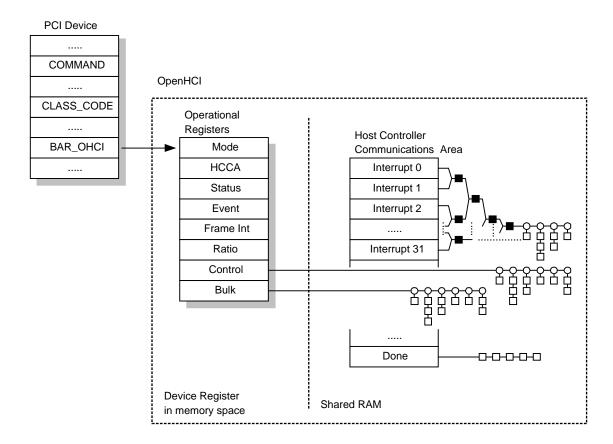

| 5.1 Communication Between OHCI Host Controller and HCD                         |    |

| 5.2 Endpoint Descriptor                                                   | 93  |

|---------------------------------------------------------------------------|-----|

| 5.2.1 Endpoint descriptor format                                          | 93  |

| 5.2.2 Endpoint descriptor field definitions                               | 93  |

| 5.3 Transfer Descriptors                                                  | 95  |

| 5.3.1 General transfer descriptor format                                  | 95  |

| 5.3.2 General transfer descriptor field definitions                       | 95  |

| 5.3.3 Isochronous transfer descriptor format                              | 97  |

| 5.3.4 Isochronous transfer descriptor field definitions                   | 97  |

| 5.3.5 Packet status word format                                           | 98  |

| 5.3.6 Packet status word field definitions                                | 98  |

| 5.3.7 Completion code definitions                                         | 98  |

| 5.4 Host Controller Communications Area                                   | 99  |

| 5.4.1 Host controller communications area format                          | 99  |

| 5.4.2 Host controller communications area description                     | 99  |

| CHAPTER 6 EHCI HOST CONTROLLER                                            | 100 |

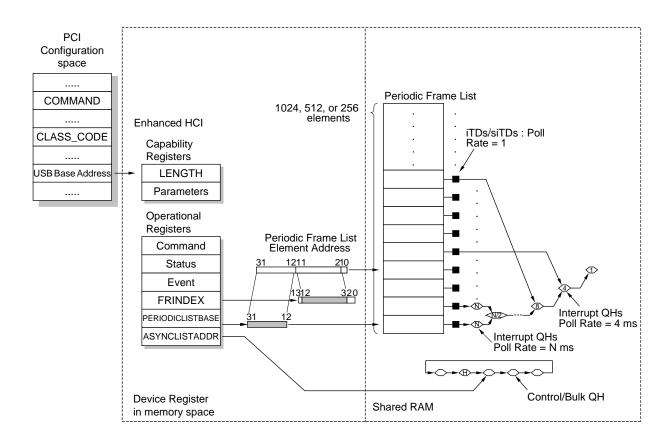

| 6.1 Control EHCI Host Controller by HCD                                   | 100 |

| 6.2 Isochronous Transfer Descriptor                                       | 100 |

| 6.2.1 Isochronous transfer descriptor format                              | 100 |

| 6.2.2 Isochronous transfer descriptor field definitions                   | 101 |

| 6.3 Split Transaction Isochronous Transfer Descriptor                     | 103 |

| 6.3.1 Split transaction isochronous transfer descriptor format            | 103 |

| 6.3.2 Split transaction isochronous transfer descriptor field definitions | 103 |

| 6.4 Queue Element Transfer Descriptor                                     | 105 |

| 6.4.1 Queue element transfer descriptor format                            | 105 |

| 6.4.2 Queue element transfer descriptor field definitions                 | 105 |

| 6.5 Queue Head                                                            | 107 |

| 6.5.1 Queue head format                                                   | 107 |

| 6.5.2 Queue head field definitions                                        | 107 |

| 6.6 Periodic Frame Span Traversal Node (FSTN)                             | 109 |

| 6.6.1 Periodic frame span traversal node descriptor format                | 109 |

| 6.6.2 Periodic frame span traversal node field definitions                | 109 |

| CHAPTER 7 POWER MANAGEMENT                                                | 110 |

| 7.1 Bus Power States and Function Power Management States                 | 110 |

| 7.1.1 PCI bus power states                                                | 110 |

| 7.1.2 USB bus states                                                      | 110 |

| 7.1.3 PCI function power management states                                |     |

| 7.2 Power Management Event                                                |     |

| 7.2.1 PME event support                                                   | 111 |

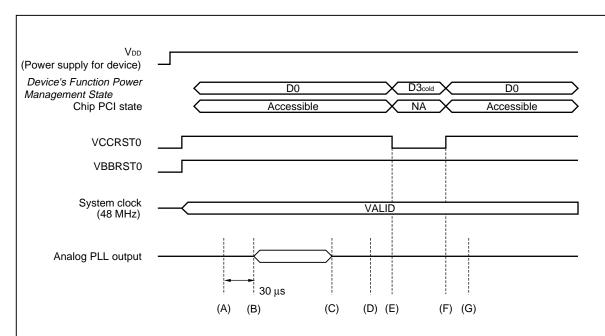

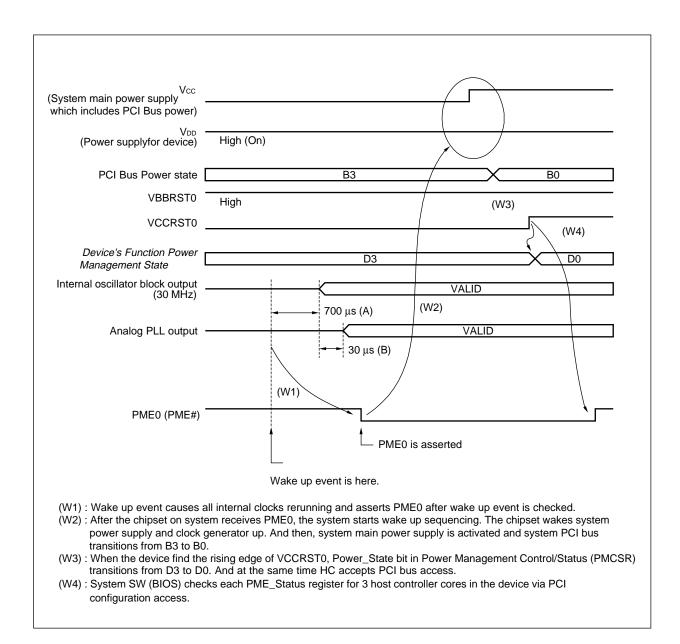

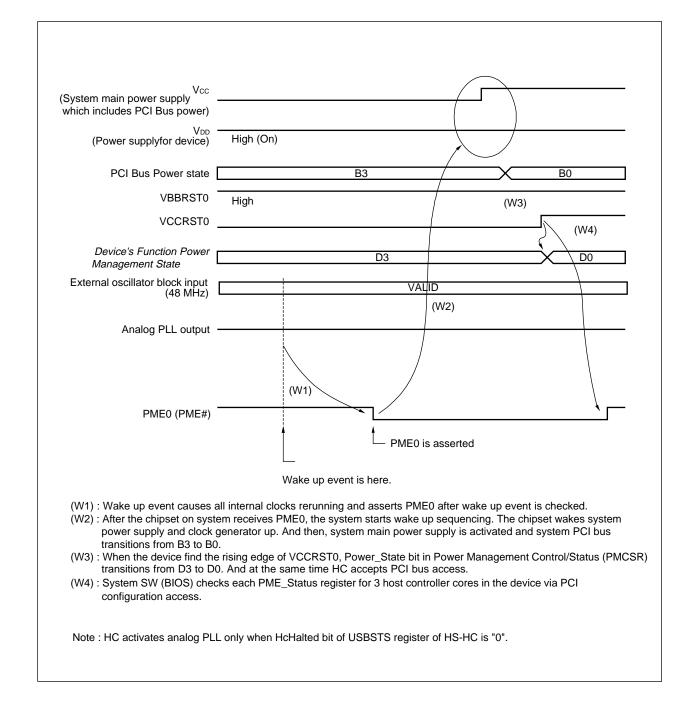

| 7.2.2 How to support the transition from D3cold to D0                     | 111 |

| 7.2.3 PME0 assertion                                                      |     |

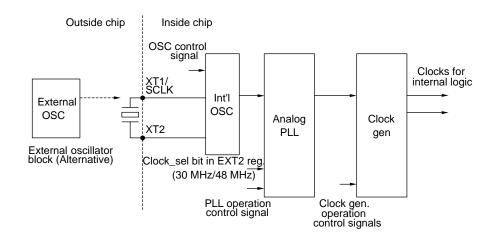

| 7.3 Control for System Clock Operation                                    |     |

| 7.3.1 Clock system                                                        |     |

| 7.3.2 Condition for clock system stopping/resuming                        |     |

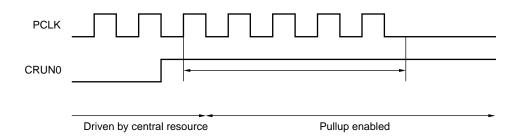

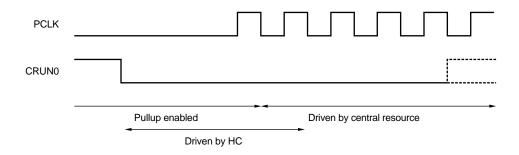

| 7.3.3 CLKRUN# support                                                     | 121 |

| CHAPTER 8 HOW TO WRITE EXTERNAL SERIAL ROMROWN       |     |

|------------------------------------------------------|-----|

| 8.1 Registers to Control I <sup>2</sup> C Interface  | 123 |

| 8.2 Supported Command for I <sup>2</sup> C Interface | 124 |

| CHAPTER 9 HOW TO CONNECT TO EXTERNAL ELEMENTS        |     |

| 9.1 Handling Unused Pins                             | 128 |

| 9.2 USB Port Connection                              | 129 |

| 9.3 PLL Circuit Connection                           |     |

| 9.4 X'tal Connection                                 | 130 |

| 9.5 External Serial ROM Connection                   | 131 |

| CHAPTER 10 PRODUCT SPECIFICATIONS                    |     |

| 10.1 Buffer List                                     |     |

| 10.2 Terminology                                     |     |

| 10.3 Electrical Specifications                       | 134 |

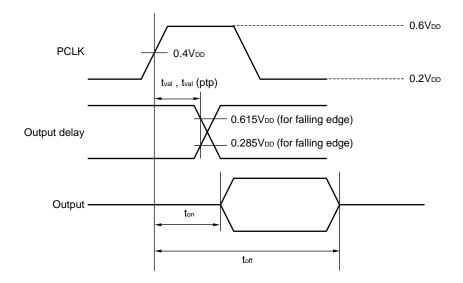

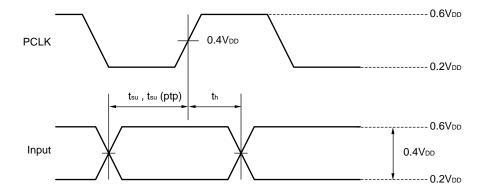

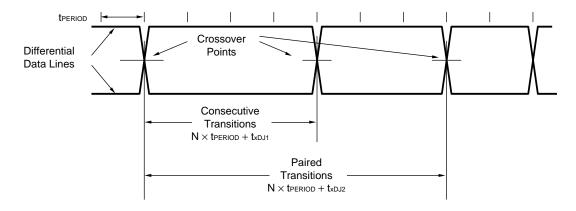

| 10.4 Timing Diagram                                  |     |

# LIST OF FIGURES

| Figure No.                              | Title                                            | Page |

|-----------------------------------------|--------------------------------------------------|------|

| 3-1 NAND-Tree Circuitry                 |                                                  | 30   |

| 4-1 OpenHCl's PCl Configuration Sp      | pace                                             | 57   |

| 4-2 Enhanced HCl's PCI Configurati      | on Space                                         | 74   |

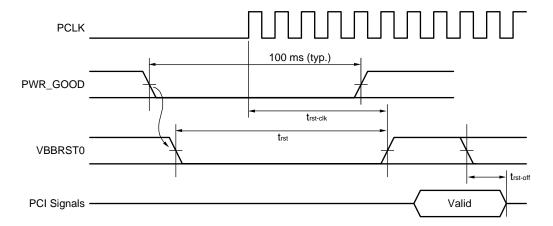

| 7-1 Wake Up State Transition from [     | 03cold (Using 30-MHz X'tal)                      | 113  |

| 7-2 Wake Up State Transition from D     | 03cold (Using 48-MHz Oscillator)                 | 114  |

| 7-3 $\mu$ PD720101's Clock System       |                                                  | 119  |

| 7-4 Clock Operation Diagram (Using      | 30-MHz X'tal)                                    | 120  |

| 7-5 Clock Operation Diagram (Using      | 48-MHz Oscillator)                               | 121  |

| 7-6 PCI Clock Stop                      |                                                  | 122  |

| 7-7 PCI Clock Start                     |                                                  | 122  |

| 7-8 Maintaining PCI Clock               |                                                  | 122  |

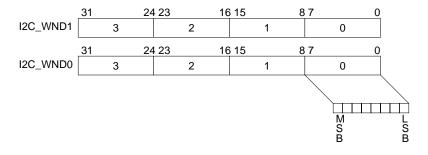

| 8-1 I2C_WND0/1 vs. Byte No              |                                                  | 125  |

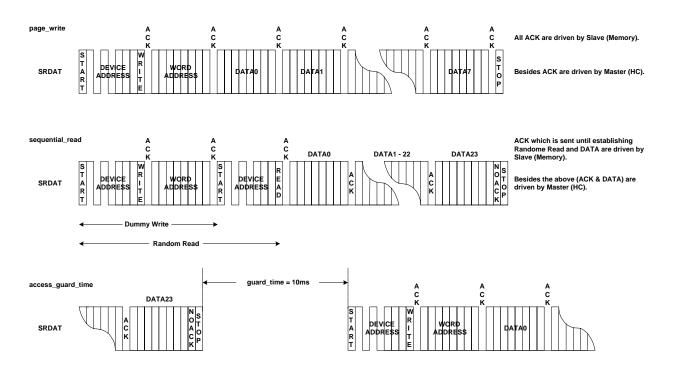

| 8-2 I <sup>2</sup> C Timing Chart       |                                                  | 126  |

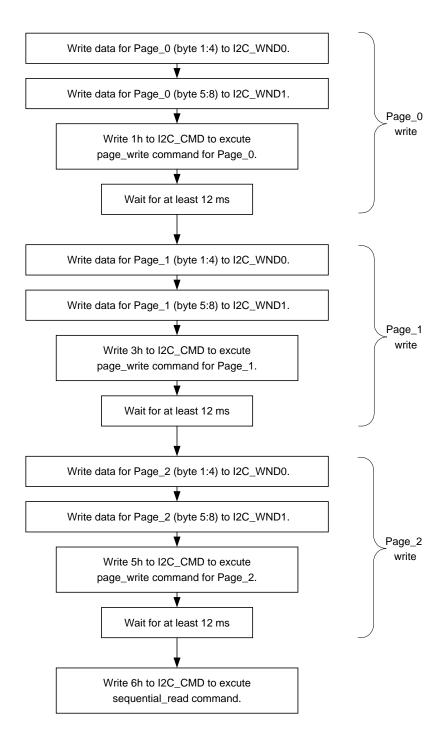

| 8-3 External Serial ROM Setting Flo     | wchart                                           | 127  |

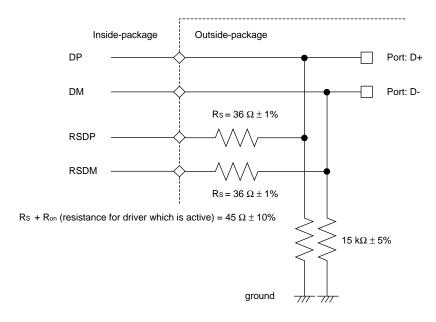

| 9-1 USB Downstream Port Connecti        | on                                               | 129  |

| 9-2 RREF Connection                     |                                                  | 129  |

| 9-3 X'tal Connection                    |                                                  | 130  |

| 9-4 External Serial ROM Connection      |                                                  | 131  |

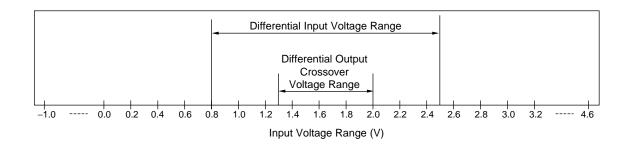

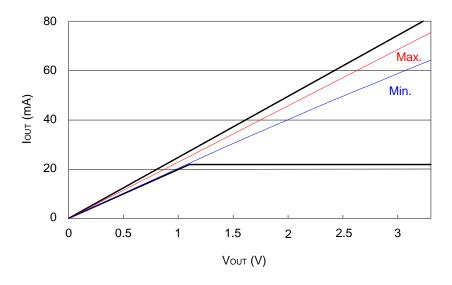

| 10-1 Differential Input Sensitivity Rai | nge for Low-/Full-speed                          | 137  |

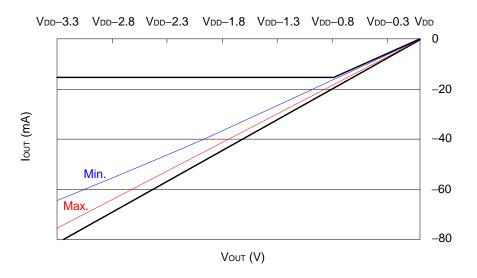

| 10-2 Full-speed Buffer VOH/IOH Cha      | aracteristics for High-speed Capable Transceiver | 137  |

| 10-3 Full-speed Buffer VOL/IOL Cha      | racteristics for High-speed Capable Transceiver  | 137  |

| 10-4 Receiver Sensitivity for Transce   | eiver at DP/DM                                   | 138  |

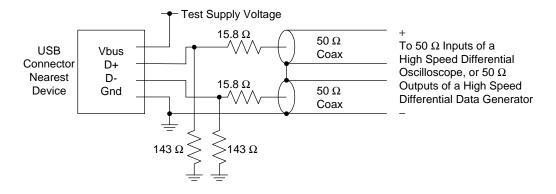

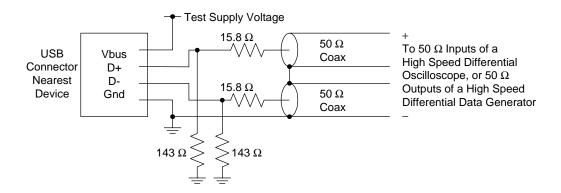

| 10-5 Receiver Measurement Fixture       | 3                                                | 138  |

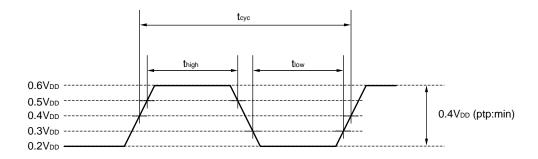

| 10-6 Transmit Waveform for Transce      | eiver at DP/DM                                   | 144  |

| 10-7 Transmitter Measurement Fixtu      | res                                              | 144  |

# LIST OF TABLES (1/2)

| Table No | o. Title                                                     | Page |

|----------|--------------------------------------------------------------|------|

| 3-1 NAN  | ND Tree Pin List                                             | 31   |

| 4-1 Fun  | ction No. List                                               | 32   |

| 4-2 Con  | figuration Space for OHCl Host Controller #1                 | 33   |

| 4-3 Reg  | sister Information                                           | 34   |

| 4-4 Con  | nmand Register                                               | 35   |

| 4-5 Stat | tus Register                                                 | 36   |

| 4-6 Bas  | e Address (BAR_OHCI) Register                                | 36   |

| 4-7 I/O  | Address Register                                             | 37   |

| 4-8 Pow  | ver Management Capabilities (PMC) Register                   | 38   |

| 4-9 Pow  | ver Management Control/Status (PMCSR) Register               | 39   |

| 4-10 EX  | (T1 Register                                                 | 40   |

| 4-11 EX  | (T2 Register                                                 | 41   |

| 4-12 Co  | onfiguration Space for OHCI Host Controller #2               | 42   |

| 4-13 Re  | gister Information                                           | 43   |

| 4-14 Co  | mmand Register                                               | 44   |

| 4-15 Sta | atus Register                                                | 45   |

| 4-16 Ba  | se Address (BAR_OHCI) Register                               | 45   |

| 4-17 Po  | wer Management Capabilities (PMC) Register                   | 46   |

| 4-18 Po  | wer Management Control/Status (PMCSR) Register               | 47   |

| 4-19 Co  | onfiguration Space for EHCI Host Controller                  | 48   |

| 4-20 Re  | gister Information                                           | 49   |

| 4-21 Co  | mmand Register                                               | 51   |

| 4-22 Sta | atus Register                                                | 52   |

| 4-23 Ba  | se Address Register                                          | 52   |

| 4-24 Po  | wer Management Capabilities (PMC) Register                   | 53   |

| 4-25 Po  | wer Management Control/Status (PMCSR) Register               | 54   |

| 4-26 EX  | (T1 Register                                                 | 55   |

| 4-27 EX  | (T2 Register                                                 | 56   |

| 4-28 Op  | perational Registers for OHCI Host Controller #1             | 58   |

| 4-29 Le  | gacy Support Registers for OHCI Host Controller #1           | 58   |

| 4-30 Op  | perational Registers for OHCI Host Controller #2             | 59   |

| 4-31 Po  | rt No Field vs NDP Field                                     | 67   |

| 4-32 Po  | rt No Field vs DR and PPCM Field                             | 68   |

| 4-33 Po  | rt No Field vs HcRhPortStatus[1:3]                           | 70   |

|          | apability and Operational Registers for EHCI Host Controller |      |

| 4-35 Ma  | apping of Legacy Function Registers                          | 89   |

# LIST OF TABLES (2/2)

| Tab             | ole No. Titl                                            | <del>F</del> | Page |

|-----------------|---------------------------------------------------------|--------------|------|

| 5_1             | Endpoint Descriptor Format                              |              | 03   |

|                 | Description of Endpoint Descriptors                     |              |      |

| 5-2<br>5-3      | ·                                                       |              |      |

|                 | Description of General TD                               |              |      |

| 5- <del>4</del> | ·                                                       |              |      |

| 5-6             |                                                         |              |      |

|                 | Packet Status Word Format                               |              |      |

|                 | Description of Packet Status Word                       |              |      |

| 5-9             | •                                                       |              |      |

| -               | Description of Host Controller Communications Area      |              |      |

| 6-1             | Isochronous Transfer Descriptor Format                  |              | .100 |

| 6-2             | Description of Isochronous Transfer Descriptors         |              | .101 |

|                 | Split Transaction Isochronous Transfer Descriptor Form  |              |      |

| 6-4             | Description of Split Transaction Isochronous Transfer D | escriptors   | .103 |

| 6-5             | Queue Element Transfer Descriptor Format                |              | .105 |

| 6-6             | Description of Queue Element Transfer Descriptors       |              | .105 |

| 6-7             | Queue Head Format                                       |              | .107 |

| 6-8             | Description of Queue Head                               |              | .107 |

| 6-9             | Queue Head Format                                       |              | .109 |

| 6-1             | 0 Description of Queue Head                             |              | .109 |

| 8-1             | Semantics for Each Byte/Bit in Page                     |              | .124 |

| 9-1             | The External Parameters                                 |              | .130 |

#### **CHAPTER 1 INTRODUCTION**

The  $\mu$ PD720101 complies with the Universal Serial Bus Specification Revision 2.0 and Open Host Controller Interface Specification for full-/low-speed signaling and Intel's Enhanced Host Controller Interface Specification for high-speed signaling and works up to 480 Mbps. The  $\mu$ PD720101 is integrated 3 host controller cores with PCI Interface and USB2.0 transceivers into a single chip.

#### 1.1 Features

- Compliant with Universal Serial Bus Specification Revision 2.0 (Data rate 1.5/12/480 Mbps)

- Compliant with Open Host Controller Interface Specification for USB Rev 1.0a

- Compliant with Enhanced Host Controller Interface Specification for USB Rev 1.0

- PCI multi-function device consists of two OHCI host controller cores for full-/low-speed signaling and one EHCI

host controller core for high-speed signaling.

- Root hub with 5 (max.) downstream facing ports which are shared by OHCl and EHCl host controller cores.

- All downstream facing ports can handle high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) transaction.

- Configurable number of downstream facing ports (2 to 5)

- 32-bit 33 MHz host interface compliant to PCI Specification release 2.2

- Supports PCI Mobile Design Guide Revision 1.1

- Supports PCI-Bus Power Management Interface Specification release 1.1

- · PCI bus bus-master access

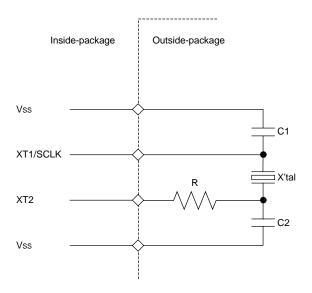

- System clock is generated by 30 MHz X'tal or 48 MHz clock input.

- · Operational registers direct-mapped to PCI memory space

- Legacy support for all downstream facing ports. Legacy support features allow easy migration for motherboard implementation.

- 3.3 V power supply, PCI signal pins have 5 V tolerant circuit.

#### 1.2 Ordering Information

| Part Number     | Package                                              |

|-----------------|------------------------------------------------------|

| μPD720101GJ-UEN | 144-pin plastic LQFP (Fine pitch) ( $20 \times 20$ ) |

| μPD720101F1-EA8 | 144-pin plastic FBGA (12 × 12)                       |

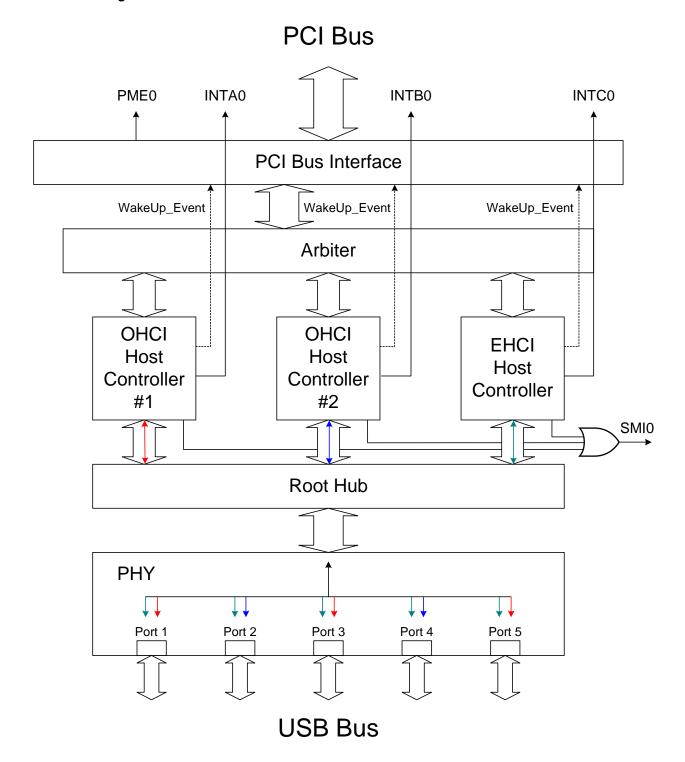

# 1.3 Block Diagram

Remark INTB0/INTC0 can be shared with INTA0 through BIOS setting. (Planning)

#### **CHAPTER 1 INTRODUCTION**

PCI Bus Interface : handles 32-bit 33 MHz PCI bus master and target function which comply with PCI

specification release 2.2. The number of enabled ports is set by bit in configuration

space.

Arbiter : arbitrates among two OHCI host controller cores and one EHCI host controller core.

OHCI Host Controller #1 : handles full- (12 Mbps)/low-speed (1.5 Mbps) signaling at port 1, 3, and 5.

OHCI Host Controller #2 : handles full- (12 Mbps)/low-speed (1.5 Mbps) signaling at port 2 and 4.

EHCI Host Controller : handles high- (480 Mbps) signaling at port 1, 2, 3, 4, and 5.

Root Hub : handles USB hub function in host controller and controls connection (routing) between

host controller core and port.

PHY : consists of high-speed transceiver, full-/low-speed transceiver, serializer, deserializer,

etc.

INTA0 : is the PCI interrupt signal for OHCI Host Controller #1.

INTB0 : is the PCI interrupt signal for OHCI Host Controller #2.

INTC0 : is the PCI interrupt signal for EHCI Host Controller.

SMI0 : is the interrupt signal which is specified by Open Host Controller Interface Specification

for USB Rev 1.0a and Enhanced Host Controller Interface Specification Rev 1.0. The SMI signal of each OHCI Host Controller and EHCI Host Controller appears at this

signal.

PME0 : is the interrupt signal which is specified by PCI-Bus Power Management Interface

Specification release 1.1. Wakeup signal of each host controller core appears at this

signal.

# COMPARISON WITH THE $\mu$ PD720100A

|                | μPD720100A                       | μPD720101 (2nd generation)       |

|----------------|----------------------------------|----------------------------------|

| EHCI revision  | 0.95                             | 1.0                              |

| EHCI           | 1                                | 1                                |

| OHCI           | 2                                | 2                                |

| Legacy support | Parallel IRQ out support         | No parallel IRQ support          |

| Clock          | 48 MHz OSC or 30 MHz OSC/X'tal   | 48 MHz OSC or 30 MHz X'tal       |

| Package        | 176-pin BGA (FP) or 160-pin LQFP | 144-pin BGA (FP) or 144-pin LQFP |

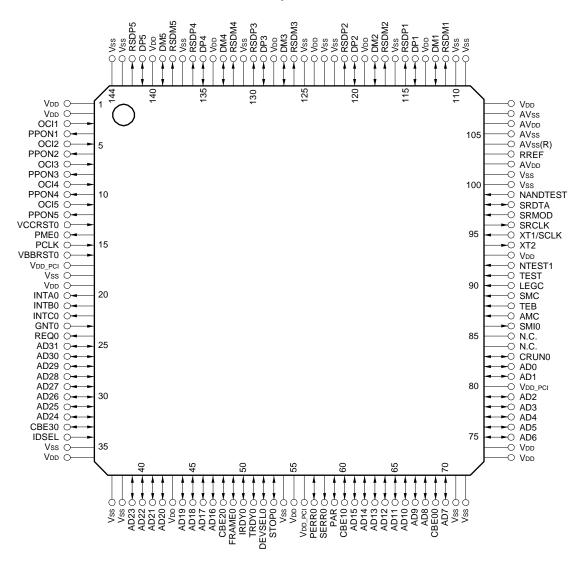

# 1.4 Pin Configuration

• 144-pin plastic LQFP (Fine pitch) (20 × 20)

μPD720101GJ-UEN

#### **Top View**

| Pin No. | Pin Name        | Pin No. | Pin Name            | Pin No. Pin Name |                     | Pin No. | Pin Name        |

|---------|-----------------|---------|---------------------|------------------|---------------------|---------|-----------------|

| 1       | V <sub>DD</sub> | 37      | Vss                 | 73               | V <sub>DD</sub>     | 109     | Vss             |

| 2       | V <sub>DD</sub> | 38      | Vss                 | 74               | V <sub>DD</sub>     | 110     | Vss             |

| 3       | OCI1            | 39      | AD23                | 75               | AD6                 | 111     | RSDM1           |

| 4       | PPON1           | 40      | AD22                | 76               | AD5                 | 112     | DM1             |

| 5       | OCI2            | 41      | AD21                | 77               | AD4                 | 113     | V <sub>DD</sub> |

| 6       | PPON2           | 42      | AD20                | 78               | AD3                 | 114     | DP1             |

| 7       | OCI3            | 43      | V <sub>DD</sub>     | 79               | AD2                 | 115     | RSDP1           |

| 8       | PPON3           | 44      | AD19                | 80               | V <sub>DD_PCI</sub> | 116     | Vss             |

| 9       | OCI4            | 45      | AD18                | 81               | AD1                 | 117     | RSDM2           |

| 10      | PPON4           | 46      | AD17                | 82               | AD0                 | 118     | DM2             |

| 11      | OCI5            | 47      | AD16                | 83               | CRUN0               | 119     | V <sub>DD</sub> |

| 12      | PPON5           | 48      | CBE20               | 84               | N.C.                | 120     | DP2             |

| 13      | VCCRST0         | 49      | FRAME0              | 85               | N.C.                | 121     | RSDP2           |

| 14      | PME0            | 50      | IRDY0               | 86               | SMI0                | 122     | Vss             |

| 15      | PCLK            | 51      | TRDY0               | 87               | AMC                 | 123     | Vss             |

| 16      | VBBRST0         | 52      | DEVSEL0             | 88               | TEB                 | 124     | V <sub>DD</sub> |

| 17      | VDD_PCI         | 53      | STOP0               | 89               | SMC                 | 125     | Vss             |

| 18      | Vss             | 54      | Vss                 | 90               | LEGC                | 126     | RSDM3           |

| 19      | V <sub>DD</sub> | 55      | V <sub>DD</sub>     | 91               | TEST                | 127     | DM3             |

| 20      | INTA0           | 56      | V <sub>DD_PCI</sub> | 92               | NTEST1              | 128     | V <sub>DD</sub> |

| 21      | INTB0           | 57      | PERR0               | 93               | V <sub>DD</sub>     | 129     | DP3             |

| 22      | INTC0           | 58      | SERR0               | 94               | XT2                 | 130     | RSDP3           |

| 23      | GNT0            | 59      | PAR                 | 95               | XT1/SCLK            | 131     | Vss             |

| 24      | REQ0            | 60      | CBE10               | 96               | SRCLK               | 132     | RSDM4           |

| 25      | AD31            | 61      | AD15                | 97               | SRMOD               | 133     | DM4             |

| 26      | AD30            | 62      | AD14                | 98               | SRDTA               | 134     | V <sub>DD</sub> |

| 27      | AD29            | 63      | AD13                | 99               | NANDTEST            | 135     | DP4             |

| 28      | AD28            | 64      | AD12                | 100              | Vss                 | 136     | RSDP4           |

| 29      | AD27            | 65      | AD11                | 101              | Vss                 | 137     | Vss             |

| 30      | AD26            | 66      | AD10                | 102              | AV <sub>DD</sub>    | 138     | RSDM5           |

| 31      | AD25            | 67      | AD9                 | 103              | RREF                | 139     | DM5             |

| 32      | AD24            | 68      | AD8                 | 104              | AVss(R)             | 140     | V <sub>DD</sub> |

| 33      | CBE30           | 69      | CBE00               | 105              | AVss                | 141     | DP5             |

| 34      | IDSEL           | 70      | AD7                 | 106              | AV <sub>DD</sub>    | 142     | RSDP5           |

| 35      | Vss             | 71      | Vss                 | 107              | AVss                | 143     | Vss             |

| 36      | V <sub>DD</sub> | 72      | Vss                 | 108              | V <sub>DD</sub>     | 144     | Vss             |

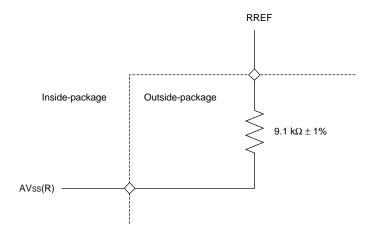

**Remark** AVss(R) should be used to connect RREF through 1 % precision reference resistor of 9.1 kΩ. Pins 84 and 85 must be clamped high on the board.

# • 144-pin plastic FBGA (12 × 12)

$\mu$ PD720101F1-EA8

#### **Bottom View**

|    |    |     |     |     |     |     |     |     |     |     |     |    | _  |    |

|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|

|    | 25 | 26  | 27  | 28  | 29  | 30  | 31  | 32  | 33  | 34  | 35  | 36 |    | 14 |

| 24 | 71 | 72  | 73  | 74  | 75  | 76  | 77  | 78  | 79  | 80  | 81  | 82 | 37 | 13 |

| 23 | 70 | 111 | 112 | 113 | 114 | 115 | 116 | 117 | 118 | 119 | 120 | 83 | 38 | 12 |

| 22 | 69 | 110 |     |     | 137 | 138 | 139 | 140 |     |     | 121 | 84 | 39 | 11 |

| 21 | 68 | 109 |     | _   |     |     |     |     |     |     | 122 | 85 | 40 | 10 |

| 20 | 67 | 108 | 136 |     |     |     |     |     |     | 141 | 123 | 86 | 41 | 9  |

| 19 | 66 | 107 | 135 |     |     |     |     |     |     | 142 | 124 | 87 | 42 | 8  |

| 18 | 65 | 106 | 134 |     |     |     |     |     |     | 143 | 125 | 88 | 43 | 7  |

| 17 | 64 | 105 | 133 |     |     |     |     |     |     | 144 | 126 | 89 | 44 | 6  |

| 16 | 63 | 104 |     |     |     |     |     |     |     |     | 127 | 90 | 45 | 5  |

| 15 | 62 | 103 |     |     | 132 | 131 | 130 | 129 |     |     | 128 | 91 | 46 | 4  |

| 14 | 61 | 102 | 101 | 100 | 99  | 98  | 97  | 96  | 95  | 94  | 93  | 92 | 47 | 3  |

| 13 | 60 | 59  | 58  | 57  | 56  | 55  | 54  | 53  | 52  | 51  | 50  | 49 | 48 | 2  |

|    | 12 | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1  |    | 1  |

| Р  | N  | М   | L   | K   | J   | Н   | G   | F   | Е   | D   | С   | В  | Α  |    |

| Pin No. | Pin Name        | Pin No. | Pin Name         | Pin No. | Pin Name            | Pin No. | Pin Name            |

|---------|-----------------|---------|------------------|---------|---------------------|---------|---------------------|

| 1       | Vss             | 37      | V <sub>DD</sub>  | 73      | V <sub>DD</sub>     | 109     | NANDTEST            |

| 2       | AD23            | 38      | V <sub>DD</sub>  | 74      | RSDP1               | 110     | Vss                 |

| 3       | AD20            | 39      | PPON2            | 75      | V <sub>DD</sub>     | 111     | AVss                |

| 4       | AD18            | 40      | OCI4             | 76      | V <sub>DD</sub>     | 112     | Vss                 |

| 5       | CBE20           | 41      | PPON5            | 77      | DP3                 | 113     | DM2                 |

| 6       | TRDY0           | 42      | PCLK             | 78      | V <sub>DD</sub>     | 114     | RSDP2               |

| 7       | SERR0           | 43      | INTC0            | 79      | RSDM5               | 115     | Vss                 |

| 8       | AD15            | 44      | AD31             | 80      | V <sub>DD</sub>     | 116     | V <sub>DD</sub>     |

| 9       | AD12            | 45      | AD28             | 81      | DP5                 | 117     | RSDM4               |

| 10      | AD9             | 46      | AD25             | 82      | Vss                 | 118     | DP4                 |

| 11      | AD7             | 47      | V <sub>DD</sub>  | 83      | OCI1                | 119     | Vss                 |

| 12      | Vss             | 48      | Vss              | 84      | OCI2                | 120     | PPON1               |

| 13      | V <sub>DD</sub> | 49      | Vss              | 85      | OCI3                | 121     | PPON3               |

| 14      | V <sub>DD</sub> | 50      | AD22             | 86      | OCI5                | 122     | PPON4               |

| 15      | AD3             | 51      | AD21             | 87      | VBBRST0             | 123     | VCCRST0             |

| 16      | AD1             | 52      | V <sub>DD</sub>  | 88      | INTB0               | 124     | V <sub>DD_PCI</sub> |

| 17      | N.C.            | 53      | AD16             | 89      | AD30                | 125     | INTA0               |

| 18      | AMC             | 54      | DEVSEL0          | 90      | AD26                | 126     | REQ0                |

| 19      | XT2             | 55      | PERR0            | 91      | AD24                | 127     | AD29                |

| 20      | SRMOD           | 56      | AD14             | 92      | IDSEL               | 128     | AD27                |

| 21      | Vss             | 57      | AD10             | 93      | CBE30               | 129     | IRDY0               |

| 22      | RREF            | 58      | AD8              | 94      | AD19                | 130     | Vss                 |

| 23      | V <sub>DD</sub> | 59      | CBE00            | 95      | AD17                | 131     | $V_{DD}$            |

| 24      | AVss            | 60      | Vss              | 96      | FRAME0              | 132     | PAR                 |

| 25      | Vss             | 61      | AD6              | 97      | STOP0               | 133     | SMI0                |

| 26      | RSDM1           | 62      | AD4              | 98      | V <sub>DD_PCI</sub> | 134     | LEGC                |

| 27      | DP1             | 63      | AD2              | 99      | CBE10               | 135     | TEST                |

| 28      | RSDM2           | 64      | CRUN0            | 100     | AD13                | 136     | XT1/SCLK            |

| 29      | DP2             | 65      | TEB              | 101     | AD11                | 137     | Vss                 |

| 30      | Vss             | 66      | V <sub>DD</sub>  | 102     | AD5                 | 138     | RSDM3               |

| 31      | RSDP3           | 67      | SRDTA            | 103     | V <sub>DD_PCI</sub> | 139     | DM3                 |

| 32      | DM4             | 68      | AV <sub>DD</sub> | 104     | AD0                 | 140     | Vss                 |

| 33      | RSDP4           | 69      | AVss(R)          | 105     | N.C.                | 141     | PME0                |

| 34      | DM5             | 70      | AV <sub>DD</sub> | 106     | SMC                 | 142     | Vss                 |

| 35      | RSDP5           | 71      | Vss              | 107     | NTEST1              | 143     | V <sub>DD</sub>     |

| 36      | Vss             | 72      | DM1              | 108     | SRCLK               | 144     | GNT0                |

**Remark** AVss(R) should be used to connect RREF through 1 % precision reference resistor of 9.1 kΩ. Pins 17 and 105 must be clamped high on the board.

# PIN INFORMATION

(1/2)

| Pin Name     | I/O     | Buffer Type                  | Active | (1/2)                                           |

|--------------|---------|------------------------------|--------|-------------------------------------------------|

|              |         |                              | Level  |                                                 |

| AD (31:0)    | I/O     | 5 V PCI I/O                  |        | PCI "AD [31 : 0]" signal                        |

| CBE (3:0)0   | I/O     | 5 V PCI I/O                  |        | PCI "C/BE [3:0]" signal                         |

| PAR          | I/O     | 5 V PCI I/O                  |        | PCI "PAR" signal                                |

| FRAME0       | I/O     | 5 V PCI I/O                  |        | PCI "FRAME#" signal                             |

| IRDY0        | I/O     | 5 V PCI I/O                  |        | PCI "IRDY#" signal                              |

| TRDY0        | I/O     | 5 V PCI I/O                  |        | PCI "TRDY#" signal                              |

| STOP0        | I/O     | 5 V PCI I/O                  |        | PCI "STOP#" signal                              |

| IDSEL        | I       | 5 V PCI input                |        | PCI "IDSEL" signal                              |

| DEVSEL0      | I/O     | 5 V PCI I/O                  |        | PCI "DEVSEL#" signal                            |

| REQ0         | 0       | 5 V PCI output               |        | PCI "REQ#" signal                               |

| GNT0         | 1       | 5 V PCI input                |        | PCI "GNT#" signal                               |

| PERR0        | I/O     | 5 V PCI I/O                  |        | PCI "PERR#" signal                              |

| SERR0        | 0       | 5 V PCI N-ch open drain      |        | PCI "SERR#" signal                              |

| INTA0        | 0       | 5 V PCI N-ch open drain      | Low    | PCI "INTA#" signal                              |

| INTB0        | 0       | 5 V PCI N-ch open drain      | Low    | PCI "INTB#" signal                              |

| INTC0        | 0       | 5 V PCI N-ch open drain      | Low    | PCI "INTC#" signal                              |

| PCLK         | I       | 5 V PCI input                |        | PCI "CLK" signal                                |

| VBBRST0      | I       | 5 V tolerant input           | Low    | Hardware reset for chip                         |

| CRUN0        | I/O     | 5 V PCI I/O                  |        | PCI "CLKRUN#" signal                            |

| PME0         | 0       | 5 V PCI N-ch open drain      | Low    | PCI "PME#" signal                               |

| VCCRST0      | 1       | 5 V tolerant input           | Low    | Reset for power management                      |

| SMI0         | 0       | 5 V tolerant N-ch open drain | Low    | System management interrupt output              |

| XT1/SCLK     | 1       | Input                        |        | System clock input or oscillator in             |

| XT2          | 0       | Output                       |        | oscillator out                                  |

| DP (5 : 1)   | I/O     | USB high speed D+ I/O        |        | USB high speed D+ signal                        |

| DM (5 : 1)   | I/O     | USB high speed D- I/O        |        | USB high speed D- signal                        |

| RSDP (5:1)   | 0       | USB full speed D+ Output     |        | USB full speed D+ signal                        |

| RSDM (5 : 1) | 0       | USB full speed D- Output     |        | USB full speed D- signal                        |

| OCI (5 : 1)  | I (I/O) | Input                        | Low    | USB root hub port's overcurrent status input    |

| PPON (5 : 1) | O (I/O) | Output                       | High   | USB root hub port's power supply control output |

| LEGC         | I (I/O) | Input                        | High   | Legacy support switch                           |

| SRCLK        | 0       | Output                       |        | Serial ROM clock out                            |

| SRDTA        | I/O     | I/O                          |        | Serial ROM data                                 |

| SRMOD        | I       | Input with 50 kΩ pull down R | High   | Serial ROM input enable                         |

| RREF         | А       | Analog                       |        | Reference resistor                              |

| NTEST1       | I       | Input with 12 kΩ pull down R | High   | Test pin                                        |

(2/2)

| Pin Name            | I/O | Buffer Type                          | Active<br>Level | Function                           |

|---------------------|-----|--------------------------------------|-----------------|------------------------------------|

| SMC                 | I   | Input with 50 k $\Omega$ pull down R | High            | Scan mode control                  |

| TEB                 | I   | Input with 50 k $\Omega$ pull down R | High            | BIST enable                        |

| AMC                 | I   | Input with 50 k $\Omega$ pull down R | High            | ATG mode control                   |

| TEST                | I   | Input with 50 k $\Omega$ pull down R | High            | Test control                       |

| NANDTEST            | I   | Input with 50 k $\Omega$ pull down R | High            | NAND tree test enable              |

| AV <sub>DD</sub>    |     |                                      |                 | V <sub>DD</sub> for analog circuit |

| V <sub>DD</sub>     |     |                                      |                 | V <sub>DD</sub>                    |

| V <sub>DD_PCI</sub> |     |                                      |                 | 5 V (5 V PCI) or 3.3 V (3.3 V PCI) |

| AVss                |     |                                      |                 | Vss for analog circuit             |

| Vss                 |     |                                      |                 | Vss                                |

| N.C.                |     |                                      |                 | No connection                      |

#### **Remarks 1.** "5 V tolerant" means that the buffer is 3 V buffer with 5 V tolerant circuit.

- 2. "5 V PCI" indicates a PCI buffer, which complies with the 3 V PCI standard, has a 5 V tolerant circuit. It does not indicate that this buffer fully complies with 5 V PCI standard. However, this function can be used for evaluating the operation of a device on a 5 V add-in card.

- **3.** The signal marked as "(I/O)" in the above table operates as I/O signals during testing. However, they do not need to be considered in normal use.

# **CHAPTER 2 PIN FUNCTIONS**

# 2.1 Pin Functions for 144-pin LQFP

The pin type describes a signal either as analog, power, input, or I/O (bi-directional).

# 2.1.1 Power supply

| Pin                 | Pin No.                                                                                      | Direction | Function                                          |

|---------------------|----------------------------------------------------------------------------------------------|-----------|---------------------------------------------------|

| V <sub>DD</sub>     | 1, 2, 19, 36, 43, 55, 73, 74, 93, 108, 113, 119, 124, 128, 134, 140                          | Power     | +3.3 V power supply                               |

| V <sub>DD_PCI</sub> | 17, 56, 80                                                                                   | Power     | +5 V for 5 V PCI or +3.3 V for 3.3 V PCI          |

| AV <sub>DD</sub>    | 102, 106                                                                                     | Power     | +3.3 V power supply for analog circuit            |

| Vss                 | 18, 35, 37, 38, 54, 71, 72,<br>100, 101, 109, 110, 116, 122,<br>123, 125, 131, 137, 143, 144 | Power     | Ground                                            |

| AVss                | 104, 105, 107                                                                                | Power     | Ground for analog circuit                         |

| N.C.                | 84, 85                                                                                       | -         | These N.C. pins must be pulled high on the board. |

# 2.1.2 Analog signaling

| Pin  | Pin No. | Direction | Function                                                                                                                                   |

|------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| RREF | 103     | Analog    | RREF must be connected a 1% precision reference resistor of 9.1 k $\Omega$ . The other side of resistor must be connected to local ground. |

#### 2.1.3 PCI interface

| Pin         | Pin No.                                                                                                                        | Direction | Function                  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------|

| AD (31 : 0) | 25, 26, 27, 28, 29, 30, 31, 32, 39, 40, 41, 42, 44, 45, 46, 47, 61, 62, 63, 64, 65, 66, 67, 68, 70, 75, 76, 77, 78, 79, 81, 82 | I/O       | PCI "AD [31 : 0]" signal  |

| CBE (3:0)0  | 33, 48, 60, 69                                                                                                                 | I/O       | PCI "C/BE [3 : 0]" signal |

| PAR         | 59                                                                                                                             | I/O       | PCI "PAR" signal          |

| FRAME0      | 49                                                                                                                             | I/O       | PCI "FRAME#" signal       |

| IRDY0       | 50                                                                                                                             | I/O       | PCI "IRDY#" signal        |

| TRDY0       | 51                                                                                                                             | I/O       | PCI "TRDY#" signal        |

| STOP0       | 53                                                                                                                             | I/O       | PCI "STOP#" signal        |

| IDSEL       | 34                                                                                                                             | I         | PCI "IDSEL" signal        |

| DEVSEL0     | 52                                                                                                                             | I/O       | PCI "DEVSEL#" signal      |

| REQ0        | 24                                                                                                                             | 0         | PCI "REQ#" signal         |

| GNT0        | 23                                                                                                                             | I         | PCI "GNT#" signal         |

| PERR0       | 57                                                                                                                             | I/O       | PCI "PERR#" signal        |

| SERR0       | 58                                                                                                                             | 0         | PCI "SERR#" signal        |

| INTA0       | 20                                                                                                                             | 0         | PCI "INTA#" signal        |

| INTB0       | 21                                                                                                                             | 0         | PCI "INTB#" signal        |

| INTC0       | 22                                                                                                                             | 0         | PCI "INTC#" signal        |

| PCLK        | 15                                                                                                                             | I         | PCI "CLK" signal          |

| VBBRST0     | 16                                                                                                                             | I         | Hardware reset for Chip   |

| CRUN0       | 83                                                                                                                             | I/O       | PCI "CLKRUN#" signal      |

| PME0        | 14                                                                                                                             | 0         | PCI "PME#" signal         |

- Remarks 1. For details of PCI operations, see the PCI Local Bus Specification Revision 2.2.

- 2. See CHAPTER 7 POWER MANAGEMENT to decide the setting of VBBRST0. The setting of this signal is decided by power management support level.

# 2.1.4 System clock & reset for power management

| Pin      | Pin No. | Direction | Caution                                                                                                                                                            |

|----------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XT1/SCLK | 95      | I         | System clock input or Oscillator input Apply 48-MHz clock input or connect to 30-MHz X'tal. Clock frequency is selected by "Clock_sel reg." in EXT2.               |

| XT2      | 94      | 0         | If 48-MHz clock input is applied to SCLK, this signal must be opened. Otherwise, connect to 30-MHz X'tal. Clock frequency is selected by "Clock_sel reg." in EXT2. |

| VCCRST0  | 13      | I         | Reset for power management.                                                                                                                                        |

**Remark** See **CHAPTER 7 POWER MANAGEMENT** to decide the setting of VCCRST0. The setting of this signal is decided by power management support level.

# 2.1.5 USB interface

| Pin          | Pin No.                 | Direction | Function                                                                                                                 |

|--------------|-------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------|

| DP (5 : 1)   | 141, 135, 129, 120, 114 | I/O       | USB D+ high-speed signal Shared with DMx pins having the same numbers.                                                   |

| RSDP (5 : 1) | 142, 136, 130, 121, 115 | 0         | USB D+ full-speed signal Connected to DPx through 36 $\Omega$ 1% precision Rs resistor.                                  |

| DM (5 : 1)   | 139, 133, 127, 118, 112 | I/O       | USB D– high-speed signal Shared with DPx pins having the same numbers.                                                   |

| RSDM (5 : 1) | 138, 132, 126, 117, 111 | 0         | USB D– full-speed signal Connected to DMx through 36 $\Omega$ 1% precision Rs resistor.                                  |

| OCI (5 : 1)  | 11, 9, 7, 5, 3          | I         | Pin for inputting the overcurrent status of the USB Root Hub Port 1: No power supply problem 0: Overcurrent has occurred |

| PPON (5 : 1) | 12, 10, 8, 6, 4         | 0         | Power supply control output for USB Root Hub Port 0: Power supply OFF 1: Power supply ON                                 |

# 2.1.6 Legacy support interface

| Pin  | Pin No. | Direction | Function                                                                           |

|------|---------|-----------|------------------------------------------------------------------------------------|

| LEGC | 90      | I         | Legacy support switch 0: Legacy OFF 1: Legacy ON                                   |

| SMI0 | 86      | 0         | System management interrupt output 0: Interrupt occurs 1: Interrupt does not occur |

# 2.1.7 Serial ROM interface

| Pin   | Pin No. | Direction | Caution                          |

|-------|---------|-----------|----------------------------------|

| SRCLK | 96      | 0         | Serial ROM Clock Out             |

| SRDTA | 98      | I/O       | Serial ROM Data                  |

| SRMOD | 97      | I         | Serial ROM Input Enable          |

|       |         |           | 0 (default): Serial ROM Inactive |

|       |         |           | 1: Serial ROM Active             |

# 2.1.8 Test signals

| Pin      | Pin No. | Direction | Caution                                                                                                                     |

|----------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| SMC      | 89      | I         | Should be left open on circuit board.                                                                                       |

| AMC      | 87      | I         | Should be left open on circuit board.                                                                                       |

| NANDTEST | 99      | I         | NAND-Tree test enable. 0 (default): NAND-Tree test disable 1: NAND-Tree test enable This can be left open on circuit board. |

| TEB      | 88      | I         | Should be left open on circuit board.                                                                                       |

| TEST     | 91      | I         | Should be left open on circuit board.                                                                                       |

| NTEST1   | 92      | I         | Should be left open on circuit board.                                                                                       |

# 2.2 Pin Functions for 144-pin FBGA

The pin type describes a signal either as analog, power, input, or I/O (bi-directional).

# 2.2.1 Power supply

| Pin              | Pin No.                                                                           | Direction | Function                                          |

|------------------|-----------------------------------------------------------------------------------|-----------|---------------------------------------------------|

| V <sub>DD</sub>  | 13, 14, 23, 37, 38, 47, 52, 66, 73, 75, 76, 78, 80, 116, 131, 143                 | Power     | +3.3 V power supply                               |

| VDD_PCI          | 98, 103, 124                                                                      | Power     | +5 V for 5 V PCI or +3.3 V for 3.3 V PCI          |

| AV <sub>DD</sub> | 68, 70                                                                            | Power     | +3.3 V power supply for analog circuit            |

| Vss              | 1, 12, 21, 25, 30, 36, 48, 49, 60, 71, 82, 110, 112, 115, 119, 130, 137, 140, 142 | Power     | Ground                                            |

| AVss             | 24, 69, 111                                                                       | Power     | Ground for analog circuit                         |

| N.C.             | 17, 105                                                                           | -         | These N.C. pins must be pulled high on the board. |

# 2.2.2 Analog signaling

| Pin  | Pin No. | Direction | Function                                                                                                                                   |

|------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| RREF | 22      | Analog    | RREF must be connected a 1% precision reference resistor of 9.1 k $\Omega$ . The other side of resistor must be connected to local ground. |

#### 2.2.3 PCI interface

| Pin         | Pin No.                                                                                                                         | Direction | Function                  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------|

| AD (31 : 0) | 44, 89, 127, 45, 128, 90, 46, 91, 2, 50, 51, 3, 94, 4, 95, 53, 8, 56, 100, 9, 101, 57, 10, 58, 11, 61, 102, 62, 15, 63, 16, 104 | I/O       | PCI "AD [31 : 0]" signal  |

| CBE (3:0)0  | 93, 5, 99, 59                                                                                                                   | I/O       | PCI "C/BE [3 : 0]" signal |

| PAR         | 132                                                                                                                             | I/O       | PCI "PAR" signal          |

| FRAME0      | 96                                                                                                                              | I/O       | PCI "FRAME#" signal       |

| IRDY0       | 129                                                                                                                             | I/O       | PCI "IRDY#" signal        |

| TRDY0       | 6                                                                                                                               | I/O       | PCI "TRDY#" signal        |

| STOP0       | 97                                                                                                                              | I/O       | PCI "STOP#" signal        |

| IDSEL       | 92                                                                                                                              | I         | PCI "IDSEL" signal        |

| DEVSEL0     | 54                                                                                                                              | I/O       | PCI "DEVSEL#" signal      |

| REQ0        | 126                                                                                                                             | 0         | PCI "REQ#" signal         |

| GNT0        | 144                                                                                                                             | 1         | PCI "GNT#" signal         |

| PERR0       | 55                                                                                                                              | I/O       | PCI "PERR#" signal        |

| SERR0       | 7                                                                                                                               | 0         | PCI "SERR#" signal        |

| INTA0       | 125                                                                                                                             | 0         | PCI "INTA#" signal        |

| INTB0       | 88                                                                                                                              | 0         | PCI "INTB#" signal        |

| INTC0       | 43                                                                                                                              | 0         | PCI "INTC#" signal        |

| PCLK        | 42                                                                                                                              | 1         | PCI "CLK" signal          |

| VBBRST0     | 87                                                                                                                              | I         | Hardware reset for Chip   |

| CRUN0       | 64                                                                                                                              | I/O       | PCI "CLKRUN#" signal      |

| PME0        | 141                                                                                                                             | 0         | PCI "PME#" signal         |

Remarks 1. For details of PCI operations, see the PCI Local Bus Specification Revision 2.2.

**2.** See **CHAPTER 7 POWER MANAGEMENT** to decide the setting of VBBRST0. The setting of this signal is decided by power management support level.

# 2.2.4 System clock & reset for power management

| Pin      | Pin No. | Direction | Caution                                                                                                                                                            |

|----------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XT1/SCLK | 136     | I         | System clock input or Oscillator input Apply 48-MHz clock input or connect to 30-MHz X'tal. Clock frequency is selected by "Clock_sel reg." in EXT2.               |

| XT2      | 19      | 0         | If 48-MHz clock input is applied to SCLK, this signal must be opened. Otherwise, connect to 30-MHz X'tal. Clock frequency is selected by "Clock_sel reg." in EXT2. |

| VCCRST0  | 123     | I         | Reset for power management.                                                                                                                                        |

**Remark** See **CHAPTER 7 POWER MANAGEMENT** to decide the setting of VCCRST0. The setting of this signal is decided by power management support level.

# 2.2.5 USB interface

| Pin          | Pin No.               | Direction | Function                                                                                                                 |

|--------------|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------|

| DP (5 : 1)   | 81, 118, 77, 29, 27   | I/O       | USB D+ high-speed signal Shared with DMx pins having the same numbers.                                                   |

| RSDP (5:1)   | 35, 33, 31, 114, 74   | 0         | USB D+ full-speed signal Connected to DPx through 36 $\Omega$ 1% precision Rs resistor.                                  |

| DM (5 : 1)   | 34, 32, 139, 113, 72  | I/O       | USB D– high-speed signal Shared with DPx pins having the same numbers.                                                   |

| RSDM (5 : 1) | 79, 117, 138, 28, 26  | 0         | USB D– full-speed signal Connected to DMx through 36 $\Omega$ 1% precision Rs resistor.                                  |

| OCI (5 : 1)  | 86, 40, 85, 84, 83    | I         | Pin for inputting the overcurrent status of the USB Root Hub Port 1: No power supply problem 0: Overcurrent has occurred |

| PPON (5 : 1) | 41, 122, 121, 39, 120 | 0         | Power supply control output for USB Root Hub Port  0: Power supply OFF  1: Power supply ON                               |

# 2.2.6 Legacy support interface

| Pin  | Pin No. | Direction | Function                                                                           |

|------|---------|-----------|------------------------------------------------------------------------------------|

| LEGC | 134     | I         | Legacy support switch 0: Legacy OFF 1: Legacy ON                                   |

| SMI0 | 133     | 0         | System management interrupt output 0: Interrupt occurs 1: Interrupt does not occur |

# 2.2.7 Serial ROM interface

| Pin   | Pin No. | Direction | Caution                          |

|-------|---------|-----------|----------------------------------|

| SRCLK | 108     | 0         | Serial ROM Clock Out             |

| SRDTA | 67      | I/O       | Serial ROM Data                  |

| SRMOD | 20      | I         | Serial ROM Input Enable          |

|       |         |           | 0 (default): Serial ROM Inactive |

|       |         |           | 1: Serial ROM Active             |

# 2.2.8 Test signals

| Pin      | Pin No. | Direction | Caution                                                                                                                     |

|----------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| SMC      | 106     | I         | Should be left open on circuit board.                                                                                       |

| AMC      | 18      | I         | Should be left open on circuit board.                                                                                       |

| NANDTEST | 109     | I         | NAND-Tree test enable. 0 (default): NAND-Tree test disable 1: NAND-Tree test enable This can be left open on circuit board. |

| TEB      | 65      | I         | Should be left open on circuit board.                                                                                       |

| TEST     | 135     | Ī         | Should be left open on circuit board.                                                                                       |

| NTEST1   | 107     | Ī         | Should be left open on circuit board.                                                                                       |

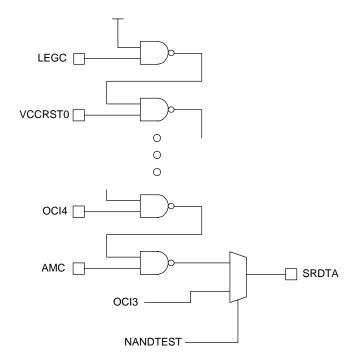

#### CHAPTER 3 INFORMATION FOR NAND-TREE TEST MODE

The  $\mu$ PD720101 supports NAND-Tree test mode. NAND-Tree test mode is for testing connection on board. When NANDTEST is set to "high", NAND-Tree test mode is enabled and all of listed bi-directional signals are configured as input mode. And all of listed output signals except for NAND-Tree's output buffer are configured as high-impedance state. The following table lists each NAND-Tree pin ordering, with the first value being the first input and the last value being the NAND-Tree output.

There are two methods for performing NAND-Tree test.

- At first, all NAND-Tree input pins should be set to "low". At that time, the output of the NAND-Tree will be "high".

Starting at the last signal on the NAND-Tree (signal at bottom of list next to output), set to "1" onto each signal, one at a time. The NAND-Tree output will be toggled when each input signal transitions from "low" to "high".

The maximum propagation delay from input signals to NAND-Tree output is 25 ns.

- The second method works in reverse. Set all NAND-Tree input pins "high". Then starting at the first signal on the NAND-Tree (signal at top of list), set to "0" onto each signal, one at a time. The NAND-Tree output will toggled on each input signal transitions from "high" to "low". The propagation delay from input signals to NAND-Tree output is 25 ns.

Figure 3-1. NAND-Tree Circuitry

Table 3-1. NAND Tree Pin List

| Pin<br>No. | Pin Name | I/O | QFP<br>Pin | BGA<br>Ball | Note | Pin<br>No. | Pin Name | I/O | QFP<br>Pin | BGA<br>Ball | Note          |

|------------|----------|-----|------------|-------------|------|------------|----------|-----|------------|-------------|---------------|

| 1          | LEGC     | I/O | 90         | L7          |      | 31         | STOP0    | I/O | 53         | G3          |               |

| 2          | VCCRST0  | I   | 13         | C9          |      | 32         | PERR0    | I/O | 57         | H2          |               |

| 3          | N.C.     | I/O | 84         | P6          |      | 33         | PAR      | I/O | 59         | J4          |               |

| 4          | N.C.     | I/O | 85         | M6          |      | 34         | CBE10    | I/O | 60         | J3          |               |

| 5          | PCLK     | ı   | 15         | A8          |      | 35         | AD15     | I/O | 61         | J1          |               |

| 6          | VBBRST0  | ı   | 16         | В8          |      | 36         | AD14     | I/O | 62         | J2          |               |

| 7          | GNT0     | ı   | 23         | D6          |      | 37         | AD13     | I/O | 63         | K3          |               |

| 8          | AD31     | I/O | 25         | A6          |      | 38         | AD12     | I/O | 64         | K1          |               |

| 9          | AD30     | I/O | 26         | В6          |      | 39         | AD11     | I/O | 65         | L3          |               |

| 10         | AD29     | I/O | 27         | C5          |      | 40         | AD10     | I/O | 66         | K2          |               |

| 11         | AD28     | I/O | 28         | A5          |      | 41         | AD9      | I/O | 67         | L1          |               |

| 12         | AD27     | I/O | 29         | C4          |      | 42         | AD8      | I/O | 68         | L2          |               |

| 13         | AD26     | I/O | 30         | B5          |      | 43         | CBE00    | I/O | 69         | M2          |               |

| 14         | AD25     | I/O | 31         | A4          |      | 44         | AD7      | I/O | 70         | M1          |               |

| 15         | AD24     | I/O | 32         | B4          |      | 45         | AD6      | I/O | 75         | N3          |               |