**User's Manual**

# VR5432™

## 64-Bit MIPS<sup>®</sup> RISC Microprocessor

Volume 1

μPD30541GD

Document No.U13751EU5V0UMJ1 Date Published: May 2001 CP (K)

© **NEC Electronics Inc.** 2000 Printed in U.S.A.

VR5432 Microprocessor User's Manual Document Number U13751EU5V0UMJ1

#### **Revision History**

February 1999: First release August 1999: Version 2, Preliminary December 1999: Version 3, Preliminary update February 2000: Version 4, Document release May 2000: Version 5, Document corrections

NEC, the NEC logo, VR Series, VR3000, VR4000, VR4300, VR5000, VR5432 and VR10000 are registered trademarks of NEC Corporation. All other product, brand, or trade names used in this publication are the trademarks or registered trademarks of their respective trademark owners.

In North America: No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. All devices sold by NECEL are covered by the provisions appearing in NECEL's Terms and Conditions of Sales only, including the limitation of liability, warranty, and patent provisions. NECEL makes no warranty, express, statutory, implied or by description, regarding information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. "Standard" quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools, industrial robots, audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliability requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in any application where failure could result in injury or death. If customers wish to use NECEL devices in applications. NECEL, customers must contact the responsible NECEL salespeople to determine NECEL's willingness to support a given application.

## Contents

## Volume 1

| Preface | XV                                   |

|---------|--------------------------------------|

| Chapter | <b>1 Introduction</b>                |

| 1.1     | Device Features 2                    |

| 1.2     | Internal Architecture                |

| 1.2.1   | Configuration                        |

| 1.2.2   | CPU Registers 6                      |

| 1.2.3   | CPU Instruction Set Overview         |

| 1.2.4   | Data Formats and Addressing10        |

| 1.2.5   | System Control Coprocessor (CP0)     |

| 1.2.6   | Floating-Point Unit (FPU)            |

| 1.2.7   | Internal Cache 16                    |

| 1.3     | Memory Management Unit (MMU)         |

| 1.3.1   | Translation Lookaside Buffer (TLB)17 |

| 1.3.2   | Operating Modes 17                   |

| 1.4     | Instruction Pipeline                 |

| Chapter | 2 Signal Descriptions                |

| 2.1     | System Interface Signals             |

| 2.2     | Power Inputs                         |

| 2.3     | Clock Interface Signals              |

| 2.4     | JTAG and Test Interface Signals      |

| 2.5     | Interrupt Interface Signals          |

| 2.6     | Initialization Interface Signals     |

| 2.7     | Pin Orientation                      |

| Chapter | 3 Pipeline                              |    |

|---------|-----------------------------------------|----|

| 3.1     | Pipeline Stages                         |    |

| 3.2     | Branch Delay                            |    |

| 3.3     | Load Delay                              |    |

| 3.4     | Interlock and Exception Handling        |    |

| 3.4.1   | Exception Conditions                    |    |

| 3.4.2   | Interrupt Latency                       |    |

| 3.4.3   | Stall Conditions                        |    |

| 3.5     | Transaction Buffer                      |    |

| Chapter | 4 Memory Management Unit                |    |

| 4.1     | Translation Lookaside Buffer            |    |

| 4.1.1   | Hits and Misses                         |    |

| 4.2     | Processor Modes                         |    |

| 4.2.1   | Processor Operating Modes               |    |

| 4.2.2   | Instruction Set Mode                    |    |

| 4.2.3   | Addressing Modes                        |    |

| 4.3     | Addresses and Address Spaces            |    |

| 4.3.1   | Virtual Addresses                       |    |

| 4.3.2   | Physical Addresses                      |    |

| 4.3.3   | Virtual-to-Physical Address Translation |    |

| 4.3.4   | 32-Bit Mode Virtual Address Translation |    |

| 4.3.5   | 64-Bit Mode Virtual Address Translation |    |

| 4.3.6   | User Address Space                      |    |

| 4.3.7   | Supervisor Space                        |    |

| 4.3.8   | Kernel Space                            |    |

| 4.4     | System Control Coprocessor              |    |

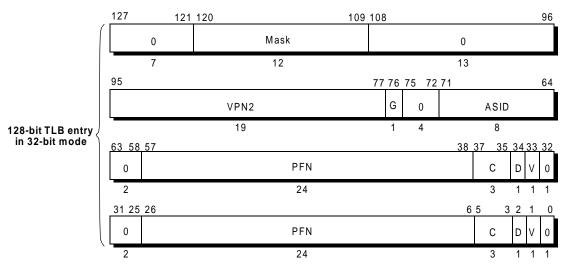

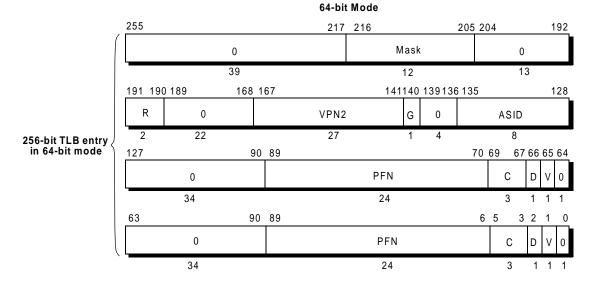

| 4.4.1   | TLB Entry Format                        |    |

| 4.4.2   | Instruction and Data Micro-TLBs         |    |

| 4.5     | CP0 Registers                           |    |

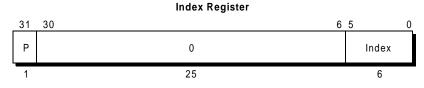

| 4.5.1   | Index Register (0)                      |    |

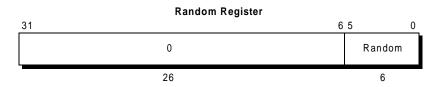

| 4.5.2   | Random Register (1)                     |    |

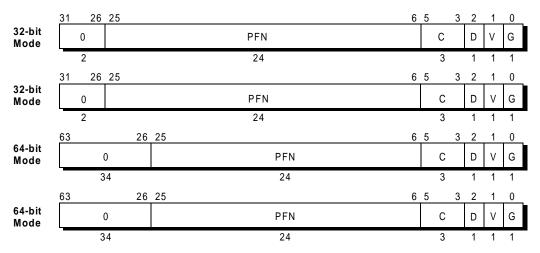

| 4.5.3   | EntryLo0 (2) and EntryLo1 (3) Registers | 72 |

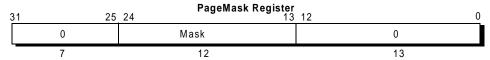

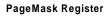

| 4.5.4   | PageMask Register (5)                   |    |

| 4.5.5   | Wired Register (6)                      |    |

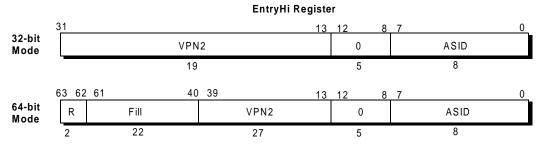

|    | 4.5.6         | EntryHi Register (10)                                    | 75  |

|----|---------------|----------------------------------------------------------|-----|

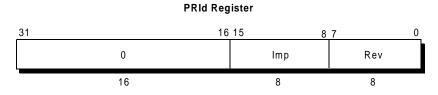

|    | 4.5.7         | Processor Revision Identifier (PRId) Register (15)       | 76  |

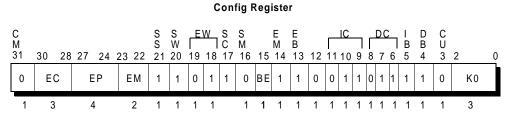

|    | 4.5.8         | Config Register (16)                                     |     |

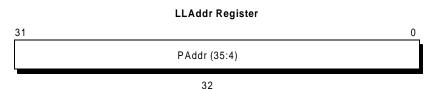

|    | 4.5.9         | Load Linked Address (LLAddr) Register (17)               |     |

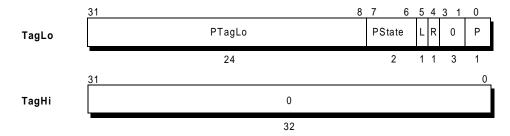

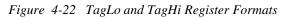

|    | 4.5.10        | Cache Tag Registers [TagLo (28) and TagHi (29)]          |     |

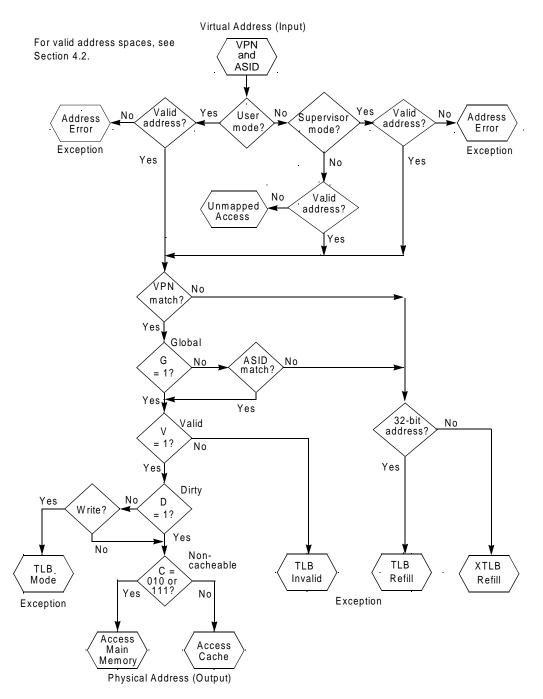

|    | 4.6           | Virtual-to-Physical Address Translation Process          |     |

|    | 4.7           | TLB Exceptions                                           | 83  |

|    | 4.8           | TLB Instructions                                         |     |

| Ch | apter         | 5 Cache Organization and Operation                       |     |

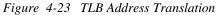

|    | 5.1           | Memory Organization                                      | 86  |

|    | 5.2           | Primary Cache Organization                               |     |

|    | 5.2.1         | Cache Line Lengths                                       |     |

|    | 5.2.2         | Cache Sizes                                              |     |

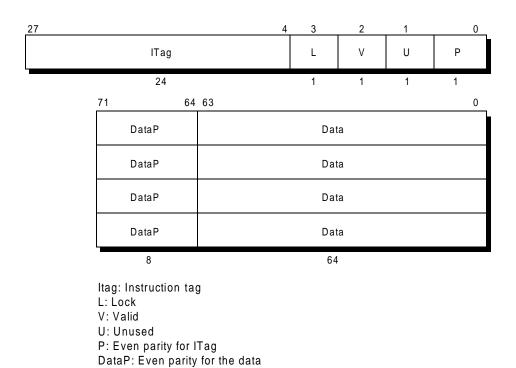

|    | 5.2.3         | Instruction Cache Organization                           | 88  |

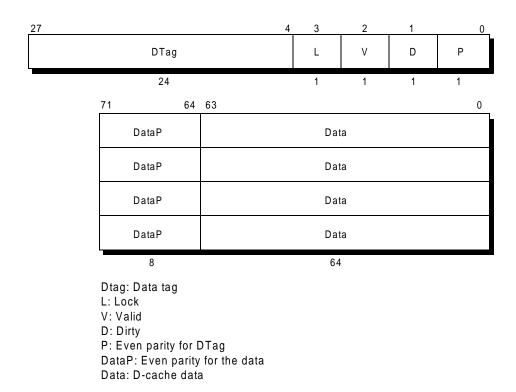

|    | 5.2.4         | Data Cache Organization                                  | 89  |

| Ch | apter         | 6 CPU Exceptions                                         |     |

|    | 6.1           | Exception Processing Overview                            |     |

|    | 6.2           | Exception Processing Registers                           |     |

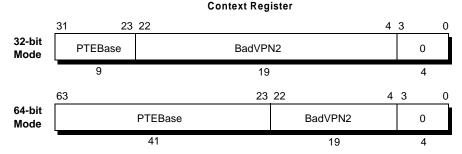

|    | <b>6</b> .2.1 | Context Register (4)                                     |     |

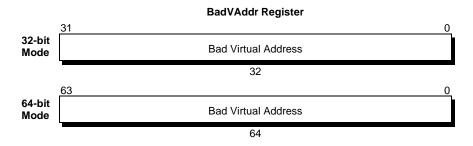

|    | 6.2.2         | Bad Virtual Address Register (BadVAddr) (8)              |     |

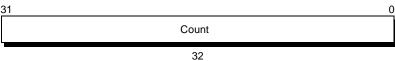

|    | 6.2.3         | Count Register (9)                                       |     |

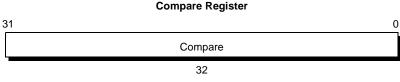

|    | 6.2.4         | Compare Register (11)                                    |     |

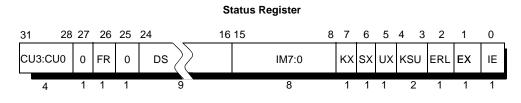

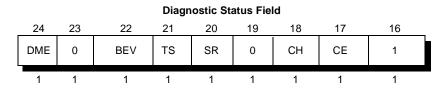

|    | 6.2.5         | Status Register (12)                                     |     |

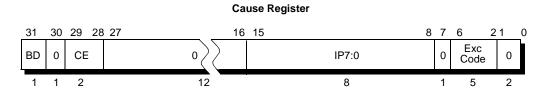

|    | 6.2.6         | Cause Register (13)                                      |     |

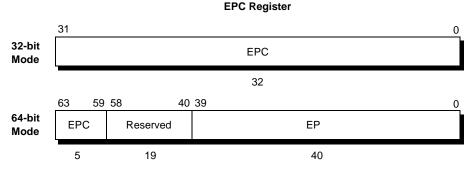

|    | 6.2.7         | Exception Program Counter (EPC) Register (14)            |     |

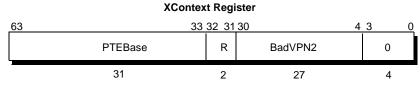

|    | 6.2.8         | XContext Register (20)                                   |     |

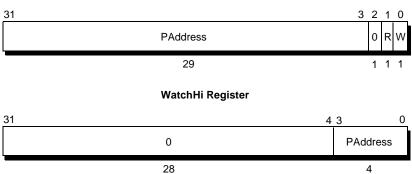

|    | 6.2.9         | WatchLo and WatchHi Registers (18 and 19)                |     |

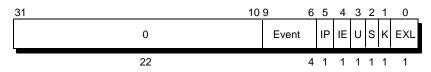

|    | 6.2.10        | Performance Counter Registers (25)                       |     |

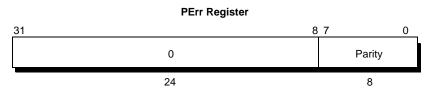

|    | 6.2.11        | Parity Error (PErr) Register (26)                        |     |

|    | 6.2.12        | Cache Error (CacheErr) Register (27)                     |     |

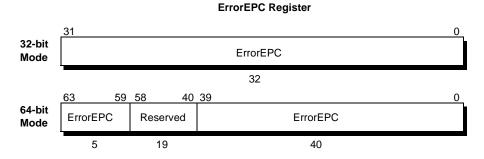

|    | 6.2.13        | Error Exception Program Counter (ErrorEPC) Register (30) |     |

|    | 6.3           | Processor Exceptions                                     | 112 |

|    | 6.3.1         | Exception Types                                          |     |

|    | 6.3.2  | Exception Vector Locations                  | . 115 |

|----|--------|---------------------------------------------|-------|

|    | 6.4    | Exception Vector Offsets                    | 115   |

|    | 6.4.1  | TLB Refill Vector Selection                 | 116   |

|    | 6.4.2  | Priority of Exceptions                      | 118   |

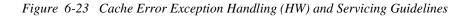

|    | 6.4.3  | Reset Exception                             | 119   |

|    | 6.4.4  | Soft Reset Exception                        | 121   |

|    | 6.4.5  | Nonmaskable Interrupt (NMI) Exception       | 122   |

|    | 6.4.6  | Address Error Exception                     | 123   |

|    | 6.4.7  | TLB Exceptions                              | 124   |

|    | 6.4.8  | Cache Error Exception                       | 127   |

|    | 6.4.9  | Bus Error Exception                         | 128   |

|    | 6.4.10 | Integer Overflow Exception                  | 129   |

|    | 6.4.11 | Trap Exception                              | 129   |

|    | 6.4.12 | System Call Exception                       | 130   |

|    | 6.4.13 | Breakpoint Exception                        | 131   |

|    | 6.4.14 | Reserved Instruction Exception              | 132   |

|    | 6.4.15 | Coprocessor Unusable Exception              | 133   |

|    | 6.4.16 | Floating-Point Exception                    | 134   |

|    | 6.4.17 | Watch Exception                             | 134   |

|    | 6.4.18 | Interrupt Exception                         | 135   |

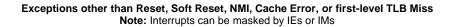

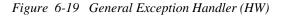

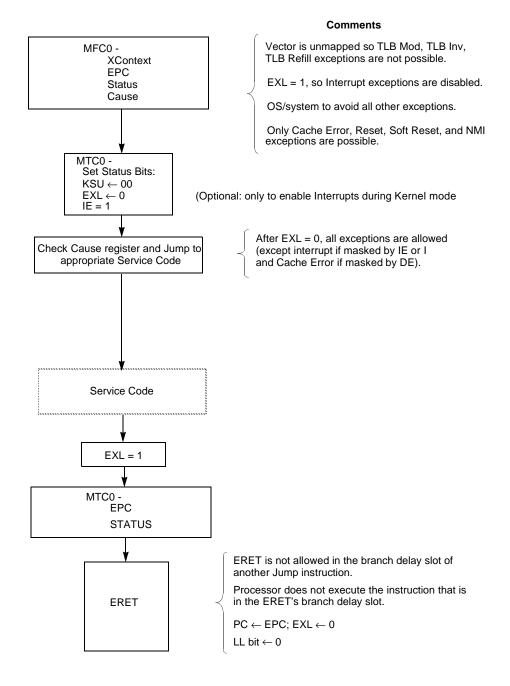

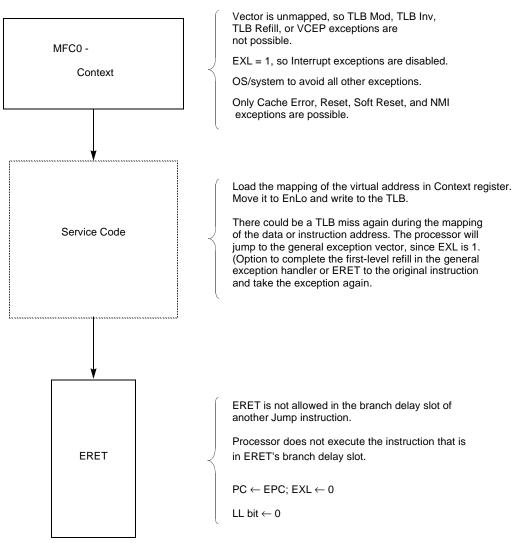

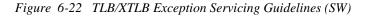

|    | 6.5    | Exception Handling and Servicing Flowcharts | 136   |

|    | 6.6    | Interrupts                                  | 143   |

|    | 6.6.1  | Hardware Interrupts                         | 143   |

|    | 6.6.2  | Nonmaskable Interrupt (NMI)                 | 143   |

|    | 6.6.3  | Asserting Interrupts                        | 143   |

| Ch | apter  | 7 Floating-Point Unit                       | 149   |

|    | 7.1    | Overview                                    | .149  |

|    | 7.2    | FPU Features                                | 150   |

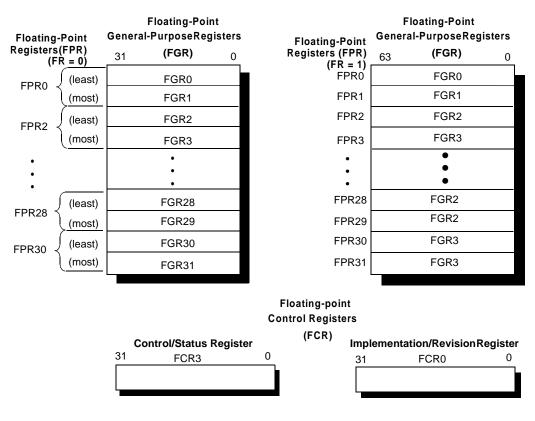

|    | 7.3    | FPU Programming Model                       | 150   |

|    | 7.4    | Floating-Point General-Purpose Registers    |       |

|    | 7.5    | Floating-Point Registers                    | . 153 |

|    | 7.6    | Floating-Point Control Registers            | . 153 |

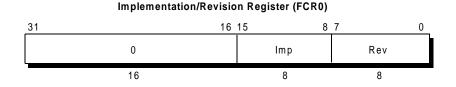

|    | 7.6.1  | Implementation and Revision Register (FCR0) | . 154 |

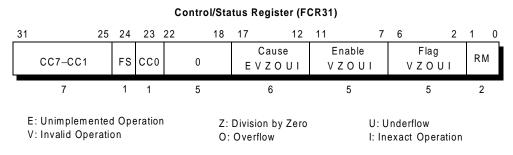

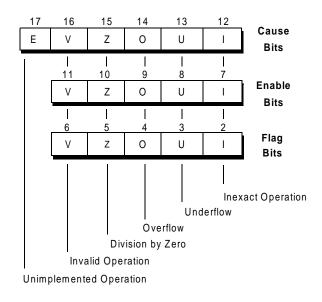

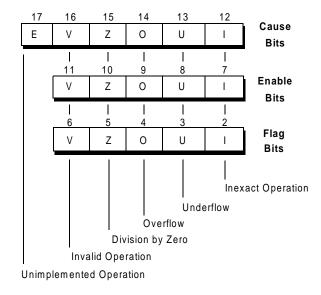

|    | 7.6.2  | Control/Status Register (FCR31)             | 155   |

| 7.7     | Floating-Point Formats                                       |     |

|---------|--------------------------------------------------------------|-----|

| 7.8     | Binary Fixed-Point Format                                    |     |

| 7.9     | Floating-Point Instruction Set Overview                      |     |

| 7.9.1   | Floating-Point Load, Store, and Move Instructions            |     |

| 7.9.2   | Floating-Point Conversion Instructions                       |     |

| 7.9.3   | Floating-Point Computational Instructions                    |     |

| 7.10    | FPU Instruction Pipeline Overview                            |     |

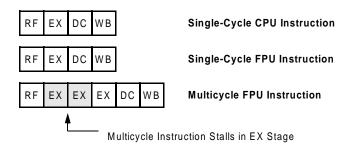

| 7.10.1  | Instruction Execution                                        |     |

| 7.10.2  | Instruction Execution Cycle Time                             |     |

| 7.10.3  | Instruction Issuing Constraints with Multicycle Instructions | 171 |

| Chapter | 8 Floating-Point Exceptions                                  |     |

| 8.1     | Exception Types                                              |     |

| 8.2     | Exception Trap Processing                                    |     |

| 8.3     | Flags                                                        |     |

| 8.4     | FPU Exceptions                                               |     |

| 8.4.1   | Inexact Operation Exception (I)                              |     |

| 8.4.2   | Invalid Operation Exception (V)                              |     |

| 8.4.3   | Division by Zero Exception (Z)                               |     |

| 8.4.4   | Overflow Exception (O)                                       |     |

| 8.4.5   | Underflow Exception (U)                                      |     |

| 8.4.6   | Unimplemented Operation Instruction Exception (E)            |     |

| 8.5     | Saving and Restoring State                                   |     |

| 8.6     | Trap Handlers for IEEE Standard 754 Exceptions               |     |

| Chapter | 9 Bus Interface                                              |     |

| 9.1     | Interface Buses In Native Mode                               |     |

| 9.2     | Interface Buses in R43K Mode                                 |     |

| Chapter | 10 System Interface Transactions (Native Mode)               | 191 |

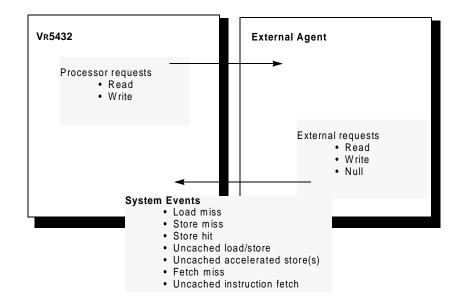

| 10.1    | Terminology                                                  |     |

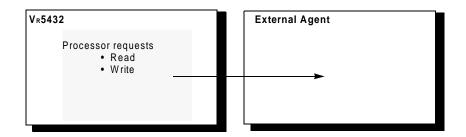

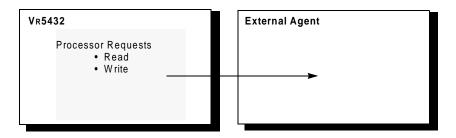

| 10.2    | Processor Requests                                           |     |

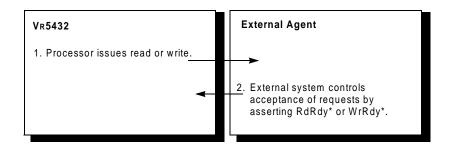

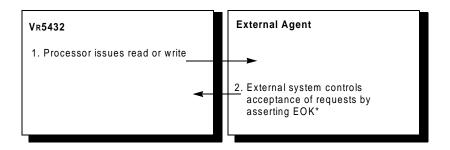

| 10.2.1  | Rules for Processor Requests                                 |     |

| 10.2.2  | Processor Read Request                                       |     |

| 10.2.3  | Processor Write Request                                      |     |

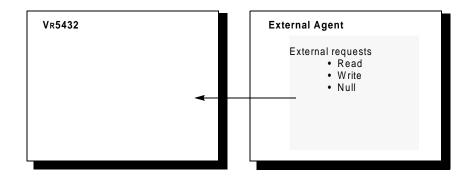

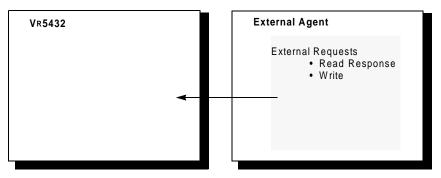

| 10.3    | External Requests                           | 198 |

|---------|---------------------------------------------|-----|

| 10.3.1  | External Read Request                       |     |

| 10.3.2  | -                                           |     |

| 10.3.3  | Read Response                               | 200 |

| 10.4    | Handling Requests                           | 201 |

| 10.4.1  | Load Miss                                   | 201 |

| 10.4.2  | Store Miss                                  |     |

| 10.4.3  | Store Hit                                   |     |

| 10.4.4  | Uncached Loads or Stores                    |     |

| 10.4.5  | Uncached Accelerated Stores                 |     |

| 10.4.6  | Uncached Instruction Fetch                  |     |

| 10.4.7  | Fetch Miss                                  |     |

|         |                                             |     |

| Chapter | 11 System Interface Protocols (Native Mode) |     |

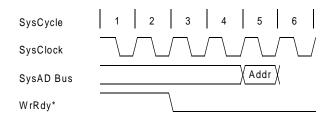

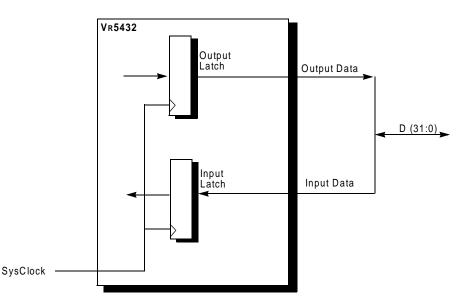

| 11.1    | Address and Data Cycles                     |     |

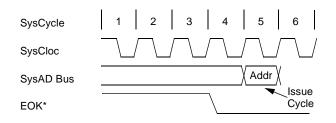

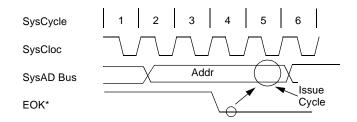

| 11.2    | Issue Cycles                                | 206 |

| 11.3    | Handshake Signals                           |     |

| 11.4    | System Interface Operation                  |     |

| 11.4.1  | Master and Slave States                     |     |

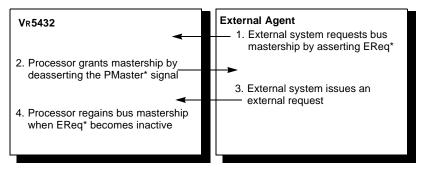

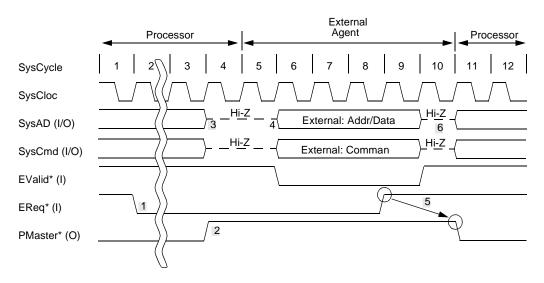

| 11.4.2  | External Arbitration                        |     |

| 11.4.3  | Uncompelled Change to Slave State           |     |

| 11.5    | Processor Request Protocols                 |     |

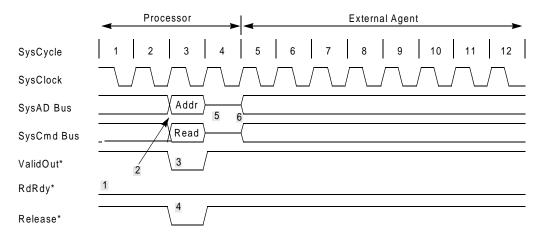

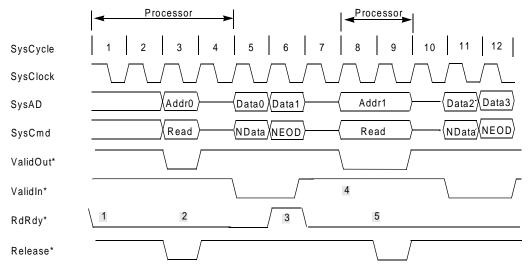

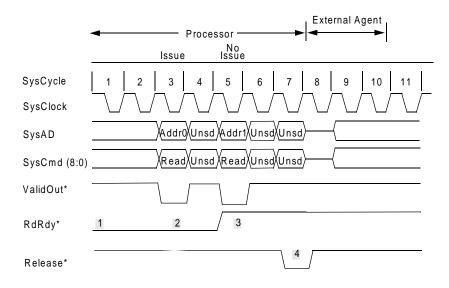

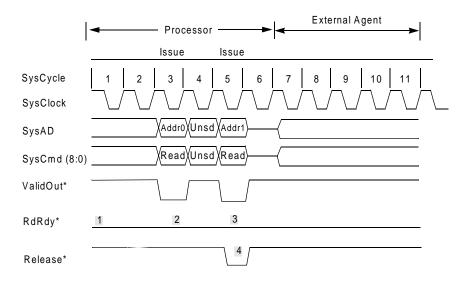

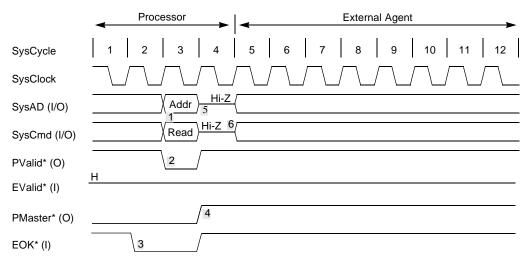

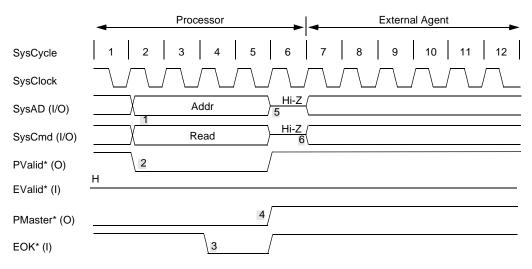

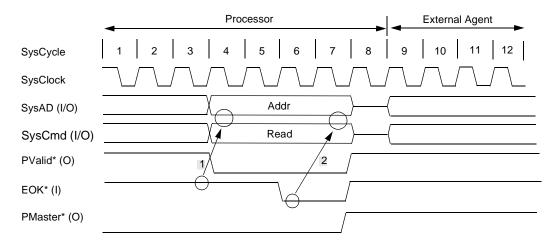

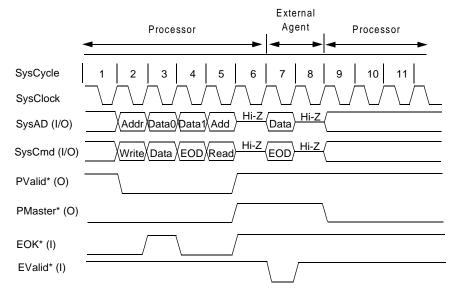

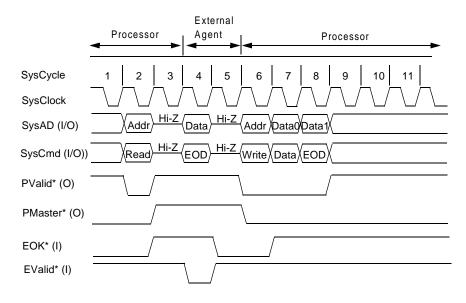

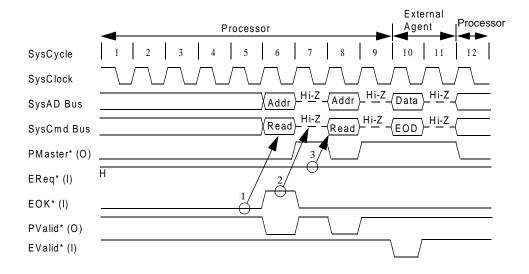

| 11.5.1  | Processor Read Request Protocol             |     |

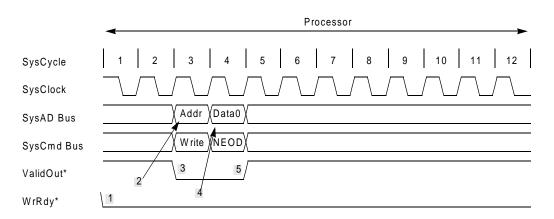

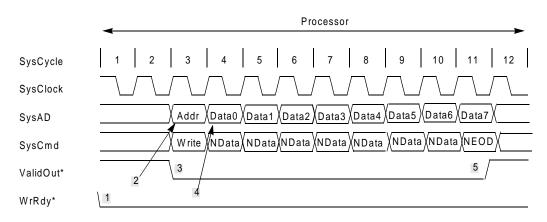

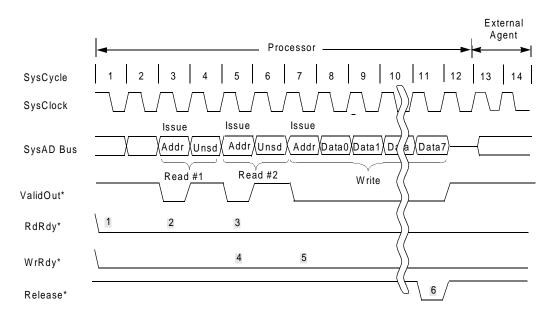

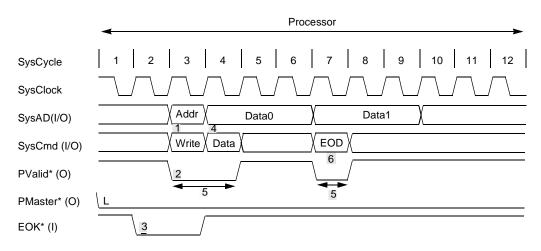

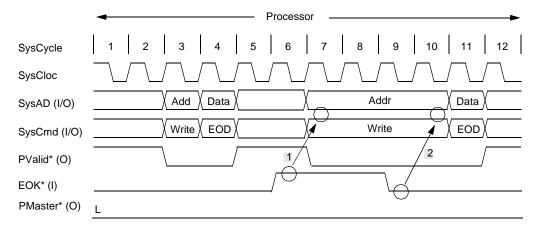

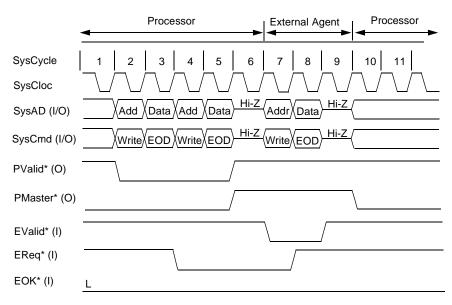

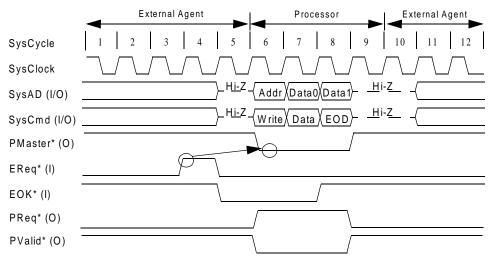

| 11.5.2  | Processor Write Request Protocol            |     |

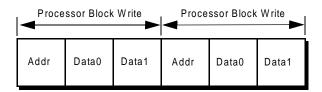

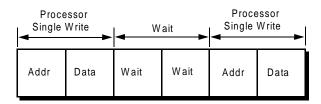

| 11.5.3  | Processor Request Flow Control              |     |

| 11.5.4  | Processor Request Timing Modes              |     |

| 11.6    | External Request Protocols                  |     |

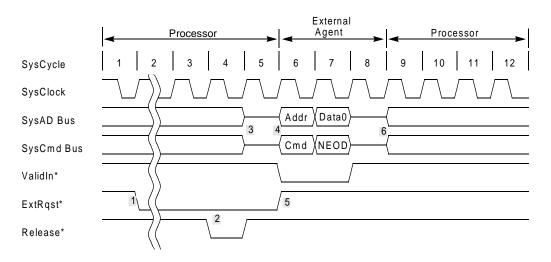

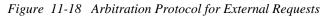

| 11.6.1  | External Arbitration Protocol               |     |

| 11.6.2  | External Read Request Protocol              |     |

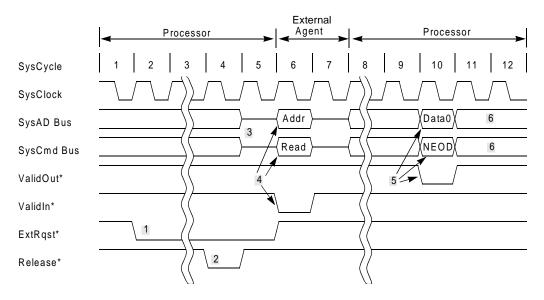

| 11.6.3  | External Null Request Protocol              |     |

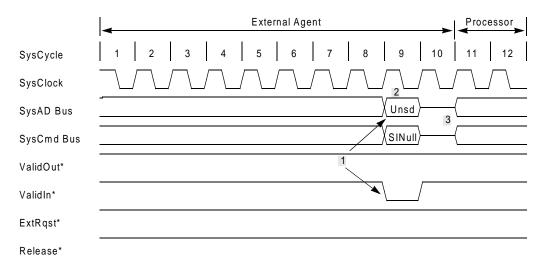

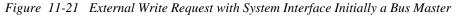

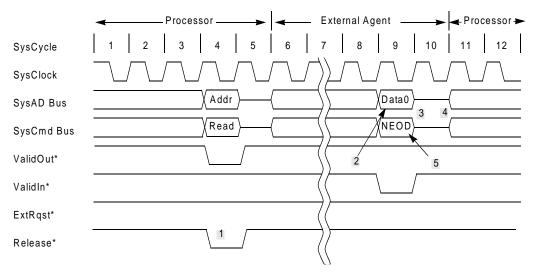

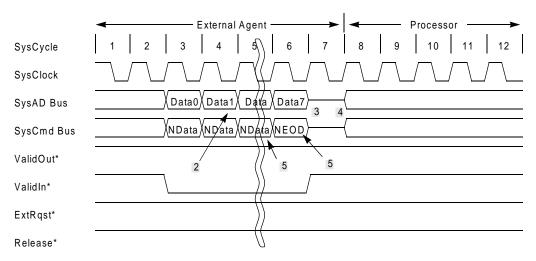

| 11.6.4  | External Write Request Protocol             |     |

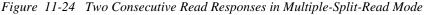

| 11.6.5  | Read Response Protocol                      |     |

| 11.7    | SysADC (3:0) Protocol                       |     |

| 11.8    | Data Rate Control                           | 236 |

| 11.9    | Data Transfer Patterns                      |     |

|     | 11.10        | Word Transfer Ordering                       | . 239 |

|-----|--------------|----------------------------------------------|-------|

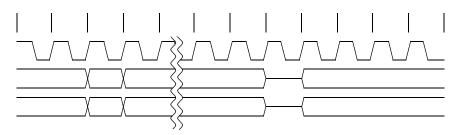

|     | <b>11.11</b> | Independent Transmissions on the SysAD Bus   | . 242 |

|     | 11.12        | System Interface Cycle Time                  | . 243 |

|     | 11.13        | System Interface Commands/Data Identifiers   | . 243 |

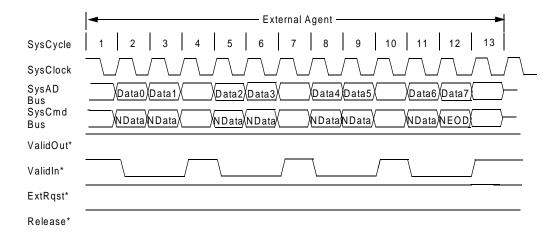

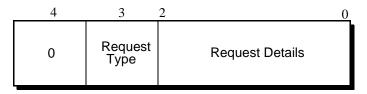

|     | 11.13.1      | Command and Data Identifier Syntax           | . 244 |

|     | 11.13.2      | System Interface Command Syntax              | . 244 |

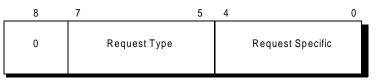

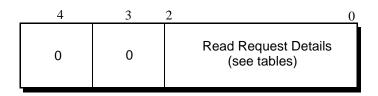

|     | 11.13.3      | Read Requests                                | . 245 |

|     | 11.13.4      | System Interface Data Identifier Syntax      | . 248 |

|     | 11.14        | System Interface Addresses                   | . 250 |

|     | 11.14.1      | Addressing Conventions                       | . 250 |

|     | 11.14.2      | Subblock Ordering                            | . 250 |

|     | 11.14.3      | Processor Internal Address Map               | . 251 |

| Cha | apter 1      | 12 System Interface Transactions (R43K Mode) | .253  |

|     | 12.1         | Processor Requests                           | . 254 |

|     | 12.1.1       | Rules for Processor Requests                 |       |

|     | 12.1.2       | Processor Read Request                       | . 256 |

|     | 12.1.3       | Processor Write Request                      | . 257 |

|     | 12.2         | External Requests                            | . 257 |

|     | 12.2.1       | External Write Request                       | . 259 |

|     | 12.2.2       | Read Response                                | . 259 |

|     | 12.3         | Handling Requests                            | . 260 |

|     | 12.3.1       | Fetch Miss                                   | . 260 |

|     | 12.3.2       | Load Miss                                    | . 261 |

|     | 12.3.3       | Store Miss                                   | . 262 |

|     | 12.3.4       | Store Hit                                    | . 262 |

|     | 12.3.5       | Uncached Loads or Stores                     | . 263 |

|     | 12.3.6       | Uncached Accelerated Stores                  |       |

|     | 12.3.7       | Uncached Instruction Fetch                   | . 264 |

| Chapter | 13 System Interface Protocols (R43K Mode)      |     |

|---------|------------------------------------------------|-----|

| 13.1    | Address and Data Cycles                        |     |

| 13.2    | Issue Cycles                                   |     |

| 13.3    | Handshake Signals                              |     |

| 13.4    | System Interface Operation                     |     |

| 13.4.1  | Master and Slave States                        |     |

| 13.4.2  | External Arbitration                           |     |

| 13.4.3  | Uncompelled Change to Slave State              |     |

| 13.5    | Processor Request Protocols                    |     |

| 13.5.1  | Processor Read Request Protocol                |     |

| 13.5.2  | Processor Write Request Protocol               |     |

| 13.5.3  | Processor Request Flow Control                 |     |

| 13.5.4  | Successive Processing of Requests              |     |

| 13.6    | External Request Protocols                     |     |

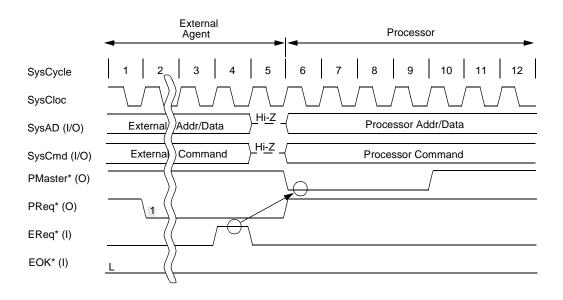

| 13.6.1  | External Arbitration Protocol                  |     |

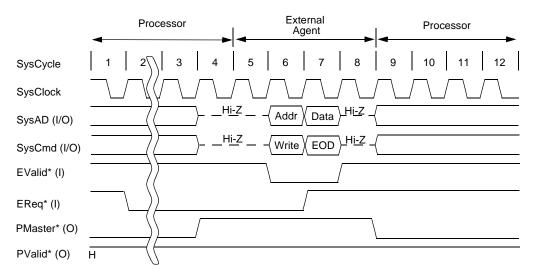

| 13.6.2  | External Write Request Protocol                |     |

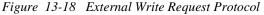

| 13.6.3  | External Read Response Protocol                |     |

| 13.7    | Discarding and Re-Executing Commands           |     |

| 13.7.1  | Re-Execution of Processor Commands             |     |

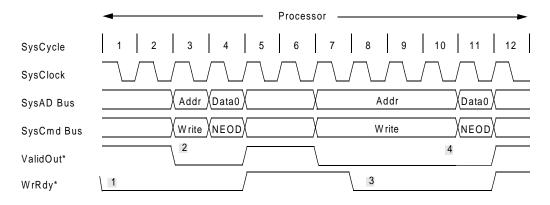

| 13.7.2  | Discarding and Re-Executing a Write Command    |     |

| 13.7.3  | Discarding and Re-Executing a Read Command     |     |

| 13.7.4  | Executing and Discarding a Command             |     |

| 13.8    | SysADC (3:0) Protocol                          | 295 |

| 13.9    | Data Flow Control                              | 295 |

| 13.9.1  | Read Response                                  | 295 |

| 13.9.2  | Write Request                                  | 295 |

| 13.9.3  | Independent Transfer on the SysAD (31:0) Bus   |     |

| 13.9.4  | System Endianness                              | 296 |

| 13.10   | System Interface Cycle Time                    |     |

| 13.10.  | 1 Release Latency Time                         | 297 |

| 13.11   | System Interface Commands and Data Identifiers |     |

| 13.12   | Command and Data Identifier Syntax             |     |

| 13.12.  | 1 System Interface Command Syntax              |     |

| 13.12.  | 2 Read Requests                                |     |

| 13.12.  | 3 Write Requests                               | 302 |

|     | 13.12.4 | 4 System Interface Data Identifier Syntax | 304   |

|-----|---------|-------------------------------------------|-------|

|     | 13.12.5 | 5 Data Identifier Bit Definitions         | . 304 |

|     | 13.13   | System Interface Addresses                | . 305 |

|     | 13.13.1 | Addressing Conventions                    | . 306 |

|     | 13.13.2 | 2 Sublock Order Data Retrieval            | . 306 |

| Cha | apter   | 14 Initialization Interface               | 307   |

|     | 14.1    | Processor Reset Signals                   | . 307 |

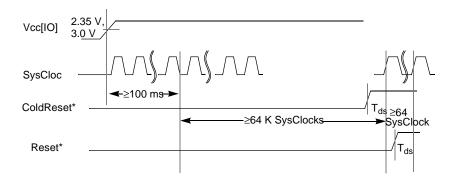

|     | 14.1.1  | Power-On Reset                            | . 308 |

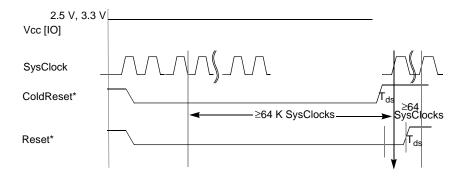

|     | 14.1.2  | Cold Reset                                | . 309 |

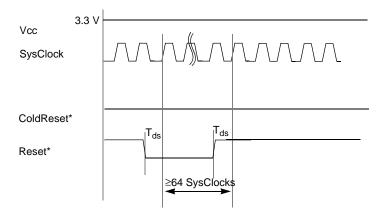

|     | 14.1.3  | Warm Reset                                | . 310 |

|     | 14.1.4  | Processor Reset State                     | . 311 |

|     | 14.2    | Processor Initialization Signals          | . 311 |

| Cha | apter   | 15 Clock Interface                        | 313   |

|     | 15.1    | Basic System Clocks                       | . 313 |

|     | 15.1.1  | SysClock/MasterClock                      | . 313 |

|     | 15.1.2  | PClock                                    | 313   |

|     | 15.2    | Alignment to SysClock                     | . 314 |

|     | 15.3    | Phase-Locked Loop (PLL)                   | . 314 |

|     | 15.4    | Bypass PLL Mode                           |       |

|     | -       |                                           |       |

## Volume 2

| Chapter | 16 Instruction Set Overview  |     |

|---------|------------------------------|-----|

| 16.1    | Instruction Set Architecture |     |

| 16.2    | Instruction Formats          |     |

| 16.3    | Load and Store Instructions  |     |

| 16.3.1  | Delayed Load Instructions    | 323 |

| 16.3.2  | Defining Access Types        | 323 |

| 16.4    | Computational Instructions   |     |

| 16.4.1  | 64-Bit Operations            | 327 |

| 16.5    | Jump and Branch Instructions |     |

| 16.5.1  | Jump Instructions            | 328 |

|    | 16.5.2  | Branch Instructions                              | 328   |

|----|---------|--------------------------------------------------|-------|

|    | 16.6    | Special Instructions                             | 329   |

|    | 16.7    | Coprocessor Instructions                         | 329   |

|    | 16.7.1  | Coprocessor Load and Store                       | 330   |

|    | 16.7.2  | Coprocessor Operations                           | 330   |

|    | 16.8    | Implementation-Specific Instructions             | 331   |

|    | 16.8.1  | Overview                                         | 331   |

|    | 16.8.2  | Implementation-Specific Instruction Descriptions | . 333 |

|    | 16.9    | Integer Rotate Instructions                      | 337   |

|    | 16.10   | Integer Multiply-Accumulate Instructions         | . 338 |

|    | 16.11   | Multimedia Extensions                            | 339   |

|    | 16.12   | Debugging Instructions                           | 340   |

|    | 16.12.1 | Instruction Notation Conventions                 | 340   |

|    |         |                                                  |       |

| Ch | apter   | 17 CPU Instruction Set                           | 345   |

|    | 17.1    | Introduction                                     | 345   |

|    | 17.2    | Functional Instruction Groups                    | 345   |

|    | 17.2.1  | Load and Store Instructions                      | 346   |

|    | 17.2.2  | Computational Instructions                       | 348   |

|    | 17.2.3  | Jump and Branch Instructions                     | 353   |

|    | 17.2.4  | Miscellaneous Instructions                       | 354   |

|    | 17.3    | System Control Coprocessor (CP0) Instructions    | 355   |

|    | 17.4    | CPU Instructions                                 | 356   |

|    | 17.5    | CPU Instruction Opcode Bit Encoding              | 565   |

|    |         |                                                  |       |

| Ch | apter   | 18 Floating-Point Unit Instruction Set           | . 569 |

|    | 18.1    | Instruction Formats                              | 569   |

|    | 18.1.1  | Floating-Point Loads, Stores, and Transfers      | 572   |

|    | 18.1.2  | Floating-Point Operations                        | 572   |

|    | 18.2    | Floating-Point Computational Instructions        | 575   |

|    | 18.3    | FPU Instructions                                 | 578   |

|    | 18.4    | FPU Instruction Opcode Bit Encoding              | 674   |

|    |         |                                                  |       |

| Chapter | 19 Multimedia Instruction Set                          | 677 |

|---------|--------------------------------------------------------|-----|

| 19.1    | Multimedia Extensions                                  | 677 |

| 19.2    | Multimedia Instruction Format                          | 681 |

| 19.3    | Multimedia Instructions                                | 682 |

| 19.4    | Multimedia Instruction Opcode Bit Encoding             | 735 |

| Chapter | 20 Debug and Test Features                             | 737 |

| 20.1    | Overview                                               | 738 |

| 20.2    | Definition of Terms                                    | 739 |

| 20.3    | Debug Mode                                             | 742 |

| 20.4    | Internal Access                                        | 743 |

| 20.4.1  | Debug Instructions                                     | 744 |

| 20.4.2  | Debug Registers                                        | 745 |

| 20.5    | External Access                                        | 759 |

| 20.5.1  | JTAG Port Signals                                      | 760 |

| 20.5.2  | JTAG-Accessible Registers                              | 766 |

| 20.5.3  | N-Wire Monitor Data Download Example                   |     |

| 20.5.4  | N-Trace Packets                                        | 780 |

| Appendi | x A Subblock Data Retrieval Order                      | 787 |

| Appendi | x B Comparing the Vr4300, Vr5000 and Vr5432 Processors | 791 |

| Appendi | x C PLL Analog Power Filtering                         | 795 |

| Appendi | x D Instruction Hazards                                | 797 |

| Index   |                                                        |     |

## Preface

|                 | The VR5432 <sup>™</sup> microproce<br>(reduced instruction set co<br>the high-performance 64-b<br>describes the architecture a<br>microprocessor. | mputer) microproc<br>bit MIPS <sup>®</sup> IV archi                             | cessor that implements itecture. This manual |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------|

| Legend          | Data significance:<br>Active-high signal name:<br>Active-low signal name:<br>Numeric representation:                                              | Higher on left an<br>XXX<br>XXX*<br>binary XXXX<br>decimal XXX<br>hexadecimal 0 | X                                            |

|                 | Prefixes representing an ex                                                                                                                       |                                                                                 |                                              |

|                 | capacity):                                                                                                                                        |                                                                                 | 10                                           |

|                 |                                                                                                                                                   | K (kilo)<br>M (mega)                                                            | $2^{10} = 1024$                              |

|                 |                                                                                                                                                   | M (mega)                                                                        | $2^{20} = 1024^2$                            |

|                 |                                                                                                                                                   | G (giga)                                                                        | $2^{30} = 1024^3$ $2^{40} = 1024^4$          |

|                 |                                                                                                                                                   | T (tera)                                                                        | $2^{10} = 1024^{10}$                         |

| Manual Overview | The manual is divided into<br>containing processor archi<br>instructions. Volume 2 cor<br>appendixes.                                             | tectural and functi                                                             | onal information and                         |

|                 | Volume 1 (U13751E)                                                                                                                                |                                                                                 |                                              |

|                 | Chapter 1: Introduction features, CPU, Floating-Po                                                                                                |                                                                                 |                                              |

|                 | <b>Chapter 2: Signal Descri</b><br>functions of the Vr5432 pr                                                                                     | -                                                                               | ne pin configuration and                     |

|                 | Chapter 3: Pipeline description stages, delays, and interloc                                                                                      |                                                                                 |                                              |

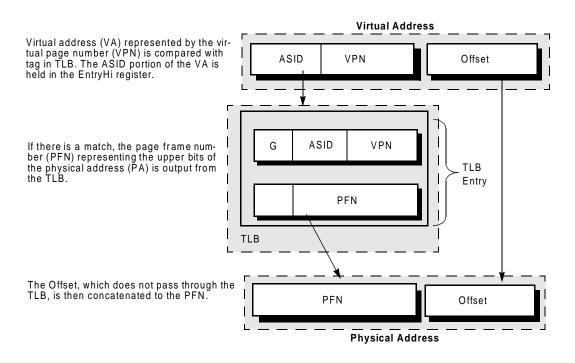

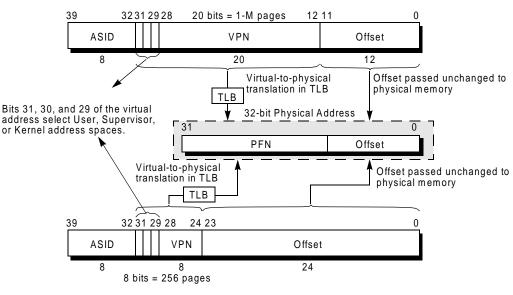

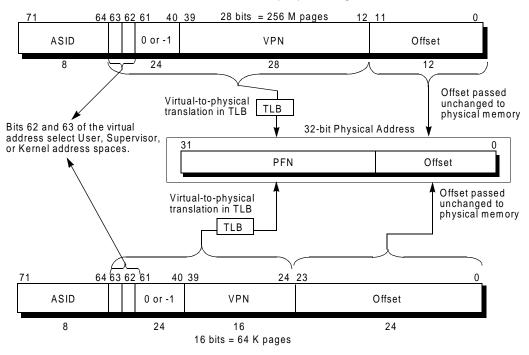

**Chapter 4: Memory Management Unit** discusses the processor's virtual and physical address spaces, the virtual-to-physical address translation, the translation lookaside buffer (TLB) process, and the system control coprocessor registers that provide the software interface to the TLB.

**Chapter 5: Cache Organization and Operation** describes the cache memory's place in the VR5432 memory configuration and individual cache organization.

**Chapter 6: CPU Exceptions** describes the processor's exception types, registers, vector offsets, processing handling, and interrupts.

**Chapter 7: Floating-Point Unit** describes the FPU coprocessor, including the programming model, instruction set and formats, and the pipeline.

**Chapter 8: Floating-Point Exceptions** discusses FPU exception types, exception trap processing, exception flags, saving and restoring states when handling an exception, and trap handlers for IEEE Standard 754 exceptions.

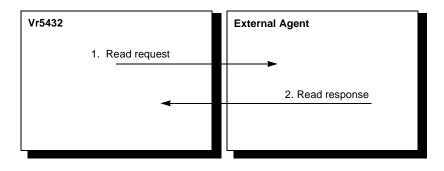

**Chapter 9: Bus Interface** describes how the processor accesses the external resources needed to satisfy cache misses and uncached operations, while permitting an external agent access to some of the processor's internal resources.

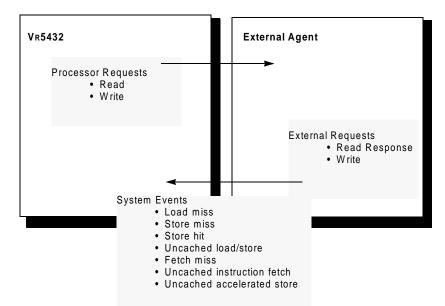

**Chapter 10: System Interface Transactions (Native Mode)** describes processor and external requests in the native system interface protocol of the VR5432 processor.

**Chapter 11: System Interface Protocols (Native Mode)** contains a cycle-by-cycle description of the system interface protocols for each type of processor and external request in the native protocol of the VR5432 processor.

**Chapter 12: System Interface Transactions (R43K Mode)** This section describes processor and external requests as they occur in R43K (VR4300 compatibility) mode.

**Chapter 13: System Interface Protocols (R43K Mode)** contains a cycle-by-cycle description of the system interface protocols for each type of processor and external request in R43K mode.

**Chapter 14: Initialization Interface** describes the processor reset and initialization signals.

**Chapter 15: Clock Interface** describes the basic system clocks, SysClock and PClock, and Phase-Locked Loop (PLL) and Bypass PLL modes.

#### Volume 2 (U15397E)

**Chapter 16: Instruction Set Overview** discusses the general attributes of the CPU, FPU, multimedia, and debugging instructions of the MIPS IV instruction set architecture (ISA) utilized by the VR5432 processor.

**Chapter 17: CPU Instruction Set** describes the details of the CPU instructions.

**Chapter 18: Floating-Point Unit Instruction Set** describes the details of the FPU instructions.

**Chapter 19: Multimedia Instruction Set** describes the details of the multimedia instructions.

**Chapter 20: Debug and Test Features** describes the VR5432 processor's debug and test functions, Debug mode, and debug instructions.

**Appendix A: Sublock Order** describes how a block of data elements (bytes, halfwords, words, or doublewords) can be retrieved from storage in sequential or nonsequential (sub-block) order.

Appendix B: Comparing the VR4300, VR5000, and VR5432 Processors delineates each processor's attributes.

**Appendix C: PLL Analog Power Filtering** illustrates the phaselocked loop circuit configuration.

**Appendix D: Instruction Hazards** identifies the VR5432 instruction hazards that occur with certain instruction and event combinations (such as pipeline delays, cache misses, interrupts, and exceptions).

#### **Related Documents**

See also the following documents. The related documents indicated here may include preliminary versions. However, preliminary versions are not marked as such.

| Product | Data Sheet | User's Manual         |                 |

|---------|------------|-----------------------|-----------------|

| Troduct | Data Sheet | Hardware Architecture | Instruction Set |

| Vr5432  | U13504E    | U13751E               | U15397E         |

| Vr5000  | U12031E    | U11761E               | U12754E         |

| Vr10000 | U12703E    | U10278E               | U12754E         |

## Introduction

The VR5432<sup>™</sup> microprocessor is an NEC VR Series<sup>™</sup> RISC (reduced instruction set computer) microprocessor that implements the high-performance 64-bit MIPS<sup>®</sup> IV architecture.

The instruction set for the VR5432 processor is compatible with those of the VR3000<sup>TM</sup> and VR4000<sup>TM</sup> microprocessor families, which are based on the MIPS III architecture. It is also compatible with the MIPS IV architecture used on the VR5000<sup>TM</sup> and VR10000<sup>TM</sup> microprocessors. Therefore, existing applications can be implemented easily with the VR5432 processor.

The VR5432 processor (part number  $\mu$ PD30541GD) implements a 32-bit system interface, which can operate in both VR5432 Native mode and R43K mode (which emulates the interface used in the VR4300<sup>TM</sup> microprocessor). For most VR4300 applications, the VR5432 offers substantial performance improvement, minimal product redesign, and fast time to market.

## 1.1 **Device Features**

The VR5432 has the following features:

- MIPS IV instruction set with MACC (multiply and accumulate) and DSP/multimedia extension

- 0.25-µm static CMOS technolog

- 64-bit architecture with 32-bit split-transaction external data bus

- Dual-issue superscalar implementatio

- 4K-entry branch prediction table with 2-bit saturating counter mechanism

- 4-entry nonblocking data cache miss queue

- 4-entry transaction buffer (4 doublewords total

- 32 KB, 2-way set-associative, line-locked, 32-byte/block instruction cache

- 32 KB, 2-way set-associative, write-through, write-back, line-locked 32-byte/block data cache

- 48-entry translation lookaside buffer (TLB), mapping two pages per entry

- 4-entry instruction micro-TLB

- 4-entry data micro-TLB

- 40-bit virtual address space

- Physical address space: 36 bits are internal; the lower 32 bits are external

- Single- and double-precision IEEE-754 floating-point operations

- Up to 83 MHz external bus with on-chip clock multiplier for internal frequency of ×2, ×2.5, ×3, or ×4 the external clock

- N-Wire and N-Trace hardware debugging interfac

- Upward compatibility with VR300 <sup>™</sup> and VR4000 devices

- Bus protocol compatibility mode for R4300 system interface

- 2.5 V core logic with 3.3 V external interfac

## 1.2 Internal Architecture

#### 1.2.1 **Configuration**

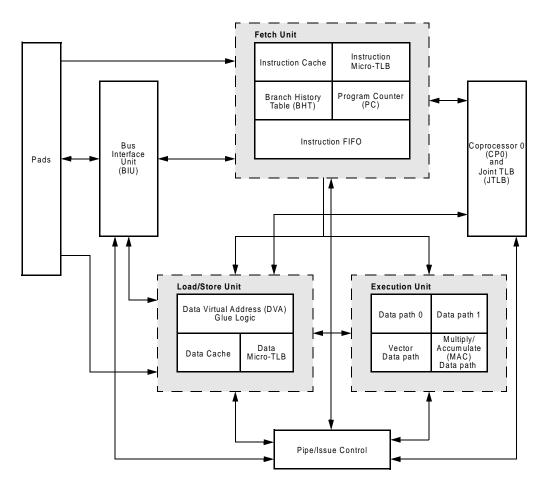

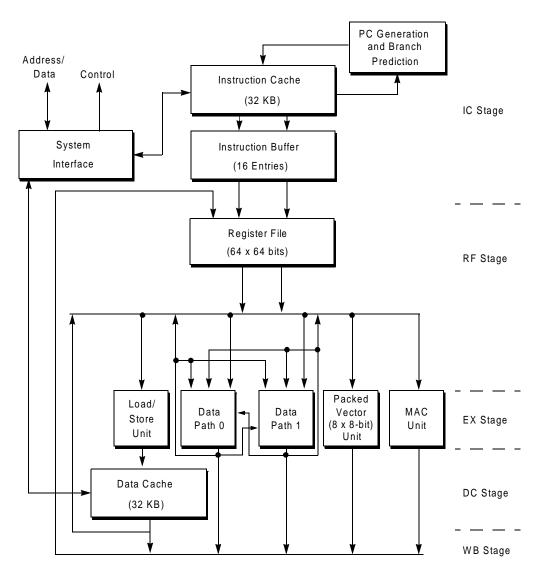

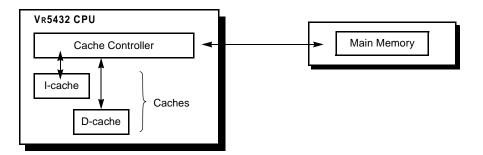

Figure 1-1 is an internal block diagram of the VR5432 processor. Descriptions of each block follow.

Figure 1-1 Block Diagram

#### Fetch Unit

The fetch unit transfers instructions from the instruction cache to the load/store unit (LSU) or the execution unit. The fetch unit includes the following elements.

**Instruction Cache.** The instruction cache is 32 KB and 2-way set associative, with line-locking capability. It has a 64-bit read and a 64-bit write port. It is always accessed on a doubleword boundary, providing two instructions each time it is accessed.

**Instruction Micro-TLB.** The instruction micro-TLB (ITLB) has four entries, each of which supports a variable page size and is refilled from the joint TLB (JTLB) using a pseudo LRU algorithm. The instruction virtual address (IVA) is translated by the ITLB. This TLB is completely invisible to software.

**Branch History Table.** The branch history table (BHT) has one entry per instruction cache doubleword. The BHT implements a 2-bit saturating counter branch prediction scheme.

**Program Counter.** The program counter (PC) keeps track of the program flow and generates new program counters. The new program counters access instructions from the instruction cache or from the main memory.

**Instruction FIFO.** This FIFO isolates instruction cache accesses from instruction issue logic. As mentioned above, the VR5432 processor can fetch up to two instructions per cycle. In some cases, both of these instructions cannot be issued. The FIFO holds these instructions until they are ready to be issued; however, the fetch unit continues to access instructions during this time.

#### Load/Store Unit

The load/store unit (LSU) loads and stores data to/from the data cache or main memory. This unit also contains data alignment logic for Load instructions. The LSU includes the following elements.

**Data Virtual Address.** When the LSU receives a Load/Store instruction from the fetch unit, it calculates an address from which data is to be retrieved or where data is to be stored. This address is the data virtual address (DVA). The LSU contains the adder that calculates this address.

**Data Cache.** The data cache is 32 KB and 2-way set associative, with line-locking capability. It has a 64-bit read and a 64-bit write port. It is always accessed on a doubleword boundary, providing a doubleword each time it is accessed.

**Data Micro-TLB.** The data micro-TLB (DTLB) has four entries, each of which supports a variable page size and is refilled from the joint TLB (JTLB) using a pseudo LRU algorithm. The DVA is translated by the DTLB. This TLB is completely invisible to software.

#### **Execution Unit**

The V<sub>R</sub>5432 is a superscalar microprocessor that can issue two instructions simultaneously. There are four execution datapaths in this processor. Data path 0 (DP0) and Data path 1 (DP1) execute both integer and floating-point instructions. The multiply/accumulate (MAC) data path executes V<sub>R</sub>5432 processor-specific MAC instructions. The vector data path works on V<sub>R</sub>5432 processor-specific multimedia instructions.

#### **Pipe/Issue Control**

Pipeline flow and instruction execution are handled by the logic, which resides in this block. This block also contains control logic, which handles interruptions that affect the pipeline flow.

#### **Coprocessor 0 and Joint TLB**

The VR5432 processor executes the MIPS instruction set. MIPS architecture defines several control and status registers, which are used to control the processor. These registers reside in the Coprocessor 0 (CP0) block. The processor also includes a 48-entry, MIPS-compatible JTLB, which supports even/odd page sizes.

#### **Bus Interface Unit**

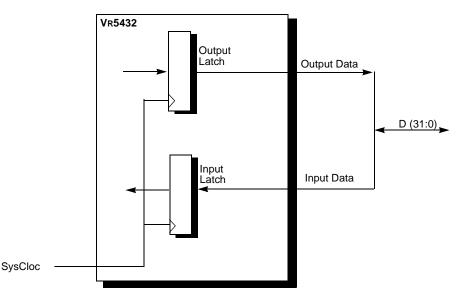

The bus interface unit (BIU) minimizes processor stalls and maximizes bus utilization. The BIU isolates the bus from the processor core and makes the most efficient use of the bus, performing burst transfers whenever possible.

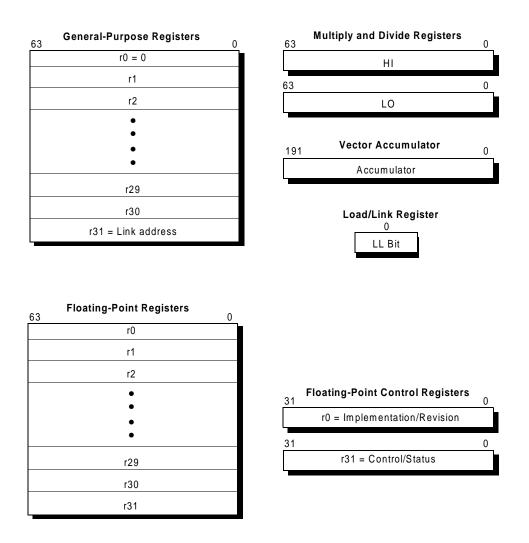

#### 1.2.2 CPU Registers

The processor provides the following registers:

- 32 64-bit general-purpose registers (GPR

- 32 64-bit floating-point registers (FPR

In addition, the processor provides the following special registers:

- 64-bit HI register, to receive the integer multiply an divide highorder doubleword result

- 64-bit LO register, to receive the integer multiply and divide loworder doubleword result

- 1-bit Load/Link (LL) Bit register

- 192-bit Accumulator register, for operating on media instruction

- 32-bit floating-point Implementation/Revision register (FCR0

- 32-bit floating-point Control/Status register (FCR31)

Two of the CPU general-purpose registers have assigned functions:

- r0 is hardwired to a value of zero, and can be used as the target register for any instruction where the result is to be discarded. r0 can also be used as a source when a zero value is needed.

- r31 is the link register used by JAL and JALR instructions. It can be used by other instructions. Make sure that other data used in calculations does not overlap with the register used by the JAL/JALR instruction

Furthermore, the processor contains dedicated registers in the system control processor (CP0) that support exception processing and address management. CPU registers can operate as either 32- or 64-bit registers, depending on the VR5432 processor operation mode.

Figure 1-2 shows the VR5432 processor registers.

Figure 1-2 VR5432 Processor Registers

The VR5432 processor has no Program Status Word (PSW) register as such; this function is covered by the Status and Cause registers included within the system control coprocessor (CP0). CP0 registers are described later in this chapter.

#### 1.2.3 **CPU Instruction Set Overview**

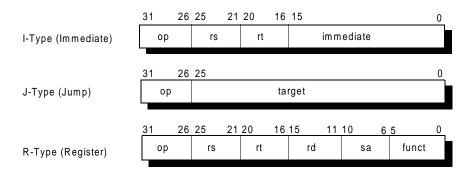

Each CPU instruction is 32 bits long. As shown in Figure 1-3, there are three instruction formats:

- Immediate (I-type)

- Jump (J-type)

- Register (R-type)

Figure 1-3 CPU Instruction Formats

The instructions can be further classified as follows.

- **Load** and **Store** instructions move data between memory and general-purpose registers. They are all immediate (I-type instructions, since the only addressing mode supported for general-purpose-registers is base register plus 16-bit, signed immediate offset (Indexed addressing is supported for floating-point registers.)

- **Computational** instructions perform arithmetic, logical, shift multiply, and divide operations on values in registers. They includ register (R-type, in which both the operands and the result are stored in registers) and immediate (I-type, in which one operand is a 16-bit signed immediate value) formats.

- Jump and Branch instructions change the control flow of a program. Jumps are always made to an address formed by combining a 26-bit target address with the high-order bits of the program counter (J-type format) or register address (R-type format). Branch instructions ar performed to the 16-bit offset address relative to the program counter (I-type). Jump and Link instructions save their return address in register 31.

- **Coprocessor** instructions were originally defined in the MIP architecture to perform operations in coprocessors. However, "true" coprocessors (in the sense of functional units that operate in parallel with the CPU) are not implemented. For example, the original coprocessor 1 was the FPU, but in the VR5432 the FPU instructions are executed using the same data paths used for integer instructions The Coprocessor 2 opcodes have been used for the multimedi instruction set extensions

- **Coprocessor 0** (system coprocessor, CP0) instructions perfor operations on CP0 registers to control the memory management and exception handling facilities of the processor.

- **Exception** instructions perform System Call exception an Breakpoint exception operations, cause a branch to the general exception handling vector based upon the result of a comparison, or implement the MAC instruction set extensions. These instructions occur in both R-type (both the operands and the result are registers) and I-type (one operand is a 16-bit immediate value) formats

Refer to Chapter 16 for an overview of instructions, Chapter 17 for CPU instruction details, Chapter 18 for FPU instruction details, Chapter 19 for multimedia instruction details, and Chapter 20 for debug and test instructions.

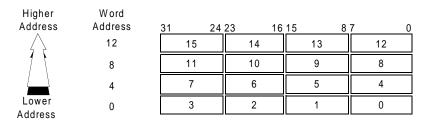

#### 1.2.4 Data Formats and Addressing

The V<sub>R</sub>5432 processor uses four data formats: a 64-bit doubleword, a 32-bit word, a 16-bit halfword, and an 8-bit byte. Byte ordering within all of the larger data formats—halfword, word, doubleword—can be configured as either big or little endian. When the V<sub>R</sub>5432 processor is configured as a big-endian system, byte 0 is the most-significant (left-most) byte, thereby providing compatibility with Motorola's MC 68000<sup>TM</sup> and IBM's System/370<sup>TM</sup> conventions. Figure 1-4 shows this configuration.

| Higher<br>Address | Word<br>Address | 31 24 | 23 16 | 15 8 | 7 0 |

|-------------------|-----------------|-------|-------|------|-----|

| $\bigwedge$       | 12              | 12    | 13    | 14   | 15  |

| 1                 | 8               | 8     | 9     | 10   | 11  |

|                   | 4               | 4     | 5     | 6    | 7   |

| Lower<br>Address  | 0               | 0     | 1     | 2    | 3   |

Figure 1-4 Big-Endian Byte Ordering

*Note:* The most-significant byte has the lowest address. A word is addressed by the address of the most-significant byte.

When configured as a little-endian system, byte 0 is always the least-significant (right-most) byte, which is compatible with Intel's iAPX<sup>TM</sup> x86 and DEC VAX<sup>TM</sup> conventions. Figure 1-5 shows this configuration.

Unless otherwise specified, the little-endian system is used throughout this manual.

Figure 1-5 Little-Endian Byte Ordering

*Note:* The least-significant byte has the lowest address. A word is addressed by the address of the least-significant byte.

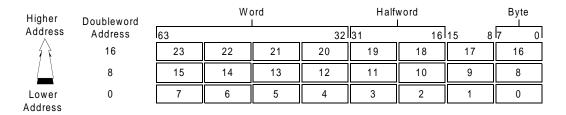

| Higher<br>Address | Doubleword |    | Wo | ord<br>I |    | Half | vord |      | Byte |

|-------------------|------------|----|----|----------|----|------|------|------|------|

| Address           | Address    | 63 |    |          | 32 | 31   | 16   | 15 8 | 7 0  |

|                   | 16         | 16 | 17 | 18       | 19 | 20   | 21   | 22   | 23   |

|                   | 8          | 8  | 9  | 10       | 11 | 12   | 13   | 14   | 15   |

| Lower<br>Address  | 0          | 0  | 1  | 2        | 3  | 4    | 5    | 6    | 7    |

#### Figure 1-6 Big-Endian Data in a Doubleword

*Note:* The most-significant byte has the lowest address. A word is addressed by the address of the most-significant byte.

| Figure 1-7 Little-Endian Data in a Doublewo | igure 1-7 | Little-Endian | Data in | a Doublewor | d |

|---------------------------------------------|-----------|---------------|---------|-------------|---|

|---------------------------------------------|-----------|---------------|---------|-------------|---|

*Note:* The least-significant byte has the lowest address. A word is addressed by the address of the least-significant byte.

The CPU uses byte addressing for halfword, word, and doubleword accesses with the following alignment constraints:

- Halfword accesses must be aligned on an even byte boundary (0, 2, 4...).

- Word accesses must be aligned on a byte boundary divisible by fou (0, 4, 8...).

- Doubleword accesses must be aligned on a byte boundary divisibl by eight (0, 8, 16...).

The following special instructions load and store words that are not aligned on 4-byte (word) or 8-byte (doubleword) boundaries:

| LWL | LWR | SWL | SWR |

|-----|-----|-----|-----|

| LDL | LDR | SDL | SDR |

These instructions are always used in pairs to access data not aligned at a boundary. To access data not aligned at a boundary, an additional PCycle is necessary, compared to accessing data aligned at a boundary.

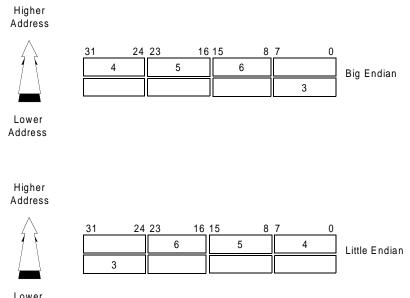

Figure 1-8 illustrates how a word misaligned and having byte address 3 is accessed in big- and little-endian systems.

Lower Address

### 1.2.5 System Control Coprocessor (CP0)

The original MIPS architecture defined up to four coprocessors (CP0 through CP3). Coprocessor 1 was the FPU, and coprocessors 2 and 3 were reserved for future use. However, with the introduction of the MIPS IV instruction set, the coprocessor 3 opcodes were assigned to extensions of the floating-point instruction set. On the VR5432 (and specific to this implementation), the coprocessor 2 opcodes have been used for multimedia instruction set extensions. Coprocessor 0 (CP0) remains the internal system control coprocessor and supports the virtual memory system and exception processing. The virtual memory system uses the on-chip TLB and CP0 registers.

CP0 converts virtual addresses into physical addresses, controls the operating mode (Kernel, Supervisor, or User mode), and performs exception processing. It also controls the cache subsystem to analyze causes and return execution from error processing. CP0 also includes implementation-dependent test and debug features.

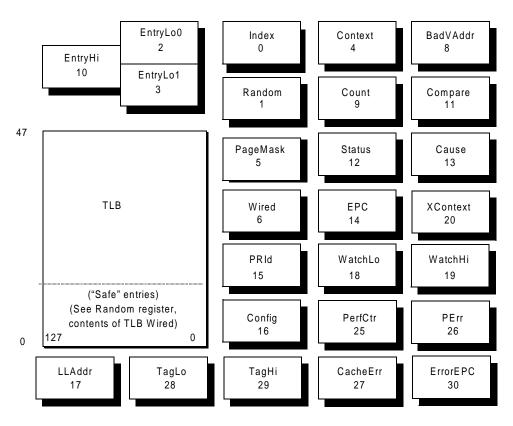

Figure 1-9 shows the CP0 registers; Table 1-1 briefly explains each register. For the details of the registers related to the virtual memory system, refer to Chapter 4; for the details of the registers used for exception processing, refer to Chapter 6.

| Register Name | Register # |

|---------------|------------|

| Index*        | 0          |

| Random*       | 1          |

| EntryLo0*     | 2          |

| EntryLo1*     | 3          |

| Context**     | 4          |

| PageMask*     | 5          |

| Wired*        | 6          |

| RFU           | 7          |

| BadVAddr**    | 8          |

| Count**       | 9          |

| EntryHi*      | 10         |

| Compare**     | 11         |

| Status**      | 12         |

| Cause**       | 13         |

| EPC**         | 14         |

| PRId          | 15         |

|               | _          |

| Register Name  | Register # |

|----------------|------------|

| Config*        | 16         |

| LLAddr         | 17         |

| WatchLo        | 18         |

| WatchHi        | 19         |

| XContext**     | 20         |

| RFU            | 21         |

| RFU            | 22         |

| RFU            | 23         |

| RFU            | 24         |

| PerfCtr        | 25         |

| Parity Error** | 26         |

| Cache Error**  | 27         |

| TagLo          | 28         |

| TagHi          | 29         |

| ErrorEPC**     | 30         |

| RFU            | 31         |

For memory management For exception processing \*

\*\*

RFU Reserved for future use

Figure 1-9 CP0 Registers

| Register<br>Number | Register<br>Name | Description                                                                                                                                                        |

|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | Index            | Index into the TLB                                                                                                                                                 |

| 1                  | Random           | Random pointer to the TLB                                                                                                                                          |

| 2                  | EntryLo0         | Even PFN and page attributes for TLB entry                                                                                                                         |

| 3                  | EntryLo1         | Odd PFN and page attributes for TLB entry                                                                                                                          |

| 4                  | Context          | Pointer to kernel PTE (32-bit addressing)                                                                                                                          |

| 5                  | PageMask         | TLB page size mask                                                                                                                                                 |

| 6                  | Wired            | Number of wired (locked) TLB entries                                                                                                                               |

| 7                  |                  | Unused                                                                                                                                                             |

| 8                  | BadVAddr         | Bad virtual address                                                                                                                                                |

| 9                  | Count            | Timer count                                                                                                                                                        |

| 10                 | EntryHi          | VPN and ASID for TLB entry                                                                                                                                         |

| 11                 | Compare          | Timer compare                                                                                                                                                      |

| 12                 | SR               | Status register                                                                                                                                                    |

| 13                 | Cause            | Cause of last exception                                                                                                                                            |

| 14                 | EPC              | Exception program counter                                                                                                                                          |

| 15                 | PRId             | Processor revision identifier                                                                                                                                      |

| 16                 | Config           | Configuration register                                                                                                                                             |

| 17                 | LLAddr           | Load linked address                                                                                                                                                |

| 18                 | WatchLo          | Memory reference trap address lower bits                                                                                                                           |

| 19                 | WatchHi          | Memory reference trap address upper bits                                                                                                                           |

| 20                 | XContext         | Pointer to the kernel PTE (64-bit addressing)                                                                                                                      |

| 21-24              |                  | Unused                                                                                                                                                             |

| 25                 | PerfCtr          | Performance counter registers:<br>Performance Event Specifier/Control 0<br>Performance Counter 0<br>Performance Event Specifier/Control 1<br>Performance Counter 1 |

| 26                 | PErr             | Parity error in cache                                                                                                                                              |

| 27                 | CacheErr         | Cache error register                                                                                                                                               |

| 28                 | TagLo            | Cache tag register                                                                                                                                                 |

Table 1-1 System Control Coprocessor (CP0) Register Definitio n

| Register<br>Number | Register<br>Name | Description                     |

|--------------------|------------------|---------------------------------|

| 29                 | TagHi            | Cache tag register (reserved)   |

| 30                 | ErrorEPC         | Error exception program counter |

| 31                 |                  | Unused                          |

Table 1-1 System Control Coprocessor (CP0) Register Definitions (continued)

### 1.2.6 Floating-Point Unit (FPU)

The floating-point unit (FPU) performs arithmetic operations on floating-point values. The FPU, with associated system software, fully conforms to the requirements of ANSI/IEEE Standard 754–1985, *IEEE Standard for Binary Floating-Point Arithmetic*.

The FPU includes:

- **Full 64-bit operation**. The FPU can contain sixteen 64-bit registers to hold single-precision or double-precision values. Another sixteen floating-point registers can be used by setting the *FR* bit of the Status register to 1. In addition, a 32-bit Control/Status register is provided, conforming to the IEEE exception processing standard.

- Load and Store instruction set. Like the CPU, the FPU uses a load and store-based instruction set. Floating-point operations are starte in a single cycle. Unlike the CPU, some FPU Load and Stor instructions are R-type

#### 1.2.7 Internal Cache

The V $_{R}$ 5432 has an instruction cache and a data cache to enhance the efficiency of pipelining. Each cache has a data width of 64 bits and can be accessed in 1 clock. The instruction cache and data cache can be accessed in parallel. Both the instruction cache and data cache have a capacity of 32 KB.

For the details of each cache, refer to Chapter 5.

## 1.3 Memory Management Unit (MMU)

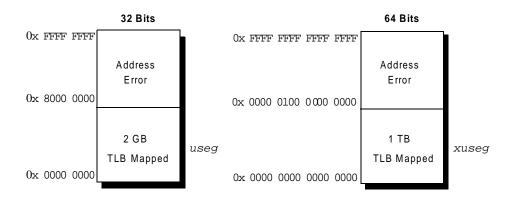

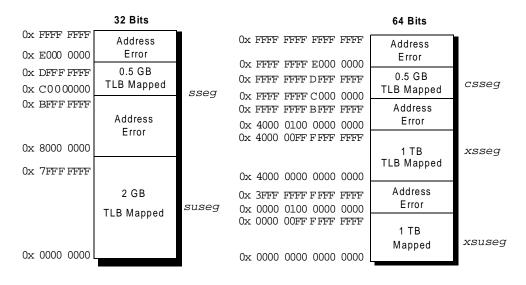

The V<sub>R</sub>5432 processor has a usable 32-bit physical addressing range of 4 GB. However, since it is rare for systems to implement a physical memory space this large, the CPU provides a logical expansion of memory space to the programmer by translating addresses into the large virtual address space. The V<sub>R</sub>5432 processor supports the following two address translation mechanisms:

- 32-bit mode, in which the virtual address space is divided into 2 GB for user processes and 2 GB for the kernel

- 64-bit mode, in which the virtual address is expanded to 1 terabyte( <sup>40</sup> bytes) of user virtual address space

A detailed description of these address spaces is given in Chapter 4.

#### 1.3.1 Translation Lookaside Buffer (TLB)

Virtual memory mapping is performed by a translation lookaside buffer, which holds virtual-to-physical address translations. This fully associative, on-chip TLB contains 48 entries, each of which maps a pair of variable-sized pages of between 4 KB and 16 MB.

The TLB can hold both instruction and data addresses, and is sometimes referred to as a joint TLB (JTLB). There are also two 4-entry micro-TLBs, one for instructions and one for data. On a miss to either micro-TLB, the pipeline is stalled while the micro-TLB is loaded from the TLB. Loading of the micro-TLBs is handled in the hardware transparently to software.

A virtual address is concatenated with a process identifier and both are sent to the JTLB for translation. If there is no matching entry in the JTLB, an exception occurs and software writes the entry contents to the on-chip JTLB from a page table in memory. The JTLB entry to be rewritten is selected by a value in either the Random or Index register.

#### 1.3.2 **Operating Modes**

The  $V_R5432$  processor has three operating modes:

- User mode

- Supervisor mode

- Kernel mode

The manner in which memory addresses are translated or mapped depends on the operating mode of the CPU; this is described in Chapter 4.

## 1.4 **Instruction Pipeline**

The  $V_R5432$  incorporates a dual-issue superscalar architecture that allows two integer or floating-point instructions to be issued simultaneously to a five-stage instruction pipeline. For details, refer to Chapter 3.

# Signal Descriptions

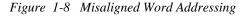

This chapter describes the VR5432 hardware interface signals. The signals include the power inputs and the interfaces for the system, clock, interrupt, initialization, N-Wire/N-Trace hardware debugging, and Joint Test Action Group (JTAG) testing.

The VR5432 supports two interface protocols: VR5432 native mode and R43K (a compatibility mode that emulates the interface used on the VR4300). The mode is selected by the level sampled on the OptionR43K\* pin during a cold reset. As described in subsequent sections, some signals are named and behave differently in the two modes.

Figure 2-1 shows the processor signals by function. Signal names used in R43 mode are shown in brackets.

*Note:* In this manual, active-low signal names are spelled with a trailing asterisk (e.g., the active-low, read-ready signal is RdRdy\*).

Figure 2-1 VR5432 Processor Signals

## 2.1 System Interface Signals

System interface signals provide connections between the  $V_R5432$  processor and the other components in the system. Table 2-1 lists the system interface signals.

| Name                    | Definition                                    | Direction | Description                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|-----------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ExtRqst*/               | External request<br>(OptionR43K* is<br>high)  | Input     | An external agent asserts ExtRqst* to request<br>use of the system interface. The processor<br>grants the request by asserting Release*.                                                                                                                                                                                                           |

| [EReq*]                 | External request<br>(OptionR43K* is<br>low)   | mput      | An external agent asserts EReq* to request<br>use of the system interface. The processor<br>grants the request by asserting PMaster*.                                                                                                                                                                                                              |

|                         | Release interface<br>(OptionR43K* is<br>high) |           | In response to the assertion of ExtRqst*, the<br>processor asserts Release*, signaling to th<br>requesting device that th system interface is<br>available. Release* is also asserted for an<br>uncompelled change to slave state when one<br>or more read requests is outstanding.                                                                |

| Release*/<br>[PMaster*] | Processor master<br>(OptionR43K* is<br>low)   | Output    | Indicates the processor is the master of the<br>system interface bus. In response to the<br>assertion o EReq*, the processor deasserts<br>PMaster*, signaling to the requesting devi<br>that th system interface is available.<br>PMaster* is also deasserted for an<br>uncompelled change to slave state when one<br>read request is outstanding. |

| PReq*/[PReq*]           | Processor request<br>(OptionR43K* is<br>high) | Output    | Indicates that the processor has another<br>request that is pending. This is used to indicate<br>that the processor would like to send another<br>transaction. It is up to the external agent to<br>grant the request by releasing the system<br>interface with an external null request.                                                          |

|                         | Processor request<br>(OptionR43K* is<br>low)  | Sulput    | Indicates the processor is requesting system<br>interface bus ownership. Also, when the<br>processor experiences a protocol error (the<br>processor detects that an external agent has<br>violated the SysAD bus protocol), the<br>processor continuously toggles PReq*.                                                                           |

Table 2-1 System Interface Signal

| Name                            | Definition                                                     | Direction        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|----------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RdRdy*/                         | Read ready<br>(OptionR43K* is<br>high)                         | Input            | The external agent asserts RdRdy* to indicate that it can accept processor read requests.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [Unused]                        | Unused<br>(OptionR43K* is<br>low)                              | mput             | The external agent asserts RdRdy* to indicate that it can accept processor read requests.         The signal is not used when the processor's interface protocol is compatible with the VR4300 interface protocol.         A 32-bit address and data bus fo communication between the processor and a external agent         A 32-bit address and data bus fo communication between the processor and a external agent         A 32-bit address and data bus fo communication between the processor and a external agent         A 4-bit bus containing parity for the SysAI bus. SysADC is valid on data cycles only.         These pins are for cache test only.         A 9-bit bus for command and data identifie transmission between the processor and an external agent         A 5-bit bus for command and data identifie transmission between the processor and an external agent. |

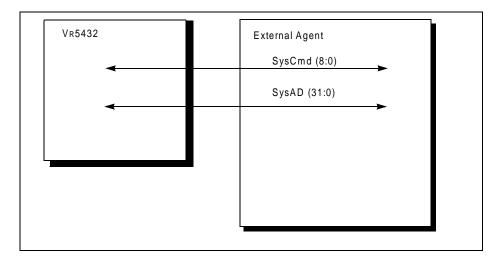

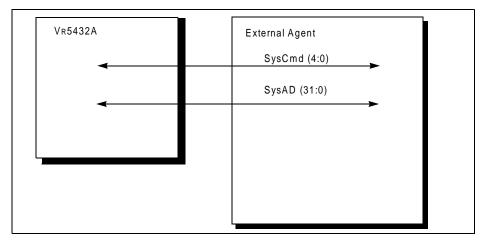

| SysAD (31:0)/                   | System address/data<br>bus (OptionR43K*<br>is high)            | Input/           | communication between the processor and an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [SysAD (31:0)]                  | System address/data<br>bus (OptionR43K*<br>is low)             | Output           | communication between the processor and an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SysADC (3:0)/<br>[SysADC (3:0)] | System address/<br>data check bus<br>(OptionR43K* is<br>high)  | Input/<br>Output | A 4-bit bus containing parity for the SysAD bus. SysADC is valid on data cycles only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| [598ADC (5.0)]                  | Cache test<br>(OptionR43K* is<br>low)                          | Output           | bus. SysADC is valid on data cycles only.<br>These pins are for cache test only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

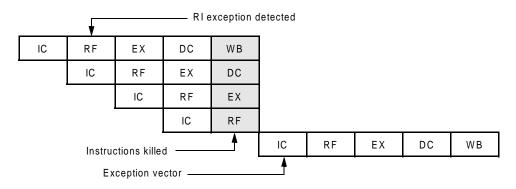

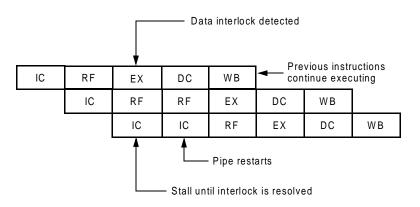

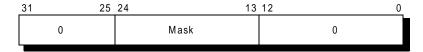

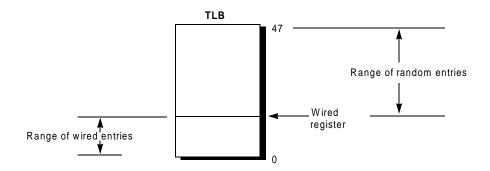

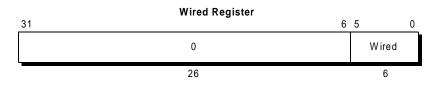

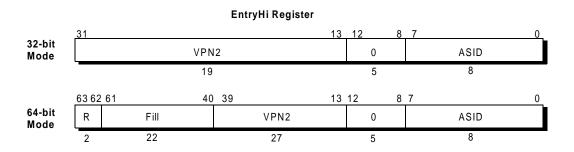

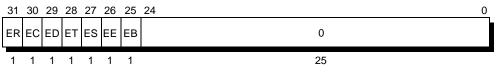

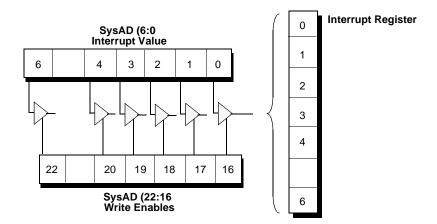

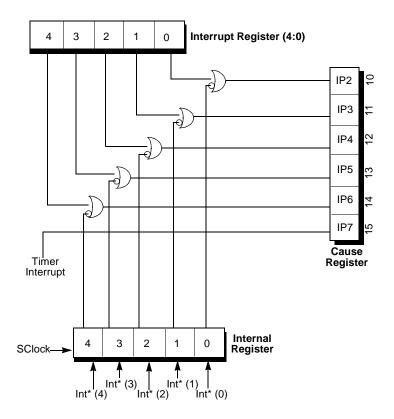

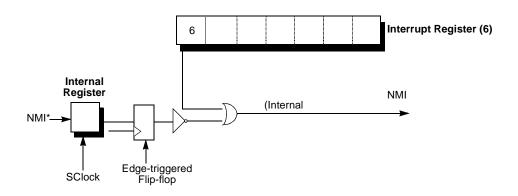

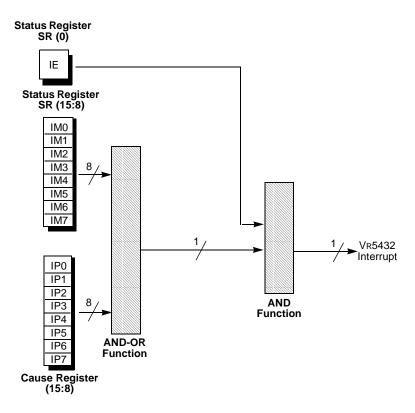

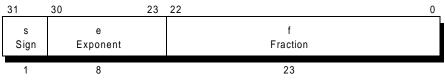

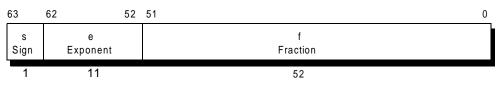

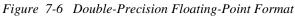

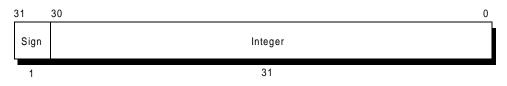

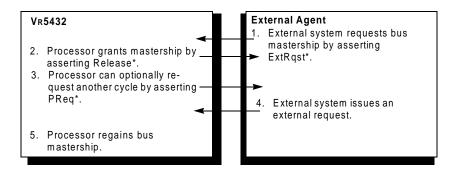

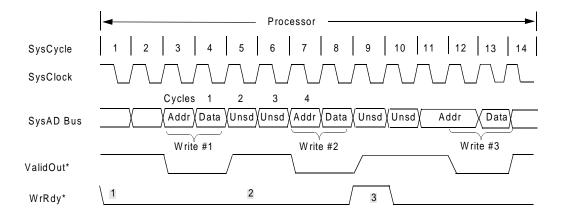

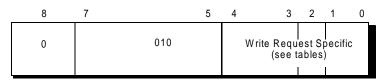

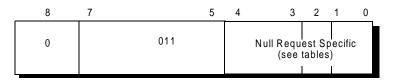

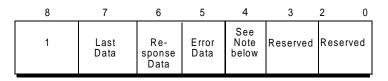

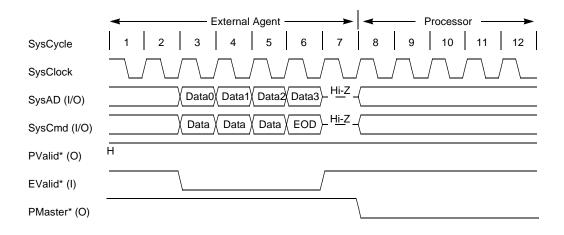

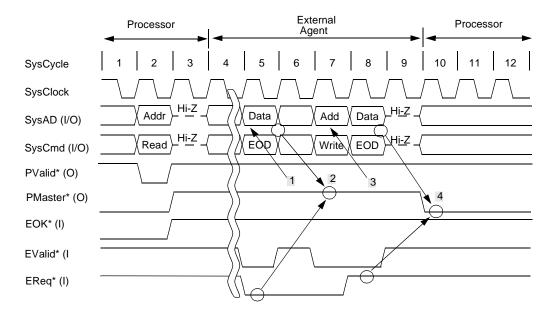

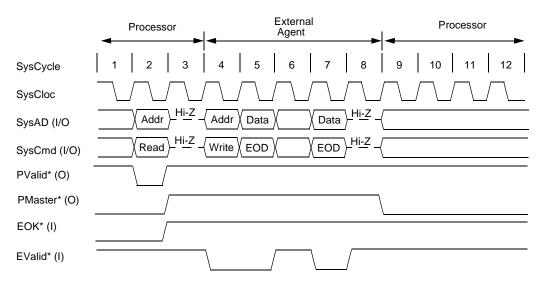

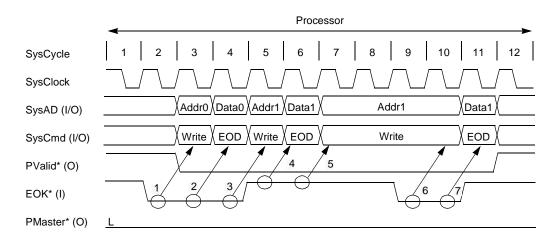

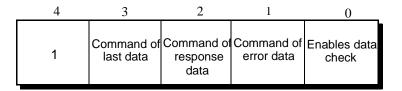

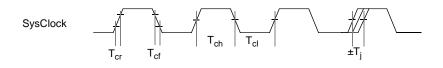

| SysCmd (8:0)/                   | System command/<br>data identifier<br>(OptionR43K* is<br>high) | Input/           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |