**User's Manual**

# VR5432™

## 64-Bit MIPS<sup>®</sup> RISC Microprocessor

Volume 2

μ**PD30541GD**

Document No.U15397EU5V0UMJ1 Date Published: May 2001 CP (K)

© **NEC Electronics Inc.** 2000 Printed in U.S.A.

VR5432 Microprocessor User's Manual Document Number U15397EU5V0UMJ1

#### **Revision History**

February 1999: First release August 1999: Version 2, Preliminary December 1999: Version 3, Preliminary update February 2000: Version 4, Document release May 2000: Version 5, Document corrections

NEC, the NEC logo, VR Series, VR3000, VR4000, VR4300, VR5000, VR5432 and VR10000 are registered trademarks of NEC Corporation. All other product, brand, or trade names used in this publication are the trademarks or registered trademarks of their respective trademark owners.

In North America: No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. All devices sold by NECEL are covered by the provisions appearing in NECEL's Terms and Conditions of Sales only, including the limitation of liability, warranty, and patent provisions. NECEL makes no warranty, express, statutory, implied or by description, regarding information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. "Standard" quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliability requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in any application where failure could result in injury or death. If customers wish to use NECEL devices in applications not intended by NECEL, customers must contact the responsible NECEL salespeople to determine NECEL's willingness to support a given application.

## Contents

## Volume 1

| Preface | XV                                   |

|---------|--------------------------------------|

| Chapter | <b>1 Introduction</b>                |

| 1.1     | Device Features 2                    |

| 1.2     | Internal Architecture                |

| 1.2.1   | Configuration                        |

| 1.2.2   | CPU Registers 6                      |

| 1.2.3   | CPU Instruction Set Overview         |

| 1.2.4   | Data Formats and Addressing10        |

| 1.2.5   | System Control Coprocessor (CP0)     |

| 1.2.6   | Floating-Point Unit (FPU)            |

| 1.2.7   | Internal Cache 16                    |

| 1.3     | Memory Management Unit (MMU)         |

| 1.3.1   | Translation Lookaside Buffer (TLB)17 |

| 1.3.2   | Operating Modes 17                   |

| 1.4     | Instruction Pipeline                 |

| Chapter | 2 Signal Descriptions                |

| 2.1     | System Interface Signals             |

| 2.2     | Power Inputs                         |

| 2.3     | Clock Interface Signals              |

| 2.4     | JTAG and Test Interface Signals      |

| 2.5     | Interrupt Interface Signals          |

| 2.6     | Initialization Interface Signals     |

| 2.7     | Pin Orientation                      |

| Chapter | 3 Pipeline                              |    |

|---------|-----------------------------------------|----|

| 3.1     | Pipeline Stages                         |    |

| 3.2     | Branch Delay                            |    |

| 3.3     | Load Delay                              |    |

| 3.4     | Interlock and Exception Handling        |    |

| 3.4.1   | Exception Conditions                    |    |

| 3.4.2   | Interrupt Latency                       |    |

| 3.4.3   | Stall Conditions                        |    |

| 3.5     | Transaction Buffer                      |    |

| Chapter | 4 Memory Management Unit                |    |

| 4.1     | Translation Lookaside Buffer            |    |

| 4.1.1   | Hits and Misses                         |    |

| 4.2     | Processor Modes                         |    |

| 4.2.1   | Processor Operating Modes               |    |

| 4.2.2   | Instruction Set Mode                    |    |

| 4.2.3   | Addressing Modes                        |    |

| 4.3     | Addresses and Address Spaces            |    |

| 4.3.1   | Virtual Addresses                       |    |

| 4.3.2   | Physical Addresses                      |    |

| 4.3.3   | Virtual-to-Physical Address Translation |    |

| 4.3.4   | 32-Bit Mode Virtual Address Translation |    |

| 4.3.5   | 64-Bit Mode Virtual Address Translation |    |

| 4.3.6   | User Address Space                      |    |

| 4.3.7   | Supervisor Space                        |    |

| 4.3.8   | Kernel Space                            |    |

| 4.4     | System Control Coprocessor              |    |

| 4.4.1   | TLB Entry Format                        |    |

| 4.4.2   | Instruction and Data Micro-TLBs         |    |

| 4.5     | CP0 Registers                           |    |

| 4.5.1   | Index Register (0)                      |    |

| 4.5.2   | Random Register (1)                     |    |

| 4.5.3   | EntryLo0 (2) and EntryLo1 (3) Registers | 72 |

| 4.5.4   | PageMask Register (5)                   |    |

| 4.5.5   | Wired Register (6)                      |    |

|    | 4.5.6         | EntryHi Register (10)                                    | 75  |

|----|---------------|----------------------------------------------------------|-----|

|    | 4.5.7         | Processor Revision Identifier (PRId) Register (15)       | 76  |

|    | 4.5.8         | Config Register (16)                                     |     |

|    | 4.5.9         | Load Linked Address (LLAddr) Register (17)               |     |

|    | 4.5.10        | Cache Tag Registers [TagLo (28) and TagHi (29)]          |     |

|    | 4.6           | Virtual-to-Physical Address Translation Process          |     |

|    | 4.7           | TLB Exceptions                                           | 83  |

|    | 4.8           | TLB Instructions                                         |     |

| Ch | apter         | 5 Cache Organization and Operation                       |     |

|    | 5.1           | Memory Organization                                      | 86  |

|    | 5.2           | Primary Cache Organization                               |     |

|    | 5.2.1         | Cache Line Lengths                                       |     |

|    | 5.2.2         | Cache Sizes                                              |     |

|    | 5.2.3         | Instruction Cache Organization                           | 88  |

|    | 5.2.4         | Data Cache Organization                                  | 89  |

| Ch | apter         | 6 CPU Exceptions                                         |     |

|    | 6.1           | Exception Processing Overview                            |     |

|    | 6.2           | Exception Processing Registers                           |     |

|    | <b>6</b> .2.1 | Context Register (4)                                     |     |

|    | 6.2.2         | Bad Virtual Address Register (BadVAddr) (8)              |     |

|    | 6.2.3         | Count Register (9)                                       |     |

|    | 6.2.4         | Compare Register (11)                                    |     |

|    | 6.2.5         | Status Register (12)                                     |     |

|    | 6.2.6         | Cause Register (13)                                      |     |

|    | 6.2.7         | Exception Program Counter (EPC) Register (14)            |     |

|    | 6.2.8         | XContext Register (20)                                   |     |

|    | 6.2.9         | WatchLo and WatchHi Registers (18 and 19)                |     |

|    | 6.2.10        | Performance Counter Registers (25)                       |     |

|    | 6.2.11        | Parity Error (PErr) Register (26)                        |     |

|    | 6.2.12        | Cache Error (CacheErr) Register (27)                     |     |

|    | 6.2.13        | Error Exception Program Counter (ErrorEPC) Register (30) |     |

|    | 6.3           | Processor Exceptions                                     | 112 |

|    | 6.3.1         | Exception Types                                          |     |

|    | 6.3.2  | Exception Vector Locations                  | . 115 |

|----|--------|---------------------------------------------|-------|

|    | 6.4    | Exception Vector Offsets                    | 115   |

|    | 6.4.1  | TLB Refill Vector Selection                 | 116   |

|    | 6.4.2  | Priority of Exceptions                      | 118   |

|    | 6.4.3  | Reset Exception                             | 119   |

|    | 6.4.4  | Soft Reset Exception                        | 121   |

|    | 6.4.5  | Nonmaskable Interrupt (NMI) Exception       | 122   |

|    | 6.4.6  | Address Error Exception                     | 123   |

|    | 6.4.7  | TLB Exceptions                              | 124   |

|    | 6.4.8  | Cache Error Exception                       | 127   |

|    | 6.4.9  | Bus Error Exception                         | 128   |

|    | 6.4.10 | Integer Overflow Exception                  | 129   |

|    | 6.4.11 | Trap Exception                              | 129   |

|    | 6.4.12 | System Call Exception                       | 130   |

|    | 6.4.13 | Breakpoint Exception                        | 131   |

|    | 6.4.14 | Reserved Instruction Exception              | 132   |

|    | 6.4.15 | Coprocessor Unusable Exception              | 133   |

|    | 6.4.16 | Floating-Point Exception                    | 134   |

|    | 6.4.17 | Watch Exception                             | 134   |

|    | 6.4.18 | Interrupt Exception                         | 135   |

|    | 6.5    | Exception Handling and Servicing Flowcharts | 136   |

|    | 6.6    | Interrupts                                  | 143   |

|    | 6.6.1  | Hardware Interrupts                         | 143   |

|    | 6.6.2  | Nonmaskable Interrupt (NMI)                 | 143   |

|    | 6.6.3  | Asserting Interrupts                        | 143   |

| Ch | apter  | 7 Floating-Point Unit                       | 149   |

|    | 7.1    | Overview                                    | .149  |

|    | 7.2    | FPU Features                                | 150   |

|    | 7.3    | FPU Programming Model                       | 150   |

|    | 7.4    | Floating-Point General-Purpose Registers    |       |

|    | 7.5    | Floating-Point Registers                    | . 153 |

|    | 7.6    | Floating-Point Control Registers            | . 153 |

|    | 7.6.1  | Implementation and Revision Register (FCR0) | . 154 |

|    | 7.6.2  | Control/Status Register (FCR31)             | 155   |

| 7.7     | Floating-Point Formats                                       |     |

|---------|--------------------------------------------------------------|-----|

| 7.8     | Binary Fixed-Point Format                                    |     |

| 7.9     | Floating-Point Instruction Set Overview                      |     |

| 7.9.1   | Floating-Point Load, Store, and Move Instructions            |     |

| 7.9.2   | Floating-Point Conversion Instructions                       |     |

| 7.9.3   | Floating-Point Computational Instructions                    |     |

| 7.10    | FPU Instruction Pipeline Overview                            |     |

| 7.10.1  | Instruction Execution                                        |     |

| 7.10.2  | Instruction Execution Cycle Time                             |     |

| 7.10.3  | Instruction Issuing Constraints with Multicycle Instructions | 171 |

| Chapter | 8 Floating-Point Exceptions                                  |     |

| 8.1     | Exception Types                                              |     |

| 8.2     | Exception Trap Processing                                    |     |

| 8.3     | Flags                                                        |     |

| 8.4     | FPU Exceptions                                               |     |

| 8.4.1   | Inexact Operation Exception (I)                              |     |

| 8.4.2   | Invalid Operation Exception (V)                              |     |

| 8.4.3   | Division by Zero Exception (Z)                               |     |

| 8.4.4   | Overflow Exception (O)                                       |     |

| 8.4.5   | Underflow Exception (U)                                      |     |

| 8.4.6   | Unimplemented Operation Instruction Exception (E)            |     |

| 8.5     | Saving and Restoring State                                   |     |

| 8.6     | Trap Handlers for IEEE Standard 754 Exceptions               |     |

| Chapter | 9 Bus Interface                                              |     |

| 9.1     | Interface Buses In Native Mode                               |     |

| 9.2     | Interface Buses in R43K Mode                                 |     |

| Chapter | 10 System Interface Transactions (Native Mode)               | 191 |

| 10.1    | Terminology                                                  |     |

| 10.2    | Processor Requests                                           |     |

| 10.2.1  | Rules for Processor Requests                                 |     |

| 10.2.2  | Processor Read Request                                       |     |

| 10.2.3  | Processor Write Request                                      |     |

| 10.3    | External Requests                           | 198 |

|---------|---------------------------------------------|-----|

| 10.3.1  | External Read Request                       |     |

| 10.3.2  |                                             |     |

| 10.3.3  | Read Response                               | 200 |

| 10.4    | Handling Requests                           | 201 |

| 10.4.1  | Load Miss                                   | 201 |

| 10.4.2  | Store Miss                                  |     |

| 10.4.3  | Store Hit                                   |     |

| 10.4.4  | Uncached Loads or Stores                    |     |

| 10.4.5  | Uncached Accelerated Stores                 |     |

| 10.4.6  | Uncached Instruction Fetch                  |     |

| 10.4.7  | Fetch Miss                                  |     |

|         |                                             |     |

| Chapter | 11 System Interface Protocols (Native Mode) |     |

| 11.1    | Address and Data Cycles                     |     |

| 11.2    | Issue Cycles                                | 206 |

| 11.3    | Handshake Signals                           |     |

| 11.4    | System Interface Operation                  |     |

| 11.4.1  | Master and Slave States                     |     |

| 11.4.2  | External Arbitration                        |     |

| 11.4.3  | Uncompelled Change to Slave State           |     |

| 11.5    | Processor Request Protocols                 |     |

| 11.5.1  | Processor Read Request Protocol             |     |

| 11.5.2  | Processor Write Request Protocol            |     |

| 11.5.3  | Processor Request Flow Control              |     |

| 11.5.4  | Processor Request Timing Modes              |     |

| 11.6    | External Request Protocols                  |     |

| 11.6.1  | External Arbitration Protocol               |     |

| 11.6.2  | External Read Request Protocol              |     |

| 11.6.3  | External Null Request Protocol              |     |

| 11.6.4  | External Write Request Protocol             |     |

| 11.6.5  | Read Response Protocol                      |     |

| 11.7    | SysADC (3:0) Protocol                       |     |

| 11.8    | Data Rate Control                           | 236 |

| 11.9    | Data Transfer Patterns                      |     |

|     | 11.10        | Word Transfer Ordering                       | . 239 |

|-----|--------------|----------------------------------------------|-------|

|     | <b>11.11</b> | Independent Transmissions on the SysAD Bus   | . 242 |

|     | 11.12        | System Interface Cycle Time                  | . 243 |

|     | 11.13        | System Interface Commands/Data Identifiers   | . 243 |

|     | 11.13.1      | Command and Data Identifier Syntax           | . 244 |

|     | 11.13.2      | System Interface Command Syntax              | . 244 |

|     | 11.13.3      | Read Requests                                | . 245 |

|     | 11.13.4      | System Interface Data Identifier Syntax      | . 248 |

|     | 11.14        | System Interface Addresses                   | . 250 |

|     | 11.14.1      | Addressing Conventions                       | . 250 |

|     | 11.14.2      | Subblock Ordering                            | . 250 |

|     | 11.14.3      | Processor Internal Address Map               | . 251 |

| Cha | apter 1      | 12 System Interface Transactions (R43K Mode) | .253  |

|     | 12.1         | Processor Requests                           | . 254 |

|     | 12.1.1       | Rules for Processor Requests                 |       |

|     | 12.1.2       | Processor Read Request                       | . 256 |

|     | 12.1.3       | Processor Write Request                      | . 257 |

|     | 12.2         | External Requests                            | . 257 |

|     | 12.2.1       | External Write Request                       | . 259 |

|     | 12.2.2       | Read Response                                | . 259 |

|     | 12.3         | Handling Requests                            | . 260 |

|     | 12.3.1       | Fetch Miss                                   | . 260 |

|     | 12.3.2       | Load Miss                                    | . 261 |

|     | 12.3.3       | Store Miss                                   | . 262 |

|     | 12.3.4       | Store Hit                                    | . 262 |

|     | 12.3.5       | Uncached Loads or Stores                     | . 263 |

|     | 12.3.6       | Uncached Accelerated Stores                  |       |

|     | 12.3.7       | Uncached Instruction Fetch                   | . 264 |

| Chapter | 13 System Interface Protocols (R43K Mode)      |     |

|---------|------------------------------------------------|-----|

| 13.1    | Address and Data Cycles                        |     |

| 13.2    | Issue Cycles                                   |     |

| 13.3    | Handshake Signals                              |     |

| 13.4    | System Interface Operation                     |     |

| 13.4.1  | Master and Slave States                        |     |

| 13.4.2  | External Arbitration                           |     |

| 13.4.3  | Uncompelled Change to Slave State              |     |

| 13.5    | Processor Request Protocols                    |     |

| 13.5.1  | Processor Read Request Protocol                |     |

| 13.5.2  | Processor Write Request Protocol               |     |

| 13.5.3  | Processor Request Flow Control                 |     |

| 13.5.4  | Successive Processing of Requests              |     |

| 13.6    | External Request Protocols                     |     |

| 13.6.1  | External Arbitration Protocol                  |     |

| 13.6.2  | External Write Request Protocol                |     |

| 13.6.3  | External Read Response Protocol                |     |

| 13.7    | Discarding and Re-Executing Commands           |     |

| 13.7.1  | Re-Execution of Processor Commands             |     |

| 13.7.2  | Discarding and Re-Executing a Write Command    |     |

| 13.7.3  | Discarding and Re-Executing a Read Command     |     |

| 13.7.4  | Executing and Discarding a Command             |     |

| 13.8    | SysADC (3:0) Protocol                          | 295 |

| 13.9    | Data Flow Control                              | 295 |

| 13.9.1  | Read Response                                  | 295 |

| 13.9.2  | Write Request                                  | 295 |

| 13.9.3  | Independent Transfer on the SysAD (31:0) Bus   |     |

| 13.9.4  | System Endianness                              | 296 |

| 13.10   | System Interface Cycle Time                    |     |

| 13.10.  | 1 Release Latency Time                         | 297 |

| 13.11   | System Interface Commands and Data Identifiers |     |

| 13.12   | Command and Data Identifier Syntax             |     |

| 13.12.  | 1 System Interface Command Syntax              |     |

| 13.12.  | 2 Read Requests                                |     |

| 13.12.  | 3 Write Requests                               | 302 |

|     | 13.12.4 | 4 System Interface Data Identifier Syntax | 304   |

|-----|---------|-------------------------------------------|-------|

|     | 13.12.5 | 5 Data Identifier Bit Definitions         | . 304 |

|     | 13.13   | System Interface Addresses                | . 305 |

|     | 13.13.1 | Addressing Conventions                    | . 306 |

|     | 13.13.2 | 2 Sublock Order Data Retrieval            | . 306 |

| Cha | apter   | 14 Initialization Interface               | 307   |

|     | 14.1    | Processor Reset Signals                   | . 307 |

|     | 14.1.1  | Power-On Reset                            | . 308 |

|     | 14.1.2  | Cold Reset                                | . 309 |

|     | 14.1.3  | Warm Reset                                | . 310 |

|     | 14.1.4  | Processor Reset State                     | . 311 |

|     | 14.2    | Processor Initialization Signals          | . 311 |

| Cha | apter   | 15 Clock Interface                        | 313   |

|     | 15.1    | Basic System Clocks                       | . 313 |

|     | 15.1.1  | SysClock/MasterClock                      | . 313 |

|     | 15.1.2  | PClock                                    | 313   |

|     | 15.2    | Alignment to SysClock                     | . 314 |

|     | 15.3    | Phase-Locked Loop (PLL)                   | . 314 |

|     | 15.4    | Bypass PLL Mode                           |       |

|     | -       |                                           |       |

## Volume 2

| Chapter | 16 Instruction Set Overview  |     |

|---------|------------------------------|-----|

| 16.1    | Instruction Set Architecture |     |

| 16.2    | Instruction Formats          |     |

| 16.3    | Load and Store Instructions  |     |

| 16.3.1  | Delayed Load Instructions    | 323 |

| 16.3.2  | Defining Access Types        | 323 |

| 16.4    | Computational Instructions   |     |

| 16.4.1  | 64-Bit Operations            | 327 |

| 16.5    | Jump and Branch Instructions |     |

| 16.5.1  | Jump Instructions            | 328 |

|    | 16.5.2  | Branch Instructions                              | 328   |

|----|---------|--------------------------------------------------|-------|

|    | 16.6    | Special Instructions                             | 329   |

|    | 16.7    | Coprocessor Instructions                         | 329   |

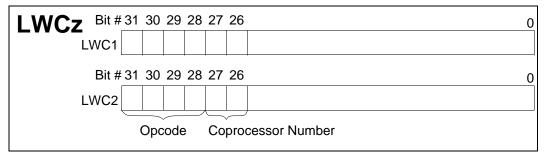

|    | 16.7.1  | Coprocessor Load and Store                       | 330   |

|    | 16.7.2  | Coprocessor Operations                           | 330   |

|    | 16.8    | Implementation-Specific Instructions             | 331   |

|    | 16.8.1  | Overview                                         | 331   |

|    | 16.8.2  | Implementation-Specific Instruction Descriptions | . 333 |

|    | 16.9    | Integer Rotate Instructions                      | 337   |

|    | 16.10   | Integer Multiply-Accumulate Instructions         | . 338 |

|    | 16.11   | Multimedia Extensions                            | 339   |

|    | 16.12   | Debugging Instructions                           | 340   |

|    | 16.12.1 | Instruction Notation Conventions                 | 340   |

|    |         |                                                  |       |

| Ch | apter   | 17 CPU Instruction Set                           | 345   |

|    | 17.1    | Introduction                                     | 345   |

|    | 17.2    | Functional Instruction Groups                    | 345   |

|    | 17.2.1  | Load and Store Instructions                      | 346   |

|    | 17.2.2  | Computational Instructions                       | 348   |

|    | 17.2.3  | Jump and Branch Instructions                     | 353   |

|    | 17.2.4  | Miscellaneous Instructions                       | 354   |

|    | 17.3    | System Control Coprocessor (CP0) Instructions    | 355   |

|    | 17.4    | CPU Instructions                                 | 356   |

|    | 17.5    | CPU Instruction Opcode Bit Encoding              | 565   |

|    |         |                                                  |       |

| Ch | apter   | 18 Floating-Point Unit Instruction Set           | . 569 |

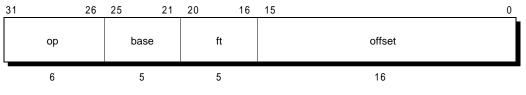

|    | 18.1    | Instruction Formats                              | 569   |

|    | 18.1.1  | Floating-Point Loads, Stores, and Transfers      | 572   |

|    | 18.1.2  | Floating-Point Operations                        | 572   |

|    | 18.2    | Floating-Point Computational Instructions        | 575   |

|    | 18.3    | FPU Instructions                                 | 578   |

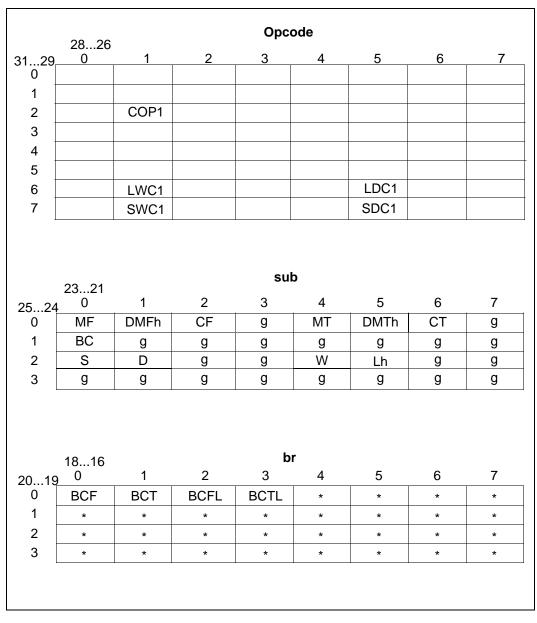

|    | 18.4    | FPU Instruction Opcode Bit Encoding              | 674   |

|    |         |                                                  |       |

| Chapter | 19 Multimedia Instruction Set                          | 677 |

|---------|--------------------------------------------------------|-----|

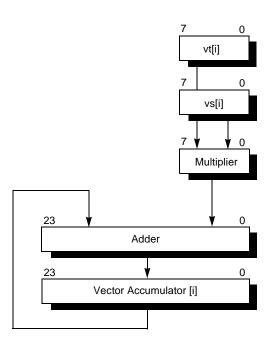

| 19.1    | Multimedia Extensions                                  | 677 |

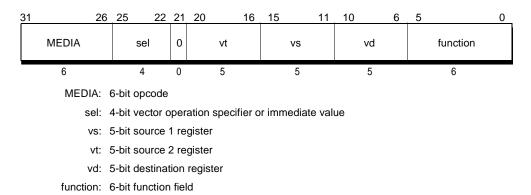

| 19.2    | Multimedia Instruction Format                          | 681 |

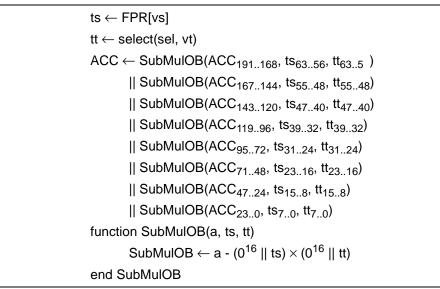

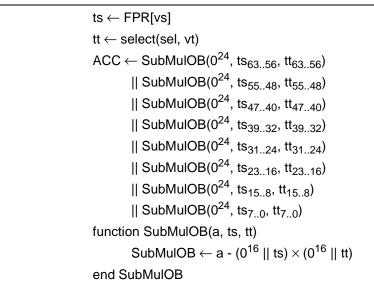

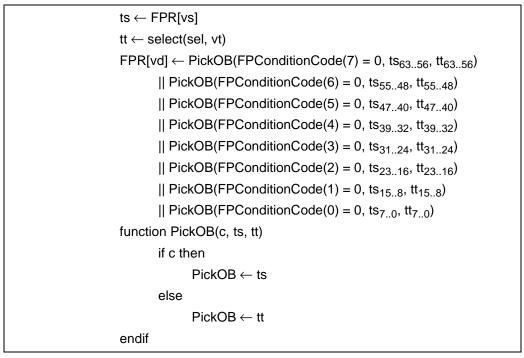

| 19.3    | Multimedia Instructions                                | 682 |

| 19.4    | Multimedia Instruction Opcode Bit Encoding             | 735 |

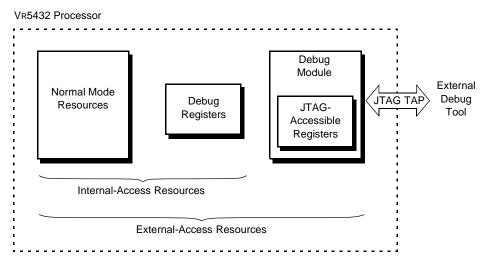

| Chapter | 20 Debug and Test Features                             | 737 |

| 20.1    | Overview                                               | 738 |

| 20.2    | Definition of Terms                                    | 739 |

| 20.3    | Debug Mode                                             | 742 |

| 20.4    | Internal Access                                        | 743 |

| 20.4.1  | Debug Instructions                                     | 744 |

| 20.4.2  | Debug Registers                                        | 745 |

| 20.5    | External Access                                        | 759 |

| 20.5.1  | JTAG Port Signals                                      | 760 |

| 20.5.2  | JTAG-Accessible Registers                              | 766 |

| 20.5.3  | N-Wire Monitor Data Download Example                   |     |

| 20.5.4  | N-Trace Packets                                        | 780 |

| Appendi | x A Subblock Data Retrieval Order                      | 787 |

| Appendi | x B Comparing the Vr4300, Vr5000 and Vr5432 Processors | 791 |

| Appendi | x C PLL Analog Power Filtering                         | 795 |

| Appendi | x D Instruction Hazards                                | 797 |

| Index   |                                                        |     |

## Preface

|                 | The VR5432 <sup>™</sup> microprocessor is an NEC VR Series <sup>™</sup> RIS (reduced instruction set computer) microprocessor that imp the high-performance 64-bit MIPS <sup>®</sup> IV architecture. This n describes the architecture and hardware functions of the VR microprocessor. |                                                                                                                                                                                                                        |                                     |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|--|

| Legend          | Data significance:<br>Active-high signal name:<br>Active-low signal name:<br>Numeric representation:                                                                                                                                                                                     | Higher on left an<br>XXX<br>XXX*<br>binary XXXX<br>decimal XXX<br>hexadecimal 0                                                                                                                                        | X                                   |  |  |  |  |  |

|                 | Prefixes representing an ex                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                        |                                     |  |  |  |  |  |

|                 | capacity):                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                        |                                     |  |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                          | K (kilo)<br>M (mega)                                                                                                                                                                                                   | $2^{10} = 1024$                     |  |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                          | M (mega)                                                                                                                                                                                                               | $2^{20} = 1024^2$                   |  |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                          | G (giga)                                                                                                                                                                                                               | $2^{30} = 1024^3$ $2^{40} = 1024^4$ |  |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                          | T (tera)                                                                                                                                                                                                               | $2^{10} = 1024^{10}$                |  |  |  |  |  |

| Manual Overview | containing processor archi                                                                                                                                                                                                                                                               | The manual is divided into two volumes. Volume 1 is the user mar<br>ontaining processor architectural and functional information an<br>instructions. Volume 2 contains the instruction set information a<br>ppendixes. |                                     |  |  |  |  |  |

|                 | Volume 1 (U13751E)                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                        |                                     |  |  |  |  |  |

|                 | <ul> <li>Chapter 1: Introduction provides an overview of the device features, CPU, Floating-Point Unit (FPU), and pipeline.</li> <li>Chapter 2: Signal Descriptions discusses the pin configurat functions of the VR5432 processor signals.</li> </ul>                                   |                                                                                                                                                                                                                        |                                     |  |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                        |                                     |  |  |  |  |  |

|                 | Chapter 3: Pipeline description stages, delays, and interloc                                                                                                                                                                                                                             |                                                                                                                                                                                                                        |                                     |  |  |  |  |  |

**Chapter 4: Memory Management Unit** discusses the processor's virtual and physical address spaces, the virtual-to-physical address translation, the translation lookaside buffer (TLB) process, and the system control coprocessor registers that provide the software interface to the TLB.

**Chapter 5: Cache Organization and Operation** describes the cache memory's place in the VR5432 memory configuration and individual cache organization.

**Chapter 6: CPU Exceptions** describes the processor's exception types, registers, vector offsets, processing handling, and interrupts.

**Chapter 7: Floating-Point Unit** describes the FPU coprocessor, including the programming model, instruction set and formats, and the pipeline.

**Chapter 8: Floating-Point Exceptions** discusses FPU exception types, exception trap processing, exception flags, saving and restoring states when handling an exception, and trap handlers for IEEE Standard 754 exceptions.

**Chapter 9: Bus Interface** describes how the processor accesses the external resources needed to satisfy cache misses and uncached operations, while permitting an external agent access to some of the processor's internal resources.

**Chapter 10: System Interface Transactions (Native Mode)** describes processor and external requests in the native system interface protocol of the VR5432 processor.

**Chapter 11: System Interface Protocols (Native Mode)** contains a cycle-by-cycle description of the system interface protocols for each type of processor and external request in the native protocol of the VR5432 processor.

**Chapter 12: System Interface Transactions (R43K Mode)** This section describes processor and external requests as they occur in R43K (VR4300 compatibility) mode.

**Chapter 13: System Interface Protocols (R43K Mode)** contains a cycle-by-cycle description of the system interface protocols for each type of processor and external request in R43K mode.

**Chapter 14: Initialization Interface** describes the processor reset and initialization signals.

**Chapter 15: Clock Interface** describes the basic system clocks, SysClock and PClock, and Phase-Locked Loop (PLL) and Bypass PLL modes.

#### Volume 2 (U15397E)

**Chapter 16: Instruction Set Overview** discusses the general attributes of the CPU, FPU, multimedia, and debugging instructions of the MIPS IV instruction set architecture (ISA) utilized by the VR5432 processor.

**Chapter 17: CPU Instruction Set** describes the details of the CPU instructions.

**Chapter 18: Floating-Point Unit Instruction Set** describes the details of the FPU instructions.

**Chapter 19: Multimedia Instruction Set** describes the details of the multimedia instructions.

**Chapter 20: Debug and Test Features** describes the VR5432 processor's debug and test functions, Debug mode, and debug instructions.

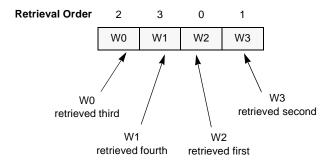

**Appendix A: Sublock Order** describes how a block of data elements (bytes, halfwords, words, or doublewords) can be retrieved from storage in sequential or nonsequential (sub-block) order.

Appendix B: Comparing the VR4300, VR5000, and VR5432 Processors delineates each processor's attributes.

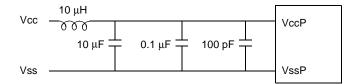

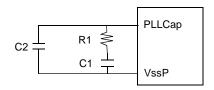

**Appendix C: PLL Analog Power Filtering** illustrates the phaselocked loop circuit configuration.

**Appendix D: Instruction Hazards** identifies the VR5432 instruction hazards that occur with certain instruction and event combinations (such as pipeline delays, cache misses, interrupts, and exceptions).

#### **Related Documents**

See also the following documents. The related documents indicated here may include preliminary versions. However, preliminary versions are not marked as such.

| Product | Data Sheet | User's Manual         |                 |  |  |  |  |

|---------|------------|-----------------------|-----------------|--|--|--|--|

| Troduct | Data Sheet | Hardware Architecture | Instruction Set |  |  |  |  |

| Vr5432  | U13504E    | U13751E               | U15397E         |  |  |  |  |

| Vr5000  | U12031E    | U11761E               | U12754E         |  |  |  |  |

| Vr10000 | U12703E    | U10278E               | U12754E         |  |  |  |  |

## Instruction Set Overview

## 16

This chapter provides an overview of the instruction set architecture (ISA) utilized by the VR5432 processor. For detailed information on each instruction type, refer to the following chapters.

- Chapter 17, CPU Instruction Set, on page 3

- Chapter 18, Floating-Point Unit Instruction Set, on page 569

- Chapter 19, Multimedia Instruction Set, on page 677

- Chapter 20, Debug and Test Features, on page 737

## 16.1 **Instruction Set Architecture**

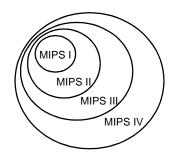

The VR5432 processor executes the MIPS IV instruction set (a superset of the MIPS III instruction set) plus instructions added by NEC specifically for VR5432 implementation. As Figure 16-1 illustrates, each new architecture level (or version) includes the former levels. Therefore, a processor implementing MIPS IV can also run MIPS I, MIPS II, or MIPS I II binary programs without change.

Figure 16-1 MIPS Architecture Extensions

The MIPS IV instruction set for the  $V_R5432$  processor utilizes the following instruction types.

- CPU instructions

- Floating-point instructions

- Multimedia instruction

- Test and debug instructions

In earlier MIPS architectures, coprocessor instructions were implementation dependent. In the MIPS IV architecture, the Coprocessor 3 instruction formats have been used for extensions to the floating-point instruction set. In the VR5432 implementation, the Coprocessor 2 instruction formats have been used for implementation-specific instruction set extensions. The new MIPS IV, VR5432 processor-specific instructions are summarized and briefly explained in Section 16.8.

## 16.2 **Instruction Formats**

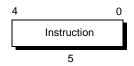

Each instruction consists of a single 32-bit word aligned on a word boundary. There are three instruction formats—immediate (I-type), jump (J-type), and Register (R-type). The use of a small number of instruction formats simplifies instruction decoding, allowing the compiler to synthesize more complicated (and less frequently used) operations and addressing modes from these three formats. See the subsequent instruction chapters for details on the formats of each instruction type.

## 16.3 Load and Store Instructions

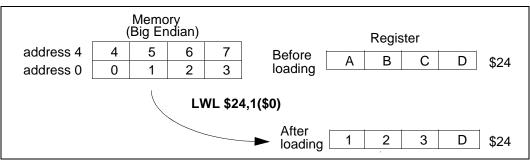

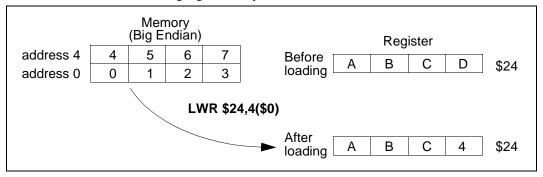

Load and Store instructions are immediate (I-type) instructions that transfer data between the memory system and the general-purpose register sets in the CPU and coprocessors. There are separate instructions for different purposes: transferring variously sized fields, treating loaded data as signed or unsigned integers, accessing unaligned fields, selecting the addressing mode, and providing atomic memory updates (read-modify-write cycles).

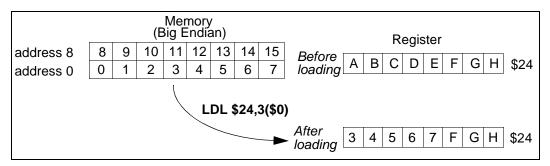

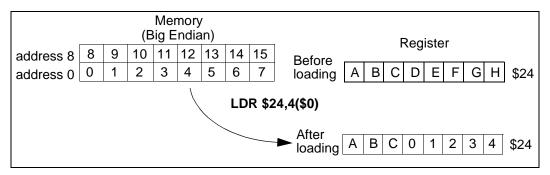

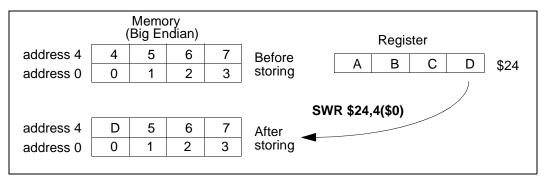

Regardless of byte ordering (big- or little-endian), the address of a halfword, word, or doubleword is the smallest byte address among the bytes forming the object. For big-endian ordering, this is the most-significant byte; for little-endian ordering, this is the least-significant byte.

Except for the few specialized instructions listed in Table 17-2, Load and Store instructions must access naturally aligned objects. An attempt to load or store an object at an address that is not an even multiple of the size of the object will cause an Address Error exception.

Load and Store operations have been added in each revision of the architecture:

MIPS II

- 64-bit coprocessor transfers

- Atomic update

#### MIPS III

- 64-bit CPU transfer

- Unsigned word load for the CPU

MIPS IV: Register + r egister addressing mode for the FPU

Table 16-1 and Table 16-2 tabulate the supported Load and Store operations and indicate the MIPS architecture level at which each operation was first supported. The instructions themselves are listed in the following sections.

|                                      |                                    | CPU | Coprocessor<br>(except 0) |       |    |  |

|--------------------------------------|------------------------------------|-----|---------------------------|-------|----|--|

| Data Size                            | Load Load<br>Signed Unsigned Store |     | Load                      | Store |    |  |

| Byte                                 | Ι                                  | Ι   | Ι                         |       |    |  |

| Halfword                             | Ι                                  | Ι   | Ι                         |       |    |  |

| Word                                 | Ι                                  | III | Ι                         | Ι     | Ι  |  |

| Doubleword                           | III                                |     | III                       | II    | II |  |

| Unaligned word                       | Ι                                  |     | Ι                         |       |    |  |

| Unaligned doubleword                 | III                                |     | III                       |       |    |  |

| Linked word<br>(atomic modify)       | II                                 |     | II                        |       |    |  |

| Linked doubleword<br>(atomic modify) | III                                |     | III                       |       |    |  |

Table 16-1

Load/Store Operations Using Register + Offset Addressing Mode

Table 16-2

Load/Store Operations Using Register + Register Addressing Mode

|            | Floating-Point Coprocessor Only |       |  |  |  |  |  |

|------------|---------------------------------|-------|--|--|--|--|--|

| Data Size  | Load                            | Store |  |  |  |  |  |

| Word       | IV                              | IV    |  |  |  |  |  |

| Doubleword | IV                              | IV    |  |  |  |  |  |

### 16.3.1 Delayed Load Instructions

The MIPS I architecture defines delayed loads; an instruction scheduling restriction requires that an instruction immediately following a load into register Rn cannot use Rn as a source register. The time between the Load instruction and the time the data is available is the "load delay slot." If no useful instruction can be put into the load delay slot, then a null operation (assembler mnemonic NOP) must be inserted.

In MIPS II, this instruction scheduling restriction is removed. Programs will execute correctly when the loaded data is used by the instruction following the load, but this may require extra read cycles. Most processors cannot actually load data quickly enough for immediate use and the processor will be forced to wait until the data is available. Scheduling load delay slots can be desirable, both for performance and compatibility with earlier VR Series processors. However, the scheduling of load delay slots is not required for correct operation of the processor.

## 16.3.2 **Defining Access Types**

Access type indicates the size of a VR5432 processor data item to be loaded or stored, as set by the Load or Store instruction opcode.

Regardless of access type or byte ordering (endianness), the address given specifies the low-order byte in the addressed field. For a big-endian configuration, the low-order byte is the most-significant byte; for a little-endian configuration, the low-order byte is the least-significant byte.

The access type, together with the three low-order bits of the address, define the bytes accessed within the addressed doubleword (shown in Table 16-3). Only the combinations shown in Table 16-3 are permissible; other combinations cause Address Error exceptions.

| Access Type Low-Order |                       |   |    | Bytes Accessed      |          |   |    |   |   |                        |   |   |   |   |      |   |   |   |   |  |

|-----------------------|-----------------------|---|----|---------------------|----------|---|----|---|---|------------------------|---|---|---|---|------|---|---|---|---|--|

| Mnemonic              | Mnemonic Address Dits |   | (6 | Big Endian<br>(630) |          |   |    |   |   | Little Endian<br>(630) |   |   |   |   |      |   |   |   |   |  |

| (Value)               | 2                     | 1 | 0  |                     | <b>J</b> |   | By |   |   |                        |   |   |   |   | Byte |   |   |   |   |  |

| Doubleword (7)        | 0                     | 0 | 0  | 0                   | 1        | 2 | 3  | 4 | 5 | 6                      | 7 | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |  |

| Septibyte (6)         | 0                     | 0 | 0  | 0                   | 1        | 2 | 3  | 4 | 5 | 6                      |   |   | 6 | 5 | 4    | 3 | 2 | 1 | 0 |  |

| Septioyte (0)         | 0                     | 0 | 1  |                     | 1        | 2 | 3  | 4 | 5 | 6                      | 7 | 7 | 6 | 5 | 4    | 3 | 2 | 1 |   |  |

| Sextibyte (5)         | 0                     | 0 | 0  | 0                   | 1        | 2 | 3  | 4 | 5 |                        |   |   |   | 5 | 4    | 3 | 2 | 1 | 0 |  |

| Sexubyle (5)          | 0                     | 1 | 0  |                     |          | 2 | 3  | 4 | 5 | 6                      | 7 | 7 | 6 | 5 | 4    | 3 | 2 |   |   |  |

| Quintibyte (4)        | 0                     | 0 | 0  | 0                   | 1        | 2 | 3  | 4 |   |                        |   |   |   |   | 4    | 3 | 2 | 1 | 0 |  |

| Quintibyte (1)        | 0                     | 1 | 1  |                     |          |   | 3  | 4 | 5 | 6                      | 7 | 7 | 6 | 5 | 4    | 3 |   |   |   |  |

| Word (3)              | 0                     | 0 | 0  | 0                   | 1        | 2 | 3  |   |   |                        |   |   |   |   |      | 3 | 2 | 1 | 0 |  |

|                       | 1                     | 0 | 0  |                     |          |   |    | 4 | 5 | 6                      | 7 | 7 | 6 | 5 | 4    |   |   |   |   |  |

|                       | 0                     | 0 | 0  | 0                   | 1        | 2 |    |   |   |                        |   |   |   |   |      |   | 2 | 1 | 0 |  |

| Triplebyte (2)        | 0                     | 0 | 1  |                     | 1        | 2 | 3  |   |   |                        |   |   |   |   |      | 3 | 2 | 1 |   |  |

|                       | 1                     | 0 | 0  |                     |          |   |    | 4 | 5 | 6                      |   |   | 6 | 5 | 4    |   |   |   |   |  |

|                       | 1                     | 0 | 1  |                     |          |   |    |   | 5 | 6                      | 7 | 7 | 6 | 5 |      |   |   |   |   |  |

|                       | 0                     | 0 | 0  | 0                   | 1        |   |    |   |   |                        |   |   |   |   |      |   |   | 1 | 0 |  |

| Halfword (1)          | 0                     | 1 | 0  |                     |          | 2 | 3  |   |   |                        |   |   |   |   |      | 3 | 2 |   |   |  |

| (-)                   | 1                     | 0 | 0  |                     |          |   |    | 4 | 5 |                        |   |   |   | 5 | 4    |   |   |   |   |  |

|                       | 1                     | 1 | 0  |                     |          |   |    |   |   | 6                      | 7 | 7 | 6 |   |      |   |   |   |   |  |

|                       | 0                     | 0 | 0  | 0                   |          |   |    |   |   |                        |   |   |   |   |      |   |   |   | 0 |  |

|                       | 0                     | 0 | 1  |                     | 1        |   |    |   |   |                        |   |   |   |   |      |   |   | 1 |   |  |

|                       | 0                     | 1 | 0  |                     |          | 2 |    |   |   |                        |   |   |   |   |      |   | 2 |   |   |  |

| Byte (0)              | 0                     | 1 | 1  |                     |          |   | 3  |   |   |                        |   |   |   |   |      | 3 |   |   |   |  |

|                       | 1                     | 0 | 0  |                     |          |   |    | 4 |   |                        |   |   |   |   | 4    |   |   |   |   |  |

|                       | 1                     | 0 | 1  |                     |          |   |    |   | 5 |                        |   |   |   | 5 |      |   |   |   |   |  |

|                       | 1                     | 1 | 0  |                     |          |   |    |   |   | 6                      |   |   | 6 |   |      |   |   |   |   |  |

|                       | 1                     | 1 | 1  |                     |          |   |    |   |   |                        | 7 | 7 |   |   |      |   |   |   |   |  |

Table 16-3 Byte Access within a Doublew or

| Access Type | SysCmd (2:0) | Meaning           |

|-------------|--------------|-------------------|

| Doubleword  | 7            | 8 bytes (64 bits) |

| Septibyte   | 6            | 7 bytes (56 bits) |

| Sextibyte   | 5            | 6 bytes (48 bits) |

| Quintibyte  | 4            | 5 bytes (40 bits) |

| Word        | 3            | 4 bytes (32 bits) |

| Triplebyte  | 2            | 3 bytes (24 bits) |

| Halfword    | 1            | 2 bytes (16 bits) |

| Byte        | 0            | 1 byte (8 bits)   |

Table 16-4 Access Type Specifications for Load/Store Instruction

## 16.4 **Computational Instructions**

Computational instructions can be in either register (R-type) format, in which both operands are registers, or immediate (I-type) format, in which one operand is a 16bit immediate.

Two's-complement arithmetic is performed on integers represented in two'scomplement notation. There are signed versions of add, subtract, multiply, and divide operations. There are add and subtract operations, called "unsigned," that are actually modulo arithmetic without overflow detection. There are unsigned versions of multiply and divide. There is a full complement of shift and logical operations.

MIPS I provides 32-bit integers and 32-bit arithmetic. MI PSIII adds 64-bit integers and provides separate Arithmetic and Shift instructions for 64-bit operands. Logical operations are not sensitive to the width of the register.

Computational instructions perform the following operations on register values:

- Arithmeti

- Logical

- Rotate

- Shift

- Multipl

- Divide

- Multiply-accumulat

- Parallel operations on packed bytes

These operations fit in the following six categories of computational instructions:

- ALU immediate instruction

- Three-operand register-type instructions

- Rotate and Shift instructions

- Multiply and Divide instructions

- Multiply-accumulate instructions

- Packed byte instructions

### **64-Bit Operations**

The VR5432 microprocessor has a 64-bit architecture that supports 32-bit operands. These operands must be sign extended. Opcodes are available for 32-bit operands for all of the basic arithmetic and logical instructions, such as: ADD, ADDU, SUB, SUBU, ADDI, SLL, SRA, and SLLV. Operations that don't use sign-extended 32-bit values correctly are unpredictable. In addition, 32-bit data is stored sign extended in a 64-bit register.

## 16.5 Jump and Branch Instructions

All Jump and Branch instructions have a delay slot of exactly one instruction. That is, the instruction immediately following a Jump or Branch instruction (the instruction occupying the delay slot) is executed while the target instruction is being fetched from the cache. A Jump or Branch instruction cannot be used in a delay slot; however, if they are used, the error is not detected and the results of such an operation are undefined.

If an exception or interrupt prevents the completion of the instruction while it is in a delay slot, the hardware sets a virtual address to the EPC register at the point of the Jump or Branch instruction that precedes it. When exception or interrupt processing is complete and the program is restored, both the Jump and Branch instruction and the instruction in the delay slot are re-executed.

Because Jump and Branch instructions may be re-executed after exception or interrupt processing, register 31 (the register in which the link address is stored) should not be used as a source register in Jump, Link/Branch, and Link instructions.

Because instructions must be word-aligned, a Jump Register or Jump and Link Register instruction must use a register that contains an address where the loworder two bits are zero. If these low-order two bits are not zero, an Address Error Exception instruction at the Jump destination is fetched.

#### 16.5.1 Jump Instructions

Subroutine calls in high-level languages are usually implemented with Jump or Jump and Link instructions, both of which are J-type instructions. In J-type format, the 26-bit target address is shifted left 2 bits and concatenated with the high-order 4 bits of the current program counter to form an absolute address.

Returns, dispatches, and large cross-page jumps are usually implemented with the Jump Register or Jump and Link Register instructions. Both are R-type instructions that take the 64-bit byte address contained in one of the general-purpose registers.

#### 16.5.2 Branch Instructions

All Branch instruction target addresses are calculated by adding the address of the instruction in the delay slot to the 16-bit offset (shifted left by 2 bits and sign-extended to 64 bits). All branches occur with a delay of one instruction.

If a conditional Branch Likely instruction is not taken, the instruction in the delay slot is nullified (i.e., discarded without affecting any data).

## 16.6 Special Instructions

Special instructions allow the software to initiate traps both conditionally and unconditionally. These instructions can cause System Call (SysCall), Breakpoint (Break), and Trap (Trap) conditions in the processor. SysCall and Break are unconditional, while Trap can specify a condition such as a Branch instruction. The Synchronize (Sync) instruction allows the software to ensure that all pending operations are complete. In the VR5432 processor implementation, the Sync instruction is executed as an NOP.

## 16.7 **Coprocessor Instructions**

Coprocessors are alternate execution units with register files separate from the CPU. The MIPS architecture provides an abstraction for up to 4 coprocessor units, numbered 0 to 3. Each architecture level defines some of these coprocessors, as shown in Table 16-5. Coprocessor 0 is always used for system control and Coprocessor 1 is used for the floating-point unit. Other coprocessors are architecturally valid, but do not have a reserved use. Some coprocessors are not defined and their opcodes are either reserved or used for other purposes.

|             | MIPS Architecture Level |              |              |                |  |  |  |  |  |

|-------------|-------------------------|--------------|--------------|----------------|--|--|--|--|--|

| Coprocessor | Ι                       | Π            | III          | IV             |  |  |  |  |  |

| 0           | Sys. control            | Sys. control | Sys. control | Sys. control   |  |  |  |  |  |

| 1           | FPU                     | FP           | FP           | FPU            |  |  |  |  |  |

| 2           | Unused                  | Unused       | Unused       | Unused         |  |  |  |  |  |

| 3           | Unused                  | Unused       | Not defined  | FPU<br>(COP1X) |  |  |  |  |  |

Table 16-5 Coprocessor Definition and Use in the MIPS Architect u r

The coprocessors may have two register sets, Coprocessor general-purpose registers and coprocessor control registers, with each set containing up to 32 registers. Coprocessor computational instructions may alter registers in either set.

System control for all MIPS processors is implemented as Coproce ssor0 (CP0), the system control coprocessor. It provides the processor control, memory management, and exception handling functions. The CP0 instructions are specific to each CPU and are documented with the CPU-specific information.

If a system includes a floating-point unit, it is implemented as coproces sor1 (CP1). In MIPS I V, the FPU also uses the computation opcode space for Coprocessor unit 3, renamed COP1X. The FPU instructions are documented in Chapter 18.

The coprocessor instructions are divided into two main groups:

- Load and Store instructions that are reserved in the main opcode space

- Coprocessor-specific operations that are defined entirely by the coprocessor

#### 16.7.1 Coprocessor Load and Store

Load and Store instructions are not defined for CP0; the Move to/from Coprocessor instructions provide the only way to write and read the CP0 registers.

#### 16.7.2 **Coprocessor Operations**

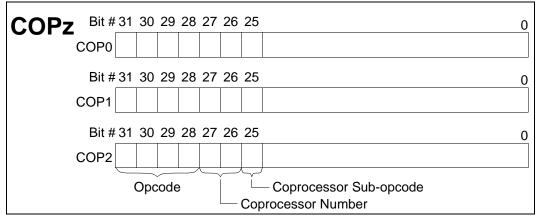

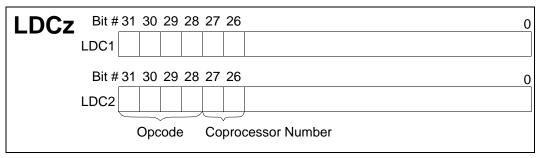

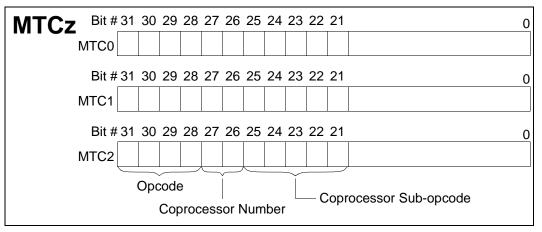

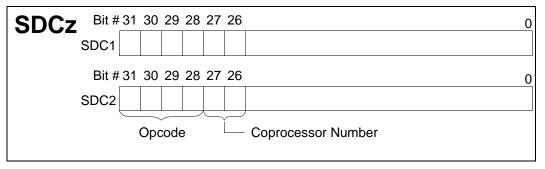

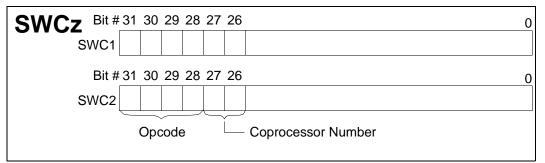

Up to four coprocessors and their instructions are shown generically for coprocessor z. Within the operation main opcode, the coprocessor has further coprocessor-specific instructions encoded.

| Mnemonic | Description             | Defined in<br>MIPS |

|----------|-------------------------|--------------------|

| COPz     | Coprocessor z Operation | Ι                  |

Table 16-6 Coprocessor Operation Instruction

## 16.8 Implementation-Specific Instructions

#### 16.8.1 **Overview**

The MIPS IV instructions added by NEC for the  $V_R5432$  processor enable the MIPS architecture to compete in the high-end numeric processing market, which has traditionally been dominated by vector architectures.

Compound Multiply-Add instructions are included, taking advantage of the fact that most floating-point computations use the chained multiply-add paradigm. The intermediate multiply result is rounded before the addition is performed.

A register + register addressing indexed mode for floating-point loads and stores eliminates the extra integer required in many array accesses. However, issuing a register + register load causes a one-cycle stall in the pipeline, which makes it useful only for compatibility with other MIPS IV implementations. Register + register indexed addressing for integer memory operations is not supported.

A set of four conditional move operators allows floating-point arithmetic IF statements to be represented without branches. THEN and ELSE clauses are computed unconditionally and the results are placed in a temporary register. Conditional move operators then transfer the temporary results to their true register. Conditional moves must be able to test both integer and floating-point conditions in order to supply the full range of IF statements. Integer tests are performed by comparing a general-purpose register against a zero value.

Because floating-point conditional moves test the floating-point condition codes, the  $V_{R}5432$  processor provides eight condition codes to give the compiler increased flexibility in scheduling the comparison and the conditional moves.

Table 16-7 lists the new instructions that complete the MIPS IV instruction set; these instructions are described in Section 16.8.2 on page 333.

| Instruction     | Definition                                    |

|-----------------|-----------------------------------------------|

| BC1F            | Branch on FP condition code false             |

| BC1T            | Branch on FP condition code true              |

| BC1FL           | Branch on FP condition code false likely      |

| BC1TL           | Branch on FP condition code true likely       |

| C.cond.fmt (cc) | Floating-point compare                        |

| LDXC1           | Load doubleword indexed to COP1               |

| LWXC1           | Load word indexed to COP1                     |

| MADD.fmt        | Floating-point multiply-add                   |

| MOVF            | Move conditional on FP condition code false   |

| MOVN            | Move on register not equal to zero            |

| MOVT            | Move conditional on FP condition code true    |

| MOVZ            | Move on register equal to zero                |

| MOVF.fmt        | FP move conditional on condition code false   |

| MOVN.fmt        | FP move on register not equal to zero         |

| MOVT.fmt        | FP move conditional on condition code true    |

| MOVZ.fmt        | FP move conditional on register equal to zero |

| MSUB.fmt        | Floating-point multiply-subtract              |

| NMADD.fmt       | Floating-point negative multiply-add          |

| NMSUB.fmt       | Floating-point negative multiply-subtract     |

| PREFX           | Prefetch indexed — register + register        |

| PREF            | Prefetch — register + offset                  |

| RECIP.fmt       | Reciprocal                                    |

| RSQRT.fmt       | Reciprocal square root                        |

| SDXC1           | Store doubleword indexed from COP1            |

| SWXC1           | Store word indexed from COP1                  |

Table 16-7 MIPS IV Instruction Additions

## 16.8.2 Implementation-Specific Instruction Descriptions

This section describes the new instructions listed in Table 16-7.

16.8.2.1 Branch on floating-point Coprocessor instructions

BC1T: Branch on FP condition True

BC1F: Branch on FP condition False

BC1TL: Branch on FP condition True Likely

BC1FL: Branch on FP condition False Likely

The four Branch instructions are upwardly compatible extensions of the Branch on floating-point coprocessor instructions of the MIPS instruction set. The BC1T and BC1F instructions are extensions of MIPS I. BC1TL and BC1FL are extensions of MIPS III. These instructions test one of eight floating-point condition codes. This encoding is upwardly compatible with previous MIPS architectures.

The branch target address is computed from the sum of the address of the instruction in the delay slot and the 16-bit offset, shifted left two bits and sign extended to 64 bits. If the contents of the floating-point condition code specified in the instruction are equal to the test value, the target address is branched to with a delay of one instruction. If the conditional branch is not taken and the nullify delay bit in the instruction is set, the instruction in the branch delay slot is nullified.

16.8.2.2 Floating-point Compare instructions

C.cond.fmt: Compares the contents of two FPU registers

The contents of the two FPU source registers specified in the instruction are interpreted and arithmetically compared. A result is determined based on the comparison and the conditions specified in the instruction.

### 16.8.2.3 Indexed floating-point Load instructions

LWXC1: Load word indexed to Coprocessor 1

LDXC1: Load doubleword indexed to Coprocessor 1

The two indexed floating-point Load instructions are exclusive to the MIPS IV instruction set and transfer floating-point data types from memory to the floating-point registers using the register + register addressing mode. There are no indexed loads to general-purpose registers. The contents of the general-purpose register specified by the base are added to the contents of the general-purpose register specified by the index to form a virtual address. The contents of the word or doubleword specified by the effective address are loaded into the floating-point register specified in the instruction.

The region bits (63:62) of the effective address must be supplied by the base. If the addition alters these bits, an Address Error exception occurs. Also, if the address is not aligned, an Address Error exception occurs.

#### 16.8.2.4 Integer conditional Move instructions

MOVT: Move conditional on condition code True

MOVF: Move conditional on condition code False

MOVN: Move conditional on register not equal to zero

MOVZ: Move conditional on register equal to zero

The four-integer Move instructions are exclusive to the MIPS IV instruction set and are used to test a condition code or a general-purpose register and then conditionally perform an integer move. The value of the floating-point condition code specified in the instruction by the 3-bit condition code specifier, or the value of the register indicated by the 5-bit general-purpose register specifier, is compared to zero. If the result indicates that the move should be performed, the contents of the specified source register are copied into the specified destination register.

| 16.8.2.5 | Floating-point Multiply-Add instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | MADD: Floating-point Multiply-Add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          | MSUB: Floating-point Multiply-Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          | NMADD: Floating-point Negative Multiply-Add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | NMSUB: Floating-point Negative Multiply-Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          | These four instructions are exclusive to the MIPS IV instruction set and accomplish two floating-point operations with one instruction. Each of these four instructions performs intermediate rounding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16.8.2.6 | Floating-point conditional Move instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          | MOVT.fmt: Floating-point conditional move on condition code True                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          | MOVF.fmt: Floating-point conditional move on condition code False                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          | MOVN.fmt: Floating-point conditional move on register not equal to zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

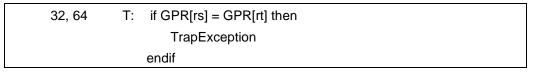

|          | MOVZ.fmt: Floating-point conditional move on register equal to zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |