**User's Manual**

# VRC4172™

# **Companion Chip for VR4121™**

μ**PD31172**

Document No. U14386EJ3V0UM00 (3rd edition) Date Published September 2000 N CP(K)

© NEC Corporation 2000 Printed in Japan [MEMO]

#### **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### **②** HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

VR4121 and VRc4172 are trademarks of NEC Corporation.

Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

- The information in this document is current as of July, 2000. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

(1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

(2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

NEC Electronics Inc. (U.S.) Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

NEC Electronics (UK) Ltd.

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99 NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

NEC Electronics (France) S.A. Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

NEC Electronics (France) S.A. Madrid Office Madrid, Spain Tel: 91-504-2787 Fax: 91-504-2860

NEC Electronics (Germany) GmbH Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd.

United Square, Singapore Tel: 65-253-8311 Fax: 65-250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP Brasil Tel: 55-11-6462-6810 Fax: 55-11-6462-6829

J00.7

# **Major Revisions in This Edition**

| Page       | Description                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------|

| Throughout | $\mu PD31172~$ Change of development status (under development $\rightarrow$ development completed) |

| р. 48      | Modification of description in 3.2.2 (4) Revision ID register (offset address: 0x08)                |

| p. 124     | Modification of description in 11.2.2 Command register (offset address: 0x04)                       |

| p. 154     | Modification of description in 11.3.20 HcRhDescriptorA (offset address: 0x48)                       |

| p. 176     | Addition of 16.4 Preserving SDRAM Data                                                              |

The mark  $\star$  shows major revised points.

#### INTRODUCTION

| This manual is intended to give users an understanding of the architecture of the                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VRc4172, using the following organization.                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>This manual covers the following main contents.</li> <li>Overview</li> <li>Pin functions</li> <li>Address map</li> <li>Internal peripheral functions</li> </ul>                                                                                                                                                                                                                                                       |

| It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.<br>To learn about the functions of the V <sub>RC</sub> 4172:<br>$\rightarrow$ Read the manual in the order listed in Contents.<br>To learn about the electrical specifications of the V <sub>RC</sub> 4172:<br>$\rightarrow$ Refer to the Data Sheet (published separately). |

|                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Conventions | Data significance:                   | Higher digits on the left and lower digits on the right |

|-------------|--------------------------------------|---------------------------------------------------------|

|             | Active low representation:           | XXX# (# after pin or signal name)                       |

|             | Note:                                | Footnote for item marked with Note in the text          |

|             | Caution:                             | Information requiring particular attention              |

|             | Remark:                              | Supplementary information                               |

|             | Numerical representation:            | Binary or decimal XXXX                                  |

|             |                                      | Hexadecimal 0xXXXX                                      |

|             | Prefixes indicating powers of 2 (add | ess space, memory capacity):                            |

|             |                                      | K (Kilo) 2 <sup>10</sup> = 1024                         |

|             |                                      | M (Mega) $2^{20} = 1024^2$                              |

|             |                                      | G (Giga) $2^{30} = 1024^3$                              |

|             |                                      | T (Tera) 2 <sup>40</sup> = 1024 <sup>4</sup>            |

|             |                                      | P (Peta) $2^{50} = 1024^{5}$                            |

|             |                                      | E (Exa) $2^{60} = 1024^{6}$                             |

|             |                                      |                                                         |

**Related Documents** Please read the following related documents in combination with this manual.

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

• Device-related documents

| Document Name                     | Document No. |

|-----------------------------------|--------------|

| VRc4172 User's Manual             | This manual  |

| μPD31172 (VRc4172) Data Sheet     | U14388E      |

| V <sub>R</sub> 4121 User's Manual | U13569E      |

| μPD30121 (VR4121) Data Sheet      | U14691E      |

- USB-related documents (These documents are not handled by NEC.)

- OPEN HCI Specification Release 1.0

- PCI Local bus Specification Revision 2.1

#### CONTENTS

| CHAPTI     | ER 1 (               | OVERVIEW                                          |    |

|------------|----------------------|---------------------------------------------------|----|

| 1.1        | Featu                | res                                               | 17 |

| 1.2        | Ordering Information |                                                   |    |

| 1.3        | Vrc41                | 72 Processor                                      |    |

|            | 1.3.1                | Internal block configuration                      | 19 |

|            | 1.3.2                | Registers of each unit                            |    |

|            |                      |                                                   |    |

|            |                      | PIN FUNCTIONS                                     |    |

| 2.1<br>2.2 |                      | onfiguration<br>f Pin Functions                   |    |

| 2.2        | 2.2.1                | System bus interface signals                      |    |

|            | 2.2.1                | USB interface signals                             |    |

|            | 2.2.2                | IEEE1284 interface signals                        |    |

|            | 2.2.3                | RS-232-C interface signals                        |    |

|            | 2.2.4                |                                                   |    |

|            | -                    | PS/2 interface signals                            |    |

|            | 2.2.6                | General-purpose port signal                       |    |

|            | 2.2.7                | General-purpose chip select signal                |    |

|            | 2.2.8                | LCD interface signal                              |    |

|            | 2.2.9                | Clock signals                                     |    |

| 2.3        |                      | atuses                                            |    |

|            | 2.3.1                | Status of pins under specific conditions          |    |

|            | 2.3.2                | External processing of pins and drive performance |    |

|            | 2.3.3                | Recommended connection of unused pins             |    |

| СЦАРТІ     | ED 2 /               | ADDRESS MAP                                       | 20 |

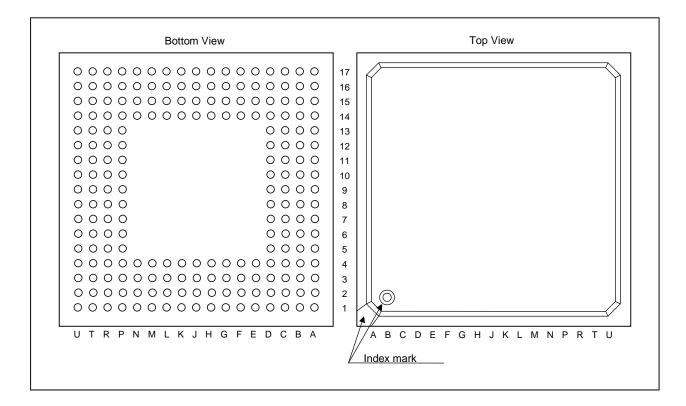

| 3.1        |                      | al I/O Spaces                                     |    |

| 3.2        |                      | aster Window (Memory)                             |    |

| 0.2        | 3.2.1                | PCI configuration cycle                           |    |

|            | 3.2.1                | PCI host controller                               |    |

| 3.3        | 0                    | aster Window (I/O)                                |    |

| 3.3<br>3.4 |                      | lave Window (Memory)                              |    |

| 5.4        | 1010                 |                                                   | J  |

| СНАРТІ     | FR 4 (               | GPIO (GENERAL-PURPOSE I/O PORT)                   | 53 |

| 4.1        |                      | ter Set                                           |    |

|            | 4.1.1                | EXGPDATA0 (0x1500 1080)                           |    |

|            | 4.1.2                | EXGPDIR0 (0x1500 1082)                            |    |

|            | 4.1.3                | EXGPINTEN0 (0x1500 1084)                          |    |

|            | 4.1.4                | EXGPINTST0 (0x1500 1086)                          |    |

|            | 4.1.5                | EXGPINTTYP0 (0x1500 1088)                         |    |

|            | 4.1.6                | EXGPINTLV0L (0x1500 108A)                         |    |

|            | 4.1.7                | EXGPINTLV0H (0x1500 108C)                         |    |

|            | 4.1.8                | EXGPDATA1 (0x1500 1000)                           |    |

|            | 4.1.9                | EXGPDIR1 (0x1500 10C0)                            |    |

|            | 4.1.10               |                                                   |    |

|            | 4.1.11               | EXGPINTST1 (0x1500 10C6)                          |    |

|            |                      |                                                   |    |

|        | 4.1.12 | EXGPINTTYP1 (0x1500 10C8)                                             | 65  |

|--------|--------|-----------------------------------------------------------------------|-----|

|        | 4.1.13 | EXGPINTLV1L (0x1500 10CA)                                             | 66  |

|        |        |                                                                       |     |

| CHAPTE | ER 5 F | PCS (PROGRAMMABLE CHIP SELECT)                                        |     |

| 5.1    | Regist | er Set                                                                | 67  |

|        | 5.1.1  | EXCS compare address registers                                        | 68  |

|        | 5.1.2  | EXCS address mask registers                                           | 70  |

| СНАРТЕ | ER 6 F | PWM CONTROLLER                                                        | 73  |

| 6.1    | Regist | er Set                                                                | 73  |

|        | 6.1.1  | LCDDUTYEN (0x1500 3880)                                               | 74  |

|        | 6.1.2  | LCDFREQ (0x1500 3882)                                                 | 75  |

|        | 6.1.3  | LCDDUTY (0x1500 3884)                                                 | 76  |

| СНАРТЕ | ER 7 F | PMU (POWER MANAGEMENT UNIT)                                           | 77  |

| 7.1    | Regist | er Set                                                                | 77  |

|        | 7.1.1  | SYSCLKCTRL (0x1500 3800)                                              | 78  |

|        | 7.1.2  | 1284CTRL (0x1500 3802)                                                | 79  |

|        | 7.1.3  | 16550CTRL (0x1500 3804)                                               | 80  |

|        | 7.1.4  | USBCTRL (0x1500 380C)                                                 | 81  |

|        | 7.1.5  | PS2PWMCTRL (0x1500 380E)                                              | 82  |

| 7.2    | Clock  | Supply                                                                |     |

| СНАРТЕ | ER 8 1 | CU (INTERRUPT CONTROL UNIT)                                           | 85  |

| 8.1    | Regist | er Set                                                                |     |

|        | 8.1.1  | 1284INTRQ (0x1500 3808)                                               | 86  |

|        | 8.1.2  | 16550INTRQ (0x1500 380A)                                              | 87  |

| СНАРТЕ |        | EEE1284 PARALLEL CONTROLLER                                           |     |

| 9.1    | Macro  | Functions                                                             |     |

| 9.2    | Regist | er Set                                                                |     |

|        | 9.2.1  | DATA (0x1500 3820: MODE (2:0) = 001, 100, DIR = 1, during read)       | 93  |

|        | 9.2.2  | DATA (0x1500 3820: MODE (2:0) = 000, 001, 100, DIR = 0, during write) | 93  |

|        | 9.2.3  | AFIFO (0x1500 3820: MODE (2:0) = 011, DIR = 0, during write)          | 94  |

|        | 9.2.4  | DSR (0x1500 3822)                                                     | 95  |

|        | 9.2.5  | DCR (0x1500 3824)                                                     | 96  |

|        | 9.2.6  | MCR (0x1500 3826: MODE (2:0) = 000, 001)                              | 97  |

|        | 9.2.7  | EPPA (0x1500 3826: MODE (2:0) = 100)                                  | 98  |

|        | 9.2.8  | EPPD (0x1500 3828: MODE (2:0) = 100)                                  | 99  |

|        | 9.2.9  | CFIFO (0x1500 3830: MODE (2:0) = 010)                                 | 99  |

|        | 9.2.10 | DFIFO (0x1500 3830: MODE (2:0) = 011)                                 | 100 |

|        | 9.2.11 | TFIFO (0x1500 3830: MODE (2:0) = 110)                                 | 101 |

|        | 9.2.12 | CNFGA (0x1500 3830: MODE (2:0) = 111)                                 | 102 |

|        | 9.2.13 | CNFGB (0x1500 3832: MODE (2:0) = 111)                                 | 103 |

|        | 9.2.14 | ECR (0x1500 3834)                                                     | 104 |

| СНАРТЕ | ER 10  | 16550 SERIAL CONTROLLER                                               | 105 |

| 10.1   | Regist | er Set                                                                |     |

|        | 10.1.1 RBR (0x1500 3810: LCR7 = 0, during read)                        |     |

|--------|------------------------------------------------------------------------|-----|

|        | 10.1.2 THR (0x1500 3810: LCR7 = 0, during write)                       |     |

|        | 10.1.3 DLL (0x1500 3810: LCR7 = 1)                                     |     |

|        | 10.1.4 IER (0x1500 3812: LCR7 = 0)                                     |     |

|        | 10.1.5 DLM (0x1500 3812: LCR7 = 1)                                     |     |

|        | 10.1.6 IIR (0x1500 3814: during read)                                  |     |

|        | 10.1.7 FCR (0x1500 3814: during write)                                 |     |

|        | 10.1.8 LCR (0x1500 3816)                                               |     |

|        | 10.1.9 MCR (0x1500 3818)                                               |     |

|        | 10.1.10 LSR (0x1500 381A)                                              |     |

|        | 10.1.11 MSR (0x1500 381C)                                              |     |

|        | 10.1.12 SCR (0x1500 381E)                                              | 119 |

| СНАРТЕ | R 11 USB HOST CONTROLLER                                               | 121 |

|        | Features                                                               |     |

|        | USB Host Control Configuration Registers                               |     |

| 11.2   | 11.2.1 Register set                                                    |     |

|        | 11.2.2 Command register (offset address: 0x04)                         |     |

|        | 11.2.3 Status register (offset address: 0x04)                          |     |

|        | 11.2.4 Base address register (offset address: 0x10)                    |     |

|        | 11.2.5 Power management control/status register (offset address: 0x10) |     |

| 11 3   | Operational Registers                                                  |     |

| 11.5   | 11.3.1 Register set                                                    |     |

|        | 11.3.2 HcRevision (offset address: 0x00)                               |     |

|        | 11.3.3 HcControl (offset address: 0x04)                                |     |

|        | 11.3.4 HcCommandStatus (offset address: 0x04)                          |     |

|        | 11.3.5 HcInterruptStatus (offset address: 0x0C)                        |     |

|        | 11.3.6 HcInterruptEnable (offset address: 0x10)                        |     |

|        | 11.3.7 HcInterruptDisable (offset address: 0x10)                       |     |

|        | 11.3.8 HcHCCA (offset address: 0x18)                                   |     |

|        | 11.3.9 HcPeriodCurrentED (offset address: 0x1C)                        |     |

|        | 11.3.10 HcControlHeadED (offset address: 0x20)                         |     |

|        | 11.3.11 HcControlCurrentED (offset address: 0x20)                      |     |

|        | 11.3.12 HcBulkHeadED (offset address: 0x28)                            |     |

|        | 11.3.13 HcBulkCurrentED (offset address: 0x20)                         |     |

|        | 11.3.14 HcDoneHead (offset address: 0x30)                              |     |

|        | 11.3.15 HcFmInterval (offset address: 0x34)                            |     |

|        | 11.3.16 HcFmRemaining (offset address: 0x38)                           |     |

|        | 11.3.17 HcFmNumber (offset address: 0x3C)                              |     |

|        | 11.3.18 HcPeriodicStart (offset address: 0x40)                         |     |

|        | 11.3.19 HcLSThreshold (offset address: 0x44)                           |     |

|        | 11.3.20 HcRhDescriptorA (offset address: 0x48)                         |     |

|        | 11.3.21 HcRhDescriptorB (offset address: 0x4C)                         |     |

|        | 11.3.22 HcRhStatus (offset address: 0x50)                              |     |

|        | 11.3.23 HcRhPortStatus 1 and 2 (offset address: 0x54, 0x58)            |     |

|        |                                                                        |     |

|        | R 12 PS/2 CONTROLLER                                                   |     |

| 12.1   | Register Set                                                           | 161 |

| 12.1.1 PS2DATA (0x1500 3870)                        |  |

|-----------------------------------------------------|--|

| 12.1.2 PS2CTRL (0x1500 3872)                        |  |

| 12.2 Transmit Procedure                             |  |

| CHAPTER 13 CONNECTION WITH VR4121                   |  |

| 13.1 Load Reduction Buffer Control                  |  |

| 13.2 Cautions When Connecting Load Reduction Buffer |  |

| CHAPTER 14 INTERRUPT SIGNALS                        |  |

| CHAPTER 15 RESET                                    |  |

| CHAPTER 16 USAGE CAUTIONS                           |  |

| 16.1 Power Supply Control                           |  |

| 16.2 Reset Pins                                     |  |

| 16.3 Cautions on VR4121 Suspend Mode                |  |

| * 16.4 Preserving SDRAM Data                        |  |

| APPENDIX GENERAL INDEX                              |  |

#### LIST OF FIGURES

| Figure N | No. Title                                                                  | Page |

|----------|----------------------------------------------------------------------------|------|

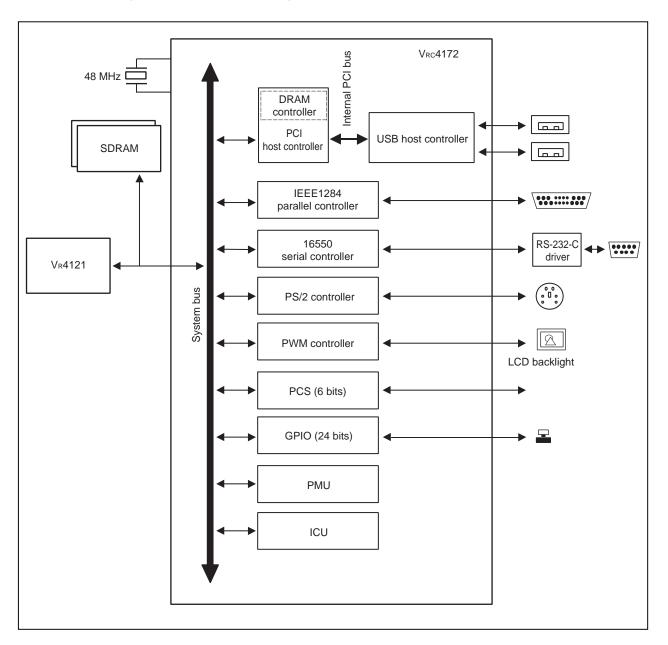

| 1-1      | Internal Block Diagram and External Block Connection Example               |      |

| 3-1      | Physical Address Space                                                     |      |

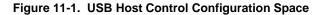

| 11-1     | USB Host Control Configuration Space                                       | 122  |

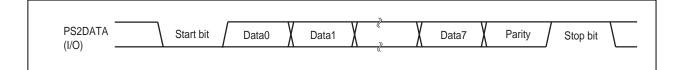

| 12-1     | Data Pattern                                                               | 166  |

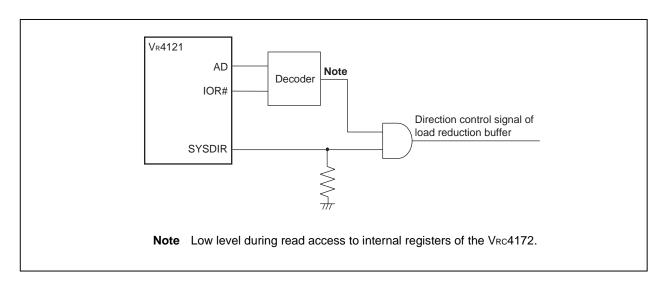

| 13-1     | Example of SYSDIR Signal (VR4121) Circuit When Using Load Reduction Buffer | 169  |

# LIST OF TABLES (1/2)

| Table No. Title |                                                   | e Page |

|-----------------|---------------------------------------------------|--------|

| 1-1             | PCI Configuration Cycle Registers                 |        |

| 1-2             |                                                   |        |

| 1-3             |                                                   |        |

| 1-4             | •                                                 |        |

| 1-5             | C C C C C C C C C C C C C C C C C C C             |        |

| 1-6             | PMU Registers                                     |        |

| 1-7             | ICU Registers                                     |        |

| 1-8             | Parallel Control Registers                        |        |

| 1-9             | Serial Control Registers                          |        |

| 1-10            | USB Host Control Configuration Registers          |        |

| 1-11            | Host Control Operational Registers                |        |

| 1-12            | PS/2 Registers                                    | 24     |

| 2-1             | System Bus Interface Signals                      |        |

| 2-2             | USB Interface Signals                             |        |

| 2-3             | IEEE1284 Interface Signals                        |        |

| 2-4             | RS-232-C Interface Signals                        |        |

| 2-5             | PS/2 Interface Signals                            |        |

| 2-6             | General-Purpose Port Signal                       |        |

| 2-7             | General-Purpose Chip Select Signal                |        |

| 2-8             | LCD Interface Signal                              |        |

| 2-9             | Clock Signals                                     |        |

| 2-10            | Statuses of Pins Under Specific Conditions        |        |

| 2-11            | External Processing of Pins and Drive Performance |        |

| 2-12            | Recommended Connection of Unused Pins             |        |

| 3-1             | Internal I/O Spaces                               |        |

| 3-2             | PCI Configuration Cycle Registers                 | 41     |

| 3-3             | PCI Host Control Registers                        | 45     |

| 4-1             | GPIO Registers                                    | 53     |

| 5-1             | PCS Registers                                     |        |

| 6-1             | PWM Registers                                     | 73     |

| 7-1             | PMU Registers                                     |        |

| 8-1             | ICU Registers                                     |        |

| 9-1             |                                                   |        |

| 9-2             | Macro Mode Correspondence Table                   |        |

# LIST OF TABLES (2/2)

| Table N | lo.                                         | Title | Page |

|---------|---------------------------------------------|-------|------|

| 9-3     | Parallel Control Registers                  |       |      |

| 10-1    | Serial Control Registers                    |       |      |

| 10-2    | Relationship Between Baud Rate and Divisor. |       |      |

| 10-3    | Interrupt Set/Reset                         |       |      |

| 11-1    | USB Host Control Configuration Registers    |       |      |

| 11-2    | Host Control Operational Registers          |       |      |

| 12-1    | PS/2 Registers                              |       |      |

| 14-1    | Interrupt Signals                           |       |      |

[MEMO]

This chapter gives an overview of the V<sub>RC</sub>4172 ( $\mu$ PD31172).

#### 1.1 Features

The VRc4172 is a companion chip for NEC's VR4121 microprocessor.

The VRc4172 features on chip a USB host controller, IEEE1284 parallel controller, 16550 serial controller, PS/2 controller, general-purpose ports (GPIO), programmable chip select function (PCS), and PWM controller (duty modulation pulse generation function for LCD backlights).

The V<sub>RC</sub>4172 can directly be connected to the V<sub>R</sub>4121, reducing the number of man-hours required for the development of Windows<sup>™</sup> CE systems.

The features of the VRc4172 are as follows.

- Can directly be connected to the VR4121

- On-chip USB host controller

- 2 USB ports

- Complies with OPEN HCI Specification Release 1.0

- Communication with USB devices asynchronous with host CPU

- Supports full speed (12 Mbps) and low speed (1.5 Mbps)

- System clock: 48 MHz

- On-chip PS/2 controller

- On-chip IEEE1284 parallel controller

- ECP, EPP, SPP and P1284 host functions

- On-chip 16550 serial controller

- Programmable chip select (PCS):6

- General-purpose ports (GPIO): 24

- On-chip PWM controller

- Duty modulation pulse generation function for LCD backlights

- Supply voltage:  $V_{DD} = 3.3 \pm 0.3 V$

#### **1.2 Ordering Information**

| Part Number      | Package                              | Internal Maximum Operating Frequency |

|------------------|--------------------------------------|--------------------------------------|

| μPD31172F1-48-FN | 208-pin plastic FBGA (15 $	imes$ 15) | 48 MHz                               |

#### 1.3 VRc4172 Processor

Figure 1-1 shows the internal block diagram of the VRc4172 and an example of connection with external components.

#### 1.3.1 Internal block configuration

#### (1) PCI host controller

The PCI host controller controls access from the system bus to the USB host controller.

Access to the USB host controller is done using the PCI bus. For this reason, the PCI host controller contains PCI configuration registers (PCI host control register). Access to the USB host controller is made possible by setting these registers.

#### (2) USB host controller

This controller is a USB host controller that complies with OPEN HCI Specification Release 1.0. It provides two downstream ports.

#### (3) IEEE1284 parallel controller

This controller is a parallel interface (host controller) that complies with the IEEE 1284 standard.

#### (4) 16550 serial controller

The 16550 serial controller is a serial interface for communication that is compatible with RS-232-C. It provides 1 channel each for transmitting and receiving data. This controller is functionally compatible with the NS16550D.

#### (5) PS/2 controller

The PS/2 controller performs control of bi-directional data transfer using the PS2CLK and PS2DATA signals.

#### (6) PWM controller

The PWM controller controls the frequency and duty of the modulation pulse for LCD backlights.

#### (7) PCS (Programmable Chip Select)

PCS compares the addresses set in a register with the addresses on the system bus and generates the EXCS# signal. The EXCS# signal is low level when the addresses match.

#### (8) GPIO (General-Purpose I/O ports)

GPIO control the GPIO pins. The GPIO pins are 24 general-purpose ports that support both input and output. Interrupt request signal input functions can be allocated to these ports, and 5 triggers can be selected: input signal changes (rising edge, falling edge, both edges), low level, and high level.

#### (9) PMU (Power Management Unit)

The PMU controls the clock supply and reset for the IEEE1284 parallel controller, 16550 serial controller, PS/2 controller, PWM controller, and USB host controller. It also performs enable/disable settings for the internal oscillator (48 MHz).

#### (10)ICU (Interrupt Control Unit)

The ICU controls the interrupts for the IEEE1284 parallel controller and the 16550 serial controller.

#### 1.3.2 Registers of each unit

The registers of the various units are listed below.

# Table 1-1. PCI Configuration Cycle Registers

| Name                               | Register Address |

|------------------------------------|------------------|

| PCI configuration address register | 0x0AFF 0CF8      |

| PCI configuration data register    | 0x0AFF 0CFC      |

#### Table 1-2. PCI Host Control Registers

| Name                         | Offset Address |

|------------------------------|----------------|

| Vendor ID register           | 0x00           |

| Command register             | 0x04           |

| Status register              | 0x06           |

| Revision ID register         | 0x08           |

| Memory base address register | 0x10 to 12     |

| Control register             | 0x50           |

#### Table 1-3. GPIO Registers

| Symbol      | Function                                            | Register Address |

|-------------|-----------------------------------------------------|------------------|

| EXGPDATA0   | GPIO (15:0) I/O data register                       | 0x1500 1080      |

| EXGPDIR0    | GPIO (15:0) I/O setting register                    | 0x1500 1082      |

| EXGPINTEN0  | GPIO (15:0) interrupt enable register               | 0x1500 1084      |

| EXGPINTST0  | GPIO (15:0) interrupt register                      | 0x1500 1086      |

| EXGPINTTYP0 | GPIO (15:0) interrupt trigger register              | 0x1500 1088      |

| EXGPINTLV0L | GPIO (15:0) interrupt level setting lower register  | 0x1500 108A      |

| EXGPINTLV0H | GPIO (15:0) interrupt level setting higher register | 0x1500 108C      |

| EXGPDATA1   | GPIO (23:16) I/O data register                      | 0x1500 10C0      |

| EXGPDIR1    | GPIO (23:16) I/O setting register                   | 0x1500 10C2      |

| EXGPINTEN1  | GPIO (23:16) interrupt enable register              | 0x1500 10C4      |

| EXGPINTST1  | GPIO (23:16) interrupt register                     | 0x1500 10C6      |

| EXGPINTTYP1 | GPIO (23:16) interrupt trigger register             | 0x1500 10C8      |

| EXGPINTLV1L | GPIO (23:16) interrupt level setting lower register | 0x1500 10CA      |

#### Table 1-4. PCS Registers

| Symbol    | Function                                            | Register Address |

|-----------|-----------------------------------------------------|------------------|

| EXCS0SELL | EXCS0# compare address lower register               | 0x1500 1090      |

| EXCS0SELH | EXCS0# compare address higher register              | 0x1500 1092      |

| EXCS0MSKL | EXCS0# compare address mask lower & enable register | 0x1500 1094      |

| EXCS0MSKH | EXCS0# compare address mask higher register         | 0x1500 1096      |

| EXCS1SELL | EXCS1# compare address lower register               | 0x1500 1098      |

| EXCS1SELH | EXCS1# compare address higher register              | 0x1500 109A      |

| EXCS1MSKL | EXCS1# compare address mask lower & enable register | 0x1500 109C      |

| EXCS1MSKH | EXCS1# compare address mask higher register         | 0x1500 109E      |

| EXCS2SELL | EXCS2# compare address lower register               | 0x1500 10A0      |

| EXCS2SELH | EXCS2# compare address higher register              | 0x1500 10A2      |

| EXCS2MSKL | EXCS2# compare address mask lower & enable register | 0x1500 10A4      |

| EXCS2MSKH | EXCS2# compare address mask higher register         | 0x1500 10A6      |

| EXCS3SELL | EXCS3# compare address lower register               | 0x1500 10A8      |

| EXCS3SELH | EXCS3# compare address higher register              | 0x1500 10AA      |

| EXCS3MSKL | EXCS3# compare address mask lower & enable register | 0x1500 10AC      |

| EXCS3MSKH | EXCS3# compare address mask higher register         | 0x1500 10AE      |

| EXCS4SELL | EXCS4# compare address lower register               | 0x1500 10B0      |

| EXCS4SELH | EXCS4# compare address higher register              | 0x1500 10B2      |

| EXCS4MSKL | EXCS4# compare address mask lower & enable register | 0x1500 10B4      |

| EXCS4MSKH | EXCS4# compare address mask higher register         | 0x1500 10B6      |

| EXCS5SELL | EXCS5# compare address lower register               | 0x1500 10B8      |

| EXCS5SELH | EXCS5# compare address higher register              | 0x1500 10BA      |

| EXCS5MSKL | EXCS5# compare address mask lower & enable register | 0x1500 10BC      |

| EXCS5MSKH | EXCS5# compare address mask higher register         | 0x1500 10BE      |

#### Table 1-5. PWM Registers

| Symbol    | Function                  | Register Address |

|-----------|---------------------------|------------------|

| LCDDUTYEN | LCDBAK enable register    | 0x1500 3880      |

| LCDFREQ   | LCDBAK frequency register | 0x1500 3882      |

| LCDDUTY   | LCDBAK duty register      | 0x1500 3884      |

#### Table 1-6. PMU Registers

| Symbol     | Function                                   | Register Address |

|------------|--------------------------------------------|------------------|

| SYSCLKCTRL | SYSCLK enable register                     | 0x1500 3800      |

| 1284CTRL   | 1284 parallel clock/reset control register | 0x1500 3802      |

| 16550CTRL  | 16550 serial clock/reset control register  | 0x1500 3804      |

| USBCTRL    | USB clock control register                 | 0x1500 380C      |

| PS2PWMCTRL | PS/2, PWM clock/reset control register     | 0x1500 380E      |

# Table 1-7. ICU Registers

| Symbol     | Function                                                | Register Address |

|------------|---------------------------------------------------------|------------------|

| 1284INTRQ  | IEEE1284 parallel controller interrupt control register | 0x1500 3808      |

| 16550INTRQ | 16550 serial controller interrupt control register      | 0x1500 380A      |

# Table 1-8. Parallel Control Registers

| Symbol | Function                    | Register Address |

|--------|-----------------------------|------------------|

| DATA   | Parallel port data register | 0x1500 3820      |

| AFIFO  | ECP address FIFO            |                  |

| DSR    | Device status register      | 0x1500 3822      |

| DCR    | Device control register     | 0x1500 3824      |

| MCR    | Mode control register       | 0x1500 3826      |

| EPPA   | EPP address register        |                  |

| EPPD   | EPP data register           | 0x1500 3828      |

| CFIFO  | Parallel port data FIFO     | 0x1500 3830      |

| DFIFO  | ECP data FIFO               |                  |

| TFIFO  | Test FIFO                   |                  |

| CNFGA  | Configuration register A    |                  |

| CNFGB  | Configuration register B    | 0x1500 3832      |

| ECR    | Expansion control register  | 0x1500 3834      |

#### Table 1-9. Serial Control Registers

| Symbol | Function                     | Register Address |

|--------|------------------------------|------------------|

| RBR    | Receive buffer register      | 0x1500 3810      |

| THR    | Transmit hold register       |                  |

| DLL    | Divide ratio lower register  |                  |

| IER    | Interrupt enable register    | 0x1500 3812      |

| DLM    | Divide ratio higher register |                  |

| IIR    | Interrupt display register   | 0x1500 3814      |

| FCR    | FIFO control register        |                  |

| LCR    | Line control register        | 0x1500 3816      |

| MCR    | Modem control register       | 0x1500 3818      |

| LSR    | Line status register         | 0x1500 381A      |

| MSR    | Modem status register        | 0x1500 381C      |

| SCR    | Scratch register             | 0x1500 381E      |

# Table 1-10. USB Host Control Configuration Registers

| Name                                                         | Offset Address |

|--------------------------------------------------------------|----------------|

| Vendor ID register                                           | 0x00           |

| Device ID register                                           | 0x02           |

| Command register                                             | 0x04           |

| Status register                                              | 0x06           |

| Revision ID register                                         | 0x08           |

| Class code base address register                             | 0x09           |

| Class code subclass register                                 |                |

| Class code programming interface register                    |                |

| Cache line size register                                     | 0x0C           |

| Latency timer register                                       | 0x0D           |

| Header type register                                         | 0x0E           |

| BIST register                                                | 0x0F           |

| Built-in self test register                                  | 0x10           |

| Subsystem vendor ID register                                 | 0x2C           |

| Subsystem ID register                                        | 0x2E           |

| Interrupt line register                                      | 0x3C           |

| Interrupt mode register                                      | 0x3D           |

| Min_Gnt register (burst cycle minimum request time register) | 0x3E           |

| Max_lat register (bus mastership request frequency register) | 0x3F           |

| Power management control/status register                     | 0xE0           |

| Symbol             | Function                       | Offset Address |

|--------------------|--------------------------------|----------------|

| HcRevision         | HC revision register           | 0x00           |

| HcControl          | HC control register            | 0x04           |

| HcCommandStatus    | HC command status register     | 0x08           |

| HcInterruptStatus  | HC interrupt status register   | 0x0C           |

| HcInterruptEnable  | HC interrupt enable register   | 0x10           |

| HcInterruptDisable | HC interrupt disable register  | 0x14           |

| HcHCCA             | HC communication area register | 0x18           |

| HcPeriodCurrentED  | HC period current ED register  | 0x1C           |

| HcControlHeadED    | HC control head ED register    | 0x20           |

| HcControlCurrentED | HC control current ED register | 0x24           |

| HcBulkHeadED       | HC bulk head ED register       | 0x28           |

| HcBulkCurrentED    | HC bulk current ED register    | 0x2C           |

| HcDoneHead         | HC done head register          | 0x30           |

| HcFmInterval       | HC frame interval register     | 0x34           |

| HcFmRemaining      | HC frame remaining register    | 0x38           |

| HcFmNumber         | HC frame number register       | 0x3C           |

| HcPeriodicStart    | HC periodic start register     | 0x40           |

| HcLSThreshold      | HC LS threshold register       | 0x44           |

| HcRhDescriptorA    | HC RH descriptor A register    | 0x48           |

| HcRhDescriptorB    | HC RH descriptor B register    | 0x4C           |

| HcRhStatus         | HC RH status register          | 0x50           |

| HcRhPortStatus1    | HC RH port status 1 register   | 0x54           |

| HcRhPortStatus2    | HC RH port status 2 register   | 0x58           |

#### Table 1-11. Host Control Operational Registers

# Table 1-12. PS/2 Registers

| Symbol  | Function                            | Register Address |

|---------|-------------------------------------|------------------|

| PS2DATA | PS/2 transmit/receive data register | 0x1500 3870      |

| PS2CTRL | PS/2 control register               | 0x1500 3872      |

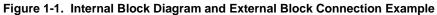

#### 2.1 Pin Configuration

• 208-pin plastic FBGA (15 × 15)

| No. | Name                       | No. | Name      | No. | Name                       | No. | Name                           |

|-----|----------------------------|-----|-----------|-----|----------------------------|-----|--------------------------------|

| A1  | GND                        | C3  | STROBE#   | E14 | GND                        | K1  | GPIO14                         |

| A2  | AUTOFEED#                  | C4  | ACK#      | E15 | PPON1                      | K2  | GPIO10                         |

| A3  | PE                         | C5  | ERROR#    | E16 | OCI2                       | K3  | GPIO7                          |

| A4  | INIT#                      | C6  | AD6       | E17 | USBRST#                    | K4  | GPIO3                          |

| A5  | IOCHRDY                    | C7  | AD7       | F1  | GPIO22                     | K14 | EXCS3#                         |

| A6  | AD19                       | C8  | AD8       | F2  | GPIO18                     | K15 | EXCS0#                         |

| A7  | AD20                       | C9  | Vdd       | F3  | CD2                        | K16 | SCAS#                          |

| A8  | AD21                       | C10 | AD9       | F4  | CD6                        | K17 | SRAS#                          |

| A9  | AD22                       | C11 | AD10      | F14 | SCLK                       | L1  | GPIO13                         |

| A10 | AD23                       | C12 | AD11      | F15 | PPON2                      | L2  | GPIO9                          |

| A11 | AD24                       | C13 | LCDBAK    | F16 | LCAS#                      | L3  | GPIO6                          |

| A12 | Reserved <sup>Note 1</sup> | C14 | SMI#      | F17 | MRAS0#                     | L4  | GPIO2                          |

| A13 | Reserved <sup>Note 1</sup> | C15 | USBINT#   | G1  | GPIO21                     | L14 | EXCS4#                         |

| A14 | DP1                        | C16 | GND       | G2  | GPIO17                     | L15 | EXCS1#                         |

| A15 | DN2                        | C17 | RD#       | G3  | CD1                        | L16 | Reserved (0) <sup>Note 2</sup> |

| A16 | DP2                        | D1  | GND       | G4  | CD5                        | L17 | GND                            |

| A17 | LCDRDY                     | D2  | SELECTIN# | G14 | Reserved <sup>Note 1</sup> | M1  | GPIO12                         |

| B1  | PS2CLK                     | D3  | DIR1284   | G15 | Reserved <sup>Note 1</sup> | M2  | GPIO8                          |

| B2  | Vdd                        | D4  | PS2INT    | G16 | UCAS#                      | M3  | GPIO5                          |

| B3  | Vdd                        | D5  | SELECT    | G17 | MRAS1#                     | M4  | GPIO1                          |

| B4  | BUSY                       | D6  | AD0       | H1  | GPIO20                     | M14 | EXCS5#                         |

| B5  | GND                        | D7  | AD1       | H2  | GPIO16                     | M15 | EXCS2#                         |

| B6  | AD12                       | D8  | AD2       | H3  | CD0                        | M16 | Reserved (0) <sup>Note 2</sup> |

| B7  | AD13                       | D9  | GND       | H4  | CD4                        | M17 | CKE                            |

| B8  | AD14                       | D10 | AD3       | H14 | Reserved <sup>Note 1</sup> | N1  | RESET                          |

| B9  | AD15                       | D11 | AD4       | H15 | ARBCLKSEL                  | N2  | BUSRQ0#                        |

| B10 | AD16                       | D12 | AD5       | H16 | ULCAS#                     | N3  | GPIO4                          |

| B11 | AD17                       | D13 | Vdd       | H17 | ROMCS2#                    | N4  | GPIO0                          |

| B12 | AD18                       | D14 | IEN       | J1  | GPIO15                     | N14 | GND                            |

| B13 | GND                        | D15 | WAKE      | J2  | GPIO11                     | N15 | DSR#                           |

| B14 | DN1                        | D16 | OCI1      | J3  | Vdd                        | N16 | RXD                            |

| B15 | Vdd                        | D17 | LCDCS#    | J4  | GND                        | N17 | RI#                            |

| B16 | GND                        | E1  | GPIO23    | J14 | Vdd                        | P1  | HOLDRQ#                        |

| B17 | WR#                        | E2  | GPIO19    | J15 | GND                        | P2  | BUSAK0#                        |

| C1  | PS2DATA                    | E3  | CD3       | J16 | UUCAS#                     | P3  | BUSRQ1#                        |

| C2  | GND                        | E4  | CD7       | J17 | ROMCS3#                    | P4  | GND                            |

Notes 1. Leave the A12, A13, G14, G15, and H14 pins open, or input 0.

2. Be sure to input 0 to the L16 and M16 pins.

**Remark** # indicates active low.

| No. | Name      | No. | Name    | No. | Name    | No. | Name  |

|-----|-----------|-----|---------|-----|---------|-----|-------|

| P5  | DATA31    | R4  | DATA23  | Т3  | Vdd     | U2  | IRQ   |

| P6  | DATA30    | R5  | DATA22  | T4  | Vdd     | U3  | IOR#  |

| P7  | DATA29    | R6  | Vdd     | T5  | DATA15  | U4  | IOW#  |

| P8  | DATA28    | R7  | DATA21  | T6  | DATA14  | U5  | GND   |

| P9  | Vdd       | R8  | DATA20  | T7  | GND     | U6  | DATA7 |

| P10 | DATA27    | R9  | GND     | Т8  | DATA13  | U7  | DATA6 |

| P11 | DATA26    | R10 | DATA19  | Т9  | DATA12  | U8  | DATA5 |

| P12 | DATA25    | R11 | DATA18  | T10 | DATA11  | U9  | DATA4 |

| P13 | DATA24    | R12 | Vdd     | T11 | DATA10  | U10 | DATA3 |

| P14 | CLKOUT48M | R13 | DATA17  | T12 | GND     | U11 | DATA2 |

| P15 | DCD#      | R14 | DATA16  | T13 | DATA9   | U12 | DATA1 |

| P16 | ТХD       | R15 | CTS#    | T14 | DATA8   | U13 | DATA0 |

| P17 | INTRP     | R16 | GND     | T15 | Vdd     | U14 | GND   |

| R1  | HOLDAK#   | R17 | XOUT48M | T16 | Vdd     | U15 | DTR#  |

| R2  | GND       | T1  | BUSCLK  | T17 | XIN48M  | U16 | RTS#  |

| R3  | BUSAK1#   | T2  | GND     | U1  | IOCS16# | U17 | GND   |

**Remark** # indicates active low.

#### Pin Names

| ACK#:         | Acknowledge                 | MRAS (0:1)#:  | DRAM Row Address Strobe   |

|---------------|-----------------------------|---------------|---------------------------|

| AD (0:24):    | Address Bus                 | OCI (1:2):    | Over Current Interrupt    |

| ARBCLKSEL:    | Arbitration Clock Select    | PE:           | Paper End                 |

| AUTOFEED#:    | Autofeed                    | PPON (1:2):   | Port Power ON             |

| BUSAK (0:1)#: | Bus Acknowledge             | PS2CLK:       | PS2 Clock                 |

| BUSCLK:       | System Bus Clock            | PS2DATA:      | PS2 Data                  |

| BUSRQ (0:1)#: | Bus Request                 | PS2INT:       | PS2 Interrupt             |

| BUSY:         | Busy                        | RD#:          | Read                      |

| CD (0:7):     | Centronics Data             | RESET:        | Reset                     |

| CKE:          | Clock Enable                | RI#:          | Ring Indicator            |

| CLKOUT48M:    | Clock Out of 48 MHz         | ROMCS (2:3)#: | ROM Chip Select           |

| CTS#:         | Clear to Send               | RTS#:         | Request to Send           |

| DATA (0:31):  | Data Bus                    | RXD:          | Receive Data              |

| DCD#:         | Data Carrier Detect         | SCAS#:        | Column Address Strobe for |

| DIR1284:      | Direction of 1284           |               | SDRAM                     |

| DN (1:2):     | USB D-                      | SCLK:         | SDRAM Clock               |

| DP (1:2):     | USB D+                      | SELECT:       | Select                    |

| DSR#:         | Data Set Ready              | SELECTIN#:    | Select in                 |

| DTR#:         | Data Terminal Ready         | SMI#:         | USB System Interrupt      |

| ERROR#:       | Error                       | SRAS#:        | Row Address Strobe for    |

| EXCS (0:5)#:  | External CS                 |               | SDRAM                     |

| GND:          | Ground                      | STROBE#:      | Strobe                    |

| GPIO (0:23):  | General Purpose I/O         | TXD:          | Transmit Data             |

| HOLDAK#:      | Hold Acknowledge            | UCAS#:        | Upper Column Address      |

| HOLDRQ#:      | Hold Request                |               | Strobe                    |

| IEN:          | USB Input Enable            | ULCAS#:       | Lower Byte of Upper       |

| INIT#:        | Initialize                  |               | Column Address Strobe     |

| INTRP:        | Interrupt                   | USBINT#:      | USB Interrupt             |

| IOCHRDY:      | I/O Channel Ready           | USBRST#:      | USB Reset                 |

| IOCS16#:      | I/O Chip Select 16          | UUCAS#:       | Upper Byte of Upper       |

| IOR#:         | I/O Read                    |               | Column Address Strobe     |

| IOW#:         | I/O Write                   | Vdd:          | Power Supply Voltage      |

| IRQ:          | I/O Request                 | WAKE:         | Wake Up Interrupt         |

| LCAS#:        | Lower Column Address Strobe | WR#:          | Write                     |

| LCDBAK:       | LCD Back Light              | XIN48M:       | Clock In of 48 MHz        |

| LCDCS#:       | LCD Chip Select             | XOUT48M:      | Clock Out of 48 MHz       |

| LCDRDY:       | LCD Ready                   |               |                           |

|               |                             |               |                           |

**Remark** # indicates active low.

### 2.2 List of Pin Functions

#### 2.2.1 System bus interface signals

These signals are used when the  $V_R4121$  and SDRAM are connected.

| Table 2-1. | System | Bus | Interface | Signals | (1/2) |

|------------|--------|-----|-----------|---------|-------|

|------------|--------|-----|-----------|---------|-------|

| Signal Name   | I/O | Function                                                                                                                                                                            |

|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK          | I/O | SDRAM operation clock                                                                                                                                                               |

| AD (0:24)     | I/O | 25-bit address bus                                                                                                                                                                  |

| DATA (0:31)   | I/O | 32-bit data bus                                                                                                                                                                     |

| LCDCS#        | I   | LCD chip select signal. This signal is active when the VR4121 uses the AD bus and DATA bus to perform LCD access.                                                                   |

| RD#           | I/O | <ul> <li>Output: Active when the VRc4172 accesses SDRAM.</li> <li>Input: Active when the VR4121 reads data from the PCI host bridge of the VRc4172.</li> </ul>                      |

| WR#           | I/O | <ul> <li>Output: Active when the VRc4172 performs data write to SDRAM.</li> <li>Input: Active when the VR4121 performs data write to the PCI host bridge of the VRc4172.</li> </ul> |

| LCDRDY        | 0   | LCD ready signal. Active when the $V_{RC}4172$ is ready to accept access by the $V_{R}4121$ to the LCD area.                                                                        |

| ROMCS (2:3)#  | I/O | SDRAM chip select signal                                                                                                                                                            |

| СКЕ           | I/O | SDRAM clock enable signal                                                                                                                                                           |

| UUCAS#        | I/O | DQM signal of SDRAM. I/O buffer control signal for DATA (24:31).                                                                                                                    |

| ULCAS#        | I/O | DQM signal of SDRAM. I/O buffer control signal for DATA (16:23).                                                                                                                    |

| MRAS (0:1)#   | I/O | SDRAM chip select signal                                                                                                                                                            |

| UCAS#         | I/O | DQM signal of SDRAM. I/O buffer control signal for DATA (8:15).                                                                                                                     |

| LCAS#         | I/O | DQM signal of SDRAM. I/O buffer control signal for DATA (0:7).                                                                                                                      |

| IOR#          | I   | System bus I/O read signal. Active during access of resources other than USB in the $V_{RC}4172$ .                                                                                  |

| IOW#          | I   | System bus I/O write signal. Active during access of resources other than USB in the $V_{RC}4172$ .                                                                                 |

| RESET         | I   | System bus reset signal                                                                                                                                                             |

| IOCS16#       | 0   | Dynamic bus sizing request signal                                                                                                                                                   |

| IOCHRDY       | 0   | System bus ready signal                                                                                                                                                             |

| HOLDRQ#       | 0   | System bus mastership request signal                                                                                                                                                |

| HOLDAK#       | I   | System bus use enable signal                                                                                                                                                        |

| SRAS#         | I/O | RAS signal of SDRAM                                                                                                                                                                 |

| SCAS#         | I/O | CAS signal of SDRAM                                                                                                                                                                 |

| BUSRQ (0 :1)# | I   | System bus mastership request signal from external bus master                                                                                                                       |

| BUSAK (0:1)#  | 0   | System bus use enable signal to external bus master                                                                                                                                 |

#### Table 2-1. System Bus Interface Signals (2/2)

| Signal Name | I/O | Function                                                                                                                 |  |  |  |  |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| INTRP       | 0   | Interrupt request signal from 16550 serial controller or IEEE1284 parallel controller                                    |  |  |  |  |

| IRQ         | 0   | Interrupt request signal from general-purpose port (GPIO (0:23)) or IEEE1284 parallel controller                         |  |  |  |  |

| USBINT#     | 0   | Interrupt request signal from USB host controller                                                                        |  |  |  |  |

| PS2INT      | 0   | Interrupt request signal from PS/2 controller                                                                            |  |  |  |  |

| BUSCLK      | Ι   | System bus clock                                                                                                         |  |  |  |  |

| ARBCLKSEL   | Ι   | Signal that selects the clock for system bus arbitration (HOLDRQ# signal control) (1: Use internal clock, 0: Use BUSCLK) |  |  |  |  |

#### 2.2.2 USB interface signals

| Signal Name | I/O | Function                                                                                                                                                           |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DP (1:2)    | I/O | Positive data signal                                                                                                                                               |

| DN (1:2)    | I/O | Negative data signal                                                                                                                                               |

| PPON (1:2)  | 0   | USB root hub port power supply control signal                                                                                                                      |

| OCI (1:2)   | I   | USB root hub port overcurrent status signal. Make this signal active when the current that flows through the Vbus line of the USB bus exceeds the reference value. |

| IEN         | I   | USB buffer input enable signal. Make this signal active to enable an input signal to the USB port.                                                                 |

| WAKE        | 0   | Wakeup interrupt request signal                                                                                                                                    |

| SMI#        | 0   | System interrupt request signal                                                                                                                                    |

| USBRST#     | I   | Reset signal to USB block                                                                                                                                          |

#### Table 2-2. USB Interface Signals

#### 2.2.3 IEEE1284 interface signals

#### Table 2-3. IEEE1284 Interface Signals

| Signal Name | I/O | Function                                |

|-------------|-----|-----------------------------------------|

| CD (0:7)    | I/O | Data signal                             |

| STROBE#     | I/O | Data strobe signal                      |

| ACK#        | I/O | Acknowledge signal                      |

| BUSY        | I/O | Busy signal                             |

| PE          | I/O | Paper end signal                        |

| SELECT      | I/O | Select signal                           |

| AUTOFEED#   | I/O | Autofeed signal                         |

| SELECTIN#   | I/O | Select input signal                     |

| ERROR#      | I/O | Fault signal                            |

| INIT#       | I/O | Initialize signal                       |

| DIR1284     | 0   | Transfer direction status output signal |

#### 2.2.4 RS-232-C interface signals

These signals are used during data transmit/receive with the VRc4172 and RS-232-C controller.

| Signal Name | I/O | Function                     |

|-------------|-----|------------------------------|

| RXD         | I   | Receive data signal          |

| CTS#        | Ι   | Transmit enable signal       |

| DSR#        | I   | Data set ready signal        |

| TXD         | 0   | Transmit data signal         |

| RTS#        | 0   | Transmit request signal      |

| DTR#        | 0   | Terminal device ready signal |

| DCD#        | I   | Carrier detection signal     |

| RI#         | I   | Call-in display signal       |

#### Table 2-4. RS-232-C Interface Signals

#### 2.2.5 PS/2 interface signals

#### Table 2-5. PS/2 Interface Signals

| Signal Name | I/O | Function          |

|-------------|-----|-------------------|

| PS2CLK      | I/O | PS/2 clock signal |

| PS2DATA     | I/O | PS/2 data signal  |

#### 2.2.6 General-purpose port signal

#### Table 2-6. General-Purpose Port Signal

| Signal Name | I/O | Function                   |

|-------------|-----|----------------------------|

| GPIO (0:23) | I/O | General-purpose I/O signal |

#### 2.2.7 General-purpose chip select signal

#### Table 2-7. General-Purpose Chip Select Signal

| Signal Name | I/O | Function                           |

|-------------|-----|------------------------------------|

| EXCS (0:5)# | 0   | General-purpose chip select signal |

#### 2.2.8 LCD interface signal

#### Table 2-8. LCD Interface Signal

| Signal Name | I/O | Function                     |

|-------------|-----|------------------------------|

| LCDBAK      | 0   | LCD backlight control signal |

#### 2.2.9 Clock signals

These signals are used to supply clocks.

| Signal Name | I/O | Function                                                                    |  |

|-------------|-----|-----------------------------------------------------------------------------|--|

| XIN48M      | I   | 48 MHz oscillator input pin. One side of a crystal resonator is connected.  |  |

| XOUT48M     | 0   | 48 MHz oscillator output pin. One side of a crystal resonator is connected. |  |

| CLKOUT48M   | 0   | 48 MHz clock output for FIR of the VR4121                                   |  |

#### 2.3 Pin Statuses

#### 2.3.1 Status of pins under specific conditions

Table 2-10 lists the statuses of pins after the  $V_{RC}4172$  is reset and when HOLDAK# = 1.

| Signal Name  | After Reset | When HOLDAK# = 1 |

|--------------|-------------|------------------|

| SCLK         | Hi-Z        | Hi-Z             |

| AD (0:24)    | Hi-Z        | Hi-Z             |

| DATA (0:31)  | Hi-Z        | Hi-Z             |

| LCDCS#       | _           | -                |

| RD#          | Hi-Z        | Hi-Z             |

| WR#          | Hi-Z        | Hi-Z             |

| LCDRDY       | Hi-Z        | Hi-Z             |

| ROMCS (2:3)# | Hi-Z        | Hi-Z             |

| CKE          | Hi-Z        | Hi-Z             |

| UUCAS#       | Hi-Z        | Hi-Z             |

| ULCAS#       | Hi-Z        | Hi-Z             |

| MRAS (0:1)#  | Hi-Z        | Hi-Z             |

| UCAS#        | Hi-Z        | Hi-Z             |

| LCAS#        | Hi-Z        | Hi-Z             |

| IOR#         | _           | _                |

| IOW#         | _           | _                |

| RESET        | _           | _                |

| IOCS16#      | Hi-Z        | Hi-Z             |

| IOCHRDY      | Hi-Z        | Hi-Z             |

| HOLDRQ#      | 1           | 1                |

| HOLDAK#      | _           | —                |

| SRAS#        | Hi-Z        | Hi-Z             |

| SCAS#        | Hi-Z        | Hi-Z             |

| BUSRQ (0:1)# | —           | —                |

| BUSAK (0:1)# | 1           | Normal operation |

| INTRP        | 0           | Normal operation |

| IRQ          | 0           | Normal operation |

| USBINT#      | 1           | Normal operation |

| PS2INT       | 0           | Normal operation |

| BUSCLK       | _           | _                |

| ARBCLKSEL    | _           | _                |

| DP (1:2)     | 1           | Normal operation |

| Table 2-10. | Statuses of Pins Under Specific Conditions ( | 1/2) |

|-------------|----------------------------------------------|------|

Remark 0: Low level, 1: High level, Hi-Z: High impedance

| Signal Name | After Reset | When HOLDAK# = 1 |

|-------------|-------------|------------------|

| DN (1:2)    | 0           | Normal operation |

| PPON (1:2)  | 0           | Normal operation |

| OCI (1:2)   | _           | —                |

| IEN         | _           | —                |

| WAKE        | 0           | Normal operation |

| SMI#        | 1           | Normal operation |

| USBRST#     | —           | —                |

| CD (0:7)    | Hi-Z        | Normal operation |

| STROBE#     | Hi-Z        | Normal operation |

| ACK#        | Hi-Z        | Normal operation |

| BUSY        | Hi-Z        | Normal operation |

| PE          | Hi-Z        | Normal operation |

| SELECT      | Hi-Z        | Normal operation |

| AUTOFEED#   | Hi-Z        | Normal operation |

| SELECTIN#   | Hi-Z        | Normal operation |

| ERROR#      | Hi-Z        | Normal operation |

| INIT#       | Hi-Z        | Normal operation |

| DIR1284     | 0           | Normal operation |

| RXD         | _           | —                |

| CTS#        | —           | —                |

| DSR#        | _           | —                |

| TXD         | 1           | Normal operation |

| RTS#        | 1           | Normal operation |

| DTR#        | 1           | Normal operation |

| DCD#        | _           | —                |

| RI#         | —           | —                |

| PS2CLK      | 0           | Normal operation |

| PS2DATA     | Hi-Z        | Normal operation |

| GPIO (0:23) | Hi-Z        | Normal operation |

| EXCS (0:5)# | 1           | Normal operation |

| LCDBAK      | 0           | Normal operation |

| CLKOUT48M   | 1           | Normal operation |

Table 2-10. Statuses of Pins Under Specific Conditions (2/2)

Remark 0: Low level, 1: High level, Hi-Z: High impedance

#### 2.3.2 External processing of pins and drive performance

Table 2-11 lists the external processing of pins and their drive performance.

| Signal Name  | External Processing     | Drive Performance | Withstand Voltage |

|--------------|-------------------------|-------------------|-------------------|

| SCLK         | _                       | 80 pF             | 3 V               |

| AD (0:24)    | _                       | 80 pF             | 3 V               |

| DATA (0:31)  | —                       | 80 pF             | 3 V               |

| LCDCS#       | Pull up                 |                   | 3 V               |

| RD#          | Pull up <sup>Note</sup> | 80 pF             | 3 V               |