# **NEC**

# **User's Manual**

# **V**RC4173<sup>TM</sup>

**VR4100 Series™ Companion Chip**

$\mu$ PD31173

Document No. U14579EJ2V0UM00 (2nd edition) Date Published February 2002 N CP(K)

### [MEMO]

#### **NOTES FOR CMOS DEVICES -**

### 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

VR4100 Series, VR4121, VR4122, and VRC4173 are trademarks of NEC Corporation.

Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

- The information in this document is current as of November, 2001. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of

third parties by or arising from the use of NEC semiconductor products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

- "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

- (Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- · Ordering information

- · Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

### **NEC Electronics (Europe) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

Branch The Netherlands

Eindhoven, The Netherlands

Tel: 040-244 58 45

Fax: 040-244 45 80

Branch Sweden Taeby, Sweden Tel: 08-63 80 820

Fax: 08-63 80 388

### **NEC Electronics (France) S.A.**

Vélizy-Villacoublay, France Tel: 01-3067-58-00 Fax: 01-3067-58-99

# NEC Electronics (France) S.A. Representación en España

Madrid, Spain Tel: 091-504-27-87 Fax: 091-504-28-60

### **NEC Electronics Italiana S.R.L.**

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Singapore Pte. Ltd.**

Novena Square, Singapore

Tel: 253-8311 Fax: 250-3583

### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP, Brasil Tel: 11-6462-6810

Fax: 11-6462-6829

J01.12

### **Major Revisions in This Edition (1/2)**

| Page          | Description                                                                                                 |

|---------------|-------------------------------------------------------------------------------------------------------------|

| Throughout    | Deletion of descriptions related to 32-bit PC card (CardBus card)                                           |

| p.25          | Modification of description in 1.1 Features                                                                 |

| p.27          | Modification of description in 1.3 (14) CARDU1, CARDU2 (PC Card Units)                                      |

| p.50          | Modification of pin I/O direction in Table 2-1 PCI Bus Interface Signals                                    |

| p.51          | Modification of pin I/O direction in Table 2-4 PC Card Interface Signals                                    |

| p.56          | Modification of Table 2-13 Test Interface Signals and Table 2-14 Test Modes                                 |

| pp.58 to 61   | Modification of Table 2-18 Pin Status and Recommended Connection Examples                                   |

| p.86          | Modification of description in 6.1 General                                                                  |

| p.89          | Addition of Note to 6.2.2 CMUSRST (base address + 0x042)                                                    |

| p.90          | Modification of register name in text of <b>7.1 General</b>                                                 |

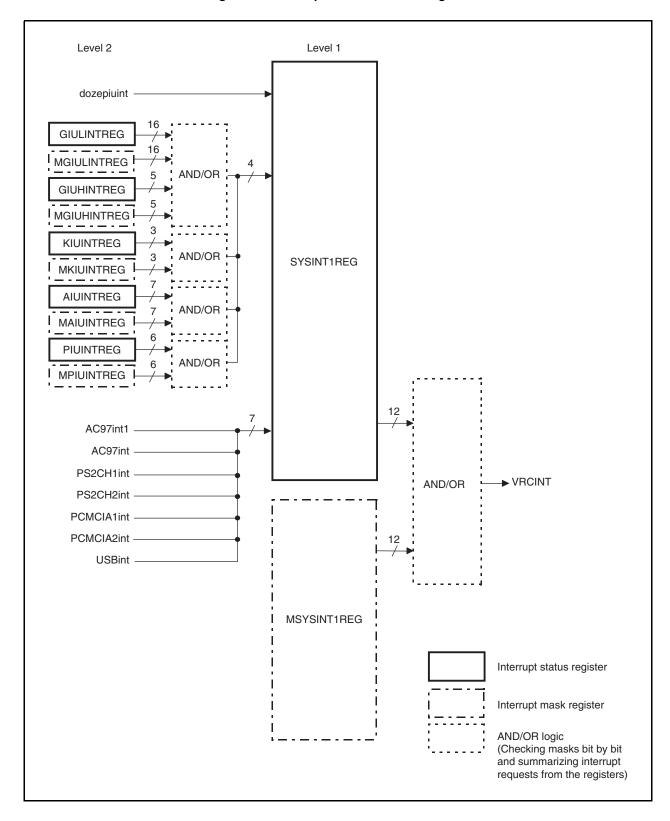

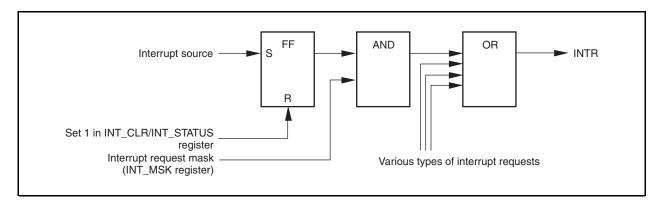

| p.91          | Modification of Figure 7-1 Interrupt Control Outline Diagram                                                |

| p.96          | Modification of description in 7.2.2 PIUINTREG (base address + 0x062)                                       |

| p.102         | Modification of description in 7.2.8 MPIUINTREG (base address + 0x06E)                                      |

| p.111         | Modification of description in 8.2.3 GIUPIODL (base address + 0x084)                                        |

| p.112         | Modification of description in 8.2.4 GIUPIODH (base address + 0x086)                                        |

| p.127         | Modification of description in 9.1.1 Block diagrams                                                         |

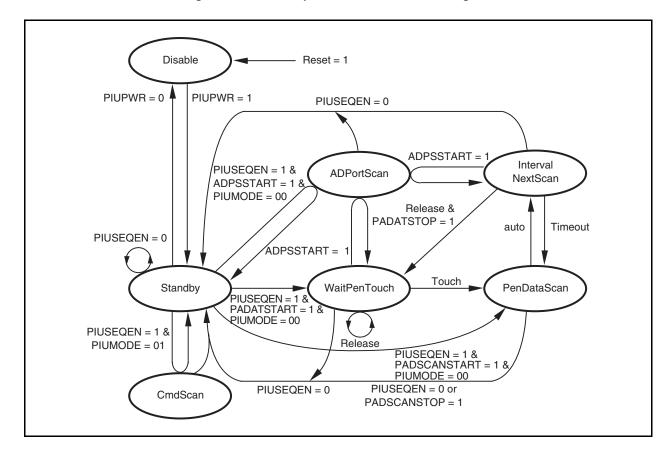

| p.129         | Modification of Figure 9-4 Scan Sequencer State Transition Diagram                                          |

| p.129         | Modification of description in 9.2 (3) ADPortScan state                                                     |

| p.130         | Modification of bit name in 9.2 (5) WaitPenTouch state                                                      |

| p.134         | Addition of Note to Table 9-2 PIUCNTREG Register Bit Manipulation and States                                |

| p.135         | Modification of description in 9.3.2 PIUINTREG (base address + 0x0A4)                                       |

| p.145         | Modification of bit name in 9.4 (2) Transfer flow for auto scan coordinate detection                        |

| p.147         | Modification of bit name in 9.4 (7) Transfer flow when returning from Suspend mode (Disable state)          |

| p.152         | Addition of Caution to 10.1 General                                                                         |

| p.154         | Modification of description in 10.2.3 SODATREG (base address + 0x0E6)                                       |

| p.158         | Modification of bit name in 10.2.7 MCNTREG (base address + 0x0F2)                                           |

| p.161         | Addition of Note to 10.2.10 SEQREG (base address + 0x0FA)                                                   |

| p.164         | Modification of description in 10.3.1 (2) When not using DMA transfer                                       |

| p.165         | Modification of bit name in 10.3.2 Input (MIC)                                                              |

| p.187         | Modification of description in 13.1 General                                                                 |

| p.196         | Addition of Caution to 13.2.11 CSRBADR (offset address: 0x10 to 0x13)                                       |

| pp.197 to 207 | Addition of Caution to 13.2.13 to 13.2.25                                                                   |

| pp.209, 210   | Addition of Caution to 13.2.28 to 13.2.30                                                                   |

| p.213         | Addition of Caution to 13.2.32 SYSCNT (offset address: 0x80 to 0x83)                                        |

| p.216         | Addition of Caution to 13.2.36 and 13.2.37                                                                  |

| pp.251, 252   | Addition of Caution to 13.3.60 and 13.3.61                                                                  |

| p.253         | Addition of Caution to 13.3.64 MEM0_CMD_TIM (PCI offset address: 0x885, ExCA extended offset address: 0x0A) |

### **Major Revisions in This Edition (2/2)**

| Page          | Description                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------|

| p.255         | Addition of Caution to 13.3.67 MEM1_CMD_TIM (PCI offset address: 0x889, ExCA extended offset address: 0x0E)     |

| p.258         | Modification of Table 13-4 CardBus Socket Registers                                                             |

| p.259         | Modification of description in 13.4.1 SKT_EV (offset address: 0x000)                                            |

| pp.262, 263   | Addition of Note to 13.4.3 SKT_PRE_STATE (offset address: 0x008)                                                |

| p.272         | Modification of Caution in 13.5.3 Power supply interface                                                        |

| p.276         | Modification of reset value of device ID register in <b>Table 14-1 USB Host Control Configuration Registers</b> |

| pp.284, 285   | Modification of bit name in 14.3.3 HcControl (offset address: 0x04)                                             |

| p.346         | Modification of Table 15-2 AC97U Operational Registers                                                          |

| pp.354, 355   | Modification of description and addition of Note in 15.3.7 CTRL (offset address: 0x18)                          |

| p.381         | Modification of Figure 15-5 AC97U-Supported Slots                                                               |

| p.385         | Modification of Remark 2 in 15.5.6 (3) Filter function                                                          |

| p.387         | Modification of bit name in 15.6 (2) SDATAOUT slot 1: CMDADDR (Command Address Port)                            |

| pp.394 to 396 | Modification of description in 15.9 (1) Data output to the Codec (slot 3, 4, or 5)                              |

| p.398         | Modification of description in 15.9 (2) Data input from the Codec (slot 3, 4, 5, or 6)                          |

| p.402         | Addition of APPENDIX A CAUTIONS                                                                                 |

| pp.403 to 407 | Addition of APPENDIX B RESTRICTIONS                                                                             |

The mark ★ shows major revised points.

#### INTRODUCTION

Target Readers This manual is intended for users who understand the functions of the V<sub>RC</sub>4173 and

develop application systems using them.

Purpose This manual is designed to help users understand the architecture of the V<sub>RC</sub>4173, as

described below.

**Organization** This manual covers the following general topics.

Overview

· Pin functions

• On-chip peripheral functions

**How to Read This Manual** This manual assumes that the reader has general knowledge of electrical engineering, logic circuits, and microcomputers.

• To gain a general understanding of VRc4173 functions

$\rightarrow\,$  Read this manual in the order of the contents.

• To learn about the electrical specifications of the VRc4173

→ Refer to the Data Sheet (separate document)

**Conventions** Data significance: Higher digits on the left and lower digits on the right

Active low representation: XXX# (# after pin or signal name)

Note: Footnote for item marked with Note in the text Caution: Information requiring particular attention

**Remark**: Supplementary information

Numerical representation: Binary or decimal ... XXXX

Hexadecimal ... 0xXXXX

Prefix indicating power of 2 (address space, memory capacity):

K (kilo)  $2^{10} = 1,024$

M (mega)  $2^{20} = 1,024^2$ G (giga)  $2^{30} = 1,024^3$

T (tera)  $2^{40} = 1,024^4$

P (peta)  $2^{50} = 1,024^{5}$

E (exa)  $2^{60} = 1,024^6$

### **Related Documents**

See the following documents when using this manual.

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

### O Documents related to device

| Document Name                                  | Document Number |

|------------------------------------------------|-----------------|

| V <sub>RC</sub> 4173 User's Manual             | This manual     |

| μPD31173 (V <sub>RC</sub> 4173) Data Sheet     | U15338E         |

| V <sub>R</sub> 4122 <sup>™</sup> User's Manual | U14327E         |

| μPD30122 (V <sub>R</sub> 4122) Data Sheet      | To be prepared  |

### **CONTENTS**

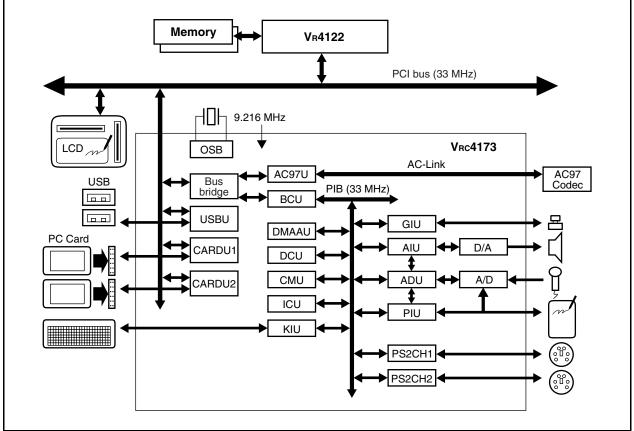

| CHAPTE | ER 1 OV  | /ERVIEW                                  | 25 |

|--------|----------|------------------------------------------|----|

| 1.1    | Featur   | res                                      | 25 |

| 1.2    |          | ing Information                          |    |

| 1.3    |          | al Block Configuration                   |    |

| 1.4    |          | evice Configuration                      |    |

| 1.5    |          | of Registers                             |    |

| СНАРТЕ | ER 2 PIN | N FUNCTIONS                              | 44 |

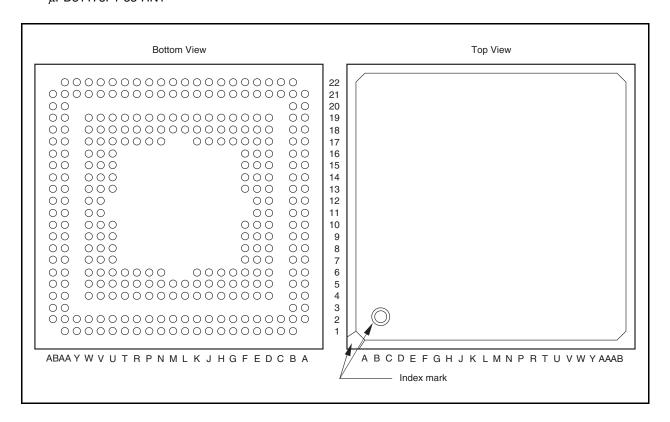

| 2.1    |          | onfiguration                             |    |

| 2.2    |          | inction Lists                            |    |

|        | 2.2.1    | PCI bus interface signals                | 50 |

|        | 2.2.2    | USB interface signals                    |    |

|        | 2.2.3    | AC-Link interface signals                | 50 |

|        | 2.2.4    | PC card interface signals                |    |

|        | 2.2.5    | Keyboard interface signals               | 54 |

|        | 2.2.6    | PS/2 interface signals                   | 54 |

|        | 2.2.7    | Touch panel interface signals            | 55 |

|        | 2.2.8    | Audio interface signal                   | 55 |

|        | 2.2.9    | General-purpose I/O signals              | 55 |

|        | 2.2.10   | Interrupt interface signal               | 56 |

|        | 2.2.11   | Clock interface signals                  | 56 |

|        | 2.2.12   | Test interface signals                   | 56 |

|        | 2.2.13   | Power supplies and grounds               | 57 |

| 2.3    | Pin Sta  | atus and Recommended Connection Examples | 58 |

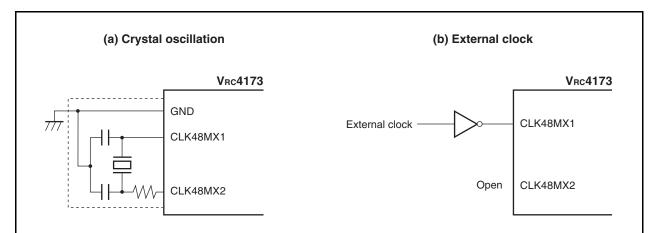

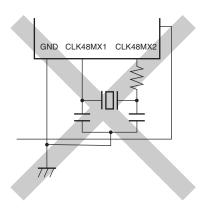

| 2.4    | Clock    | Oscillator Connection                    | 62 |

| CHAPTE | ER 3 BC  | CU (BUS CONTROL UNIT)                    | 64 |

| 3.1    |          | al                                       |    |

| 3.2    | Regist   | ter Set                                  | 64 |

|        | 3.2.1    | VID (offset address: 0x00 to 0x01)       | 65 |

|        | 3.2.2    | DID (offset address: 0x02 to 0x03)       | 65 |

|        | 3.2.3    | PCICMD (offset address: 0x04 to 0x05)    | 66 |

|        | 3.2.4    | PCISTS (offset address: 0x06 to 0x07)    | 67 |

|        | 3.2.5    | RID (offset address: 0x08)               | 68 |

|        | 3.2.6    | CLASSC (offset address: 0x09 to 0x0B)    | 68 |

|        | 3.2.7    | CACHELS (offset address: 0x0C)           | 68 |

|        | 3.2.8    | MLT (offset address: 0x0D)               | 69 |

|        | 3.2.9    | HEDT (offset address: 0x0E)              | 69 |

|        | 3.2.10   | BIST (offset address: 0x0F)              | 69 |

|        | 3.2.11   | BADR (offset address: 0x10 to 0x13)      | 70 |

|        | 3.2.12  | SUBVID (offset address: 0x2C to 0x2D) | 71 |

|--------|---------|---------------------------------------|----|

|        | 3.2.13  | SUBID (offset address: 0x2E to 0x2F)  | 71 |

|        | 3.2.14  | INTL (offset address: 0x3C)           | 72 |

|        | 3.2.15  | INTP (offset address: 0x3D)           | 72 |

|        | 3.2.16  | MIN_GNT (offset address: 0x3E)        | 72 |

|        | 3.2.17  | MAX_LAT (offset address: 0x3F)        | 73 |

|        | 3.2.18  | BUSCNT (offset address: 0x40)         | 73 |

|        | 3.2.19  | IDSELNUM (offset address: 0x41)       | 74 |

| CHAPTE | ER 4 DN | MAAU (DMA ADDRESS UNIT)               | 75 |

| 4.1    | Genera  | al                                    | 75 |

| 4.2    | Regist  | ter Set                               | 76 |

|        | 4.2.1   | AIU IN DMA base address registers     | 77 |

|        | 4.2.2   | AIU IN DMA address registers          | 78 |

|        | 4.2.3   | AIU OUT DMA base address registers    | 79 |

|        | 4.2.4   | AIU OUT DMA address registers         | 80 |

| CHAPTE | R 5 DC  | CU (DMA CONTROL UNIT)                 | 81 |

| 5.1    | Genera  | al                                    | 81 |

| 5.2    | DMA F   | Priority Control                      | 81 |

| 5.3    | Regist  | ter Set                               | 81 |

|        | 5.3.1   | DMARSTREG (base address + 0x020)      | 82 |

|        | 5.3.2   | DMAIDLEREG (base address + 0x022)     | 82 |

|        | 5.3.3   | DMASENREG (base address + 0x024)      | 83 |

|        | 5.3.4   | DMAMSKREG (base address + 0x026)      | 84 |

|        | 5.3.5   | DMAREQREG (base address + 0x028)      | 85 |

| CHAPTE | ER 6 CM | MU (CLOCK MASK UNIT)                  | 86 |

| 6.1    | Genera  | al                                    | 86 |

| 6.2    | Regist  | ter Set                               | 87 |

|        | 6.2.1   | CMUCLKMSK (base address + 0x040)      | 87 |

|        | 6.2.2   | CMUSRST (base address + 0x042)        | 89 |

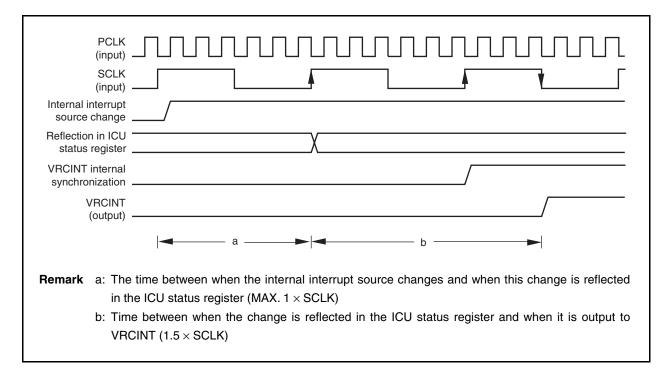

| CHAPTE | R 7 ICI | U (INTERRUPT CONTROL UNIT)            | 90 |

| 7.1    | Genera  | al                                    | 90 |

| 7.2    |         | ter Set                               |    |

|        | 7.2.1   | SYSINT1REG (base address + 0x060)     |    |

|        | 7.2.2   | PIUINTREG (base address + 0x062)      |    |

|        | 7.2.3   | AIUINTREG (base address + 0x064)      |    |

|        | 7.2.4   | KIUINTREG (base address + 0x066)      |    |

|        | 7.2.5   | GIULINTREG (base address + 0x068)     |    |

|        | 726     | GILIHINTREG (hase address + 0x06A)    |    |

|        | 7.2.7   | MSYSINT1REG (base address + 0x06C)                                     | 100 |

|--------|---------|------------------------------------------------------------------------|-----|

|        | 7.2.8   | MPIUINTREG (base address + 0x06E)                                      | 102 |

|        | 7.2.9   | MAIUINTREG (base address + 0x070)                                      | 103 |

|        | 7.2.10  | MKIUINTREG (base address + 0x072)                                      | 104 |

|        | 7.2.11  | MGIULINTREG (base address + 0x074)                                     | 105 |

|        | 7.2.12  | MGIUHINTREG (base address + 0x076)                                     | 105 |

| 7.3    | Notes   | for Register Setting                                                   | 106 |

| CHAPTE | R 8 GIL | U (GENERAL-PURPOSE I/O UNIT)                                           | 107 |

| 8.1    | Genera  | al                                                                     | 107 |

| 8.2    | Regist  | er Set                                                                 | 108 |

|        | 8.2.1   | GIUDIRL (base address + 0x080)                                         | 109 |

|        | 8.2.2   | GIUDIRH (base address + 0x082)                                         | 110 |

|        | 8.2.3   | GIUPIODL (base address + 0x084)                                        | 111 |

|        | 8.2.4   | GIUPIODH (base address + 0x086)                                        | 112 |

|        | 8.2.5   | GIUINTSTATL (base address + 0x088)                                     | 113 |

|        | 8.2.6   | GIUINTSTATH (base address + 0x08A)                                     | 114 |

|        | 8.2.7   | GIUINTENL (base address + 0x08C)                                       | 115 |

|        | 8.2.8   | GIUINTENH (base address + 0x08E)                                       | 115 |

|        | 8.2.9   | GIUINTTYPL (base address + 0x090)                                      | 116 |

|        | 8.2.10  | GIUINTTYPH (base address + 0x092)                                      | 117 |

|        | 8.2.11  | GIUINTALSELL (base address + 0x094)                                    | 118 |

|        | 8.2.12  | GIUINTALSELH (base address + 0x096)                                    | 119 |

|        | 8.2.13  | GIUINTHTSELL (base address + 0x098)                                    | 120 |

|        | 8.2.14  | GIUINTHTSELH (base address + 0x09A)                                    | 121 |

|        | 8.2.15  | SELECTREG (base address + 0x09E)                                       | 123 |

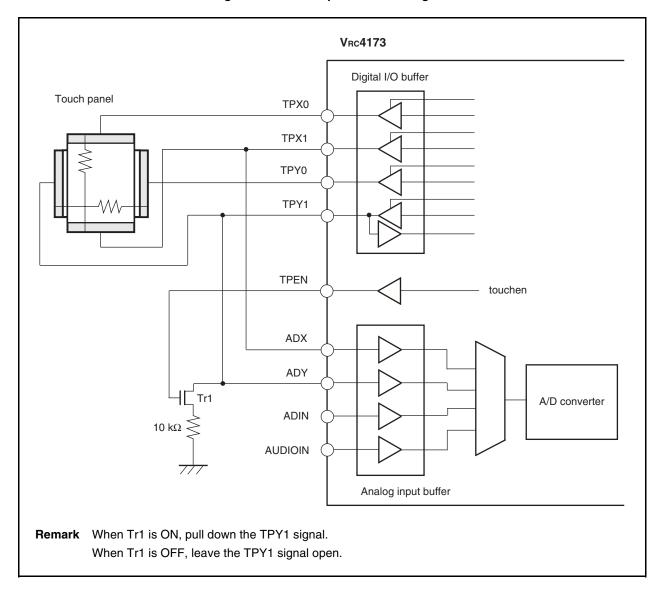

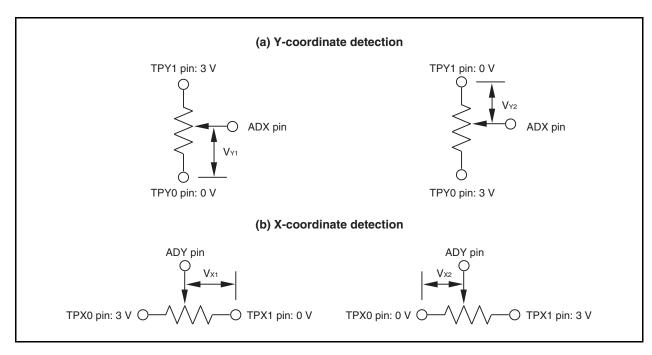

| СНАРТЕ | R 9 PIL | J (TOUCH PANEL INTERFACE UNIT)                                         | 125 |

| 9.1    | Genera  | al                                                                     | 125 |

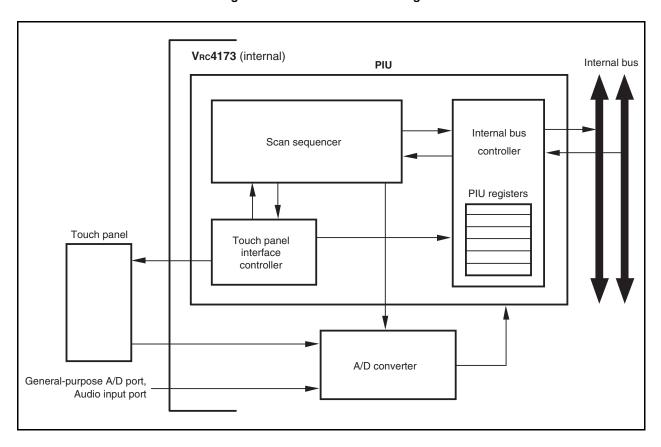

|        | 9.1.1   | Block diagrams                                                         | 126 |

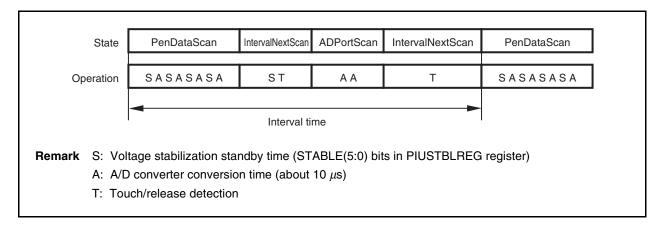

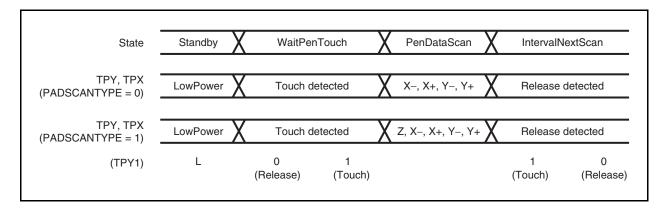

| 9.2    | Scan S  | Sequencer State Transition                                             |     |

| 9.3    |         | er Set                                                                 |     |

|        | 9.3.1   | PIUCNTREG (base address + 0x0A2)                                       | 132 |

|        | 9.3.2   | PIUINTREG (base address + 0x0A4)                                       | 135 |

|        | 9.3.3   | PIUSIVLREG (base address + 0x0A6)                                      | 136 |

|        | 9.3.4   | PIUSTBLREG (base address + 0x0A8)                                      | 137 |

|        | 9.3.5   | PIUCMDREG (base address + 0x0AA)                                       | 138 |

|        | 9.3.6   | PIUASCNREG (base address + 0x0B0)                                      | 139 |

|        | 9.3.7   | PIUAMSKREG (base address + 0x0B2)                                      |     |

|        | 9.3.8   | PIUCIVLREG (base address + 0x0BE)                                      |     |

|        | 9.3.9   | PIUPBnmREG (base address + 0x0C0 to base address + 0x0CE, base address |     |

|        |         | base address + 0x0DE)                                                  |     |

|        | 9.3.10  | PIUABnREG (base address + 0x0D0 to base address + 0x0D2)               |     |

| 9.4    | Status  | Transfer Flow                                                          |     |

| 9.5    | Relationships Among TPX, TPY, ADX, ADY, TPEN, ADIN, |                                                         |     |  |

|--------|-----------------------------------------------------|---------------------------------------------------------|-----|--|

|        |                                                     | JDIOIN Pins and States                                  |     |  |

| 9.6    | Timing                                              | ]                                                       | 149 |  |

|        | 9.6.1                                               | Touch/release detection timing                          | 149 |  |

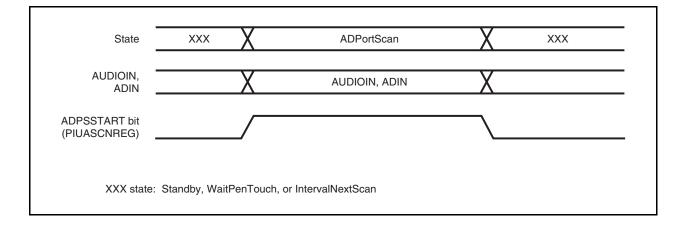

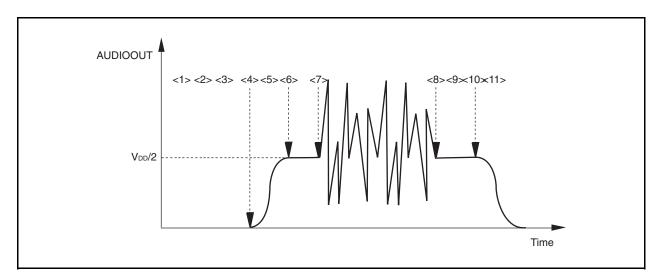

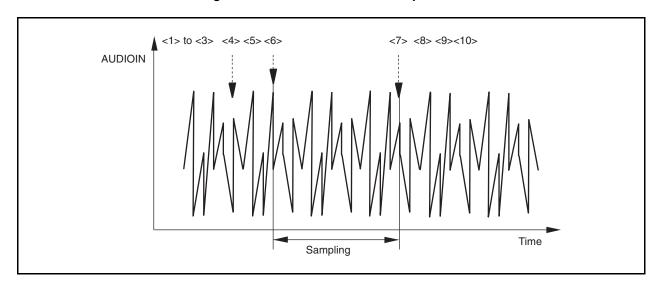

|        | 9.6.2                                               | A/D port scan timing                                    | 149 |  |

| 9.7    | Data Lo                                             | ost Generation Conditions                               | 150 |  |

| CHAPTE | R 10 A                                              | IU (AUDIO INTERFACE UNIT)                               | 152 |  |

| 10.1   | Genera                                              | al                                                      | 152 |  |

| 10.2   | Registe                                             | er Set                                                  | 152 |  |

|        | 10.2.1                                              | MDMADATREG (base address + 0x0E0)                       | 153 |  |

|        | 10.2.2                                              | SDMADATREG (base address + 0x0E2)                       | 153 |  |

|        | 10.2.3                                              | SODATREG (base address + 0x0E6)                         | 154 |  |

|        | 10.2.4                                              | SCNTREG (base address + 0x0E8)                          | 155 |  |

|        | 10.2.5                                              | SCNVRREG (base address + 0x0EA)                         | 156 |  |

|        | 10.2.6                                              | MIDATREG (base address + 0x0F0)                         | 157 |  |

|        | 10.2.7                                              | MCNTREG (base address + 0x0F2)                          | 158 |  |

|        | 10.2.8                                              | MCNVRREG (base address + 0x0F4)                         | 159 |  |

|        | 10.2.9                                              | DVALIDREG (base address + 0x0F8)                        | 160 |  |

|        | 10.2.10                                             | SEQREG (base address + 0x0FA)                           | 161 |  |

|        | 10.2.11                                             | INTREG (base address + 0x0FC)                           | 162 |  |

| 10.3   | Operat                                              | tion Sequence                                           | 163 |  |

|        | 10.3.1                                              | Output (Speaker)                                        | 163 |  |

|        | 10.3.2                                              | Input (MIC)                                             | 165 |  |

| CHAPTE | R 11 K                                              | IU (KEYBOARD INTERFACE UNIT)                            | 166 |  |

| 11.1   | Genera                                              | al                                                      | 166 |  |

| 11.2   |                                                     | er Set                                                  |     |  |

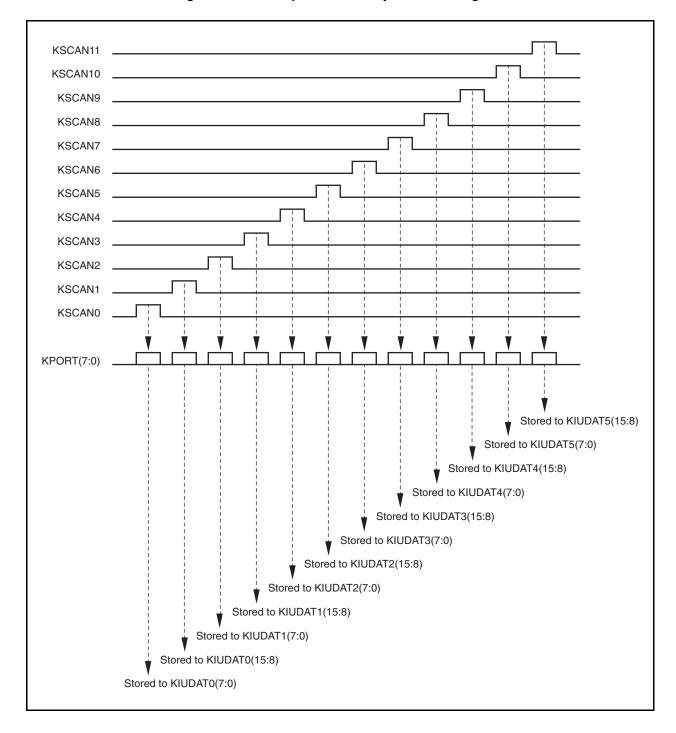

|        | •                                                   | KIUDATn (base address + 0x100 to base address + 0x10A)  |     |  |

|        | 11.2.2                                              | KIUSCANREP (base address + 0x110)                       |     |  |

|        | 11.2.3                                              | KIUSCANS (base address + 0x112)                         |     |  |

|        | 11.2.4                                              | KIUWKS (base address + 0x114)                           |     |  |

|        | 11.2.5                                              | KIUWKI (base address + 0x116)                           |     |  |

|        | 11.2.6                                              | KIUINT (base address + 0x118)                           |     |  |

|        | 11.2.7                                              | KIURST (base address + 0x11A)                           |     |  |

|        | 11.2.8                                              | SCANLINE (base address + 0x11E)                         |     |  |

| CHAPTE | R 12 P                                              | S2U (PS/2 UNIT)                                         | 182 |  |

| 12.1   |                                                     | al                                                      |     |  |

| 12.1   |                                                     | er Set                                                  |     |  |

|        | 12.2.1                                              | PS2CHnDATA (base address + 0x120, base address + 0x140) |     |  |

|        | 12.2.2                                              | PS2CHnCTRL (base address + 0x122, base address + 0x142) |     |  |

|        | 12.2.2                                              | PS2CHnRST (base address + 0x124, base address + 0x144)  |     |  |

| 12.3   | Transm  | nission Procedure                       | 186 |

|--------|---------|-----------------------------------------|-----|

| СНАРТЕ | R 13 C  | ARDU1, CARDU2 (PC CARD UNITS)           | 187 |

| 13.1   | Genera  | 1                                       | 187 |

| 13.2   |         | uration Register Set                    |     |

|        | 13.2.1  | VID (offset address: 0x00 to 0x01)      | 190 |

|        | 13.2.2  | DID (offset address: 0x02 to 0x03)      | 190 |

|        | 13.2.3  | PCICMD (offset address: 0x04 to 0x05)   | 191 |

|        | 13.2.4  | PCISTS (offset address: 0x06 to 0x07)   | 193 |

|        | 13.2.5  | RID (offset address: 0x08)              | 194 |

|        | 13.2.6  | CLASSC (offset address: 0x09 to 0x0B)   | 194 |

|        | 13.2.7  | CACHELS (offset address: 0x0C)          | 194 |

|        | 13.2.8  | MLT (offset address: 0x0D)              | 195 |

|        | 13.2.9  | HEDT (offset address: 0x0E)             | 195 |

|        | 13.2.10 | BIST (offset address: 0x0F)             | 195 |

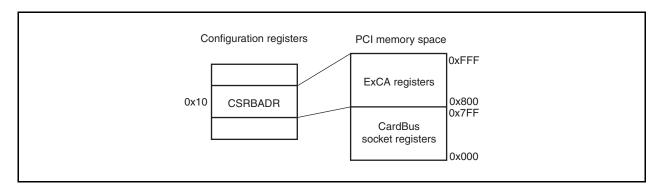

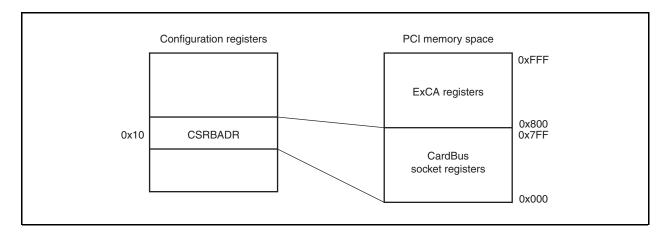

|        | 13.2.11 | CSRBADR (offset address: 0x10 to 0x13)  | 196 |

|        | 13.2.12 | CAP (offset address: 0x14)              | 196 |

|        | 13.2.13 | SECSTS (offset address: 0x16 to 0x17)   | 197 |

|        | 13.2.14 | PCIBNUM (offset address: 0x18)          | 198 |

|        | 13.2.15 | CARDNUM (offset address: 0x19)          | 198 |

|        | 13.2.16 | SUBBNUM (offset address: 0x1A)          | 198 |

|        | 13.2.17 | CLT (offset address: 0x1B)              | 199 |

|        | 13.2.18 | MEMB0 (offset address: 0x1C to 0x1F)    | 200 |

|        | 13.2.19 | MEML0 (offset address: 0x20 to 0x23)    | 201 |

|        | 13.2.20 | MEMB1 (offset address: 0x24 to 0x27)    | 202 |

|        | 13.2.21 | MEML1 (offset address: 0x28 to 0x2B)    | 203 |

|        | 13.2.22 | IOB0 (offset address: 0x2C to 0x2F)     | 204 |

|        | 13.2.23 | IOL0 (offset address: 0x30 to 0x33)     | 205 |

|        | 13.2.24 | IOB1 (offset address: 0x34 to 0x37)     | 206 |

|        | 13.2.25 | IOL1 (offset address: 0x38 to 0x3B)     | 207 |

|        | 13.2.26 | INTL (offset address: 0x3C)             | 207 |

|        | 13.2.27 | INTP (offset address: 0x3D)             | 208 |

|        | 13.2.28 | BRGCNT (offset address: 0x3E to 0x3F)   | 208 |

|        | 13.2.29 | SUBVID (offset address: 0x40 to 0x41)   | 210 |

|        | 13.2.30 | SUBID (offset address: 0x42 to 0x43)    | 210 |

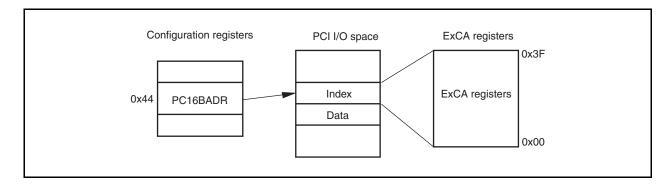

|        | 13.2.31 | PC16BADR (offset address: 0x44 to 0x47) | 211 |

|        | 13.2.32 | SYSCNT (offset address: 0x80 to 0x83)   | 212 |

|        | 13.2.33 | DEVCNT (offset address: 0x91)           | 213 |

|        | 13.2.34 | SKDMA0 (offset address: 0x94 to 0x97)   | 214 |

|        | 13.2.35 | SKDMA1 (offset address: 0x98 to 0x9B)   | 215 |

|        | 13.2.36 | CHIPCNT (offset address: 0x9C)          | 216 |

|        | 13.2.37 | SERRDIS (offset address: 0x9F)          | 216 |

|        | 13.2.38 | CAPID (offset address: 0xA0)            | 217 |

|        | 13.2.39 | NIP (offset address: 0xA1)              | 217 |

|      | 13.2.40 | PMC (offset address: 0xA2 to 0xA3)                                  | 218 |

|------|---------|---------------------------------------------------------------------|-----|

|      | 13.2.41 | PMCSR (offset address: 0xA4 to 0xA5)                                | 219 |

|      | 13.2.42 | PMCSR_BSE (offset address: 0xA6)                                    | 219 |

|      | 13.2.43 | DATA (offset address: 0xA7)                                         | 220 |

|      | 13.2.44 | TEST (offset address: 0xFC)                                         | 220 |

| 13.3 | ExCA R  | egister Set                                                         | 221 |

|      | 13.3.1  | ID_REV (PCI offset address: 0x800, ExCA offset address: 0x00)       | 226 |

|      | 13.3.2  | IF_STATUS (PCI offset address: 0x801, ExCA offset address: 0x01)    | 227 |

|      | 13.3.3  | PWR_CNT (PCI offset address: 0x802, ExCA offset address: 0x02)      | 228 |

|      | 13.3.4  | INT_GEN_CNT (PCI offset address: 0x803, ExCA offset address: 0x03)  | 229 |

|      | 13.3.5  | CARD_SC (PCI offset address: 0x804, ExCA offset address: 0x04)      | 230 |

|      | 13.3.6  | CARD_SCI (PCI offset address: 0x805, ExCA offset address: 0x05)     | 231 |

|      | 13.3.7  | ADR_WIN_EN (PCI offset address: 0x806, ExCA offset address: 0x06)   | 232 |

|      | 13.3.8  | IO_WIN_CNT (PCI offset address: 0x807, ExCA offset address: 0x07)   | 233 |

|      | 13.3.9  | IO_WIN0_SAL (PCI offset address: 0x808, ExCA offset address: 0x08)  | 233 |

|      | 13.3.10 | IO_WIN0_SAH (PCI offset address: 0x809, ExCA offset address: 0x09)  | 234 |

|      | 13.3.11 | IO_WINO_EAL (PCI offset address: 0x80A, ExCA offset address: 0x0A)  | 234 |

|      | 13.3.12 | IO_WIN0_EAH (PCI offset address: 0x80B, ExCA offset address: 0x0B)  | 234 |

|      | 13.3.13 | IO_WIN1_SAL (PCI offset address: 0x80C, ExCA offset address: 0x0C)  | 235 |

|      | 13.3.14 | IO_WIN1_SAH (PCI offset address: 0x80D, ExCA offset address: 0x0D)  | 235 |

|      | 13.3.15 | IO_WIN1_EAL (PCI offset address: 0x80E, ExCA offset address: 0x0E)  | 235 |

|      | 13.3.16 | IO_WIN1_EAH (PCI offset address: 0x80F, ExCA offset address: 0x0F)  | 236 |

|      | 13.3.17 | MEM_WIN0_SAL (PCI offset address: 0x810, ExCA offset address: 0x10) | 236 |

|      | 13.3.18 | MEM_WIN0_SAH (PCI offset address: 0x811, ExCA offset address: 0x11) | 236 |

|      | 13.3.19 | MEM_WIN0_EAL (PCI offset address: 0x812, ExCA offset address: 0x12) | 237 |

|      | 13.3.20 | MEM_WINO_EAH (PCI offset address: 0x813, ExCA offset address: 0x13) | 237 |

|      | 13.3.21 | MEM_WIN0_OAL (PCI offset address: 0x814, ExCA offset address: 0x14) | 237 |

|      | 13.3.22 | MEM_WIN0_OAH (PCI offset address: 0x815, ExCA offset address: 0x15) | 238 |

|      | 13.3.23 | GEN_CNT (PCI offset address: 0x816, ExCA offset address: 0x16)      | 238 |

|      | 13.3.24 | MEM_WIN1_SAL (PCI offset address: 0x818, ExCA offset address: 0x18) | 239 |

|      | 13.3.25 | MEM_WIN1_SAH (PCI offset address: 0x819, ExCA offset address: 0x19) | 239 |

|      | 13.3.26 | MEM_WIN1_EAL (PCI offset address: 0x81A, ExCA offset address: 0x1A) | 239 |

|      | 13.3.27 | MEM_WIN1_EAH (PCI offset address: 0x81B, ExCA offset address: 0x1B) | 240 |

|      | 13.3.28 | MEM_WIN1_OAL (PCI offset address: 0x81C, ExCA offset address: 0x1C) | 240 |

|      | 13.3.29 | MEM_WIN1_OAH (PCI offset address: 0x81D, ExCA offset address: 0x1D) | 240 |

|      | 13.3.30 | GLO_CNT (PCI offset address: 0x81E, ExCA offset address: 0x1E)      | 241 |

|      | 13.3.31 | MEM_WIN2_SAL (PCI offset address: 0x820, ExCA offset address: 0x20) | 241 |

|      | 13.3.32 | MEM_WIN2_SAH (PCI offset address: 0x821, ExCA offset address: 0x21) | 242 |

|      | 13.3.33 | MEM_WIN2_EAL (PCI offset address: 0x822, ExCA offset address: 0x22) | 242 |

|      | 13.3.34 | MEM_WIN2_EAH (PCI offset address: 0x823, ExCA offset address: 0x23) | 242 |

|      | 13.3.35 | MEM_WIN2_OAL (PCI offset address: 0x824, ExCA offset address: 0x24) | 243 |

|      | 13.3.36 | MEM_WIN2_OAH (PCI offset address: 0x825, ExCA offset address: 0x25) | 243 |

|      | 13.3.37 | MEM_WIN3_SAL (PCI offset address: 0x828, ExCA offset address: 0x28) | 243 |

|      | 13.3.38 | MEM_WIN3_SAH (PCI offset address: 0x829, ExCA offset address: 0x29) | 244 |

|      | 13.3.39 | MEM_WIN3_EAL (PCI offset address: 0x82A, ExCA offset address: 0x2A) | 244 |

|      | 13.3.40 | MEM_WIN3_EAH (PCI offset address: 0x82B, ExCA offset address: 0x2B)            | 244 |

|------|---------|--------------------------------------------------------------------------------|-----|

|      | 13.3.41 | MEM_WIN3_OAL (PCI offset address: 0x82C, ExCA offset address: 0x2C)            | 245 |

|      | 13.3.42 | MEM_WIN3_OAH (PCI offset address: 0x82D, ExCA offset address: 0x2D)            | 245 |

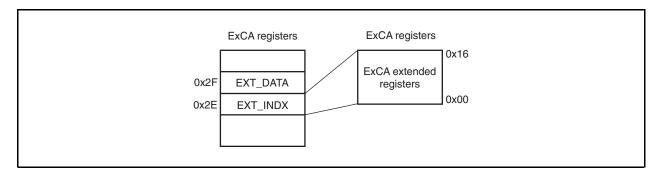

|      | 13.3.43 | EXT_INDX (ExCA offset address: 0x2E)                                           | 245 |

|      | 13.3.44 | EXT_DATA (ExCA offset address: 0x2F)                                           | 246 |

|      | 13.3.45 | MEM_WIN4_SAL (PCI offset address: 0x830, ExCA offset address: 0x30)            | 246 |

|      | 13.3.46 | MEM_WIN4_SAH (PCI offset address: 0x831, ExCA offset address: 0x31)            | 246 |

|      | 13.3.47 | MEM_WIN4_EAL (PCI offset address: 0x832, ExCA offset address: 0x32)            | 247 |

|      | 13.3.48 | MEM_WIN4_EAH (PCI offset address: 0x833, ExCA offset address: 0x33)            | 247 |

|      | 13.3.49 | MEM_WIN4_OAL (PCI offset address: 0x834, ExCA offset address: 0x34)            | 247 |

|      | 13.3.50 | MEM_WIN4_OAH (PCI offset address: 0x835, ExCA offset address: 0x35)            | 248 |

|      | 13.3.51 | IO_WIN0_OAL (PCI offset address: 0x836, ExCA offset address: 0x36)             | 248 |

|      | 13.3.52 | IO_WIN0_OAH (PCI offset address: 0x837, ExCA offset address: 0x37)             | 248 |

|      | 13.3.53 | IO_WIN1_OAL (PCI offset address: 0x838, ExCA offset address: 0x38)             | 249 |

|      | 13.3.54 | IO_WIN1_OAH (PCI offset address: 0x839, ExCA offset address: 0x39)             | 249 |

|      | 13.3.55 | MEM_WIN0_SAU (PCI offset address: 0x840, ExCA extended offset address: 0x00)   | 249 |

|      | 13.3.56 | MEM_WIN1_SAU (PCI offset address: 0x841, ExCA extended offset address: 0x01)   | 250 |

|      | 13.3.57 | MEM_WIN2_SAU (PCI offset address: 0x842, ExCA extended offset address: 0x02)   | 250 |

|      | 13.3.58 | MEM_WIN3_SAU (PCI offset address: 0x843, ExCA extended offset address: 0x03)   | 250 |

|      | 13.3.59 | MEM_WIN4_SAU (PCI offset address: 0x844, ExCA extended offset address: 0x04)   | 251 |

|      | 13.3.60 | IO_SETUP_TIM (PCI offset address: 0x880, ExCA extended offset address: 0x05)   | 251 |

|      | 13.3.61 | IO_CMD_TIM (PCI offset address: 0x881, ExCA extended offset address: 0x06)     | 252 |

|      | 13.3.62 | IO_HOLD_TIM (PCI offset address: 0x882, ExCA extended offset address: 0x07)    | 252 |

|      | 13.3.63 | MEM0_SETUP_TIM (PCI offset address: 0x884, ExCA extended offset address: 0x09) | 253 |

|      | 13.3.64 | MEM0_CMD_TIM (PCI offset address: 0x885, ExCA extended offset address: 0x0A)   | 253 |

|      | 13.3.65 | MEM0_HOLD_TIM (PCI offset address: 0x886, ExCA extended offset address: 0x0B)  | 254 |

|      | 13.3.66 | MEM1_SETUP_TIM (PCI offset address: 0x888, ExCA extended offset address: 0x0D) | 254 |

|      | 13.3.67 | MEM1_CMD_TIM (PCI offset address: 0x889, ExCA extended offset address: 0x0E)   | 255 |

|      | 13.3.68 | MEM1_HOLD_TIM (PCI offset address: 0x88A, ExCA extended offset address: 0x0F)  | 255 |

|      | 13.3.69 | MEM_TIM_SEL1 (PCI offset address: 0x88C, ExCA extended offset address: 0x11)   | 256 |

|      | 13.3.70 | MEM_TIM_SEL2 (PCI offset address: 0x88D, ExCA extended offset address: 0x12)   | 256 |

|      | 13.3.71 | MEM_WIN_PWEN (PCI offset address: 0x891, ExCA extended offset address: 0x16)   |     |

| 13.4 | CardBu  | s Socket Register Set                                                          | 258 |

|      | 13.4.1  | SKT_EV (offset address: 0x000)                                                 | 259 |

|      | 13.4.2  | SKT_MASK (offset address: 0x004)                                               | 261 |

|      | 13.4.3  | SKT_PRE_STATE (offset address: 0x008)                                          | 262 |

|      | 13.4.4  | SKT_FORCE_EV (offset address: 0x00C)                                           | 264 |

|      | 13.4.5  | SKT_CNT (offset address: 0x010)                                                |     |

| 13.5 |         | I Unit Operation                                                               |     |

|      | 13.5.1  | 16-bit PC card support                                                         |     |

|      | 13.5.2  | Interrupts                                                                     |     |

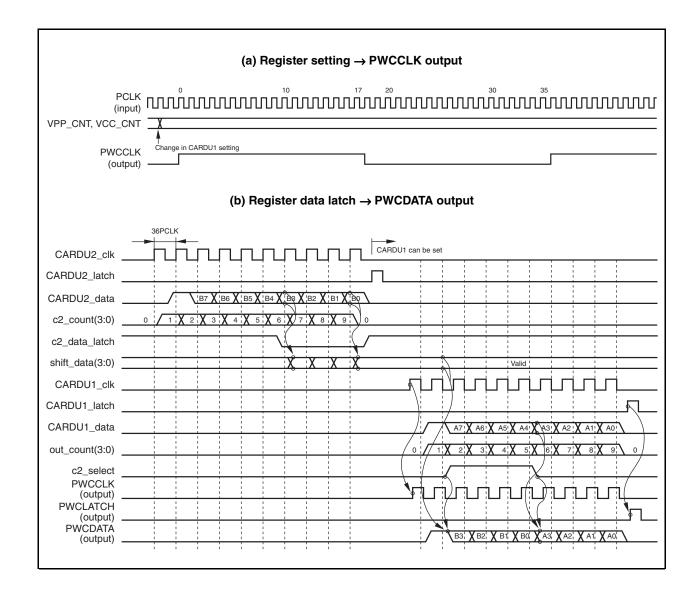

|      | 13.5.3  | Power supply interface                                                         | 271 |

|      |         |                                                                                |     |

CHAPTER 14 USBU (UNIVERSAL SERIAL BUS UNIT).....274

| 14.1 | Feature | es                                               | 274 |

|------|---------|--------------------------------------------------|-----|

| 14.2 | USB Ho  | ost Control Configuration Registers              | 275 |

|      | 14.2.1  | Register set                                     | 276 |

|      | 14.2.2  | Command register (offset address: 0x04)          | 277 |

|      | 14.2.3  | Status register (offset address: 0x06)           | 278 |

|      | 14.2.4  | Base address register (offset address: 0x10)     | 279 |

|      | 14.2.5  | Power management register (offset address: 0xE0) | 280 |

| 14.3 | Operati | onal Registers                                   | 282 |

|      | 14.3.1  | Register set                                     | 282 |

|      | 14.3.2  | HcRevision (offset address: 0x00)                | 283 |

|      | 14.3.3  | HcControl (offset address: 0x04)                 | 284 |

|      | 14.3.4  | HcCommandStatus (offset address: 0x08)           | 286 |

|      | 14.3.5  | HcInterruptStatus (offset address: 0x0C)         | 288 |

|      | 14.3.6  | HcInterruptEnable (offset address: 0x10)         | 290 |

|      | 14.3.7  | HcInterruptDisable (offset address: 0x14)        | 292 |

|      | 14.3.8  | HcHCCA (offset address: 0x18)                    | 294 |

|      | 14.3.9  | HcPeriodCurrentED (offset address: 0x1C)         | 295 |

|      | 14.3.10 | HcControlHeadED (offset address: 0x20)           | 296 |

|      | 14.3.11 | HcControlCurrentED (offset address: 0x24)        | 297 |

|      | 14.3.12 | HcBulkHeadED (offset address: 0x28)              | 298 |

|      | 14.3.13 | HcBulkCurrentED (offset address: 0x2C)           | 299 |

|      | 14.3.14 | HcDoneHead (offset address: 0x30)                | 300 |

|      | 14.3.15 | HcFmInterval (offset address: 0x34)              | 301 |

|      | 14.3.16 | HcFmRemaining (offset address: 0x38)             | 302 |

|      | 14.3.17 | HcFmNumber (offset address: 0x3C)                | 303 |

|      | 14.3.18 | HcPeriodicStart (offset address: 0x40)           | 304 |

|      | 14.3.19 | HcLSThreshold (offset address: 0x44)             | 305 |

|      | 14.3.20 | HcRhDescriptorA (offset address: 0x48)           | 306 |

|      | 14.3.21 | HcRhDescriptorB (offset address: 0x4C)           | 308 |

|      | 14.3.22 | HcRhStatus (offset address: 0x50)                | 310 |

|      | 14.3.23 | HcRhPortStatus1, 2 (offset address: 0x54, 0x58)  | 312 |

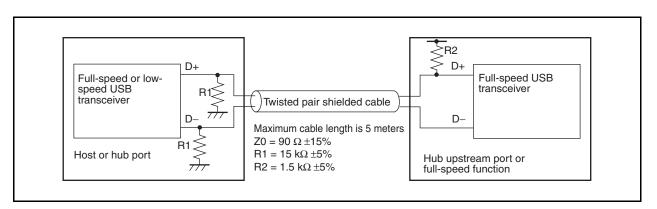

| 14.4 | USB Sp  | pecifications                                    | 316 |

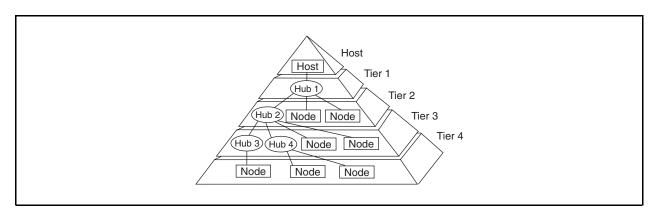

|      | 14.4.1  | General                                          | 316 |

|      | 14.4.2  | Host controller communication methods            | 318 |

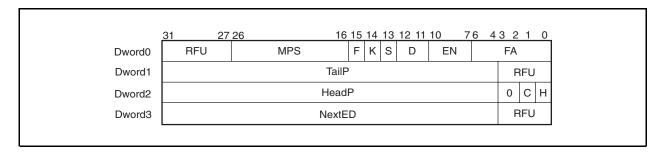

|      | 14.4.3  | ED (Endpoint Descriptor)                         | 321 |

|      | 14.4.4  | ED format                                        | 321 |

|      | 14.4.5  | ED fields                                        | 322 |

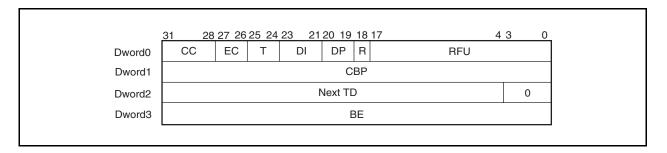

|      | 14.4.6  | TD (Transfer Descriptor)                         | 323 |

|      | 14.4.7  | GeneralTD format                                 | 323 |

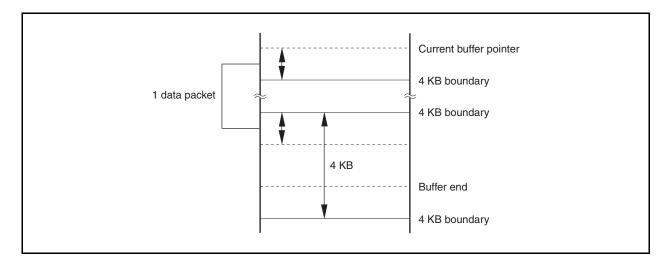

|      | 14.4.8  | GeneralTD fields                                 | 324 |

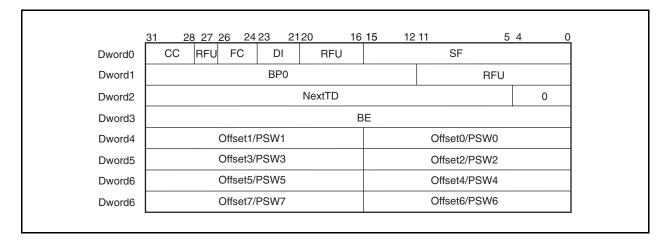

|      | 14.4.9  | IsochronousTD format                             | 326 |

|      | 14.4.10 | IsochronousTD fields                             | 327 |

|      | 14.4.11 | HCCA (Host Controller Communication Area)        | 327 |

|      | 14.4.12 | HCCA format                                      | 328 |

|      | 14.4.13 | HCCA overview                                    | 328 |

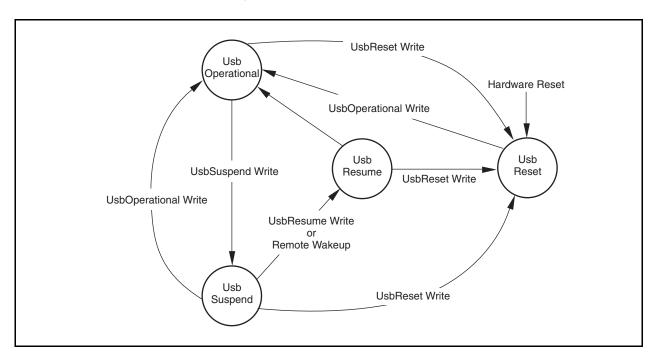

|        | 14.4.14 | HC state transitions                      | 329 |

|--------|---------|-------------------------------------------|-----|

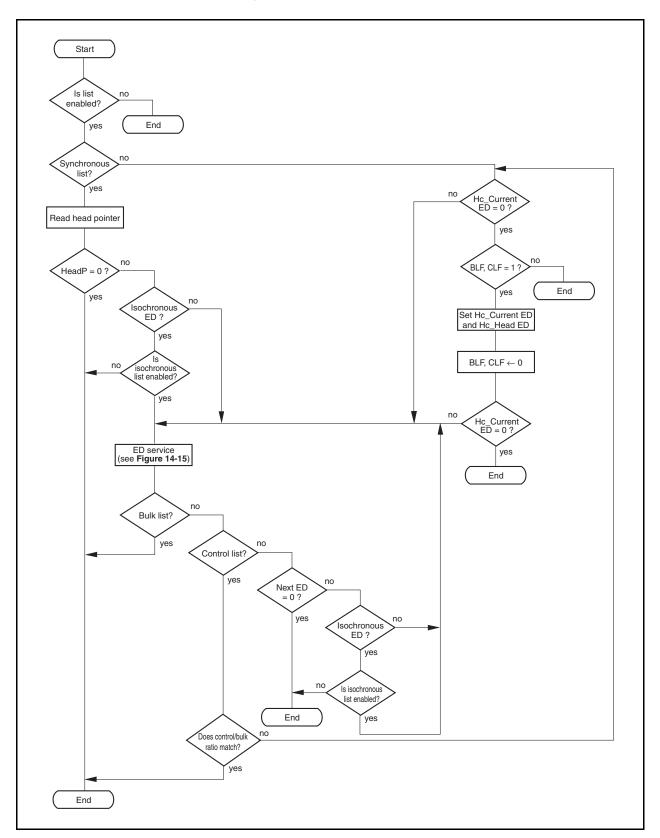

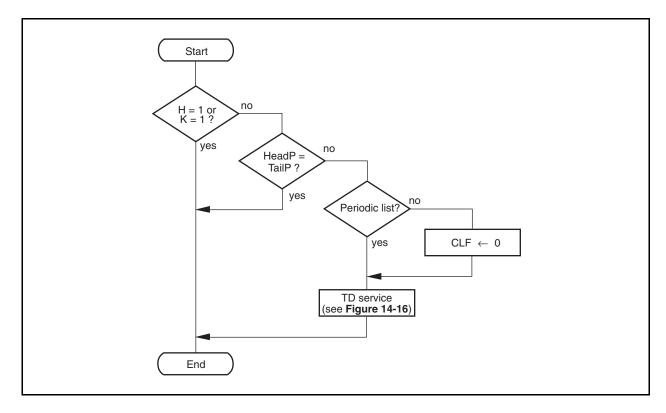

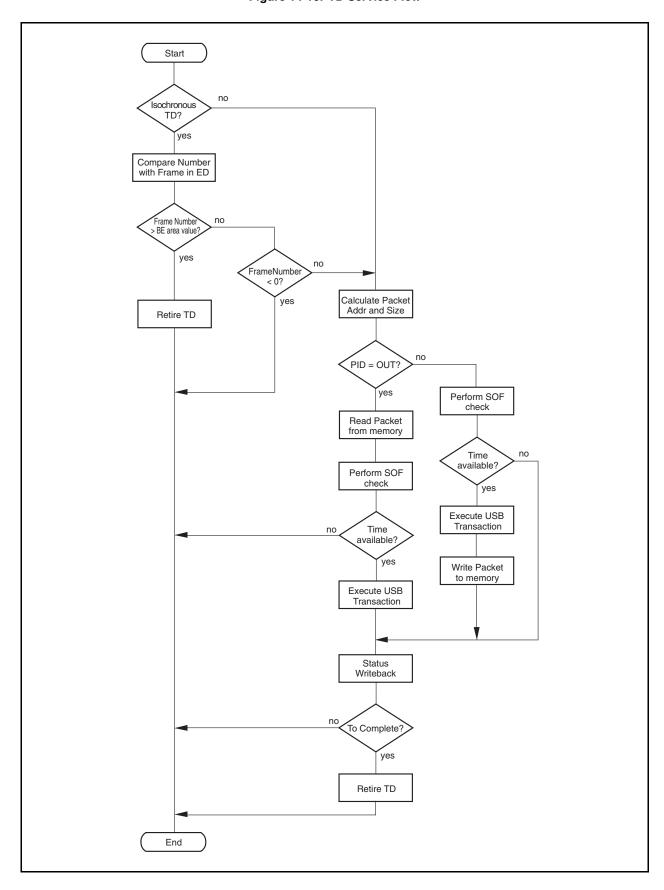

|        | 14.4.15 | List service flow                         | 330 |

|        |         |                                           |     |

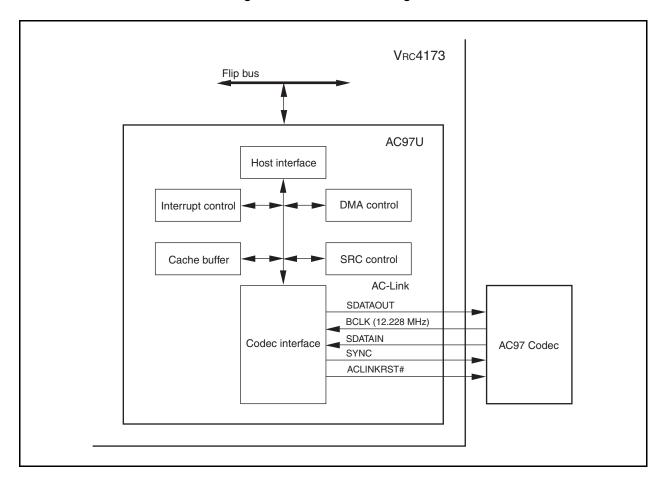

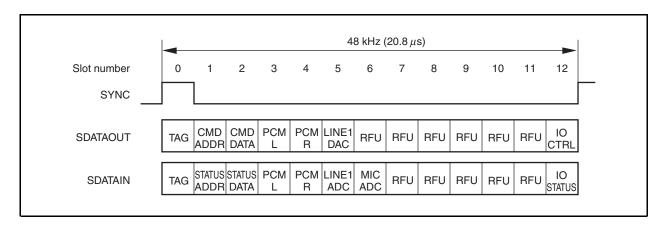

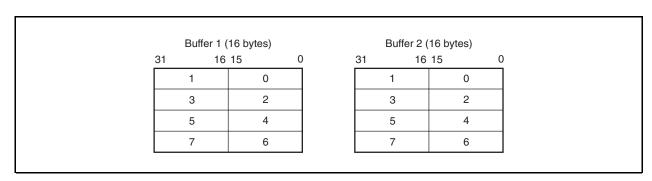

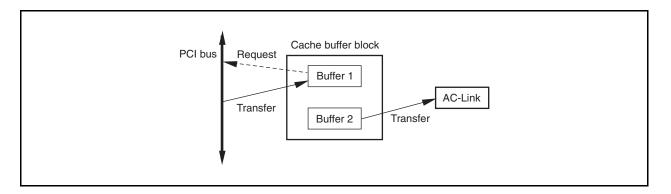

| CHAPTE | R 15 AC | C97U (AC97 UNIT)                          | 336 |

| 15.1   | Genera  | ıl                                        | 336 |

| 15.2   |         | uration Register Set                      |     |

|        | 15.2.1  | VID (offset address: 0x00 to 0x01)        |     |

|        | 15.2.2  | DID (offset address: 0x02 to 0x03)        |     |

|        | 15.2.3  | PCICMD (offset address: 0x04 to 0x05)     |     |

|        | 15.2.4  | PCISTS (offset address: 0x06 to 0x07)     |     |

|        | 15.2.5  | RID (offset address: 0x08)                |     |

|        | 15.2.6  | CLASSC (offset address: 0x09 to 0x0B)     | 340 |

|        | 15.2.7  | CACHELS (offset address: 0x0C)            | 340 |

|        | 15.2.8  | MLT (offset address: 0x0D)                | 341 |

|        | 15.2.9  | HEDT (offset address: 0x0E)               | 341 |

|        | 15.2.10 | BIST (offset address: 0x0F)               | 341 |

|        | 15.2.11 | BASEADR (offset address: 0x10 to 0x13)    | 342 |

|        | 15.2.12 | SVID (offset address: 0x2C to 0x2D)       | 343 |

|        | 15.2.13 | SUBID (offset address: 0x2E to 0x2F)      | 343 |

|        | 15.2.14 | EXROMADR (offset address: 0x30 to 0x33)   | 344 |

|        | 15.2.15 | INTL (offset address: 0x3C)               | 344 |

|        | 15.2.16 | INTP (offset address: 0x3D)               | 345 |

|        | 15.2.17 | MIN_GNT (offset address: 0x3E)            | 345 |

|        | 15.2.18 | MAX_LAT (offset address: 0x3F)            | 345 |

| 15.3   | Operati | ional Register Set                        | 346 |

|        | 15.3.1  | INT_CLR/INT_STATUS (offset address: 0x00) | 347 |

|        | 15.3.2  | CODEC_WR (offset address: 0x04)           | 349 |

|        | 15.3.3  | CODEC_RD (offset address: 0x08)           | 350 |

|        | 15.3.4  | CODEC_REQ (offset address: 0x0C)          | 351 |

|        | 15.3.5  | SLOT12_WR (offset address: 0x10)          | 352 |

|        | 15.3.6  | SLOT12_RD (offset address: 0x14)          | 353 |

|        | 15.3.7  | CTRL (offset address: 0x18)               | 354 |

|        | 15.3.8  | ACLINK_CTRL (offset address: 0x1C)        | 356 |

|        | 15.3.9  | SRC_RAM_DATA (offset address: 0x20)       | 358 |

|        | 15.3.10 | INT_MASK (offset address: 0x24)           | 359 |

|        | 15.3.11 | DAC1_CTRL (offset address: 0x30)          | 361 |

|        | 15.3.12 | DAC1L (offset address: 0x34)              | 362 |

|        | 15.3.13 | DAC1_BADDR (offset address: 0x38)         | 363 |

|        | 15.3.14 | DAC2_CTRL (offset address: 0x3C)          | 364 |

|        | 15.3.15 | DAC2L (offset address: 0x40)              | 365 |

|        | 15.3.16 | DAC2_BADDR (offset address: 0x44)         | 366 |

|        | 15.3.17 | DAC3_CTRL (offset address: 0x48)          | 367 |

|        | 15.3.18 | DAC3L (offset address: 0x4C)              | 368 |

|        | 15.3.19 | DAC3_BADDR (offset address: 0x50)         | 369 |

|                                                                          | 15.3.21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADC1L (offset address: 0x58)                                                                                                                                                                                                                                                                                                                 | 371                      |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.12012 (011001 addirect)                                                                                                                                                                                                                                                                                                                    |                          |

|                                                                          | 15.3.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADC1_BADDR (offset address: 0x5C)                                                                                                                                                                                                                                                                                                            | 372                      |

|                                                                          | 15.3.23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADC2_CTRL (offset address: 0x60)                                                                                                                                                                                                                                                                                                             | 373                      |

|                                                                          | 15.3.24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADC2L (offset address: 0x64)                                                                                                                                                                                                                                                                                                                 | 374                      |

|                                                                          | 15.3.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADC2_BADDR (offset address: 0x68)                                                                                                                                                                                                                                                                                                            | 375                      |

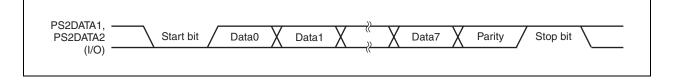

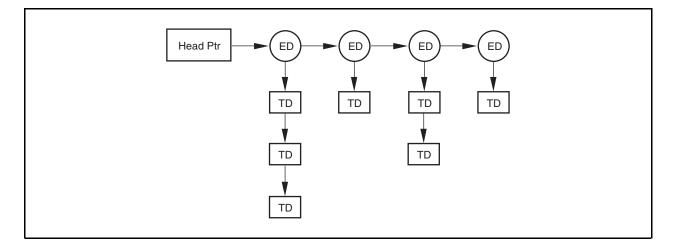

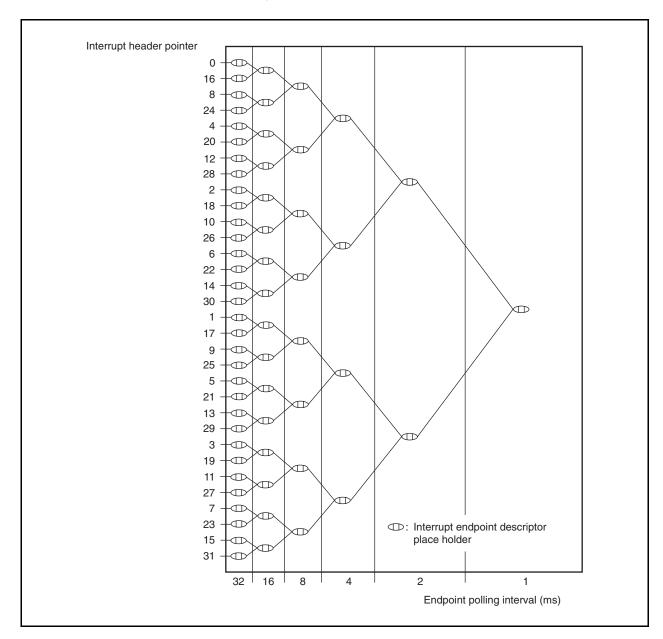

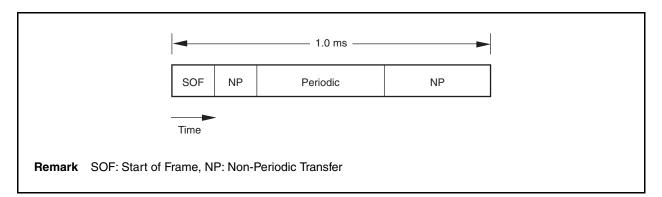

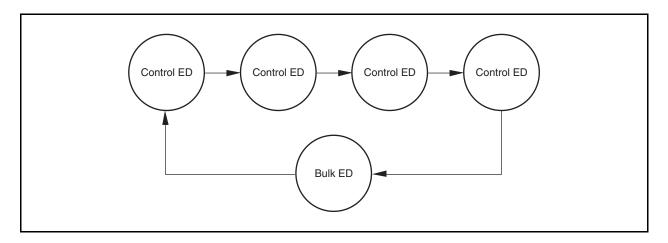

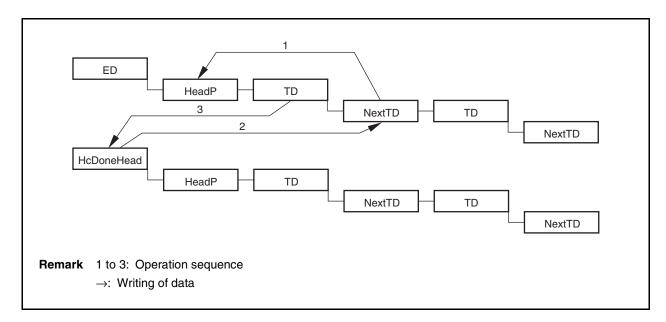

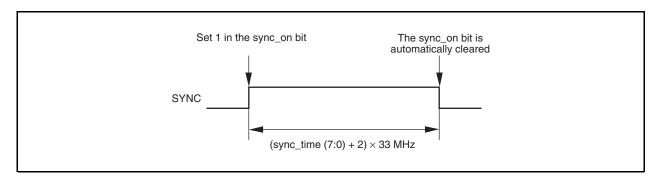

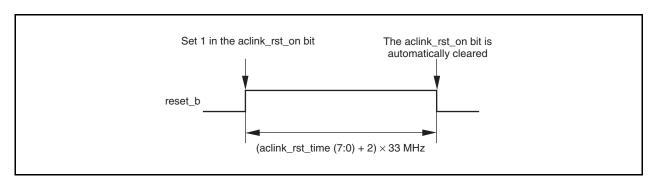

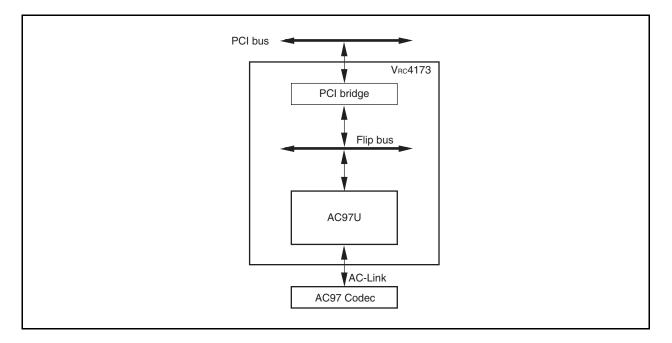

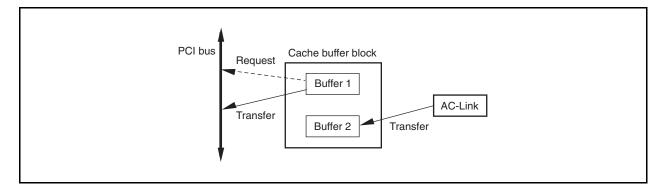

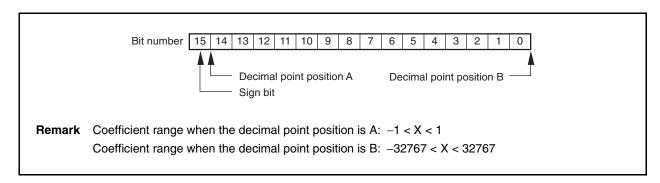

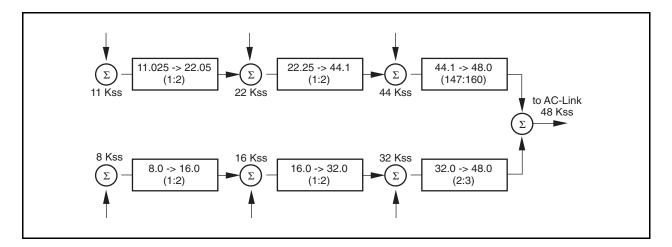

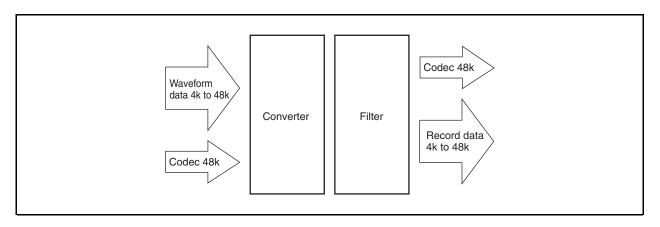

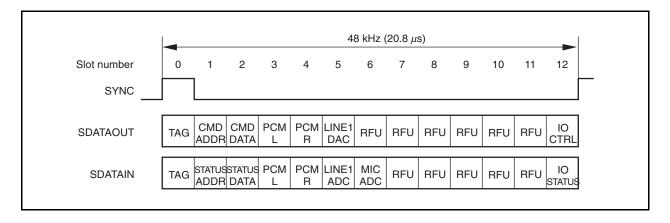

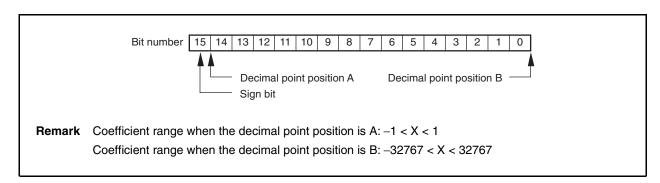

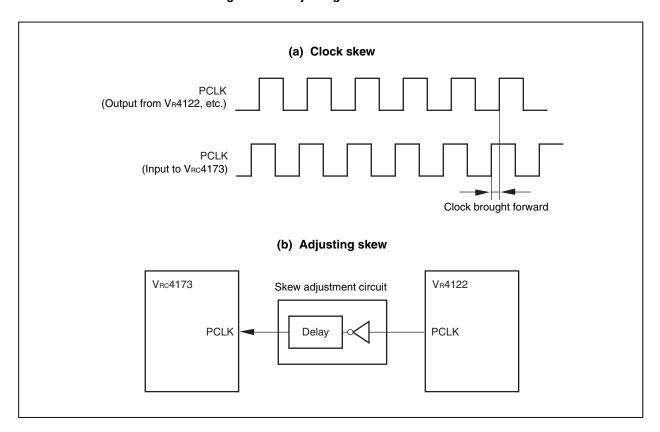

|                                                                          | 15.3.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADC3_CTRL (offset address: 0x6C)                                                                                                                                                                                                                                                                                                             | 376                      |