## NEC

## **VRC4375 System Controller**

Data Sheet August 2000

### **Description**

The VRC4375™ system controller is a software-configurable chip that interfaces directly with an NEC VR43xx™ 64-bit MIPS® RISC CPU and PCI bus without external logic or buffering. The system controller also interfaces with memory (SDRAM, EDO, fast-page DRAM, and flash/boot ROM) with minimal to no buffering. The memory bus can also interface with SRAM and general-purpose I/O devices. As an interface with the VR43xx CPU, the VRC4375 acts as a memory controller, DMA controller, and PCI bridge. As an interface with PCI agents, the VRC4375 acts as either a PCI bus master or a PCI bus target. Alternatively, the VRC4375 may be located on a PCI bus add-on board.

#### **Features**

#### □ CPU Interface

- Direct connection to the 66 MHz VR43xx CPU bus

- 3.3-volt I/O

- Support for all VR43xx bus cycles

- Little-endian or big-endian byte ordering modes

#### ■ Memory Interface

- Support for boot ROM/flash memory, base memory, and up to two SIMMs

- SIMM capacity of up to 128 MB

- Programmable address ranges for base and SIMM memory

- Support for two-bank 4/16 Mb devices and four-bank 64/128/256 Mb devices

- CAS latency of 2 or 3 in base memory or SIMM SDRAM, programmable to support faster new devices or slower legacy devices

- SIMM burst access time programmable in one or two cycle(s)

- 66 MHz memory bus

- 64 MB base memory range: SDRAM and EDO DRAM

- 256 MB SIMM memory range: SDRAM, EDO and fast-page DRAM

- Several speed grades supported within each memory range

- Open DRAM page maintained within base memory

- Eight-word (32-byte) write FIFO (CPU to memory)

- Two-word (8-byte) prefetch FIFO (memory to CPU or memory to PCI)

- On-chip DRAM and SDRAM refresh generation

- Up to 64 MB of write-protectable boot ROM or up to 64 MB of flash ROM

- Flash/boot ROM devices with 8-/16-/32-bit configuration support

- Programmable timing to interface general-purpose I/O device or boot ROM in the boot ROM address range

#### □ PCI Interface

- Master and target capabilities

- Host bridge and add-on board modes

- PCI bus arbiter with programmable arbitration scheme

- Programmable arbitration scheme for PCI/CPU accessed to memory

- Big-endian or little-endian byte ordering modes

- 4-word (16-byte) bidirectional PCI master FIFO (CPU is PCI bus master)

- 8-word (32-byte) bidirectional PCI target FIFO (memory is PCI bus target)

- 33 MHz PCI bus clock rate

- 132 MB/s burst transfers

- Interrupt support for add-on board mode

- 3.3 V inputs; 5 V-tolerant inputs/outputs

#### □ DMA Controller

- Four highly robust DMA channels

- CPU-initiated block transfers between memory and PCI bus

- 8-word (32-byte) bidirectional DMA FIFO

- Sophisticated, programmable DMA channel arbitration priority scheme

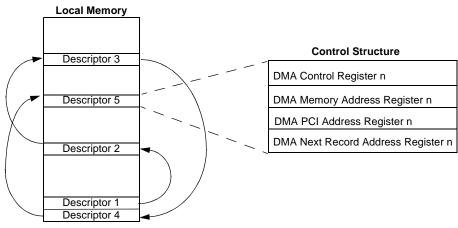

- Four sets of DMA control registers for chained transfers

- Next address pointer in each channel to support scatter/gather operation

- Programmable DMA arbitration priority

- · Bidirectional unaligned transfers

- Transfers at maximum PCI bandwidth of 132 MB/s

#### □ Interrupt Controller

- Nonmaskable interrupt and interrupt signals (NMI# and INT#)

- Maskable interrupt-causing events

#### □ UART

- NY16550L Universal Asynchronous Receiver/Transmitter

- Modem control functions

- Separate receiver and transmitter FIFOs (16 bytes each)

- Even-, odd- or no-parity bit generation

- Fully prioritized interrupt control

#### □ Timers

- One 32-bit loadable watchdog timer that generates a nonmaskable interrupt

- Two 32-bit loadable general-purpose timers that generate interrupts

- Highly sophisticated timers with programmable clock, start/stop, auto reload/ restart, and enable/disable interrupt bits

### Ordering Information

| Part Number                            | Package      |  |  |  |

|----------------------------------------|--------------|--|--|--|

| V <sub>RC</sub> 4375<br>μPD65948S1-068 | 256-pin TBGA |  |  |  |

## System Configuration

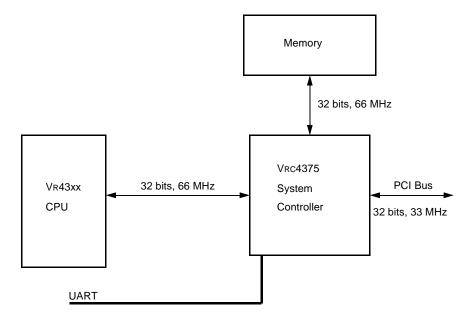

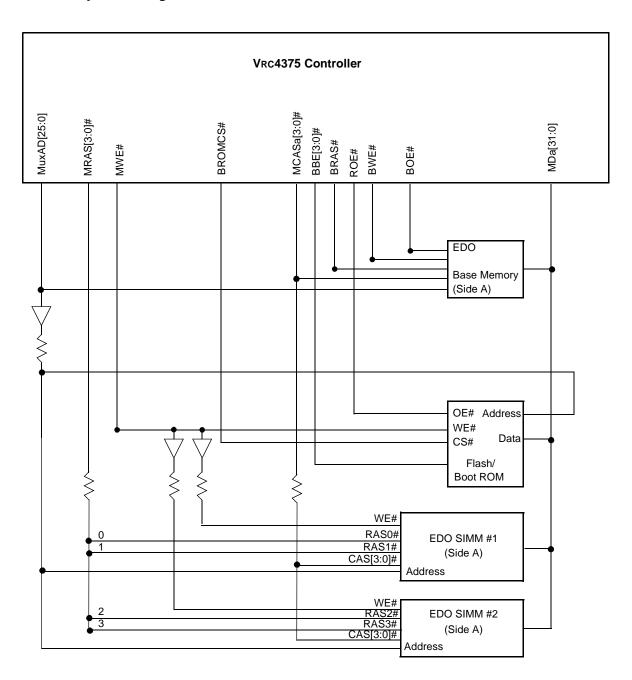

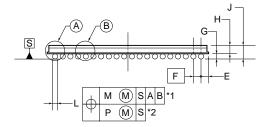

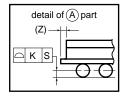

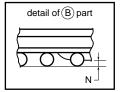

Figure 1 shows the controller used as a host bridge in a typical system. Alternatively, the controller can be located on a PCI bus Add-On Board.

Figure 1. System Connection

**Note:** F244- or F245-type buffers may be needed on the MuxAD bus and, for DIMM, on certain chip-select signals.

### **Terminology**

In this document:

- □ Signal names ending with # (such as NMI#) are active-low signals.

- Word means 4 bytes. This definition of word differs from the definition in the PCI Local Bus Specification, where a word is 2 bytes.

- B means byte.

- □ b means bit.

- □ *CAS* means column address strobe.

- ☐ *Memory* means the local memory attached to the VRC4375 controller.

- □ SIMM<sup>™</sup> and DIMM<sup>™</sup> mean single and dual in-line memory module unless explicitly stated otherwise.

- □ *Module* means a set of chips, as in a SIMM or DIMM.

- □ *EDO DRAM* means extended data out dynamic random access memory.

- □ *SDRAM* means synchronous DRAM.

- □ *RDRAM*<sup>®</sup> means Rambus<sup>®</sup> DRAM, which is designed to conform to the interface that defines the Rambus Channel.

## Reference Documents

The following documents were used in the creation of this data sheet. Unless otherwise specified, the latest version of each document applies.

- □ MIPS® R4300 Preliminary RISC Processor Specification Revision 2.2 (available from MIPS Technologies, Inc.)

- □ PCI Local Bus Specification Revision 2.1 and PCI System Design Guide Revision 1.0 (available from the Peripheral Component Interconnect Special Interest Group)

- □ NEC VR4300™ Microprocessor User's Manual (document number U10504EJ6V0UM00)

## **Contents**

|      | Description1Features1Ordering Information2System Configuration3Terminology4Reference Documents4 |

|------|-------------------------------------------------------------------------------------------------|

| 1.0  | Pin Configuration                                                                               |

| 2.0  | Block Diagram                                                                                   |

| 3.0  | Signal Summary                                                                                  |

| 4.0  | Registers, Resources, and Implementation                                                        |

| 5.0  | CPU Interface                                                                                   |

| 6.0  | Memory Interface                                                                                |

| 7.0  | PCI Bus Interface                                                                               |

| 8.0  | DMA Transfers                                                                                   |

| 9.0  | Interrupts83                                                                                    |

| 10.0 | Clocking                                                                                        |

| 11.0 | Reset Configuration Signals                                                                     |

| 12.0 | Endian Mode Software Issues                                                                     |

| 13.0 | Timing Diagrams102                                                                              |

| 14.0 | Electrical Characteristics                                                                      |

| 15.0 | Package Drawing                                                                                 |

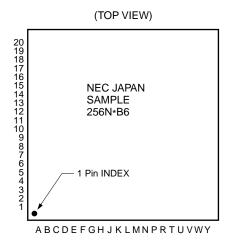

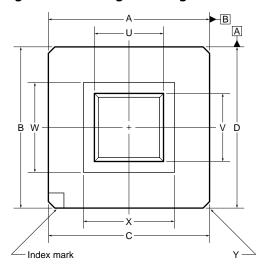

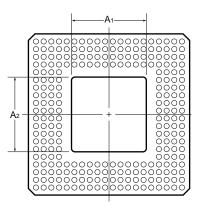

## 1.0 Pin Configuration

Figure 2. Pin Configuration

256TBGA

Table 1. Pin Assignment

| Pin<br>Number | Grid<br>Number | Pin Name              |

|---------------|----------------|-----------|---------------|----------------|-----------|---------------|----------------|-----------|---------------|----------------|-----------------------|

| 1             | A1             | GND       | 45            | P20            | MuxAD[24] | 89            | P2             | TRDY#     | 133           | B14            | MDa[26]               |

| 2             | B1             | CLK [0]   | 46            | N20            | ROE#      | 90            | R2             | AD[17]    | 134           | B13            | MRAS[0]#              |

| 3             | C1             | CLK[1]    | 47            | M 20           | MuxAD[20] | 91            | T2             | FRAME#    | 135           | B12            | MCAS[0]#              |

| 4             | D1             | GNT[3]#   | 48            | L20            | BRAS#     | 92            | U2             | AD[18]    | 136           | B11            | GND                   |

| 5             | E1             | INTA#     | 49            | K20            | VDD       | 93            | V2             | GND       | 137           | B10            | GND                   |

| 6             | F1             | LOCK#     | 50            | J20            | MDa[15]   | 94            | W2             | CBE[3]#   | 138           | В9             | MuxAD[8]              |

| 7             | G1             | GNT[0]#   | 51            | H20            | MDa[13]   | 95            | W3             | VDD       | 139           | В8             | GND                   |

| 8             | H1             | GND       | 52            | G20            | VDD       | 96            | W 4            | AD[26]    | 140           | В7             | MuxAD[6]              |

| 9             | J1             | AD[1]     | 53            | F20            | MuxAD[19] | 97            | W 5            | AD[29]    | 141           | В6             | MuxAD[2]              |

| 10            | K1             | AD[5]     | 54            | E20            | MuxAD[18] | 98            | W 6            | SysAD[16] | 142           | B5             | GND                   |

| 11            | L1             | GND       | 55            | D20            | GND       | 99            | W 7            | SysAD[13] | 143           | B4             | MDa[18]               |

| 12            | M 1            | VDD       | 56            | C20            | MuxAD[14] | 100           | W 8            | iochrdy   | 144           | В3             | MDa[2]                |

| 13            | N 1            | AD[13]    | 57            | B20            | BBE[0]#   | 101           | W 9            | SysAD[8]  | 145           | C3             | NMI#                  |

| 14            | P1             | GND       | 58            | A20            | VDD       | 102           | W10            | GND       | 146           | D3             | GND                   |

| 15            | R1             | DEVSEL    | 59            | A19            | MDa[23]   | 103           | W11            | SysAD[2]  | 147           | E3             | SERR#                 |

| 16            | T1             | IRDY#     | 60            | A18            | MDa[22]   | 104           | W12            | RST#      | 148           | F3             | GNT[1]#               |

| 17            | U1             | GND       | 61            | A17            | MuxAD[11] | 105           | W13            | GND       | 149           | G3             | REQ[2]#               |

| 18            | V1             | AD[20]    | 62            | A16            | GND       | 106           | W14            | PValid#   | 150           | Н3             | AD[0]                 |

| 19            | W 1            | AD[22]    | 63            | A15            | BOE#      | 107           | W15            | SysAD[28] | 151           | J3             | AD[3]                 |

| 20            | Y1             | AD[21]    | 64            | A14            | MDa[27]   | 108           | W16            | SysAD[30] | 152           | К3             | AD[6]                 |

| 21            | Y2             | AD[23]    | 65            | A13            | MRAS[1]#  | 109           | W 17           | SysAD[23] | 153           | L3             | AD[8]                 |

| 22            | Y3             | AD[24]    | 66            | A12            | MCAS[3]#  | 110           | W18            | GND       | 154           | М3             | AD[11]                |

| 23            | Y4             | GND       | 67            | A11            | MCAS[2]#  | 111           | W19            | SysAD[19] | 155           | N3             | AD[15]                |

| 24            | Y5             | AD[28]    | 68            | A10            | MuxAD[9]  | 112           | V19            | VDD       | 156           | Р3             | CBE[1]#               |

| 25            | Y6             | GND       | 69            | A 9            | VDD       | 113           | U19            | SysCmd[4] | 157           | R3             | STOP#                 |

| 26            | Y7             | SysAD[14] | 70            | A 8            | MDa[7]    | 114           | T19            | SysCmd[2] | 158           | Т3             | CBE[2]#               |

| 27            | Y8             | INT#      | 71            | Α7             | MDa[6]    | 115           | R19            | GND       | 159           | U3             | AD[19]                |

| 28            | Y9             | SysAD[9]  | 72            | A 6            | MuxAD[10] | 116           | P19            | MuxAD[25] | 160           | V3             | AD[25]                |

| 29            | Y10            | SysAD[5]  | 73            | A5             | MuxAD[3]  | 117           | N19            | SDCKE[0]  | 161           | V 4            | AD[27]                |

| 30            | Y11            | SysAD[3]  | 74            | A 4            | VDD       | 118           | M19            | MuxAD[21] | 162           | V5             | AD[30]                |

| 31            | Y12            | VDD       | 75            | А3             | MDa[19]   | 119           | L19            | GND       | 163           | V 6            | SysAD[15]             |

| 32            | Y13            | EOK#      | 76            | A2             | MDa[3]    | 120           | K19            | BROMCS#   | 164           | V7             | SysAD[12]             |

| 33            | Y14            | GND       | 77            | B2             | GND       | 121           | J19            | GND       | 165           | V 8            | SysAD[10]             |

| 34            | Y15            | SysAD[29] | 78            | C2             | CLK[2]    | 122           | H19            | MDa[12]   | 166           | V 9            | SysAD[7]              |

| 35            | Y16            | SysAD[26] | 79            | D2             | IDSEL     | 123           | G19            | MDa[30]   | 167           | V10            | SysAD[4]              |

| 36            | Y17            | VDD       | 80            | E2             | REQ[3]#   | 124           | F19            | GND       | 168           | V11            | GND                   |

| 37            | Y18            | SysAD[21] | 81            | F2             | GNT[2]#   | 125           | E19            | MuxAD[17] | 169           | V12            | REFCLK                |

| 38            | Y19            | SysAD[20] | 82            | G2             | REQ[0]#   | 126           | D19            | MuxAD[15] | 170           | V13            | MasterClock<br>(MCLK) |

| 39            | Y20            | VDD       | 83            | H2             | GND       | 127           | C19            | BBE[1]#   | 171           | V14            | SysAD[31]             |

| 40            | W20            | GND       | 84            | J2             | AD[2]     | 128           | B19            | GND       | 172           | V15            | SysAD[27]             |

| 41            | V20            | SysAD[18] | 85            | K2             | AD[7]     | 129           | B18            | MDa[21]   | 173           | V16            | SysAD[25]             |

| 42            | U20            | GND       | 86            | L2             | CBE[0]#   | 130           | B17            | MuxAD[12] | 174           | V17            | SysAD[22]             |

| 43            | T20            | SysCmd[3] | 87            | M 2            | AD[12]    | 131           | B16            | MDa[11]   | 175           | V18            | SysAD[17]             |

Table 1. Pin Assignment (continued)

| Pin<br>Number | Grid<br>Number | Pin Name  | Pin<br>Number | Grid<br>Number | Pin Name | Pin<br>Number | Grid<br>Number | Pin Name  | Pin<br>Number | Grid<br>Number | Pin Name |

|---------------|----------------|-----------|---------------|----------------|----------|---------------|----------------|-----------|---------------|----------------|----------|

| 44            | R20            | UART_RxD  | 88            | N2             | AD[14]   | 132           | B15            | BWE#      | 176           | U18            | EValid#  |

| 177           | T18            | SysCmd[1] | 197           | C11            | MCAS[1]# | 217           | T4             | AD[16]    | 237           | L17            | VDD      |

| 178           | R18            | UART_TxD  | 198           | C10            | MuxAD[7] | 218           | U4             | GND       | 238           | K17            | SDCAS#   |

| 179           | P18            | UART_DSR  | 199           | C9             | MDa[5]   | 219           | U5             | AD[31]    | 239           | J17            | SDRAS#   |

| 180           | N18            | SDCKE[1]  | 200           | C8             | MuxAD[5] | 220           | U6             | VDD       | 240           | H17            | GND      |

| 181           | M18            | MuxAD[22] | 201           | C7             | MuxAD[1] | 221           | U7             | SysAD[11] | 241           | G17            | MDa[28]  |

| 182           | L18            | GND       | 202           | C6             | MDa[16]  | 222           | U8             | GND       | 242           | F17            | VDD      |

| 183           | K18            | SDCLK[1]  | 203           | C5             | MDa[17]  | 223           | U9             | SysAD[6]  | 243           | E17            | BBE[3]#  |

| 184           | J18            | SDCLK[0]  | 204           | C 4            | MDa[1]   | 224           | U10            | VDD       | 244           | D17            | GND      |

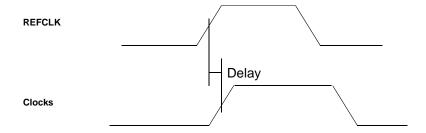

| 185           | H18            | MDa[14]   | 205           | D4             | GND      | 225           | U11            | SysAD[1]  | 245           | D16            | MDa[9]   |

| 186           | G18            | MDa[29]   | 206           | E4             | PERR#    | 226           | U12            | SysAD[0]  | 246           | D15            | VDD      |

| 187           | F18            | MDa[31]   | 207           | F4             | VDD      | 227           | U13            | GND       | 247           | D14            | MDa[24]  |

| 188           | E18            | MuxAD[16] | 208           | G 4            | REQ[1]#  | 228           | U14            | TESTB     | 248           | D13            | GND      |

| 189           | D18            | BBE[2]#   | 209           | H4             | GND      | 229           | U15            | VDD       | 249           | D12            | MRAS[3]# |

| 190           | C18            | MDa[20]   | 210           | J4             | AD[4]    | 230           | U16            | SysAD[24] | 250           | D11            | VDD      |

| 191           | C17            | MuxAD[13] | 211           | K4             | VDD      | 231           | U17            | GND       | 251           | D10            | MDa[4]   |

| 192           | C16            | MDa[10]   | 212           | L4             | AD[9]    | 232           | T17            | SysCmd[0] | 252           | D9             | MuxAD[4] |

| 193           | C15            | MDa[8]    | 213           | M 4            | AD[10]   | 233           | R17            | VDD       | 253           | D8             | GND      |

| 194           | C14            | MDa[25]   | 214           | N 4            | GND      | 234           | P17            | UART_DTR  | 254           | D7             | MuxAD[0] |

| 195           | C13            | MWE#      | 215           | P4             | PAR      | 235           | N17            | GND       | 255           | D6             | VDD      |

| 196           | C12            | MRAS[2]#  | 216           | R4             | VDD      | 236           | M17            | MuxAD[23] | 256           | D5             | MDa[0]   |

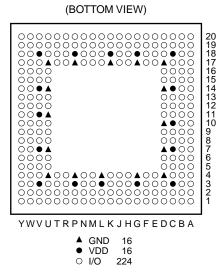

## 2.0 Block Diagram

This section provides the block diagram for the system controller. For descriptions of each interface block, see:

- □ Section 5.0 "CPU Interface" on page 17

- □ Section 6.0 "Memory Interface" on page 18

- □ Section 7.0 "PCI Bus Interface" on page 55

Figure 3. Block Diagram

## 3.0 Signal Summary

The VRc4375 controller utilizes a 256-pin tape ball grid array (TBGA) package. Table 2 through Table 5 summarize the signal functions. The # symbol following a signal name indicates an active-low signal.

Table 2. CPU Interface Signals

| Signal                | Buffer Type<br>(NEC<br>Library) | I/O | Reset<br>Value | Pull-up/<br>Pull-down<br>Resistance<br>(Ohms) | Max imum<br>AC<br>Load (pF) | Maximum<br>DC<br>Drive (mA) | Description                                                                                                             |

|-----------------------|---------------------------------|-----|----------------|-----------------------------------------------|-----------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------|

| EOK#                  | B001                            | 0   | High           |                                               | 20                          | 12                          | External ready. Signifies that the controller is capable of accepting a processor request.                              |

| EValid#               | B001                            | 0   | High           |                                               | 20                          | 12                          | External agent valid. Indicates that the controller is driving valid information on the SysAD and SysCmd buses.         |

| INT#                  | B001                            | 0   | High           |                                               | 30                          | 12                          | Interrupt request                                                                                                       |

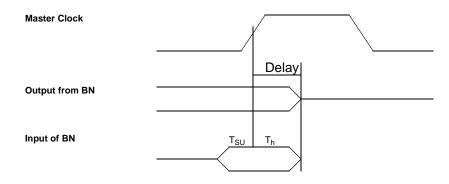

| MasterClock<br>(MCLK) | B001                            | 0   | Toggle         |                                               | 20                          | 12                          | 66-MHz master clock to CPU                                                                                              |

| NMI#                  | B0UC                            | 0   | High           | 50 K pull-up                                  | 20                          | 6                           | Nonmaskable interrupt; asserted when a PCI device asserts SERR# or by the Internal counter                              |

| PValid#               | FIU1                            | I   |                |                                               |                             |                             | Processor valid. Signifies that the V <sub>R</sub> 43xx CPU is driving valid information on the SysAD and SysCmd buses. |

| SysAD[31:0]           | B00C                            | I/O | Hi-Z           |                                               | 20                          | 6                           | System address/data bus                                                                                                 |

| SysCmd[4:0]           | B00C                            | I/O | Hi-Z           |                                               | 20                          | 6                           | System command/data ID bus                                                                                              |

Table 3. Memory Interface Signals

| Signal       | Buffer<br>Type (NEC<br>Library) | I/O | Reset<br>Value | Pull-up/<br>Pull-down<br>Resistance<br>(Ohms) | Maximum<br>AC<br>Load (pF) | Maximum<br>DC<br>Drive (mA) | Description                                                                                |

|--------------|---------------------------------|-----|----------------|-----------------------------------------------|----------------------------|-----------------------------|--------------------------------------------------------------------------------------------|

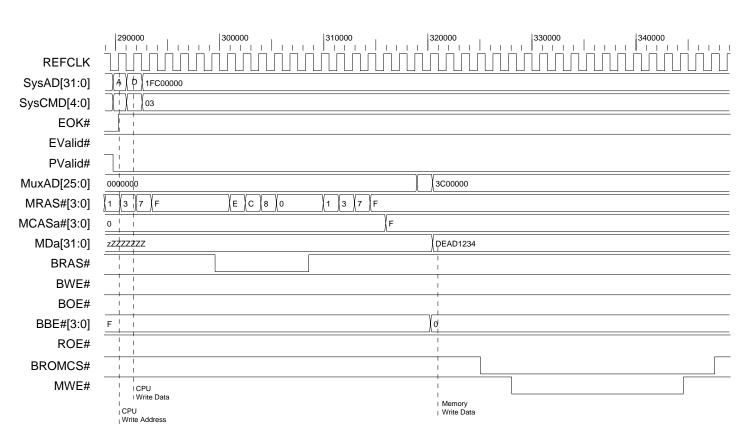

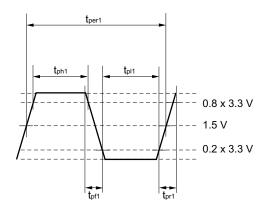

| BOE#         | B001                            | 0   | High           |                                               | 50                         | 12                          | Base memory output enable. See Figure 4.                                                   |

| BRAS#        | B001                            | 0   | High           |                                               | 50                         | 12                          | Base memory row address strobe. See Figure 4.                                              |

| BROMCS#      | B001                            | 0   | High           |                                               | 30                         | 12                          | Boot ROM chip select                                                                       |

| BWE#         | B001                            | 0   | High           |                                               | 50                         | 12                          | Base memory write enable. See Figure 4.                                                    |

| ROE#         | B001                            | 0   | High           |                                               | 30                         | 12                          | Boot ROM/flash ROM output enable. Connect to ROM OE pin.                                   |

| BBE[3:0]#    | B001                            | 0   | High           |                                               | 30                         | 12                          | Byte enable for PROM/flash ROM                                                             |

| MRAS[3:0]#   | B001                            | 0   | High           |                                               | 70                         | 12                          | Memory row address strobes. See Figure 5.                                                  |

| MCAS[3:0]#   | B001                            | 0   | High           |                                               | 70                         | 12                          | Memory column address strobes. See Figure 5.                                               |

| MDa[31:0]    | B00C                            | I/O | High           |                                               | 50                         | 12                          | Memory data (even), boot ROM address                                                       |

| MuxAD[14:0]  | B0D1                            | I/O | Hi-Z           | 50K pull-<br>down<br>(internal)               | 70                         | 12                          | Multiplexed row/column address; also lower boot ROM address bits                           |

| MuxAD[25:15] | B0D1                            | I/O | Hi-Z           | 50K pull-<br>down<br>(internal)               | 50                         | 12                          | Upper boot ROM address bits                                                                |

| MWE#         | B001                            | 0   | High           |                                               | 30                         | 12                          | Boot ROM and SIMM write enable                                                             |

| iochrdy      | B001                            | I   | High           |                                               | 30                         | 12                          | I/O channel ready signal. Input during normal operation. See Section 6.6 for more details. |

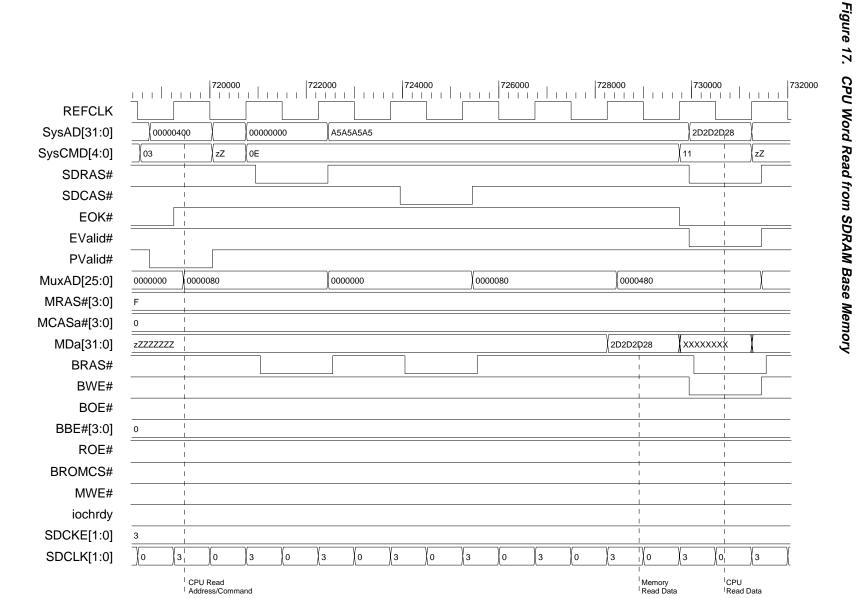

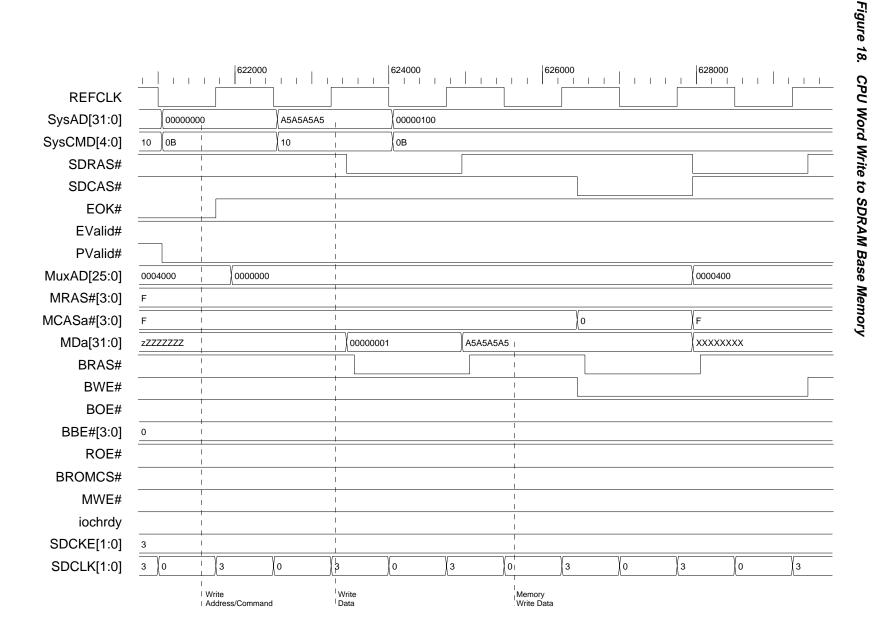

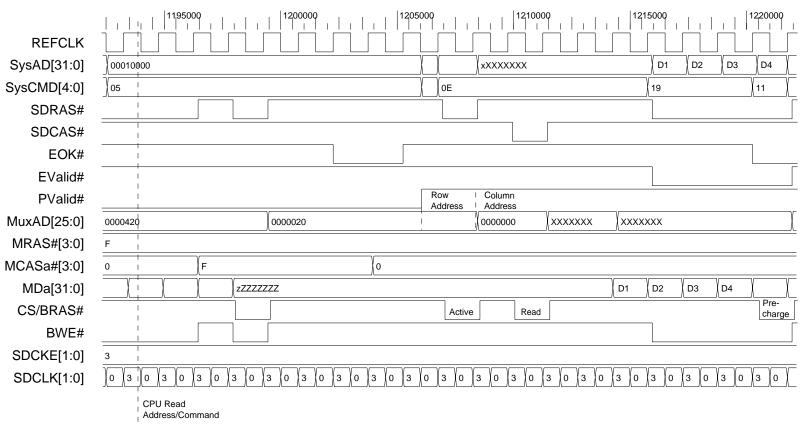

| SDCAS#       | B001                            | 0   | High           |                                               | 50                         | 12                          | SDRAM column address strobe                                                                |

| SDRAS#       | B001                            | 0   | High           |                                               | 50                         | 12                          | SDRAM row address strobe                                                                   |

| SDCKE[1:0]   | B001                            | 0   | High           |                                               | 50                         | 12                          | SDRAM clock enable                                                                         |

| SDCLK[1:0]   | B001                            | 0   | High           |                                               | 50                         | 12                          | 66-MHz SDRAM clock                                                                         |

Table 4. PCI Interface Signals

| Signal      | Buffer<br>Type<br>(NEC<br>Library) | I/O        | Reset<br>Value | Pull-up/<br>Pull-down<br>Resistance<br>(Ohms) | Maximum<br>AC<br>Load (pF) | Maximum<br>DC<br>Drive (mA) | Description                            |

|-------------|------------------------------------|------------|----------------|-----------------------------------------------|----------------------------|-----------------------------|----------------------------------------|

| AD[31:0]    | BW01                               | I/O        | Hi-Z           | (Olillis)                                     | 70                         | PCI, 12 Note                | PCI multiplexed address and data bus   |

| CBE[3:0]#   | BW01                               | 1/0        | Hi-Z           |                                               | 50                         | 12                          | PCI bus command and byte-enable        |

| CLK[2:0]    | BW01                               | 0          | Toggle         |                                               | 50                         | 12                          | PCI clock, 33 MHz                      |

| DEVSEL#     | BW01                               | 1/0        | Hi-Z           |                                               | 50                         | 12                          | PCI device select                      |

| FRAME#      | BW01                               | 1/0        | Hi-Z           |                                               | 50                         | 12                          | PCI cycle frame                        |

| GNT[0]#     | BW01                               | I/O        | High           |                                               | 10                         | 12                          | PCI bus grant                          |

| GNT[3:1]#   | BW01                               | 0          | High           |                                               | 10                         | 12                          | PCI bus grant                          |

| IDSEL       | BW01                               | ı          |                |                                               |                            |                             | PCI initialization device select       |

| INTA#       | BW01                               | I/O        |                |                                               | 10                         | 12                          | PCI interrupt A                        |

| IRDY#       | BW01                               | I/O        | Hi-Z           |                                               | 50                         | 12                          | PCI initiator ready                    |

| LOCK#       | BW01                               | I/O        | Hi-Z           |                                               | 10                         | 12                          | PCI lock atomic operation              |

| PAR         | BW01                               | I/O        | Hi-Z           |                                               | 50                         | 12                          | PCI parity of A/D[31:0] and C/BE[3:0]# |

| PERR#       | BW01                               | I/O        | Hi-Z           |                                               | 10                         | 12                          | PCI parity error                       |

| REQ[0]#     | BW01                               | I/O        |                |                                               | 10                         | 12                          | PCI bus request                        |

| REQ[3:1]#   | BW01                               | I          |                |                                               |                            |                             | PCI bus request                        |

| RST#        | BW01                               | I          |                |                                               |                            |                             | Reset (Chip)                           |

| SERR#       | BW01                               | I/O        | Hi-Z           |                                               | 10                         | 12                          | PCI system error                       |

| STOP#       | BW01                               | I/O        | Hi-Z           |                                               | 50                         | 12                          | PCI stop request from target           |

| TRDY#       | BW01                               | I/O        | Hi-Z           |                                               | 50                         | 12                          | PCI target ready                       |

| Note: Compa | atible with PC                     | l specific | ation.         |                                               |                            |                             |                                        |

## Table 5. Utility Signals

| Signal                 | Buffer Type<br>(NEC<br>Library) | I/O | Reset<br>Value | Pull-up/<br>Pull-down<br>Resistance<br>(Ohms) | Max imum<br>AC<br>Load (pF) | Maximum<br>DC<br>Drive (mA) | Description                                           |

|------------------------|---------------------------------|-----|----------------|-----------------------------------------------|-----------------------------|-----------------------------|-------------------------------------------------------|

| REFCLK                 | F1V1                            | Į   | Toggle         |                                               |                             |                             | 66 MHz system reference clock                         |

| UART_TXD               | BWDC                            | I/O | Hi-Z           | 50 K (to<br>GND, inter-<br>nal)               | 50                          | 6                           | UART transmit data                                    |

| UART_RXD               | F1V1                            | I   | Hi-Z           |                                               | 50                          | 6                           | UART receive data                                     |

| UART_DTR               | BWDC                            | I/O | Hi-Z           | 50 K (to<br>GND, inter-<br>nal)               | 50                          | 6                           | UART data terminal ready                              |

| UART_DSR               | F1V1                            | I   | Hi-Z           |                                               | 50                          | 6                           | UART data set ready                                   |

| UART test/<br>MuxAD 15 | B0D1                            | I   | Hi-Z           |                                               | 50                          | 6                           | Used to test UART hardmacro at LSI chip tester        |

| TESTB                  | B0D1                            | I   | Hi-Z           |                                               | 50                          | 6                           | Input used by UART. Pulled high for normal operation. |

## 4.0 Registers, Resources, and Implementation

### 4.1

## **Register Summary**

Table 6 summarizes the controller's register set (base memory address 0x0F00\_0000 in system memory). Accesses above offset 0x1FF return 0 with the data error bit set on SysCmd[0], update the controller's Bus Error Status Register (Section 9.1.1), and cause an interrupt (INT#), if enabled.

Table 6. Register Summary

| Offset from Base<br>Memory Address<br>0x0F00_0000 | Register Name                                          | Size<br>(Bytes) | CPU Bus<br>R/W | PCI Bus (R/W)  | Reference                 |

|---------------------------------------------------|--------------------------------------------------------|-----------------|----------------|----------------|---------------------------|

| 0x0                                               | Base Memory Control register                           | 4               | R/W            | Not accessible | Section 6.7.1 on page 30  |

| 0x4                                               | SIMM Memory Control Register 1                         | 4               | R/W            | Not accessible | Section 6.8.1 on page 38  |

| 0x8                                               | Reserved                                               | 4               |                | Not accessible |                           |

| 0xC                                               | SIMM Memory Control Register 2                         | 4               | R/W            | Not accessible | Section 6.8.1 on page 38  |

| 0x10                                              | Reserved                                               | 4               |                | Not accessible |                           |

| 0x14                                              | PCI Master Address Window Register 1                   | 4               | R/W            | Not accessible | Section 7.3.1 on page 57  |

| 0x18                                              | PCI Master Address Window Register 2                   | 4               | R/W            | Not accessible | Section 7.3.1 on page 57  |

| 0x1C                                              | PCI Target Address Window Register 1                   | 4               | R/W            | Not accessible | Section 7.4.1 on page 59  |

| 0x20                                              | PCI Target Address Window Register 2                   | 4               | R/W            | Not accessible | Section 7.4.1 on page 59  |

| 0x24                                              | PCI Master I/O Window register                         | 4               | R/W            | Not accessible | Section 7.3.1 on page 57  |

| 0x28                                              | PCI Configuration Data register                        | 4               | R/W            | Not accessible | Section 7.5 on page 61    |

| 0x2C                                              | PCI Configuration Address register                     | 4               | R/W            | Not accessible | Section 7.5 on page 61    |

| 0x30                                              | PCI Mailbox Register 1                                 | 4               | R/W            | R/W            | Section 7.11 on page 72   |

| 0x34                                              | PCI Mailbox Register 2                                 | 4               | R/W            | R/W            | Section 7.11 on page 72   |

| 0x38                                              | DMA Control Register 1                                 | 4               | R/W            | Not accessible | Section 8.3.1 on page 77  |

| 0x3C                                              | DMA Memory Address Register 1                          | 4               | R/W            | Not accessible | Section 8.3.3 on page 80  |

| 0x40                                              | DMA PCI Address Register 1                             | 4               | R/W            | Not accessible | Section 8.3.4 on page 81  |

| 0x44                                              | DMA Control Register 2                                 | 4               | R/W            | Not accessible | Section 8.3.1 on page 77  |

| 0x48                                              | DMA Memory Address Register 2                          | 4               | R/W            | Not accessible | Section 8.3.3 on page 80  |

| 0x4C                                              | DMA PCI Address Register 2                             | 4               | R/W            | Not accessible | Section 8.3.4 on page 81  |

| 0x50                                              | Bus Error Status register                              | 4               | R              | Not accessible | Section 9.1.1 on page 85  |

| 0x54                                              | Interrupt Control and Status Register 1                | 4               | R/W            | Not accessible | Section 9.1.2 on page 85  |

| 0x58                                              | DRAM Refresh Counter register                          | 4               | R/W            | Not accessible | Section 6.9.1 on page 44  |

| 0x5C                                              | Boot ROM Write-Protect register                        | 4               | R/W            | Not accessible | Section 6.5.3 on page 26  |

| 0x60                                              | PCI Exclusive Access register                          | 4               | R/W            | Not accessible | Section 7.12.1 on page 73 |

| 0x64                                              | DMA Words Remaining register                           | 4               | R              | Not accessible | Section 8.3.6 on page 82  |

| 0x68                                              | DMA Current Memory Address register                    | 4               | R              | Not accessible | Section 8.3.7 on page 82  |

| 0x6C                                              | DMA Current PCI Address register                       | 4               | R              | Not accessible | Section 8.3.8 on page 82  |

| 0x70                                              | PCI Retry Counter                                      | 4               | R              | Not accessible | Section 7.8 on page 70    |

| 0x74                                              | PCI Enable register                                    | 4               | R/W            | Not accessible | Section 7.10 on page 71   |

| 0x78                                              | Power-on Memory Initialization register                | 4               | R/W            | Not accessible | Section 6.11.1 on page 45 |

| 0x7C                                              | Endian Mode register (EM)                              | 4               | R/W            | Not accessible | Section 12.0 on page 94   |

| 0x80                                              | DMA/CPU/PCI Memory Arbiter Priority Selection register | 4               | R/W            | Not accessible | Section 8.3.2 on page 79  |

| 0x84                                              | UART Receiver Data Buffer register (UARTRBR)           | 4               | R              | Not accessible | Section 6.12.1 on page 47 |

| 0x84                                              | UART Transmitter Data Holding register (UARTTHR)       | 4               | W              | Not accessible | Section 6.12.2 on page 47 |

| 0x88                                              | UART Interrupt Enable register (UARTIER)               | 4               | R/W            | Not accessible | Section 6.12.3 on page 47 |

| 0x84                                              | UART Divisor Latch LSB (UARTDLL)                       | 4               | R/W            | Not accessible | Section 6.12.4 on page 48 |

## Table 6. Register Summary (continued)

| Offset from Base<br>Memory Address<br>0x0F00_0000 | Register Name                                                                                                                           | Size<br>(Bytes) | CPU Bus<br>R/W      | PCI Bus (R/W)  | Reference                  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|----------------|----------------------------|

| 0x88                                              | UART Divisor Latch MSB register (UARTDLM)                                                                                               | 4               | R/W                 | Not accessible | Section 6.12.5 on page 48  |

| 0x8C                                              | UART Interrupt ID register (UARTIIR)                                                                                                    | 4               | R                   | Not accessible | Section 6.12.6 on page 48  |

| 0x8C                                              | UART FIFO Control register (UARTFCR)                                                                                                    | 4               | W                   | Not accessible | Section 6.12.7 on page 49  |

| 0x90                                              | UART Line Control register (UARTLCR)                                                                                                    | 4               | R/W                 | Not accessible | Section 6.12.8 on page 50  |

| 0x94                                              | UART Modem Control register (UARTMCR)                                                                                                   | 4               | R/W                 | Not accessible | Section 6.12.9 on page 51  |

| 0x98                                              | UART Line Status register (UARTLSR)                                                                                                     | 4               | R/W                 | Not accessible | Section 6.12.10 on page 52 |

| 0x9C                                              | UART Modem Status register (UARTMSR)                                                                                                    | 4               | R/W                 | Not accessible | Section 6.12.11 on page 53 |

| 0xA0                                              | UART Scratch register (UARTSCR)                                                                                                         | 4               | R/W                 | Not accessible | Section 6.12.12 on page 54 |

| 0xA4                                              | DMA Control Register 3                                                                                                                  | 4               | R/W                 | Not accessible | Section 8.3.1 on page 77   |

| 0xA8                                              | DMA Memory Address Register 3                                                                                                           | 4               | R/W                 | Not accessible | Section 8.3.3 on page 80   |

| 0xAC                                              | DMA PCI Address Register 3                                                                                                              | 4               | R/W                 | Not accessible | Section 8.3.4 on page 81   |

| 0xB0                                              | DMA Control Register 4                                                                                                                  | 4               | R/W                 | Not accessible | Section 8.3.1 on page 77   |

| 0xB4                                              | DMA Memory Address Register 4                                                                                                           | 4               | R/W                 | Not accessible | Section 8.3.3 on page 80   |

| 0xB8                                              | DMA PCI Address Register 4                                                                                                              | 4               | R/W                 | Not accessible | Section 8.3.4 on page 81   |

| 0xBC                                              | DMA Next Record Pointer Register 1                                                                                                      | 4               | R/W                 | Not accessible | Section 8.3.5 on page 81   |

| 0xC0                                              | DMA Next Record Pointer Register 2                                                                                                      | 4               | R/W                 | Not accessible | Section 8.3.5 on page 81   |

| 0xC4                                              | DMA Next Record Pointer Register 3                                                                                                      | 4               | R/W                 | Not accessible | Section 8.3.5 on page 81   |

| 0xC8                                              | DMA Next Record Pointer Register 4                                                                                                      | 4               | R/W                 | Not accessible | Section 8.3.5 on page 81   |

| 0xCC                                              | Set Timer Counter Register 1                                                                                                            | 4               | R/W                 | Not accessible | Section 9.1.3 on page 88   |

| 0xD0                                              | Set Timer Counter Register 2                                                                                                            | 4               | R/W                 | Not accessible | Section 9.1.3 on page 88   |

| 0xD4                                              | Set NMI Timer register                                                                                                                  | 4               | R/W                 | Not accessible | Section 9.1.3 on page 88   |

| 0xD8                                              | Read Timer Counter Register 1                                                                                                           | 4               | R                   | Not accessible | Section 9.1.3 on page 88   |

| 0xDC                                              | Read Timer Counter Register 2                                                                                                           | 4               | R                   | Not accessible | Section 9.1.3 on page 88   |

| 0xE0                                              | Read NMI Timer register                                                                                                                 | 4               | R                   | Not accessible | Section 9.1.3 on page 88   |

| 0xE4                                              | Timers/PCI INTA# Interrupt Control and Status<br>Register 2                                                                             | 4               | R/W                 | Not accessible | Section 9.1.3 on page 88   |

| 0xE8                                              | General-Purpose I/O Timing Control register                                                                                             | 4               | R/W                 | Not accessible | Section 6.6.1 on page 29   |

| 0xEC                                              | Reserved                                                                                                                                |                 |                     |                |                            |

| 0xF0:0xFF                                         | Reserved                                                                                                                                |                 |                     |                |                            |

| 0x100:0x1FF                                       | PCI Configuration Space registers<br>(Host Bridge mode)                                                                                 | 1, 2, 4         | R/W                 | Not accessible | Section 7.5 on page 61     |

| 0x100:0x1FF                                       | PCI Configuration Space registers (Add-On Board mode, where the controller is located on a PCI bus boar rather than on the motherboard) |                 | Not ac-<br>cessible | R/W            | Section 7.7 on page 67     |

4.2 Resource **Accessibility**  Table 7 summarizes the accessibility of the controller's internal registers, memory ranges, and PCI bus resources from the CPU and from PCI bus masters.

Table 7. Resources Accessible Through The VRC4375 System Controller

| Resource                                               | Accessible from CPU                           | Accessible from PCI Bus                               | Reference                                          |

|--------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------|----------------------------------------------------|

| CPU                                                    | _                                             | No                                                    | Section 5.0 on page 17                             |

| Controller's internal registers (except PCI mailboxes) | Word                                          | No                                                    | Section 6.0, Section 7.0, Section 8.0, Section 9.0 |

| Boot ROM                                               | Byte writes<br>Word, halfword, or byte reads  | No <sup>1</sup>                                       | Section 6.5 on page 24                             |

| Base memory                                            | Any CPU burst <sup>2</sup>                    | Any PCI burst <sup>3</sup>                            | Section 6.7 on page 30                             |

| SIMM memory                                            | Any CPU burst <sup>1</sup>                    | Any PCI burst <sup>2</sup>                            | Section 6.8 on page 38                             |

| PCI mailboxes                                          | Word                                          | Word <sup>4</sup>                                     | Section 7.11 on page 72                            |

| PCI Configuration Space registers                      | Word, halfword, or byte <sup>5</sup>          | Word, halfword, or byte in Add-<br>On Board mode only | Section 7.5 on page 61, Section 7.7 on page 67     |

| PCI memory space                                       | Any CPU burst of 4 words or less <sup>1</sup> | No                                                    | PCI Local Bus Specification                        |

| PCI I/O space                                          | Any CPU burst of 4 words or less <sup>1</sup> | No                                                    | PCI Local Bus Specification                        |

| PCI configuration space                                | Word, halfword, or byte <sup>5</sup>          | Word, halfword, or byte                               | PCI Local Bus Specification                        |

- Notes: 1. Because the boot ROM does not support burst transfers, it cannot be accessed from the PCI bus. The PCI interface issues cache-line reads to the target inside the controller.

- 2. Alignment and burst length as defined by the VR43xx CPU.

- 3. Any size burst length, any alignment. Burst may be disconnected by the controller.

- 4. The controller accepts bursts of words to the PCI mailboxes. However, the controller performs a target disconnect without data after each data transfer.

- 5. Any size access less than or equal to one word, aligned as defined by the VR43xx CPU.

#### 4.3

## Implementation **Summary**

To create a system using the VRC4375 system controller:

- 1. Configure the hardware using the information provided throughout this data sheet.

- 2. Power-up and initialize the memory, following the steps in Section 6.11 on page 45.

- 3. Initialize the PCI bus interface, using the configuration information provided in Section 7.0 on page 55.

#### **CPU Interface**

The controller interfaces directly with the V<sub>R</sub>43xx Series CPU, in full compliance with the *MIPS R4300 Preliminary RISC Processor Specification, Revision 2.2*. The connection is via the CPU's 66-MHz SysAD bus using a 3.3-volt I/O. All of the CPU's SysAD bus operations are supported.

#### 5.1

## Endian Configuration

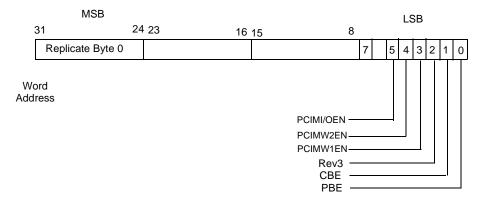

The BE bit in the  $V_R43xx$  CPU's Configuration register specifies the CPU's byte ordering at reset. BE = 0 configures little-endian order; BE = 1 configures big-endian order.

The BC bit in the VR43xx CPU's Configuration register specifies the PCI byte ordering at reset. BC = 0 configures little-endian order; BC = 1 configures big-endian order.

The VRC4375 controller's CPU interface supports either big- or little-endian byte ordering on the SysAD bus. The endianness for the CPU depends on the state of the MuxAD[11] signal at reset; the endianness for the PCI depends on the state of the MuxAD[12] signal at reset, as described in Section 11.0. All of the controller's other interfaces operate only in little-endian mode. All of the internal configuration, command, status and control registers are considered little endian. The software implications of this, and some related PCI device examples, are described in Section 12.0.

#### 5.2

#### **Data Rate Control**

The controller-to-CPU data rate is determined by the EValid# signal. The CPU to controller data rate is programmable in the EP field (bits 27:24) of the CPU's Configuration register. Although the CPU supports both D and Dxx data rates, the controller only supports the D data rate.

#### 5.3

#### **Address Decoding**

The controller latches the address on the SysAD bus. It then decodes the address and SysCmd signals to determine the transaction type. Ten address ranges can be decoded:

- ☐ Two ranges for boot ROM

- □ Boot ROM address ranges for I/O devices. (Do not put I/O devices in the "fault recovery address" range.)

- □ One range for the controller's internal Configuration registers

- One range for base memory

- Two ranges for SIMM/DIMM memory

- Two ranges for the PCI Master Address Windows

- One range for the PCI I/O address window

Boot ROM is mapped according to its size, as specified in Table 14 on page 24. The controller's internal registers are fixed at base memory address 0x0F00\_0000, to allow the CPU to access them during boot, before they have been configured. All other decode ranges are programmable.

#### 5.4

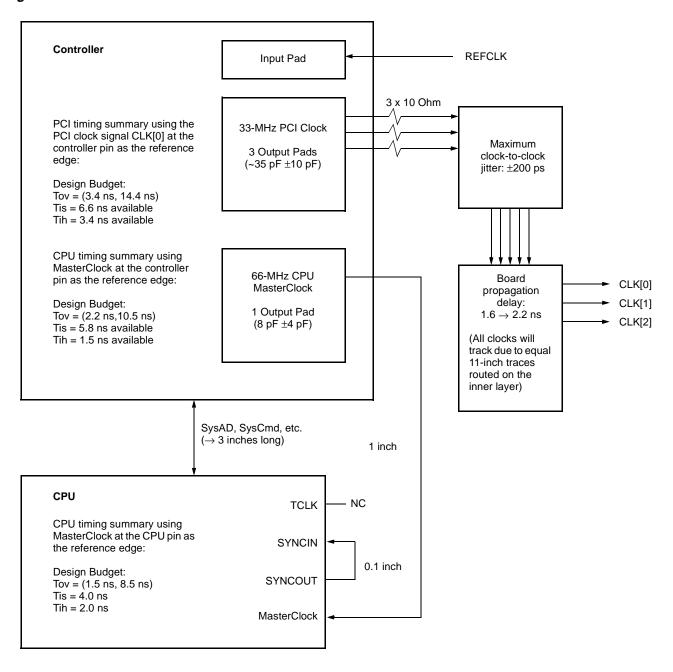

#### **Trace Requirements**

All traces between the CPU and the controller must be limited to 3 inches or less. TCLK is not used. See Section 10.0 on page 92 for details on clocking.

#### **Memory Interface**

The CPU accesses memory attached to the controller in the normal way, by addressing the system memory space. For large block transfers, the CPU can also initiate DMA transfers between memory and the PCI (bidirectionally), as described in Section 8.0. External PCI bus masters access the controller's memory through the PCI Target Address Windows, as described in Section 7.4.

The controller's memory interface has the following internal FIFOs that support transfers between memory and the various sources and destinations:

- □ 8-word (32-byte) write FIFO (CPU to memory)

- □ 2-word (8-byte) prefetch FIFO (memory to CPU or memory to PCI)

- □ 8-word (32-byte) bidirectional DMA FIFO (PCI to memory or memory to PCI)

#### 6.1

## Memory Regions and Devices

The controller connects directly to memory and manages the addresses, data, and control signals for the following address ranges.

- Two boot ROM ranges: standard and fault recovery

- One base memory range (programmable)

- □ Two SIMM memory ranges (programmable). DIMM modules can also be used.

- General-purpose I/O device within the boot ROM range

The following memory modules are examples of what can be used.

- □ Flash in boot ROM and/or SIMM 2 memory ranges

- □ EDO DRAM for base or SIMM memory; maximum of 64 MB in SIMM range using EDO DRAMs

- □ Synchronous DRAM (SDRAM); maximum of 256 MB in SIMM range

- 16 Mb for base or SIMM memory (NEC part numbers μPD4516421, μPD4564841, μPD4564163, and μPD4516821)

- 64-Mb, 4-bank devices for base or SIMM memory (NEC part numbers μPD4564441 and μPD4564841)

- 64-Mb, 4 M x 16 devices

- 128-Mb, 4-bank devices for base or SIMM memory (NEC part number μPD45128841)

- 2 M x 32-bit devices in base and SIMM memory

Boot ROM can be configured with 85-ns or slower flash chips. In addition to its standard boot address range, boot ROM can also be mapped to a fault-recovery range in SIMM memory slot 2, if that slot is configured with 85-ns flash chips. Prior to accessing boot ROM, software must configure this address range, as described in Section 6.5.

Boot ROM timing is flexible; the timing is controlled by two registers as described in Section 6.6.

Base memory can include 4-Mb EDO or NEC 8-/16-Mb SDRAM chips. If SDRAM is used for base memory, it cannot be bank interleaved. Prior to accessing base memory, software must configure this address range, as described in Section 6.7.

The two SIMM memory ranges can be single sided (SIMM) or double sided (DIMM), Page mode or Non-page mode, and may include any of the supported memory types.

The 100-pin DIMM package is the only DIMM package supported. Prior to accessing SIMM memory, software must configure this address range, as described in Section 6.8.

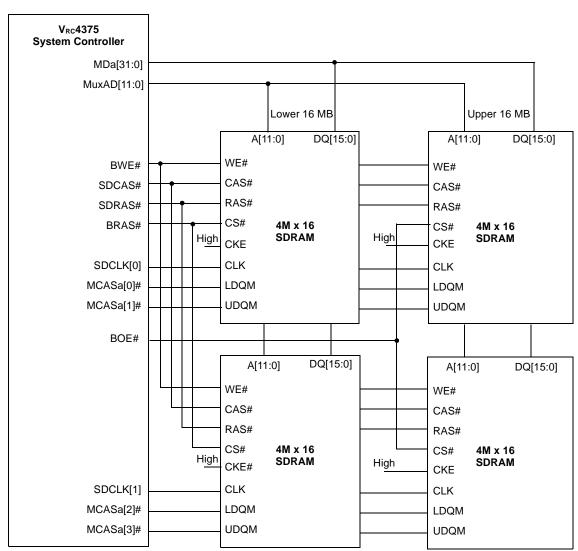

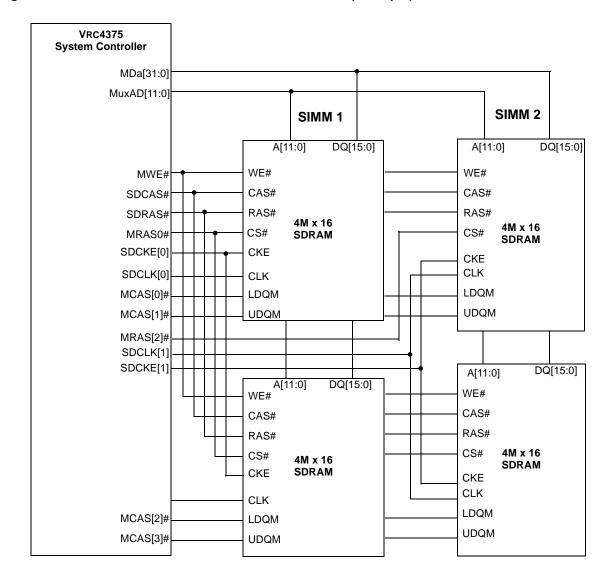

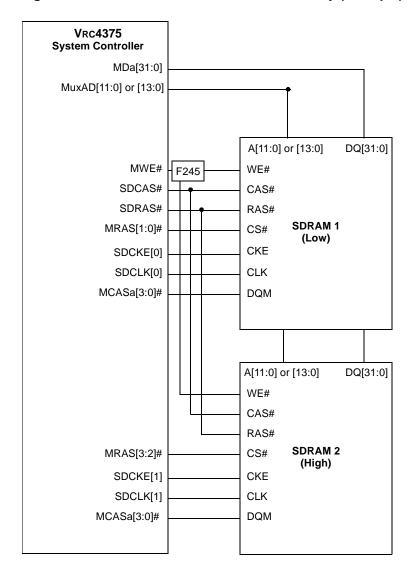

Figure 4 shows a block diagram of controller-to-memory connections for DRAM. Figure 6 on page 36 and Figure 7 on page 37 show examples of controller-to-memory connections for SDRAM.

A typical system with SDRAM in the base memory address range and SIMM memory address range is shown in Figure 4 on page 19.

Figure 4. Memory Block Diagram

## Address Multiplexing Modes

The controller supports four address multiplexing modes (mux modes) in the base memory and SIMM memory ranges. Table 8 shows these modes and the row address x column address configurations they support.

Table 8. Address Multiplexing Modes

| Address Multiplexing Mode | Row Address x Column Address Configurations |

|---------------------------|---------------------------------------------|

| Mux Mode 0                | 9 x 9                                       |

| Mux Mode 1                | 10 x 9, 10 x 10                             |

| Mux Mode 2                | 11 x 9, 11 x 10, 11 x 11                    |

| Mux Mode 3                | 12 x 9, 12 x 10, 12 x 11, 12 x 12           |

| Mux Mode 4                | 14 x 14 (64-/128-Mb SDRAMs only)            |

| Any mux mode              | 12 x 8, 11 x 8, 10 x 8                      |

Configuration of the address multiplexing modes is done in the Base Memory Control register (Section 6.7.1) and SIMM memory control registers (Section 6.8.1). The selection of mode determines which system address bits are output from the controller on the memory interface MuxAD bus during row and column addressing.

Table 9 shows the MuxAD-to-SysAD mapping for DRAM. When EDO DRAM is used for base memory, either the  $12 \times 8$  or  $10 \times 10$  configuration may be used. 16-/64-/128-Mb EDO devices are supported.

Table 9. MuxAD-to-SysAD Address Mapping for EDO DRAM

|         | SysAD Mapping |                |                 |                 |                 |  |  |

|---------|---------------|----------------|-----------------|-----------------|-----------------|--|--|

| MuxAD   |               | Column         | Column          |                 |                 |  |  |

| Signals | Row           | Mode 0<br>(x9) | Mode 1<br>(x10) | Mode 2<br>(x11) | Mode 3<br>(x12) |  |  |

| 0       | 11            | 3              | 3               | 3               | 3               |  |  |

| 1       | 12            | 4              | 4               | 4               | 4               |  |  |

| 2       | 13            | 5              | 5               | 5               | 5               |  |  |

| 3       | 14            | 6              | 6               | 6               | 6               |  |  |

| 4       | 15            | 7              | 7               | 7               | 7               |  |  |

| 5       | 16            | 8              | 8               | 8               | 8               |  |  |

| 6       | 17            | 9              | 9               | 9               | 9               |  |  |

| 7       | 10            | 2              | 2               | 2               | 2               |  |  |

| 8       | 18            | 19             | 20              | 21              | 22              |  |  |

| 9       | 19            | 20             | 21              | 22              | 23              |  |  |

| 10      | 20            | 21             | 22              | 23              | 24              |  |  |

| 11      | 21            | 22             | 23              | 24              | 25              |  |  |

Table 10 shows the MuxAD-to-SysAD mapping for SDRAM. When SDRAM is used in base memory, Mux Mode 3 must be used and 16-/64-/128-Mb SDRAM devices can be used.

Table 10. MuxAD-To-SysAD Address Mapping for SDRAM

|         | SysAD Mapping |                         |                                              |                                       |                                       |  |  |  |  |

|---------|---------------|-------------------------|----------------------------------------------|---------------------------------------|---------------------------------------|--|--|--|--|

| MuxAD   | Column        |                         |                                              |                                       |                                       |  |  |  |  |

| Signals | Row           | Mode 3<br>(16-Mb SDRAM) | Mode 4 <sup>1</sup><br>(64-/128-Mb<br>SDRAM) | Mode 5 <sup>2</sup><br>(128-Mb SDRAM) | Mode 6 <sup>3</sup><br>(256-Mb SDRAM) |  |  |  |  |

| 0       | 11            | 2                       | 2                                            | 2                                     | 2                                     |  |  |  |  |

| 1       | 12            | 3                       | 3                                            | 3                                     | 3                                     |  |  |  |  |

| 2       | 13            | 4                       | 4                                            | 4                                     | 4                                     |  |  |  |  |

| 3       | 14            | 6                       | 6                                            | 6                                     | 6                                     |  |  |  |  |

| 4       | 15            | 7                       | 7                                            | 7                                     | 7                                     |  |  |  |  |

| 5       | 16            | 8                       | 8                                            | 8                                     | 8                                     |  |  |  |  |

| 6       | 17            | 9                       | 9                                            | 9                                     | 9                                     |  |  |  |  |

| 7       | 10            | 5                       | 5                                            | 5                                     | 5                                     |  |  |  |  |

| 8       | 18            | 22                      | 24                                           | 24                                    | 24                                    |  |  |  |  |

| 9       | 19            | 23                      | 25                                           | 25                                    | 25                                    |  |  |  |  |

| 10      | 20            | Hardwired to 0          | Hardwired to 0                               | Hardwired to 0                        | Hardwired to 0                        |  |  |  |  |

| 11      | 21            | 21                      | 21                                           | 26                                    | 27                                    |  |  |  |  |

| 12      | 22            | 21                      | 22                                           | 22                                    | 22                                    |  |  |  |  |

| 13      | 23            |                         | 23                                           | 23                                    | 23                                    |  |  |  |  |

| 14      | 24            |                         | 24                                           | 24                                    | 24                                    |  |  |  |  |

Notes:

- 1. 16-Mb SDRAM can be used in either the base memory or SIMM ranges. 64-Mb, 4-bank SDRAMs are supported only in SIMM and base memory regions. It can also drive 1 M x 32-bit memory devices.

- 2. Mux Mode 5 is used to drive 4-bank, 128-Mb memory devices. These devices can be organized in x4, x8, x16, and x32 configurations.

- **3.** Mux Mode 6 is used to drive 4-bank, 256-Mb devices. These devices can be organized in x4, x8, x16, and x32 configurations.

## Memory Performance

Memory access speed is determined by memory type and speed. Table 11 lists examples of 66-MHz memory bus clock cycles required for each 8-word (32-byte) CPU instruction cache line fill transfer. The first number in the "SysAD CPU Clocks (66 MHz)" column is for the first word; the remaining numbers are for the subsequent words. Only the most common combinations are shown.

Refer to more details in Section 6.7.1 and Section 6.8.1.

Read performance is calculated by counting the rising edge for MCLK, where the read command is issued by the CPU. Because the CPU issues write data with no wait states once the write command is issued, the numbers in the table represent the rate at which data is written to memory. The sum of the numbers represents the number of cycles between when the write operation was issued and when the next CPU memory operation can begin. Table 11 provides examples of memory performance.

Table 11. Examples of Memory Performance

| Memory Type/<br>Speed | CAS Latency   | Page<br>Mode | Page<br>Hit | R/W | Sequential<br>Addresses | Base or<br>SIMM<br>Memory | SysAD CPU<br>Clocks (66 MHz)      |

|-----------------------|---------------|--------------|-------------|-----|-------------------------|---------------------------|-----------------------------------|

| SDRAM, 10 ns          | No, $CAS = 3$ | No           | No          | R   | No                      | Base                      | 7-1-1-1-1-1                       |

| SDRAM, 10 ns          | No, $CAS = 3$ | No           | No          | W   | No                      | Base                      | 5-1-1-1-1-1                       |

| SDRAM, 10 ns          | No, CAS = 3   | No           | No          | R   | No                      | SIMM                      | 10-2-2-2-2-2-2 or<br>10-1-1-1-1-1 |

| SDRAM, 10 ns          | No, CAS = 3   | No           | No          | W   | No                      | SIMM                      | 6-2-2-2-2-2 or<br>6-1-1-1-1-1-1   |

| SDRAM, 10 ns          | No, CAS = 2   | No           | No          | R   | No                      | Base                      | 6-1-1-1-1-1                       |

| SDRAM, 10 ns          | No, CAS = 2   | No           | No          | W   | No                      | Base                      | 5-1-1-1-1-1                       |

| SDRAM, 10 ns          | No, CAS = 2   | No           | No          | R   | No                      | SIMM                      | 8-1-1-1-1-1                       |

| SDRAM, 10 ns          | No, CAS = 2   | No           | No          | W   | No                      | SIMM                      | 6-1-1-1-1-1                       |

| EDO, 60 ns            | No            | No           | No          | R   |                         | Base                      | 9-2-2-2-2-2                       |

| EDO, 60 ns            | No            | No           | No          | W   | Not applicable          | Base                      | 7-2-2-2-2-2                       |

| EDO, 60 ns            | No            | No           | No          | R   |                         | SIMM                      | 11-4-4-4-4-4                      |

| EDO, 60 ns            | No            | No           | No          | W   |                         | SIMM                      | 9-4-4-4-4-4                       |

| Fast-page, 70 ns      | No            | No           | No          | R   |                         | SIMM                      | 11-5-5-5-5-5                      |

| Fast-page, 70 ns      | No            | No           | No          | W   |                         | SIMM                      | 10-5-5-5-5-5                      |

| Flash/SRAM/I/O        | No            | No           | No          | R   |                         |                           | 13-7-7-7-7-7                      |

| Flash/SRAM/I/O        | No            | No           | No          | W   |                         |                           | 11-6-6-6-6-6-6                    |

## Placement, Loading, and Example Delays

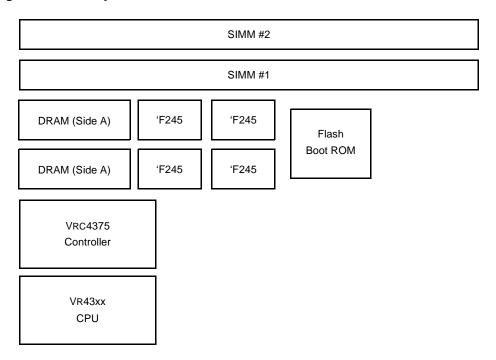

Figure 5 shows the physical placement recommendations for motherboard chips. Table 12 shows minimum and maximum AC loadings for the memory interface signals. Table 13 shows example trace delays between memory and the controller.

Figure 5. Memory Placement

Table 12. Memory Signal AC Loading

| Signal       | Min.<br>(pF) | Max.<br>(pF) | Description                                          |

|--------------|--------------|--------------|------------------------------------------------------|

| MuxAD[25:15] | 10           | 50           | ROM address upper bits                               |

| MuxAD[14:00] | 10           | 70           | Multiplexed row/column address, ROM address low bits |

| BRAS#        | 5            | 50           | Base memory row address strobe                       |

| MRAS[3:0]#   | 15           | 70           | SIMM memory row address strobes                      |

| MCASa[3:0]#  | 20           | 70           | Column address strobe, even addresses                |

| MWE#         | 10           | 30           | Boot ROM and SIMM write enable                       |

| BOE#         | 10           | 50           | Base memory output enable                            |

| ROE#         | 10           | 30           | ROM/flash output enable                              |

| BWE#         | 10           | 50           | Base memory write enable                             |

| BROMCS#      | 10           | 30           | Boot ROM chip select                                 |

| MDa[31:0]    | 20           | 70           | Memory data, boot ROM data                           |

| SDCLK[1:0]   | 10           | 50           | 66-MHz SDRAM clock                                   |

| SDCKE[1:0]   | 10           | 70           | SDRAM clock enable                                   |

| SDCS[1:0]#   | 10           | 50           | SDRAM command select                                 |

| SDCAS#       | 20           | 50           | SDRAM column address strobe                          |

| SDRAS#       | 20           | 50           | SDRAM row address strobe                             |

Table 13. Example SIMM DRAM Delays

| Signal                   | Source                                      | Destination                                   | Delay Subtotal<br>(120 ps/inch) | RC Delay<br>(2 x R x C)  | Total<br>Delay <sup>1</sup> |

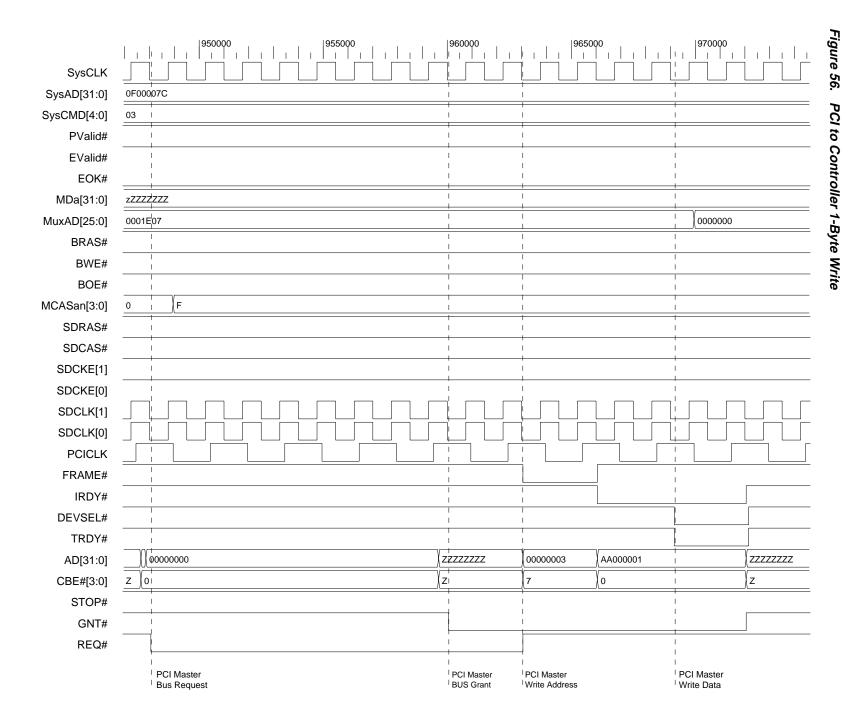

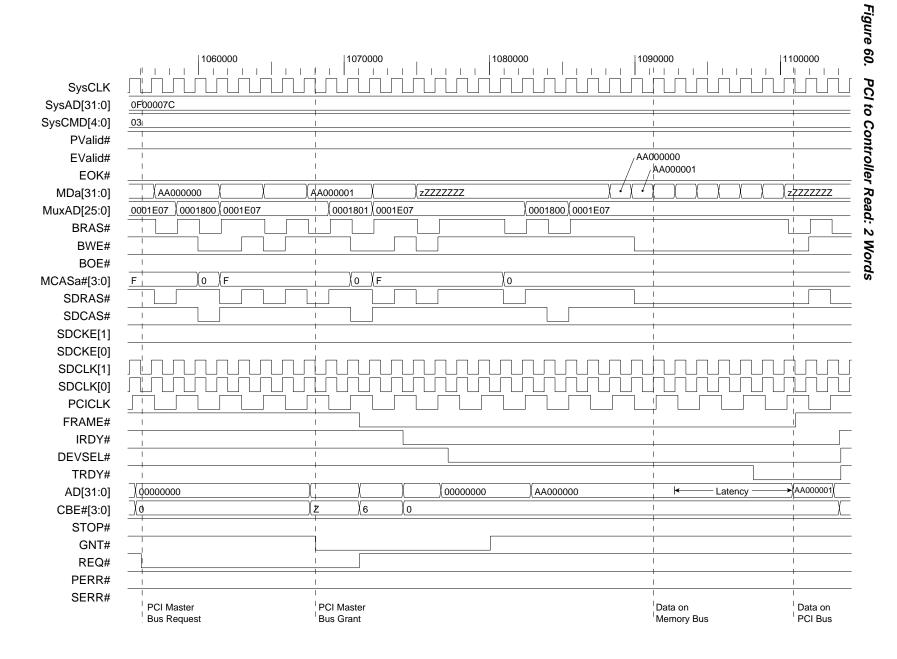

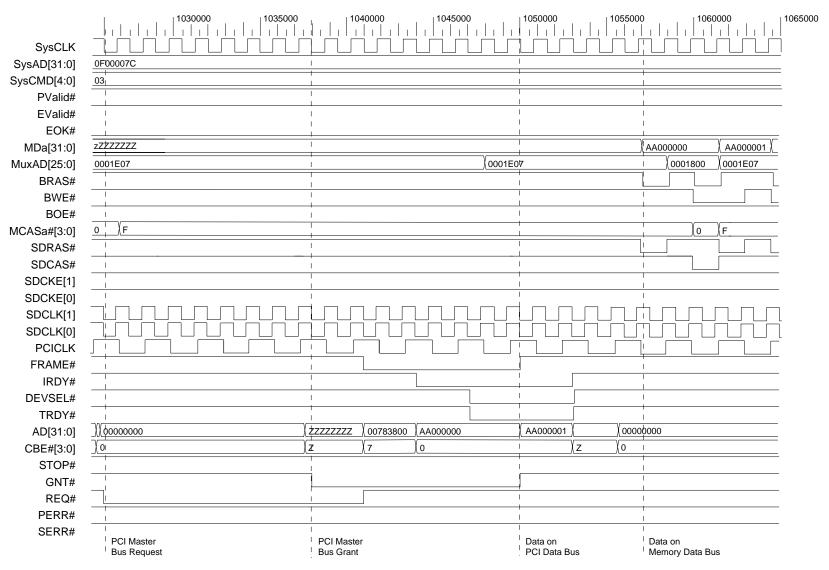

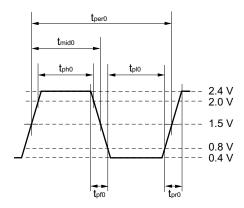

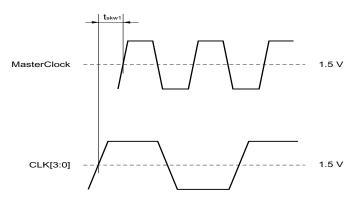

|--------------------------|---------------------------------------------|-----------------------------------------------|---------------------------------|--------------------------|-----------------------------|