INTEGRATED CIRCUITS

# DATA HANDBOOK

FAST Logic Supplement

Signetics Philips Components

# FAST Logic Supplement

Signetics

Philips Components

Signetics reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Signetics Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics customers using or selling Signetics Products for use in such applications do so at their own risk and agree to fully indemnify Signetics for any damages resulting from such improper use or sale.

Signetics registers eligible circuits under the Semiconductor Chip Protection Act.

© Copyright 1990 NAPC.

All rights reserved.

# PREFACE

Since the publication of the 1989 FAST Logic Data Handbook, twentyfour new products have been released. Product specifications for these products are contained in this supplement and supercede any previously published "Preliminary Specifications".

| 74F189A | 74F711 | 74F1763 | 74F8960  |

|---------|--------|---------|----------|

| 74F219A | 74F712 | 74F1766 | 74F8962  |

| 74F646A | 74F723 | 74F3893 | 74F8963  |

| 74F648A | 74F725 | 74F5074 | 74F50109 |

| 74F651A | 74F777 | 74F5300 | 74F50728 |

| 74F652A | 74F807 | 74F5302 | 74F50729 |

A series of Industrial Temperature part types, guaranteed over an extended temperature range of -40°C to +85°C (instead of the traditional temperature range of 0°C to + 70°C) has also been released. Specifications for these parts and ordering information has been added to the existing data sheets. An "I" prefix has been added to designate the industrial temperature range part types:

| 174F86  | 174F244B | 174F656A | 174F3037 |

|---------|----------|----------|----------|

| 174F112 | 174F280B | 174F657  |          |

| I74F175 | 174F655A | 174F776  |          |

Development of the following part types listed as "preliminary" in the 1989 FAST Logic Data Handbook has been discontinued and these should not be considered as valid part types:

74F657A 74F1761 74F4763

Additional changes, corrections, or additions to existing specifications have been made and are included in this supplement for reference. Only those pages of individual product specifications which had a change, correction, pr addition are included along with the first page of the product specification. All revised areas have been highlighted by a bold dotted square to facilitate locating the change.

Four application notes AN219, AN222, AN220 and AN222 which support the 74F50XXX family are contained in this supplement. These application notes are not in the 1989 FAST Data Manual.

This booklet is a supplement to the 1989 FAST Logic Data Handbook and should be used in conjunction with it.

# **Product Status**

### FAST Logic Products

| DEFINITIONS                  |                        |                                                                                                                                                                                                                                                          |  |  |  |

|------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Data Sheet<br>Identification | Product Status         | Definition                                                                                                                                                                                                                                               |  |  |  |

| Objective Specification      | Formative or In Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                                       |  |  |  |

| Preliminary Specification    | Preproduction Product  | This data sheet contains preliminary data and<br>supplementary data will be published at a later date.<br>Signetics reserves the right to make changes at any time<br>without notice in order to improve design and supply the best<br>possible product. |  |  |  |

| Product Specification        | Full Production        | This data sheet contains Final Specifications. Signetics<br>reserves the right to make changes at any time without notice<br>in order to improve design and supply the best possible<br>product.                                                         |  |  |  |

### TABLE OF CONTENTS

| PART NO.         | DATE REV. | DESCRIPTION OF ADDITION/CHANGE                                                                                                      | PAGE     |

|------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

| 74F06            | 11/07/90  | DC Electrical Characteristics (Vol - Max Low-level output voltage)                                                                  | 1        |

| 74F07            |           | DC Electrical Characteristics (Vol - Max Low-level output voltage)                                                                  | 1        |

| 74F07<br>74F74   |           | Logic Symbol (Pins 11, 10, 13), AC Waveforms (Dn)                                                                                   | 3        |

| 74F85            | 4/27/00   | I/O loading & Fan-Out table, Logic Diagram (pin3), Ordering Info. (SOL)                                                             | 5        |

| 74F86            |           | Added feature of Industrial Temperature Range (-40 to +85 C)                                                                        | 7        |

| 74F112           |           | Added feature of Industrial Temperature Range (-40 to +65 C)                                                                        | 9        |

| 74F132           |           | Accelectrical Characteristics (Propagation Delays)                                                                                  | 11       |

| 74F132           |           | I/O loading & Fan-Out table (pins)                                                                                                  | 13       |

| 74F139           |           | I/O loading & Fan-Out table (Load value H/L)                                                                                        | 14       |

| 74F155           |           | Fctn. Table (A Inputs)                                                                                                              | 15       |

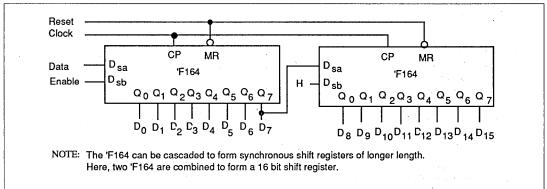

| 74F164           |           | Ordering Info. (SO), AC Elec. Char. (Prop Delay, MR to Qn)                                                                          | 17       |

| 74F175           |           | Text (Features), Table 2 (Ind. Temp Spec), AC Elec. Char., AC Set-Up Rec.                                                           | 19       |

| 74F189A          |           | New Product Specification                                                                                                           | 21       |

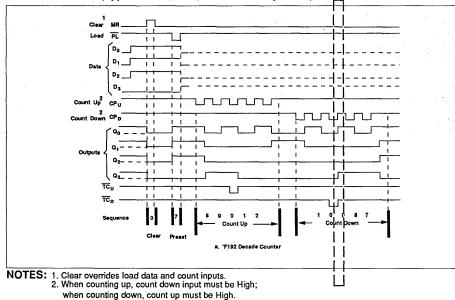

| 74F192           |           | Timing Diagram (TCD & Q3)                                                                                                           | 27       |

| 74F195           | 10/5/80   | AC Electrical Characteristics (Propagation Delay, CP to Qn)                                                                         | 29       |

| 74F219A          |           | New Product Specification                                                                                                           | 31       |

| 74F219A          |           | AC Electrical Characteristics (propagation delays)                                                                                  | 37       |

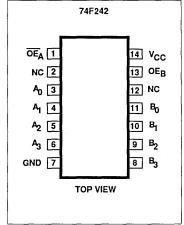

| 74F242           |           | AC Electrical Characteristics (propagation delays)<br>AC Electrical Characteristics (propagation delays on the 242 only)            | 37       |

| 74F244           |           | Added feature of Industrial Temperature Range (-40 to +85 C)                                                                        | 39       |

| 74F251           |           | AC Electrical Characteristics (Output Disable Time, Output Enable Time)                                                             | 41       |

| 74F251A          |           | AC Electrical Characteristics (On the 251 only)                                                                                     | 41       |

| 74F257           |           | Logic Diagram (Nor gates changed to OR gates)                                                                                       | 41       |

| 74F257<br>74F269 |           |                                                                                                                                     | 45       |

| 74F289           | 2/9/90    | Logic Diagram, Application (Cascading Diagram)<br>AC Elec. Char. (Prop. Delay, In-SigE), DC Elec. Char. (High Level Input Current). | 45       |

|                  |           |                                                                                                                                     | 48       |

| 74F280B          |           | Added feature of Industrial Temperature Range (-40 to +85 C)                                                                        | 40<br>51 |

| 74F298<br>74F299 |           | AC Electrical Characteristics (fmax)                                                                                                | 53       |

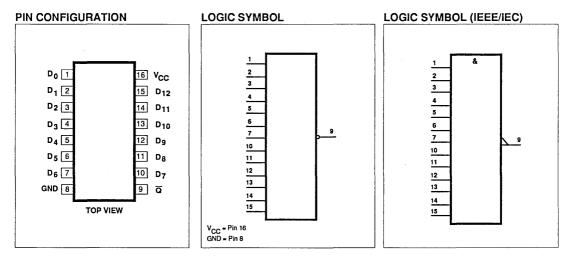

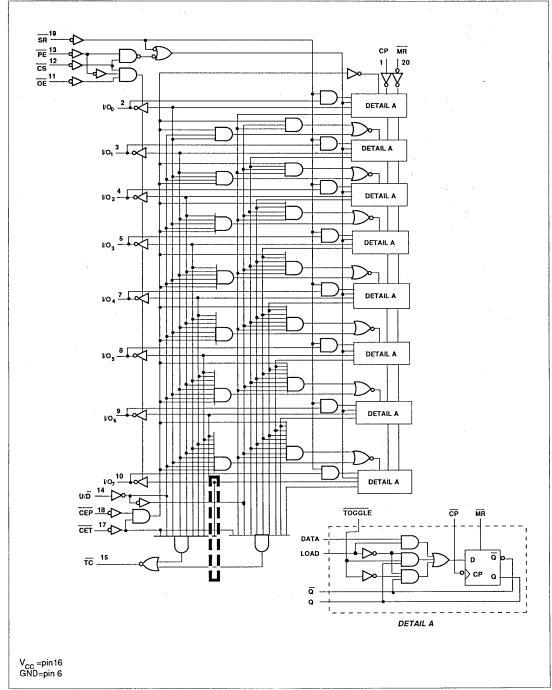

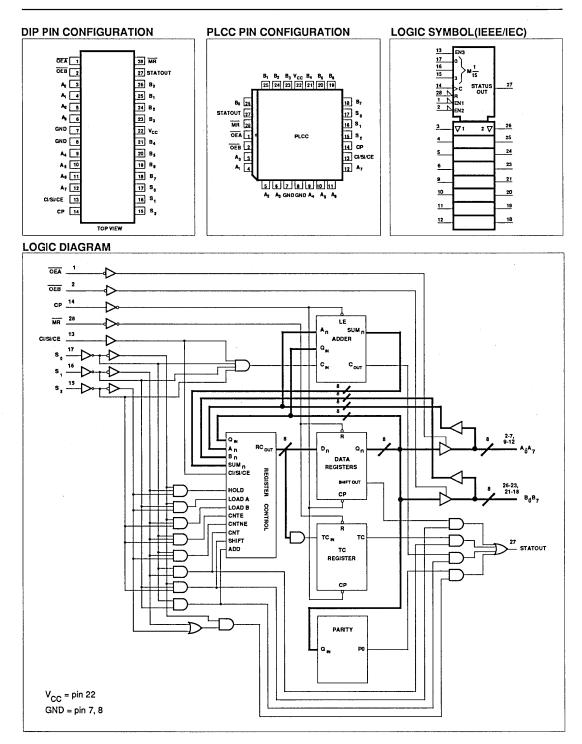

| 74F299<br>74F323 |           | I/O loading & Fan-Out table, Pin Conf., Logic Symbol, Logic Diagram, Fctn. Table                                                    | 56       |

| 74F323           |           | I/O loading & Fan-Out table, Pin Conf., Logic Symbol, Logic Diagram, Fctn. Table                                                    | 59       |

|                  |           | AC Electrical Characteristics (OE Time to High or Low Level)                                                                        | 59       |

| 74F366           |           | AC Electrical Characteristics (OE Time to High or Low Level)                                                                        |          |

| 74F367           |           | AC Electrical Characteristics (OE Time to High or Low Level)                                                                        | 59       |

| 74F368           |           | AC Electrical Characteristics (OE Time to High or Low Level)                                                                        | 59       |

| 74F373           |           | Table 1 & 2 (Propagation delay & fmax)                                                                                              | 61       |

| 74F374           |           | Table 1 & 2 (Propagation delay & fmax)                                                                                              | 61       |

| 74F378           |           | Text (Features)                                                                                                                     | 62       |

| 74F410           |           | Text (Functional Description)                                                                                                       | 63       |

| 74F524           |           | I/O loading & Fan-Out table (C/SO - Def.)                                                                                           | 65       |

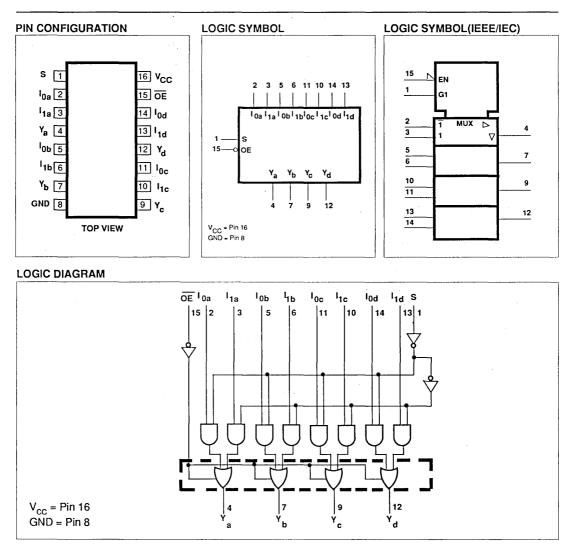

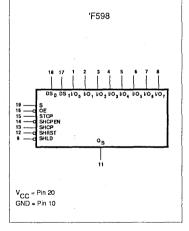

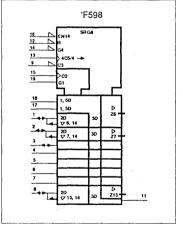

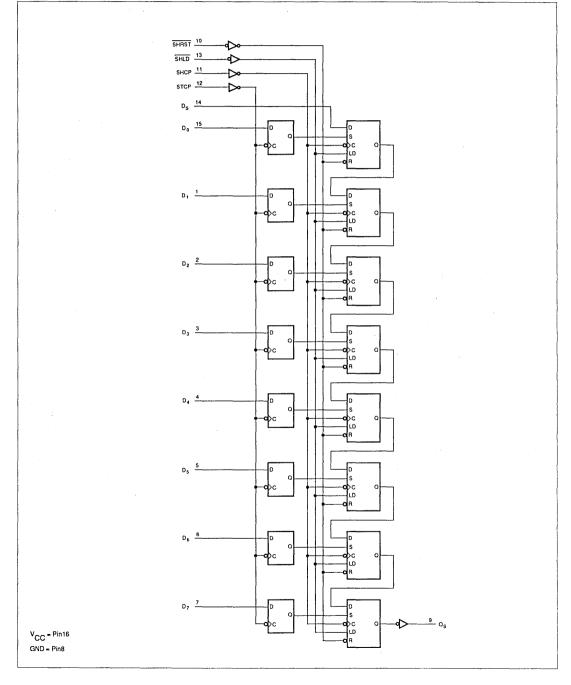

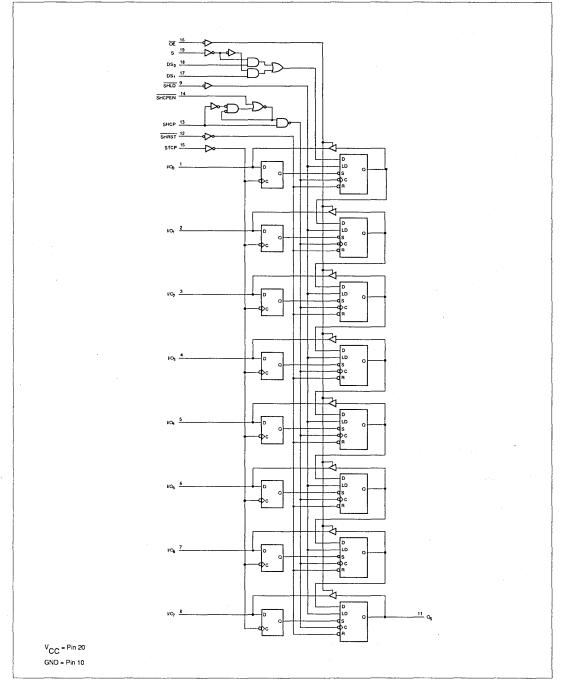

| 74F539           |           | Pin Conf., Logic Symbol, Logic Diagram (Pin No.)                                                                                    | 66       |

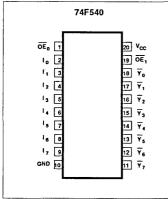

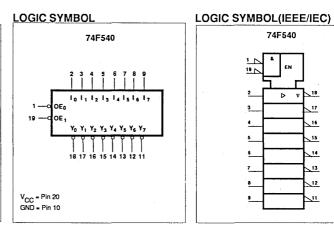

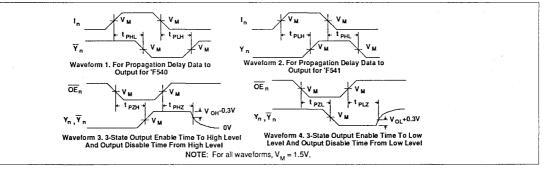

| 74F540           |           | AC Electrical Characteristics (OE Time to High or Low Level)                                                                        | 68       |

| 74F541           |           | AC Electrical Characteristics (OE Time to High or Low Level) On the 540 only                                                        | 68       |

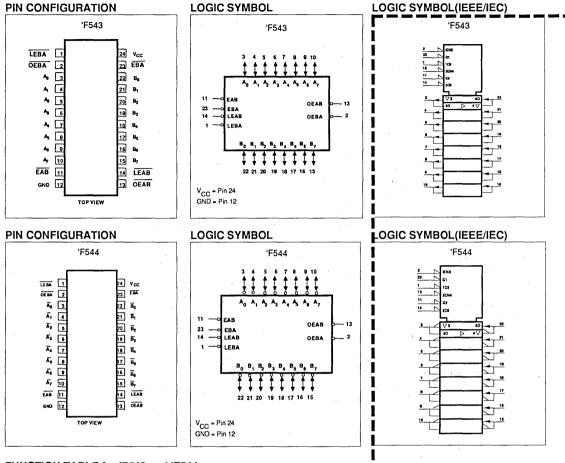

| 74F543           |           | IEEE/IEC Logic Symbol                                                                                                               | 70       |

| 74F544           |           | IEEE/IEC Logic Symbol                                                                                                               | 70       |

| 74F552           |           | I/O loading & Fan-Out table (Def.)                                                                                                  | 72       |

| 74F563           |           | Table 1&2 (Prop delay & fmax), I/O table & Fan-out, AC Elec Char, AC Set-Up Req                                                     | 73       |

| 74F564           |           | Table 1&2 (Prop delay & fmax), I/O table & Fan-out, AC Elec Char, AC Set-Up Req                                                     | 73       |

| 74F573           |           | DC Elec. Char. (Icc), AC Elec. Char. (F574 only), Tables 1,2, AC Set-Up Rec.                                                        | 74-1     |

| 74F574           |           | DC Elec. Char. (lcc), AC Elec. Char. Tables 1,2 , AC Set-Up Rec                                                                     | 74-1     |

| 74F579           |           | AC Elec. Char., AC Set-Up Req., Logic Diagram                                                                                       | 75       |

| 74F582           |           | Text (Description)                                                                                                                  | 79       |

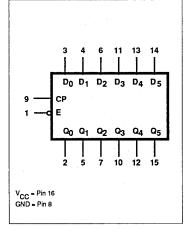

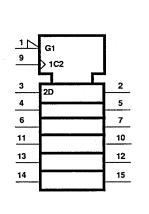

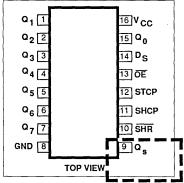

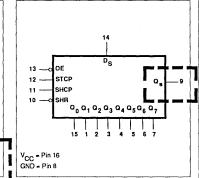

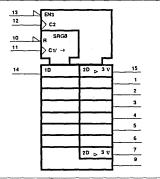

| 74F595           | 4/18/90   | AC Elec. Char, AC Set-Up Req., Pin Conf., Logic Symbol (pin 9)                                                                      | 80       |

### TABLE OF CONTENTS

| PART NO.  | DATE REV. | DESCRIPTION OF ADDITION/CHANGE                                                       | PAGE |

|-----------|-----------|--------------------------------------------------------------------------------------|------|

|           |           |                                                                                      |      |

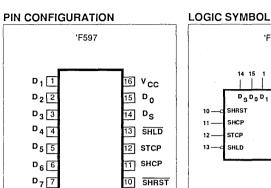

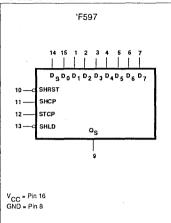

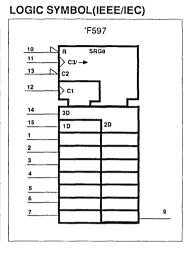

| 74F597    |           | Updated Preliminary Specification                                                    | 82   |

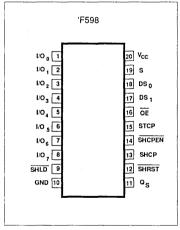

| 74F598    |           | Updated Preliminary Specification                                                    | 82   |

| 74F604    | 3/1/90    | Text (Title, Description), Logic symbol (IEE/IEC), AC Elec. Char., I/O loading table | 92   |

| 74F605    |           | Text (Title, Description), Logic symbol (IEE/IEC), AC Elec. Char., I/O loading table | 96   |

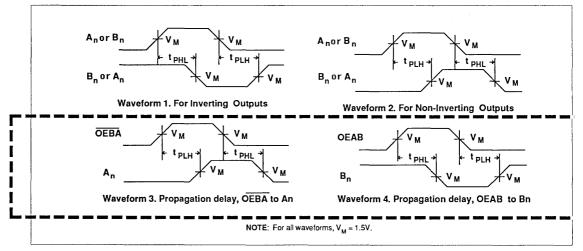

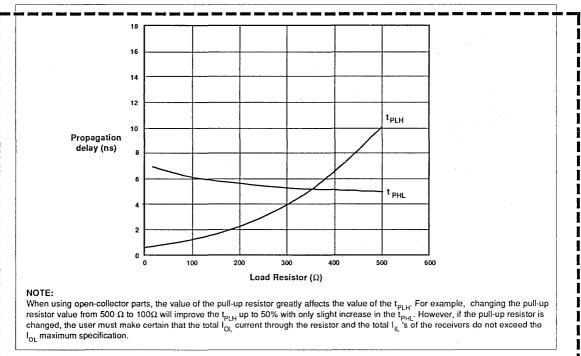

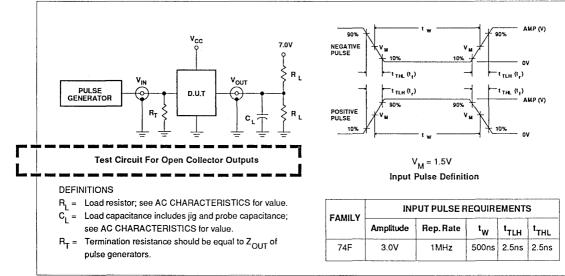

| 74F621    |           | Text (featues), Test Ckt & Waveforms, Graph, AC Waveforms                            | 99   |

| 74F622    |           | Text (featues), Test Ckt & Waveforms, Graph, AC Waveforms                            | 99   |

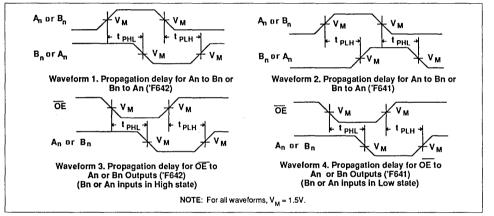

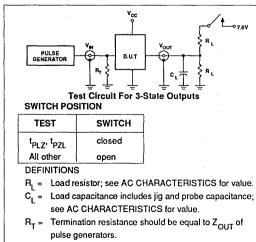

| 74F640    |           | AC Electrical Characteristics                                                        | 102  |

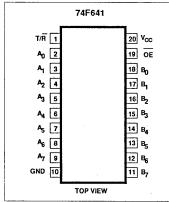

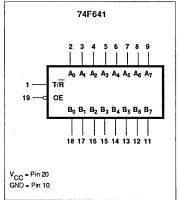

| 74F641    |           | AC Electrical Characteristics                                                        | 104  |

| 74F642    |           | AC Electrical Characteristics                                                        | 104  |

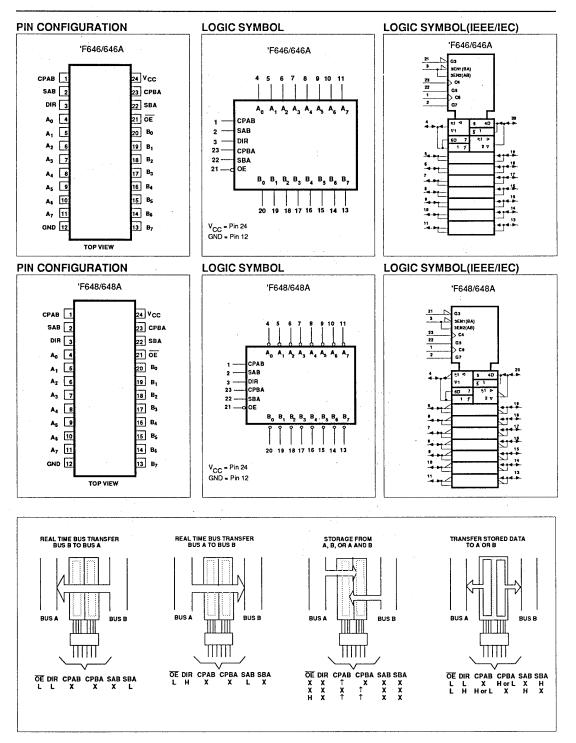

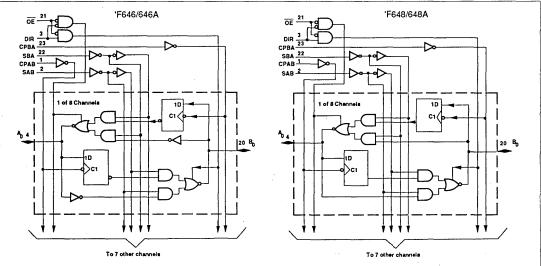

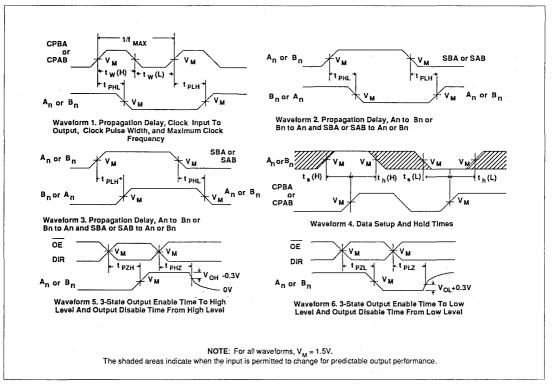

| 74F646    |           | AC/DC Elec. Char., Rec. Oper. Cond., Fctn Table (first two rows)                     | 107  |

| 74F646A   |           | New Product Specification                                                            | 107  |

| 74F648    |           | AC/DC Elec. Char., Rec. Oper. Cond., Fctn Table (first two rows)                     | 107  |

| 74F648A   |           | New Product Specification                                                            | 107  |

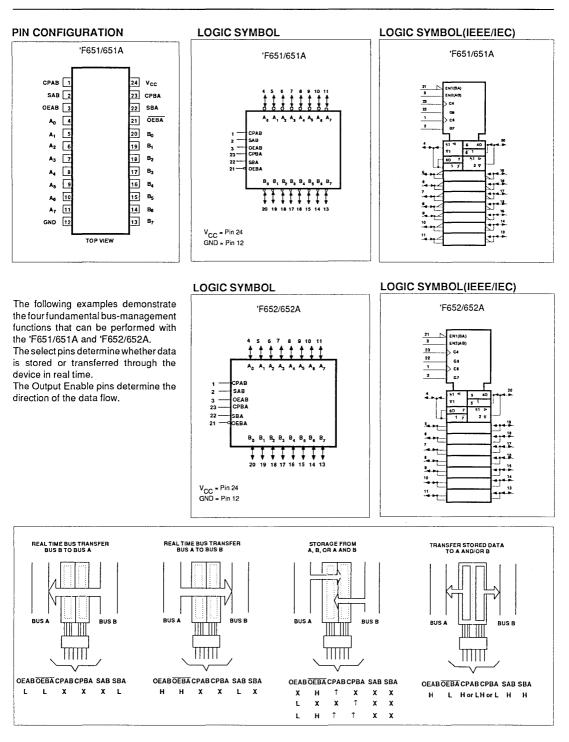

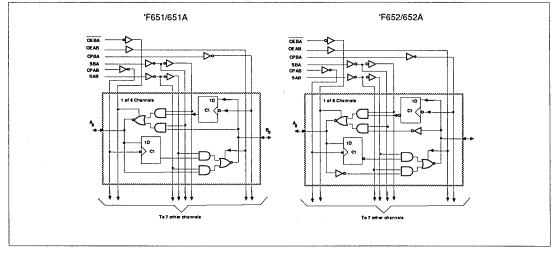

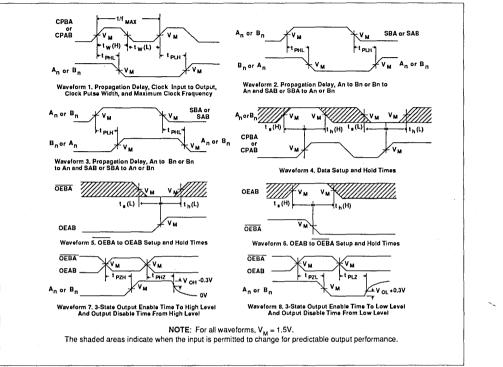

| 74F651    |           | Text (Features), DC Elec. Char. (Io)                                                 | 116  |

| 74F651A   |           | New Product Specification                                                            | 116  |

| 74F652    |           | Text (Features), DC Elec. Char. (Io)                                                 | 116  |

| 74F652A   |           | New Product Specification                                                            | 116  |

| 74F655A   |           | Added feature of Industrial Temperature Range (-40 to +85 C)                         | 124  |

| 74F656A   |           | Added feature of Industrial Temperature Range (-40 to +85 C)                         | 124  |

| 74F657    | 3/19/90   | Text (Features), Ordering Info. (Ind. Temp), AC/DC Elec. Char.,                      | 127  |

| 74F657A   |           | Deleted Part type                                                                    |      |

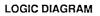

| 74F676    |           | Logic Diagram                                                                        | 134  |

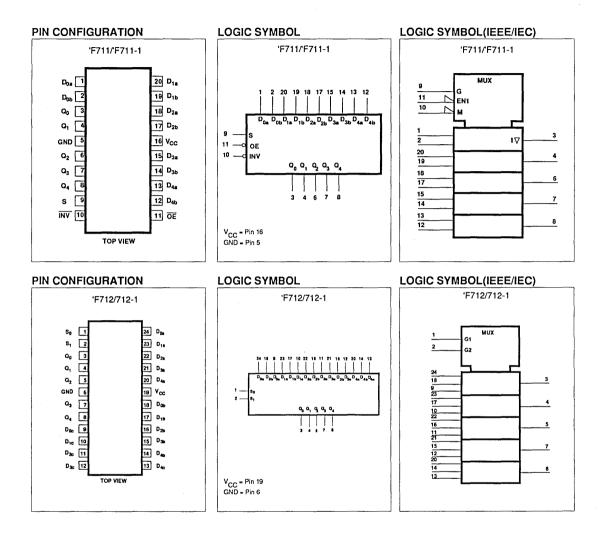

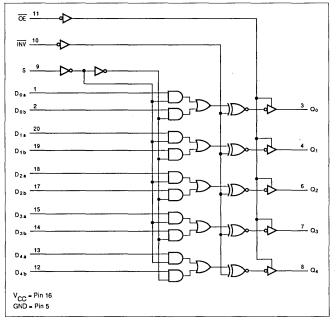

| 74F711    |           | New Product Specification                                                            | 136  |

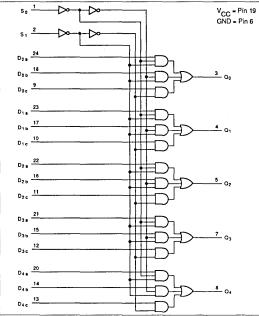

| 74F712    |           | New Product Specification                                                            | 136  |

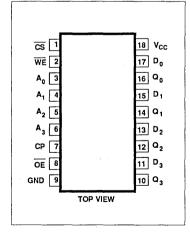

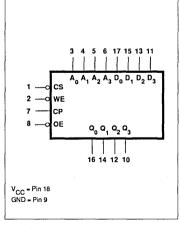

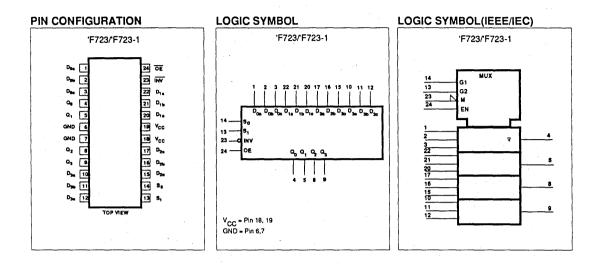

| 74F723    | 9/20/89   | New Product Specification                                                            | 143  |

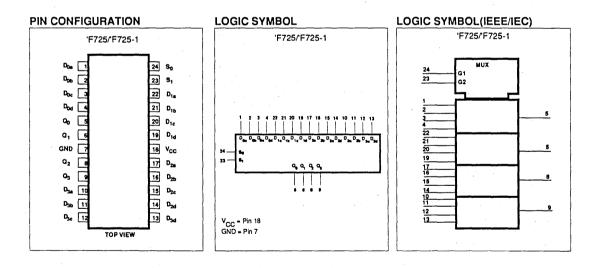

| 74F725    | 9/20/89   | New Product Specification                                                            | 143  |

| 74F776    | 1/29/89   | Added feature of Industrial Temperature Range (-40 to +85 C)                         | 151  |

| 74F777    | 2/27/90   | New Product Specification                                                            | 153  |

| 74F779    | 9/20/89   | Text (Features),                                                                     | 160  |

| 74F786    | 9/27/89   | AC Electrical Characteristics                                                        | 161  |

| 74F807    | 4/27/90   | New Product Specification                                                            | 163  |

| 74F821    | 4/27/90   | AC Set-Up Req., DC Elec. Char., Fctn Table notes,                                    | 170  |

| 74F822    | 4/27/90   | AC Set-Up Req., DC Elec. Char., Fctn Table notes,                                    | 170  |

| 74F823    | 4/27/90   | AC Set-Up Req., DC Elec. Char., Fctn Table notes,                                    | 170  |

| 74F824    |           | AC Set-Up Req., DC Elec. Char., Fctn Table notes,                                    | 170  |

| 74F825    | 4/27/90   | AC Set-Up Req., DC Elec. Char., Fctn Table notes,                                    | 170  |

| 74F826    |           | AC Set-Up Req., DC Elec. Char., Fctn Table notes,                                    | 170  |

| 74F835    |           | Text (Features), Table 1, AC/DC Elec. Char., AC Set-UP Req.                          | 174  |

| 74F841    |           | AC Waveforms                                                                         | 177  |

| 74F842    |           | AC Waveforms                                                                         | 177  |

| 74F843    |           | AC Waveforms                                                                         | 177  |

| 74F844    |           | AC Waveforms                                                                         | 177  |

| 74F845    |           | AC Waveforms                                                                         | 177  |

| 74F846    |           | AC Waveforms                                                                         | 177  |

| 74F1604   |           | Pin Configuration                                                                    | 179  |

| 74F1760   |           | Updated Preliminary Specification                                                    | 180  |

| 74F1761   |           | Deleted Part type                                                                    | 1    |

| 74F1763   | 11/17/89  | New Product Specification                                                            | 187  |

| 74F1764   |           | DC Elec. Char. (Vol)                                                                 | 199  |

| 74F1764-1 |           | DC Elec. Char. (Vol)                                                                 | 199  |

### TABLE OF CONTENTS

| ART NO.  | DATE REV. | DESCRIPTION OF ADDITION/CHANGE                                      | PAGE  |

|----------|-----------|---------------------------------------------------------------------|-------|

|          |           |                                                                     |       |

| 1F1765   |           | DC Elec. Char. (Vol)                                                | 199   |

| 1F1765-1 | 5/17/90   | DC Elec. Char. (Vol)                                                | 199   |

| 1F1766   |           | New Product Specification                                           | 200-1 |

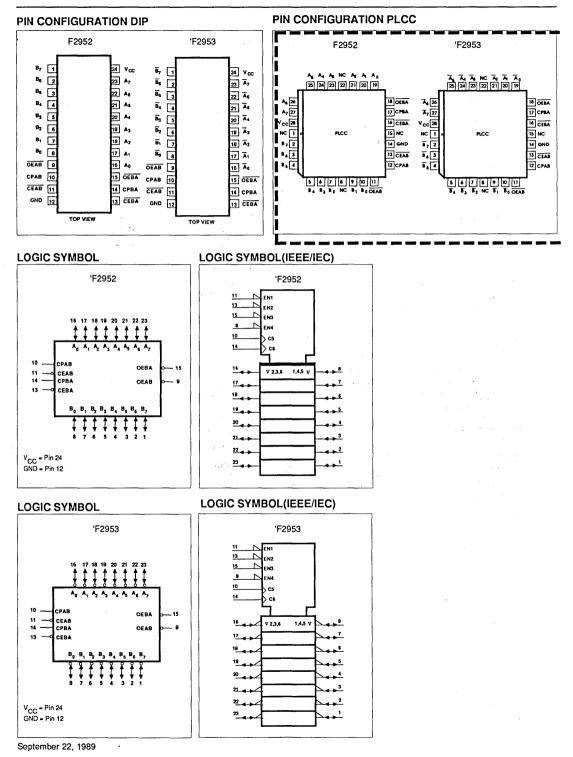

| 1F2952   |           | Ordering Info., Pin Conf.                                           | 201   |

| 1F2953   |           | Ordering Info., Pin Conf.                                           | 201   |

| 1F3037   |           | Added feature of Industrial Temperature Range (-40 to +85 C)        | 203   |

| 1F3038   |           | AC Electrical Characteristics, Ordering Info.                       | 206   |

| 1F3040   |           | Ordering Info., AC/DC Electrical Characteristics                    | 208   |

| 1F3893   | 9/15/89   | New Product Specification                                           | 210   |

| 1F4763   |           | Deleted Part type                                                   |       |

| 1F5074   | 1/8/90    | New Product Specification                                           | 215   |

| 1F5300   | 12/13/89  | New Product Specification                                           | 222   |

| IF5302   | 1/8/90    | New Product Specification                                           | 228   |

| IF8960   | 11/27/89  | New Product Specification                                           | 235   |

| IF8961   | 11/27/89  | Recommended Oper. Cond., AC Waveforms                               | 235   |

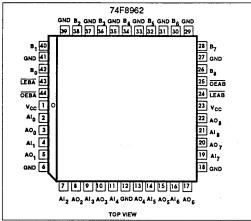

| IF8962   | 4/18/90   | New Product Specification                                           | 246   |

| IF8963   | 4/18/90   | New Product Specification                                           | 246   |

| IF30240  | 9/15/89   | Ordering Info.                                                      | 256   |

| IF30244  |           | Ordering Info.                                                      | 256   |

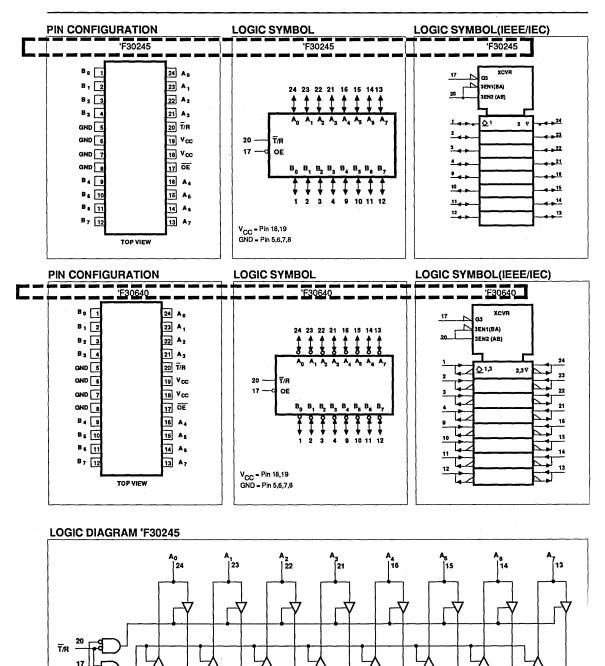

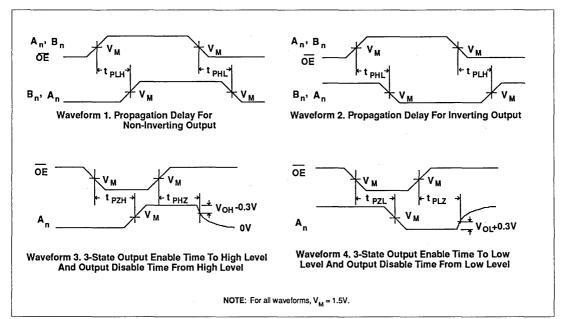

| F30245   | 4/18/90   | Pin Conf., Logic Symbol, Logic Symbol (IEEE/IEC), AC Elec. Char.    | 257   |

| IF30640  | 4/18/90   | Pin Conf., Logic Symbol, Logic Symbol (IEEE/IEC), AC Elec. Char.    | 257   |

| F50109   | 1/8/90    | New Product Specification                                           | 260   |

| F50728   | 3/19/90   | New Product Specification                                           | 267   |

| F50729   | 5/3/90    | New Product Specification                                           | 273   |

| V219     | Nov-89    | A Metastability Primer                                              | 280   |

| 1220     | Sep-89    | Synchronizing and Clock Driving Solutions Using the 74F50XXX Family | 285   |

| 1221     | Jan-90    | Multiplying and Dividing Clock Frequencies Using the 74F50729       | 290   |

| 1222     | Jan-90    | Eliminating Glitches Using the 74F50XXX Family                      | 293   |

.

| Document No.  | 853-1122              |

|---------------|-----------------------|

| ECN No.       | 98618                 |

| Date of issue | November 27, 1989     |

| Status        | Product Specification |

### FEATURES

- Open Collector output drive 64mA

- · High speed

- 12V output termination voltage

- Symmetrical propagation delays

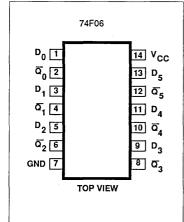

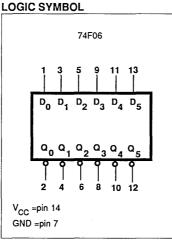

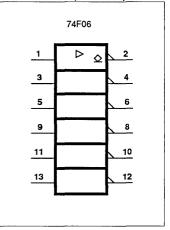

# FAST 74F06, 74F07 Inverter/Buffer/Drivers

74F06 Hex Inverter Buffer/Driver (Open Collector) 74F07 Hex Buffer/Driver (Open Collector)

| ТҮРЕ  | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|-------|------------------------------|-----------------------------------|

| 74F06 | 3.5ns                        | 18mA                              |

| 74F07 | 4.5ns                        | 21mA                              |

### ORDERING INFORMATION

| PACKAGES           | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%; T <sub>A</sub> = 0°C to +70°C |

|--------------------|-----------------------------------------------------------------------------|

| 14-Pin Plastic DIP | N74F06N, N74F07N                                                            |

| 14-Pin Plastic SO  | N74F06D, N74F07D                                                            |

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS           | DESCRIPTION        | 74F(U.L.)<br>HIGH/LOW | LOAD VALUE<br>HIGH/LOW |

|----------------|--------------------|-----------------------|------------------------|

| D <sub>n</sub> | Data input         | 1.0/1.0               | 20µA/0.6mA             |

| ā              | Data output ('F06) | OC/106.7              | OC/64mA                |

| Q <sub>n</sub> | Data output ('F07) | OC/106.7              | OC/64mA                |

NOTE:

1. One (1.0) FAST Unit Load is defined as:  $20\mu A$  in the High state and 0.6mA in the Low state.

2. OC = Open Collector.

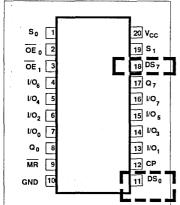

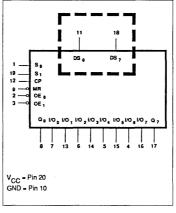

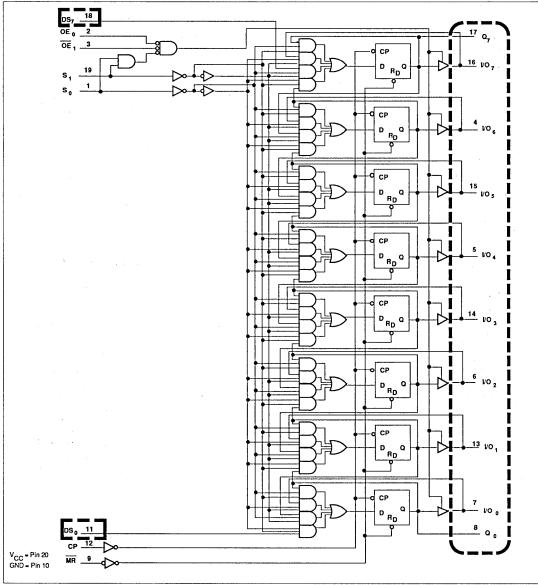

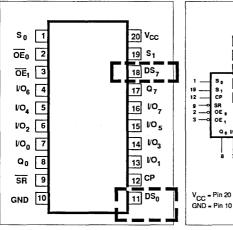

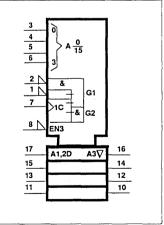

### **PIN CONFIGURATION**

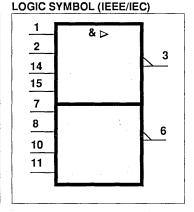

### LOGIC SYMBOL(IEEE/IEC)

### Inverter/Buffer/Drivers

### 74F06,74F07

### RECOMMENDED OPERATING CONDITIONS

|                 |                                      |     | LIMITS |     |      |  |

|-----------------|--------------------------------------|-----|--------|-----|------|--|

| SYMBOL          | PARAMETER                            | Min | Nom    | Max | UNIT |  |

| V <sub>cc</sub> | Supply voltage                       | 4.5 | 5.0    | 5.5 | v    |  |

| V <sub>IH</sub> | High-level input voltage             | 2.0 |        |     | v    |  |

| V <sub>IL</sub> | Low-level input voltage              |     |        | 0.8 | V    |  |

| I <sub>IK</sub> | Input clamp current                  |     |        | -18 | mA   |  |

| V <sub>OH</sub> | High-level output voltage            |     |        | 12  | v    |  |

| I <sub>OL</sub> | Low-level output current             |     |        | 64  | mA   |  |

| TA              | Operating free-air temperature range | 0   |        | 70  | °C   |  |

### DC ELECTRICAL CHARACTERISTICS (Over recommended operating free-air temperature range unless otherwise noted.)

|                 | PARAMETER                |                       |                                                                                              | 1                           |                            | LIMITS           |      |      |    |

|-----------------|--------------------------|-----------------------|----------------------------------------------------------------------------------------------|-----------------------------|----------------------------|------------------|------|------|----|

| SYMBOL          |                          |                       | TEST CONDITIONS <sup>1</sup>                                                                 |                             | Min                        | Typ <sup>2</sup> | Max  | UNIT |    |

| I <sub>ОН</sub> | High-level output curre  | ent                   | V <sub>CC</sub> = MIN, V <sub>I</sub>                                                        | L = MAX, V <sub>OH</sub> =N | MAX, V <sub>IH</sub> = MIN |                  |      | 250  | μA |

| V               | Low-level output voltage | 20                    | $V_{CC} = MIN,$                                                                              | I <sub>OL</sub> =MAX        | ±10%V <sub>CC</sub>        |                  | 0.30 | 0.50 | V  |

| V <sub>OL</sub> | Low-level output voltage |                       | $ \begin{vmatrix} V_{CC} = MIN, \\ V_{IL} = MAX, \\ V_{IH} = MIN \end{vmatrix} I_{OL} = MAX$ | ±5%V <sub>CC</sub>          |                            | 0.30             | 0.50 | _ V  |    |

| V <sub>IK</sub> | Input clamp voltage      |                       | $V_{CC} = MIN, I_I = I_{IK}$                                                                 |                             |                            | -0.73            | -1.2 | v    |    |

| l <sub>i</sub>  | Input current at maxim   | um input voltage      | V <sub>CC</sub> =MAX, V <sub>1</sub> = 7.0V                                                  |                             |                            |                  | 100  | μA   |    |

| I <sub>IH</sub> | High-level input curren  | t                     | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.7V                                                 |                             |                            |                  |      | 20   | μA |

| ۱ <sub>۱۱</sub> | Low-level input current  | L                     | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.5V                                                 |                             |                            |                  | -0.6 | mA   |    |

|                 |                          | 74F06                 |                                                                                              |                             |                            |                  | 5.0  | 8,0  | mA |

|                 | Supply current [total]   | 1                     |                                                                                              |                             |                            |                  | 30   | 43   | mA |

| cc              |                          | V <sub>CC</sub> = MAX |                                                                                              |                             |                            | 10               | 14   | mA   |    |

|                 | 74F07                    |                       |                                                                                              |                             |                            |                  | 32   | 45   | mA |

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

2. All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

|                                      | PARAMETER                                   |       | TEST CONDITION | LIMITS                                                                  |            |            |                                                                                                                |            |      |

|--------------------------------------|---------------------------------------------|-------|----------------|-------------------------------------------------------------------------|------------|------------|----------------------------------------------------------------------------------------------------------------|------------|------|

| SYMBOL                               |                                             |       |                | $T_{A} = +25^{\circ}C$ $V_{CC} = 5V$ $C_{L} = 50pF$ $R_{L} = 100\Omega$ |            |            | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$ $V_{CC} = 5V \pm 10\%$ $C_{L} = 50\text{pF}$ $R_{L} = 100\Omega$ |            | UNIT |

|                                      |                                             |       |                | Min                                                                     | Тур        | Max        | Min                                                                                                            | Max        | 1    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay $D_n$ to $\overline{Q}_n$ | 74F06 | Waveform 1     | 2.0<br>1.5                                                              | 3.5<br>3.0 | 6.0<br>5.5 | 1.5<br>1.0                                                                                                     | 6.5<br>6.0 | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay $D_n$ to $Q_n$            | 74F07 | Waveform 2     | 2.0<br>3.0                                                              | 4.0<br>5.0 | 6.0<br>7.0 | 2.0<br>2.5                                                                                                     | 6.5<br>7.5 | ns   |

### AC ELECTRICAL CHARACTERISTICS

| Document No.  | 853-0335              |  |  |

|---------------|-----------------------|--|--|

| ECN No.       | 99598                 |  |  |

| Date of issue | May 15, 1990          |  |  |

| Status        | Product Specification |  |  |

| FAST Products |                       |  |  |

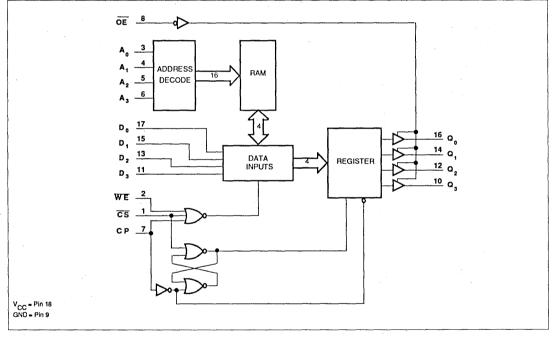

### DESCRIPTION

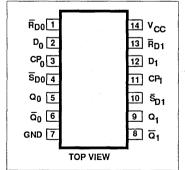

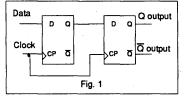

The 74F74 is a dual positive edge-triggered D-type flip-flop featuring individual Data, Clock, Set and Reset inputs; also true and complementary outputs.

Set  $(\overline{S}_D)$  and Reset  $(\overline{R}_D)$  are asynchronous active-Low inputs and operate independently of the Clock (CP) input.

Set  $(\overline{S}_D)$  and Reset  $(\overline{R}_D)$  are synchronously

active Low inputs and operate independently of the clock (CP). When Set and Reset are inactive (High), Data at the D input is transferred to the Q and  $\overline{Q}$  outputs on the Low-to-High transition of the Clock. Data must be stable just one setup time prior to the Low-to-High transition of the clock for predictable operation.

Clock triggering occurs at a voltage level and is not directly related to the transition time of the positive-going pulse. Following the hold time interval, data at the D input may be changed without affecting the levels of the output.

# FAST 74F74 FLIP-FLOP

### **Dual D-Type Flip-Flop**

| TYPE  | TYPICAL f <sub>MAX</sub> | TYPICAL SUPPLY CURRENT<br>(TOTAL) |  |  |

|-------|--------------------------|-----------------------------------|--|--|

| 74F74 | 125 MHz                  | 11.5mA                            |  |  |

### ORDERING INFORMATION

| PACKAGES           | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 10\%$ ; $T_A = 0^{\circ}C$ to $\pm 70^{\circ}C$ |

|--------------------|--------------------------------------------------------------------------------------|

| 14-Pin Plastic DIP | N74F74N                                                                              |

| 14-Pin Plastic SO  | N74F74D                                                                              |

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS                                                     | DESCRIPTION                       | 74F(U.L.)<br>HIGH/LOW | LOAD VALUE<br>HIGH/LOW |

|----------------------------------------------------------|-----------------------------------|-----------------------|------------------------|

| D <sub>0</sub> , D <sub>1</sub>                          | Data inputs                       | 1.0/1.0               | 20µA/0.6mA             |

| CP0, CP                                                  | Clock inputs (active rising edge) | 1.0/1.0               | 20µA/0.6mA             |

| S <sub>D0</sub> , S <sub>D1</sub>                        | Set inputs (active Low)           | 1.0/3.0               | 20µA/1.8mA             |

| $\overline{R}_{D0}, \overline{R}_{D1}$                   | Reset inputs (active Low)         | 1.0/3.0               | 20µA/1.8mA             |

| ଦ <sub>୦</sub> , ଦ <sub>ା</sub> ,  ପ୍ <sub>୦</sub> , ପ୍ୱ | Data outputs                      | 50/33                 | 1.0mA/20mA             |

NOTE:

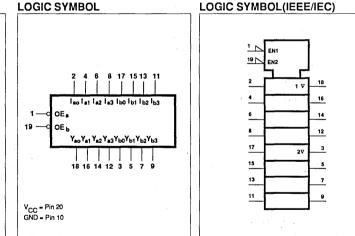

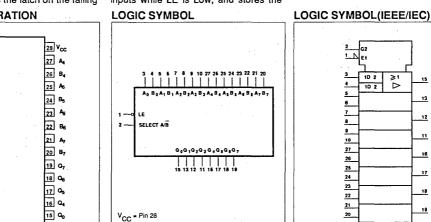

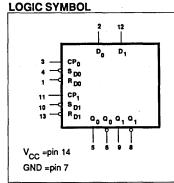

LOGIC SYMBOL

One (1.0) FAST Unit Load is defined as:  $20\mu A$  in the High state and 0.6mA in the Low state.

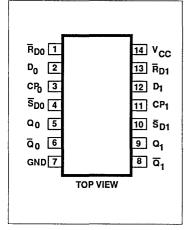

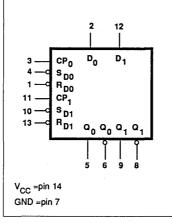

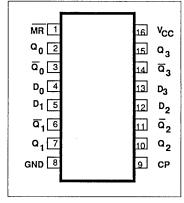

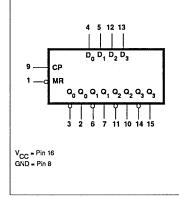

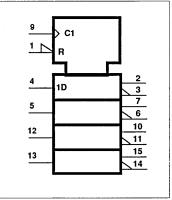

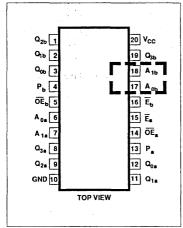

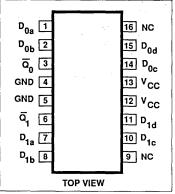

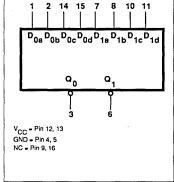

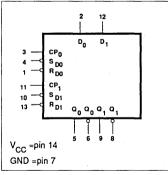

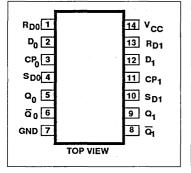

### **PIN CONFIGURATION**

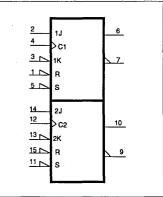

### LOGIC SYMBOL(IEEE/IEC)

### FLIP-FLOP

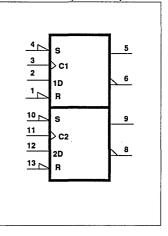

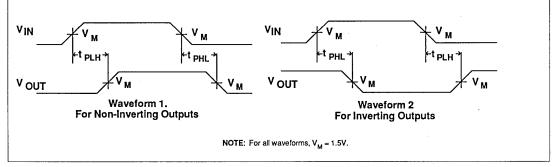

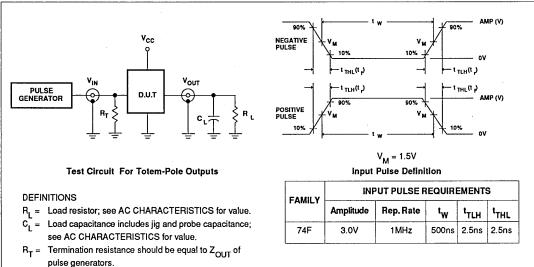

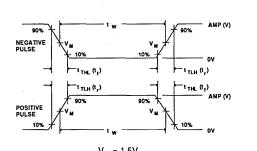

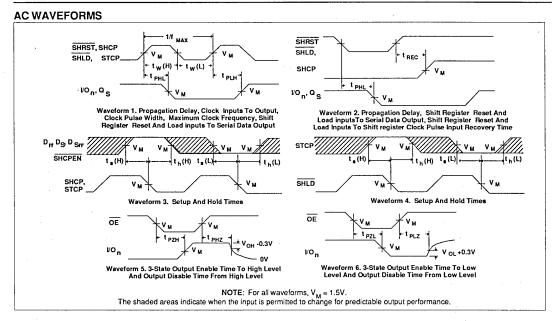

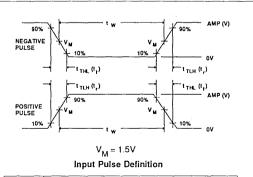

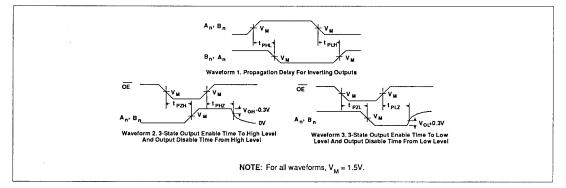

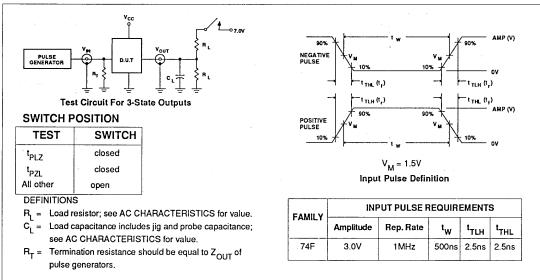

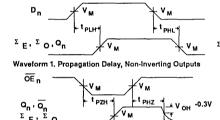

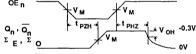

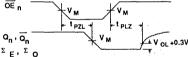

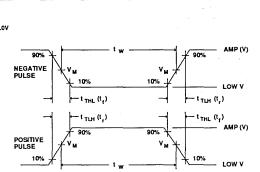

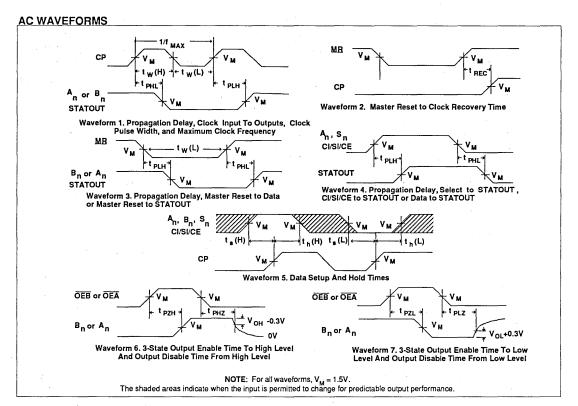

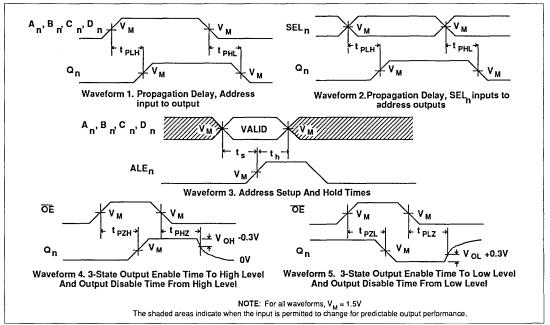

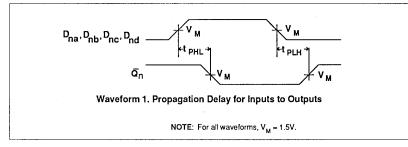

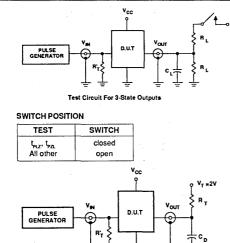

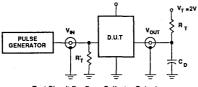

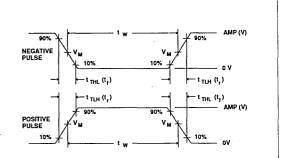

### AC WAVEFORMS

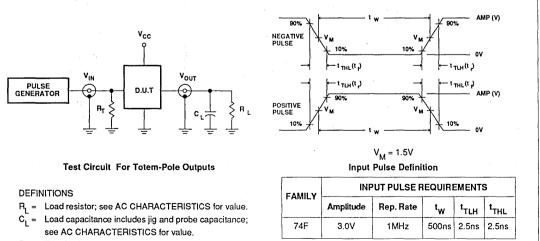

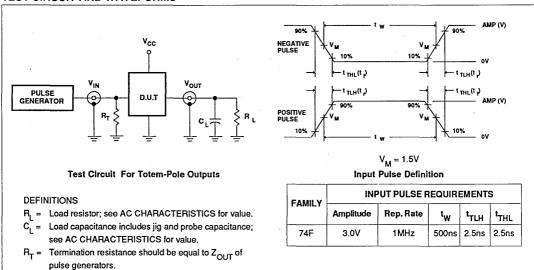

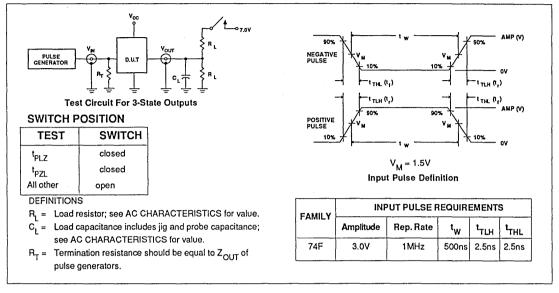

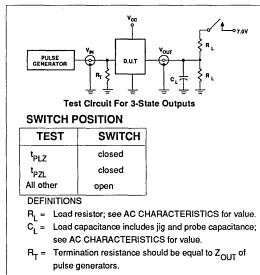

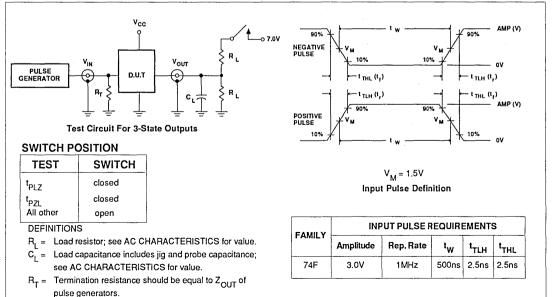

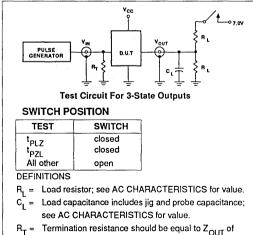

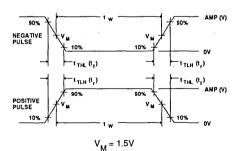

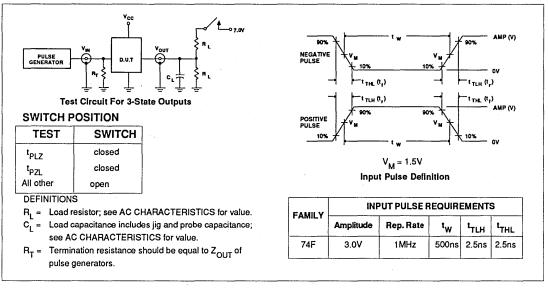

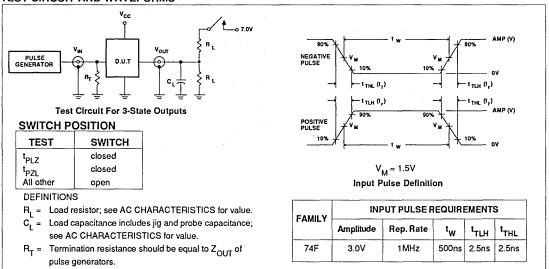

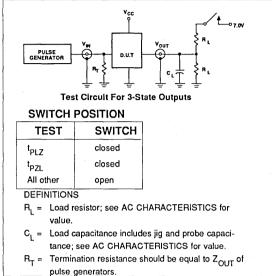

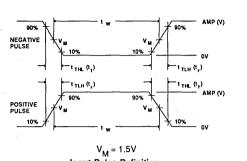

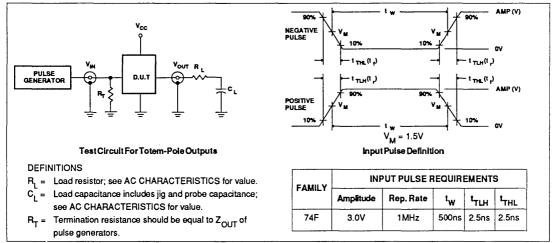

### TEST CIRCUIT AND WAVEFORMS

4

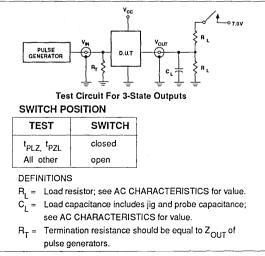

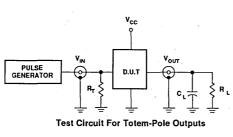

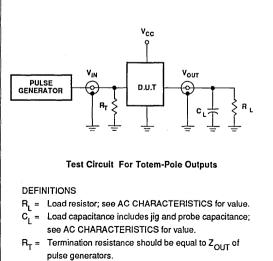

R<sub>T</sub> = Termination resistance should be equal to Z<sub>OUT</sub> of pulse generators.

October 5, 1989

| •             |                       |  |  |

|---------------|-----------------------|--|--|

| Document No.  | 853-0055              |  |  |

| ECN No.       | 99494                 |  |  |

| Date of issue | April 27, 1990        |  |  |

| Status        | Product Specification |  |  |

| FAST Products |                       |  |  |

### FEATURES

- High-impedance NPN base inputs for reduced loading (20µA in High and Low states)

- Magnitude comparison of any binary words

- Serial of parallel expansion without extra gating

### DESCRIPTION

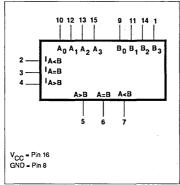

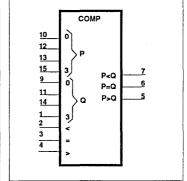

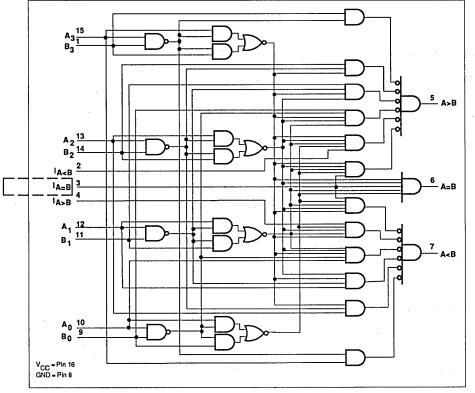

The 74F85 is a 4-bit magnitude comparator that can be expanded to almost any length. It compares two 4-bit binary, BCD, or other monotonic codes and presents the three possible magnitude results at the outputs. The 4-bit inputs are weighted  $(A_0 - A_3)$  and  $(B_0 - B_3)$  where  $A_3$  and  $B_3$  are the most significant bits. The operation of the 74F85 is described in the Function Table, showing all possible logic conditions. The upper part of the table describes the normal operation under all conditions that will occur in a single device or in a series expansion scheme. In the upper part of the table the three outputs are mutually exclusive. In the lower part of the table, the outputs reflect the feed-forward conditions that exists in the

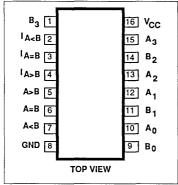

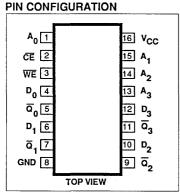

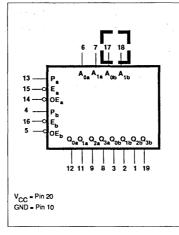

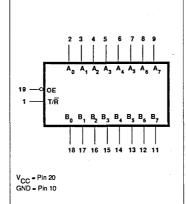

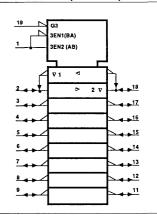

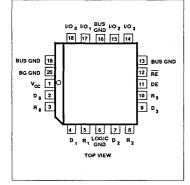

### **PIN CONFIGURATION**

# FAST 74F85 Comparator

### 4-Bit Magnitude Comparator

| TYPE  | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |  |  |

|-------|------------------------------|-----------------------------------|--|--|

| 74F85 | 7.0ns                        | 40mA                              |  |  |

### **ORDERING INFORMATION**

| PACKAGES           | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%; T <sub>A</sub> = 0°C to +70°C |

|--------------------|-----------------------------------------------------------------------------|

| 16-Pin Plastic DIP | N74F85N                                                                     |

| 16-Pin Plastic SOL | N74F85D                                                                     |

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE LOADVALUE 74F(U.L.) PINS DESCRIPTION HIGH/LOW HIGH/LOW 1.0/0.033 20µA/20µA A\_- A3 Comparing inputs Bo- Ba 1.0/0.033 20µA/20µA Comparing inputs Expansion inputs (active High) 1.0/0.033 20µA/20µA A<B, A=B, A>B A<B, A=B, A>B 1.0mA/20mA 50/33 Data outputs (active High)

NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

parallel expansion scheme. The expansion inputs I<sub>A>B</sub>, I<sub>A=B</sub> and I<sub>A<B</sub> are the least significant bit positions. When used for series expansion, the A>B, A=B and A<B outputs of the least significant word are connected to the corresponding I<sub>A>B</sub>, I<sub>A=B</sub> and I<sub>A<B</sub> inputs of the next higher

stage. Stages can be added in this manner to any length, but a propagation delay penalty of about 15ns is added with each additional stage. For proper operation the expansion inputs of the least significant word should be tied as follows:  $I_{A>B} = Low$ ,  $I_{A=B} = High and I_{A<B} = Low$ .

### LOGIC SYMBOL

### LOGIC SYMBOL(IEEE/IEC)

# Comparator

# FAST 74F85

Product Specification

### LOGIC DIAGRAM

### FUNCTION TABLE

| CO                              | MPARIN                                                                                                        | ig inpu                         | ITS                             | EXPA                | ISION II                       | VPUTS            |     | OUTPUT                                 | rs  |   |

|---------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------|--------------------------------|------------------|-----|----------------------------------------|-----|---|

| A <sub>3</sub> ,B <sub>3</sub>  | A2,B2                                                                                                         | A <sub>1</sub> ,B <sub>1</sub>  | A <sub>0</sub> ,B <sub>0</sub>  | I <sub>A&gt;B</sub> | I <sub>A<b< sub=""></b<></sub> | I <sub>A=B</sub> | A>B | A <b< th=""><th>A=B</th><th></th></b<> | A=B |   |

| A3>B3                           | X                                                                                                             | Х                               | X                               | X                   | х                              | X                | н   | L·                                     | L   | 1 |

| A <sub>3</sub> <b<sub>3</b<sub> | х                                                                                                             | Х                               | х                               | x                   | х                              | х                | L   | н                                      | L   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A2>B2                                                                                                         | х                               | Х                               | x                   | х                              | Х                | н   | L j                                    | L   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A2 <b2< td=""><td>X</td><td>Х</td><td>x</td><td>X</td><td>х</td><td>L</td><td>н</td><td>L</td><td></td></b2<> | X                               | Х                               | x                   | X                              | х                | L   | н                                      | L   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A <sub>2</sub> =B <sub>2</sub>                                                                                | A1>B1                           | X                               | X                   | x                              | Х                | н   | L                                      | L   | 1 |

| A <sub>3</sub> =B <sub>3</sub>  | A <sub>2</sub> =B <sub>2</sub>                                                                                | A <sub>1</sub> <b<sub>1</b<sub> | Х                               | X                   | х                              | х                | L   | н                                      | L   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A2=B2                                                                                                         | A <sub>1</sub> =B <sub>1</sub>  | A <sub>0</sub> >B <sub>0</sub>  | X                   | х                              | х                | н   | L                                      | L   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A <sub>2</sub> =B <sub>2</sub>                                                                                | A <sub>1</sub> =B <sub>1</sub>  | A <sub>0</sub> <b<sub>0</b<sub> | x                   | х                              | х                | L   | н                                      | L   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A <sub>2</sub> =B <sub>2</sub>                                                                                | A <sub>1</sub> =B <sub>1</sub>  | A <sub>0</sub> =B <sub>0</sub>  | н                   | L                              | L                | н   | L                                      | L   | 1 |

| A <sub>3</sub> =B <sub>3</sub>  | A <sub>2</sub> =B <sub>2</sub>                                                                                | A <sub>1</sub> =B <sub>1</sub>  | A <sub>0</sub> =B <sub>0</sub>  | L                   | н                              | L                | L   | н                                      | L   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A2=B2                                                                                                         | A <sub>1</sub> =B <sub>1</sub>  | A <sub>0</sub> =B <sub>0</sub>  | L                   | L                              | Н                | L   | L                                      | н   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A2=B2                                                                                                         | A <sub>1</sub> =B <sub>1</sub>  | A <sub>0</sub> =B <sub>0</sub>  | X                   | х                              | н                | L   | L                                      | Н   | ] |

| A3=B3                           | A2=B2                                                                                                         | A <sub>1</sub> =B <sub>1</sub>  | A <sub>0</sub> =B <sub>0</sub>  | н                   | н                              | L                | L   | L                                      | L   |   |

| A <sub>3</sub> =B <sub>3</sub>  | A <sub>2</sub> =B <sub>2</sub>                                                                                | A <sub>1</sub> =B <sub>1</sub>  | A <sub>0</sub> =B <sub>0</sub>  | L                   | L                              | L                | н   | н                                      | L   |   |

High voltage levelLow voltage level

April 27, 1990

<sup>=</sup> Don't care

| -             |                       |

|---------------|-----------------------|

| Document No.  | 853-0336              |

| ECN No.       | 98773                 |

| Date of issue | February 9, 1990      |

| Status        | Product Specification |

| FAST Products |                       |

### FEATURE

Industrial temperature range available (-40°C to +85°C)

FUNCTION TABLE

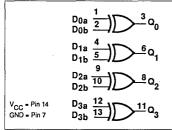

| IN              | PUTS            | OUTPUT         |

|-----------------|-----------------|----------------|

| D <sub>na</sub> | D <sub>nb</sub> | Q <sub>n</sub> |

| L               | L               | L              |

| L               | н               | н              |

| н               | L               | н              |

| н               | Н               | L              |

H = High voltage level L = Low voltage level

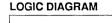

### LOGIC DIAGRAM

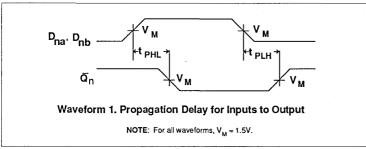

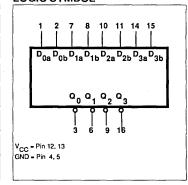

### **PIN CONFIGURATION**

# FAST 74F86 Gate

# Quad 2-Input Exclusive-OR Gate

| ТҮРЕ  | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|-------|------------------------------|-----------------------------------|

| 74F86 | 4.3 ns                       | 16.5 mA                           |

### **ORDERING INFORMATION**

| PACKAGES           | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%<br>T <sub>A</sub> = 0°C to +70°C | INDUSTRIAL RANGE<br>$V_{CC} = 5V \pm 10\%$<br>$T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |

|--------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 14-Pin Plastic DIP | N74F86N                                                                       | 174F86N                                                                                     |

| 14-Pin Plastic SO  | N74F86D                                                                       | 174F86D                                                                                     |

|                    |                                                                               |                                                                                             |

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS                              | DESCRIPTION | 74F(U.L.)<br>HIGH/LOW | LOAD VALUE<br>HIGH/LOW |

|-----------------------------------|-------------|-----------------------|------------------------|

| D <sub>na</sub> , D <sub>nb</sub> | Data inputs | 1.0/1.0               | 20µA/0.6mA             |

| Q <sub>n</sub>                    | Data output | 50/33                 | 1.0mA/20mA             |

#### NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

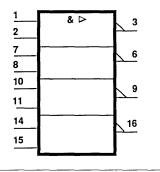

### LOGIC SYMBOL (IEEE/IEC)

Gate

# FAST 74F86

### **AC ELECTRICAL CHARACTERISTICS**

|                                      |                                                                                               |                |            |            |            | LIM                                                                                      | ITS                  |                                                 |             |      |

|--------------------------------------|-----------------------------------------------------------------------------------------------|----------------|------------|------------|------------|------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------|-------------|------|

| SYMBOL                               | PARAMETER                                                                                     | TEST CONDITION |            |            | 5V<br>IpF  | T <sub>A</sub> = 0<br>+70<br>V <sub>CC</sub> = 5<br>C <sub>L</sub> =<br>R <sub>L</sub> = | °C<br>V ±10%<br>50pF | ^ +85<br>V <sub>CC</sub> ≓5<br>C <sub>L</sub> = | -           | UNIT |

|                                      |                                                                                               |                | Min        | Тур        | Max        | Min                                                                                      | Max                  | Min                                             | Max         |      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay $D_{na}$ or $D_{nb}$ to $Q_n$ ( Other input Low)                            | Waveform 1     | 3.0<br>3.0 | 4.0<br>4.2 | 5.5<br>5.5 | 3.0<br>3.0                                                                               | 6.5<br>6.5           | 3.0<br>2.5                                      | 7.0<br>8.0  | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>D <sub>na</sub> or D <sub>nb</sub> to Q <sub>n</sub> ( Other input High) | Waveform 2     | 3.5<br>3.0 | 5.3<br>4.7 | 7.0<br>6.5 | 3.5<br>3.0                                                                               | 8.0<br>7.5           | 3.5<br>3.0                                      | 10.0<br>8.0 | ns   |

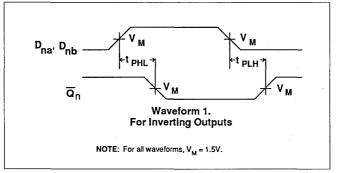

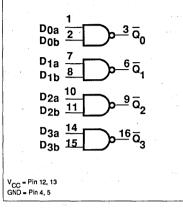

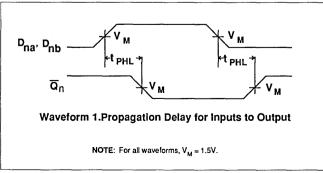

### AC WAVEFORMS

### TEST CIRCUIT AND WAVEFORMS

| Document No.  | 853-0338              |

|---------------|-----------------------|

| ECN No.       | 98775                 |

| Date of issue | February 9, 1990      |

| Status        | Product Specification |

| FAST Products |                       |

### FEATURE

Industrial temperature range available (-40°C to +85°C)

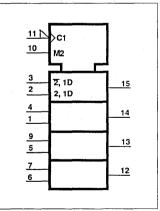

### DESCRIPTION

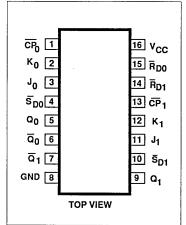

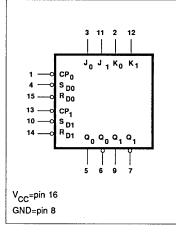

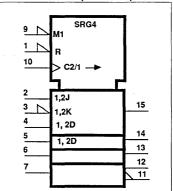

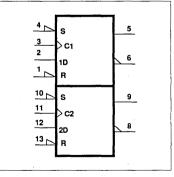

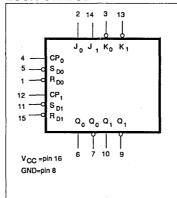

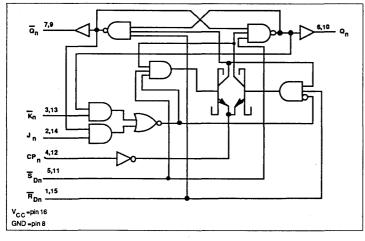

The 74F112, Dual Negative Edge-Triggered JK-Type Flip-Flop, features individual J, K, Clock ( $\overline{CP}_n$ ), Set ( $\overline{S}_D$ ) and Reset ( $\overline{R}_D$ ) inputs, true ( $Q_n$ ) and complementary ( $\overline{Q}_n$ ) outputs.

The  $\overline{S}_D$  and  $\overline{R}_D$  inputs, when Low, set or reset the outputs as shown in the Function Table regardless of the level at the other inputs.

A High level on the clock  $(\overline{CP}_n)$  input enables the J and K inputs and data will be accepted. The logic levels at the J and K inputs may be allowed to change while the  $\overline{CP}_n$  is High and flip-flop will perform according to the Function Table as long as minimum setup and hold times are observed. Output changes are initiated by the High-to-Low transition of the  $\overline{CP}_n$ .

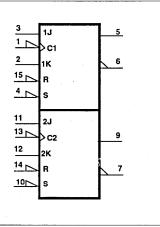

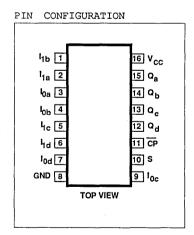

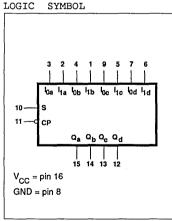

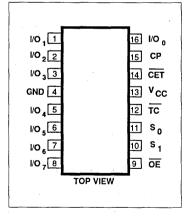

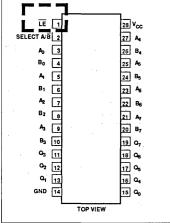

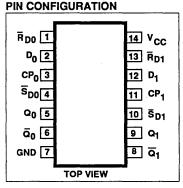

### **PIN CONFIGURATION**

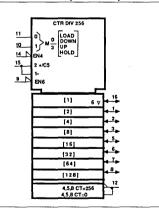

# FAST 74F112 Flip-Flop

### Dual J-K Negative Edge-triggered Flip-Flop

| TYPE    | TYPICAL f <sub>MAX</sub> | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|---------|--------------------------|-----------------------------------|

| N74F112 | 100MHz                   | 15mA                              |

### **ORDERING INFORMATION**

| PACKAGES           | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%<br>T <sub>A</sub> = 0°C to +70°C | INDUSTRIAL RANGE<br>$V_{CC} = 5V \pm 10\%$<br>$T_A = -40^{\circ}C$ to +85°C |

|--------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 16-Pin Plastic DIP | N74F112N                                                                      | I74F112N                                                                    |

| 16-Pin Plastic SO  | N74F112D                                                                      | I74F112D                                                                    |

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS                                            | DESCRIPTION                             | 74F(U.L.)<br>HIGH/LOW | LOAD VALUE<br>HIGH/LOW |

|-------------------------------------------------|-----------------------------------------|-----------------------|------------------------|

| J <sub>0</sub> , J <sub>1</sub>                 | J inputs                                | 1.0/1.0               | 20µA/0.6mA             |

| К <sub>0</sub> , К <sub>1</sub>                 | K inputs                                | 1.0/1.0               | 20µA/0.6mA             |

| ទី <sub>D0</sub> , ទី <sub>D1</sub>             | Set inputs (active Low)                 | 1.0/5.0               | 20µA/3.0mA             |

| $\overline{R}_{D0}$ , $\overline{R}_{D1}$       | Reset inputs (active Low)               | 1.0/5.0               | 20µA/3.0mA             |

|                                                 | Clock Pulse input (active falling edge) | 1.0/4.0               | 20µA/2.4mA             |

| $Q_{0},\overline{Q}_{0};Q_{1},\overline{Q}_{1}$ | Data outputs                            | 50/33                 | 1.0mA/20mA             |

| NOTE:                                           |                                         |                       | •••••••••              |

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

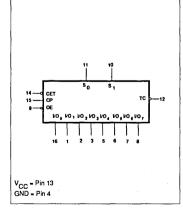

### LOGIC SYMBOL

### LOGIC SYMBOL(IEEE/IEC)

### Flip-Flop

### Product Specification

### FAST 74F112

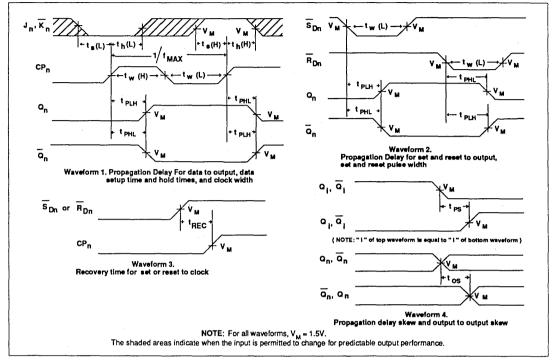

### **AC ELECTRICAL CHARACTERISTICS**

|                                      |                                                                                                    |                |            |                              |            | LIM                                                         | ITS        |                                                             |                        |      |

|--------------------------------------|----------------------------------------------------------------------------------------------------|----------------|------------|------------------------------|------------|-------------------------------------------------------------|------------|-------------------------------------------------------------|------------------------|------|

|                                      |                                                                                                    |                | т,         | A = +2                       | 5°C        | T <sub>A</sub> = 0<br>+70                                   | °C         | +85                                                         |                        |      |

| SYMBOL                               | PARAMETER                                                                                          | TEST CONDITION | C          | /cc = 50<br>L = 50<br>L = 50 | рF         | V <sub>CC</sub> = 5<br>C <sub>L</sub> =<br>R <sub>L</sub> = |            | V <sub>CC</sub> = 5<br>C <sub>L</sub> =<br>R <sub>L</sub> = | V ±10%<br>50pF<br>500Ω | UNIT |

|                                      |                                                                                                    |                | Min        | Тур                          | Max        | Min                                                         | Max        | Min                                                         | Max                    |      |

| f <sub>max</sub>                     | Maximum clock frequency                                                                            | Waveform 1     | 85         | 100                          |            | 80                                                          |            | 80                                                          |                        | MHz  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay $\overline{CP}$ to $Q_n$ or $\overline{Q}_n$                                     | Waveform 1     | 2.0<br>2.0 | 5.0<br>5.0                   | 6.5<br>6.5 | 2.0<br>2.0                                                  | 7.5<br>7.5 | 2.0<br>2.0                                                  | 7.5<br>7.5             | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay $\overline{S}_{Dn}, \overline{R}_{D}$ to $\Omega_{n}$ or $\overline{\Omega}_{n}$ | Waveform 2,3   | 2.0        | 4.5<br>4.5                   | 6.5<br>6.5 | 2.0<br>2.0                                                  | 7.5<br>7.5 | 1.5<br>1.5                                                  | 7.5<br>7.5             | ns   |

|                                      |                                                                                                    | · · ·          |            | J                            |            |                                                             |            | Ī                                                           |                        |      |

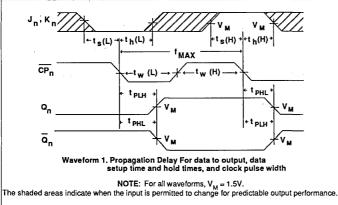

### AC SETUP REQUIREMENTS

|                                          |                                                                  | 1 A            |                                                                         |     |                                                            | LIM                  | ITS                                                                                       |                       |      |    |

|------------------------------------------|------------------------------------------------------------------|----------------|-------------------------------------------------------------------------|-----|------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------|-----------------------|------|----|

| SYMBOL                                   | PARAMETER                                                        | TEST CONDITION | $T_{A} = +25^{\circ}C$ $V_{CC} = 5V$ $C_{L} = 50pF$ $R_{L} = 500\Omega$ |     | $T_A = 0$<br>+70<br>$V_{CC} = 5$<br>$C_L = 0$<br>$R_L = 0$ | №C<br>V ±10%<br>50pF | T <sub>A</sub> = -4<br>+85<br>V <sub>CC</sub> = 5<br>C <sub>L</sub> =<br>R <sub>L</sub> = | 5°C<br>V ±10%<br>50pF | UNIT |    |

|                                          |                                                                  |                | Min                                                                     | Тур | Max                                                        | Min                  | Max                                                                                       | Min                   | Max  |    |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup time, High or Low<br>J <sub>n</sub> , K <sub>n</sub> to CP | Waveform 1     | 4.0<br>3.5                                                              |     |                                                            | 5.0<br>4.0           |                                                                                           | 5.0<br>4.0            |      | ns |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, High or Low $J_n$ , $K_n$ to $\overline{CP}$          | Waveform 1     | 0.0<br>0.0                                                              |     |                                                            | 0.0<br>0.0           |                                                                                           | 0.0<br>0.0            | -    | ns |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CP Pulse width<br>High or Low                                    | Waveform 1     | 4.5<br>4.5                                                              |     |                                                            | 5.0<br>5.0           |                                                                                           | 5.0<br>5.0            |      | ns |

| t <sub>w</sub> (L)                       | ਤੋ <sub>Dn</sub> , R <sub>D</sub> Pulse width<br>Low             | Waveform 2,3   | 4.5                                                                     |     |                                                            | 5.0                  |                                                                                           | 5.0                   |      | ns |

| t <sub>REC</sub>                         | Re∞very time<br>S <sub>Dn</sub> , R <sub>D</sub> to CP           | Waveform 2,3   | 4.5                                                                     |     |                                                            | 5.0                  |                                                                                           | 5.0                   |      | ns |

### AC WAVEFORMS

| Document No.  | 853-0342              |

|---------------|-----------------------|

| ECN No.       | 98710                 |

| Date of issue | November 27, 1990     |

| Status        | Product Specification |

| FAST Products |                       |

### DESCRIPTION

The 74F132 contains four 2-input NAND gates which accept standard TTL input signals and provide standard TTL output levels. They are capable of transforming slowly changing input signals into sharply defined, jitter-free output signals. In addition, they have greater noise margin than conventional NAND gates. Each circuit contains a 2-input Schmitt trigger followed by a Darlington level shifter and a phase splitter driving a TTL totem-pole output. The Schmitt trigger uses positive feedback to effectively speed-up slow input transitions, and provide different input threshold voltages for positive and negative-going transitions. This hysteresis between the positive-going and negative-going input threshold (typically 800mv) is determined by reisistor ratios and is essentially insensitive to temperature and supply voltage variations. As long as three inputs remain at a more positive voltage than  $V_{T+MAX}$ , the gate will respond in the transition of the other input as shown in Waveform 1.

# FAST 74F132 Schmitt Trigger Quad 2-Input NAND Schmitt Trigger

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 74F132 | 6.3 ns                       | 13 mA                             |

### **ORDERING INFORMATION**

| PACKAGES           | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%; T <sub>A</sub> = 0°C to +70°C |

|--------------------|-----------------------------------------------------------------------------|

| 14-Pin Plastic DIP | N74F132N                                                                    |

| 14-Pin Plastic SO  | N74F132D                                                                    |

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS                              | DESCRIPTION | 74F(U.L.)<br>HIGH/LOW                 | LOAD VALUE<br>HIGH/LOW |

|-----------------------------------|-------------|---------------------------------------|------------------------|

| D <sub>na</sub> , D <sub>nb</sub> | Data inputs | 1.0/1.0                               | 20µA/0.6mA             |

| ā,                                | Data output | 50/33                                 | 1.0mA/20mA             |

| NOTE                              | · · · ·     | · · · · · · · · · · · · · · · · · · · |                        |

NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

### LOGIC SYMBOL

### LOGIC SYMBOL (IEEE/IEC)

### Schmitt Trigger

FAST 74F132

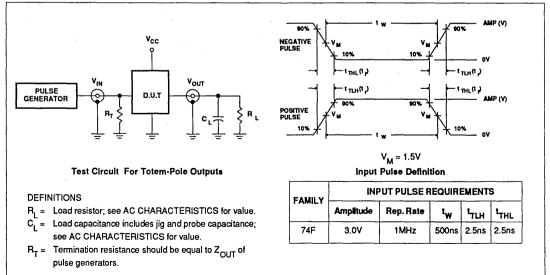

### AC ELECTRICAL CHARACTERISTICS

|                                      |                                                             |                |            |                                                                         | LIMITS     |                                       |                                       |      |  |

|--------------------------------------|-------------------------------------------------------------|----------------|------------|-------------------------------------------------------------------------|------------|---------------------------------------|---------------------------------------|------|--|

| SYMBOL                               | PARAMETER                                                   | TEST CONDITION |            | $T_{A} = +25^{\circ}C$ $V_{CC} = 5V$ $C_{L} = 50pF$ $R_{L} = 500\Omega$ |            | Ŷ <sub>cc</sub> =<br>C <sub>L</sub> = | C to +70°C<br>5V ±10%<br>50pF<br>500Ω | UNIT |  |

|                                      |                                                             |                | Min        | Тур                                                                     | Max        | Min                                   | Max                                   |      |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay $D_{na}$ , $D_{nb}$ to $\overline{Q}_{n}$ | Waveform 1     | 3.5<br>4.5 | 5.5<br>6.0                                                              | 7.0<br>8.0 | 3.0<br>4.5                            | 8.5<br>8.5                            | ns   |  |

### AC WAVEFORMS

### TEST CIRCUIT AND WAVEFORMS

| Document No.  | 853-1154              |  |

|---------------|-----------------------|--|

| ECN No.       | 97893                 |  |

| Date of issue | October 16, 1989      |  |

| Status        | Product Specification |  |

| FAST Products |                       |  |

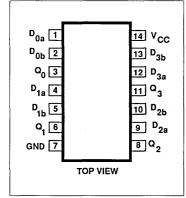

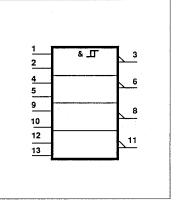

FAST 74F133 Gate 13-Input NAND Gate

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 74F133 | 4.0 ns                       | 2.0 mA                            |

### **ORDERING INFORMATION**

| PACKAGES           | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%; T <sub>A</sub> = 0°C to +70°C |

|--------------------|-----------------------------------------------------------------------------|

| 14-Pin Plastic DIP | N74F133N                                                                    |

| 14-Pin Plastic SO  | N74F133D                                                                    |

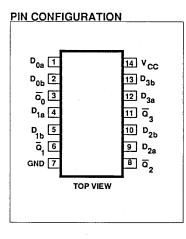

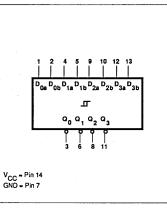

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS                            | DESCRIPTION | 74F(U.L.)<br>HIGH/LOW | LOAD VALUE<br>HIGH/LOW |

|---------------------------------|-------------|-----------------------|------------------------|

| D <sub>0</sub> -D <sub>12</sub> | Data inputs | 1.0/1.0               | 20µA/0.6mA             |

| <br>ā                           | Data Output | 50/33                 | 1.0mA/20mA             |

NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

### 13

| Document No.  | 853-0344              |

|---------------|-----------------------|

| ECN No.       | 98903                 |

| Date of issue | February 23, 1990     |

| Status        | Product Specification |

| FAST Products |                       |

### FEATURES

- Demultiplexing capability

- Two independent 1-of-4 decoders

- · Multifunction capability

### DESCRIPTION

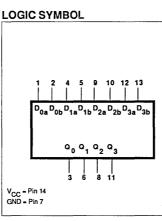

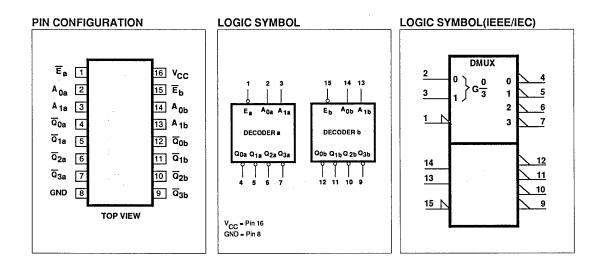

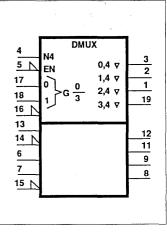

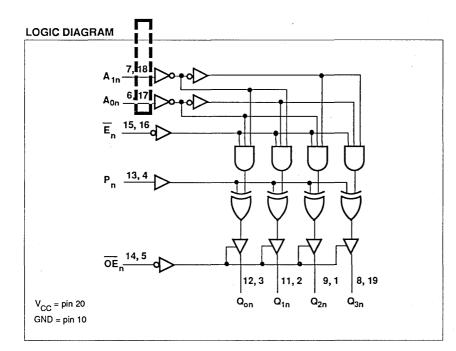

The 74F139 is a high speed, dual 1-of-4 decoder/demultiplexer. This device has two independent decoders, each accepting two binary weighted inputs  $(A_{0n}, A_{1n})$  and providing four mutually exclusive active-Low outputs  $(\overline{Q}_{0n} - \overline{Q}_{3n})$ . Each decoder has an active-Low Enable  $(\overline{E})$ . When  $\overline{E}$  is High, every output is forced High. The Enable can be used as the Data input for a 1-of-4 demultiplexer application.

# FAST 74F139 Decoder/Demultiplexer

### Dual 1-of-4 Decoder//Demultiplexer

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 74F139 | 5.3ns                        | 13mA                              |

### **ORDERING INFORMATION**

|   | PACKAGES           | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%; T <sub>A</sub> = 0°C to +70°C |

|---|--------------------|-----------------------------------------------------------------------------|

| · | 16-Pin Plastic DIP | N74F139N                                                                    |

|   | 16-Pin Plastic SO  | N74F139D                                                                    |

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| DESCRIPTION                | 74F(U.L.)<br>HIGH/LOW                        | LOAD VALUE<br>HIGH/LOW                                                                                                     |

|----------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Address inputs             | 1.0/1.0                                      | 20µA/0.6mA                                                                                                                 |

| Enable inputs (active Low) | 1.0/1.0                                      | 20µA/0.6mA                                                                                                                 |

| Data outputs (active Low)  | 50/33                                        | 1.0mA/20mA                                                                                                                 |

|                            | Address inputs<br>Enable inputs (active Low) | DESCRIPTION         HIGH/LOW           Address inputs         1.0/1.0           Enable inputs (active Low)         1.0/1.0 |

NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

| -             |                       |

|---------------|-----------------------|

| Document No.  | 853-1155              |

| ECN No.       | 98493                 |

| Date of issue | January 8, 1990       |

| Status        | Product Specification |

| FAST Products | -L                    |

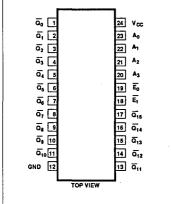

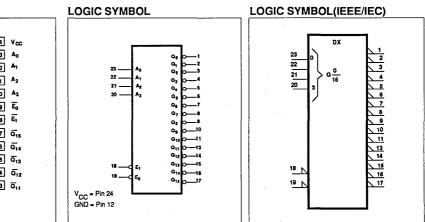

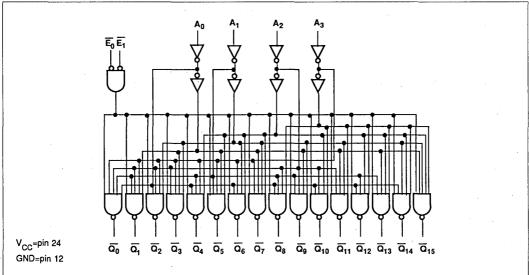

# FAST 74F154 Decoder/Demultiplexer

### 1-of-16 Decoder/Demultiplexer

### FEATURES

- 16-line demultiplexing capability

- Mutually exclusive outputs

- 2-input enable gate for strobing or expansion

### DESCRIPTION

The 74F154 decoder accepts four active High binary address inputs and provides 16 mutually exclusive active Low outputs. The 2-input Enable ( $\overline{E}_0$ ,  $\overline{E}_1$ ) gate can be used to strobe the decoder to eliminate the normal decoding "glitches" on the outputs, or it can be used for expansion of the decoder. The Enable gate has two AND'ed inputs which must be Low to enable the outputs.

The 74F154 can be used as a 1-of-16 demultiplexer by using one of the Enable inputs as the multiplexed data input. When the other Enable is Low, the addressed output will follow the state of the applied data.

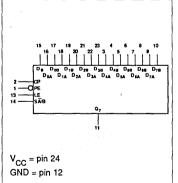

### PIN CONFIGURATION

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 74F154 | 5.5 ns                       | 26mA                              |

### **ORDERING INFORMATION**

| PACKAGES                         | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%; T <sub>A</sub> = 0°C to +70°C |

|----------------------------------|-----------------------------------------------------------------------------|

| 24-Pin Plastic Slim DIP (300mil) | N74F154N                                                                    |

| 24-Pin Plastic SOL               | N74F154D                                                                    |

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS                            | DESCRIPTION   | 74F(U.L.)<br>HIGH/LOW | LOAD VALUE<br>HIGH/LOW |

|---------------------------------|---------------|-----------------------|------------------------|

| A <sub>0</sub> - A <sub>3</sub> | Data inputs   | 1.0/1.0               | 20µA/0.6mA             |

| Ē <sub>0</sub> , Ē              | Enable inputs | 1.0/1.0               | 20µA/0.6mA             |

| <u>_</u>                        | Data outputs  | 50/33                 | 1.0mA/20mA             |

NOTE:

One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

## Decoder/Demultiplexer

# FAST 74F154

### **FUNCTION TABLE**

|   |   | IN             | PUTS     | 5              |      |             |    |                  |                  |    |                |                  |    | JTPU               |            |                        |                 |                 |                 |                 |                 |

|---|---|----------------|----------|----------------|------|-------------|----|------------------|------------------|----|----------------|------------------|----|--------------------|------------|------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Ē | Ē | A <sub>0</sub> | A,       | A <sub>2</sub> | Α3   | ā,          | ā, | $\overline{Q}_2$ | $\overline{Q}_3$ | ā₄ | ۵ <sub>۶</sub> | $\overline{Q}_6$ | α, | $\overline{Q}_{g}$ | <u>ō</u> , | <b>Q</b> <sub>10</sub> | Q <sub>11</sub> | Q <sub>12</sub> | Q <sub>13</sub> | Q <sub>14</sub> | Q <sub>15</sub> |

| L | н | X              | X        | X              | X    | н           | н  | н                | н                | н  | н              | н                | н  | н                  | н          | н                      | н               | Н               | Н               | н               | н               |

| н | L | X              | Х        | Х              | X    | H I         | н  | н                | н                | н  | н              | н                | н  | н                  | н          | н                      | н               | н               | н               | н               | Н               |

| н | н | X              | х        | х              | Х    | н           | н  | н                | Н                | н  | н              | Н                | н  | н                  | Н          | н                      | н               | Н               | Н               | Н               | Н               |

| L | L | L              | L        | Ľ              | L    | L           | н  | н                | н                | н  | н              | Н                | н  | н                  | . H        | H                      | н               | н               | Н               | Н               | н               |

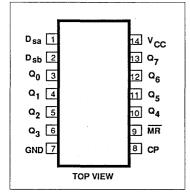

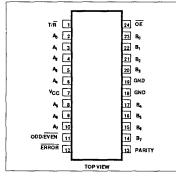

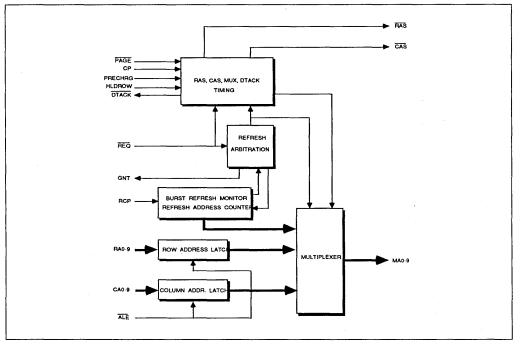

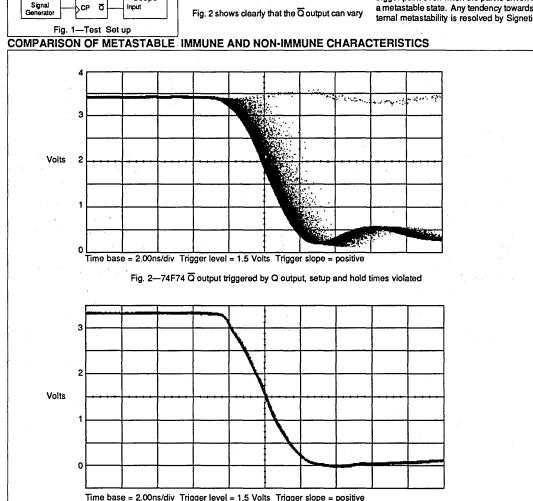

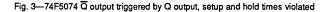

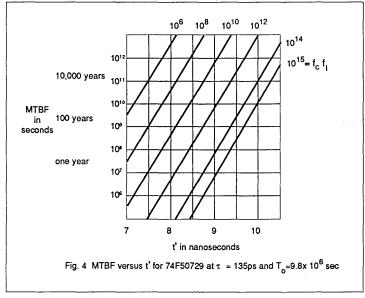

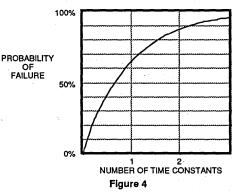

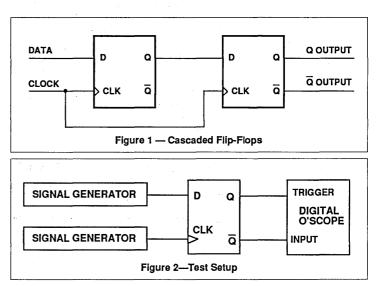

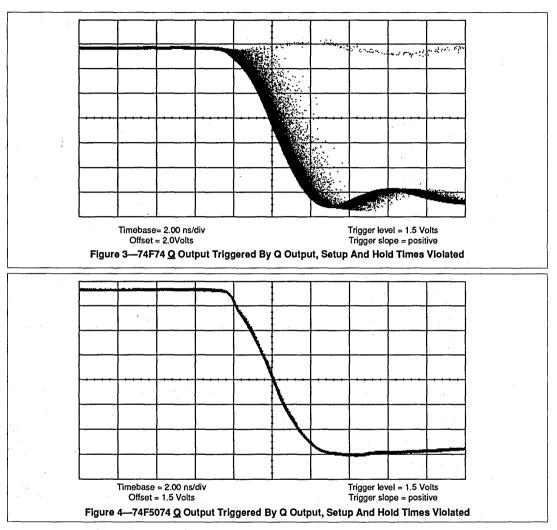

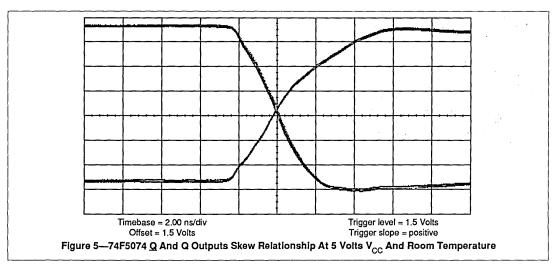

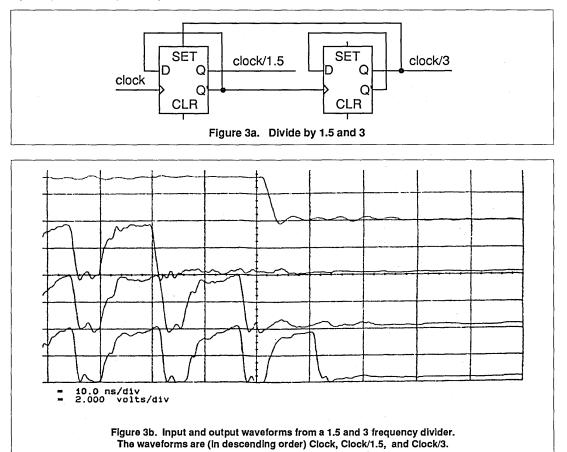

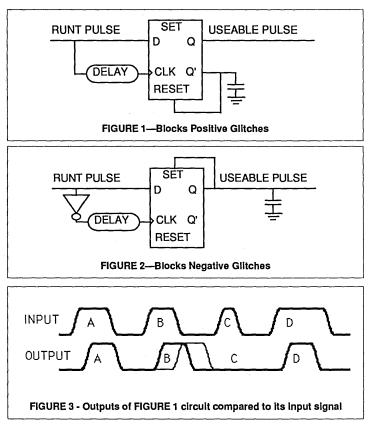

| L | L | н              | L        | L              | L    | н           | L  | н                | н                | Н  | н              | н                | н  | н                  | н          | н                      | н               | н               | Н               | Н               | н               |