### **Programmable Logic**

Data Book

# **Programmable Logic**

1989

Data Book

1989

**General Information**

**Data Sheets**

2

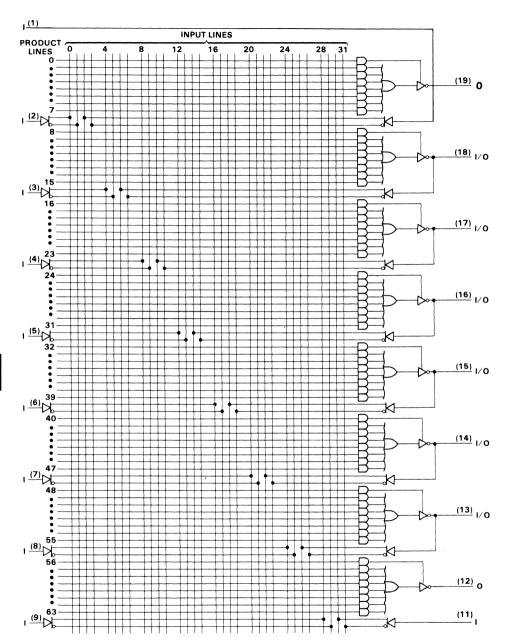

**Application Reports**

3

**Mechanical Data**

4

## The Programmable Logic Data Book

### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1988, Texas Instruments Incorporated

### INTRODUCTION

In this volume, Texas Instruments presents technical information on TI's broad line of programmable logic devices (PLDs), including 10-ns, 20-pin PAL® circuits.

Tl's programmable logic products include high-speed leadership circuits, as well as standard 20- and 24-pin PAL devices in a variety of speed/power versions. This data book includes specifications on existing and future products, including:

- High-performance, low-power IMPACT™ and IMPACT-X™ 20- and 24-pin standard PAL circuits

- High-complexity Latched- and Registered-input PAL ICs and Exclusive-OR arrays

- Flexible, '22V10-architecture macrocell PAL ICs, including TI's enhanced, 20-ns version, the TIBPAL22VP10-20

- High-speed 6- and 3-ns, 10KH and 100K ECL IMPACT™ and ExCL™ PAL circuits

- Ultra-low-power UV-erasable and one-time programmable CMOS PAL ICs, including 20-pin, '22V10, and generic architectures

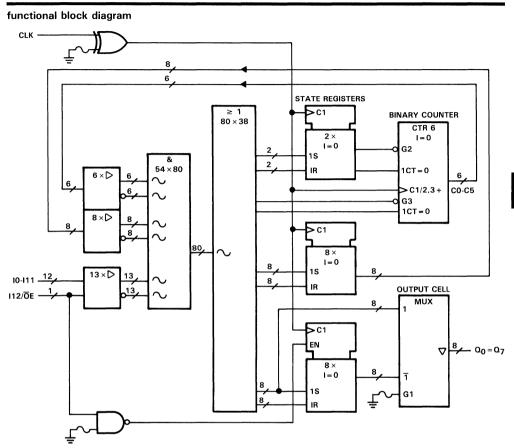

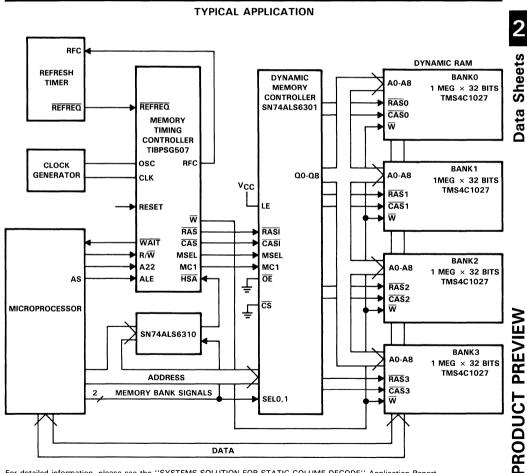

- Fast, 50-MHz programmable state machines, including enhanced versions of '82S105B/167B sequencers and the TIBPSG507 Programmable Sequence Generator

Texas Instruments high-speed programmable bipolar devices utilize TI's advanced IMPACT™ and new IMPACT-X™ technologies. IMPACT-X™ uses trench isolation and polysilicon emitters to increase performance and reduce power dissipation compared to traditional processes. IMPACT-X™ provides 1.5-µm feature sizes and 7-µm pitch.

Based on IMPACT-X™, TI's new ECL process, ExCL™, offers even greater speed and density for high-performance ECL circuits.

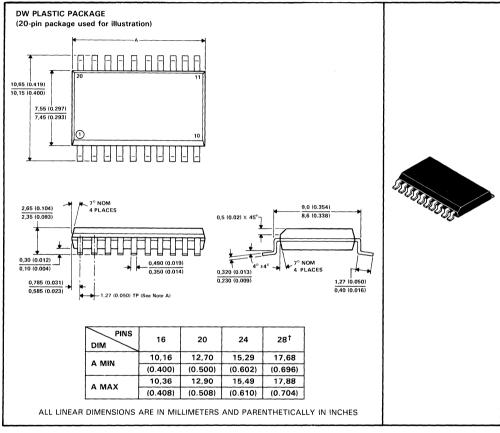

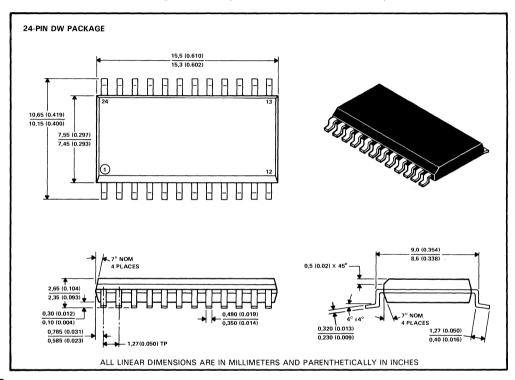

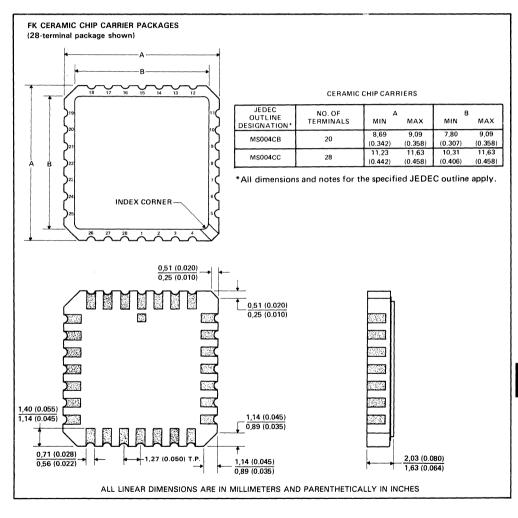

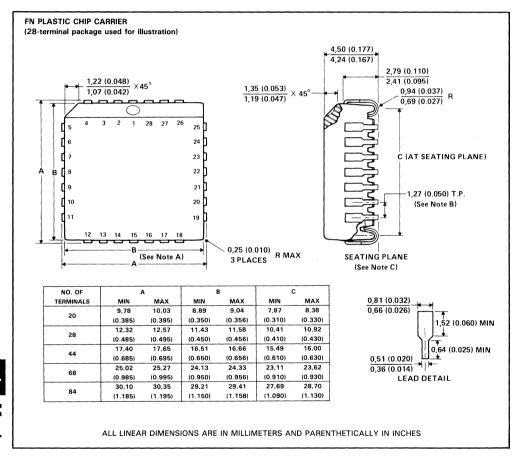

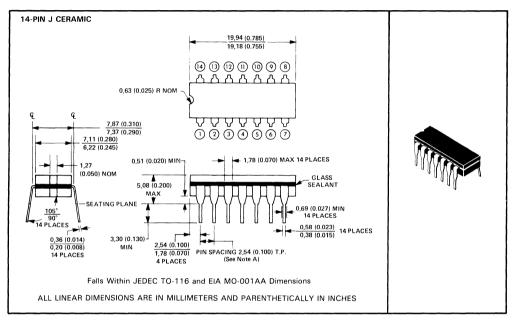

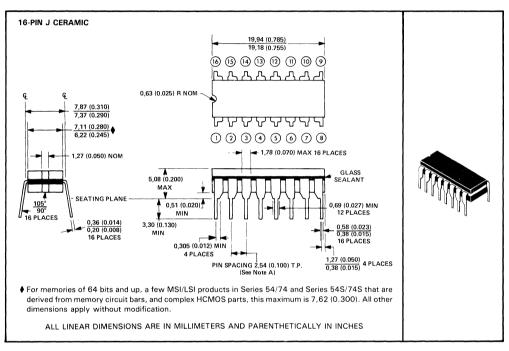

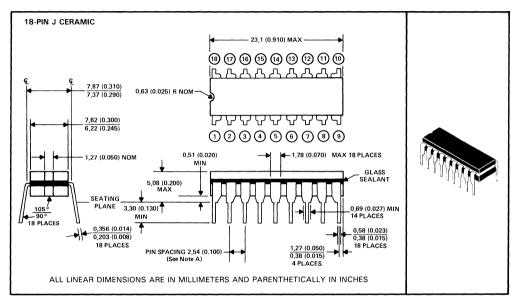

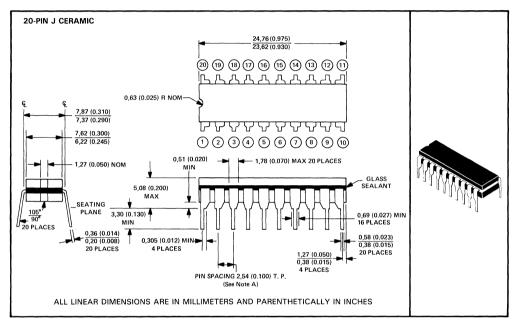

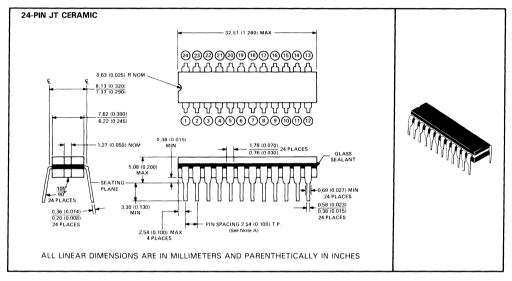

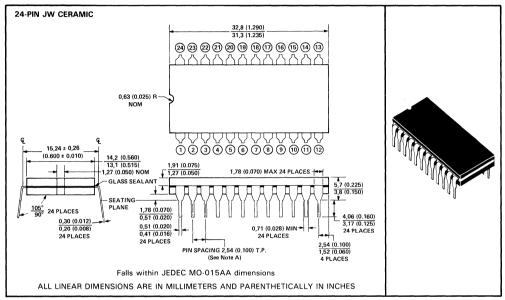

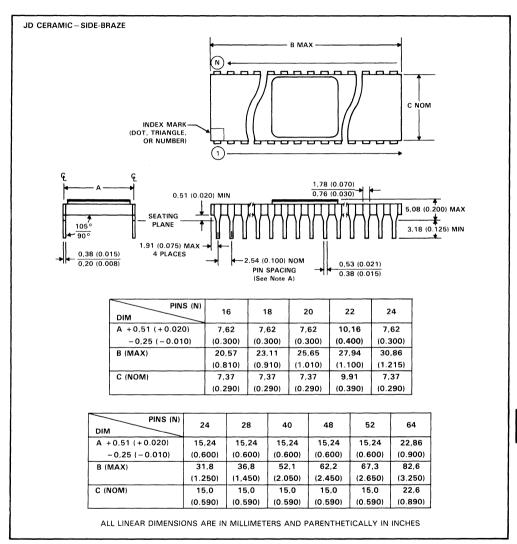

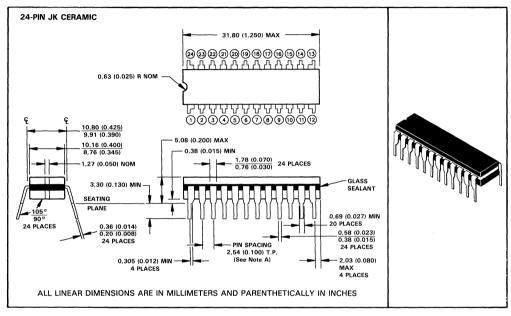

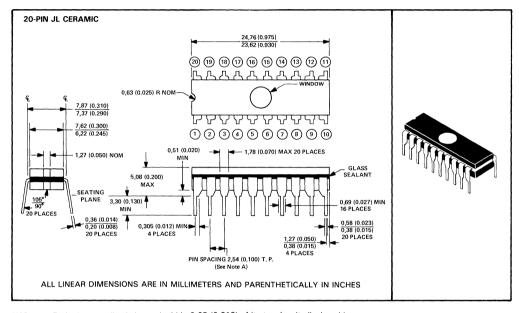

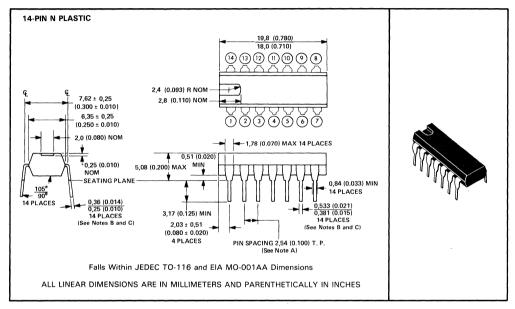

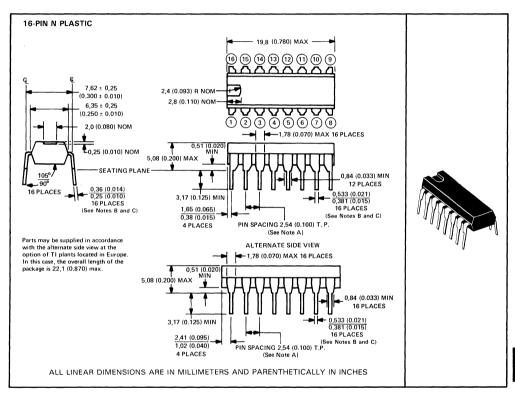

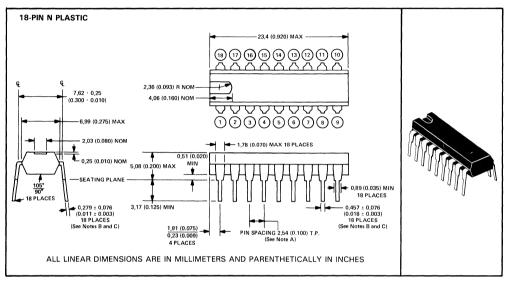

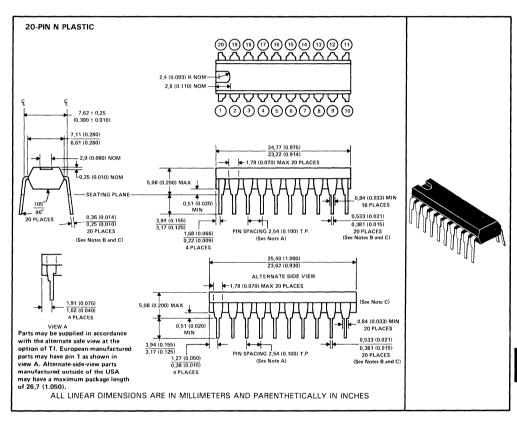

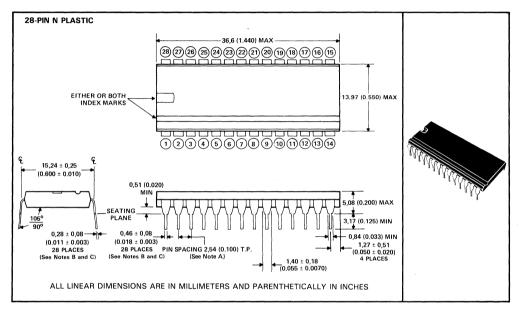

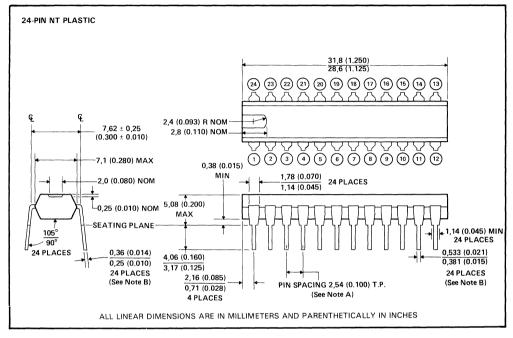

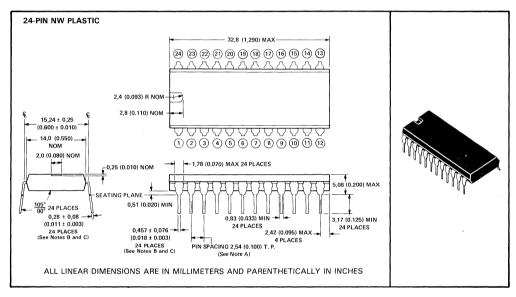

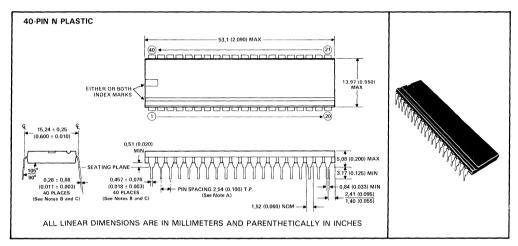

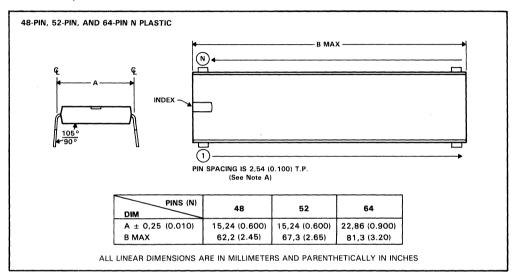

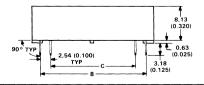

This volume contains design and specification data for 78 device types. Package dimensions are given in the Mechanical Data section in metric measurement (and parenthetically in inches).

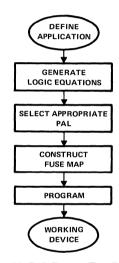

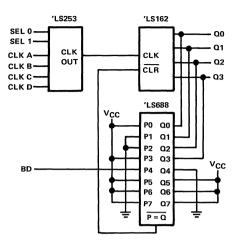

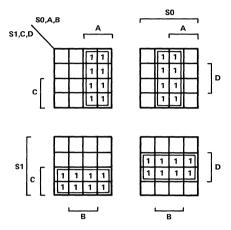

Four programmable logic application reports have been incorporated into this data book as a reference tool. They are: Designing with Texas Instruments Field Programmable Logic; Hard Array Logic; A Designer's Guide to the PSG507; and Systems Solutions for Static Column Decode.

Complete technical data for any Texas Instruments semiconductor product is available from your nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at 1-800-232-3200.

PAL is a registered trademark of Monolithic Memories Inc. IMPACT and IMPACT-X are trademarks of Texas Instruments Incorporated. EXCL is a trademark of Texas Instruments Incorporated.

**General Information**

1

Data Sheets

2

**Application Reports**

3

Mechanical Data

4

### Contents

|                                       | Page |

|---------------------------------------|------|

| Alphanumeric Index                    | 1-3  |

| Glossary                              | 1-5  |

| Explanation of Function Tables        | 1-9  |

| Parameter Measurement Information     | 1-11 |

| Ordering Information                  | 1-12 |

| Hardware/Software Manufacturers       | 1-13 |

| TI IMPACT™ Design and Service Centers | 1-14 |

|                 |                 | Page  |                  |                  | Page  |

|-----------------|-----------------|-------|------------------|------------------|-------|

| PAL16L8AC       | PAL16L8AM       | 2-3   | TIBPAL20L10-30C  |                  | 2-127 |

| PAL16L8A-2C     | PAL16L8A-2M     | 2-3   | TIBPAL20SP8-20C  | TIBPAL20SP8-30M  | 2-139 |

| PAL16R4AC       | PAL16R4AM       | 2-3   | TIBPAL20X4-20C   | TIBPAL20X4-25M   | 2-115 |

| PAL16R4A-2C     | PAL16R4A-2M     | 2-3   | TIBPAL20X4-30C   |                  | 2-127 |

| PAL16R6AC       | PAL16R6AM       | 2-3   | TIBPAL20X8-20C   | TIBPAL20X8-25M   | 2-115 |

| PAL16R6A-2C     | PAL16R6A-2M     | 2-3   | TIBPAL20X8-30C   |                  | 2-127 |

| PAL16R8AC       | PAL16R8AM       | 2-3   | TIBPAL20X10-20C  | TIBPAL20X10-25M  | 2-115 |

| PAL16R8A-2C     | PAL16R8A-2M     | 2-3   | TIBPAL20X10-30C  |                  | 2-127 |

| PAL20L8AC       | PAL20L8AM       | 2-15  | TIBPAL22V10C     | TIBPAL22V10M     | 2-145 |

| PAL20R4AC       | PAL20R4AM       | 2-15  | TIBPAL22V10AC    | TIBPAL22V10AM    | 2-145 |

| PAL20R6AC       | PAL20R6AM       | 2-15  | TIBPAL22VP10-20C | TIBPAL22VP10-25M | 2-157 |

| PAL20R8AC       | PAL20R8AM       | 2-15  | TIBPALR19L8C     | TIBPALR19L8M     | 2-169 |

| TIBPAD16N8-7C   |                 | 2-27  | TIBPALR19R4C     | TIBPALR19R4M     | 2-169 |

| TIBPAD18N8-6C   |                 | 2-35  | TIBPALR19R6C     | TIBPALR19R6M     | 2-169 |

| TIBPAL16L8-10C  | TIBPAL16L8-12M  | 2-41  | TJBPALR19R8C     | TIBPALR19R8M     | 2-169 |

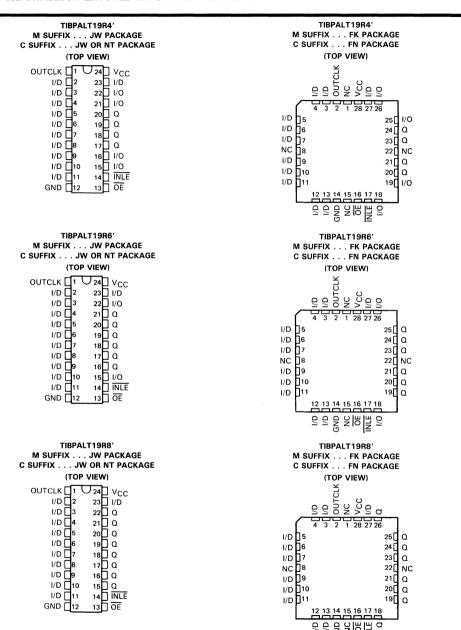

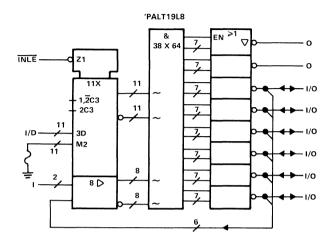

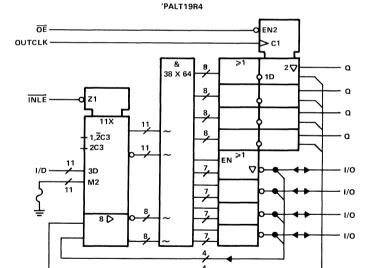

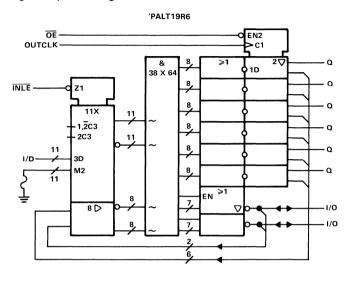

| TIBPAL16L8-12C  | TIBPAL16L8-15M  | 2-57  | TIBPALT19L8C     | TIBPALT19L8M     | 2-181 |

| TIBPAL16L8-15C  | TIBPAL16L8-20M  | 2-67  | TIBPALT19R4C     | TIBPALT19R4M     | 2-181 |

| TIBPAL16L8-25C  | TIBPAL16L8-30M  | 2-77  | TIBPALT19R6C     | TIBPALT19R6M     | 2-181 |

| TIBPAL16R4-10C  | TIBPAL16R4-12M  | 2-41  | TIBPALT19R8C     | TIBPALT19R8M     | 2-181 |

| TIBPAL16R4-12C  | TIBPAL16R4-15M  | 2-57  | TIBPLS506C       | TIBPLS506M       | 2-193 |

| TIBPAL16R4-15C  | TIBPAL16R4-20M  | 2-67  | TIBPSG507C       | TIBPSG507M       | 2-201 |

| TIBPAL16R4-25C  | TIBPAL16R4-30M  | 2-77  | TIB82S105BC      | TIB82S105BM      | 2-209 |

| TIBPAL16R6-10C  | TIBPAL16R6-12M  | 2-41  | TIB82S167BC      | TIB82S167BM      | 2-219 |

| TIBPAL16R6-12C  | TIBPAL16R6-15M  | 2-57  | TICHAL16L8-35C   |                  | 2-229 |

| TIBPAL16R6-15C  | TIBPAL16R6-20M  | 2-67  | TICHAL16R4-35C   |                  | 2-229 |

| TIBPAL16R6-25C  | TIBPAL16R6-30M  | 2-77  | TICHAL16R6-35C   |                  | 2-229 |

| TIBPAL16R8-10C  | TIBPAL16R8-12M  | 2-41  | TICHAL16R8-35C   |                  | 2-229 |

| TIBPAL16R8-12C  | TIBPAL16R8-15M  | 2-57  | TICPAL16L8-55C   |                  | 2-243 |

| TIBPAL16R8-15C  | TIBPAL16R8-20M  | 2-67  | TICPAL16R4-55C   |                  | 2-243 |

| TIBPAL16R8-25C  | TIBPAL16R8-30M  | 2-77  | TICPAL16R6-55C   |                  | 2-243 |

| TIBPAL20L8-15C  | TIBPAL20L8-20M  | 2-87  | TICPAL16R8-55C   |                  | 2-243 |

| TIBPAL20L8-25C  | TIBPAL20L8-30M  | 2-101 | TICPAL18V8-25C   | TICPAL18V8-30M   | 2-257 |

| TIBPAL20R4-15C  | TIBPAL20R4-20M  | 2-87  | TICPAL22V10C     | TICPAL22V10M     | 2-271 |

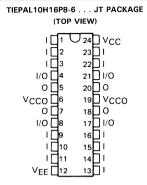

| TIBPAL20R4-25C  | TIBPAL20R4-30M  | 2-101 | TIEPAL10H16P8-3C |                  | 2-285 |

| TIBPAL20R6-15C  | TIBPAL20R6-20M  | 2-87  | TIEPAL10H16P8-6C |                  | 2-291 |

| TIBPAL20R6-25C  | TIBPAL20R6-30M  | 2-101 | TIEPAL10016P8-3C |                  | 2-297 |

| TIBPAL20R8-15C  | TIBPAL20R8-20M  | 2-87  | TIEPAL10016P8-6C |                  | 2-303 |

| TIBPAL20R8-25C  | TIBPAL20R8-30M  | 2-101 | TIFPLA839C       | TIFPLA839M       | 2-309 |

| TIBPAL20L10-20C | TIBPAL20L10-25M | 2-115 | TIFPLA840C       | TIFPLA840M       | 2-309 |

|                 |                 |       |                  |                  |       |

### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

### PART 1 — GENERAL CONCEPTS AND CLASSIFICATIONS OF CIRCUIT COMPLEXITY

### Chip-Enable Input

A control input that when active permits operation of the integrated circuit for input, internal transfer, manipulation, refreshing, and/or output of data and when inactive causes the integrated circuit to be in reduced-power standby mode.

NOTE: See "chip-select input."

### Chip-Select Input

A gating input that when inactive prevents input or output of data to or from an integrated circuit. NOTE: See "chip-enable input."

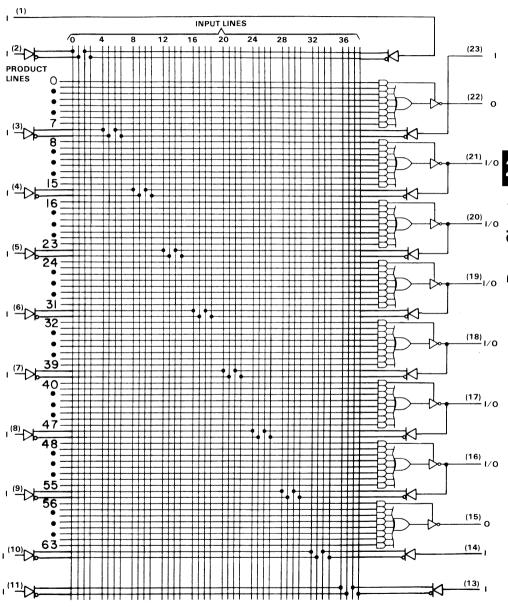

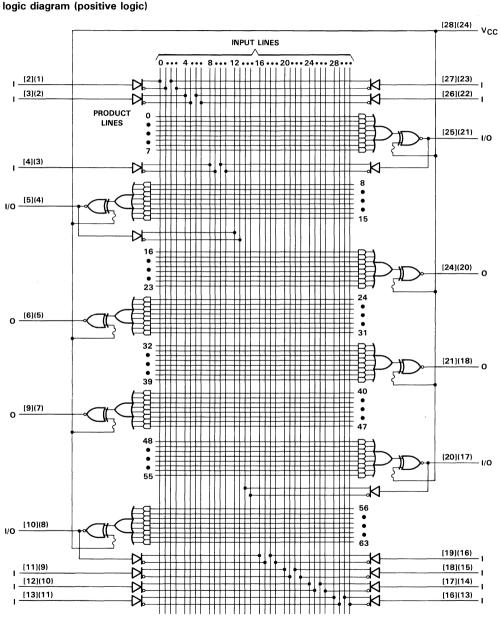

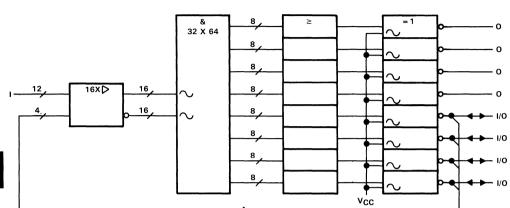

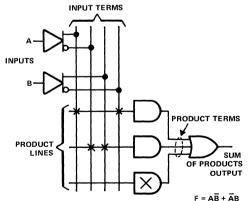

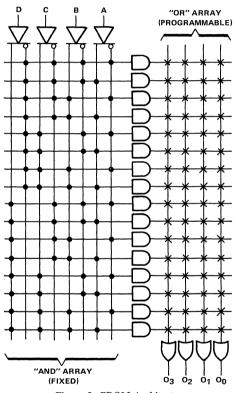

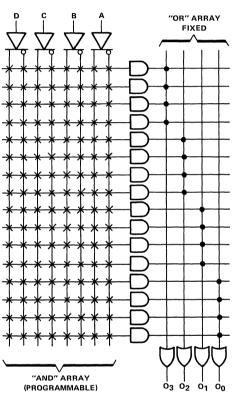

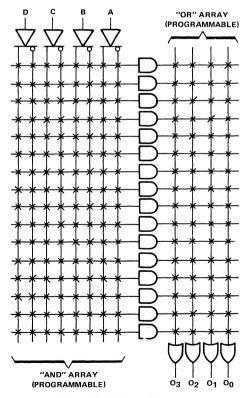

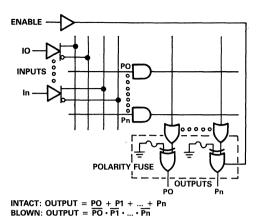

### Field-Programmable Logic Array (FPLA)

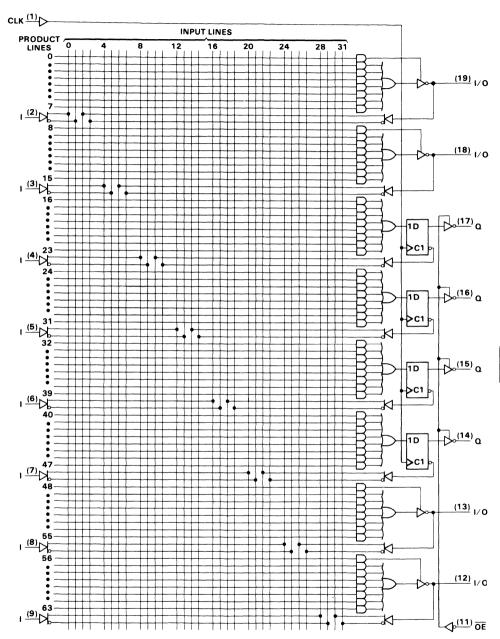

A user-programmable integrated circuit whose basic logic structure consists of a programmable AND array and whose outputs feed a programmable OR array.

### **Gate Equivalent Circuit**

A basic unit-of-measure of relative digital-circuit complexity. The number of gate equivalent circuits is that number of individual logic gates that would have to be interconnected to perform the same function.

### Large-Scale Integration (LSI)

A concept whereby a complete major subsystem or system function is fabricated as a single microcircuit. In this context a major subsystem or system, whether digital or linear, is considered to be one that contains 100 or more equivalent gates or circuitry of similar complexity.

### Mask-Programmed Read-Only Memory

A read-only memory in which the data content of each cell is determined during manufacture by the use of a mask, the data content thereafter being unalterable.

### Medium-Scale Integration (MSI)

A concept whereby a complete subsystem or system function is fabricated as a single microcircuit. The subsystem or system is smaller than for LSI, but whether digital or linear, is considered to be one that contains 12 or more equivalent gates or circuitry of similar complexity.

### Memory Cell

The smallest subdivision of a memory into which a unit of data has been or can be entered, in which it is or can be stored, and from which it can be retrieved.

### **Memory Integrated Circuit**

An integrated circuit consisting of memory cells and usually including associated circuits such as those for address selection, amplifiers, etc.

### Output-Enable Input

A gating input that when active permits the integrated circuit to output data and when inactive causes the integrated circuit output(s) to be at a high impedance (off).

### Programmable Array Logic (PAL®)

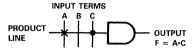

A user-programmable integrated circuit which utilizes proven fuse link technology to implement logic functions. Implements sum of products logic by using a programmble AND array whose outputs feed a fixed OR array.

### Programmable Read-Only Memory (PROM)

A read-only memory that after being manufactured can have the data content of each memory cell altered once only.

### Random-Access Memory (RAM)

A memory that permits access to any of its address locations in any desired sequence with similar access time for each location.

NOTE: The term RAM, as commonly used, denotes a read/write memory.

### Read/Write Memory

A memory in which each cell may be selected by applying appropriate electronic input signals and the stored data may be either (a) sensed at appropriate output terminals, or (b) changed in response to other similar electronic input signals.

### Small-Scale Integration (SSI)

Integrated circuits of less complexity than medium-scale integration (MSI).

### Typical (TYP)

A calculated value representative of the specified parameter at nominal operating conditions ( $V_{CC}=5~V$ ,  $T_A=25~{}^{\circ}C$ ), based on the measured value of devices processed, to emulate the process distribution.

### Very-Large-Scale Integration (VLSI)

A concept whereby a complete system function is fabricated as a single microcircuit. In this context, a system, whether digital or linear, is considered to be one that contains 3000 or more gates or circuitry of similar complexity.

### Volatile Memory

A memory the data content of which is lost when power is removed.

PAL is a registered trademark of Monolithic Memories Inc.

### PART 2 — OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)

### f<sub>max</sub> Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

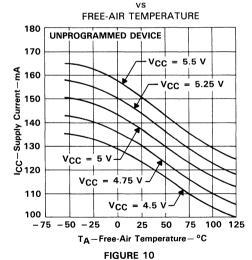

### ICC Supply current

The current into\* the VCC supply terminal of an integrated circuit.

### ICCH Supply current, outputs high

The current into \* the VCC supply terminal of an integrated circuit when all (or a specified number) of the outputs are at the high level.

### ICCL Supply current, outputs low

The current into\* the VCC supply terminal of an integrated circuit when all (or a specified number) of the outputs are at the low level.

### IIH High-level input current

The current into\* an input when a high-level voltage is applied to that input.

### IIL Low-level input current

The current into\* an input when a low-level voltage is applied to that input.

### IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

### IOL Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

### IOS (IO) Short-circuit output current

The current into \* an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

### IOZH Off-state (high-impedance-state) output current (of a three-state output) with high-level voltage applied

The current flowing into\* an output having three-state capability with input conditions established that, according to the production specification, will establish the high-impedance state at the output and with a high-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a low level if it were enabled.

### IOZL Off-state (high-impedance-state) output current (of a three-state output) with low-level voltage applied

The current flowing into \* an output having three-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output and with a low-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a high level if it were enabled.

<sup>\*</sup>Current out of a terminal is given as a negative value.

### VIH High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

### VIK Input clamp voltage

An input voltage in a region of relatively low differential resistance that serves to limit the input voltage swing.

### VIL Low-level input voltage

An input voltage level within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

### VOH High-level output voltage

The voltage at an output terminal with input conditions applied that, according to the product specification, will establish a high level at the output.

### VOL Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to the product specification, will establish a low level at the output.

### ta Access time

The time interval between the application of a specific input pulse and the availability of valid signals at an output.

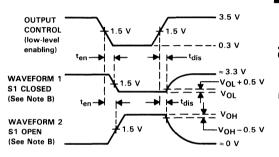

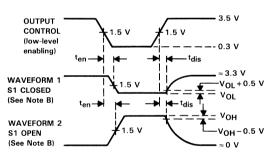

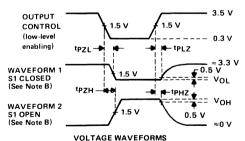

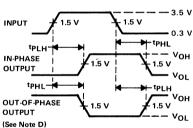

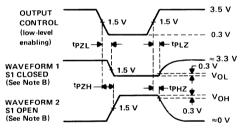

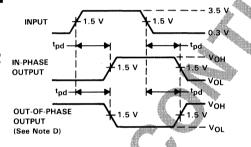

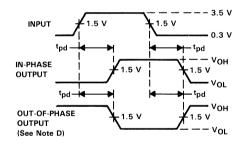

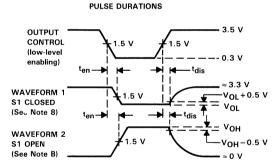

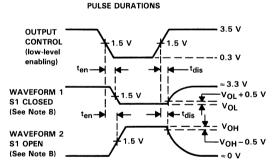

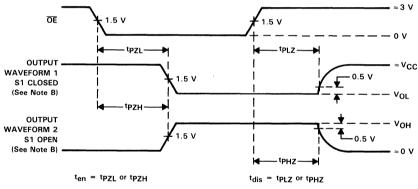

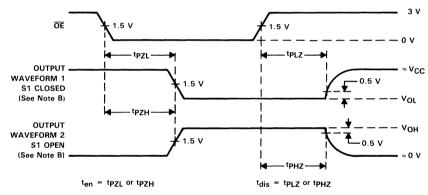

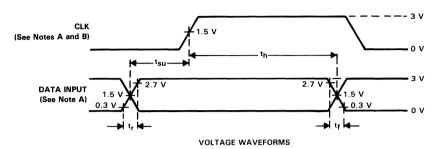

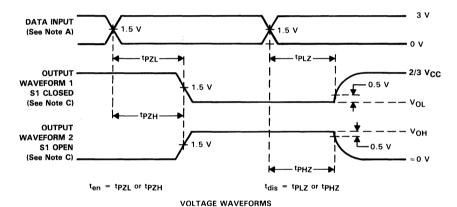

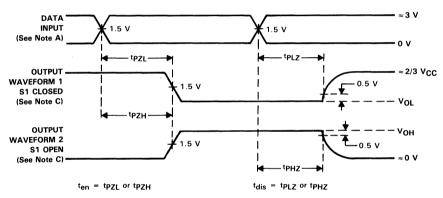

### t<sub>dis</sub> Disable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state. ( $t_{dis} = t_{PHZ}$  or  $t_{PLZ}$ ).

### ten Enable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low). ( $t_{en} = t_{PZH}$  or  $t_{PZL}$ ).

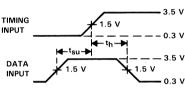

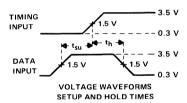

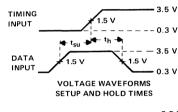

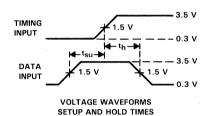

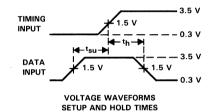

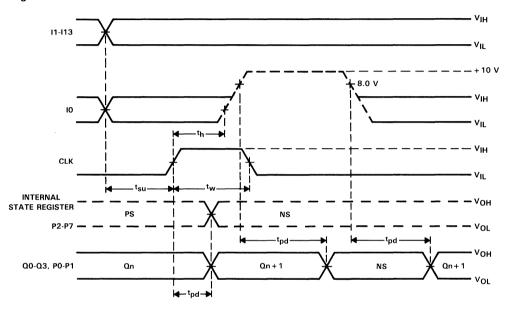

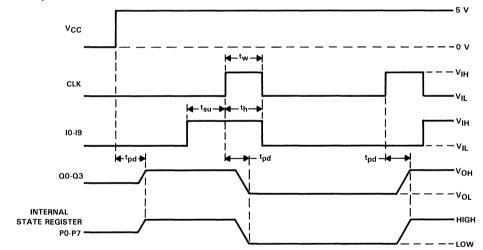

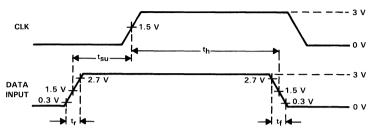

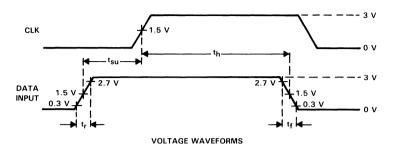

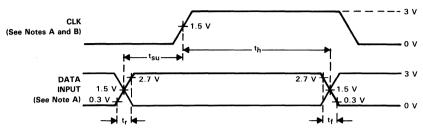

### th Hold time

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

2. The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

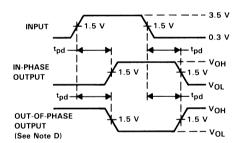

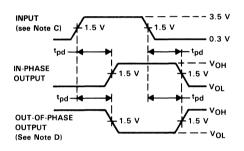

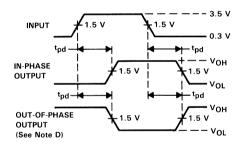

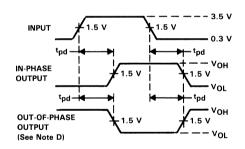

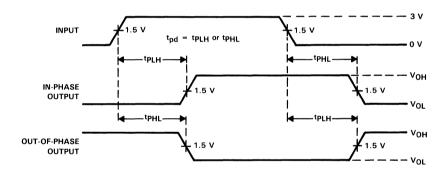

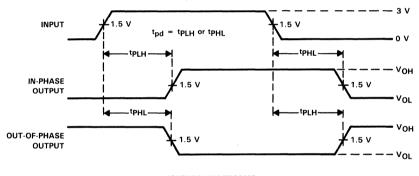

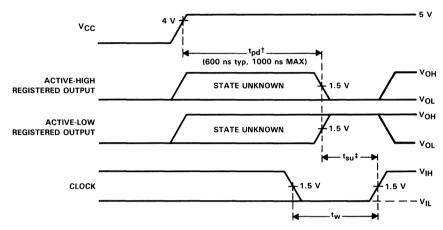

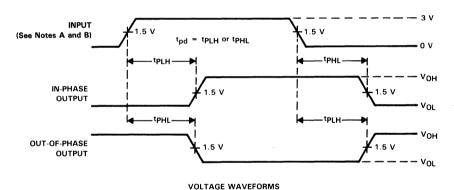

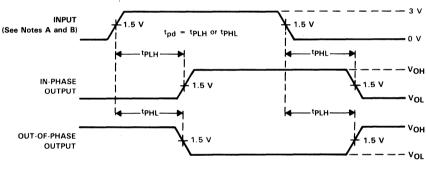

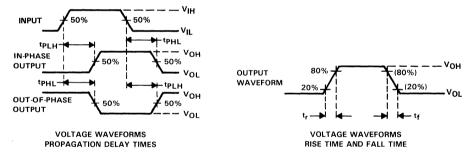

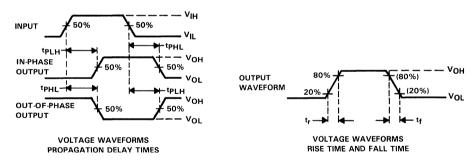

### tpd Propagation delay time

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. ( $t_{pd} = t_{PHL}$  or  $t_{PLH}$ ).

### Propagation delay time, high-to-low level output **tPHL**

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

### Disable time (of a three-state output) from high level **tPHZ**

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined high level to a high-impedance (off) state.

### Propagation delay time, low-to-high-level output **tPLH**

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

### tPLZ Disable time (of a three-state output) from low level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from the defined low level to a high-impedance (off) state.

### **tPZH** Enable time (of a three-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high level.

### Enable time (of a three-state output) to low level **tPZL**

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined low level.

### Sense recovery time tsr

The time interval needed to switch a memory from a write mode to a read mode and to obtain valid data signals at the output.

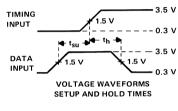

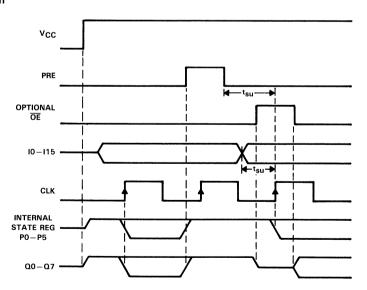

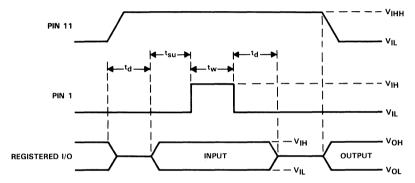

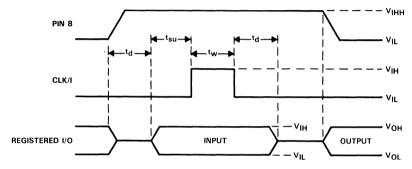

### Setup time tsu

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

- NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- 2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

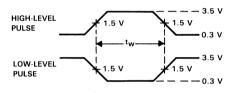

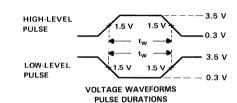

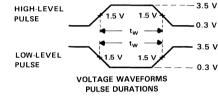

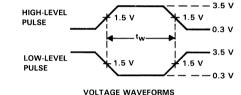

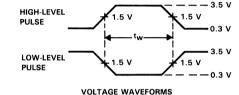

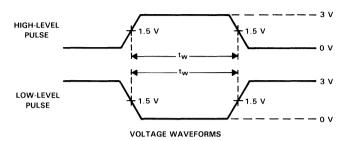

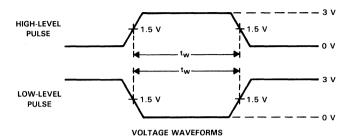

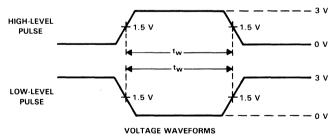

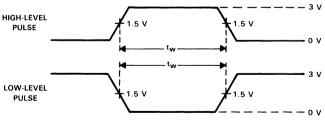

### Pulse duration (width) tw

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

TOGGLE =

The following symbols are used in function tables on TI data sheets.

н = high level (steady state) L low level (steady state) 1 transition from low to high level 1 transition from high to low level value/level or resulting value/level is routed to indicated destination value/level is reentered Х irrelevant (any input, including transitions) Z off (high impedance) state of a 3-state output the level of steady-state inputs A through H respectively QO the level of Q before the indicated steady-state input conditions were established complement of  $\Omega_0$  or level of  $\overline{\Omega}$  before the indicated steady-state input conditions were ŌΩ established  $Q_n$ level of Q before the most recent active transition indicated by ↓ or ↑ one high-level pulse one low-level pulse

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

each output changes to the complement of its previous level on each transition indicated by

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\bigcirc$  or  $\bigcirc$  , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

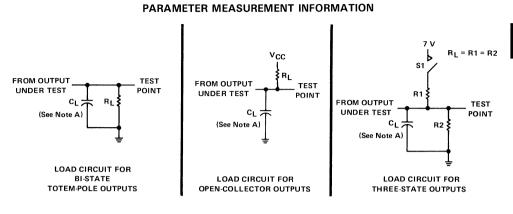

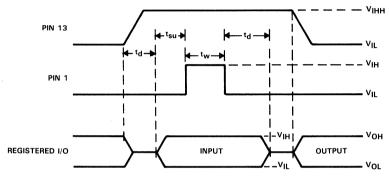

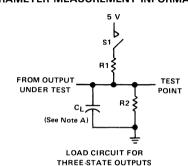

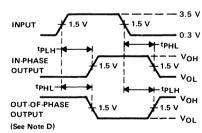

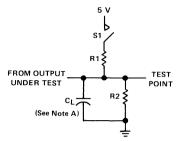

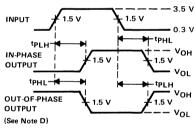

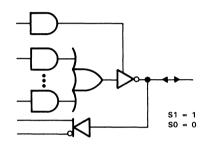

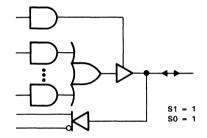

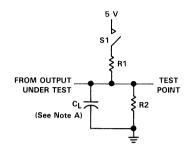

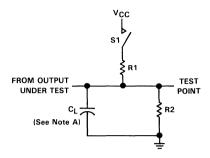

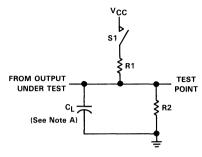

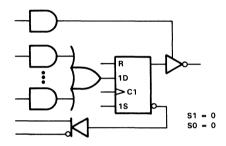

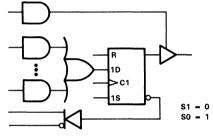

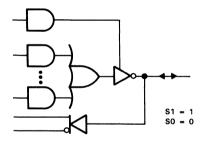

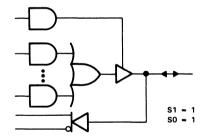

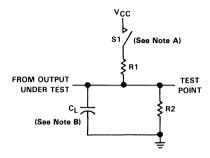

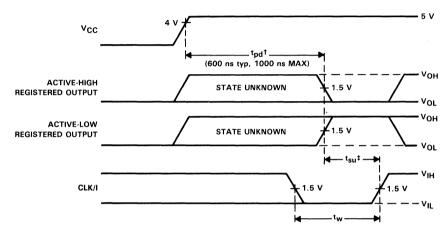

NOTE A: C<sub>1</sub> includes probe and jig capacitance.

NOTES: B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics: PRR  $\leq$  1 MHz,  $t_r = t_f = 2$  ns, duty cycle = 50%.

- D. When measuring propagation delay times of 3-state outputs, switch S1 is open.

**EXAMPLE:**

# General Information

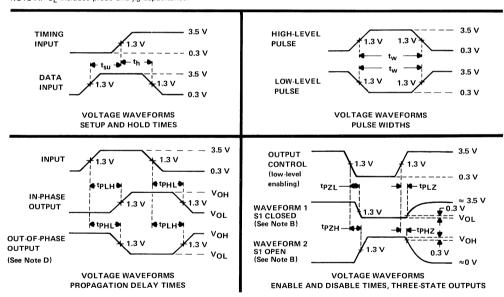

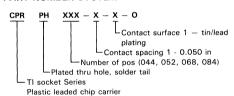

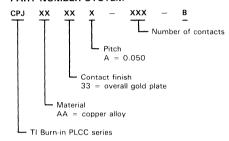

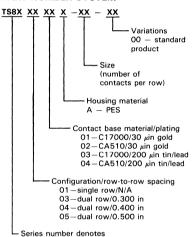

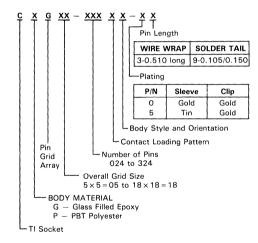

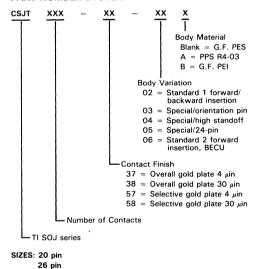

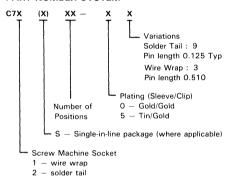

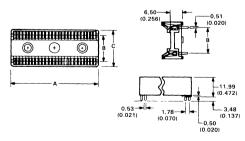

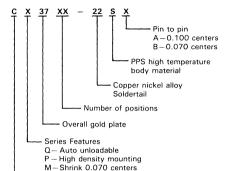

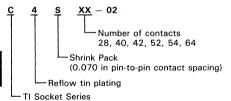

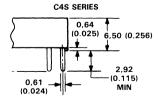

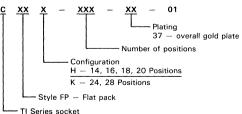

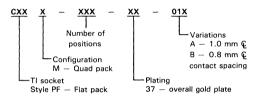

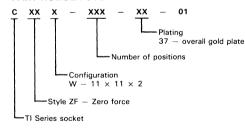

### PAL® NUMBERING SYSTEM AND ORDERING INSTRUCTIONS

Factory orders for leadership PAL® circuits described in this catalog should include a nine-part type number as explained in the example below. Exclude the prefix when ordering standard PALs.

PAL

TIB

PAL is a registered trademark of Monolithic Memories Inc.

### ADDRESSES FOR PAL AND FPLA PROGRAMMING AND SOFTWARE MANUFACTURERS T

### HARDWARE MANUFACTURERS

DATA I/O 10525 WILLOWS ROAD REDMOND, WA 98073-9746 (800) 247-5700

DIGITAL MEDIA, INC 11770 WARNER AVE, UNIT 225 FOUNTAIN VALLEY, CA 92708 (714) 751-1373

STAG MICRO SYSTEMS 1600 WYATT DRIVE SANTA CLARA, CA 95054 (800) 227-8836

### SOFTWARE MANUFACTURERS

DATA I/O (ABEL) 10525 WILLOWS ROAD REDMOND, WA 98073-9746 (800) 247-5700 PERSONAL CAD SYSTEMS (CUPL) 1290 PARKMOOR AVE SAN JOSE, CA 95126 (408) 971-1300

<sup>&</sup>lt;sup>†</sup>Texas Instruments does not endorse or warrant the suppliers referenced. Presently, Texas Instruments has certified DATA I/O, Sunrise, Structured Design and Digital Media. Other programmers are now in the certification process. For a current list of certified programmers, please contact your local TI sales representative.

### TI IMPACT™ DESIGN AND SERVICE CENTERS

Design and programming assistance is offered by Texas Instruments IMPACT™ Design and Service Centers. The centers are equipped with the latest in software and hardware tools for design, debugging, prototyping, and production on a local basis. Supported by a professional engineering staff, the centers provide complete code development, device programming, symbolization, functional and DC parametric testing.

### NORTHERN CALIFORNIA

MARSHALL IMPACT CENTER 336 LOS COCHES STREET MILPITAS, CA 95035 (408) 942-4600

### SOUTHERN CALIFORNIA

WYLE IMPACT CENTER 17872 COWAN AVENUE IRVINE, CA 92714 (714) 863-9953

### **BOSTON**

HALL-MARK IMPACT CENTER 6 COOK STREET, PINEHURST PARK BILLERICA, MA 01821 (617) 935-9777

General Information

Data Sheets

Application Reports 3

Mechanical Data 4

### PAL16L8A, PAL16L8A-2, PAL16R4A, PAL16R4A-2 PAL16R6A, PAL16R6A-2, PAL16R8A, PAL16R8A-2 STANDARD HIGH-SPEED PAL® CIRCUITS

FEBRUARY 1984-REVISED DECEMBER 1987

- Standard High-Speed (25 ns) PAL Family

- Choice of Operating Speeds

HIGH SPEED, A Devices . . . 35 MHz

HALF POWER, A-2 Devices . . . 18 MHz

- Choice of Input/Output Configuration

- Package Options Include Both Plastic and Ceramic Chip Carriers in Addition to Plastic and Ceramic DIPs

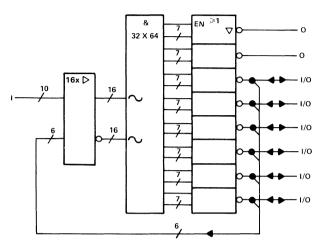

| DEVICE  | INPUTS | 3-STATE<br>0 OUTPUTS | REGISTERED<br>Q OUTPUTS | I/O PORTS |

|---------|--------|----------------------|-------------------------|-----------|

| PAL16L8 | 10     | 2                    | 0                       | 6         |

| PAL16R4 | 8      | 0                    | 4 (3-state)             | 4         |

| PAL16R6 | 8      | 0                    | 6 (3-state)             | 2         |

| PAL16R8 | 8      | 0                    | 8 (3-state)             | 0         |

### description

These programmable array logic devices feature high speed and a choice of either standard or half-power devices. They combine Advanced Low-Power Schottky† technology with proven titanium-tungsten fuses. These devices will provide reliable, high-performance substitutes for conventional TTL logic. Their easy programmability allows for quick design of "custom" functions and typically result in a more compact circuit board. In addition, chip carriers are available for further reduction in board space.

The Half-Power versions offer a choice of operating frequency, switching speeds, and power dissipation. In many cases, these Half-Power devices can result in significant power reduction from an overall system level.

The PAL16' M series is characterized for operation over the full military temperature range of -55 °C to 125 °C. The PAL16' C series is characterized for operation from 0 °C to 70 °C.

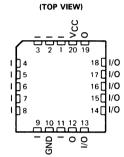

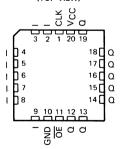

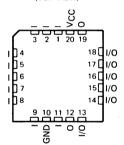

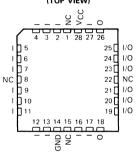

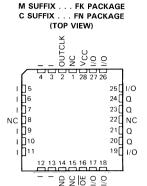

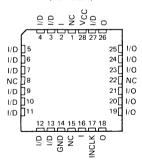

PAL16L8'

M SUFFIX . . . FH OR FK PACKAGE

C SUFFIX . . . FN PACKAGE

(TOP VIEW)

PAL is a registered trademark of Monolithic Memories Inc.

<sup>&</sup>lt;sup>†</sup>Integrated Schottky-Barrier diode-clamped transistor is patented by Texas Instruments, U.S. Patent Number 3,463,975.

9 10 11 12 13

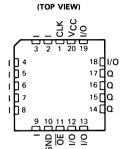

PAL16R8'

GND OE O

14 ∏ Q

hв

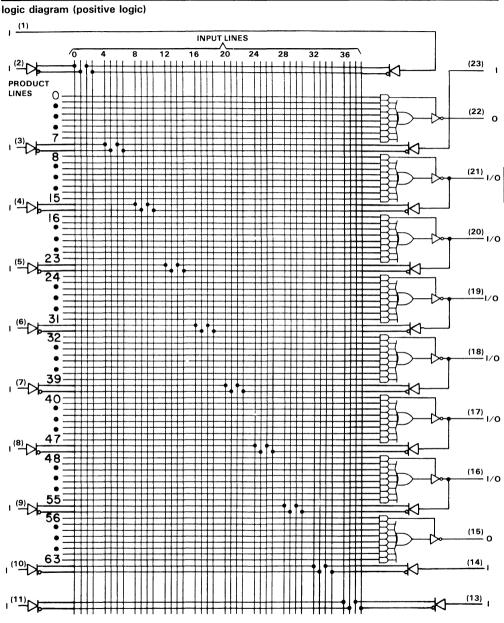

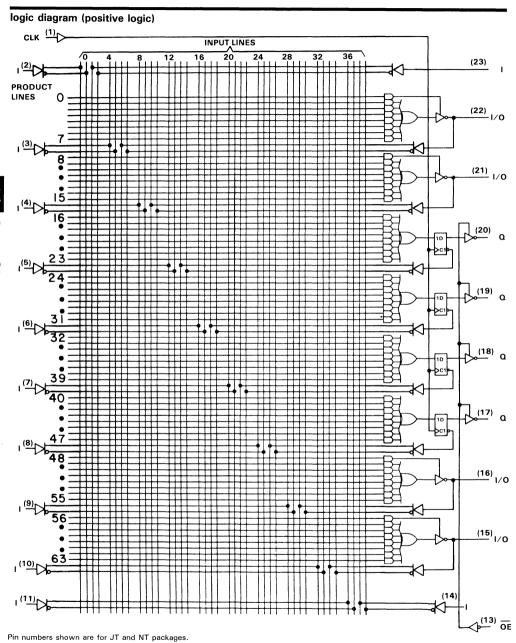

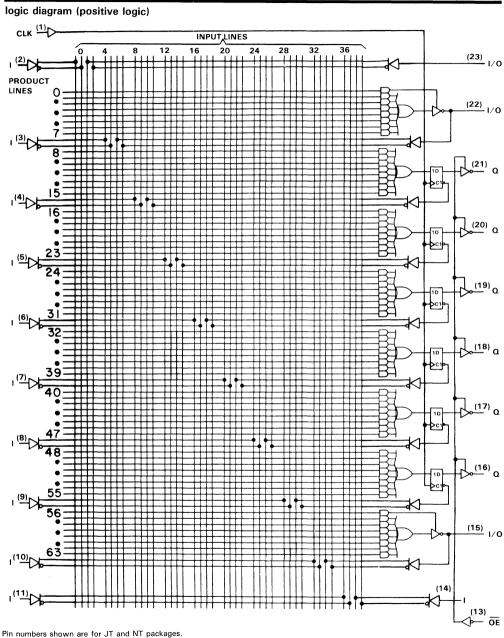

### functional block diagrams (positive logic)

~ denotes fused inputs

### functional block diagrams (positive logic)

### 'PAL16R6A 'PAL16R6A-2

'PAL16R8A 'PAL16R8A-2

~ denotes fused inputs

### PAL16L8A, PAL16L8A-2, PAL16R4A, PAL16R4A-2 PAL16R6A, PAL16R6A-2, PAL16R8A, PAL16R8A-2 STANDARD HIGH-SPEED *PAL*® CIRCUITS

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                  | . 7 | ٧ |

|---------------------------------------------------|-----|---|

| Input voltage (see Note 1)                        | 5.5 | ٧ |

| Voltage applied to a disabled output (see Note 1) | 5.5 | V |

| Operating free-air temperature range: M suffix    | 25° | С |

| C suffix                                          | 70° | С |

| Storage temperature range65°C to 1                | 50° | С |

NOTE 1: These ratings apply except for programming pins during a programming cycle.

### recommended operating conditions

|     | DADAMETED                      | N          | 1 SUFFIX | < | C   | UNIT |     |      |      |

|-----|--------------------------------|------------|----------|---|-----|------|-----|------|------|

|     | PARAMETER                      |            |          |   | MAX | MIN  | NOM | MAX  | UNIT |

| Vcc | Supply voltage                 |            | 4.5      | 5 | 5.5 | 4.75 | 5   | 5.25 | ٧    |

|     | High level innut valence       | OE input   | 2.4      |   | 5.5 | 2    |     | 5.5  | V    |

| VIH | High-level input voltage       | All others | 2        |   | 5.5 | 2    |     | 5.5  | 1 °  |

| VIL | Low-level input voltage        |            |          |   | 0.8 |      |     | 0.8  | V    |

| ЮН  | High-level output current      |            |          |   | - 2 |      |     | -3.2 | mA   |

| loL | Low-level output current       |            |          |   | 12  |      |     | 24   | mA   |

| TA  | Operating free-air temperature |            | - 55     |   | 125 | 0    |     | 70   | °C   |

### programming information

Texas Instruments Programmable Logic Devices can be programmed using widely available software and inexpensive device programmers.

Complete programming specifications, algorithms, and the latest information on hardware, software, and firmware are available upon request. Information on programmers capable of programming Texas Instruments Programmable Logic is also available, upon request, from the nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at (214) 997-5762.

### PAL16L8A, PAL16R4A, PAL16R6A, PAL16R8A STANDARD HIGH-SPEED PAL® CIRCUITS

### recommended operating conditions

|                 |                                            |            |     | M SUFFIX |     | (   |     |     |      |

|-----------------|--------------------------------------------|------------|-----|----------|-----|-----|-----|-----|------|

|                 |                                            |            | MIN | TYP      | MAX | MIN | TYP | MAX | UNIT |

| fclock          | Clock frequency                            |            | 0   |          | 25  | 0   |     | 35  | MHz  |

|                 | Data dissatism and Nation                  | Clock high | 15  |          |     | 12  |     |     |      |

| t <sub>w</sub>  | Pulse duration, see Note 2                 | Clock low  | 20  |          |     | 16  |     |     | ns   |

| t <sub>su</sub> | Setup time, input or feedback before CLK ↑ |            | 25  |          |     | 20  |     |     | ns   |

| th              | Hold time, input or feedback after CLK↑    |            | 0   |          |     | 0   |     |     | ns   |

NOTE 2: The total clock period of clock high and clock low must not exceed clock frequency, f<sub>clock</sub>. The minimum pulse durations specified are only for clock high or clock low, but not for both simultaneously.

### electrical characteristics over recommended operating free-air temperature range

|                 | 24245752  |                               | T CONDITIONS†           |            | N    | SUFFIX | <     | С   | SUFFIX           |       |      |

|-----------------|-----------|-------------------------------|-------------------------|------------|------|--------|-------|-----|------------------|-------|------|

|                 | PARAMETER | TEST CONDITIONS               |                         |            | MIN  | TYP‡   | MAX   | MIN | TYP <sup>‡</sup> | MAX   | UNIT |

| V <sub>IK</sub> |           | V <sub>CC</sub> = MIN,        | I <sub>I</sub> = -18 mA |            |      |        | -1.5  |     |                  | - 1.5 | V    |

| VoH             |           | V <sub>CC</sub> = MIN,        | I <sub>OH</sub> = MAX   |            | 2.4  | 3.2    |       | 2.4 | 3.3              |       | V    |

| VOL             |           | V <sub>CC</sub> = MIN,        | I <sub>OL</sub> = MAX   |            |      | 0.25   | 0.4   |     | 0.35             | 0.5   | V    |

| lozh            | Outputs   | V MAN                         | V- 27V                  |            |      |        | 20    |     |                  | 20    |      |

| 10ZH            | I/O ports | V <sub>CC</sub> = MAX,        | $V_0 = 2.7 \text{ V}$   |            |      |        | 100   |     |                  | 100   | μΑ   |

| 1               | Outputs   | VCC = MAX,                    | V <sub>O</sub> = 0.4 V  |            |      |        | - 20  |     |                  | - 20  | μΑ   |

| IOZL            | I/O ports | VCC = WAX,                    | VO = 0.4 V              |            |      |        | -250  |     |                  | - 250 | μΑ   |

| lj              |           | $V_{CC} = MAX,$               | $V_{I} = 5.5 V$         |            |      |        | 0.2   |     |                  | 0.1   | mA   |

| Ιн              |           | $V_{CC} = MAX,$               | $V_1 = 2.7 V$           |            |      |        | 25    |     |                  | 20    | μА   |

|                 |           |                               | .,                      | OE INPUT   |      |        | -0.25 |     |                  | -0.4  |      |

| ηL              |           | V <sub>CC</sub> = MAX,        | $V_{i} = 0.4 V$         | All others |      |        | -0.2  |     |                  | -0.2  | mA   |

| IO§             |           | V <sub>CC</sub> = MAX,        | $V_0 = 2.25 \text{ V}$  |            | - 30 |        | -125  | -30 |                  | -125  | mA   |

| lcc             |           | $V_{CC} = MAX,$ $V_{I} = 0 V$ | Outputs Open            |            |      | 140    | 185   |     | 140              | 180   | mA   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

### switching characteristics over recommended supply voltage and operating free-air temperature ranges (unless otherwise noted)

| PARAMETER        | FROM    | то              | TEST COMPLETIONS     |     | M SUFF | IX  | (   | SUFFIX | <   | UNIT |

|------------------|---------|-----------------|----------------------|-----|--------|-----|-----|--------|-----|------|

| PANAIVIETEN      | FROW    | TEST CONDITIONS | TEST CONDITIONS      | MIN | TYP‡   | MAX | MIN | TYP‡   | MAX | UNIT |

| f <sub>max</sub> |         |                 |                      | 25  | 45     |     | 35  | 45     |     | MHz  |

| <sup>t</sup> pd  | 1, 1/0, | 0, 1/0          |                      |     | 15     | 30  |     | 15     | 25  | ns   |

| t <sub>pd</sub>  | CLK↑    | Q               | $R_L = 500 \Omega$ , |     | 10     | 20  |     | 10     | 15  | ns   |

| t <sub>en</sub>  | ŌĒ↓     | Q               | $C_L = 50 pF$ ,      |     | 15     | 25  |     | 15     | 22  | ns   |

| t <sub>dis</sub> | ŌĒ↑     | Q               | See Note 3           |     | 10     | 25  |     | 10     | 15  | ns   |

| t <sub>en</sub>  | 1, 1/0  | 0, 1/0          |                      |     | 14     | 30  |     | 14     | 25  | ns   |

| <sup>t</sup> dis | 1, 1/0  | 0, 1/0          |                      |     | 13     | 30  |     | 13     | 25  | ns   |

$<sup>^{\</sup>ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

$<sup>^{\</sup>ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

<sup>§</sup>The output conditions have been chosen to produce a current that closely aproximates one half of the true short-circuit output current, Ins.

### PAL16L8A-2, PAL16R4A-2, PAL16R6A-2, PAL16R8A-2 STANDARD HIGH-SPEED PAL® CIRCUITS

### recommended operating conditions

|                 |                                |             |     | VI SUFF | IX                                      |     | C SUFFIX |     | LIBUT |

|-----------------|--------------------------------|-------------|-----|---------|-----------------------------------------|-----|----------|-----|-------|

|                 |                                |             | MIN | TYP     | MAX                                     | MIN | TYP      | MAX | UNIT  |

| fclock          | Clock frequency                |             | 0   |         | 16                                      | 0   |          | 18  | MHz   |

| +               | Pulse duration, see Note 2     | Clock high  | 28  |         | *************************************** | 25  |          |     |       |

| τ <sub>w</sub>  | Tuise duration, see Note 2     | Clock low   | 28  |         |                                         | 25  |          |     | ns    |

| t <sub>su</sub> | Setup time, input or feedback  | before CLK↑ | 35  |         |                                         | 28  |          |     | ns    |

| th              | Hold time, input or feedback a | fter CLK↑   | 0   |         |                                         | 0   |          |     | ns    |

NOTE 2: The total clock period of clock high and clock low must not exceed clock frequency, f<sub>clock</sub>. The minimum pulse durations specified are only for clock high or clock low, but not for both simultaneously.

### electrical characteristics over recommended operating free-air temperature range

|                | PARAMETER | 750                           | T CONDITIONS†           |            | ٨   | SUFFI            | X     | С    | SUFFIX | (     | UNIT |

|----------------|-----------|-------------------------------|-------------------------|------------|-----|------------------|-------|------|--------|-------|------|

| FANAIVIE I EK  |           | 168                           | TEST CONDITIONS.        |            |     | TYP <sup>‡</sup> | MAX   | MIN  | TYP‡   | MAX   | UNIT |

| VIK            |           | V <sub>CC</sub> = MIN,        | I <sub>I</sub> = -18 mA |            |     |                  | -1.5  |      |        | - 1.5 | V    |

| Vон            |           | V <sub>CC</sub> = MIN,        | I <sub>OH</sub> = MAX   |            | 2.4 | 3.2              |       | 2.4  | 3.3    |       | V    |

| VOL            |           | V <sub>CC</sub> = MIN,        | I <sub>OL</sub> = MAX   |            |     | 0.25             | 0.4   |      | 0.35   | 0.5   | V    |

| lozh           | Outputs   | V MAY                         | V <sub>O</sub> = 2.7 V  |            |     |                  | 20    |      |        | 20    | _    |

| ·02n           | I/O ports | $V_{CC} = MAX,$               | $v_0 = 2.7 \text{ v}$   |            |     |                  | 100   |      |        | 100   | μΑ   |

| 1              | Outputs   | VCC = MAX,                    | Vo = 0.4 V              |            |     |                  | - 20  |      |        | - 20  |      |

| IOZL           | I/O ports | T VCC = MAX,                  | ν <sub>0</sub> = 0.4 ν  |            |     |                  | - 250 |      |        | - 250 | μΑ   |

| l <sub>i</sub> |           | V <sub>CC</sub> = MAX,        | $V_{  } = 5.5 V$        |            |     |                  | 0.2   |      |        | 0.1   | mA   |

| JН             |           | $V_{CC} = MAX$ ,              | V <sub>I</sub> = 2.7 V  |            |     |                  | 25    |      |        | 20    | μΑ   |

|                |           |                               |                         | OE INPUT   |     |                  | -0.2  |      |        | -0.2  |      |

| ΊL             |           | $V_{CC} = MAX,$               | $V_1 = 0.4 V$           | All others |     |                  | -0.1  |      |        | -0.1  | mA   |

| IO§            |           | V <sub>CC</sub> = MAX,        | $V_0 = 2.25 \text{ V}$  |            | -30 |                  | - 125 | - 30 |        | - 125 | mA   |

| lcc            |           | $V_{CC} = MAX,$ $V_{I} = 0 V$ | Outputs Open            |            |     | 75               | 95    |      | 70     | 90    | mA   |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

### switching characteristics over recommended supply voltage and operating free-air temperature ranges (unless otherwise noted)

| DARAMETER        | 50014   |        | TEST CONDITIONS      | M SUFFIX |                  |     | C   |      |     |      |

|------------------|---------|--------|----------------------|----------|------------------|-----|-----|------|-----|------|

| PARAMETER        | FROM    | то     | TEST CONDITIONS      |          | TYP <sup>‡</sup> | MAX | MIN | TYP‡ | MAX | UNIT |

| fmax             |         |        |                      | 16       | 25               |     | 18  | 25   |     | MHz  |

| t <sub>pd</sub>  | 1, 1/0, | 0, 1/0 |                      |          | 25               | 40  |     | 25   | 35  | ns   |

| t <sub>pd</sub>  | CLK ↑   | a      | $R_L = 500 \Omega$ , |          | 11               | 35  |     | 11   | 25  | ns   |

| t <sub>en</sub>  | ŌĒ↓     | Q      | $C_L = 50 pF$ ,      |          | 20               | 35  |     | 20   | 25  | ns   |

| <sup>t</sup> dis | ŌĒ↑     | a      | See Note 3           |          | 11               | 30  |     | 11   | 20  | ns   |

| t <sub>en</sub>  | 1, 1/0  | 0, 1/0 |                      |          | 25               | 40  |     | 25   | 35  | ns   |

| tdis             | 1, 1/0  | 0, 1/0 |                      |          | 25               | 35  |     | 25   | 30  | ns   |

$<sup>^{\</sup>ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

<sup>&</sup>lt;sup>‡</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

<sup>§</sup>The output conditions have been chosen to produce a current that closely aproximates one half of the true short-circuit output current, IOS.

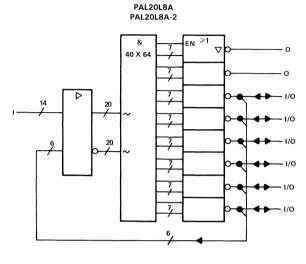

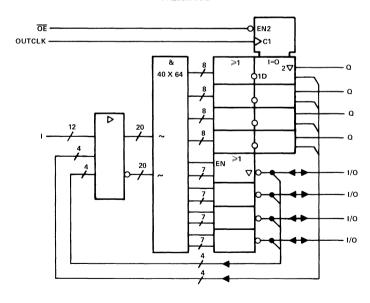

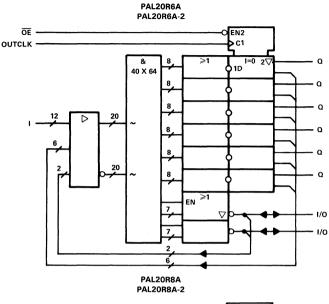

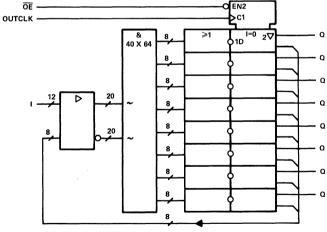

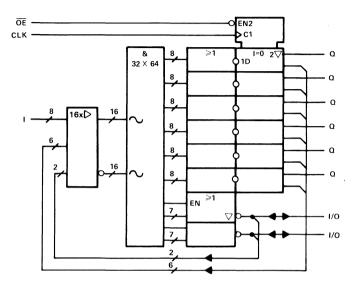

### PAL20L8A, PAL20R4A, PAL20R6A, PAL20R8A STANDARD HIGH-SPEED PAL® CIRCUITS

D2706, DECEMBER 1982-REVISED DECEMBER 1987

- Standard High Speed (25 ns) PAL Family

- Choice of Input/Output Configuration

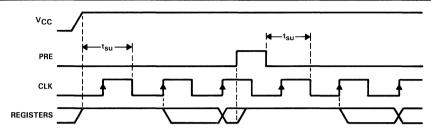

- Preload Capability on Output Registers

- DIP Options Include Both 300-mil Plastic and 600-mil Ceramic

| DEVICE    | I INPUTS | 3-STATE<br>O OUTPUTS | REGISTERED<br>Q OUTPUTS | I/O<br>PORTS |

|-----------|----------|----------------------|-------------------------|--------------|

| 'PAL20L8A | 14       | 2                    | 0                       | 6            |

| 'PAL20R4A | 12       | 0                    | 4 (3-state buffers)     | 4            |

| 'PAL20R6A | 12       | 0                    | 6 (3-state buffers)     | 2            |

| 'PAL20R8A | 12       | 0                    | 8 (3-state buffers)     | 0            |

### description

These programmable array logic devices feature high speed and a choice of either standard or half-power speeds. They combine Advanced Low-Power Schottky<sup>†</sup> technology with proven titanium-tungsten fuses. These devices will provide reliable, high performance substitutes over conventional TTL logic. Their easy programmability allows for quick design of "custom" functions and typically result in a more compact circuit board. In addition, chip carriers are also available for further reduction in board space.

In addition, extra circuitry has been provided to allow loading of each register asynchronously to either a high or low state. This feature simplifies testing because the registers can be set to an initial state prior to executing the test sequence.

The PAL20' series is characterized for operation over the full military temperature range of  $-55\,^{\circ}\text{C}$  to 125 $^{\circ}\text{C}$ . The commercial range is characterized from 0 $^{\circ}\text{C}$  to 70 $^{\circ}\text{C}$ .

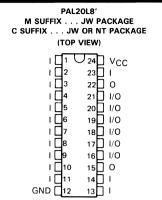

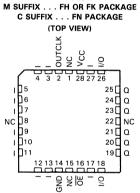

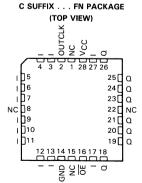

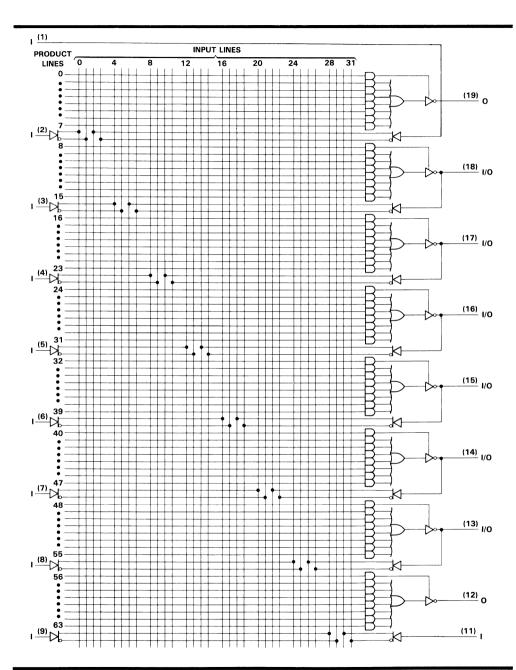

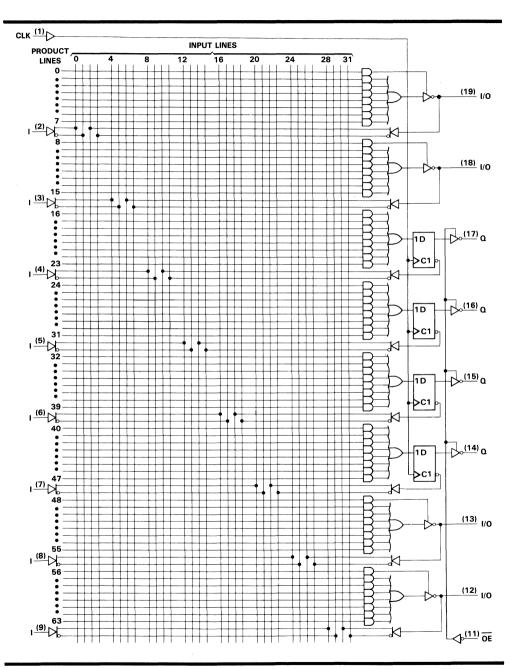

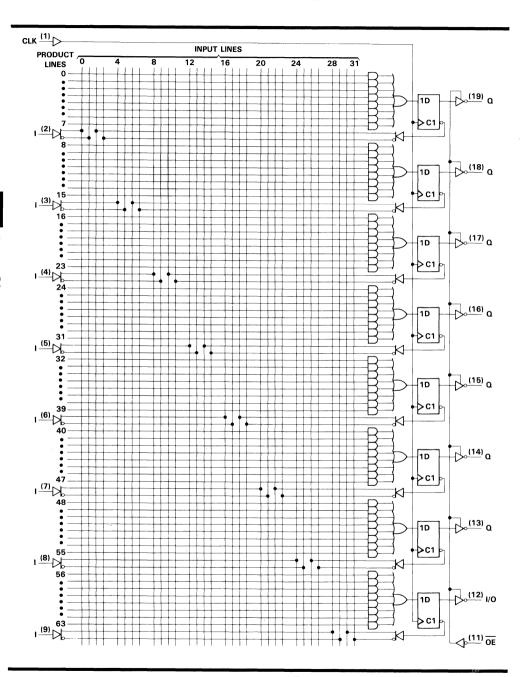

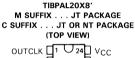

PAL20L8'

M SUFFIX . . . FH OR FK PACKAGE

C SUFFIX . . . FN PACKAGE

(TOP VIFW)

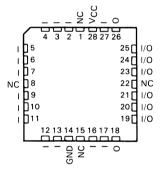

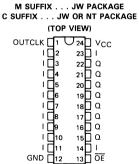

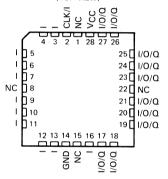

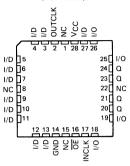

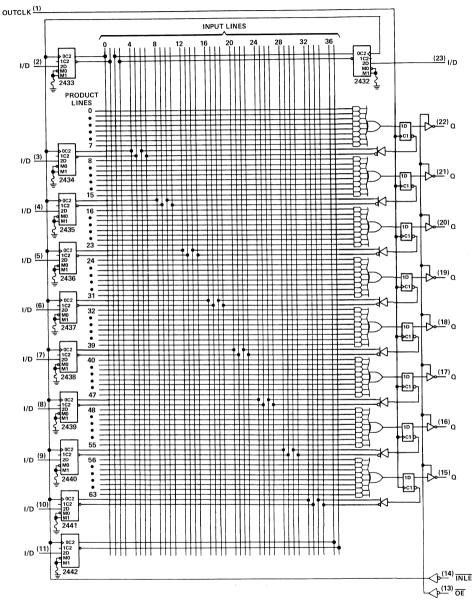

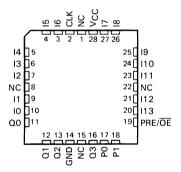

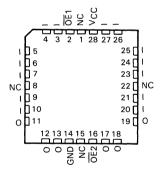

#### PAL20R4' M SUFFIX . . . JW PACKAGE C SUFFIX . . . JW OR NT PACKAGE (TOP VIEW) OUTCLK 1 24 V<sub>CC</sub> 21 1/0 1 □4 1 🛮 5 20 Q 19 🖸 Q 18 Q 17 Q 16 1/0 1 10 15 1/0

GND 712

14 📗 📗

13 OE

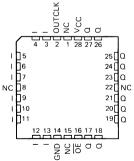

PAL20R8'

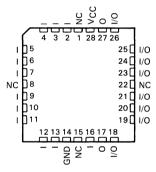

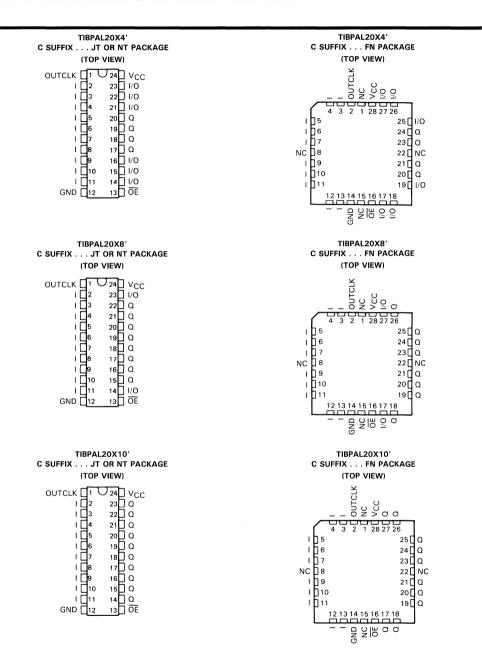

|              |       | PAL2         | DR4'  |       |       |

|--------------|-------|--------------|-------|-------|-------|

| M SUFF       | IX    | . FH         | OR FI | K PAC | KAGE  |

| C St         | JFFIX |              | FN PA | ACKAC | 3E    |

|              | ť     | TOP V        | (IEW) |       |       |

|              | •     |              |       |       |       |

|              |       | 7            |       |       |       |

|              |       | OUTCLK<br>NC | VCC   | 0     |       |

|              |       | ōž           | > _   | _ ≥   |       |

|              | 4 3   | 2 1          | 28 27 | 7 26  | 7     |

| ıhs          | , ,   | - '          | 2021  | 25    | d 1/0 |

| . 5          |       |              |       |       | 7     |

| 1 6          |       |              |       | 24    | 9 -   |

| 1 <b>4</b> 7 |       |              |       | 23    | Qα    |

| NC []8       |       |              |       | 22    | □ NC  |

| 1 🛮 9        |       |              |       | 21    | ďα    |

| 1 🛮 10       |       |              |       | 20    | ďα    |

| 1 1511       |       |              |       | 19    | _     |

|              | 12 13 | 14 15        | 16 17 |       | ٦″~   |

|              | عَث   |              | صد    | ےما   |       |

|              |       | ე ე          | 등 -   | 0     |       |

|              |       | GND          | Ü     | _     |       |

|              |       | -            |       |       |       |

DA 1 00D 4/

PAL20R8'

M SUFFIX . . . FH OR FK PACKAGE

PAL20R6'

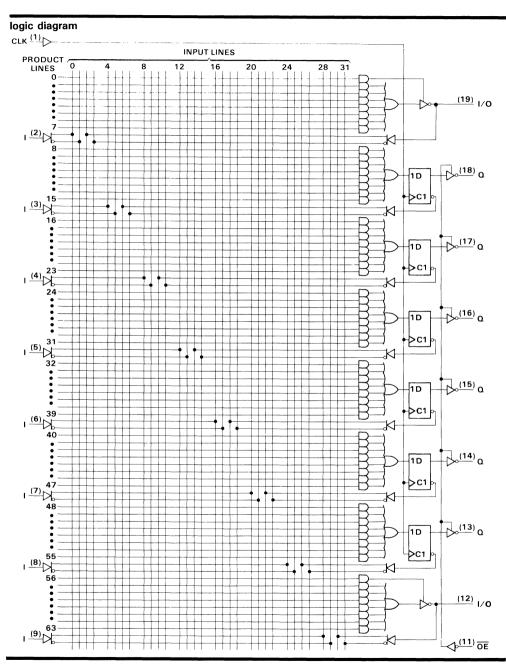

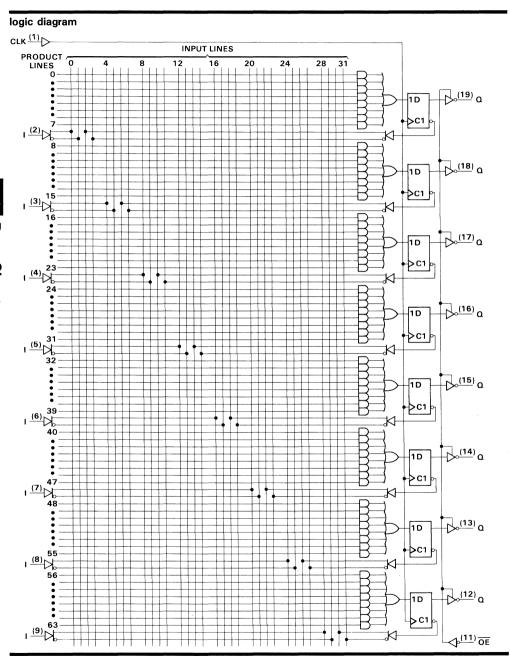

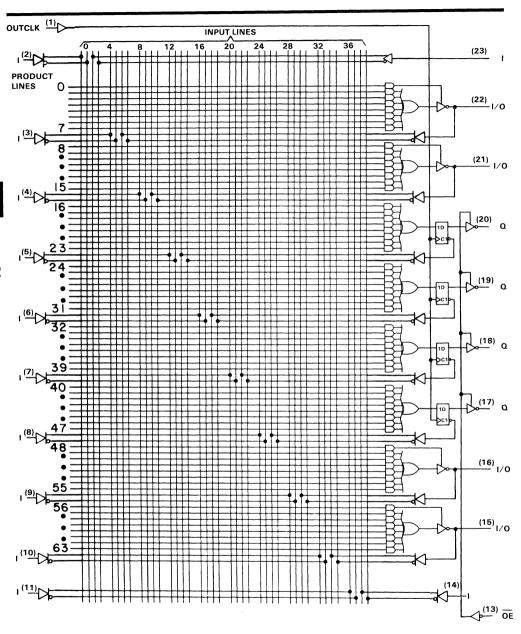

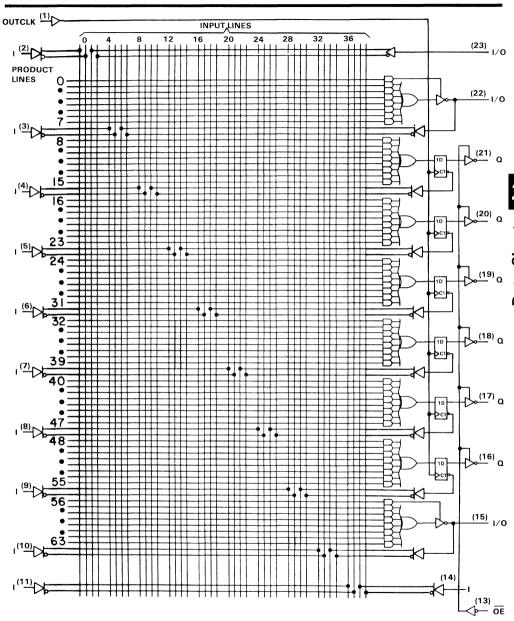

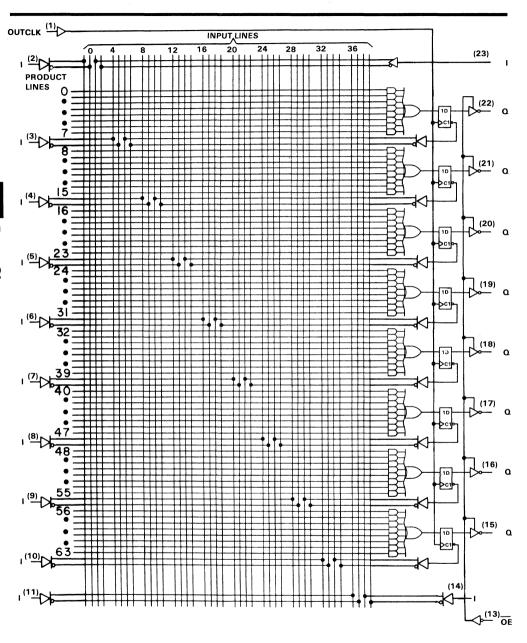

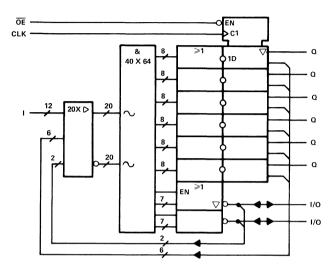

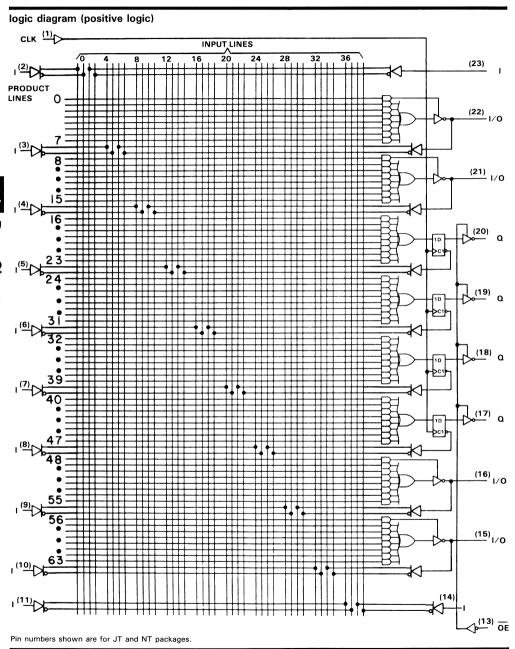

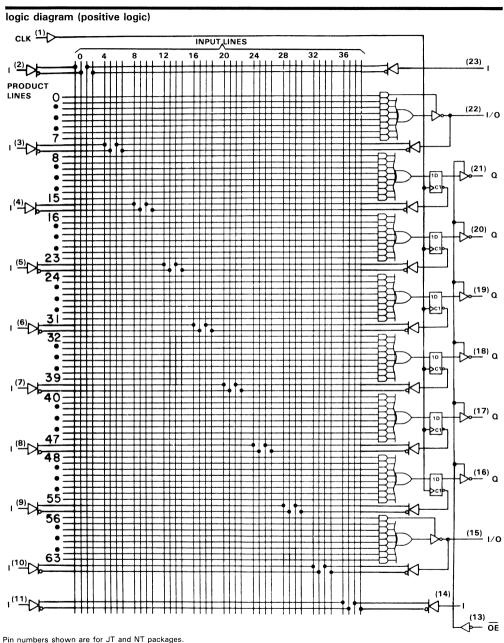

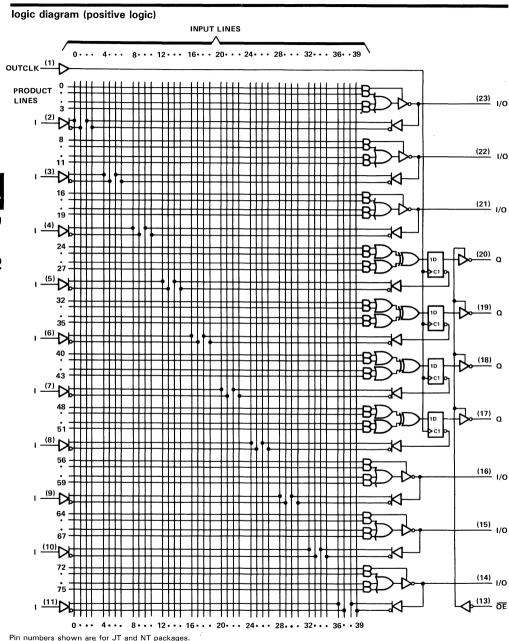

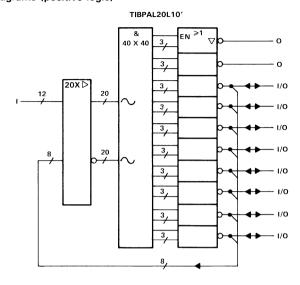

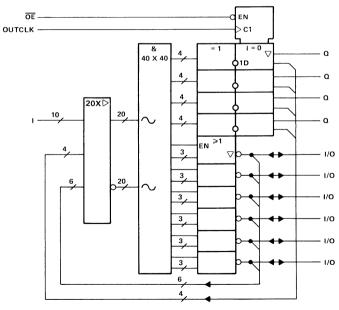

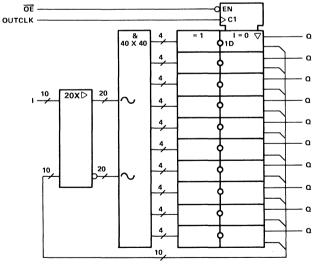

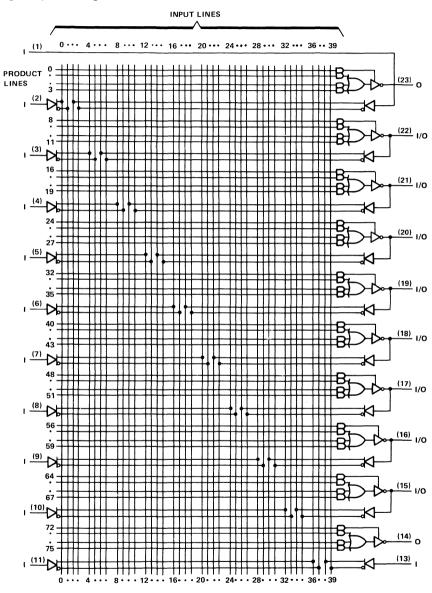

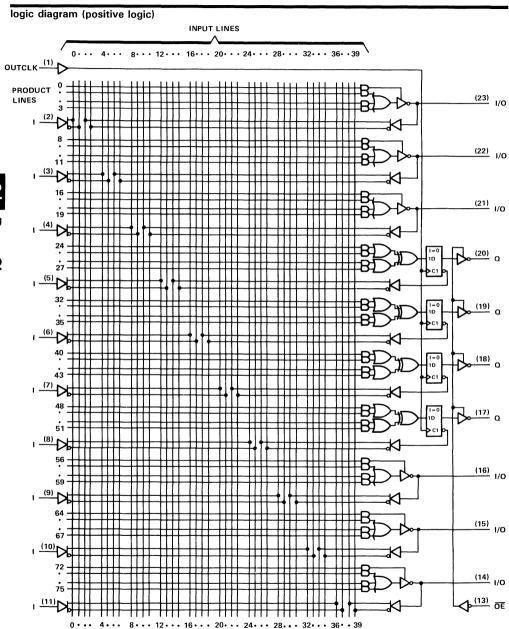

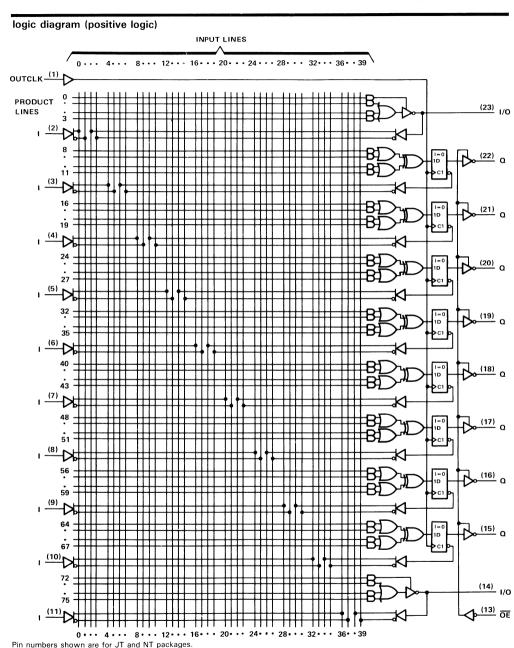

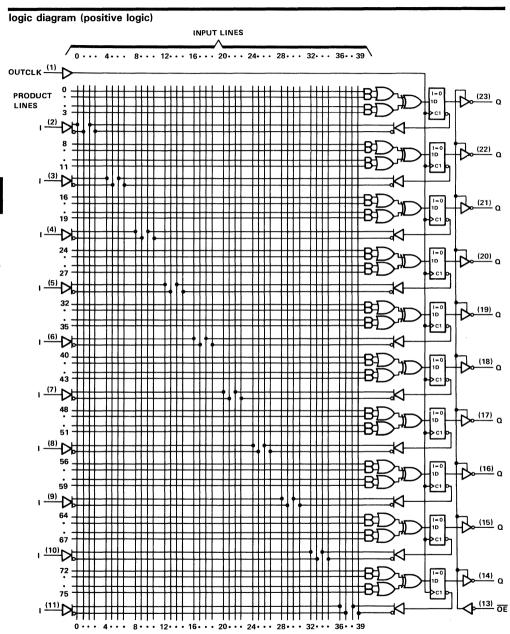

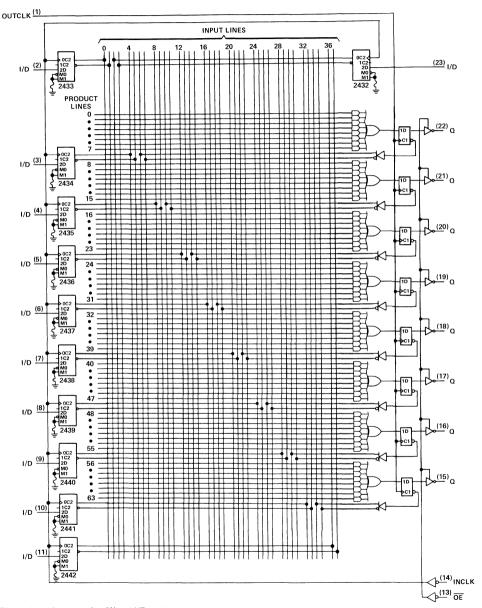

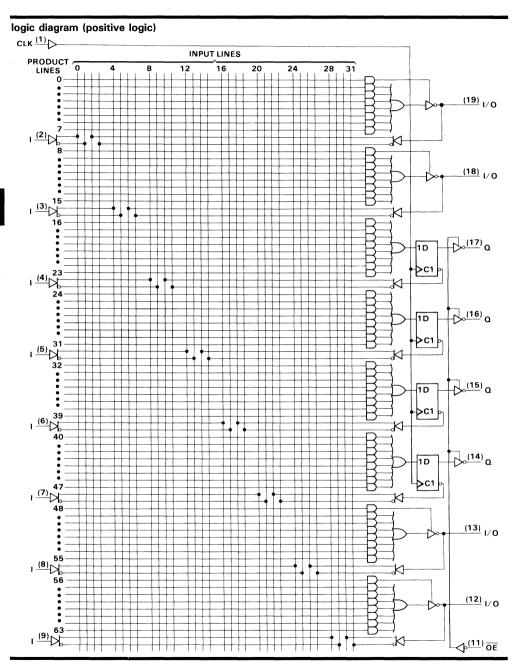

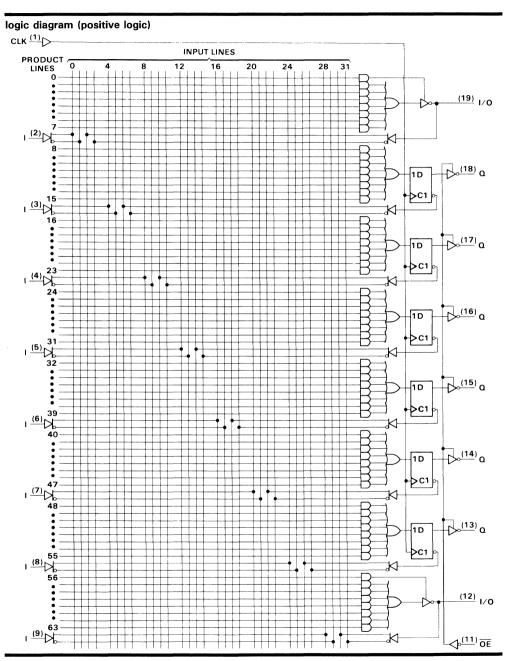

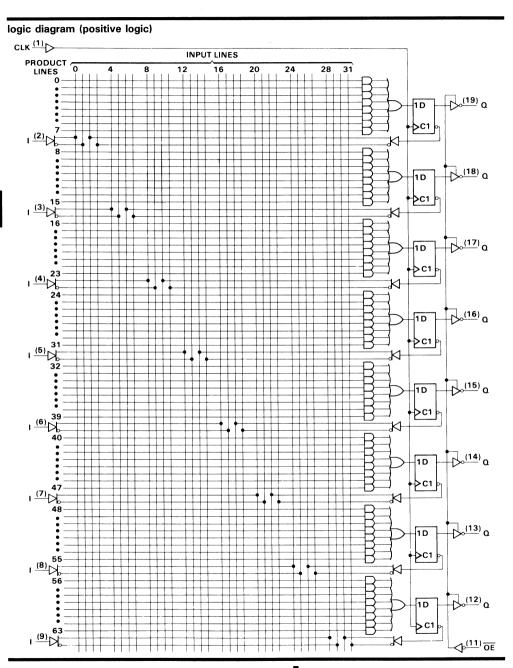

#### functional block diagrams (positive logic)

PAL20R4A PAL20R4A-2

#### functional block diagrams (positive logic)

#### PAL20L8A, PAL20R4A, PAL20R6A, PAL20R8A STANDARD HIGH-SPEED PAL® CIRCUITS

| absol | ute max | imum | ratings | over | operating | free-air | temperature | range | (unless | otherw | ise noted) |  |

|-------|---------|------|---------|------|-----------|----------|-------------|-------|---------|--------|------------|--|

|       |         |      |         |      |           |          |             |       |         |        |            |  |

| Supply voltage, VCC (see Note 1)                  |        | . 7  | ٧  |

|---------------------------------------------------|--------|------|----|

| Input voltage (see Note 1)                        |        | 5.5  | ٧  |

| Voltage applied to a disabled output (see Note 1) |        | 5.5  | ٧  |

| Operating free-air temperature range: M SUFFIX 55 | °C to  | 125° | °C |

| C SUFFIX                                          | 0°C to | 709  | ٥С |

| Storage temperature range65                       | °C to  | 150  | ٥С |

NOTE 1: These ratings apply except for programming pins during a programming cycle.

#### recommended operating conditions

|                               | PARAMETER                                     |      |      | M SUFFIX C SUFFIX |     |      |     |      | UNIT |

|-------------------------------|-----------------------------------------------|------|------|-------------------|-----|------|-----|------|------|

|                               |                                               |      |      | NOM               | MAX | MIN  | NOM | MAX  | UNII |

| Vcc                           | V <sub>CC</sub> Supply voltage                |      |      | 5                 | 5.5 | 4.75 | 5   | 5.25 | ٧    |

| VIH                           | High-level input voltage                      |      | 2    |                   | 5.5 | 2    |     | 5.5  | >    |

| VIL                           | V <sub>IL</sub> Low-level input voltage       |      |      |                   | 0.8 |      |     | 0.8  | V    |

| IOH High-level output current |                                               |      |      |                   | - 2 |      |     | -3.2 | mA   |

| IOL Low-level output current  |                                               |      |      | 12                |     |      | 24  | mA   |      |

| fclock                        | Clock frequency                               |      | 0    |                   | 20  | 0    |     | 30   | MHz  |

|                               | Pulse duration, clock                         | High | 20   |                   |     | 15   |     |      | ns   |

| tw                            | ruise duration, clock                         | Low  | 20   |                   |     | 15   |     |      | ns   |

| t <sub>su</sub>               | Setup time, input or feedback before OUTCLK1  |      | 30   |                   |     | 25   |     |      | ns   |

| th                            | th Hold time, input or feedback after OUTCLK1 |      | 0    |                   |     | 0    |     |      | ns   |

| TA                            | Operating free-air temperature                |      | - 55 |                   | 125 | 0    |     | 70   | °C   |

#### programming information

Texas Instruments Programmable Logic Devices can be programmed using widely available software and inexpensive device programmers.

Complete programming specifications, algorithms, and the latest information on hardware, software, and firmware are available upon request. Information on programmers capable of programming Texas Instruments Programmable Logic is also available, upon request, from the nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at (214) 997-5762.

### PAL20L8A, PAL20R4A, PAL20R6A, PAL20R8A STANDARD HIGH-SPEED PAL® CIRCUITS

#### electrical characteristics over recommended free-air operating temperature range

| BA   | RAMETER      | TEST CONDITIONS†                                                         | N    | 1 SUFFI          | Х     | C    | LINUT            |       |      |

|------|--------------|--------------------------------------------------------------------------|------|------------------|-------|------|------------------|-------|------|

| PAI  | NAMETER      | TEST CONDITIONS.                                                         | MIN  | TYP <sup>‡</sup> | MAX   | MIN  | TYP <sup>‡</sup> | MAX   | UNIT |

| ViK  |              | V <sub>CC</sub> = MIN, I <sub>I</sub> = -18 mA                           |      |                  | - 1.5 |      |                  | - 1.5 | V    |

| Voн  |              | V <sub>CC</sub> = MIN, I <sub>OH</sub> = MAX                             | 2.4  | 3.2              |       | 2.4  | 3.3              |       | V    |

| VOL  |              | V <sub>CC</sub> = MIN, I <sub>OL</sub> = MAX                             |      | 0.25             | 0.4   |      | 0.35             | 0.5   | V    |

| lozu | O, Q outputs | V <sub>CC</sub> = MAX, V <sub>IH</sub> = 2.7 V                           |      |                  | 20    |      |                  | 20    | μА   |

| lozh | I/O ports    | VCC = MAX, VIH = 2:7 V                                                   |      |                  | 100   |      |                  | 100   | μΑ   |

|      | O, Q outputs | $V_{CC} = MAX, V_{IH} = 0.4 V$                                           | Ĺ    |                  | - 20  |      |                  | - 20  |      |

| lozL | I/O ports    | VCC = WAX, VIH = 0.4 V                                                   |      |                  | - 250 |      |                  | - 250 | μΑ   |

| ſ.   | OE Input     | V MAY V. E.E.V.                                                          |      |                  | 0.2   |      |                  | 0.2   |      |

| 11   | All others   | $V_{CC} = MAX, V_I = 5.5 V$                                              |      |                  | 0.1   |      |                  | 0.1   | mA   |

| 1    | OE Input     | V MAN V 27V                                                              |      |                  | 40    |      |                  | 40    |      |

| ΉΗ   | All others   | $V_{CC} = MAX$ , $V_I = 2.7 V$                                           |      |                  | 20    |      |                  | 20    | μΑ   |

|      | OE Input     | MAN N 0 4 N                                                              |      |                  | -0.4  |      |                  | -0.4  |      |

| ηL   | All others   | $V_{CC} = MAX, V_I = 0.4 V$                                              |      |                  | -0.2  |      |                  | -0.2  | mA   |

| IO§  |              | $V_{CC} = MAX$ , $V_{O} = 2.25 V$                                        | - 30 |                  | - 125 | - 30 |                  | - 125 | mA   |

| lcc  |              | $V_{CC} = MAX$ , $V_I = 0 V$ , Outputs open, $\overline{OE}$ at $V_{IH}$ |      | 150              | 210   |      | 150              | 210   | mA   |

$<sup>^\</sup>dagger$ For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $^\ddagger$ All typical values are V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

### switching characteristics over recommended operating free-air temperature range (unless otherwise noted)

| DADAMETED        | FDOM    | FROM TO TEST CONDITIONS |                        | N  | M SUFFIX         |     |     | C SUFFIX         |     |      |

|------------------|---------|-------------------------|------------------------|----|------------------|-----|-----|------------------|-----|------|

| PARAMETER        | FRUM    | 10                      | TEST CONDITIONS        |    | TYP <sup>‡</sup> | MAX | MIN | TYP <sup>‡</sup> | MAX | UNIT |

| f <sub>max</sub> |         |                         |                        | 20 |                  |     | 30  |                  |     | MHz  |

| t <sub>pd</sub>  | I, I/O  | 0, 1/0                  |                        |    | 15               | 30  |     | 15               | 25  | ns   |

| <sup>t</sup> pd  | OUTCLK↑ | Q                       | $R_L = 500 \Omega$ ,   |    | 10               | 20  |     | 10               | 15  | ns   |

| t <sub>en</sub>  | ŌĒ      | Q                       | C <sub>L</sub> = 50 pF |    | 10               | 25  |     | 10               | 20  | ns   |

| t <sub>dis</sub> | ŌĒ↑     | Q                       | See Note 2             |    | 11               | 25  |     | 11               | 20  | ns   |

| t <sub>en</sub>  | I, I/O  | 0, 1/0                  |                        |    | 14               | 30  |     | 14               | 25  | ns   |

| <sup>t</sup> dis | 1, 1/0  | 0, 1/0                  |                        |    | 12               | 30  |     | 12               | 25  | ns   |

$<sup>^{\</sup>ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

NOTE 2: Load circuits and voltage waveforms are shown in Section 1.

<sup>§</sup>The output conditions have been chosen to produce a current that closely approximates one half the true short-circuit current, IOS.

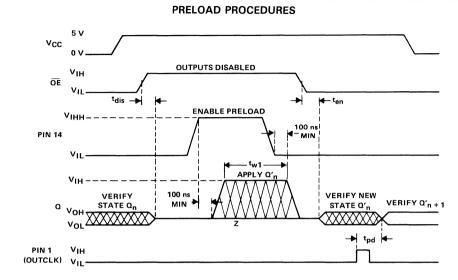

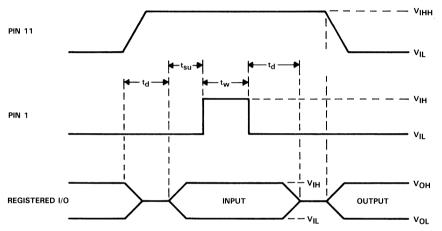

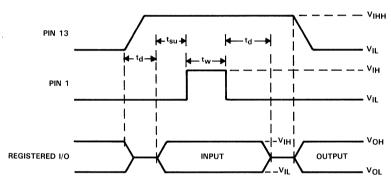

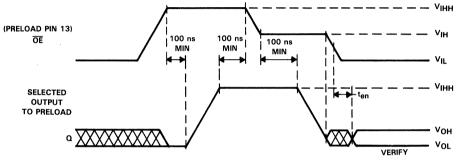

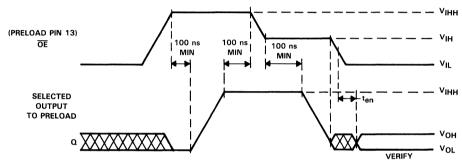

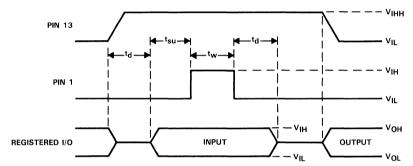

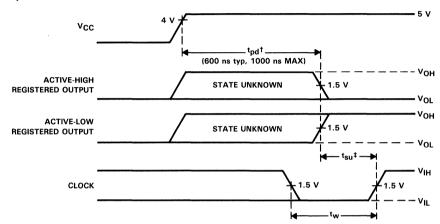

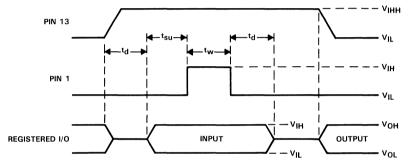

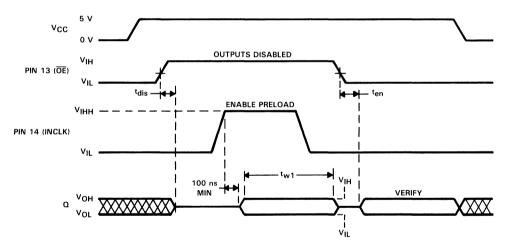

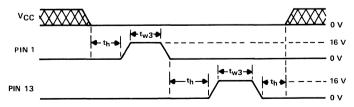

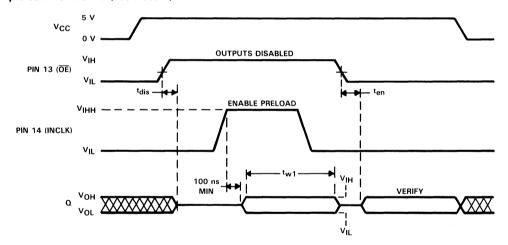

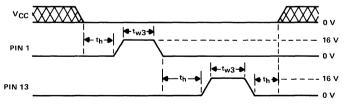

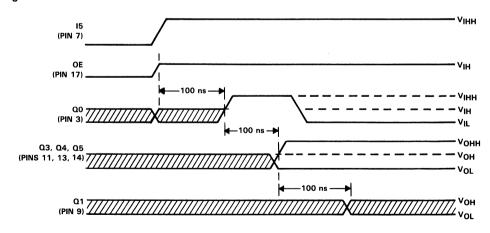

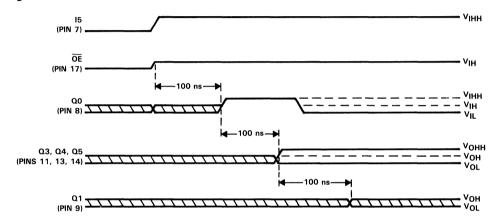

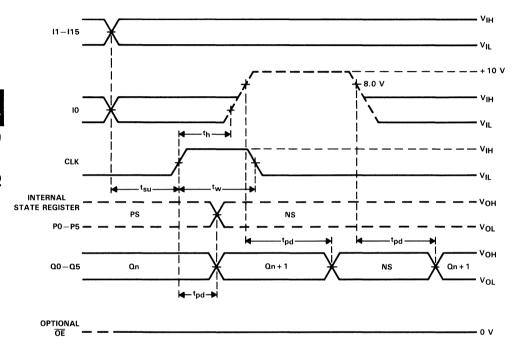

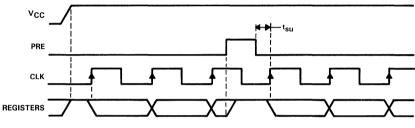

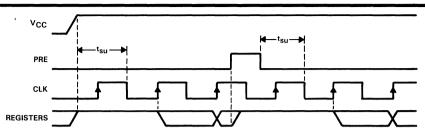

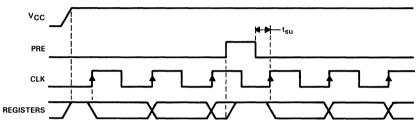

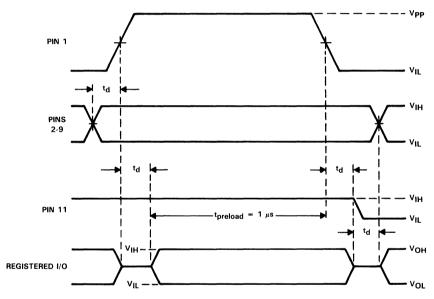

FIGURE 1. PRELOAD WAVEFORMS

#### preload procedure for registered outputs

- Step 1 Pin 13 to VIH, Pin 1 to VIL, and VCC to 5 volts.

- Step 2 Pin 14 to VIHH for 10 to 50 microseconds.

- Step 3 Apply V<sub>IL</sub> for a low and V<sub>IH</sub> for a high at the Q outputs.

- Step 4 Pin 14 to VIL.

- Step 5 Remove the voltages applied to the outputs.

- Step 6 Pin 13 to VIL.

- Step 7 Check the output states to verify preload.

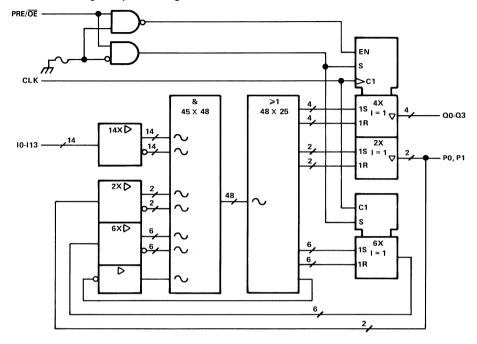

D3085, JANUARY 1988

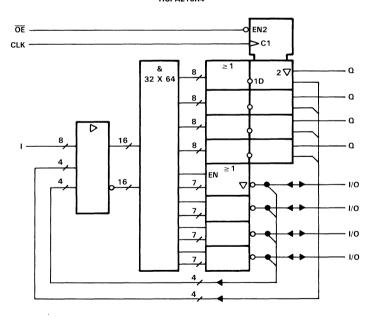

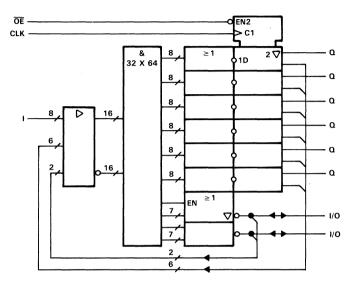

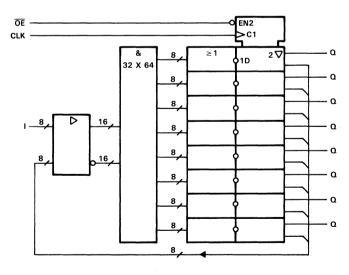

#### TIBPAD16N8-7C HIGH-PERFORMANCE PROGRAMMABLE ADDRESS DECODER

Very-High-Speed Address Decoder (Ideal for Use with High Speed Processors)

- I/O Propagation Delay: 7 ns Max

- Field Programmable on Standard PLD Programmers

- Fully TTL Compatible

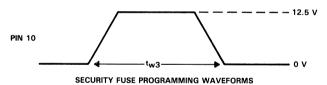

- Security Fuse Prevents Unauthorized Duplication

- Dependable Texas Instruments Quality and Reliability

- Potential Applications

Address Decoders

Code Detectors

Peripheral Selectors

Fault Monitors

Machine State Decoders

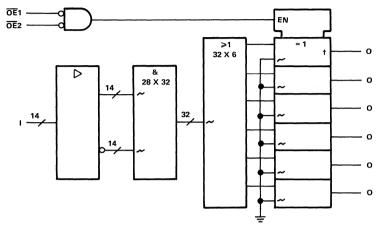

#### description

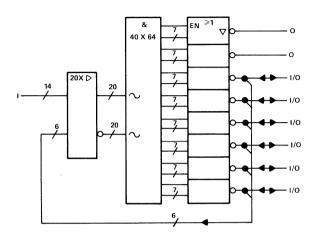

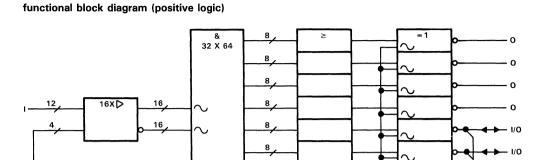

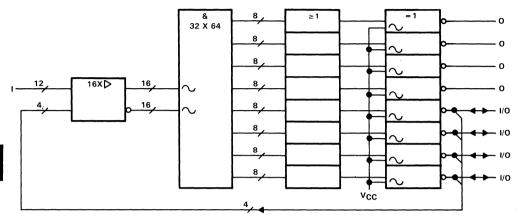

The TIBPAD16N8 is a very-high-speed Programmable Address Decoder featuring 7 ns maximum propagation delay, the highest speed in the TTL programmable logic family. The TIBPAD16N8 utilizes the IMPACT-X™ process and proven titanium-tungsten fuse technology to provide reliable, high performance substitutes for conventional TTL logic.

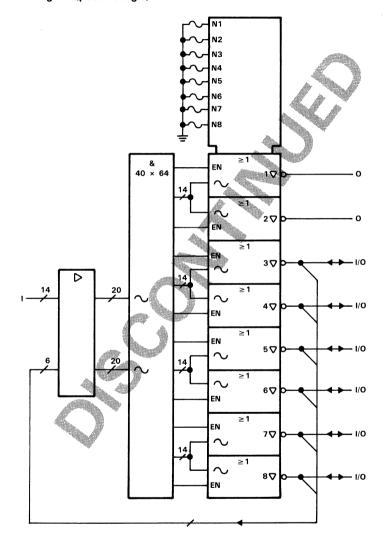

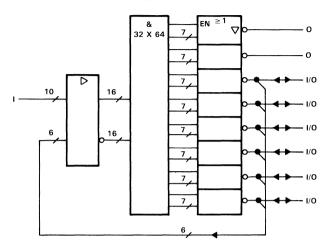

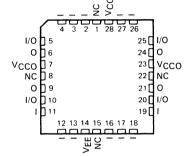

EN PACKAGE

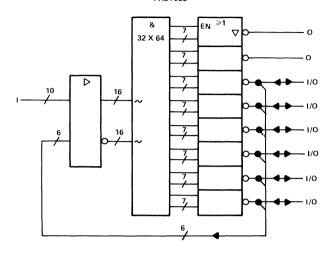

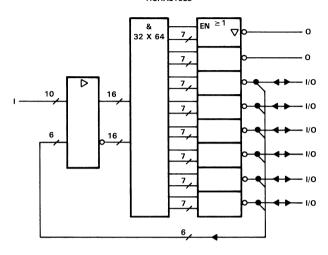

The TIBPAD16N8 contains 10 dedicated inputs and 8 outputs. Each output has two product terms, one of which is used to enable the inverting buffer associated with the respective output. Six of the outputs are I/O ports, the remaining two are dedicated outputs. Each of the six I/O ports can be individually programmed as an input or an output; this allows the device to be used for functions requiring up to 16 inputs and 2 outputs or 10 inputs and 8 outputs.

The TIBPAD16N8 is supplied with all six I/O ports in the input configuration (output buffers in the high-impedance state). If an I/O port is selected to be an output, it must be programmed accordingly. It is recommended that all unused outputs on this device remain in the three-state condition for better noise immunity.

The TIBPAD16N8-7C is characterized for operation from 0 °C to 75 °C.

IMPACT-X is a trademark of Texas Instruments Incorporated.

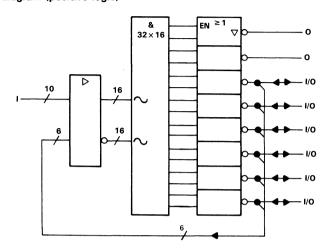

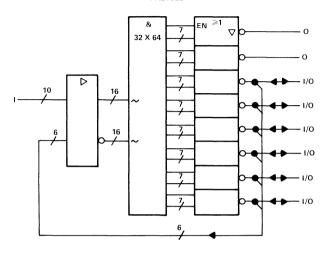

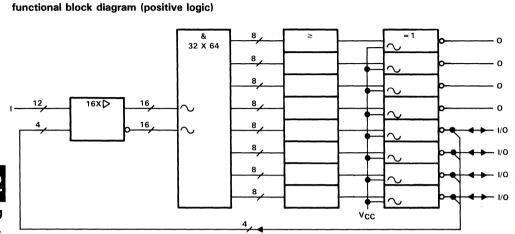

#### functional block diagram (positive logic)

#

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                  | 7 V           |

|---------------------------------------------------|---------------|

| Input voltage (see Note 1)                        | 5.5 V         |

| Voltage applied to a disabled output (see Note 1) | 5.5 V         |

| Operating free-air temperature range              | 0°C to 75°C   |

| Storage temperature range                         | 65°C to 150°C |

NOTE 1: These ratings apply except for programming pins during programming cycle.

#### recommended operating conditions

|     |                                | MIN  | NOM | MAX  | UNIT |

|-----|--------------------------------|------|-----|------|------|

| Vcc | Supply voltage                 | 4.75 | 5   | 5.25 | V    |

| VIH | High-level input voltage       | 2    |     |      | V    |

| VIL | Low-level input voltage        |      |     | 0.8  | ٧    |

| ЮН  | High-level output current      |      |     | -3.2 | mA   |

| lor | Low-level output current       |      |     | 24   | mA   |

| TA  | Operating free-air temperature | 0    |     | 75   | °C   |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER         | TEST CONDITIONS                                             | MIN  | TYP <sup>†</sup> | MAX   | UNIT |

|-------------------|-------------------------------------------------------------|------|------------------|-------|------|

| VIK               | $V_{CC} = 4.75 \text{ V},  I_{I} = -18 \text{ mA}$          |      |                  | -1.5  | V    |

| VoH               | $V_{CC} = 4.75 \text{ V},  I_{OH} = -3.2 \text{ mA}$        | 2.4  | 3                |       | V    |

| V <sub>OL</sub>   | $V_{CC} = 4.75 \text{ V},  I_{OL} = 24 \text{ mA}$          |      | 0.3              | 0.5   | ٧    |

| l <sub>l</sub>    | $V_{CC} = 5.25 \text{ V},  V_{I} = 5.5 \text{ V}$           |      |                  | 0.2   | mA   |

| lozh <sup>‡</sup> | $V_{CC} = 5.25 \text{ V},  V_{O} = 2.7 \text{ V}$           |      |                  | 0.1   | mA   |

| lozL <sup>‡</sup> | $V_{CC} = 5.25 \text{ V},  V_{O} = 0.4 \text{ V}$           |      |                  | -0.1  | mA   |

| ин <sup>‡</sup>   | $V_{CC} = 5.25 \text{ V},  V_{I} = 2.7 \text{ V}$           |      |                  | 25    | μΑ   |

| I <sub>IL</sub> ‡ | $V_{CC} = 5.25 \text{ V},  V_{I} = 0.4 \text{ V}$           |      |                  | -0.25 | mA   |

| IO <sup>§</sup>   | $V_{CC} = 5 \text{ V}, \qquad V_{O} = 0.5 \text{ V}$        | - 30 | -70              | -130  | mA   |

| lcc               | $V_{CC} = 5.25 \text{ V},  V_{I} = 0,  \text{Outputs open}$ |      | 120              | 180   | mA   |

| CL                | V <sub>I</sub> = 2 V                                        |      | 5                |       | pF   |

| C <sub>o</sub>    | $V_0 = 2 V$                                                 |      | 6                |       | pF   |

$<sup>^{\</sup>dagger}$  All typical values are at VCC = 5 V, TA = 25 °C.

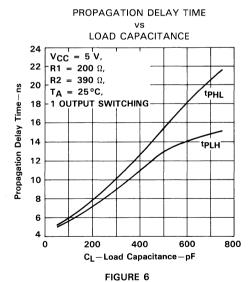

### switching characteristics with two outputs switching (typical PAD mode) over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER        | FROM   | то                            | TEST<br>CONDITIONS | MIN | TYP <sup>†</sup> | MAX | UNIT |

|------------------|--------|-------------------------------|--------------------|-----|------------------|-----|------|

| <sup>t</sup> pd  | I, I/O | O, I/O<br>2 outputs switching | R1 = 200 Ω,        | 2   | 5                | 7   | ns   |

| t <sub>en</sub>  | 1, 1/0 | 0, 1/0                        | $R2 = 390 \Omega$  | 3   | 8                | 10  | ns   |

| <sup>t</sup> dis | I, I/O | 0, 1/0                        |                    | 3   | 8                | 10  | ns   |

<sup>&</sup>lt;sup>†</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C

<sup>‡</sup>I/O leakage is the worst case of IOZL and IIL or IOZH and IIH.

<sup>§</sup> This parameter approximates I<sub>OS</sub>. The condition V<sub>O</sub> = 0.5 V takes tester noise into account. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

- 3.5 V

-- 0.3 V

≈ 3.3 V

tdis

#### TIBPAD16N8-7C HIGH-PERFORMANCE PROGRAMMABLE ADDRESS DECODER

#### programming information

Texas Instruments Programmable Logic Devices can be programmed using widely available software and inexpensive device programmers.

Complete programming specifications, algorithms, and the latest information on hardware, software, and firmware are available upon request. Information on programmers capable of programming Texas Instruments Programmable Logic is also available, upon request, from the nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at (214) 997-5762.

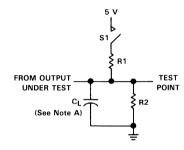

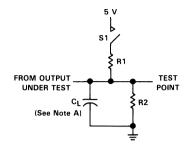

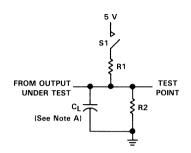

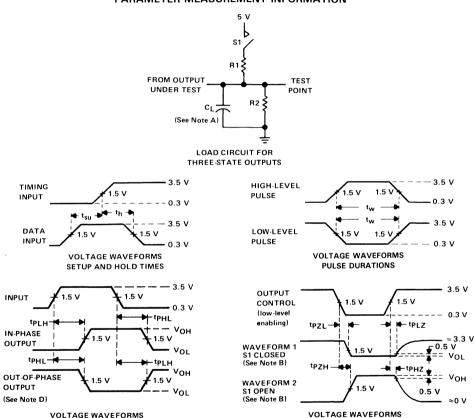

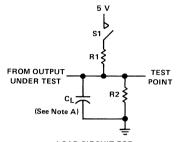

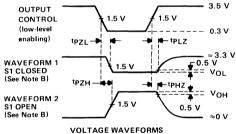

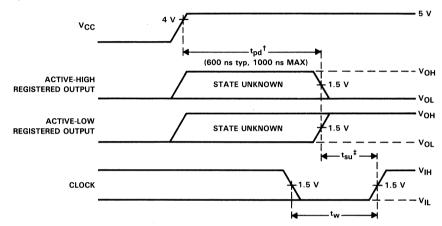

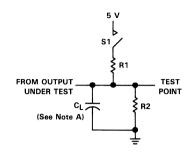

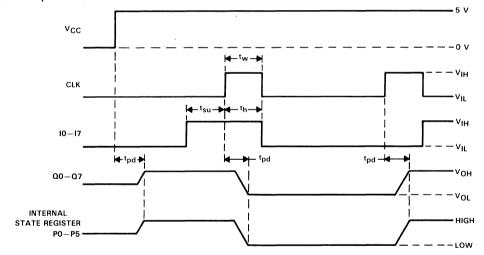

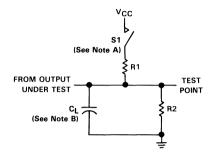

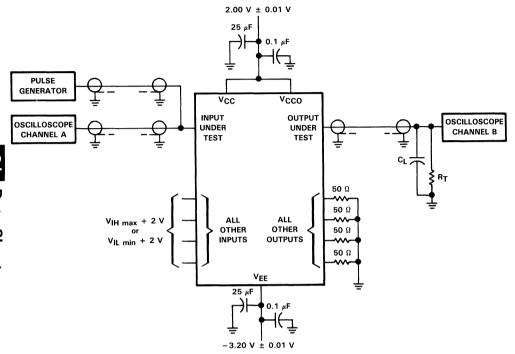

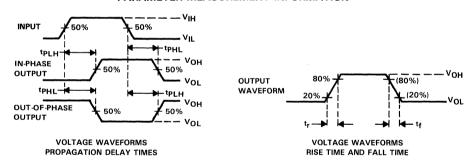

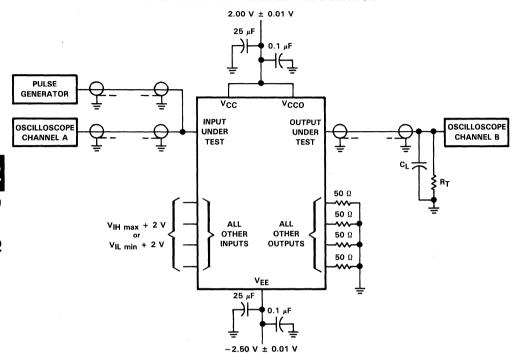

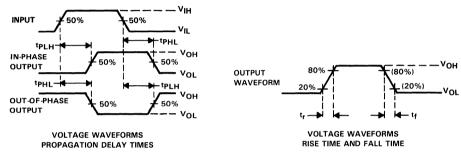

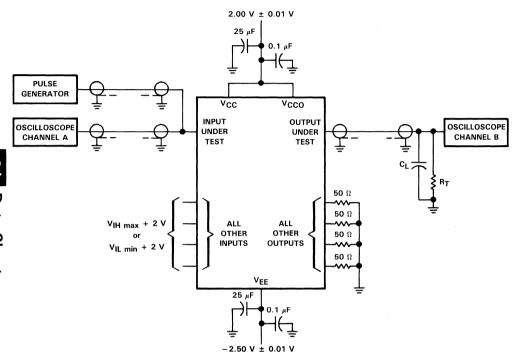

#### PARAMETER MEASUREMENT INFORMATION

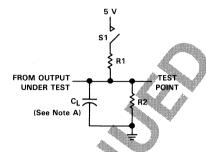

#### LOAD CIRCUIT FOR THREE-STATE OUTPUTS

OUTPUT

CONTROL

(low-level

enabling)

WAVEFORM 1 V<sub>OL</sub> + 0.5 V 1.5 V S1 CLOSED  $v_{OL}$ (See Note B) tdis ۷он WAVEFORM 2 VOH−0.5 V S1 OPEN (See Note B) ≈0 V

#### VOLTAGE WAVEFORMS PROPAGATION DELAY TIMES

#### VOLTAGE WAVEFORMS **ENABLE AND DISABLE TIMES. THREE-STATE OUTPUTS**

- NOTES: A. C<sub>I</sub> includes probe and jig capacitance and is 50 pF for t<sub>pd</sub> and t<sub>en</sub>, 5 pF for t<sub>dis</sub>.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics: PRR  $\leq$  1 MHz,  $t_r = t_f = 2$  ns, duty cycle = 50%

- D. When measuring propagation delay times of 3-state outputs, switch S1 is closed.

#### FIGURE 1

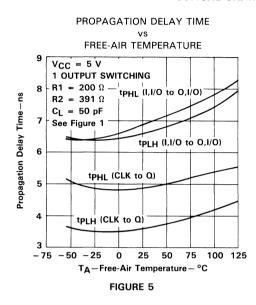

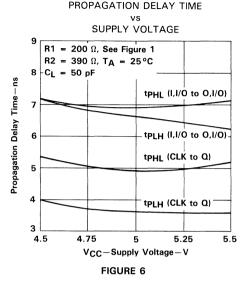

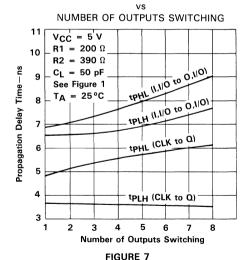

#### WORST CASE MULTIPLE OUTPUT SWITCHING CHARACTERISTICS

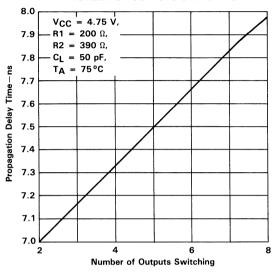

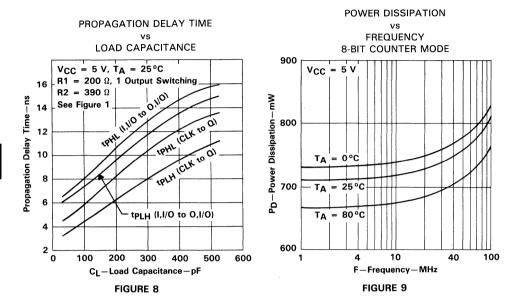

### WORST CASE PROPAGATION DELAY TIME vs

#### NUMBER OF OUTPUTS SWITCHING

FIGURE 2

#### TIBPAD16N8-7C HIGH-PERFORMANCE PROGRAMMABLE ADDRESS DECODER

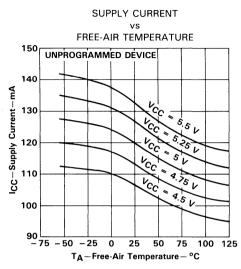

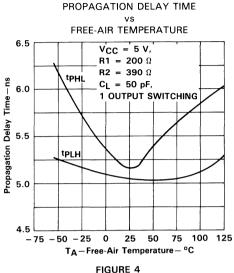

#### TYPICAL CHARACTERISTICS

FIGURE 3

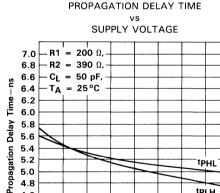

5.2

5.0

4.8

4.6 4.4

4.2 4.0

4.5

VCC-Supply Voltage-V FIGURE 5

4.75

**tPHL**

tPLH.

5.25

5.5

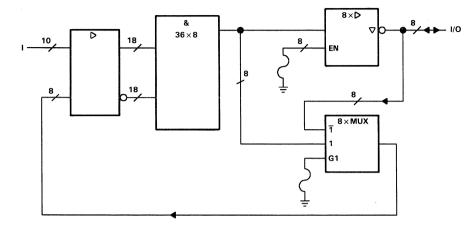

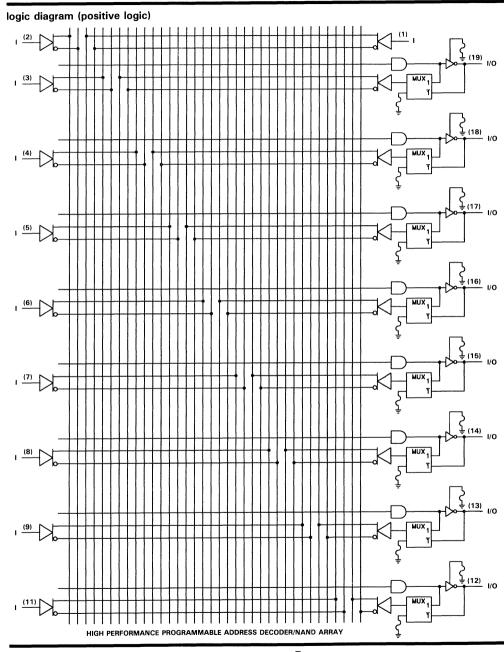

#### TIBPAD18N8-6C HIGH-PERFORMANCE PROGRAMMABLE ADDRESS DECODER/NAND ARRAY

D3086, DECEMBER 1987

- Very High Speed Address Decoder (Ideal for Use with High Speed Processors)

- I/O Propagation Delay: 6 ns Max

- Suitable for High Speed NAND-NAND Logic Implementation

- Field Programmable on Standard PLD **Programmers**

- Fully TTL Compatible

- Security Fuse Prevents Unauthorized Duplication

- Dependable Texas Instruments Quality and Reliability

- Potential Applications Address Decoders Random Logic (NAND-NAND) Code Detectors **Peripheral Selectors Fault Monitors**

Machine State Decoders

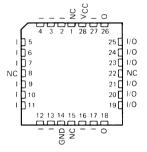

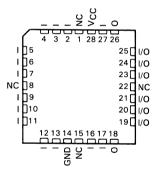

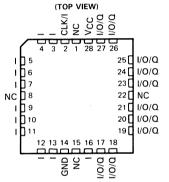

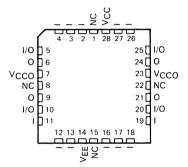

FN PACKAGE (TOP VIEW)

#### description

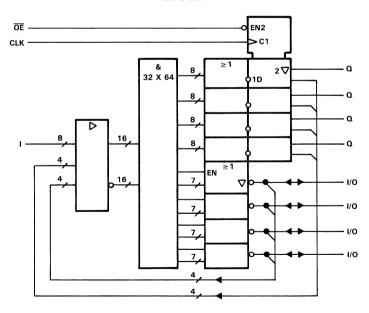

The TIBPAD18N8-6C is a very-high-speed Programmable Address Decoder featuring 6-ns maximum propagation delay, the highest speed in the TTL programmable logic family. The TIBPAD18N8 uses the IMPACT-X™ process and proven titanium-tungsten fuse technology to provide reliable, high-performance substitutes for conventional TTL logic.

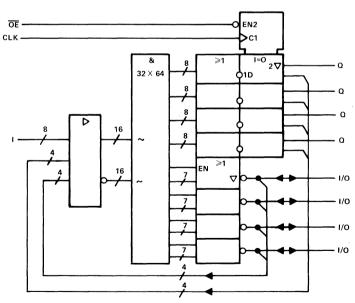

The TIBPAD18N8-6C contains 10 dedicated inputs and 8 product terms, each followed by an inverting buffer leading to an I/O port. Each of the eight I/O ports can be individually programmed as an input or an output, depending on the state of the fuse controlling the output buffer, as indicated by Table 1. This allows the device to be used for functions ranging from 17 inputs and a single output to 10 inputs and 8 outputs.

A high-speed feedback path, which does not go through the output buffer, is provided to offer higher performance operation in designs where feedback is required. The architectural fuse on the I/O multiplexer is used for the selection of this path (see Table 2). This makes the TIBPAD18N8-6C ideal for the implementation of a very fast NAND-NAND logic.

The TIBPAD18N8 is supplied with all eight I/O ports in the input configuration (output buffers in the highimpedance state). If an I/O port is selected to be an output, it must be programmed accordingly. It is recommended that all unused outputs on this device remain in the high-impedance state for better noise immunity.

The TIBPAD18N8-6C is characterized for operation from 0°C to 75°C.

IMPACT-X is a trademark of Texas Instruments Incorporated.

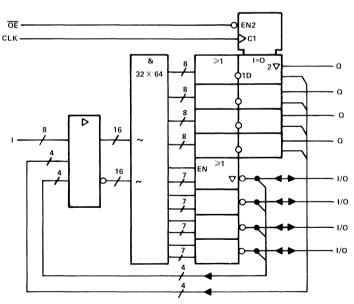

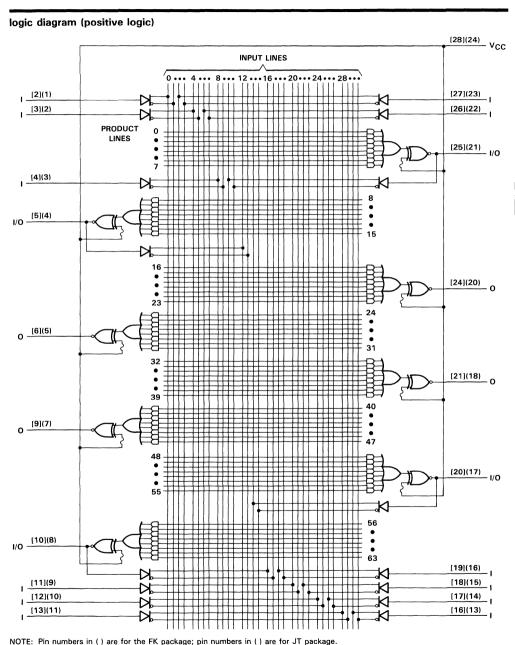

#### functional block diagram (positive logic)

**Table 1. Output Buffer Programming**

| ARCHITECTURAL<br>FUSE | OPERATION      |

|-----------------------|----------------|

|                       | Input          |

| Intact                | (Output Buffer |

|                       | in Hi-Z State) |

| Blown                 | Output         |

Table 2. I/O Multiplexer Programming

| ARCHITECTURAL<br>FUSE | OPERATION    |

|-----------------------|--------------|

| Intact                | I/O Feedback |

| Blown                 | High-Speed   |

| ΠWUI                  | Feedback     |

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                  | 7 V   |

|---------------------------------------------------|-------|

| Input voltage (see Note 1) 5                      | 5.5 V |

| Voltage applied to a disabled output (see Note 1) | 5.5 V |

| Operating free-air temperature range              | 75°C  |

| Storage temperature range                         | 50°C  |

NOTE 1: These ratings apply except for programming pins during a programming cycle.

#### recommended operating conditions

|     |                                       | MIN  | NOM | MAX  | UNIT |

|-----|---------------------------------------|------|-----|------|------|

| VCC | Supply voltage                        | 4.75 | 5   | 5.25 | V    |

| VIH | High-level input voltage (see Note 2) | 2    |     |      | ٧    |

| VIL | Low-level input voltage (see Note 2)  |      |     | 0.8  | V    |

| Іон | High-level output current             |      |     | -3.2 | mA   |

| lOL | Low-level output current              |      |     | 24   | mA   |

| TA  | Operating free-air temperature        | 0    |     | 75   | °C   |

NOTE 2: These are absolute voltage levels with respect to the ground pin of the device and include all overshoots due to system and/or tester noise. Testing these parameters should not be attempted without suitable equipment.

### electrical characteristics over recommended operating free-air temperature range (unless otherwise

| PARAMETER | TEST CONDITIONS                                    | MIN | TYP <sup>†</sup> | MAX   | UNIT |

|-----------|----------------------------------------------------|-----|------------------|-------|------|

| VIK       | $V_{CC} = 4.75 \text{ V},  I_{I} = -18 \text{ mA}$ |     |                  | -1.2  | ٧    |

| Voн       | V <sub>CC</sub> = 4.75 V, I <sub>OH</sub> = MAX    | 2.4 | 3                |       | ٧    |

| VOL       | $V_{CC} = 4.75 \text{ V},  I_{OL} = \text{MAX}$    |     | 0.37             | 0.5   | ٧    |

| lozh      | $V_{CC} = 5.25 \text{ V},  V_{O} = 2.7 \text{ V}$  |     |                  | 20    | μΑ   |

| IOZL      | $V_{CC} = 5.25 \text{ V},  V_{O} = 0.4 \text{ V}$  |     |                  | - 20  | μΑ   |

| lį        | $V_{CC} = 5.25 \text{ V},  V_{I} = 5.5 \text{ V}$  |     |                  | 0.2   | μΑ   |

| ήн        | $V_{CC} = 5.25 \text{ V},  V_{I} = 2.7 \text{ V}$  |     |                  | 20    | μΑ   |

| կլ        | $V_{CC} = 5.25 \text{ V},  V_{I} = 0.4 \text{ V}$  |     |                  | -0.25 | mA   |

| los       | $V_{CC} = 5.25 \text{ V},  V_{O} = 0 \text{ V}$    |     |                  |       | mA   |

| Icc       | $V_{CC} = 5.25 \text{ V},  V_{I} = 4.5 \text{ V}$  |     | 140              | 180   | mA   |

#### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER       | FROM | то                                                                                             | TEST<br>CONDITIONS  | MIN | TYP <sup>†</sup> | MAX | UNIT |

|-----------------|------|------------------------------------------------------------------------------------------------|---------------------|-----|------------------|-----|------|

|                 |      | I/O (no feedback)                                                                              |                     |     | 4                | 6   | ns   |

| <sup>†</sup> pd | 1    | I/O (with 1 feedback path  — I/O MUX fuse blown)                                               | $R1 = 200 \Omega$ , |     | 8                | 10  | ns   |

|                 | I    | I I/O (with 2 feedback paths $R2 = 390 \Omega$ , $-$ I/O MUX fuse blown) $C_L = 50 \text{ pF}$ |                     |     | 12               | 14  | ns   |

|                 |      | I/O (with 3 feedback paths  — I/O MUX fuse blown)                                              | -                   |     | 16               | 18  | ns   |

$<sup>^{\</sup>dagger}$ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_{A} = 25 \, ^{\circ}\text{C}$ .

### HIGH-PERFORMANCE PROGRAMMABLE ADDRESS DECODER/NAND ARRAY

#### PARAMETER MEASUREMENT INFORMATION

#### LOAD CIRCUIT FOR THREE-STATE OUTPUTS

#### **VOLTAGE WAVEFORMS** PROPAGATION DELAY TIMES

**VOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES, THREE-STATE OUTPUTS**

- NOTES: A.  $C_L$  includes probe and jig capacitance and is 50 pF for  $t_{pd}$  and  $t_{en}$ , 5 pF for  $t_{dis}$ .

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics: PRR  $\leq$  1 MHz,  $t_r = t_f = 2$  ns, duty cycle = 50%

- D. When measuring propagation delay times of 3-state outputs, switch S1 is closed.

#### FIGURE 1

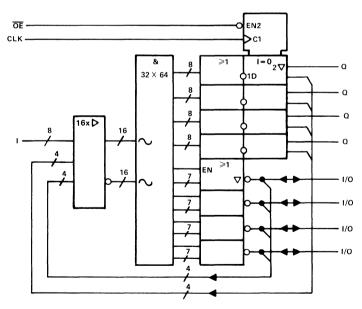

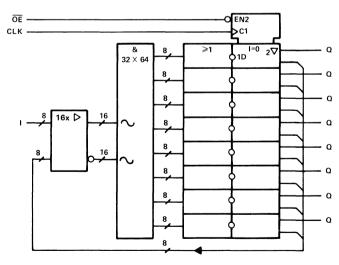

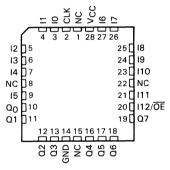

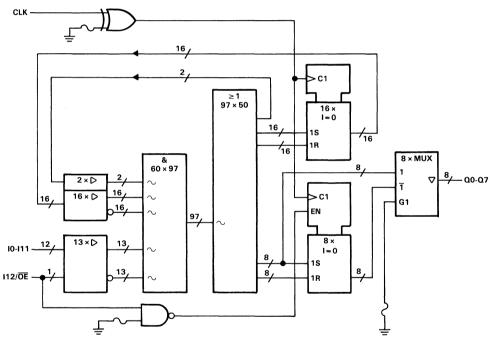

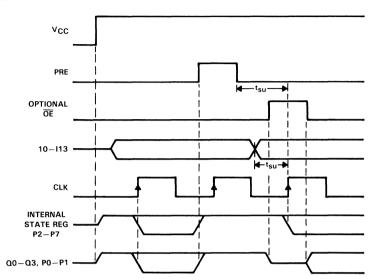

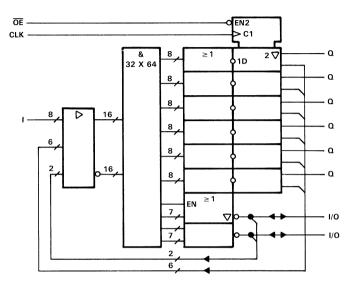

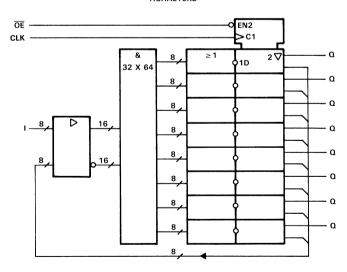

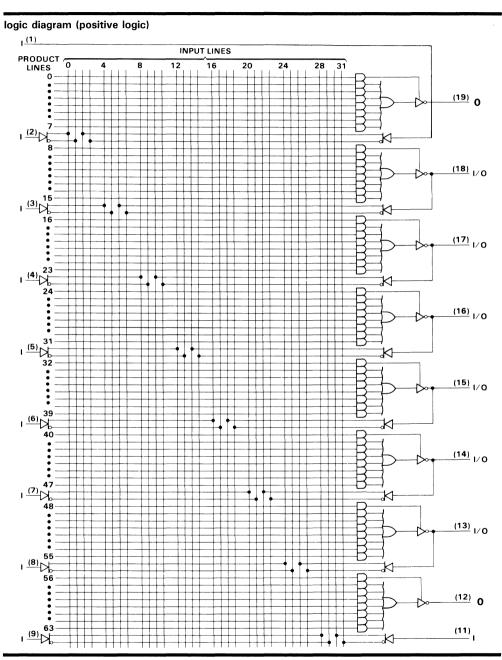

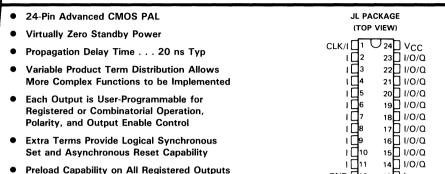

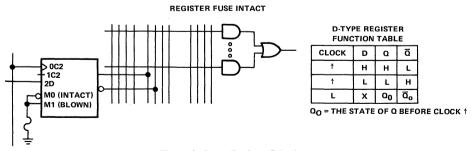

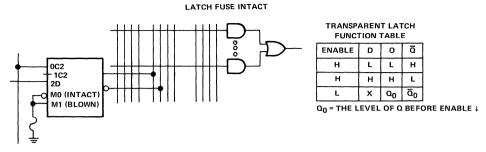

## TIBPAL16L8-12M, TIBPAL16R4-12M, TIBPAL16R6-12M, TIBPAL16R8-12M TIBPAL16L8-10C, TIBPAL16R4-10C, TIBPAL16R6-10C, TIBPAL16R8-10C HIGH-PERFORMANCE IMPACT ™PAL® CIRCUITS

D3023, MAY 1987-JANUARY 1988

High-Performance Operation:

fmax (w/o feedback)

TIBPAL16R'-10C Series . . . 62.5 MHz TIBPAL16R'-12M Series . . . 56 MHz

fmax (with feedback)

TIBPAL16R'-10C Series . . . 55.5 MHz

TIBPAL16R'-12M Series . . . 48 MHz

Propagation Delay

TIBPAL16L-10C . . . 10 ns Max TIBPAL16L-12M . . . 12 ns Max

- Functionally Equivalent, but Faster than Existing 20-Pin PALs

- Preload Capability on Output Registers Simplifies Testing

- Power-Up Clear on Registered Devices (All Register Outputs are Set Low, but Voltage Levels at the Output Pins Remain High)

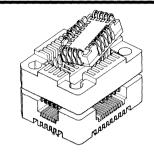

- Package Options Include Both Plastic and Ceramic Chip Carriers in Addition to Plastic and Ceramic DIPs

- Security Fuse Prevents Duplication

- Dependable Texas Instruments Quality and Reliability

| DEVICE  | INPUTS | 3-STATE<br>0 OUTPUTS | REGISTERED<br>Q OUTPUTS | I/O<br>PORTS |

|---------|--------|----------------------|-------------------------|--------------|

| PAL16L8 | 10     | 2                    | 0                       | 6            |

| PAL16R4 | 8      | 0                    | 4 (3-state)             | 4            |

| PAL16R6 | 8      | 0                    | 6 (3-state)             | 2            |

| PAL16R8 | 8      | 0                    | 8 (3-state)             | 0            |

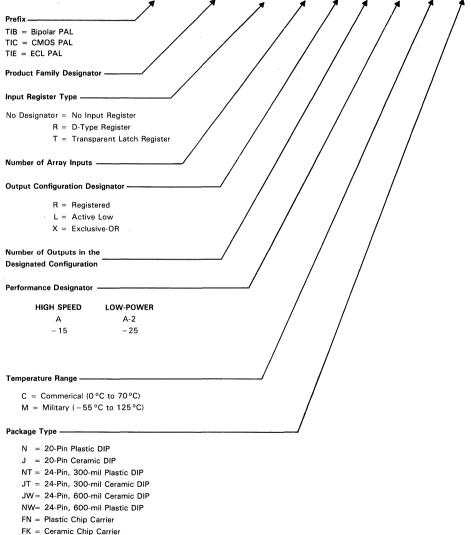

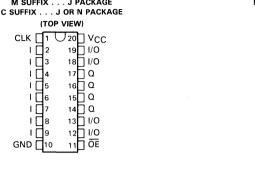

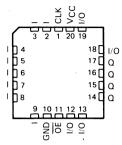

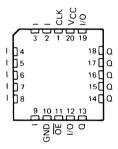

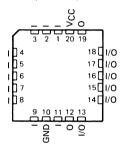

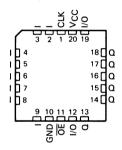

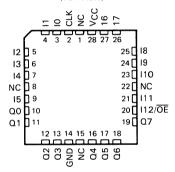

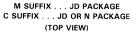

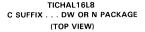

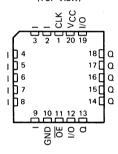

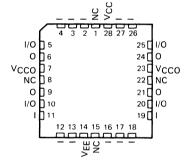

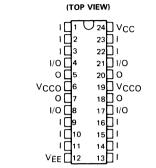

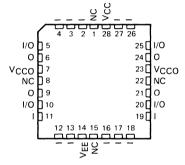

TIBPAL16L8'

M SUFFIX . . . J PACKAGE

C SUFFIX . . . J OR N PACKAGE

(TOP VIEW)

TIBPAL16L8'

M SUFFIX . . . FK PACKAGE

C SUFFIX . . . FN PACKAGE

(TOP VIEW)

Pin assignments in operating mode

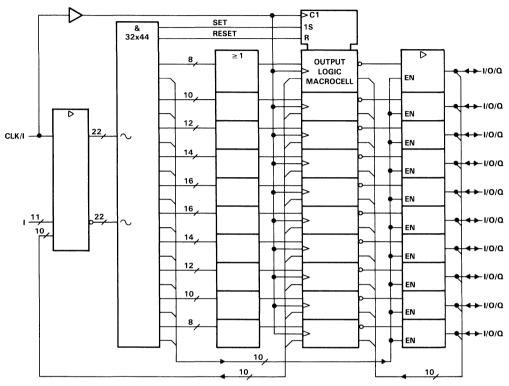

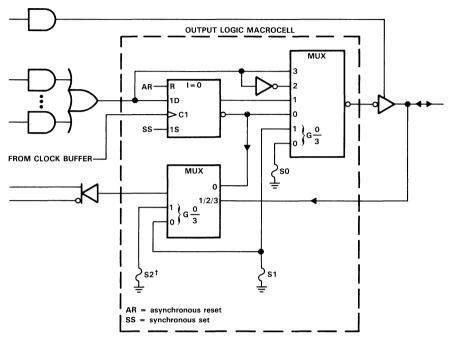

#### description

These programmable array logic devices feature high speed and functional equivalency when compared with currently available devices. These IMPACT™ circuits combine the latest Advanced Low-Power Schottky† technology with proven titanium-tungsten fuses to provide reliable, high-performance substitutes for conventional TTL logic. Their easy programmability allows for quick design of custom-functions and typically results in a more compact circuit board. In addition, chip carriers are available for further reduction in board space.

All of the register outputs are set to a low level during power-up. Extra circuitry has been provided to allow loading of each register asynchronously to either a high or low state. This feature simplifies testing because the registers can be set to an initial state prior to executing the test sequence.

The TIBPAL16' M series is characterized for operation over the full military temperature range of -55 °C to 125 °C. The TIBPAL16' C series is characterized for operation from 0 °C to 75 °C.

IMPACT™ is a trademark of Texas Instruments Incorporated. PAL® is a registered trademark of Monolithic Memories Inc.

<sup>†</sup>Integrated Schottky-Barrier diode-clamped transistor is patented by Texas Instruments, U.S. Patent Number 3,463,975.

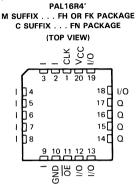

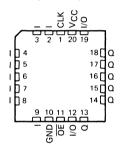

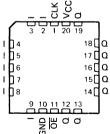

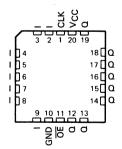

## TIBPAL16R4' M SUFFIX . . . J PACKAGE C SUFFIX . . . J OR N PACKAGE (TOP VIEW)

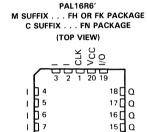

## TIBPAL16R6' M SUFFIX . . . J PACKAGE C SUFFIX . . . J OR N PACKAGE (TOP VIEW)

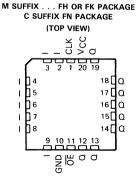

## TIBPAL16R8' M SUFFIX . . . J PACKAGE C SUFFIX . . . J OR N PACKAGE (TOP VIEW)

Pin assignments in operating mode

## TIBPAL16R4' M SUFFIX . . . FK PACKAGE C SUFFIX . . . FN PACKAGE (TOP VIEW)

## TIBPAL16R6' M SUFFIX . . . FK PACKAGE C SUFFIX . . . FN PACKAGE (TOP VIEW)

## TIBPAL16R8' M SUFFIX . . . FK PACKAGE C SUFFIX . . . FN PACKAGE (TOP VIEW)

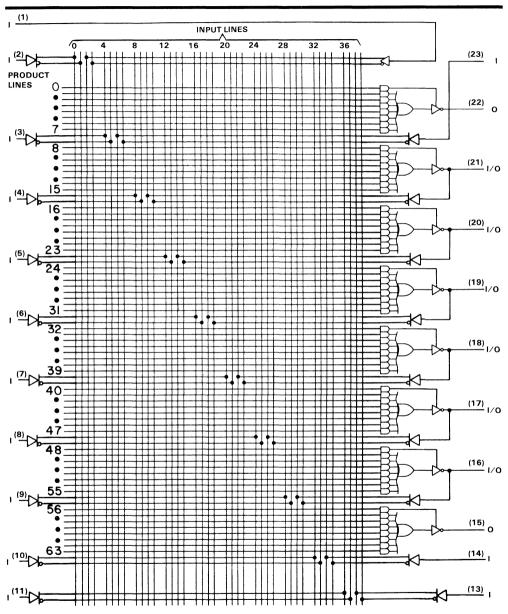

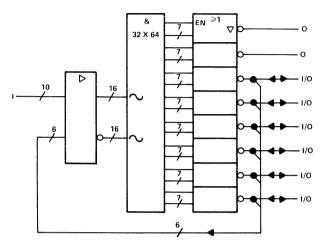

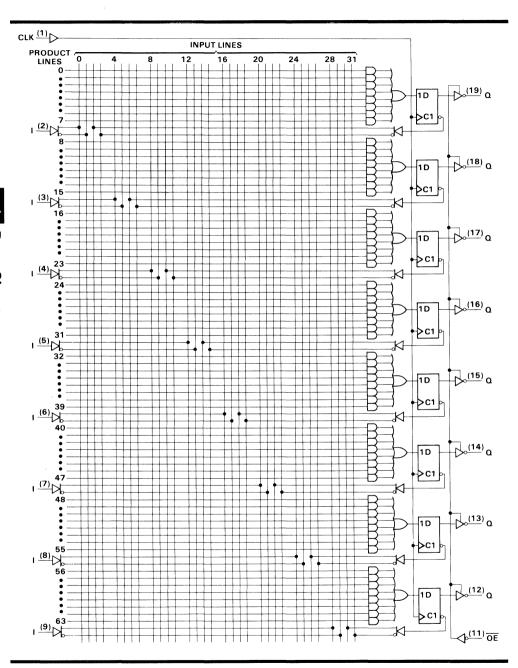

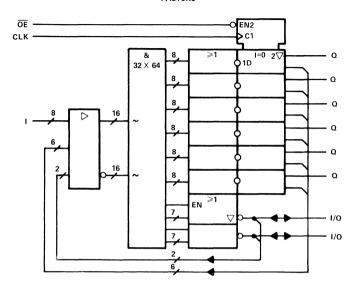

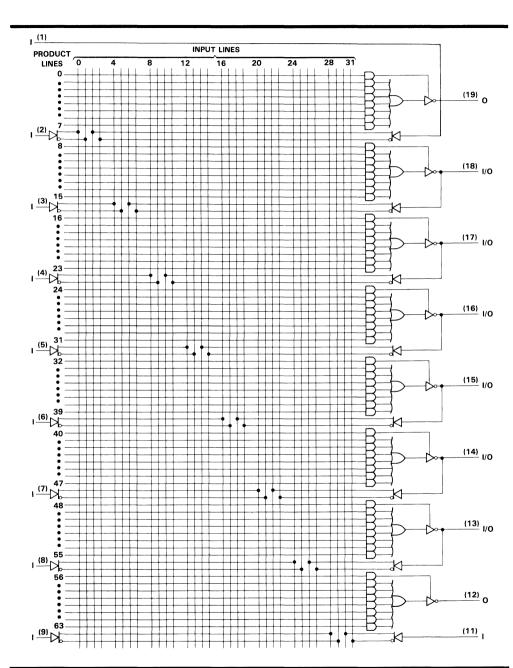

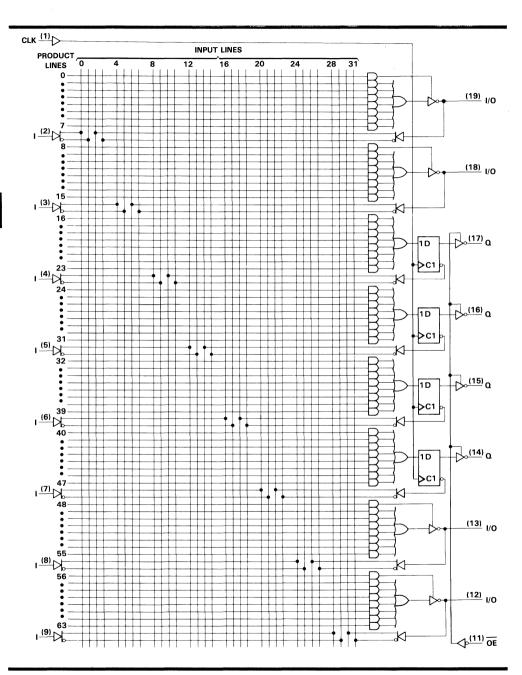

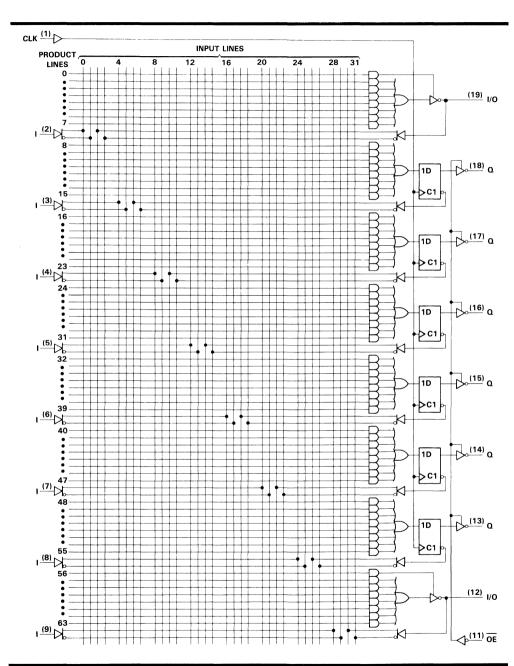

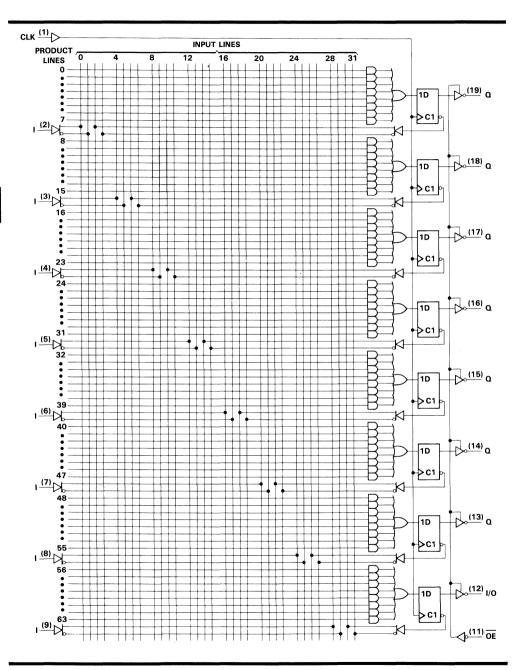

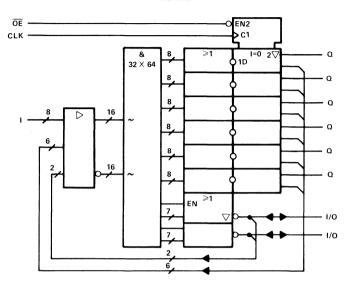

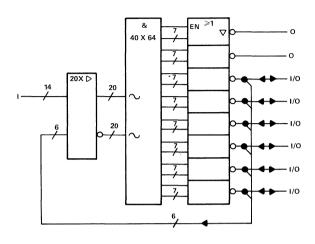

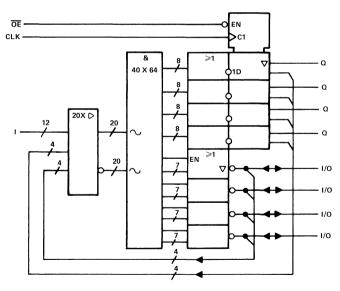

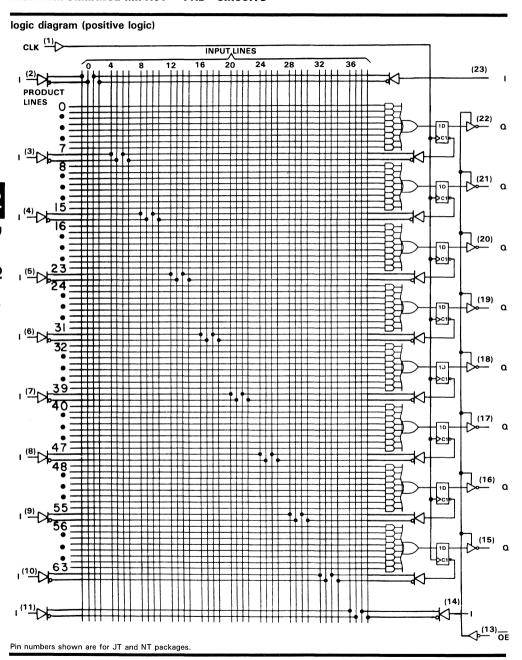

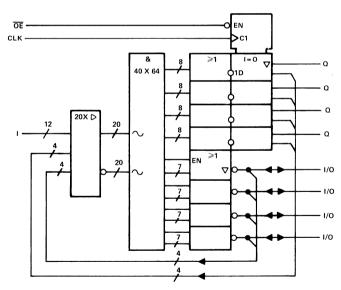

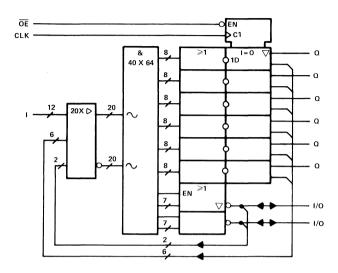

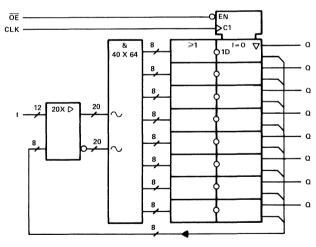

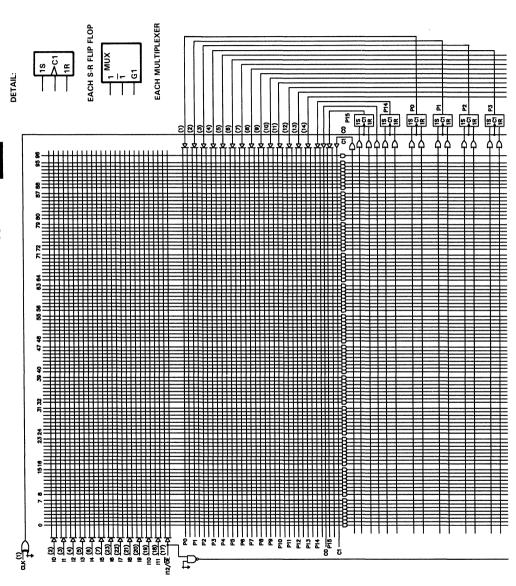

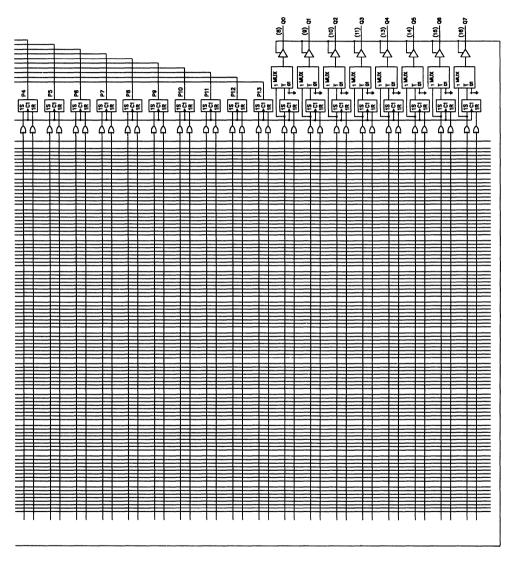

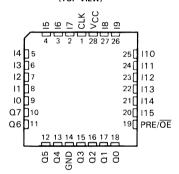

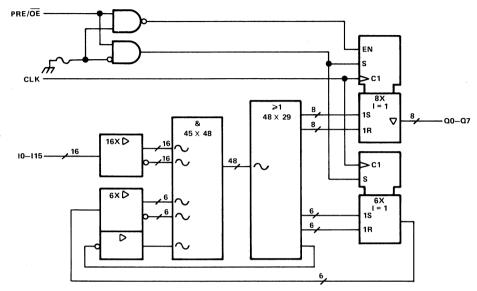

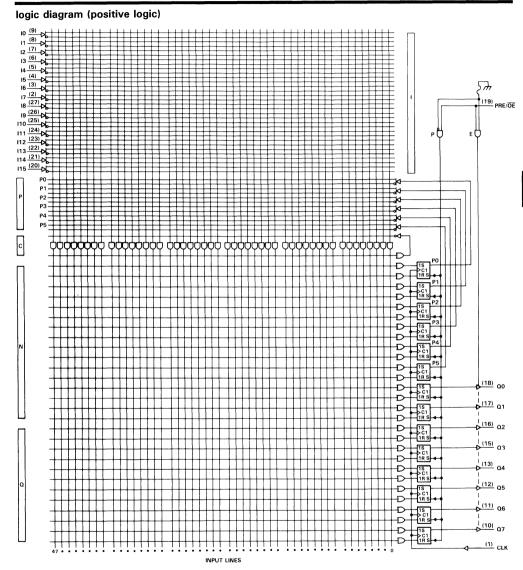

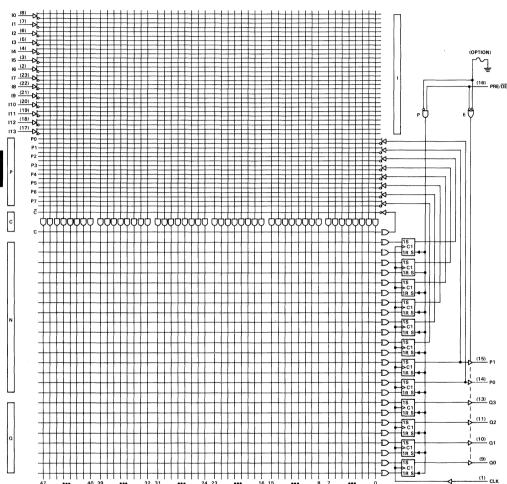

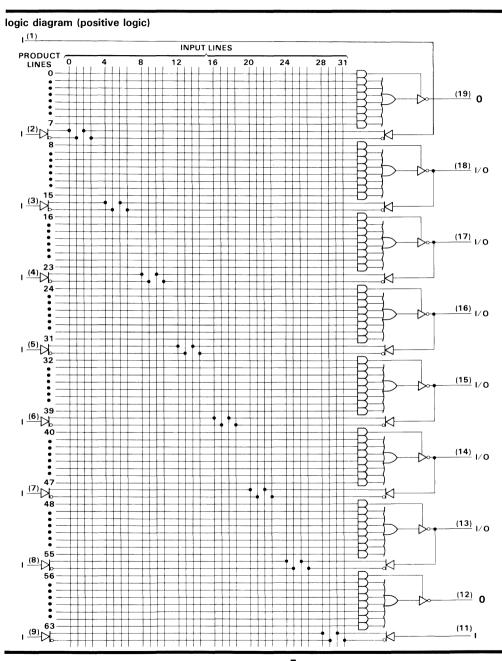

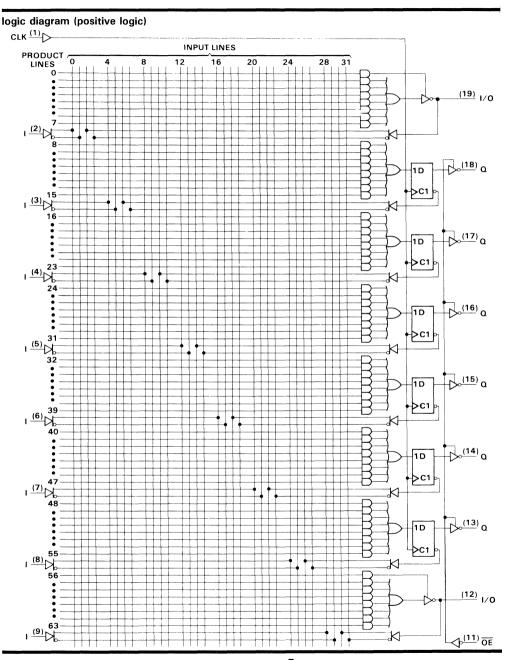

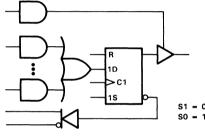

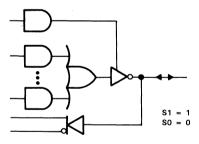

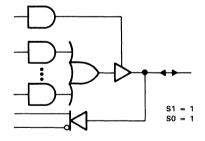

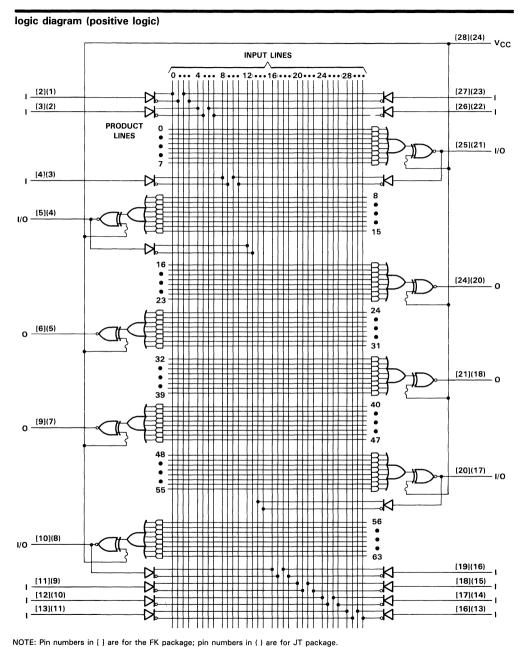

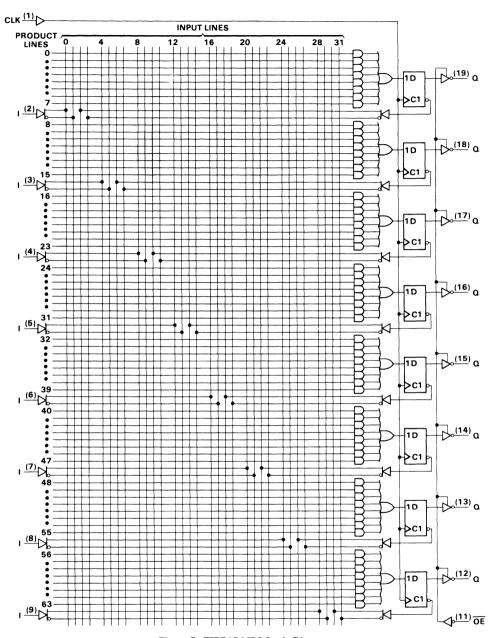

#### functional block diagrams (positive logic)

'PAL16L8

'PAL16R4

→ denotes fused inputs

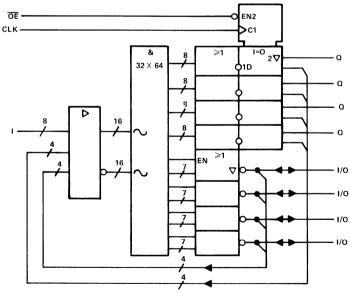

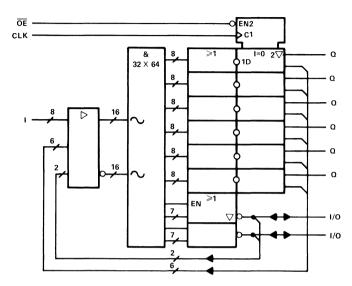

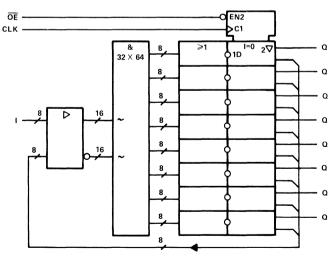

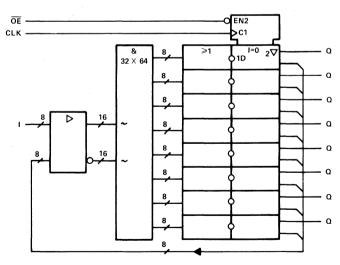

#### functional block diagrams (positive logic)

'PAL16R8

∼ denotes fused inputs

#### TIBPAL16L8-12M, TIBPAL16R4-12M, TIBPAL16R6-12M, TIBPAL16R8-12M TIBPAL16L8-10C, TIBPAL16R4-10C, TIBPAL16R6-10C, TIBPAL16R8-10C HIGH-PERFORMANCE IMPACT ™PAL® CIRCUITS

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                  | . 7 | ν   |

|---------------------------------------------------|-----|-----|

| Input voltage (see Note 1)                        | 5.5 | V   |

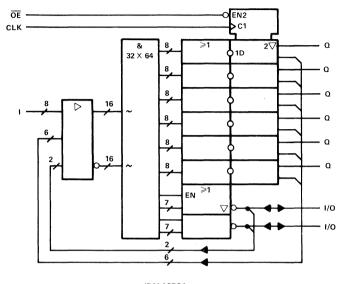

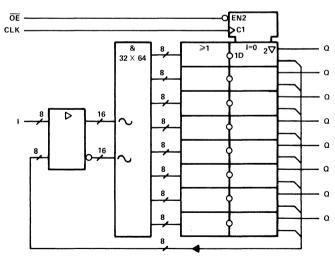

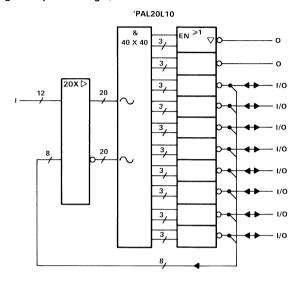

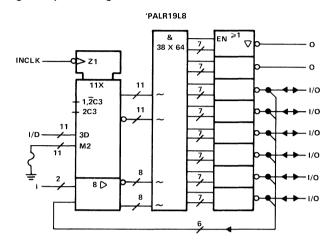

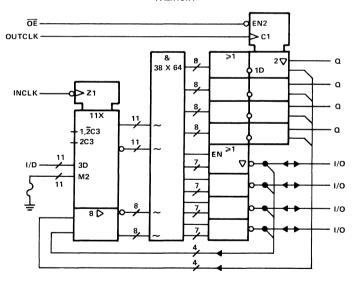

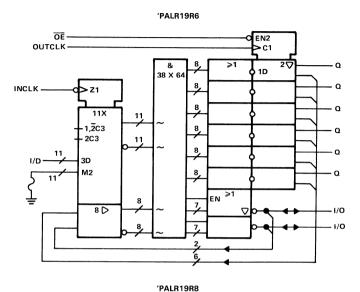

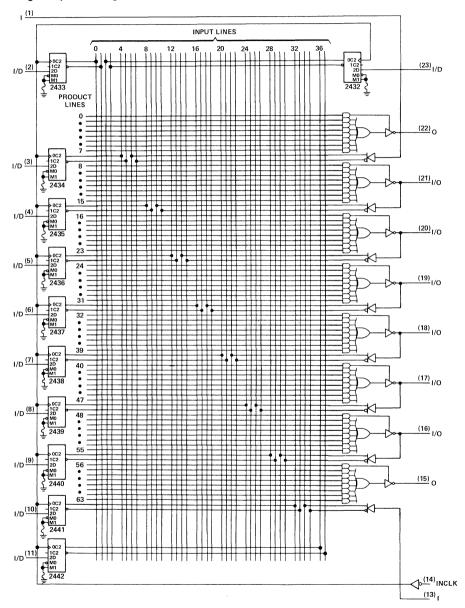

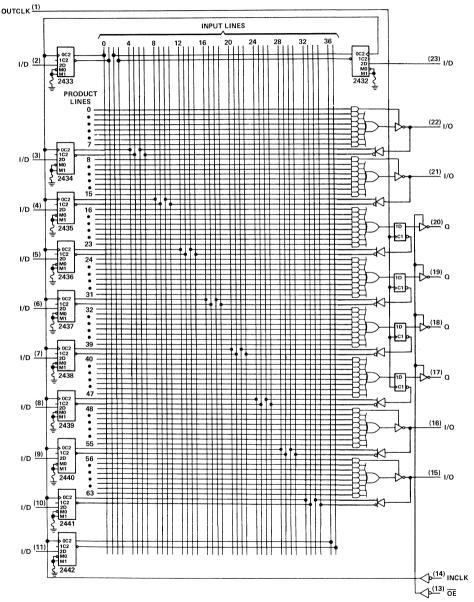

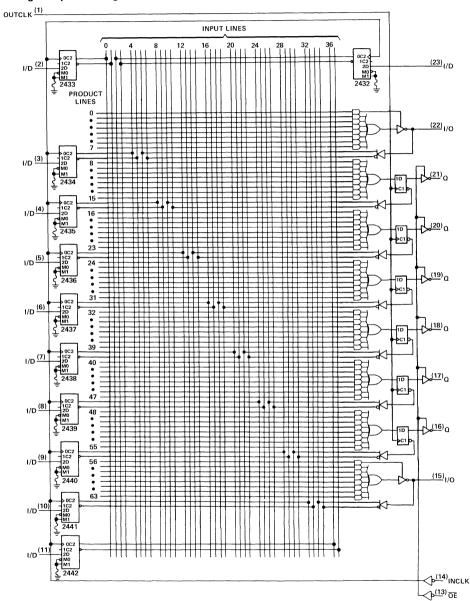

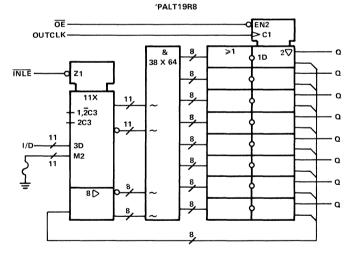

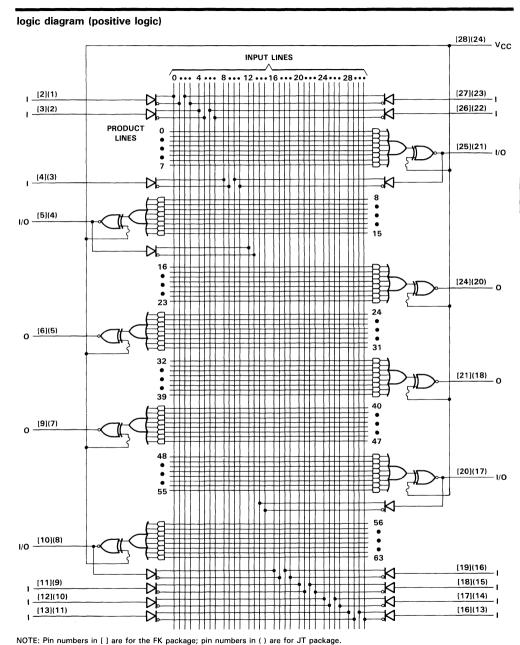

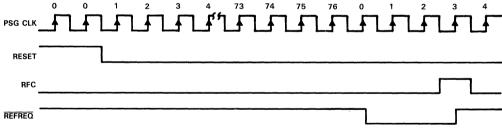

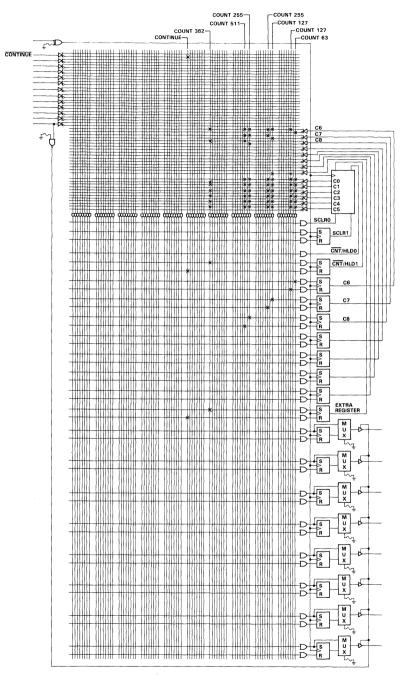

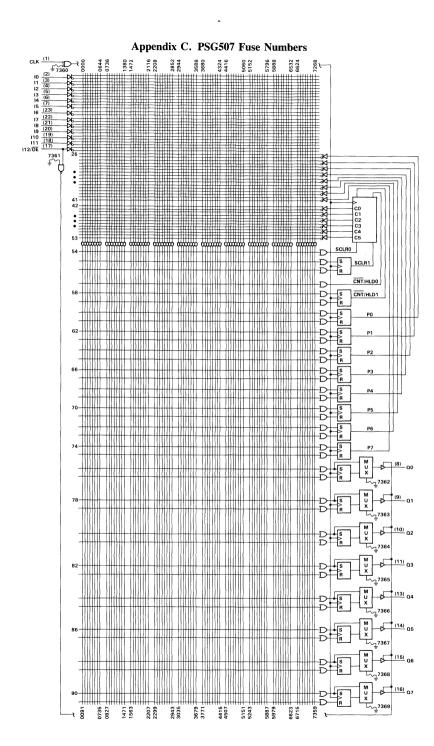

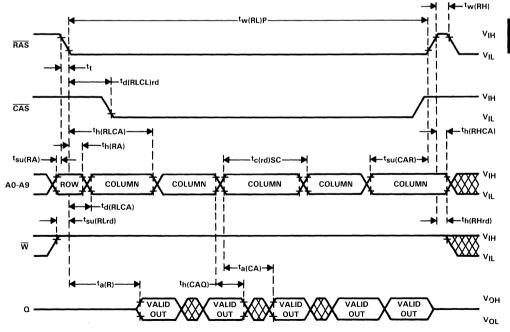

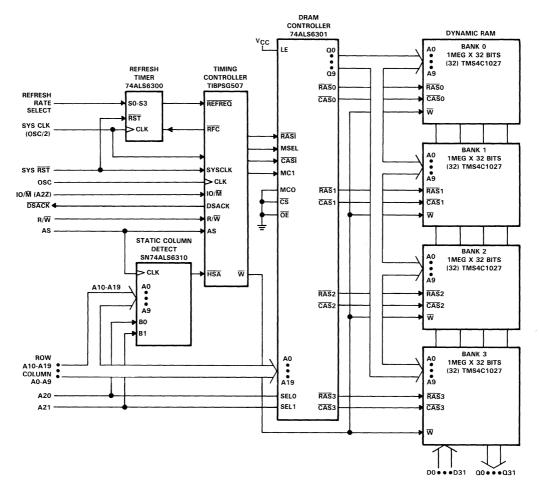

| Voltage applied to a disabled output (see Note 1) | 5.5 | V   |