SCAMP II PC/AT-COMPATIBLE SYSTEM CONTROLLER

VL82C315A DATA MANUAL

Portable Systems Division June 1992

ADVANCE INFORMATION

1992

# VL82C315A DATA MANUAL

Portable Systems Division June 1992

ADVANCE INFORMATION

The information contained in this document has been carefully checked and is believed to be reliable. However, VLSI Technology, Inc., (VLSI) makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon, it. VLSI does not guarantee that the use of any information contained herein will not infringe upon the patent, trademark, copyright, mask work right or other rights of third parties, and no patent or other license is implied hereby.

This document does not in any way extend VLSI's warranty on any product beyond that set forth in its standard terms and conditions of sale. VLSI Technology, Inc., reserves the right to make changes in the products or specifications, or both, presented in this publication at any time and without notice.

#### LIFE SUPPORT APPLICATIONS

VLSI Technology, Inc., products are not intended for use as critical components in life support appliances, devices, or systems in which the failure of a VLSI product to perform could be expected to result in personal injury. © 1992 VLSI Technology, Inc. Printed in U.S.A.

This manual provides the reader with a preliminary technical reference for VLSI Technology, Inc.'s VL82C315A SCAMP System Controller device for use in PC/AT-compatible applications. If you should require performance or functions not included in this manual, please contact your local VLSI Technology Design Center or Sales Office. The addresses are listed on the last page of this manual.

Since computer technology is extremely fast-moving, it is planned that VLSI's Personal Computer Products Division will revise, update, and publish this manual often. This will allow timely publication of data on new products, as well as improvements on existing ones. The most current information may also be obtained from your local VLSI Technology, Inc. Sales Office, Representative, or the Personal Computer Division in Tempe, Arizona.

Readers are encouraged to send their comments, corrections, or suggestions to:

Director, Marketing Communications VLSI Technology, Inc. 8375 South River Parkway Tempe, AZ 85284

## Page Number

| Item                                                          | Numb |

|---------------------------------------------------------------|------|

| FEATURES                                                      |      |

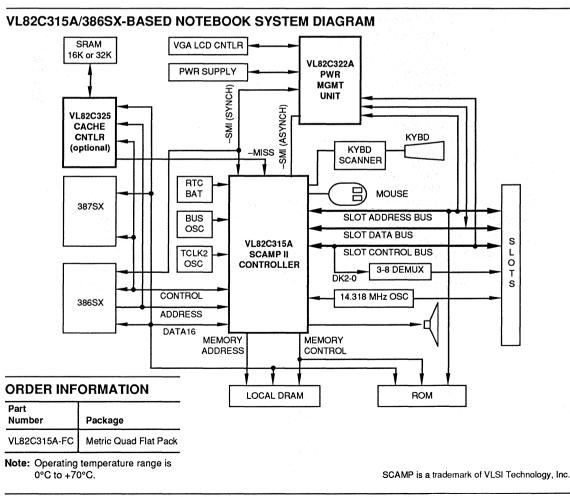

| VL82C315A/386SX-BASED NOTEBOOK SYSTEM DIAGRAM                 | 1    |

| ORDER INFORMATION                                             | 1    |

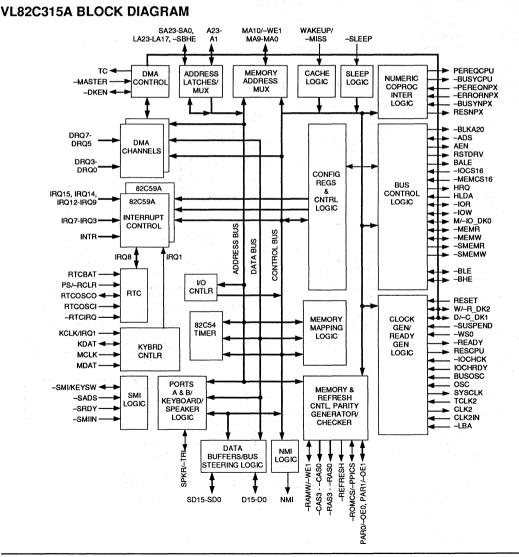

| VL82C315A BLOCK DIAGRAM                                       |      |

| OVERVIEW                                                      |      |

|                                                               |      |

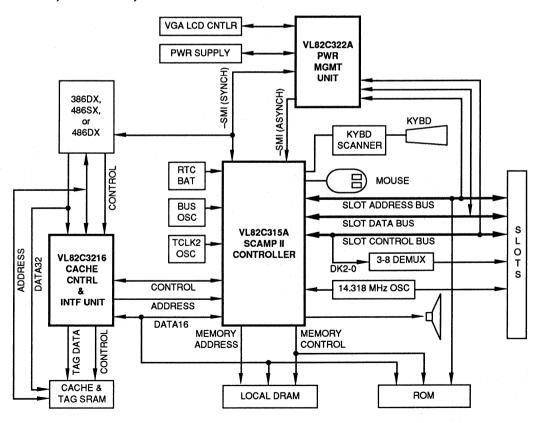

| VL82C315A, VL82C3216, 386DX/486-BASED NOTEBOOK SYSTEM DIAGRAM |      |

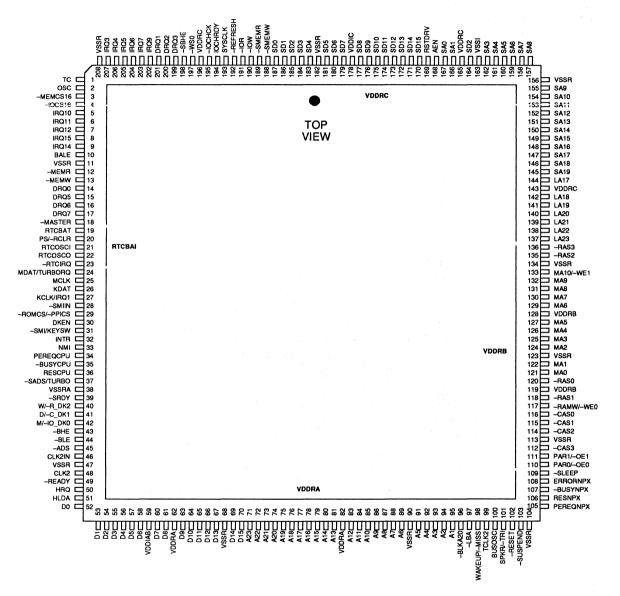

| PIN DIAGRAM                                                   |      |

| PIN TYPE BY OPERATIONAL STATE                                 |      |

| SIGNAL DESCRIPTIONS                                           |      |

| FUNCTIONAL DESCRIPTION                                        | 21   |

| CPU INTERFACE                                                 |      |

| Local Bus Accesses                                            |      |

| Slot Bus Accesses                                             |      |

| Bus Arbitration                                               |      |

| System Reset                                                  |      |

| CPU-Only Reset<br>CPU Self-Test Request                       |      |

| •                                                             |      |

|                                                               |      |

| Coprocesor-Only Reset Logic<br>Error/Interrupt Logic          |      |

| Busy Logic                                                    |      |

| Toggle Busy                                                   |      |

| PEREQ Logic                                                   |      |

| DRAM CONTROLLER                                               |      |

| 512Kx8 DRAM Support                                           |      |

| Memory Maps                                                   | 27   |

| Page Mode and Interleave Mode Operations                      |      |

| Interleave Mode Operation                                     |      |

| Page Mode Operation                                           |      |

| DRAM Speed Vs Wait State Configuration<br>RAS Shut-Off        |      |

| DRAM Refresh                                                  |      |

| System Board Refresh                                          |      |

| Off-Board DRAM Refresh                                        |      |

| Self-Refresh Mode                                             |      |

| Suspend Mode Refresh                                          |      |

| RAS-Only and CAS-before-RAS Refresh                           |      |

| Self-Refresh Mode<br>DRAM Registers                           |      |

| DRAM Map Register (RAMMAP)                                    |      |

| DRAM Control Register (RAMSET)                                |      |

| Refresh Control Register (REFCTL)                             |      |

| ADDRESS MAPPER/DECODER                                        |      |

| Slot Pointer                                                  |      |

| Remapping of Memory Range A0000h-FFFFFh                       |      |

| Relocating System and Slot ROM                                |      |

## Page Number

| Item |                                                                                         | Numbe |

|------|-----------------------------------------------------------------------------------------|-------|

|      | On-Board ROM Width and Location                                                         |       |

|      | Using Flash Memory for On-Board ROM                                                     |       |

|      | Shadowing                                                                               |       |

|      | PCMCIA 1.0 Memory Card Support                                                          | 41    |

|      | Memory Card Control Register (MCDCTL)                                                   |       |

|      | DIRECT MEMORY ACCESS (DMA)                                                              |       |

|      | DMA Controller Registers                                                                |       |

|      | Middle Address Bit Latches                                                              |       |

|      | Page Registers                                                                          |       |

|      | Address Generation                                                                      |       |

|      | ROMDMA Register                                                                         |       |

|      | DMA Power Management Option                                                             |       |

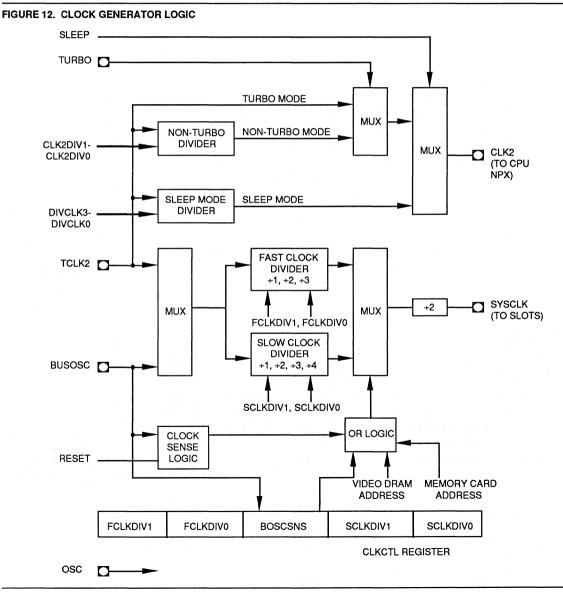

|      | CLOCK GENERATION                                                                        |       |

|      | Clock Signals                                                                           | 40    |

|      | Programmable AT Bus Clock                                                               |       |

|      | Clock Control Register (CLKCTL)                                                         |       |

|      | Clock Control Enhancements                                                              |       |

|      |                                                                                         |       |

|      | POWER MANAGEMENT MODE CONTROL                                                           |       |

|      | Sleep Mode Operation                                                                    |       |

|      | Sleep Mode Configuration Register (SLPCTL)                                              |       |

|      | Suspend Mode Operation                                                                  |       |

|      | Entering the Suspend Mode                                                               |       |

|      | Exiting the Suspend Mode (Resume)<br>Powering the VL82C315A Off During the Suspend Mode |       |

|      | ISA BUS INTERFACE                                                                       | 54    |

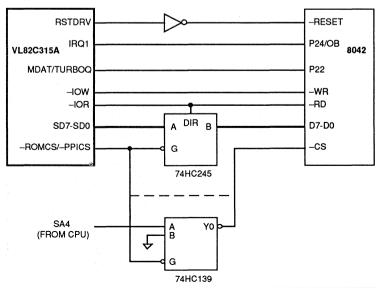

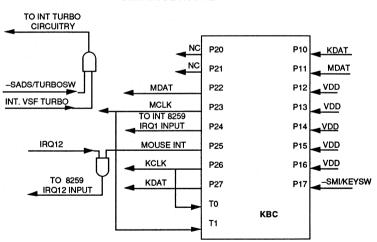

|      | KEYBOARD CONTROLLER INTERFACE                                                           |       |

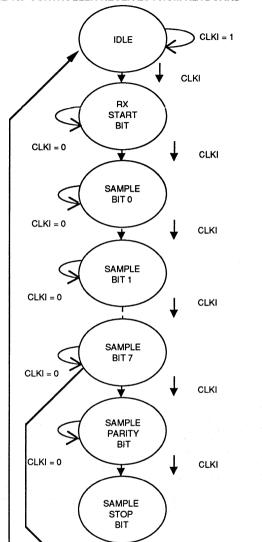

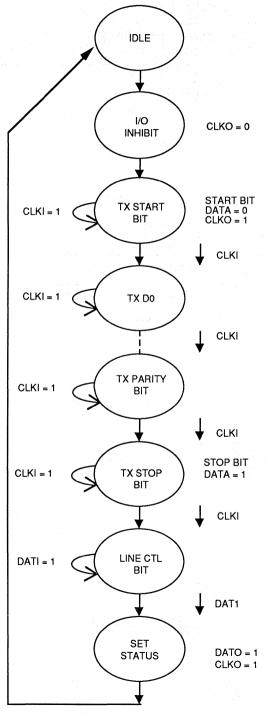

|      | Keyboard Controller Functional Description                                              |       |

|      | Keyboard Controller Interface to PC/AT                                                  |       |

|      | Keyboard Controller Interface Protocol                                                  |       |

|      | Programmer Interface                                                                    |       |

|      | Keyboard Controller Command Set                                                         |       |

|      | Command Descriptions                                                                    |       |

|      | Emulation of A20GATE and –RC.                                                           |       |

|      | Keyboard Power Management                                                               |       |

|      | Keyboard Configuration in Different Modes                                               |       |

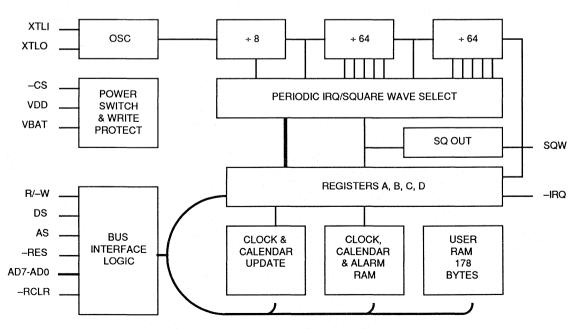

|      | REAL-TIME CLOCK                                                                         |       |

|      | Time of Day Register Descriptions                                                       |       |

|      | RTC Control Register Description                                                        |       |

|      | Register A Description                                                                  |       |

|      | Register B Description                                                                  |       |

|      | Register C Description                                                                  | 72    |

|      | Register D Description                                                                  |       |

|      | RTC CMOS Standby RAM Description                                                        |       |

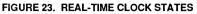

|      | General Operational Notes                                                               |       |

|      | Set Operation                                                                           |       |

|      | 24/12-Hour Mode                                                                         |       |

|      | Update Operation                                                                        |       |

|      | Alarm Operation                                                                         |       |

|      | Interrupts                                                                              |       |

Page Number

| Item |                                                                                         | Numb |

|------|-----------------------------------------------------------------------------------------|------|

|      | Divider Control                                                                         | 73   |

|      | Periodic Interrupt Selection                                                            | 73   |

|      | Update Cycle                                                                            |      |

|      | Power-Down Mode                                                                         |      |

|      | RTC Address Space Control                                                               |      |

|      | -RTCIRQ Operation                                                                       |      |

|      | INTERRUPT CONTROLLER                                                                    |      |

|      | Interrupt Controller Registers                                                          |      |

|      | TIMER/COUNTER                                                                           |      |

|      | Timer/Counter Registers                                                                 | 77   |

|      | SYSTEM MANAGEMENT MODE (SMM)                                                            |      |

|      | Shadow Control Effects During SMM                                                       | 80   |

|      | SMM IO Break Functions                                                                  |      |

|      | IO Break Mask Registers                                                                 |      |

|      | SMI IO Break Status Registers                                                           |      |

|      | Programmable IO Break Registers                                                         |      |

|      | Programmable Timer-Based –SMI Generation                                                |      |

|      | Timer Registers                                                                         |      |

|      | SMM System Robustness Features<br>CPU Reset Request Indicator                           |      |

|      | Halt Indicator                                                                          |      |

|      | Interaction of RSTREQ and SMM                                                           |      |

|      | Interaction of HLTACT and SMM                                                           |      |

|      | TURBO/SLOW CPU CONTROL                                                                  |      |

|      | PORT B AND NMI LOGIC                                                                    |      |

|      | VLSI SPECIAL FEATURES                                                                   |      |

|      | Miscellaneous Configuration Register (MISCSET)                                          | 91   |

|      | DEDICATED INTERNAL CONTROL REGISTERS                                                    |      |

|      | PARITY GENERATION AND DETECTION CIRCUIT                                                 |      |

|      |                                                                                         |      |

|      | LOCAL BUS PERIPHERAL SUPPORT                                                            |      |

|      | CPU Access to Local Bus Devices                                                         |      |

|      | Local Bus Access Input (-LBA)                                                           |      |

|      | Programmable Local Bus Memory Regions<br>DMA and Master Mode Local Bus Memory Transfers |      |

|      | Local Bus Watchdog Timer                                                                |      |

|      | IN-CIRCUIT TEST LOGIC                                                                   |      |

|      | SPECIAL VL82C315A CYCLES AND RESET OPTIONS                                              |      |

|      | Halt/Shutdown Cycles                                                                    |      |

|      | ISA Cycles                                                                              |      |

|      | Coprocessor Cycles                                                                      |      |

|      | System Reset Options                                                                    |      |

|      | REGISTER SUMMARY                                                                        |      |

|      | System Configuration                                                                    |      |

|      | Summary of Configuration Registers                                                      |      |

|      | Version (00h)                                                                           |      |

|      | Index Register                                                                          |      |

|      | Data Port Register                                                                      |      |

|      |                                                                                         | -    |

## Page Number

| t | e | r | r | 1 |  |

|---|---|---|---|---|--|

|   |   |   |   |   |  |

| AC CHARACTERISTICS           | <br>법 성고도 방법을 통해 한 것이라는 것이다.      |     |

|------------------------------|-----------------------------------|-----|

| ABSOLUTE MAXIMUM RATINGS     | <br>                              |     |

| DC CHARACTERISTICS: 5 VOLT   |                                   |     |

| DC CHARACTERISTICS: 3.3 VOLT |                                   | 140 |

| VDD CONNECTION OPTIONS       |                                   |     |

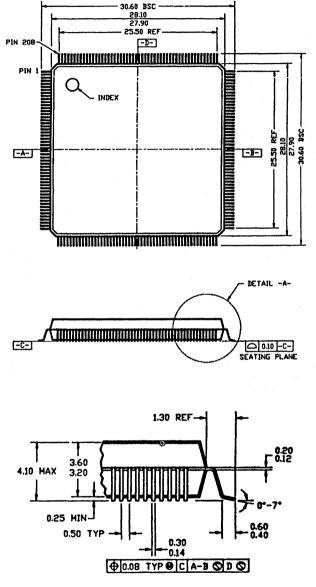

| PACKAGE OUTLINE              |                                   |     |

| SALES OFFICE LISTING         | <br>이 아이는 것 같은 것을 하는 것이 없을 것을 했다. |     |

### LIST OF TABLES

| Table 1.  | DRAM Memory Maps                                           | .27 |

|-----------|------------------------------------------------------------|-----|

| Table 2.  | Logically Remapped DRAM Memory - Special Cases             | .28 |

| Table 3.  | Page/Interleave Versus Memory Map                          |     |

| Table 4.  | Automatic Interleave Versus Populated Banks                |     |

| Table 5.  | 256K DRAM Page/Interleave Mapping                          | .30 |

| Table 6.  | 1M DRAM Page/Interleave Mapping                            |     |

| Table 7.  | 4M DRAM Page/Interleave Mapping                            |     |

| Table 8.  | RAMMAP Configuration Register                              | .33 |

| Table 9 . | RAMSET Configuration Register                              |     |

| Table 10. | REFCTL Configuration Register                              | .35 |

| Table 11. | SLTPTR Configuration Register                              | .36 |

| Table 12. | Effect of Slot Pointer                                     | .36 |

| Table 13. | Relocation of System and Slot ROM                          | .38 |

| Table 14. | Shadowing Configuration Registers                          | .40 |

| Table 15. | PCMCIA 1.0 IC Memory Card Index Register and Data Port Map | .41 |

| Table 16. | MCDCTL Configuration Register                              | .43 |

| Table 17. | DMA Controller Registers                                   |     |

| Table 18. | DMA Addressing for Slot Bus Accesses                       | .45 |

| Table 19. | DMA Addressing for System Board Memory                     | .46 |

| Table 20. | ROMDMA Configuration Register                              | .47 |

| Table 21. | AT Bus Clock Frequencies                                   |     |

| Table 22. | CLKCTL Configuration Register                              | .50 |

| Table 23. | SLPCTL Configuration Register                              | .52 |

| Table 24. | BUSCTL1 Configuration Register                             |     |

| Table 25. | BUSCTL2 Configuration Register                             | .55 |

| Table 26. | Accessing the Command, Status and Data Registers           | .56 |

| Table 27. | PC/AT Status Register                                      | .59 |

| Table 28. | PS/2 Status Register                                       | .60 |

| Table 29. | PC/AT and PS/2 Commands                                    | .61 |

| Table 30. | Added PS/2 Commands                                        | .61 |

| Table 31. | PC/AT Mode Register                                        | .62 |

| Table 32. | PS/2 Mode Register                                         | .62 |

| Table 33. | KBDCTL Configuration Register                              | .66 |

| Table 34. | Active Turbo Options by Keyboard Mode                      | .69 |

| Table 35. | RTCLSB Configuration Register                              | .75 |

| Table 36. | RTCMSB Configuration Register                              | .75 |

| Table 37. | 82C59A Registers - Write Operation                         | .76 |

| Table 38. | 82C59A Registers - Read Operation                          | .76 |

| Table 39. | Counter/Timer Registers                                    |     |

| Table 40. | SMMCTL Register                                            |     |

|           |                                                            |     |

# TABLE OF CONTENTS

# Page Number

#### Item

| Table 41.       | SMMSKA Configuration Register                     |     |

|-----------------|---------------------------------------------------|-----|

| Table 42.       | SMMSKB Configuration Register                     |     |

| Table 43.       | SMSTSA Configuration Register                     |     |

| Table 44.       | SMSTSB Configuration Register                     |     |

| Table 45.       | PIO2HI Configuration Register                     |     |

| Table 46.       | PIO2LO Configuration Register                     |     |

| Table 47.       | PIO1HI Configuration Register                     |     |

| Table 48.       | PIO1LO Configuration Register                     |     |

| Table 49.       | IO Break Programmable Timer Registers             |     |

| Table 50.       | Port B Register                                   |     |

| Table 51.       | MISCSET Configuration Register                    |     |

| Table 52.       | Dedicated I/O Control Registers                   |     |

| Table 53.       | Configuration Index Register                      |     |

| Table 54.       | Configuration Data Port Register                  |     |

| Table 55.       | Fast A20 Register                                 |     |

| Table 56.       | Fast CPU Reset Register                           |     |

| Table 57.       | Coprocessor Control Registers                     |     |

| Table 58.       | Coprocessor Speed Control Registers               | 94  |

| Table 59.       | Configuration Enable/Disable Registers            |     |

| Table 60.       | PMRA1, PMRR1, PRA2, PMRR2 Configuration Registers |     |

| Table 61.       | Pin Assignment for In-Circuit Test Mode           |     |

| Table 62.       | Halt/Shutdown Detection                           |     |

| Table 63.       | Configuration Register                            |     |

| Table 64.       | Indexed Configuration Registers Map               |     |

| Table 65.       | Indexed Configuration Registers Reset Values      |     |

| Table 66.       | Dedicated I/O Control Registers                   |     |

| Table 67.       | VDD Connections                                   | 142 |

|                 |                                                   |     |

| LIST OF FIGURES |                                                   |     |

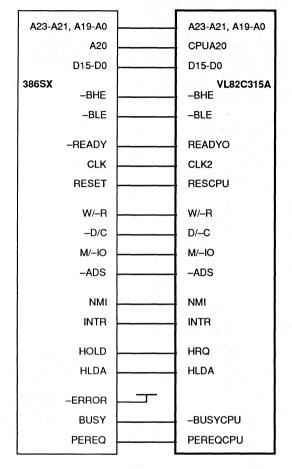

| Figure 1.       | CPU Interface                                     |     |

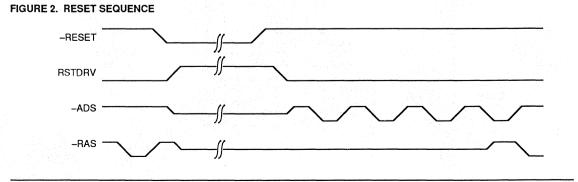

| Figure 2.       | Reset Sequence                                    |     |

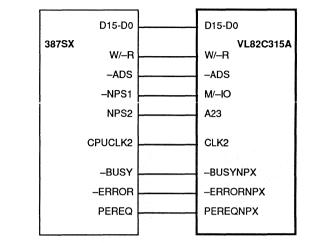

| Figure 3.       | Numeric Coprocessor Interface                     |     |

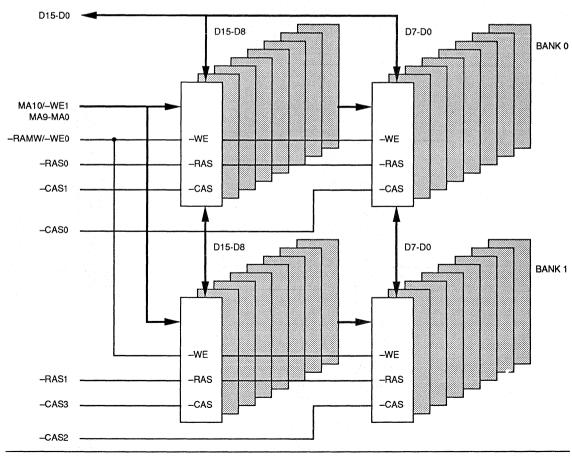

| Figure 4.       | Two Bank DRAM System                              |     |

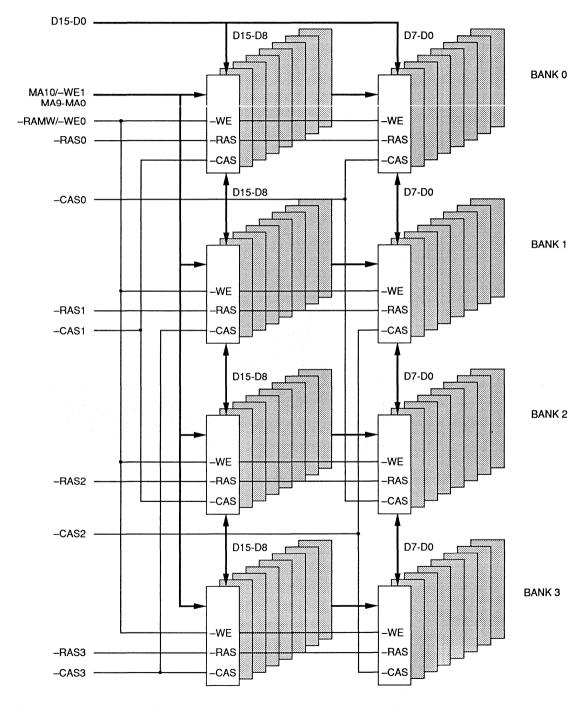

| Figure 5.       | Four Bank DRAM System                             |     |

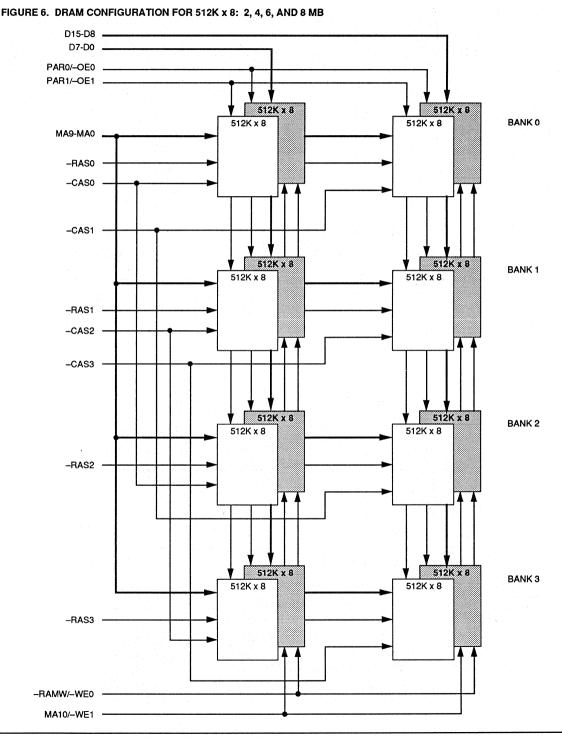

| Figure 6.       | DRAM Configuration for 512Kx8: 2, 4, 6, and 8 MB  |     |

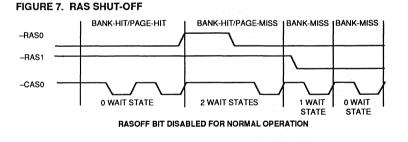

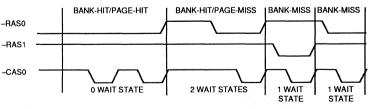

| Figure 7.       | RAS Shut-Off                                      |     |

| Figure 8.       | Effect of Slot Pointer                            |     |

| <b>F</b> ' |                                           | 50 |

|------------|-------------------------------------------|----|

| Figure 8.  | Effect of Slot Pointer                    |    |

| Figure 9.  | Remapping of 384K DRAM                    |    |

| Figure 10. | Shadow RAM Control                        |    |

| Figure 11. | Memory Mapping for PCMCIA 1.0 Memory Card |    |

| Figure 12. | Clock Generator Logic Diagram             |    |

| Figure 13. | Controller Receives from Keyboard         | 57 |

| Figure 14. | Controller Transmits to Keyboard          |    |

| Figure 15. | External Keyboard Controller Interface    |    |

| Figure 16. | Keyboard Configuration Mode Option 1      | 67 |

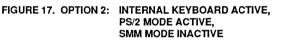

| Figure 17. | Keyboard Configuration Mode Option 2      |    |

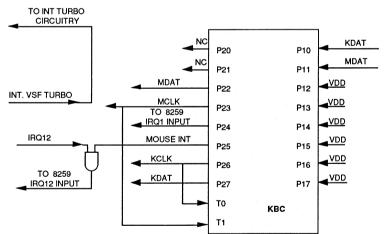

| Figure 18. | Keyboard Configuration Mode Option 3      | 68 |

| Figure 19. | Keyboard Configuration Mode Option 4      | 68 |

| Figure 20. | Keyboard Configuration Mode Option 5      | 69 |

| Figure 21. | Real-Time Clock Block Diagram             | 70 |

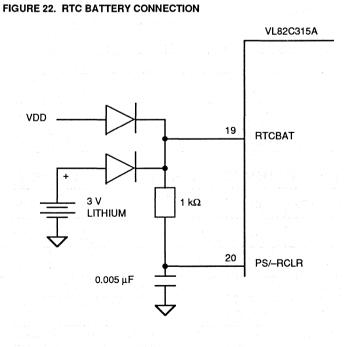

| Figure 22. | RTC Battery Connection                    | 74 |

| Figure 23. | Real-Time Clock States                    | 75 |

|            |                                           |    |

Item

# TABLE OF CONTENTS

# Page Number

| ÷., |             |                                                       |       |

|-----|-------------|-------------------------------------------------------|-------|

| 1   | Figure 24.  | Counter/Timer Block Diagram                           | 77    |

|     | Figure 25.  | Examples of Shadow Control Effects during SMM         | 79    |

|     | Figure 26.  | ICT Test Mode Timing Waveform                         |       |

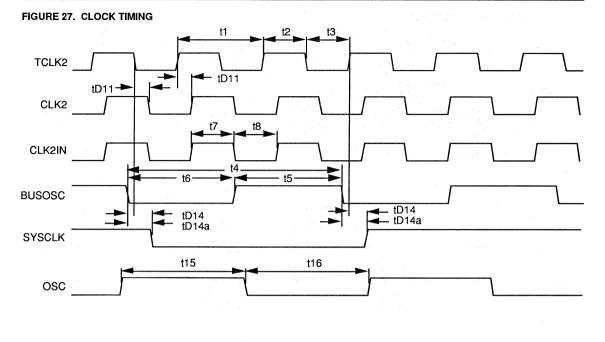

|     | Figure 27.  | Clock Timing                                          | . 116 |

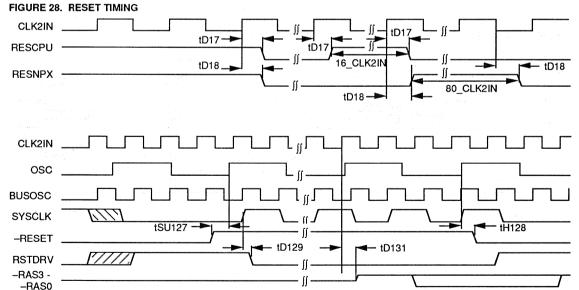

|     | Figure 28.  | Reset Timing                                          | 116   |

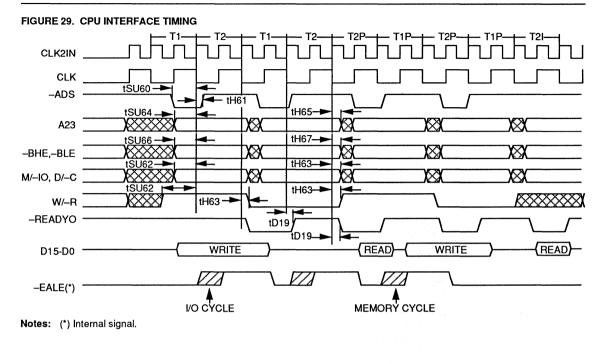

|     | Figure 29.  | CPU Interface Timing                                  | 117   |

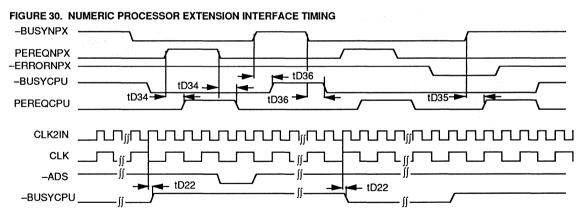

|     | Figure 30.  | Numeric Processor Extension Interface Timing          | .117  |

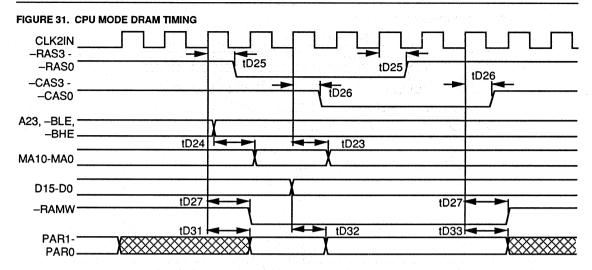

|     | Figure 31.  | CPU Mode DRAM Timing                                  | . 118 |

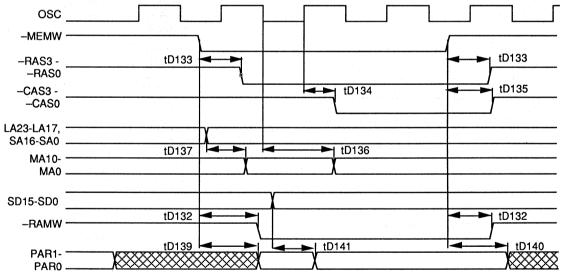

|     | Figure 32.  | HLDA Mode DRAM Timing                                 | .118  |

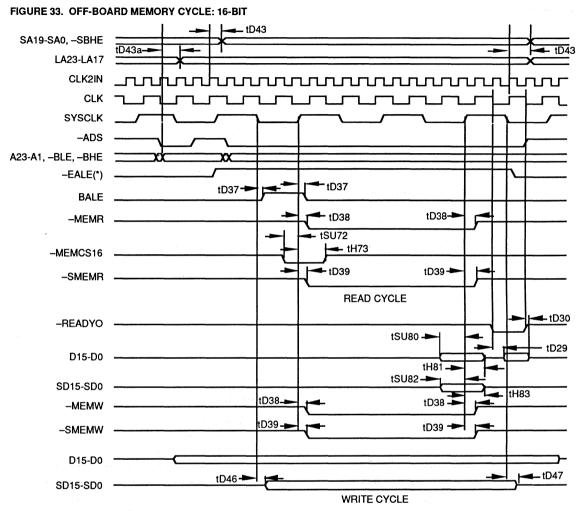

|     | Figure 33.  | Off-Board Memory Cycle: 16-Bit                        | .119  |

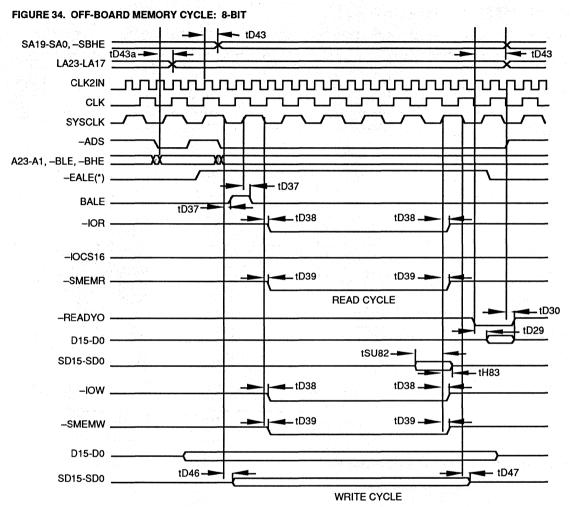

|     | Figure 34.  | Off-Board Memory Cycle: 8-Bit                         | . 120 |

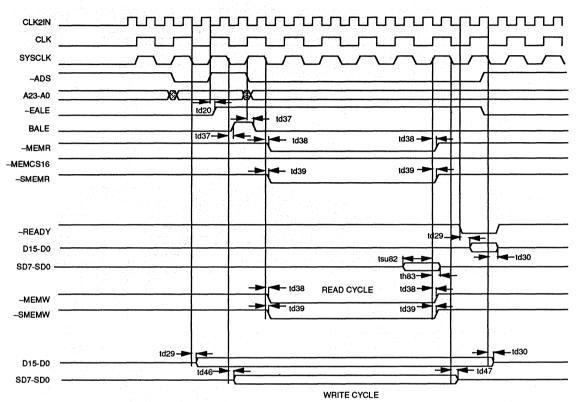

|     | Figure 35.  | Off-Board I/O Cycle: 16-Bit                           | .121  |

|     | Figure 36.  | Off-Board I/O Cycle: 8-Bit                            | . 122 |

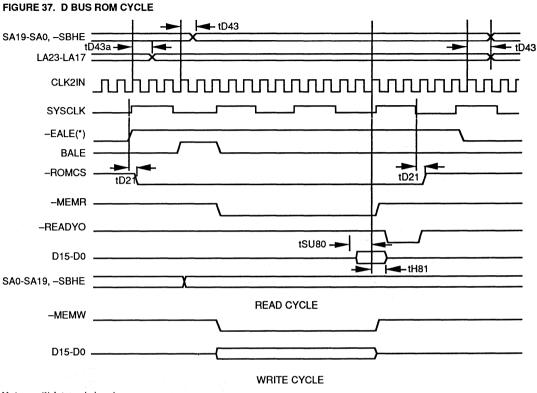

|     | Figure 37.  | D Bus ROM Cycle                                       | . 123 |

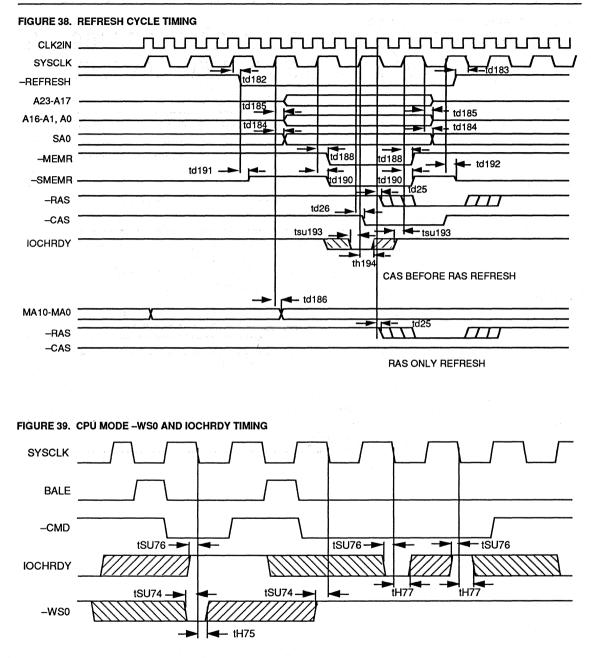

|     | Figure 38.  | Refresh Cycle Timing                                  | . 124 |

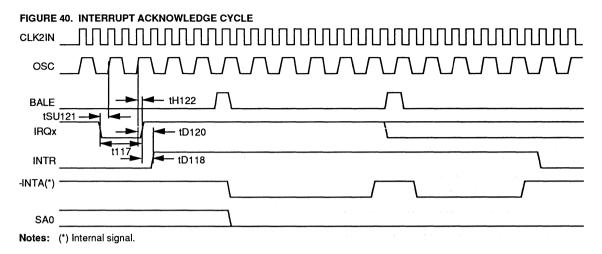

|     | Figure 39.  | CPU Mode – WS0 and IOCHRDY Timing                     | .124  |

|     | Figure 40.  | Interrupt Acknowledge Cycle                           | .125  |

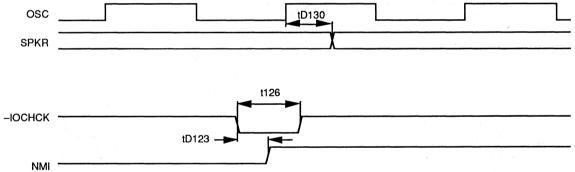

|     | Figure 41.  | Speaker and –IOCHCK Timing                            |       |

|     | Figure 42.  | PCMCIA 1.0 Memory Card Timing                         | .126  |

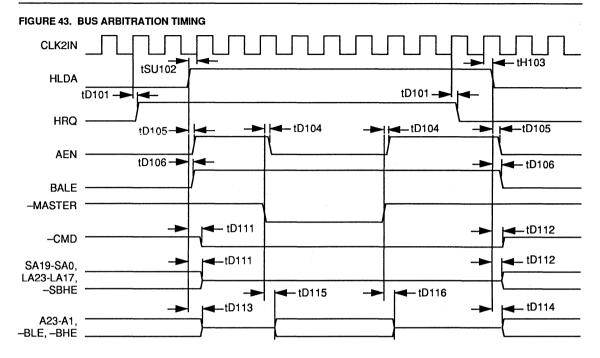

|     | Figure 43.  | Bus Arbitration Timing                                | . 127 |

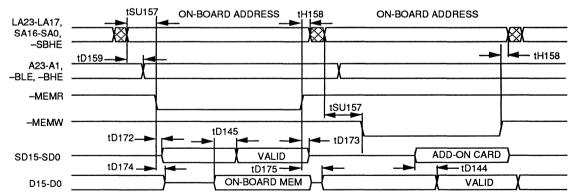

|     | Figure 44.  | Master Mode Cycle Timing: On-Board Memory Accesses    | .127  |

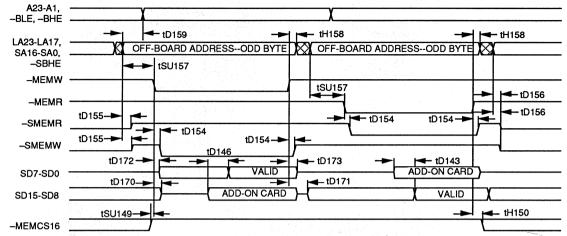

|     | Figure 45.  | Master Mode Cycle Timing: Off-Board Memory Accesses   | . 128 |

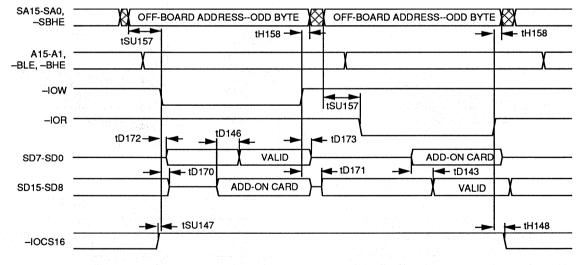

|     | Figure 46.  | Master Mode Cycle Timing: I/O Accesses                | .128  |

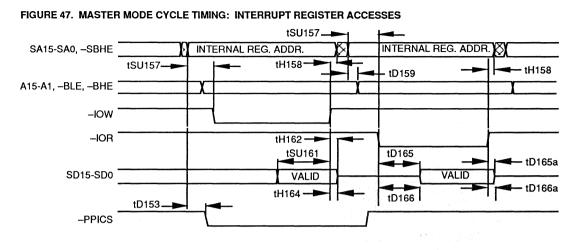

|     | Figure 47.  | Master Mode Cycle Timing: Interrupt Register Accesses | . 129 |

|     | Figure 48.  | Master Mode Refresh Timing                            | . 129 |

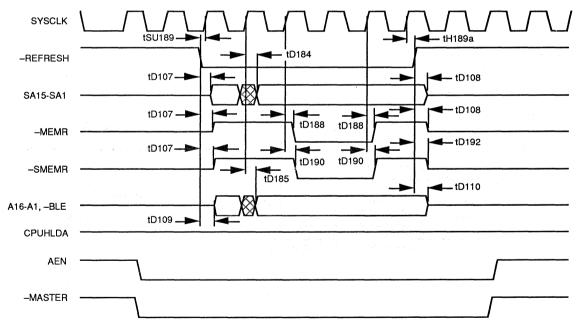

|     | Figure 49A. | DMA Mode Timing: 8-Bit Cycle                          | .130  |

|     | Figure 49B. | DMA Mode Timing: 8-Bit Cycle                          | .131  |

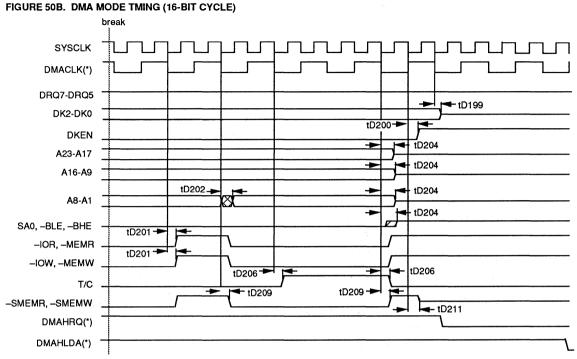

|     | Figure 50A. | DMA Mode Timing: 16-Bit Cycle                         |       |

|     | Figure 50B. | DMA Mode Timing: 16-Bit Cycle                         | . 133 |

|     | Figure 51.  | IOCHRDY Timing: DMA Cycles                            | 134   |

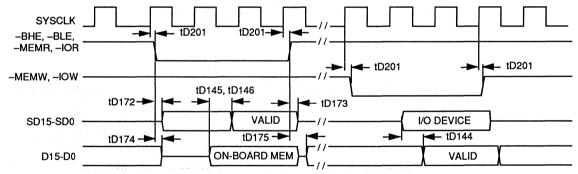

|     | Figure 52.  | DMA Mode Data Steering: On-Board Memory Accesses      |       |

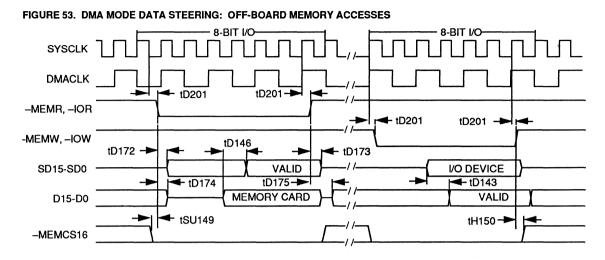

|     | Figure 53.  | DMA Mode Data Steering: Off-Board Memory Accesses     | . 135 |

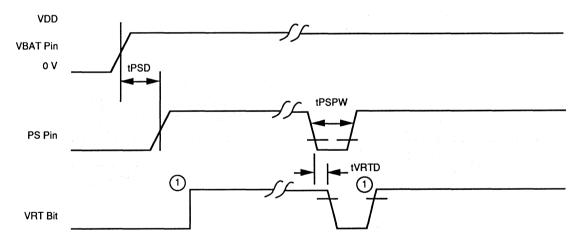

|     | Figure 54.  | Real-Time Clock Standby Mode Control                  | . 135 |

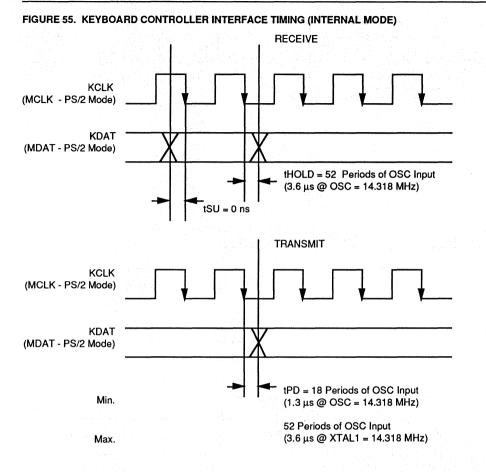

|     | Figure 55.  | Keyboard Controller Interface Timing (Internal Mode)  | . 136 |

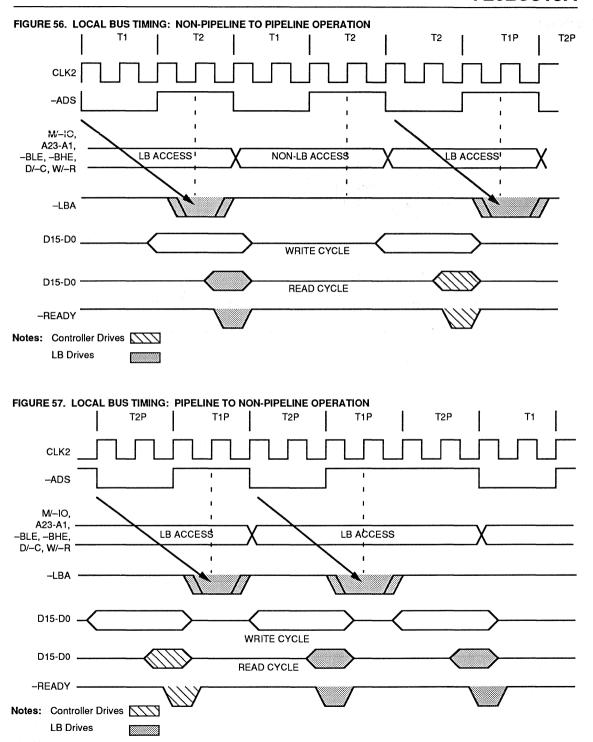

|     | Figure 56.  | Local Bus Timing: Non-Pipeline to Pipeline Operation  |       |

|     | Figure 57.  | Local Bus Timing: Pipeline to Non-Pipeline Operation  |       |

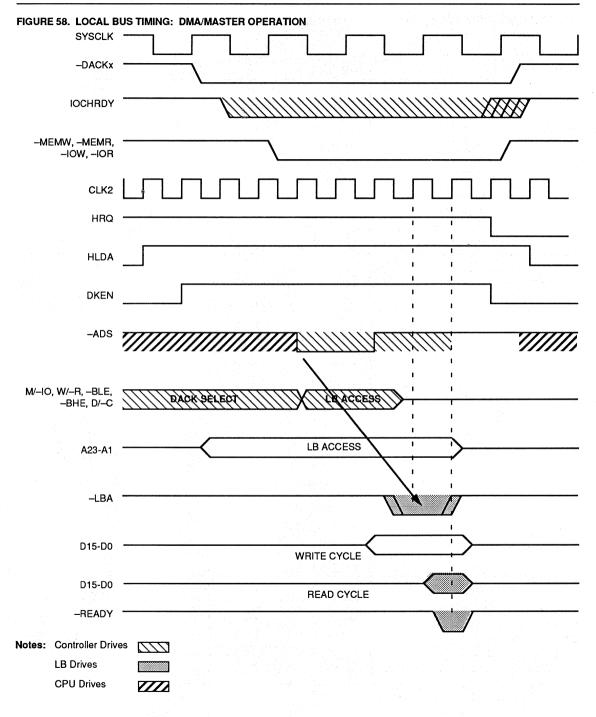

|     | Figure 58.  | Local Bus Timing: DMA/Master Operation                | . 138 |

|     |             |                                                       |       |

x

SCAMP<sup>TM</sup> II SYSTEM CONTROLLER

### FEATURES

- Compatible with 386SX-based PC/AT compatible systems. Also 386DX, 486SX, or 486DX via VL82C3216 Cache Controller and Interface Unit

- Up to 33 MHz system clock in 5.0 V systems or 25 MHz in 3.3 V systems

- Replaces 11 peripheral devices on the motherboard:

- Two 82C37A DMA controllers

- 74LS612 memory mapper

- Two 82C59A interrupt controllers

- 82C54 timer

- 82284 clock generator and ready interface

- 82288 bus controller

- Keyboard controller

- Real-time clock

- Includes:

- Memory/refresh controller

- Port B and NMI logic

- Bus steering logic

- Parity generation checking logic

- Turbo Mode control logic

- Staggered refresh to minimize power supply load variations

- Three-state control pin for board level testability

- Supports:

- Up to 16 MB system memory

- PCMCIA 1.x IC Memory Card

- mapping logic – VL82C325 (SX) Cache Controller compatibility

- Four 16- or 18-bit wide banks of 256K, 1M, or 4M DRAM or eight 16-bit wide banks of 512K x 8 DRAM

- Shadow RAM in 640K to 1M range

- 387SX numeric coprocessors

- 8- or 16-bit wide BIOS ROMs

- Synchronous or asynchronous slot bus operation up to 16 MHz

- Relocation of video and slot ROMs

- · Power saving features include:

- Sleep and Suspend Modes

- Slow DRAM refresh

- CAS-before-RAS and Self-Refresh DRAM

- Sleep Mode refresh switch to 32 kHz clock

# ADVANCE INFORMATION VL82C315A

#### Features (Cont.)

- Leakage Control in Stop Clock or Suspend Mode

- CPU on or off option in Suspend Mode

- Low-power page interleave memory mode

- Fully static operation

- DMA power management mode

Full SMM (System Management

- Mode) and I/O break support

- Supports standard Sleep Mode for interface to the VL82C322A Power

Management Unit (PMU) or other third party PMUs

- Programmable, extendable peripheral cycle

- Disable software coprocessor reset option

- Option for automatic bus speed-up on video or PCMCIA accesses

- Full support for local bus peripherals

- Separate power pin and internal level shifters for ISA bus signals allows for 5.0 V ISA bus operation in 3.3 V systems

- Other advanced features

- Programmable I/O decode for 10- or 16-bit addresses

- Hardware configurable setup to minimize custom BIOS requirements

- Programmable drive current to reduce ringing on DRAM

- · 3.3 V or 5.0 V operation

- 0.8-micron CMOS technology

- 208-lead metric quad flat pack (MQFP)

## OVERVIEW

The VL82C315A is a true single chip AT high-performance controller for 3865X-based PC/AT systems. It is capable of interfacing to 386DX and 486(DX/SX) systems via the companion VL82C3216 Cache Controller and Interface Unit. The VL82C315A is intended primarily for low-power applications requiring a high degree of integration (e.g., notebooks). However, the VL82C315A is also an excellent choice for high integration, low-cost desktop systems running up to 33 MHz.

The VL82C315A includes the dual 82C37A DMA controllers, dual 82C59A programmable interrupt controllers, 82C54 programmable interval timer, 82284 clock and ready generator, 82288 bus controller, 8042 keyboard controller, and 146818A-compatible real-time clock. Also included is the logic for SMM (System Management Mode) control, address/data bus control, memory control, shutdown, refresh generation and refresh/DMA arbitration.

The controller also includes the following:

- AMD and Cyrix compatible SMM and I/O Break interface

- Complete ISA bus interface logic

- Integrated power management features

- · Supports slow and self-refresh DRAM

- Memory/refresh controller

- Port B and NMI logic

- Bus steering logic

- Turbo Mode control logic

- · Optional parity checking logic

- · Optional parity generation logic

The VL82C315A supports 387SXcompatible numeric coprocessors including versions that support slow and stop clock operation.

The memory controller logic is capable of accessing up to 16 MB. There can be up to four banks of 256K, 1M, or 4M attached in the system or eight banks of 512K x 8 DRAMs. The VL82C315A can drive the full compliment of DRAM banks without external buffering. It features Built-in Page Mode operation. This, along with two-way interleaving, allow the PC designer to maximize

## VL82C315A, VL82C3216, 386DX/486-BASED NOTEBOOK SYSTEM DIAGRAM

AMD is a registered trademark of Advance Micro Devices, Inc.

# ADVANCE INFORMATION VL82C315A

system performance using low-cost DRAMs. Support is also included for zero, one, or two wait state operation of system DRAM.

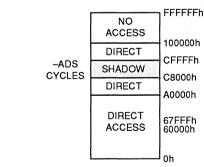

Shadowing features are supported on 16K boundaries between C0000h and DFFFFh, and on 32K boundaries between A0000h and BFFFFh, and between E0000h and FFFFFh. Simultaneous shadowed ROM, and direct system board access is possible in a non-overlapping fashion throughout this memory space. Control over four access options is provided. The options are:

- 1. Access ROM or slot bus for reads and writes.

- Access system board DRAM for reads and writes.

- 3. Access system board DRAM for reads and slot bus for writes.

- 4. Shadow setup mode. Read ROM or slot bus, write system board DRAM.

The VL82C315A handles system board refresh directly and also controls the timing of slot bus refresh. Refresh is performed in the standard PC/ATcompatible Mode where on- and offboard refreshes are performed synchronously. Refreshes are staggered to minimize power supply loading and attenuate noise on the VDD and ground pins. In the VL82C315A, refresh can be programmed to support CAS-before-RAS refresh operation, standard RASonly refresh operation, self-refresh, or no refresh. The VL82C315A supports the PC/AT standard refresh period of 15.625 µs plus 125 µs or 250 µs slow refresh options. When the Suspend Mode is active, the real-time clock's 32 kHz oscillator is used as the timing reference for absolute minimum power dissipation. Self-refresh is possible only in the Suspend Mode. DRAM accesses are not possible in this mode of operation. When self-refresh is active, it is only enabled when the Suspend Mode is also active. Otherwise, CAS-before-RAS refresh is used.

A 146818A-compatible real-time clock (RTC) is provided that supports battery voltages down to 2.4 volt standard. It also includes 128 extra battery-backed RAM locations (178 total) for operating system and power-management support. The base address of the RTC is programmable, but defaults to the PC standard address. The hardware supports an external RTC. It may be used with the internal RTC or by itself by disabling the internal RTC.

An internal keyboard controller replaces the standard 8042 required in a standard PC environment. It provides a keyboard and PS/2<sup>®</sup> mouse interface. As an option, the internal keyboard controller can be disabled allowing use of an external controller.

The 387SX is supported. A software coprocessor reset does not leave a 387SX in the same state as does the reset of a 287. The VL82C315A can be programmed to disable these software resets if problems arise.

The interrupt controller logic consists of two 82C59A megacells with eight interrupt request lines each for a total of 16 interrupts. The two megacells are cascaded internally and two of the interrupt request inputs are connected to internal circuitry allowing a total of 13 external interrupt requests. There is a special programmable logic included in the VL82C315A which allows glitch-free inputs on all the interrupt request pins.

The interval timer includes one 82C54 counter/timer megacell. The counter/ timer has three independent 16-bit counters and six programmable counter modes.

The DMA controllers are 82C37A compatible. The DMAs control data transfers between an I/O channel and on- or off-board memory. DMA can transfer data over the full 16 MB range available. There are internal latches provided for latching the middle address bits output by the 82C37A megacells on the data bus, and 74LS612 memory mappers are provided to generate the upper address bits. An optional lowpower DMA mode is available. In this mode, the DMA clocks are stopped except when DMA accesses are in progress.

The VL82C315A can be programmed for asynchronous or synchronous operation of the AT<sup>®</sup> bus.

The VL82C315A also performs all of the data buffer control functions required. Under the control of the CPU, the VL82C315A chip routes data to and from the CPU's D bus and slots (SD bus). The parity is checked for D bus DRAM read operations. The data is latched for synchronization with the CPU. Parity is generated for all data written to the D bus. The parity function may be optionally disabled except when 512K x 8 DRAM memory maps are used. In this case, parity is not an available option.

The VL82C315A generates control signals for external buffers to perform high-to-low and low-to-high byte swaps on the SD bus. For transfers between two peripherals on the slot bus, the flow control outputs of the VL82C315A disable the external data buffers. The VL82C315A also provides the feature of a single input, –TRI, to disable all of its outputs for board level testability.

The VL82C315A SCAMP II Controller's functions are programmable via a set of internal Configuration Registers. The state of the memory address bus, parity pins, DKEN, -BLKA20, -RAMW/-WE0, and -ROMCS/-PPICS pins on reset is used to determine the default configuration. A dip switch can be used to establish the initial configuration.

5.0 V only, 3.3 V only, or mixed mode operation is supported. In mixed mode operation it is possible to operate the ISA bus at 5.0 V and the remainder of the system at 3.3 V. Separated power buses are provided for:

- A. ISA bus signal I/O pads

- B. DRAM interface I/O pads

- C. Real-time clock

- D. CPU interface I/O pads

- E. Internal core logic

This break-out allows the following options:

- 1. The ISA bus runs at 5.0 V while the remainder of the VL82C315A logic runs at 3.3 V with internal level shifting.

- 2. The CPU can be shut down while the remainder of the system continues powered.

- 3. The DRAM interface can remain powered during the Suspend Mode in order to provide refresh while other circuitry is powered down.

AT and PS/2 are registered trademarks of IBM Corporation.

# ADVANCE INFORMATION VL82C315A

## **PIN DIAGRAM**

5

# ADVANCE INFORMATION VL82C315A

## PIN TYPE BY OPERATIONAL STATE

| Pin Name      | Pin<br>No. | Pin<br>Type   | Input<br>Type      | Drive<br>mA | Power<br>Rail | Suspend Mode<br>CPU On (Note 9) | Suspend Mode<br>CPU Off (Note 9) |

|---------------|------------|---------------|--------------------|-------------|---------------|---------------------------------|----------------------------------|

| тс            | 1          | O-TS          |                    | 12          | С             | PD - Note 8                     | PD - Note 8                      |

| OSC           | 2          |               | TTL (Notes 7 & 10) |             | С             | HI-Z                            | HI-Z                             |

| -MEMCS16      | 3          | I (Note 1)    | CMOS (Note 10)     |             | С             | HI-Z                            | HI-Z                             |

| -IOCS16       | 4          | I (Note 1)    | TTL                |             | С             | HI-Z                            | HI-Z                             |

| IRQ10         | 5          | l             | TTL                |             | С             | PD                              | PD                               |

| IRQ11         | 6          | 1             | TTL                |             | С             | PD                              | PD                               |

| IRQ12         | 7          | 1             | TTL                |             | C             | PD                              | PD                               |

| IRQ15         | 8          | I             | TTL                |             | С             | PD                              | PD                               |

| IRQ14         | 9          | I S           | TTL                |             | С             | PD                              | PD                               |

| BALE          | 10         | O-TS          |                    | 12          | С             | PD                              | PD                               |

| VSSR          | 11         | GND           |                    |             | Ring Gnd      |                                 |                                  |

| -MEMR         | 12         | IO (Note 2)   | TTL (Note 10)      | 12          | С             | HI-Z                            | HI-Z                             |

| -MEMW         | 13         | IO (Note 2)   | TTL (Note 10)      | 12          | С             | HI-Z                            | HI-Z                             |

| DRQ0          | 14         | 1 generation  | TTL                |             | С             | PD                              | PD                               |

| DRQ5          | 15         | 1             | TTL                |             | С             | PD                              | PD                               |

| DRQ6          | 16         | 1             | TTL                |             | С             | PD                              | PD                               |

| DRQ7          | 17         | I             | TTL                |             | С             | PD                              | PD                               |

| -MASTER       | 18         | 1             | TTL                |             | С             | PD                              | PD                               |

| RTCBAT        | 19         | PWR           |                    |             | RTC PWR       |                                 |                                  |

| PS/-RCLR      | 20         | I-PU          | CMOS-S             |             | RTC BAT       | Unchanged                       | Unchanged                        |

| RTCOSCI       | 21         | 1             | CMOS               |             | RTC BAT       | Unchanged                       | Unchanged                        |

| RTCOSCO       | 22         | 0             |                    |             | RTC BAT       | Unchanged                       | Unchanged                        |

| -RTCIRQ       | 23         | IO-PU         | TTL-S              | 4           | RTC BAT       | Unchanged                       | Unchanged                        |

| MDAT/TURBORQ  | 24         | IO (Note 1)   | TTL-S              | 12          | Α             | HI-Z                            | HI-Z                             |

| MCLK          | 25         | IO (Note 1)   | TTL-S              | 12          | Α             | HI-Z                            | HI-Z                             |

| KDAT          | 26         | IO (Note 1)   | TTL-S              | 12          | Α             | HI-Z                            | HI-Z                             |

| KCLK/IRQ1     | 27         | IO (Note 1)   | TTL-S              | 12          | Α             | HI-Z                            | HI-Z                             |

| -SMIIN        | 28         |               | TTL                |             | Α             | High                            | PD                               |

| -ROMCS/-PPICS | 29         | IO            | TTL                | 4           | A             | High                            | PD                               |

| DKEN          | 30         | 10            | TTL                | 4           | Α             | Low                             | PD                               |

| -SMI/KEYSW    | 31         | IO (Note 1)   | TTL-S              | 4           | Α             | HI-Z                            | HI-Z                             |

| INTR          | 32         | O-TS          |                    | 4           | Α             | Unchanged                       | PD                               |

| NMI           | 33         | O-TS          |                    | 4           | Α             | Unchanged                       | PD                               |

| PEREQCPU      | 34         | O-TS (Note 3) |                    | 4           | Α             | Unchanged                       | PD                               |

6

# ADVANCE INFORMATION VL82C315A

| Pin Name    | Pin<br>No. | Pin<br>Type   | Input<br>Type                          | Drive<br>mA | Power<br>Rail | Suspend Mode<br>CPU On (Note 9) | Suspend Mode<br>CPU Off (Note 9) |

|-------------|------------|---------------|----------------------------------------|-------------|---------------|---------------------------------|----------------------------------|

| -BUSYCPU    | 35         | O-TS (Note 4) |                                        | 4           | A             | Unchanged                       | PD                               |

| RESCPU      | 36         | Ю             | TTL                                    | 4           | A             | Low                             | PD                               |

| -SADS/TURBO | 37         | I             | TTL (Note 10)                          |             | A             | HI-Z                            | PD                               |

| VDDRA       | 38         | PWR           |                                        |             | A Supply      |                                 |                                  |

| -SRDY       | 39         | O-TS (Note 4) |                                        | 4           | A             | High                            | PD                               |

| W/-R_DK2    | 40         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| D/-C_DK1    | 41         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| M/-IO_DK0   | 42         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| -BHE        | 43         | Ю             | TTL                                    | 4           | А             | PD                              | PD                               |

| -BLE        | 44         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| -ADS        | 45         | Ю             | TTL (Note 10)                          | 4           | Α             | HI-Z                            | PD                               |

| CLK2IN      | 46         | I             | CMOS                                   |             | Α             | HI-Z                            | HI-Z                             |

| VSSR        | 47         | GND           |                                        |             | Ring Gnd      |                                 |                                  |

| CLK2        | 48         | Ю             | TTL                                    | 8           | А             | Low                             | Low                              |

| -READY      | 49         | Ю             | TTL                                    | 4           | I             | High                            | PD                               |

| HRQ         | 50         | Ю             | TTL                                    | 4           | A             | High                            | PD                               |

| HLDA        | 51         | . <b>1</b>    | TTL                                    |             | A             | HI-Z                            | PD                               |

| D0          | 52         | Ю             | TTL                                    | 4           | А             | PD                              | PD                               |

| D1          | 53         | Ю             | TTL                                    | 4           | А             | PD                              | PD                               |

| D2          | 54         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| D3          | 55         | Ю             | TTL                                    | 4           | Α             | PD                              | PD                               |

| D4          | 56         | Ю             | TTL                                    | 4           | Α             | PD                              | PD                               |

| D5          | 57         | 10            | TTL                                    | 4           | A             | PD                              | PD                               |

| D6          | 58         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| VDDIAB      | 59         | PWR           |                                        |             | A & B Core    |                                 |                                  |

| D7          | 60         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| D8          | 61         | Ю             | TTL                                    | 4           | А             | PD                              | PD                               |

| VDDRA       | 62         | PWR           |                                        |             | A Supply      |                                 |                                  |

| D9          | 63         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| D10         | 64         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| D11         | 65         | ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| D12         | 66         | Ю             | TTL                                    | 4           | A             | PD                              | PD                               |

| D13         | 67         | Ю             | TTL                                    | 4           | А             | PD                              | PD                               |

| VSSR        | 68         | GND           | ······································ |             | Ring Gnd      |                                 |                                  |

# ADVANCE INFORMATION VL82C315A

## PIN TYPE BY OPERATIONAL STATE (Cont.)

| Pin Name     | Pin<br>No. | Pin<br>Type | Input<br>Type  | Drive<br>mA | Power<br>Rail | Suspend Mode<br>CPU On (Note 9) | Suspend Mode<br>CPU Off (Note 9) |

|--------------|------------|-------------|----------------|-------------|---------------|---------------------------------|----------------------------------|

| D14          | 69         | 10          | TTL            | 4           | Α             | PD                              | PD                               |

| D15          | 70         | Ю           | TTL            | 4           | A             | PD                              | PD                               |

| A23          | 71         | Ю           | TTL            | 4           | A             | PD                              | PD                               |

| A22          | 72         | ю           | TTL            | 4           | A             | PD                              | PD                               |

| A21          | 73         | 10          | TTL            | 4           | A             | PD                              | PD                               |

| A20          | 74         | 10          | TTL            | 4           | A             | PD                              | PD                               |

| A19          | 75         | Ю           | TTL            | 4           | A             | PD                              | PD                               |

| A18          | 76         | 10          | TTL            | 4           | A             | PD                              | PD                               |

| A17          | 77         | Ю           | TTL            | 4           | А             | PD                              | PD                               |

| A16          | 78         | 10          | TTL            | 4           | A             | PD                              | PD                               |

| A15          | 79         | Ю           | TTL            | 4           | A             | PD                              | PD                               |

| A14          | 80         | Ю           | TTL            | 4           | А             | PD PD                           | PD                               |

| A13          | 81         | 10          | TTL            | 4           | A             | PD                              | PD                               |

| VDDRA        | 82         | PWR         |                |             | A Supply      |                                 |                                  |

| A12          | 83         | Ю           | TTL            | 4           | A             | PD                              | PD                               |

| A11          | 84         | 10          | TTL            | 4           | A             | PD                              | PD                               |

| A10          | 85         | 10          | TTL            | 4           | A             | PD                              | PD                               |

| A9           | 86         | 10          | TTL            | 4           | Α             | PD                              | PD                               |

| A8           | 87         | 10          | TTL            | 4           | Α             | PD                              | PD                               |

| A7           | 88         | IO          | TTL            | 4           | A             | PD                              | PD                               |

| A6           | 89         | Ю           | TTL            | 4           | А             | PD                              | PD                               |

| VSSR         | 90         | GND         |                |             | Ring Gnd      |                                 |                                  |

| A5           | 91         | Ю           | TTL            | 4           | A             | PD                              | PD                               |

| A4           | 92         | Ю           | TTL            | 4           | A             | PD                              | PD                               |

| A3           | 93         | Ю           | TTL            | 4           | А             | PD                              | PD                               |

| A2           | 94         | 10          | TTL            | 4           | А             | PD                              | PD                               |

| A1           | 95         | 10          | TTL            | 4           | А             | PD                              | PD                               |

| -BLKA20      | 96         | Ю           | TTL            | 4           | А             | PD                              | PD                               |

| –LBA         | 97         |             | TTL            |             | А             | HI-Z                            | PD                               |

| WAKEUP/-MISS | 98         | ю           | TTL            | 4           | А             | HI-Z                            | PD                               |

| TCLK2        | 99         | 1           | CMOS (Note 10) | 1           | А             | HI-Z                            | HI-Z                             |

| BUSOSC       | 100        |             | CMOS (Note 10) |             | Α             | HI-Z                            | HI-Z                             |

| SPKR/-TRI    | 101        | IO-PU       | TTL TO TRADE   | 8           | A             | PU                              | PU                               |

| -RESET       | 102        |             | TTL-S          |             | Α             | HI-Z                            | HI-Z                             |

8

ADVANCE INFORMATION VL82C315A

| Pin Name   | Pin<br>No. | Pin<br>Type | Input<br>Type | Drive<br>mA | Power<br>Rail | Suspend Mode<br>CPU On (Note 9) | Suspend Mode<br>CPU Off (Note 9) |

|------------|------------|-------------|---------------|-------------|---------------|---------------------------------|----------------------------------|

| -SUSPEND   | 103        | 1           | TTL           |             | A             | HI-Z                            | HI-Z                             |

| VSSR       | 104        | GND         |               |             | Ring Gnd      |                                 |                                  |

| PEREQNPX   | 105        | 1           | TTL (Note 10) |             | A             | HI-Z                            | PD                               |

| RESNPX     | 106        | Ю           | TTL           | 4           | A             | Low                             | PD                               |

| -BUSYNPX   | 107        | 1           | TTL (Note 10) |             | A             | HI-Z                            | PD                               |

| -ERRORNPX  | 108        | 1           | TTL (Note 10) |             | A             | HI-Z                            | PD                               |

| -SLEEP     | 109        | 1           | TTL           |             | A             | HI-Z                            | HI-Z                             |

| PAR0/OE0   | 110        | Ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| PAR1/-OE1  | 111        | Ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| -CAS3      | 112        | Ю           | TTL           | 12/24       | В             | (Note 5)                        | (Note 5)                         |

| VSSR       | 113        | GND         |               |             | Ring Gnd      |                                 |                                  |

| -CAS2      | 114        | Ю           | TTL           | 12/24       | В             | (Note 5)                        | (Note 5)                         |

| -CAS1      | 115        | Ю           | TTL           | 12/24       | В             | (Note 5)                        | (Note 5)                         |

| -CAS0      | 116        | Ю           | TTL           | 12/24       | В             | (Note 5)                        | (Note 5)                         |

| -RAMW/-WE0 | 117        | Ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| -RAS1      | 118        | 10          | TTL           | 12/24       | В             | (Note 5)                        | (Note 5)                         |

| VDDRB      | 119        | PWR         |               |             | B Supply      |                                 |                                  |

| -RAS0      | 120        | Ю           | TTL           | 12/24       | В             | (Note 5)                        | (Note 5)                         |

| MAO        | 121        | ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| MA1        | 122        | Ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| VSSR       | 123        | GND         |               |             | Ring Gnd      |                                 |                                  |

| MA2        | 124        | Ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| МАЗ        | 125        | Ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| MA4        | 126        | ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| MA5        | 127        | 10          | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| VDDRB      | 128        | PWR         |               |             | B Supply      |                                 |                                  |

| MA6        | 129        | ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| MA7        | 130        | 10          | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| MA8        | 131        | 10          | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| MA9        | 132        | Ю           | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| MA10/-WE1  | 133        | 10          | TTL           | 12/24       | В             | (Note 6)                        | (Note 6)                         |

| VSSR       | 134        | GND         |               |             | Ring Gnd      |                                 |                                  |

| -RAS2      | 135        | Ю           | TTL           | 12/24       | В             | (Note 5)                        | (Note 5)                         |

| -RAS3      | 136        | 10          | TTL           | 12/24       | В             | (Note 5)                        | (Note 5)                         |

# ADVANCE INFORMATION VL82C315A

| Pin Name | Pin<br>No. | Pin<br>Type | Input<br>Type | Drive<br>mA | Power<br>Rail | Suspend Mode<br>CPU On (Note 9) | Suspend Mode<br>CPU Off (Note 9) |

|----------|------------|-------------|---------------|-------------|---------------|---------------------------------|----------------------------------|

| LA23     | 137        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| LA22     | 138        | Ю           | TTL           | 12          | С             | PD                              | PD                               |

| LA21     | 139        | Ю           | TTL           | 12          | С             | PD                              | PD                               |

| LA20     | 140        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| LA19     | 141        | 10          | TTL           | 12          | с             | PD                              | PD                               |

| LA18     | 142        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| VDDRC    | 143        | PWR         |               |             | C Supply      |                                 |                                  |

| LA17     | 144        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA19     | 145        | O-TS        |               | 12          | С             | PD                              | PD                               |

| SA18     | 146        | O-TS        |               | 12          | С             | PD                              | PD                               |

| SA17     | 147        | O-TS        |               | 12          | С             | PD                              | PD                               |

| SA16     | 148        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA15     | 149        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA14     | 150        | Ю           | TTL           | 12          | с             | PD                              | PD                               |

| SA13     | 151        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA12     | 152        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA11     | 153        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA10     | 154        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA9      | 155        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| VSSR     | 156        | GND         |               |             | Ring Gnd      |                                 |                                  |

| SA8      | 157        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA7      | 158        | IO          | TTL           | 12          | С             | PD                              | PD                               |

| SA6      | 159        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA5      | 160        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| SA4      | 161        | Ю           | TTL           | 12          | С             | PD                              | PD                               |

| SA3      | 162        | Ю           | TTL           | 12          | С             | PD                              | PD                               |

| VSSI     | 163        | GND         |               |             | Core Gnd      |                                 |                                  |

| SA2      | 164        | 10          | TTL           | 12          | С             | PD                              | PD                               |

| VDDRC    | 165        | PWR         |               |             | C Supply      |                                 | y an eo bliochtaire<br>A         |

| SA1      | 166        | Ю           | TTL           | 12          | C             | PD                              | PD                               |

| SA0      | 167        | Ю           | TTL           | 12          | С             | PD                              | PD                               |

| AEN      | 168        | O-TS        |               | 12          | С             | PD                              | PD                               |

| RSTDRV   | 169        | O-TS        |               | 12          | С             | PD                              | PD                               |

| SD15     | 170        | 10          | TTL           | 12          | С             | PD                              | PD                               |

# ADVANCE INFORMATION VL82C315A

| Pin Name | Pin<br>No. | Pin<br>Type    | input<br>Type   | Drive<br>mA | Power<br>Rail | Suspend Mode<br>CPU On (Note 9) | Suspend Mode<br>CPU Off (Note 9) |

|----------|------------|----------------|-----------------|-------------|---------------|---------------------------------|----------------------------------|

| SD14     | 171        | ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD13     | 172        | Ю              | TTL             | 12          | с             | PD                              | PD                               |

| SD12     | 173        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD11     | 174        | 10             | ŢŢĹ             | 12          | с             | PD                              | PD                               |

| SD10     | 175        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD9      | 176        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD8      | 177        | IO             | TTL             | 12          | С             | PD                              | PD                               |

| VDDIC    | 178        | PWR            |                 |             | C Core        |                                 |                                  |

| SD7      | 179        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD6      | 180        | 10             | TTL             | 12          | С             | PD                              | PD                               |

| SD5      | 181        | 10             | TTL             | 12          | С             | PD                              | PD                               |

| VSSR     | 182        | GND            |                 |             | Ring Gnd      |                                 |                                  |

| SD4      | 183        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD3      | 184        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD2      | 185        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD1      | 186        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| SD0      | 187        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| -SMEMW   | 188        | O-TS (Note 2)  |                 | 12          | С             | HI-Z                            | HI-Z                             |

| -SMEMR   | 189        | O-TS (Note 2)  |                 | 12          | С             | HI-Z                            | HI-Z                             |

| -IOW     | 190        | IO (Note 2)    | TTL (Note 10)   | 12          | С             | HI-Z                            | HI-Z                             |

| -IOR     | 191        | IO (Note 2)    | TTL (Note 10)   | 12          | С             | HI-Z                            | HI-Z                             |

| -REFRESH | 192        | IO-OD (Note 1) | TTL-S (Note 10) | 12          | С             | HI-Z                            | HI-Z                             |

| SYSCLK   | 193        | O-TS           |                 | 12          | С             | PD                              | PD                               |

| IOCHRDY  | 194        | 10             | TTL (Note 10)   | 12          | С             | PD                              | PD                               |

| -IOCHCK  | 195        | 1              | TTL (Note 10)   |             | С             | PD                              | PD                               |

| VDDRC    | 196        | PWR            |                 |             | C Supply      |                                 |                                  |

| -WS0     | 197        | 1              | TTL (Note 10)   |             | С             | PD                              | PD                               |

| -SBHE    | 198        | Ю              | TTL             | 12          | С             | PD                              | PD                               |

| DRQ3     | 199        | I              | TTL             |             | С             | PD                              | PD                               |

| DRQ2     | 200        |                | TTL             |             | С             | PD                              | PD                               |

| DRQ1     | 201        | 1              | TTL             |             | с             | PD                              | PD                               |

| IRQ9     | 202        | 1              | TTL             |             | С             | PD                              | PD                               |

| IRQ7     | 203        | 1              | TTL             |             | С             | PD                              | PD                               |

| IRQ6     | 204        | 1              | TTL             | 11          | С             | PD                              | PD                               |

## PIN TYPE BY OPERATIONAL STATE (Cont.)

| Pin Name | Pin<br>No. | Pin<br>Type                      | Input<br>Type | Drive<br>mA | Power<br>Rail | Suspend Mode<br>CPU On (Note 9) | Suspend Mode<br>CPU Off (Note 9) |

|----------|------------|----------------------------------|---------------|-------------|---------------|---------------------------------|----------------------------------|

| IRQ5     | 205        |                                  | TTL           |             | С             | PD                              | PD                               |

| IRQ4     | 206        | $[\mathbf{I}_{ij}]$ . So for $j$ | TTL           |             | С             | PD                              | PD                               |

| IRQ3     | 207        |                                  | TTL           |             | С             | PD                              | PD                               |

| VSSR     | 208        | GND                              |               |             | Ring Gnd      |                                 |                                  |

Notes: 1. These pins are normally open-collector signals and require an external pull-up resistor.

2. These pins require an external pull-up resistor (10 k $\Omega$  is recommended).

- 3. These pins are pulled down externally at the processor.

- 4. These pins are pulled up externally at the processor.

- 5. These pins operate during the Suspend Mode. If the VL82C315's core is powered off, they become three-state.

- These pins are normally driven during the Suspend Mode. If the VL82C315's core is powered off, they become three-state.

- 7. The TTL level shifter cell is LSTC15 modified to remain in TTL levels between 2.7 and 5.5 V.

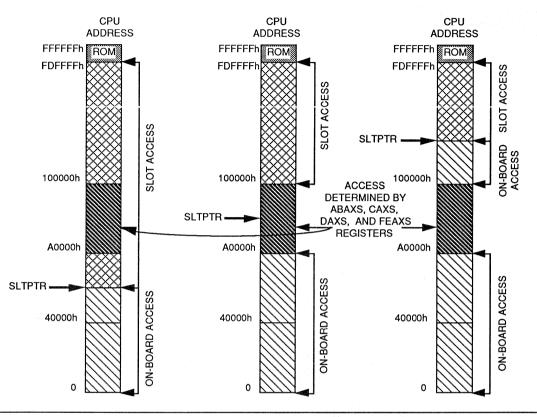

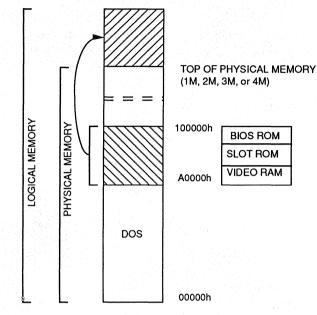

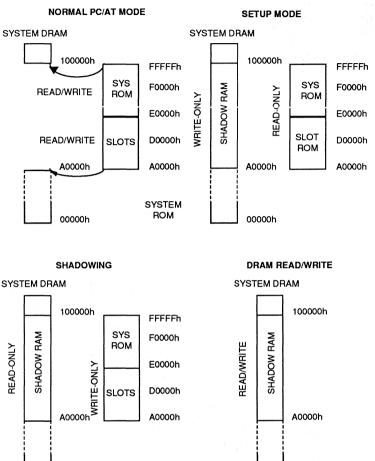

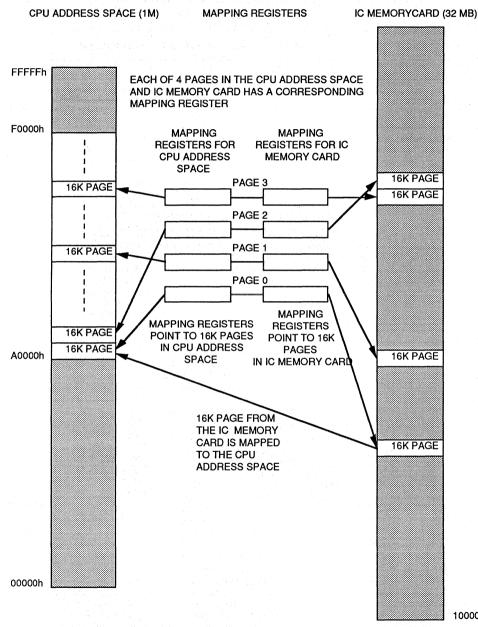

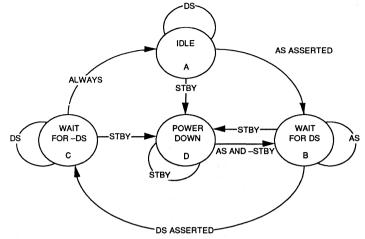

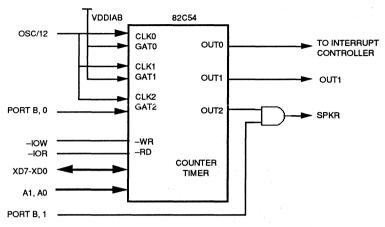

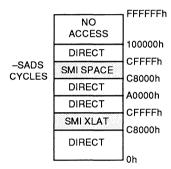

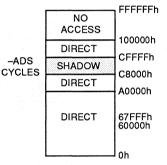

- PD indicates a high-impedance state with approximately 20 kΩ minimum resistance to VSS. A programmable pulldown cell is used on these lines.