## COMPUTER DESIGN

#### TECHNOLOGY FOR **ADVANCED WORKSTATIONS**

## Turn Your *Standard* Personal Computer Into The Ultimate Engineering Workstation.

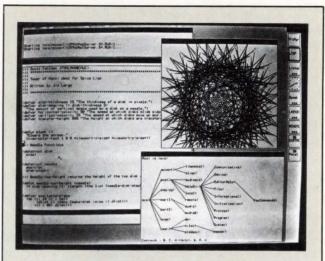

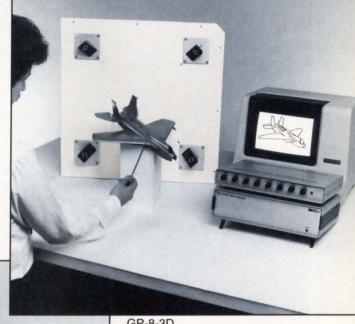

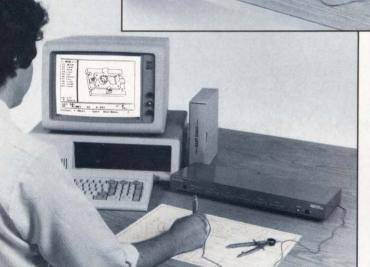

In December of 1983, Case Technology introduced the CT1000 System, a set of professional electronic design programs for the IBM PC. Now, over 300 customers have discovered that the CT1000 has more capability in its front-end design capture than any other competitively-priced system.

The CT1000 offers its users *all* of the general graphics operations such as zoom, pan, rotate, set and copy, associated with sophisticated design systems. However, the capabilities don't end there.

Consider these advanced features:

- Intelligent Rubberbanding

- Closest Point Line Drawing

- Automatic Text Placement

- Automatic Location Labeling

- Smart Signal Naming

- Interactive Component Dragging

- Configurable Menus

- Complete "SCALD" Design Concepts

- Lower Memory Utilization

- Simple ASCII File Interface

And there's much more. Powerful timing verification and logic simulation tools are also available, which, in combination with the CT1000's design capture capabilities, offer the user the *most* cost-effective solution in computer-aided electronic design.

If you haven't discovered the CT1000 system, call or write today for more information. Contact: Case Technology Inc., 633 Menlo Avenue, Menlo Park, California 94025. Tel: (415) 322-4057.

For front-end engineering solutions, see Case Technology first . . . and save both time and money.

### THE PERIPHERAL DESERT

Many tri and tri again — but never make it.

Model 9400 GCR tape system—the latest in a long and honored line of Kennedy products. Products that have always been first in innovation, design, and performance. Model 9400 carries on this tradition of 'first across the line'. For complete details on the industry's premier tri-density, hi-performance tape system, write or call today.

#### KENNEDY

An Allegheny International Company 1600 Shamrock Ave., Monrovia, CA 91016 (818) 357-8831 • ITT TELEX 472-0116 KENNEDY TWX 310-472-0116 KENNEDY

KENNEDY • GUALITY • COUNT ON IT

### **COMPUTER DESIGN®**

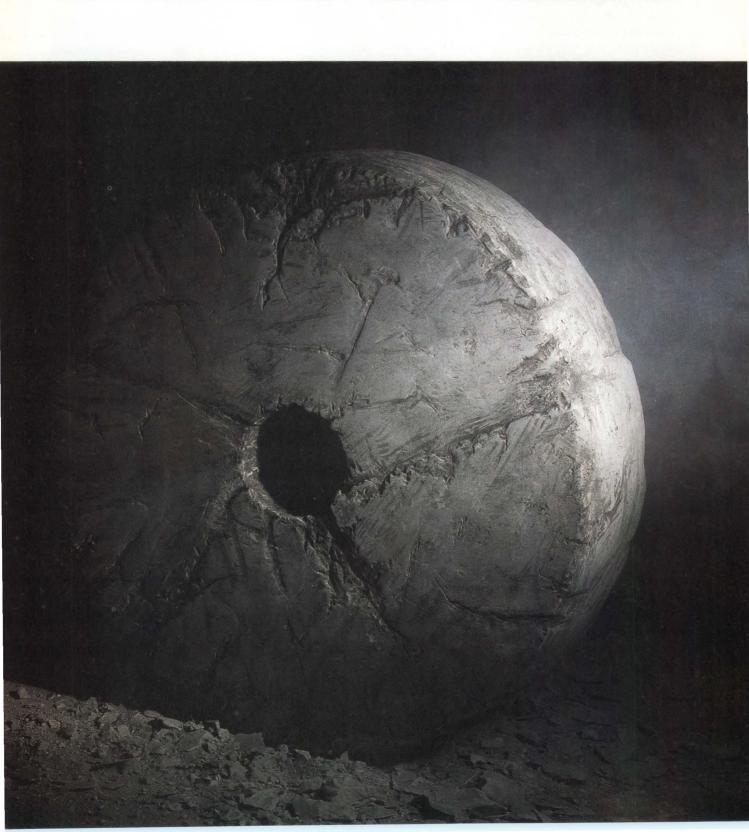

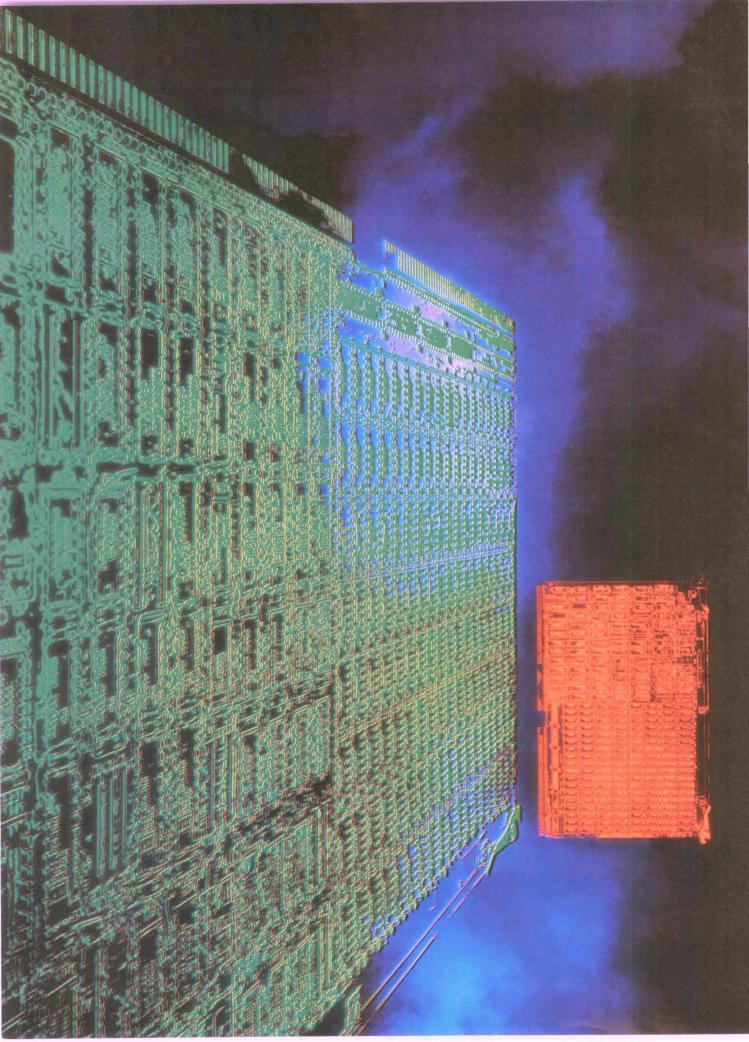

This month's cover was designed and created by Tom McCullough at Coddbarrett Associates, Inc. It was executed using a DICOMED D-38 design station and a D-48 high resolution film recorder.

#### SPECIAL REPORT ON

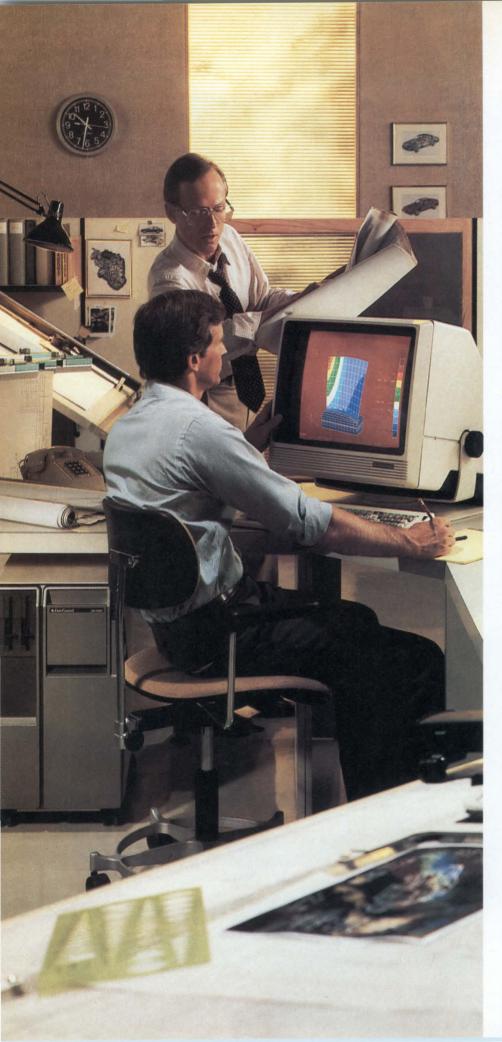

#### TECHNOLOGY FOR ADVANCED WORKSTATIONS

- 109 Workstations are adopting artificial intelligence techniques to improve software development as well as component and system design. For example, symbolic processing software, Lisp environments, and data flow architectures are making their mark. Designers of computer-based systems need to know what these new workstations can do for them. They also need to know how to choose between the new offerings as costs decline and workstations become generally available.

- 111 Revolution brewing in workstation technology New machines sport symbolic processing environments to speed the design process and accommodate the realities of design work.

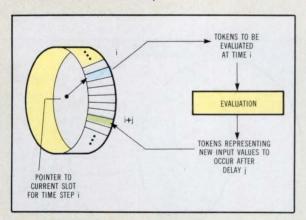

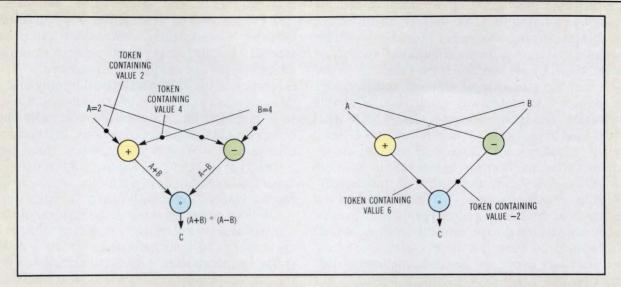

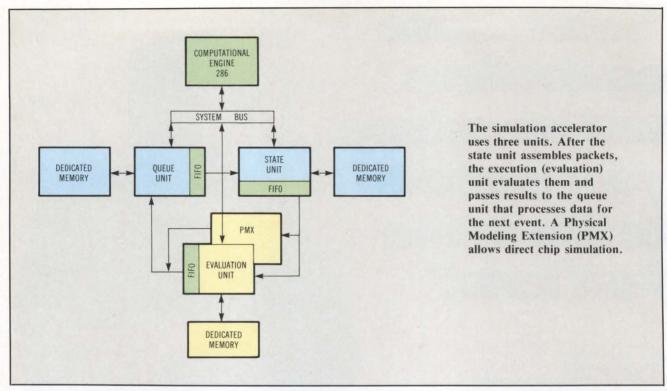

- 131 Data flow concepts speed simulation in CAE systems By exploiting the similarities between a fifth-generation, data-driven system and the so-called discrete-event simulation algorithm, a hardware accelerator can boost simulation speed 100 times.

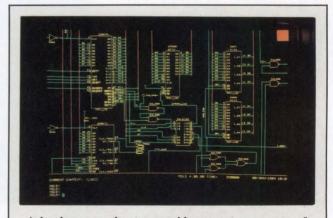

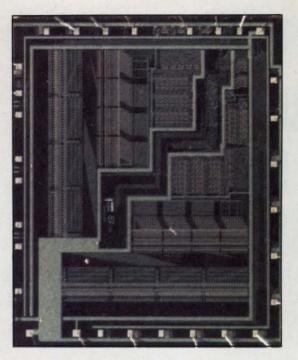

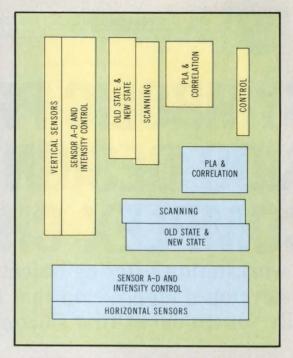

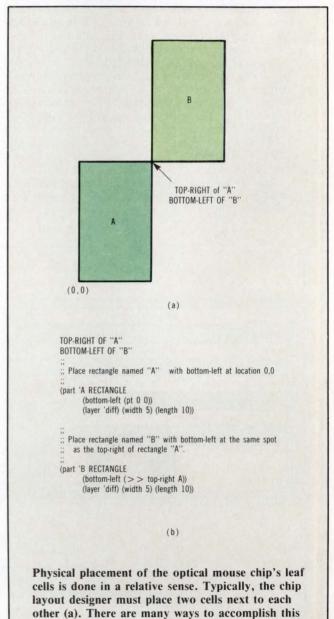

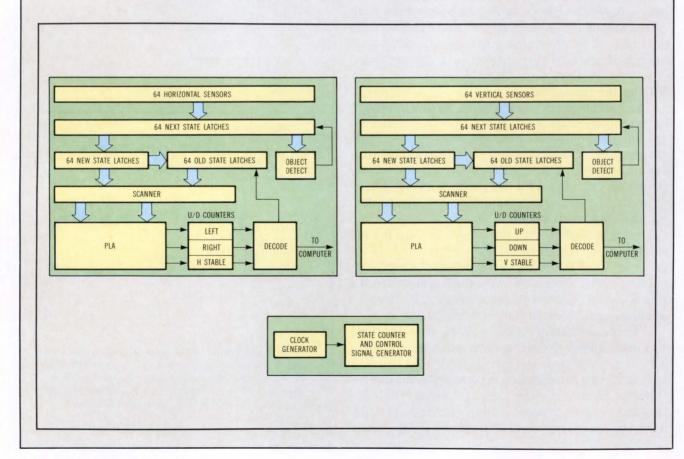

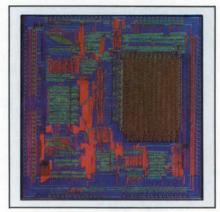

- 147 Symbolic processor aids design of complex chips A workstation offering object oriented programming is used to develop a mouse chip that is testable, reproducible, and fully functional at first silicon.

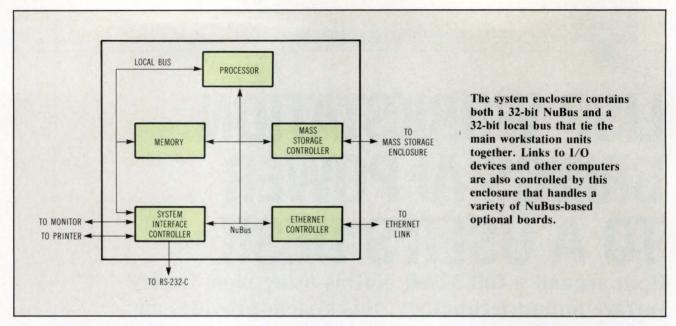

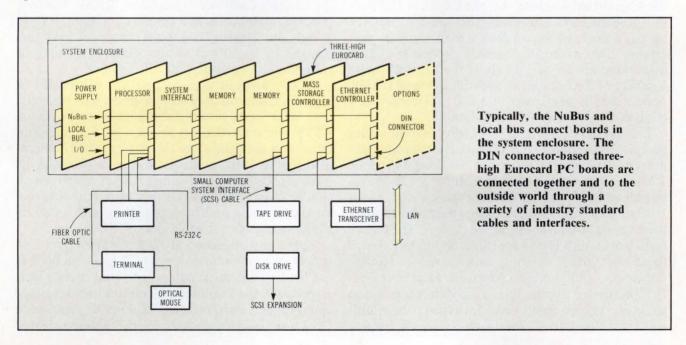

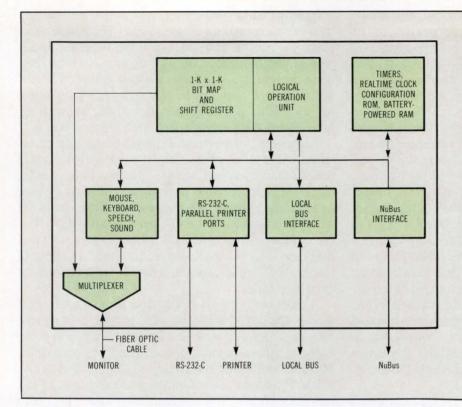

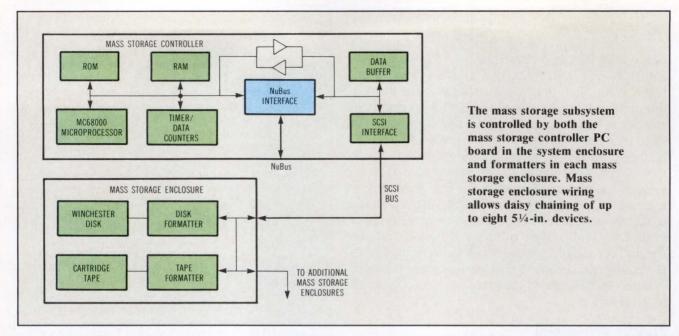

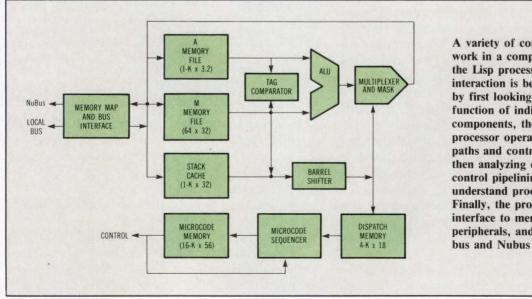

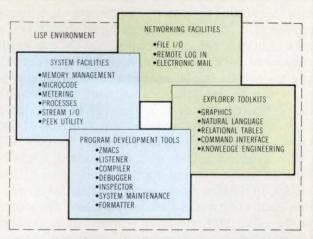

- 155 Lisp workstation brings AI power to a user's desk Built around a full 32-bit NuBus using high density surface mount technology, this system provides an exploratory programming environment in a small ergonomic package.

#### SYSTEM TECHNOLOGY

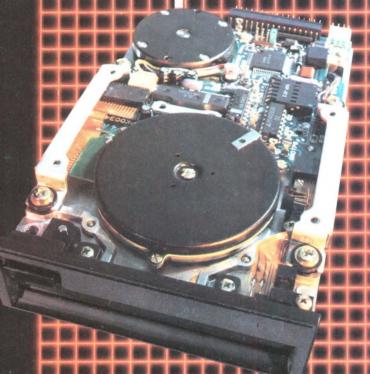

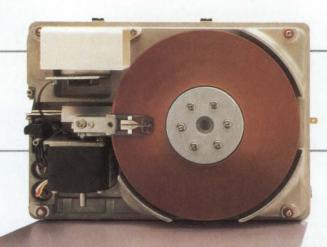

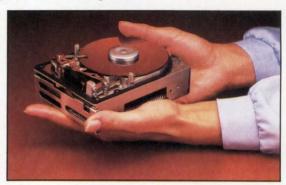

- 29 Memory systems: Shrinkage continues unabated—Winchesters settle in at 3½ in.

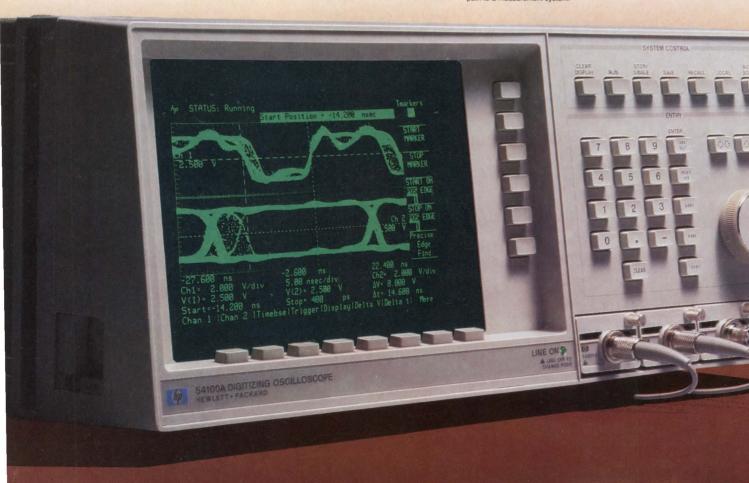

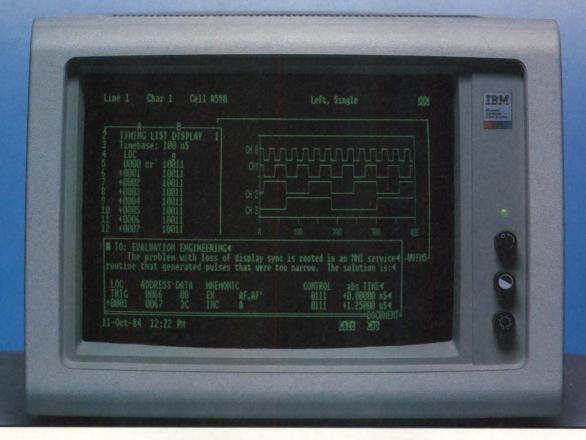

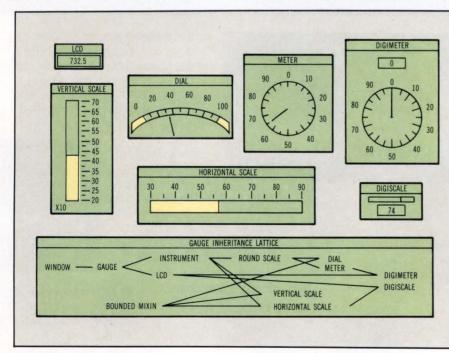

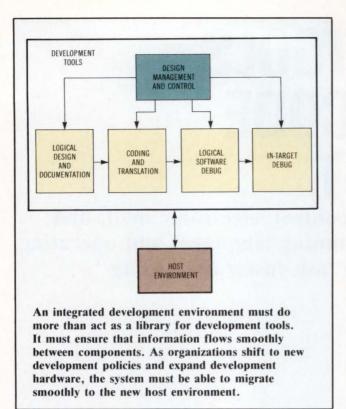

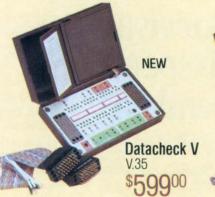

- 40 Test & development: Debugging tools transform CAE environments

- 54 Computers: Integration fuels personal computer hardware advances

- 64 Control & automation: Machine vision technology is coming of age—but it's not here yet

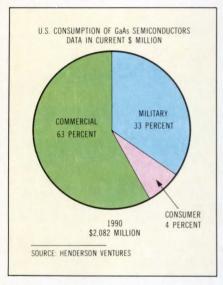

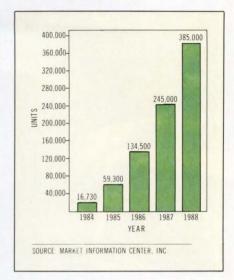

- 72 Integrated circuits: Gallium arsenide technology on the move

- 81 Packaging & power: Surface-mount technology paves the way for smaller boards

- 92 Integrated circuits: Variety, density, and high performance mark ISSCC chip designs

- Computers: Mini/Micro West stands alone

Page 81

#### SYSTEM DESIGN

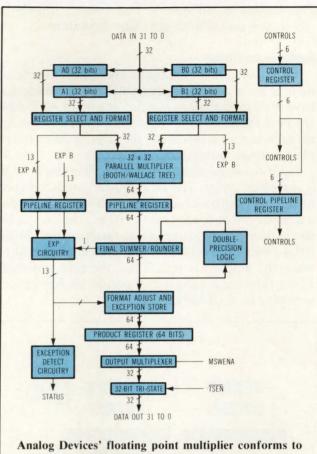

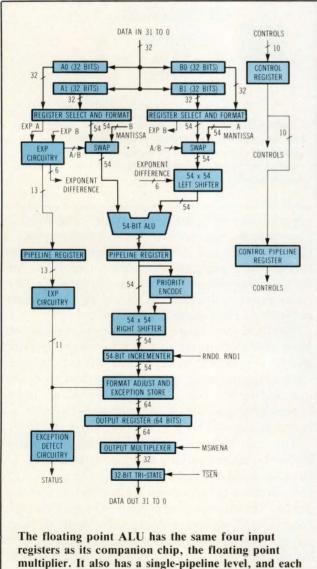

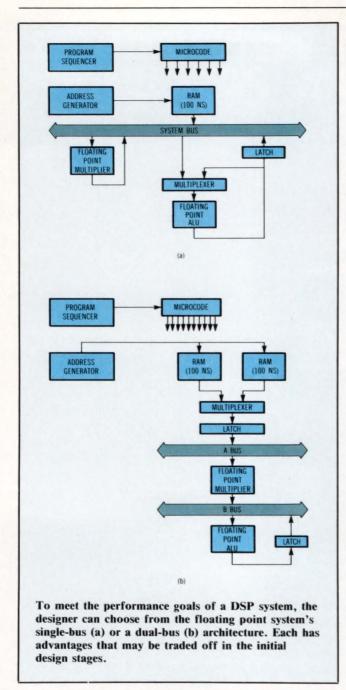

Integrated circuits: IEEE floating point chips implement

DSP architectures

Full compliance with Draft 10 version of the standard allows designers

to produce working systems now.

173 Software: Ada may define new ground rules for programming By providing such benefits as structural constructs, modularity, and concurrent processing, Ada could help set a new standard for programming languages both outside and inside the DoD.

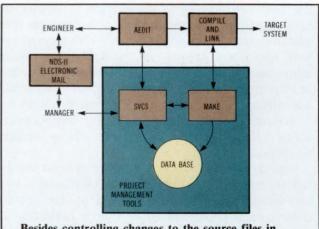

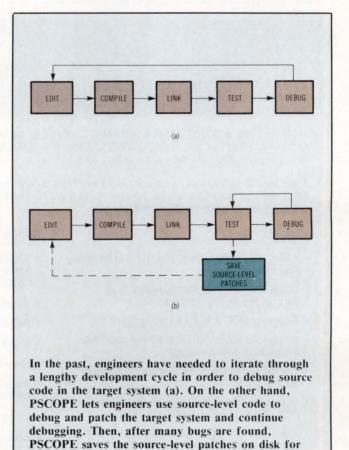

- 179 Test & development: Integrated tools accelerate code development Integrated source and version control, electronic mail, and standard interfaces for programming languages and operating systems can move the software task faster than using additional programmers.

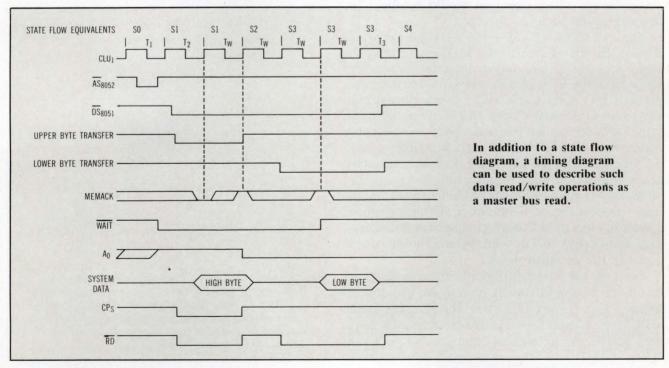

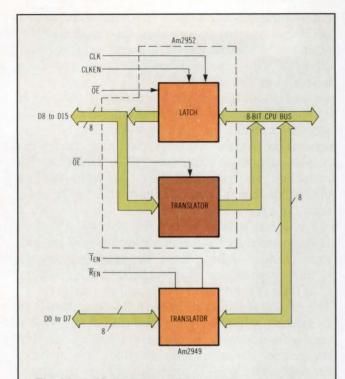

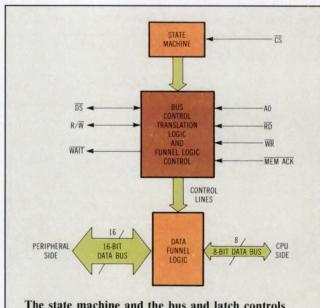

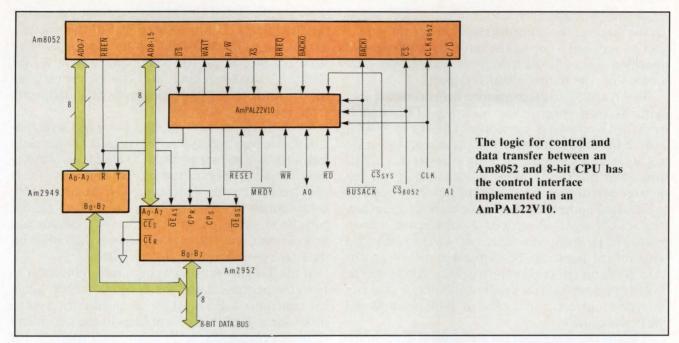

- 187 Integrated circuits: Mixing data paths expands options in system design Chip designers are creating powerful CPUs and peripherals with 16- and 32-bit parts. Combining these with 8-bit parts overcomes limitations imposed by established designs, incomplete families, and software incompatibility.

#### SYSTEM COMPONENTS

Integrated circuits:

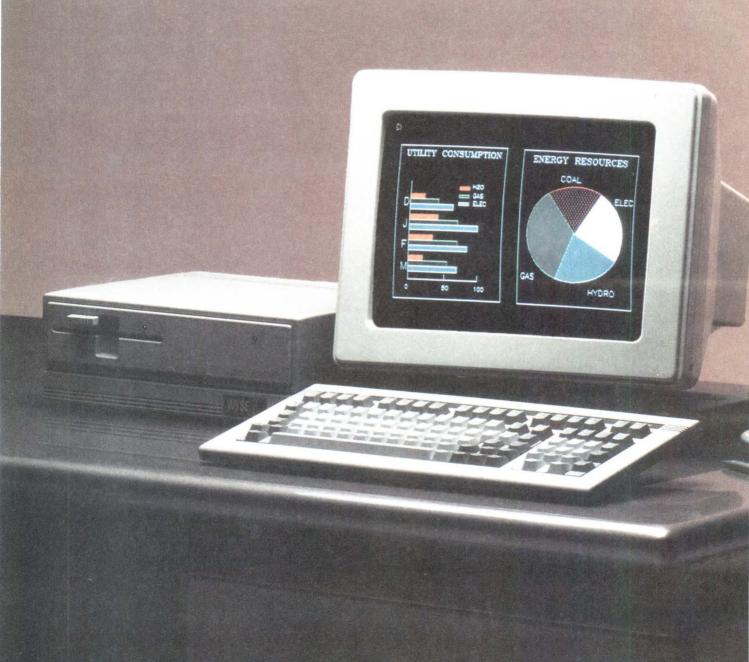

201 Chip set improves floating point performance tenfold

206 A 32-bit VLSI family provides independent building blocks

208 Single-chip image processor sports non-von Neumann architecture

Computers

202 Integral disk and printer mark transportable computer that runs Unix

202 Supercomputer/supermini gap narrowed by 64-bit system

204 Latest VAX delivers performance with large machine technology

Microprocessors/microcomputers:

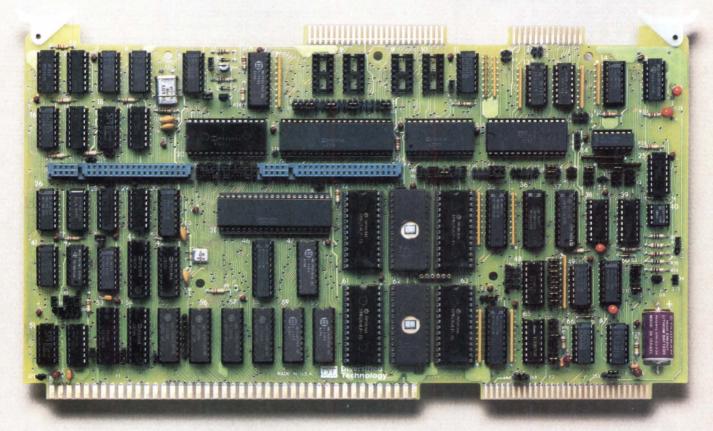

204 Single board holds complete VMEbus system

Peripherals:

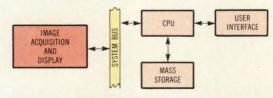

206 Voice recognizer broadens data entry options

Test & development:

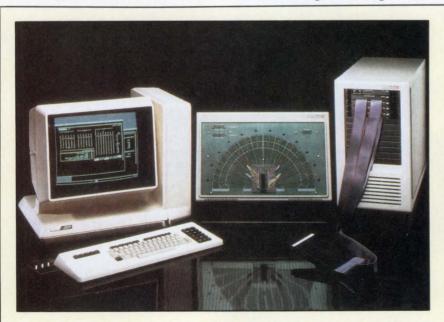

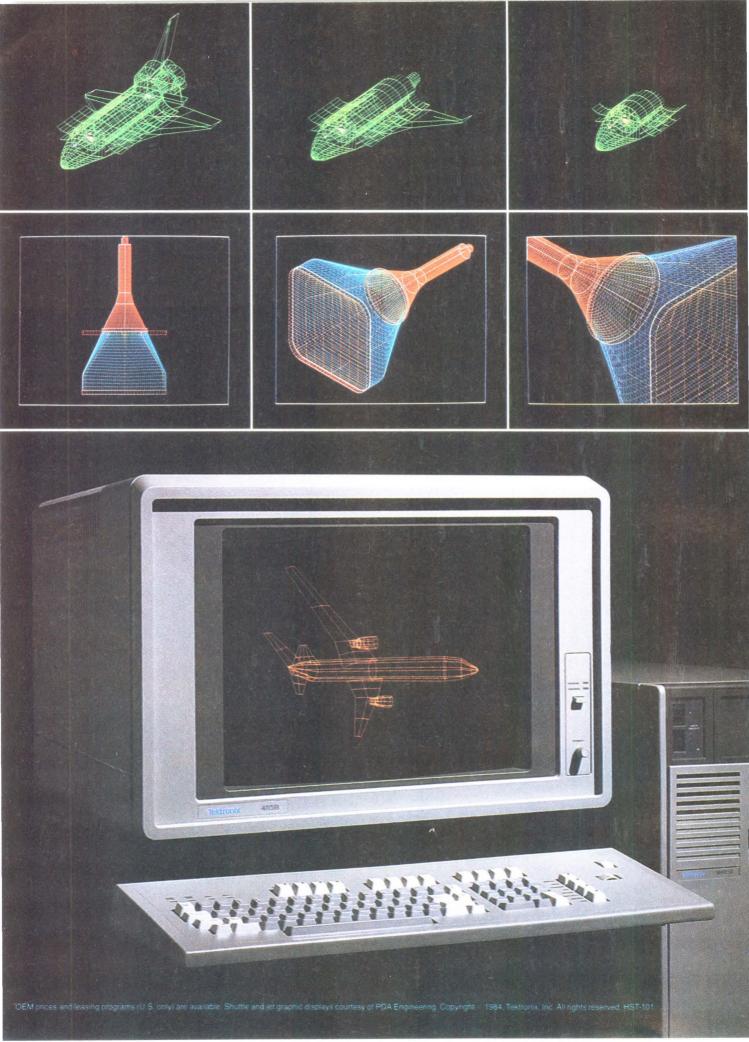

208 Graphics system downloads rendering tasks from the host

210 Diversification and enhancement highlight portable scope family

Memory systems:

210 Micro-Winchester is built tough for the portable world

#### **DEPARTMENTS**

- 5 Up front

- 13 Editorial

- 22 Letters to the editor

- 231 Literature

- 233 Market forecasts

- 237 Calendar

- 238 Designer's bookcase

- 239 System showcase

- 240 Advertisers' index

- 241 Recruitment

- 243 Reader inquiry card

- 243 Change of address card

POSTMASTER: CHANGE OF ADDRESS FORM 3579 to be sent to COMPUTER DESIGN, Circulation Department, P.O. Box 593, Littleton, MA 01460 (UPS 127-340).

#### Microprocessor programming made simple.

"Keep it simple" was the principle of the 14th Century English philosopher William of Occam and it has even more validity today. Faced with the problems of sophisticated computer systems, designers have found that ever more complex programming languages are further complicating their tasks. Until now.

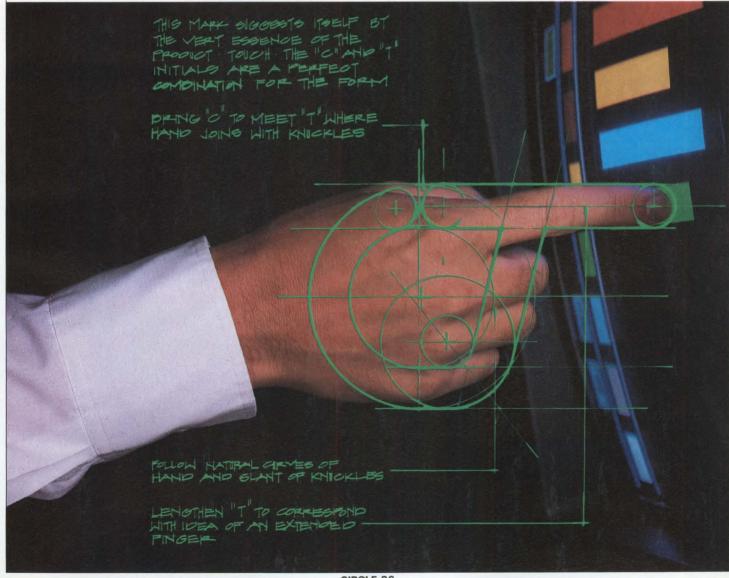

#### Occam. Created for system design and implementation.

When we started designing our new VLSI family of 10-MIP transputers, we built on William's simple philosophy. To take advantage of the possibilities opened up by the transputer, we needed to create a language capable of properly addressing parallelism and multiprocessor systems.

With the ability to describe concurrency (whether timeshared or real) and to handle message-passing at the lowest level of the language, all aspects of a system can be described, designed and implemented in occam. From interrupt handling through signal processing to screen editors to artificial intelligence. And on.

But occam is not limited to our

transputer family. It provides an efficient, responsive implementation language for systems built on today's microprocessors. It also opens up future possibilities with its performance-enhancing multiprocessor capabilities. And INMOS now offers a product to let you exploit occam's total capability in your system.

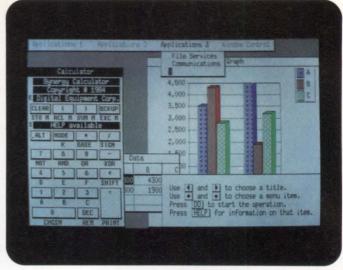

#### Simplify your job with the Occam Programming System.

The Occam Programming System (OPS) gives you the tools for complete VAX / VMS software development. This package includes an integrated editor / checker, an optimizing VAX compiler and full documentation. This gives you a supportive environment for the development of occam programs

for execution on the VAX. Cross-compilers for 68000 and 8086-based systems will also be available.

What's more, the occam programs developed and proven on the OPS will give you a head start for work with the INMOS transputer. Extensions to the OPS will be available which will allow occam programs to run on the transputer.

And if you have a requirement to program the transputer in other popular high-level languages, other extensions will include compilers for C, Fortran, and Pascal.

#### Get started today.

Contact us for our information pack on occam, the Occam Programming System and the transputer. You'll be surprised how simple your life can be.

For quick response, call us at (303) 630-4000 or write: Occam, P.O. Box 16000, Colorado Springs, CO 80935.

inmos, and occam are trademarks of the Inmos Group of Companies

#### **UP FRONT**

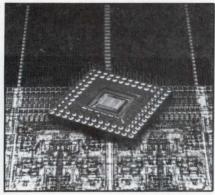

#### Hitachi's 32-bit micro scares Motorola investors

Hitachi, Ltd leaked news of its plans to build a 68000-compatible 32-bit microcomputer at a recent Tokyo technical conference. Although the chip will not be available until 1987, Hitachi's apparent aim to dominate the high end of the microprocessor market sent tremors through the semiconductor industry. Hitachi's Micro 32 now has 300,000 transistors, but the final 1.3-micron technology CMOS chip will contain 420,000 transistors, according to microprocessor marketing manager Sarv Thakur. Tests conducted at Hitachi's Central Research Labs confirm the 32-bit chip will operate at 5 million instructions per second, with a 20-MHz internal clock (40-MHz external clock), according to Thakur. The chip will control a 32-bit bus and will perform full multiply and divide operations on 32-bit data. It includes a pipelined architecture and a high speed cache memory to aid interfacing with I/O processors and other fast peripherals. Eventual packaging is likely to be a leadless chip carrier or a pin-grid array system. As significant as the chip's high performance will be its full upward compatibility with the Motorola 68000. The chip may become 68020-compatible. "We are negotiating with Motorola to license the 68020," says Thakur. However, he is quick to add, "We are talking about a 1987 part. The 68020 really doesn't compete directly with the Micro 32. The 68020 is a step beyond the 68000, but the Micro 32 is several steps beyond." On the day of Hitachi's announcement, Motorola's stock was the most active issue on the New York stock exchange, falling \$1.625. While some of the trading was attributed to Merrill Lynch's reduced earnings estimates for Motorola the same day, many analysts said the Hitachi news contributed heavily. - W.E.S.

#### Realtime operating system runs Unix software

Despite its many benefits as a programming environment, Unix is inherently unsuited for realtime applications. Industrial Programming, Inc of Jericho, NY, promises a solution for software developers who want to develop realtime applications in such fields as machine and process control, signal processing, and image enhancement, yet work within the Unix environment. By the second or third quarter of 1985, Industrial Programming's MTOS-UX operating system will run on the 68000 and the 68010, providing rapid response to external interrupts. Otherwise, it looks like Unix System V to the application software. A 68020 version is in the planning stage.—H.H.

#### IBM-to-VAX links proliferate

IBM products are moving into former Digital Equipment Corp strongholds. At the recent Dexpo West in Anaheim, Calif, a number of companies introduced IBM PC-to-VAX file transfer packages. Among those making it possible to use PCs in the VAX environment were Ross Systems (Palo Alto, Calif), Marc Software International (Palo Alto, Calif), Data Processing Design (Anaheim, Calif), and National Information Systems (Cupertino, Calif). Xyplex of Concord, Mass unveiled a controller that links IBM

(continued on page 6)

#### **UP FRONT**

(continued from page 5)

PCs to VAX/VMS systems over Xyplex's proprietary local area network. "DEC blew it so badly in the personal computer area that hooking up PCs to VAXes has become a major part of the DEC market," one exhibitor who wanted to remain anonymous remarked. Meanwhile, IBM's Engineering and Scientific Support Center in Atlanta, Ga demonstrated links between DEC products and IBM's new 4361 supermini, a VAX competitor. Attempting to make inroads into the VAX market. IBM showed a unit to give its 4361 DEC Unibus compatibility, plus a software package from Flexcomm (Seattle, Wash) to transfer files between the 4361 and the VAX. According to Dick Evans, manager of the Atlanta facility, IBM is telling DEC users, "Keep your [DEC] products, but take a look at ours. Now we can communicate."—R.G.

#### Digital Research may unveil multitasking for 68000

Combined with Digital Research's Macintosh-like Graphics Environment Manager shown at Comdex in November, the Concurrent DOS multitasking operating system appears ideal for system integrators targeting end users with MS-DOS compatible computers. The Concurrent/GEM combination offers MS-DOS compatibility within the 8086 family, a full complement of proven language compilers, and the chance to develop transportable vertical applications. The only missing link at this point is a Concurrent DOS for processors outside the 8088/8086 family. Developers may not have long to wait. Among those seen visiting the Digital Research suite at Comdex was Sam Tramiel, president of Atari Corp of Sunnyvale, Calif. Tramiel has already admitted that Atari's new home computers, expected to battle IBM, Apple, and Commodore for the low end consumer market, will feature the GEM interface. It is believed Atari's new 16-bit machines will use the 68000 microprocessor and cost around \$500. If GEM is indeed running on the 68000, Digital Research of Pacific Grove, Calif will probably announce GEM and Concurrent for the 68000 and possibly the 80286 in the next few months.—W.E.S.

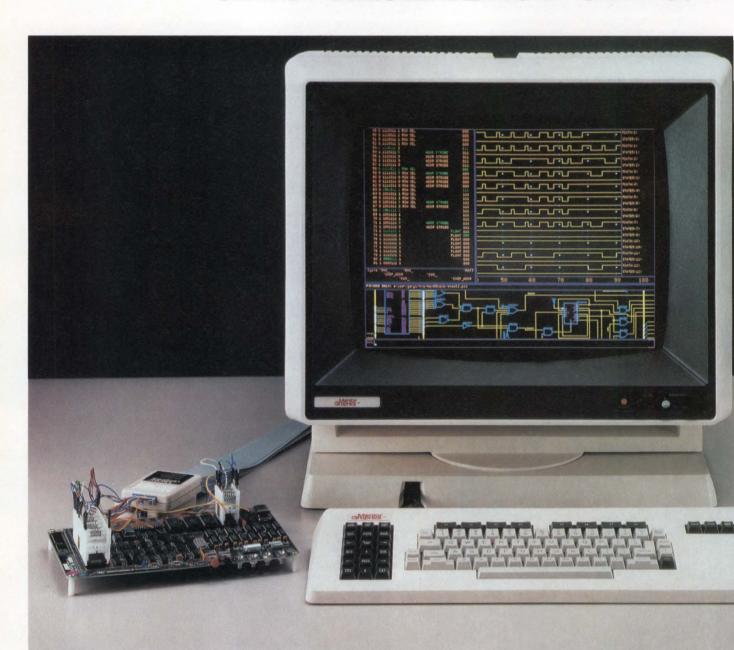

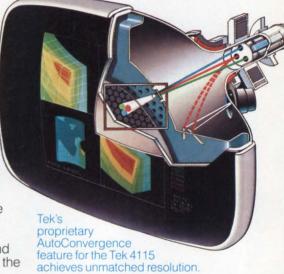

#### Manufacturers back proposal for design data standardization

The Electronic Design Interchange Format, an attempt to standardize the formatting of design data used in computer aided design/computer aided engineering enters the public arena this month with release of the first EDIF specifications. EDIF revision 1.0 proposes a design interchange format for gate array and semicustom ICs. Eventually, EDIF will provide a standard interface for the transfer of design data between silicon foundries, CAD/CAE equipment, and automatic test systems. With active support from Daisy, Mentor Graphics, Tektronix, Motorola, National Semiconductor, and Texas Instruments, EDIF should be off to a good start.—R.G.

#### STC learns perils of surviving in IBM's shadow

The Chapter 11 filing by Storage Technology Corp (Louisville, Colo) and its ensuing financial reorganization demonstrate not only the internal auditing troubles that can bring a high-tech company to its knees, but the danger of following too closely in IBM's footsteps as well. STC manufactures copycat peripherals

(continued on page 8)

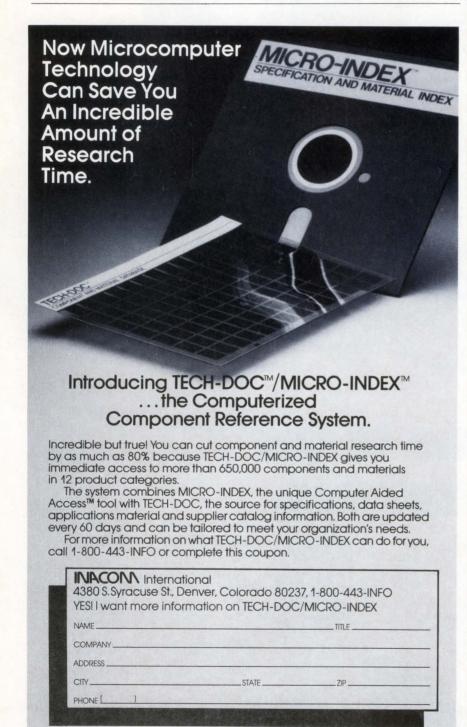

#### Dataram does more with memory

For nearly two decades, Dataram has been leading the way in memory technology, supplying more memory than any other company to leading minicomputer manufacturers, end users, systems houses, OEMs and others throughout the world.

Experience that translates into superior design and reliable performance for you today. That means more for you — more capacity, more capability, more reliability, and more performance with more savings...so you can get more from your minicomputer.

Want to learn more? Contact Dataram at (609) 799-0071 today.

#### for VAX users

- VAX-11/780 Series Compatible

- 4.0 MB with ECC on a Single Hex Board

- System Expansion to 32 MB in a Single Cabinet

- Socketed DRAMs

- Spare DRAM on Board

- VAX-11/750, 11/730, and 11/725 Compatible

- 1.0 MB with ECC on Single Hex Board

- Maximum System Expansion to 8.0 MB on VAX-11/750

- On-Board Memory Select and Power-On Status Indicators

Dataram Corporation ☐ Princeton Road ☐ Cranbury, New Jersey 08512 ☐ (609) 799-0071 ☐ TWX: 510-685-2542

#### **UP FRONT**

(continued from page 6)

for IBM mainframes. Its problems began with production of the 2.5-Gbyte 8380 disk drive, the highest-capacity drive STC sells. "We didn't have the thin-film head technology in place until late 1983." explains corporate communications vice president Gordon Swartzfager. But, IBM already had a stranglehold on customer orders for 8380s by the time STC made it to market. Then, in September, IBM cut prices 10 percent. In its rush to get orders, Storage Technology discounted heavily; when sales figures for the quarter ending September 30 were tallied, STC faced a \$60 million loss. The situation holds its share of irony. STC recently received a \$10 million order from IBM itself. IBM has been having trouble stocking parts for one of its small tape drive controllers, which STC also sells. So IBM is ordering the tape drive systems from STC until it can catch up with the demand. According to one industry consultant, STC shipped half the 11,500 tape drives sold last year—several times as many as IBM.-W.E.S.

#### Floppy disk drive makers are flipping

Hard times have hit floppy disk drive makers, and it's not just the trend toward hard disks. Slowed personal computer sales and increased competition have manufacturers spinning their wheels. Among those hurt, Seagate Technology (Scotts Valley, Calif) reported sales for the quarter ending Sept 30, 1984 were roughly half those of the previous quarter. Miniscribe Corp (Longmont, Colo) reported a third-quarter loss of \$2.5 million after netting \$1.4 million a year earlier. The bad news doesn't stop there. Other manufacturers of drives or media with sliding third-quarter sales and earnings include Tandon (Chatsworth, Calif), Verbatim (Sunnyvale, Calif), and Dysan (Santa Clara, Calif). The storage company with the most exciting revenue increases (338 percent increase from third-quarter 1983 to third-quarter 1984) doesn't even sell conventional media. That's Iomega Corp (Ogden, Utah), makers of the Bernoulli Box. Of course, there's good news for purchasers of disk drives—the predicted disk drive shakeout should pull prices down faster than a disk head crash.—W.E.S.

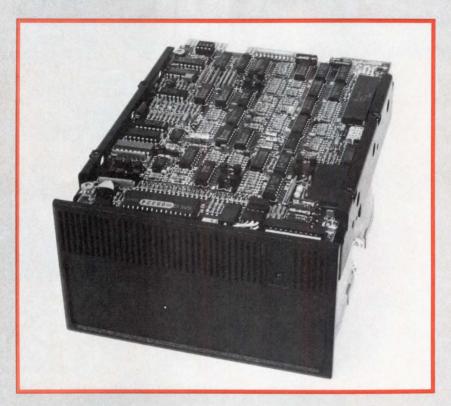

#### Transputer nears readiness

Inmos Corp, which announced its Occam parallel programming language about two years ago and promised a silicon transputer by the fourth quarter of 1984, is on schedule. Inmos has the T424 processor in silicon and is working on final masking. First samples of the chip will be released on a Eurocard evaluation board around the middle of the year. Individual chips should follow in the second half. Meanwhile, true believers can begin developing software for the device on a VAX using the Inmos Occam Programming System for the VAX/VMS.—W.E.S.

COMPUTER DESIGN © 1984 (ISSN-0010-4566) is published monthly, with a thirteenth and fourteenth issue respectively in June and October by PennWell Publishing Company, Advanced Technology Group, 119 Russell St., Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$60 in U.S.A. and \$85 elswhere. Single copy price is \$6.00 in U.S.A. and \$8.50 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Road, Ann Arbor, Michigan 48106. Officers of PennWell Publishing company, 1421 S. Sheridan, Tulsa, OK 74101; P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Senior Vice President; H. Mason Fackert, Group Vice President; Carl J. Lawrence, Group Vice President; V. John Maney, Vice President/Finance; L. John Ford, Vice President.

COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501.

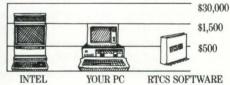

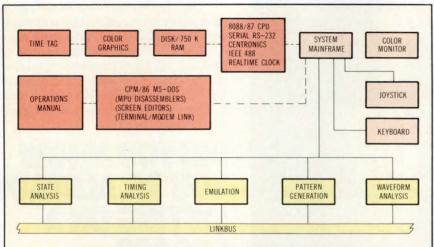

### INTELLIGENT LIFE

Discover the intelligent alternative to high-priced microprocessor development systems with ZAX professional development equipment. ZAX development systems feature powerful in-circuit emulators that are both microprocessor inclusive and PC compatible. The result: Flexible systems that can manage your most far-reaching design

ZAX CORPORATION

projects, while still keeping your budget firmly on the ground.

Your Leader in Microprocessor Development Systems.

To find out more about the intelligent development systems from

Zax Corporation 2572 White Road. Irvine. California 92714 (714) 474-1170 • 800-421-0982 • ILX 183829

ZAX, call 800-421-0982 \* 714-474-1170 today.

CIRCLE 5

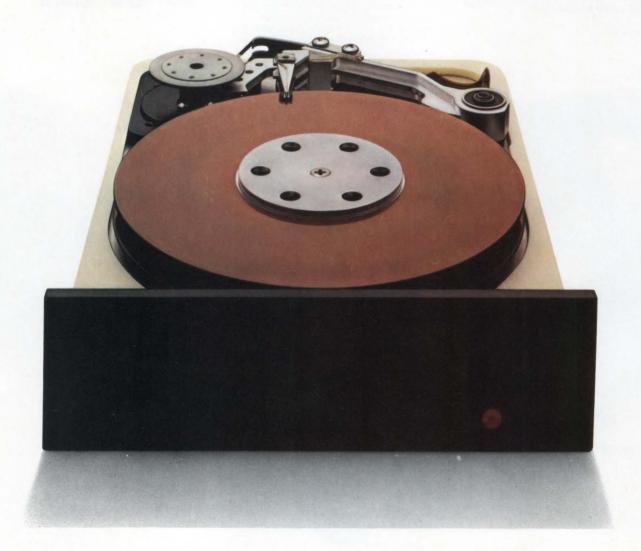

# WHEN IT COMES TO WINCHESTERS, WE RUN CIRCLES AROUND THE COMPETITION.

Tandon's made so many improvements in Winchesters that the rest of

the drive industry is dizzy just trying to keep up.

We build a wide range of drives. Open-loop and high performance closed-loop models. In both full and half-height versions ranging from 12.8 to 36.2MB unformatted capacities.

All are available in high quantities now, because Tandon's been ramping up capacities at a pace like never before. And we've kept up the pace of improving Winchester performance as well, so the most advanced technology is ready when you need it.

As far as our current line is concerned, the low-cost TM500 line has become the most reliable full-height 12.8 and 19.1MB drives you can get. The

new TM252 half-height 12.8MB surpasses the industry's most critical specifications. And our TM703 has been increased to 36.2MB to make it the ideal high capacity drive for desktop business systems.

Another part of our success revolves around our highly automated plated media plant in Northern California. Its buttoned-down efficiency and technological sophistication guarantee higher quality and higher volume production than ever.

What's more, our proprietary plated media is used in all our Winchesters, no matter what the capacity. It's more durable, more reliable. And it has six times more storage capacity than oxide media. At less than half the cost.

In fact, it's so good, other drive manufacturers are buying their plated media from us.

So all around, Tandon Winchesters have more capacity in less space at less cost.

And that's a pretty good circle to run around in.

## THE DRIVING FORCE BEHIND THE SMALL COMPUTER INDUSTRY.

Tandon Corporation, 20320 Prairie, Chatsworth, CA 91311. (818) 993-6644, TWX: 910-494-1721, Telex: 194794. Regional Sales Offices: Boston (603) 888-8612 • New York (201) 851-2322 • Atlanta (404) 934-0620 • Chicago (312) 530-7401 • Dallas (214) 423-6260 • Irvine (714) 669-9622 • Santa Clara (408) 727-4545 • Kelsterback/Frankfurt, West Germany 6107-2091, Telex: 411547 • Reading/London, England (0734) 664-676, Telex: 848411. Distributors: Hall-Mark, Kierulff, Schweber.

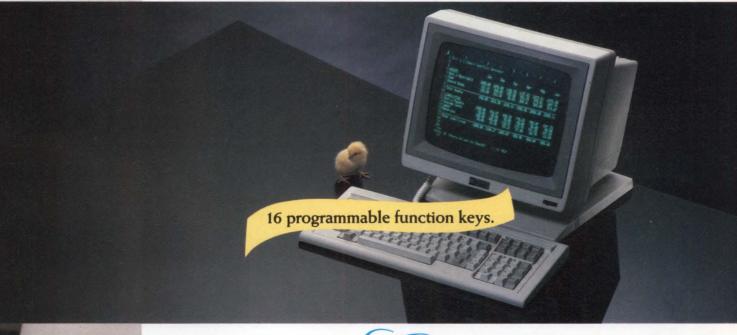

#### **M**HITACHI

- $= 1280 \times 1024$

- Resolution

- 60Hz, Noninterlace

- 100 MHz Bandwidth

- Compact, modular design

HM 4619

#### (1) HITACHI

- 1280 × 1024 Resolution

- 30Hz, interlaced

- 45MHz Bandwidth

- 0.1/0.3 mm

12 SERENGER ALEKT AND SERENGER A MENTER TO A SERENGER TE HM 3619/

#### (1) HITACHI

- 1024 × 1024 Resolution

- 40 MHz Bandwidth

- Compact

NEW

HM 3719

#### (1) HITACHI

- 640 × 512 Resolution

- 25 MHz Bandwidth

HM 2719

## **©**HITACH

Bridges The Gap In OEM RGB Color Monitors

THAT A STATE

The world of computer graphics is moving at incredible speed. Software advances dictate hardware advances; new applications demand new engineering specifications. "Limited standards" don't always fit the need.

Hitachi is the totally integrated OEM source. Our complete range of RGB Color Monitors provide a very wide selection of power, resolution, size and price. More important, we can and do modify specifications to meet highly specialized individual OEM requirements.

Best of all, our "standard" monitors and our "not so standard" monitors all reflect clearly the world renowned Hitachi technology and our dedication to design excellence

HITACHI.....the image speaks for itself.

The Image Speaks For Itself.

1.78.7 .. 4 .. 7

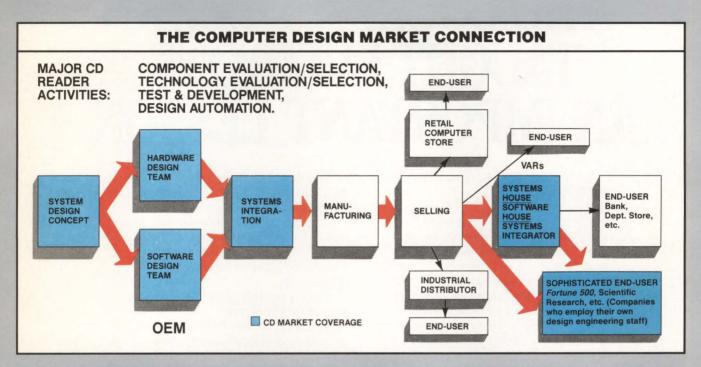

#### THE VAR AND OTHER GOBBLEDYGOOK

More than any other industry, it seems, the computer business is afflicted by too many acronyms and abbreviations. Originally intended to simplify and speed communication, all this jargon more often causes confusion and impedes the flow of information. Though some trade publications could have helped to reinforce a standardized terminology, they have merely added to the confusion by proliferating ambiguous acronyms. As an editor this saddens me; as an engineer it really annoys me.

The confusion has escalated to the point where, even within the computer industry, some abbreviations have at least two entirely different meanings. Consider, for example, PCB, µC, VAR, and PC.

Depending on which story you read in which publication, PCBs might be printed circuit boards or polychlorinated biphenyls. This gets even more confusing when the polychlorinated biphenyl is a solvent for cleaning a printed circuit board—in other words, you have a PCB degreasing a PCB. As a journalist, I can understand the pressure on headline writers to abbreviate. But the acronym PCB in computer publication headlines is about as confusing and frustrating as the use of "Giants" in a sports headline (when the story could be about the San Francisco baseball Giants or the New York football Giants).

While the acronym PCB may have originated with overzealous headline writers, I believe the magazines that promoted the new µC and VAR acronyms did so deliberately. Those magazines compete with Computer Design to some extent; therefore, our editors and readers must grapple with the confusion other magazines helped to create.

The first heavy use of  $\mu C$  to mean microcomputer occurred in a magazine that somewhat immodestly describes itself as "everything designers need" (a slogan that helps us forget its initials originally stood for Electrical Design News). To put itself on the map as a microprocessor and microcomputer journal, it adopted such eve-catching abbreviations as  $\mu P$  and  $\mu C$ . The main problem with that, of course, is that μC and μP were already standard abbreviations (with  $\mu$ C meaning microcoulomb). Fortunately, most other design magazines either refused to use the  $\mu$ C and µP acronyms, or have reversed their earlier decisions to use them.

Now let's look at the VAR. When I first studied electrical engineering, a VAR was a clearly defined electrical unit. The initials stood for volt ampere reactive. Today,

however, the initials have a vastly different meaning within the computer industry. Depending on who uses the term, a VAR can be a value added reseller, value added remarketer, or value added retailer.

According to another competing magazine that calls itself "the trade journal of the value added marketplace," VARs are system houses, consultants, computer distributors/dealers, and third-

party system integrators. Recently, VARs have become increasingly attractive to companies selling hardware and software because VARs buy products for resale into vertical end-user markets. Note, however, that a VAR is not a clearly defined occupation (such as engineering management) but a rather amorphously defined group of organizations. Note, also, that most of those types of organizations employ engineers (such as readers of Computer Design) and that the engineers are responsible for any real value added to systems built by those organizations. Why then does the "trade journal of the value added marketplace" define the concept so vaguely? My theory is that its editors are forced to do so because the readership of the magazine itself is vaguely defined. The lack of clarity allows them to avoid explaining who adds value and who merely adds cost.

Before closing, I would like to nominate PC as the most confusing abbreviation of all time. In a computer publication, PC could stand for printed circuit, personal computer, professional computer, programmable controller, program counter, or professional communication. For the creation of that particular monster, we must all accept part of the responsibility. Even at Computer Design, I must confess, we have sometimes used it without defining it.

mulal Elephia

Michael S. Elphick Editor in Chief

## 256K DRAMS IN CHMOS. THERE HAVE BEEN OTHER INNOVATIONS AS IMPORTANT.

But not lately. Intel's 256K DRAM in CHMOS will set new industry standards. Redefine high performance. And change the direction of VLSI technology.

Our revolutionary new chip provides four times the storage capacity, a high data bandwidth

mode and a drastically lower power consumption than NMOS DRAMs.

It combines the best benefits of CMOS static

RAMs, low power and high bandwidth, with the traditional high density and cost effectiveness of DRAMs.

Making the 256K CHMOS DRAM the perfect building block to a smaller, faster, low-power portable system with the same

The bigb performance advantage.

For a typical LKx1K display.

High performance

MOS better than two to one. high performance

as a desktop.

For the first time, you can design your truly portable system to run the most powerful spreadsheet software on the market. Without costly CMOS SRAMs. Even workstation processing

is possible in a portable.

High speed. High bandwidth. Onetwentieth the standby power requirement of NMOS DRAMs. Intel offers an entire family of 256K and 64K DRAMs in The low power advantage: Intel's CHMOS Dynamic RAMs require only 5% of conventional NMOS. CHMOS. The breakthrough combination of our own high performance technology, HMOS, with the low power advantages of CMOS.

On the performance side, high data bandwidth is the result of two new

methods of data access. Both Ripplemode™ and Static column mode provide the ability to randomly read or write

> any series of bits within a single row at a minimum cycle time of 65ns. This incredible speed makes the **CHMOS DRAM** NMOS family the ideal solution for graphics, array processors and other high speed

digital signal processing

applications.

51C256H

In addition, their resistance to soft errors provides the extremely high reliability critical to medical instrumentation, financial transaction sys-

> tems and other failsafe applications.

Low power. High density. Unbeatable performance. Available now for your system design.

Call Intel today, toll-free at (800) 538-1876. In California, (800)

672-1833.

NMO!

Because there have been innovations as important. But none as important to you.

© 1984 Intel Corporation

Teamwork is making a comeback in America. Cooperation on the production line helped America win World War II. We're in another kind of battle today — a fight for economic survival in an increasingly competitive world market. Cooperation in the workplace is helping us meet this challenge too.

In plants and offices throughout the country, management is asking employees for their ideas on how to increase productivity and improve the work environment. And workers and their unions are responding with a wealth of practical suggestions and a renewed spirit of cooperation.

For information about how others are working better by working together, contact:

Cooperative Labor-Management Programs U.S. Department of Labor Washington, D.C. 20216 202-523-6098

#### U.S. Department of Labor

Printed by this publication as a public service Photograph: Lange Collection, Oakland Museum

#### **COMPUTER DESIGN**

Editorial/Executive Offices: The PennWell Building, Littleton, MA 01460, Tel: (617) 486-9501

Editor in Chief, Michael S. Elphick

Executive Editor, John Miklosz Managing Editor, Sydney F. Shapiro Assistant Managing Editor. Leslie Ann Wheeler Senior Editor, John Bond

Senior Editor, Peg Killmon

Senior Editor, William E. Suydam, Jr. Special Features Editor, James W. Hughes

Senior Associate Editor. Malinda E. Banash

Associate Editor, Jack Vaughan Art Director, Emilie Whitcomb Copy Editors.

Helen McElwee, Nancy E. Purcell, Leah A. Rappaport, Ann Marie Tisevich Editorial Assistants, Vickie Frechette.

Susan M. Wheatley New York Field Office: 120 Mineola Blvd, Suite 510, Mineola, NY 11501, Tel: (516) 741-4780 Senior Editor, Nicolas Mokhoff Tel: (718) 886-4242

Special Features Editor, Harvey J. Hindin Western Field Office: 540 Weddell Dr, Suite 8 Sunnyvale, CA 94089, Tel: (408) 745-0715

West Coast Managing Editor, Tom Williams

Senior Editor, Bill W. Furlow Field Editor, Richard Goering

Production Director, Linda M. Wright Production Manager, Philip Korn Production Assistant, Elizabeth Mogren Staff Artist, Jay Gordon Technical Art, Designline Ad Traffic Coordinator, Debra L. Stone Printing Services, Padraic Wagoner

National Sales Manager. Frederick A. Stanley Circulation Director, Robert P. Dromgoole Business Development Manager, Leslie Ringe Promotion Director, Steve Fedor Marketing Services Coordinator, Linda J. Battle

Publisher, Frederic H. Landmann

#### **DennWell**

Advanced Technology Group 119 Russell St, Littleton, MA 01460 Tel: (617) 486-9501

H. Mason Fackert, Group Vice President Daniel R. Campbell,

Vice President Adminstration Kirk S. Campbell, Finance Director John M. Abernathy, MIS/DP Director Saul B. Dinman, Editorial Director Patricia M. Armstrong, Administrative Services Manager

#### Introducing CalComp's new electrostatic plotters.

CalComp 5700 Series electrostatic plotters deliver dry hardcopy faster and more economically than any other electrostatic. Running at the industry's highest paper throughput speeds—up to 2.0 inches per second—they turn out more plots per day, more plots per dollar.

As you'd expect from CalComp, you get the best price/performance possible. For less than you'd expect, you get plots with 400 or 200-dpi resolution. And when it comes to accuracy, the 5700 Series can't be beat. With 0.1% vertical and horizontal accuracy, you can count on your drawings to be exactly right. Overlay

registration is excellent.

Another advantage of the 5700 Series is the unique CalComp Enviroclean™ toning system. It automatically recycles toner to keep plots and the environment clean. You save

on supplies since there's no waste.

With CalComp 5700 Series electrostatic plotters, there's no need to compromise productivity, image quality, or your budget. And a choice of four models assures a precise match with your needs.

Discover how CalComp's electrostatic plotters can do more work and cost you less. Call toll-free today, 1-800-CALCOMP, ext. 156, or write CalComp, 2411 W. La Palma Ave., P.O. Box 3250, Anaheim, CA 92803.

CIRCLE 9

## "Standard cells have but I need to

## many advantages, justify the cost." With Texas Instruments, you can.

At a very early stage, you'll know what your standard-cell ICs from TI will cost. And you can depend on that estimate because TI commits to it.

TI's Standard-cell Design System is TTL based. That means we can quickly, easily, and accurately translate your TTL logic requirements into equivalent standard-cell functions to arrive at reliable cost figures.

In so doing, we will determine the chip size and the number of I/Os—major factors affecting costs. We will evaluate the advantages of various partitioning schemes and take into consideration packaging options.

TI will detail nonrecurring engineering costs—what it will take to get you prototypes—as well as recurring, or production, costs. We will tell you where these costs will occur and why they will occur. We will also suggest ways to keep them to a minimum. The result: No surprises along the line.

And in assessing the feasibility of TI's 3-µm CMOS standard-cell technology for your logic, we may recommend TI's comprehensive gate-array family as the most economical alternative for you.

Count on

significant system savings

Major improvements in system performance, reliability, and power consumption alone often justify the cost of standard-cell ICs.

In addition, there are more tangible system savings you can count on. One standard-cell IC can replace hundreds of individually packaged chips. Your system parts count is dramatically reduced. Printed-wiring boards can be fewer and smaller. Inventory and assembly costs are cut.

TTL design rules save time

Familiar TTL design techniques are used in the design of your TI standard-cell ICs. Actually, the process is very similar to breadboarding with standard TTL logic packages. Which means you

don't have to invest time and effort in learning new rules.

TI's standard-cell library contains all the popular SN54/74 functions you've worked with over the years. Plus RAM, ROM, PLA, ALU, and linear functions. As well as design-for-test cells that ensure thorough design testability.

You can draw your schematic or generate it via an engineering work station. Tl's standard-cell library is supported on such third-party work stations as Mentor, Daisy, and Valid and on several PC systems. Tl will provide the translation software for automatic generation of the Tl design-description language.

TI Regional Technology Centers can add to your savings

You can hold costs down by performing much of the initial design work yourself. For example: Schematic capture, simulation, testability analysis, test-pattern generation, and the test-pattern grading required to finalize your standard-cell design. You can also perform the chip layout, or leave that to us.

You'll find these steps progressively easier as you execute subsequent stan-

dard-cell designs, but the first time you will probably need assistance.

That's where TI's convenient Regional Technology Centers come in. Strategically located throughout the country, they are staffed with standard-cell specialists who will provide whatever advice and counsel you need. Each Center has engineering work stations for your use plus the software tools and the computers necessary to complete your logic design. In short, the Centers are a reliable time- and money-saving design resource.

Our results pay off

A number of simulation and testability steps are built into TI's standard-cell design flow. These checks and double-checks are vital to fulfilling our commitment to deliver prototypes that perform to your specifications. They help us achieve our goal of first-pass success, so you are spared any second-pass expenses.

Typically within 8 to 12 weeks after the initial design, you will receive prototypes for your in-system evaluation. You give us your okay; we produce

and deliver in quantity.

#### Call 1-800-232-3200, Ext. 120

To find out more about the performance improvements and the economies that justify TI's standard-cell ICs, get our brochure, pocket selection guide, sample data sheets, and a more detailed description of the design process. Call the telephone number given above or circle the Reader Service Card number. Or write Texas Instruments Incorporated, Dept. SRSØ33OS, P.O. Box 809066, Dallas, Texas 75380-9066.

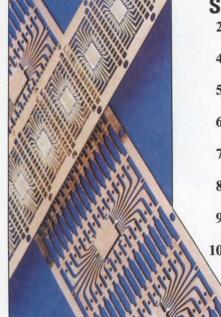

Breadboard on a chip: All the logic packages you might ordinarily put on a printed-wiring board could be functionally contained in a single standard-cell IC to achieve dramatic system cost savings.

#### TEXAS INSTRUMENTS

Creating useful products and services for you.

27-4981 ©1984 TI

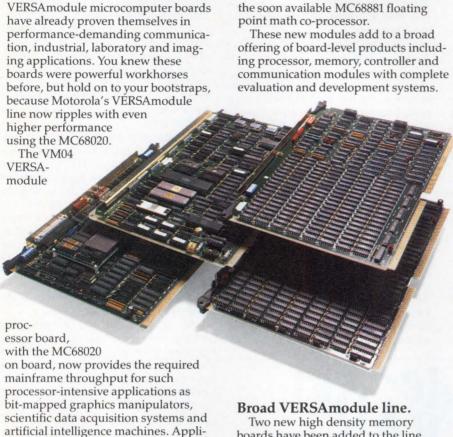

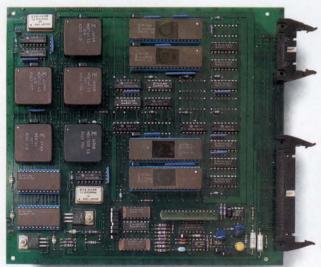

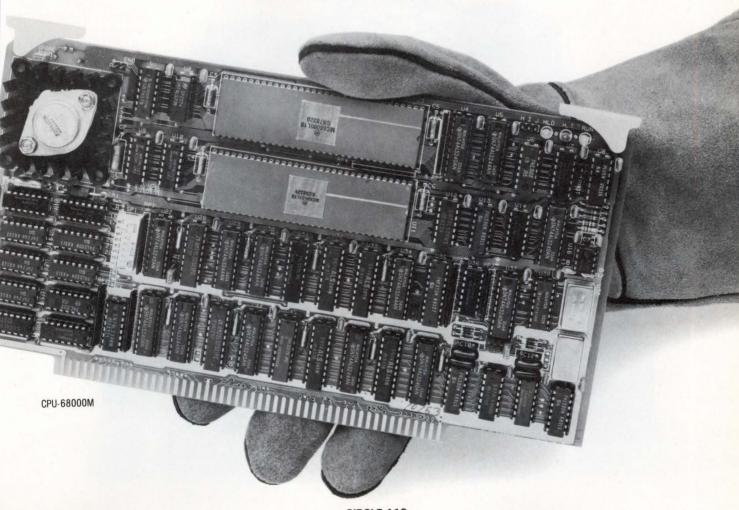

## Challenge the mainframes. VERSAmodules now run the MC68020, true 32-bit performance standard.

frame machines. Gaining speed, adding power, lowering overhead.

cations that, before this, required main-

The new VERSAmodule VM04 processor board can access more than 4 billion bytes of data and manipulate or process 32 individual pieces of information every 180 billionths of a second (180 nanoseconds). Measured in millions of instructions per second (MIPS), the VM04 operates at a sustained rate of 2 to 3 MIPS, with burst rates exceeding eight MIPS, challenging the speed of some mainframe computers.

16K bytes of instruction/data cache on-board help reduce off-board memory accesses to ensure top performance. When off-board access is needed, the VM04 calls on the interface capabilities of Motorola's MC68020-specific RAMbus™ to eliminate most arbitration overhead and speed memory transfers.

The VM04 monoboard is the first MC68020 processor board to offer paged memory management hardware, plus an interface to support

boards have been added to the line to complement the MC68020-based monoboard.

The VM12 includes 1 or 4 Mbytes of RAM and supports the full 32-bit address width of the M68000 Family.

The VM13 dynamic RAM module provides 1 or 4 Mbytes of random access memory dual ported to both RAMbus™ and VERSAbus. A perfect system mate for the VM04 32-bit monoboard, the VM13 has error detection and diagnostic capability.

For system applications requiring high-capacity rotating mass storage, the VM22 disk controller supports four SMD drives and four SA 400/800 floppy disk drives. Data transfer speeds up to 3 Mbytes/sec are maintained by the direct memory access feature of the disk controller.

A choice of real-time and whose-time-has-come operating systems.

The VERSAmodule Family is supported by both of Motorola's M68000 operating systems: the VERSAdos" operating system for real-time applications, and the SYSTEM V/68™ operating system where a UNIX™ operating system environment is desired.

Full operating system support, including VERSAdos real-time device drivers, is available today for MC68000and MC68010-based VERSAmodule monoboards. Porting is under way to assure their early availability on the VM04 monoboard.

Continued Motorola support.

Add to all this Motorola's expertise, proven products, training and service support and you can understand why VERSAmodules continue to be your best high-performance choice for board-level applications.

For more detailed information on VERSAmodule system components,

mail in the coupon or call your local Motorola semiconductor sales office, authorized systems distributor or systems representative.

#### MOTOROLA

VERSAmodule, VERSAbus, VERSAdos, SYSTEM V/68 and RAMbus are trademarks of Motorola Inc. UNIX is a trademark of AT&T Bell Laboratories.

| To: Motoro  | la Semicon | ductor Pro | ducts, In | c., P.O. | . Box 2091 | 2, Phoenix | , AZ 85036 |

|-------------|------------|------------|-----------|----------|------------|------------|------------|

| Please send | l me more  | informatio | on on the | VERSA    | Amodule    | system.    |            |

|             | -          |            |           |          |            |            |            |

| Name    |  |  |

|---------|--|--|

| Title   |  |  |

| Company |  |  |

Address

City

206CD010085

#### **LETTERS TO THE EDITOR**

#### In search of essence

You are to be commended for your Editorial in the Oct 15, 1984 issue (p 13). This country surely needs quality circles and problem-solving groups. However, are you sure what you have written is, in fact, the essence of the company you describe? I don't want to sound like sour grapes.

For years, I have been involved in the purchase of electronic components. Very seldom do I find a company person to be helpful. National Semiconductor is no exception, for I remember an incident in particular.

I called National Semi at various locations on the West Coast for various quantities of programmable logic array chips manufactured there. After many transfers I got to the correct person. I was told that the chips were available, but with a long delivery time. (The person was indifferent.)

I checked with a local supplier who told me that he had a sufficient stock of Japanese PLA chips for my needs. They were cheaper also. It's been my experience that National Semi is no different from any other American corporation. The Japanese are always there, ready to give you what you need. It's amazing.

John Haines 4004 Heathfield Rd Rockville, MD 20853

As I pointed out in my editorial, the statements attributed to National's president, Charles E. Sporck, were from his testimony to the Congressional Joint Economic Committee. Moreover, having visited the company's Santa Clara plant several times and having observed some of the strategies he claims to use, I have no reason to doubt his word. The guestion seems to be, therefore, not whether National uses these management strategies but, whether the strategies are effective.

Also, I think Mr Haines is really asking another important question not directly related to the company's management style. I, too, have never really understood why most American semiconductor companies encourage their sales and applications people to concentrate their efforts on large volume purchasers while diverting other potential customers to distributors. This strategy does not allow for the fact that design engineers initially buy only small quantities of ICs for breadboarding and prototyping—even though their designs may eventually result in huge orders after the system goes into production. So, with their existing strategy, many semiconductor companies seem to be turning away future sales to maximize current sales.

Another question Mr Haines might have asked, but did not, is why so many semiconductor companies with progressive management styles are having problems with the U.S. government due to allegedly inadequate testing of military-grade ICs. At the very minimum, one would expect that use of a quality circle would result in improved product quality. If, however, the major benefit of the new management strategies is a unified sense of purpose and direction throughout the company, management cannot duck responsibility for the actions of individual employees.

So, as Mr Haines implies, either the management strategies do not work, or they work so well that employees quickly sense when top management places a greater emphasis on short-run profitability than on customer service or product reliability.

Michael Elphick Editor in Chief

#### Article corrections

In the article "Digital Signal Processing Moves into High Gear" by Harvey Hindin, Computer Design, Oct 15, 1984, p 61, the credit for some information extracted from the Apr 19, 1984 issue of "In-Stat Research Letter" was inadvertently omitted. In addition, in the illustration on p 66, also from the "In-Stat Research Letter," an error from the original was repeated; "MkHz" should, of course, have been "MHz." Finally, in that same illustration, "RAM multiply speed" should have been "raw multiply speed."

y Trade DE!

y Trade Why Spend a Fortune for an 11/44 or VAX?

Get the performance benefits of an 11/73 by using Able's Microverter Plus. At the same time, you can hang on to your investment in UNIBUS\* peripherals! You benefit because

- With MICROVERTER PLUS, you can use 18-bit UNIBUS DMA devices with up to 4 mb of Q-Bus memory

- MICROVERTER PLUS is compatible with PDP-11/73, LSI-11/23, and -11/23+ processors

- MICROVERTER PLUS is software transparent to RSTS/E, RSX-11, UNIX,\*\* and DSM\*

- MICROVERTER PLUS can help increase your communication capability

- All at a fraction of the cost of a new system

UPGRADE with a MICROVERTER PLUS from ABLE. Call us toll-free at 800/332-2253 (outside California), or 800/225-3332 (inside California)

ABLE COMPUTER, 3080 Airway Ave., Costa Mesa CA 92626 (714) 979-7030, TWX 910 595-1729, TELEX 668307

\*PDP, UNIBUS and DSM (DEC System M.U.M.P.S.) are trademarks of Digital Equipment Corporation. \*\* UNIX is a trademark of AT&T.

Letters to the Editor

should be addressed to:

Editor in Chief Computer Design 119 Russell St Littleton, MA 01460 IF YOU THINK

THAT SIGNETICS

JUST CRANKS OUT A BUNCH

OF JELLYBEAN PRODUCTS,

IT'S TIME YOU TURNED

THE PAGE.

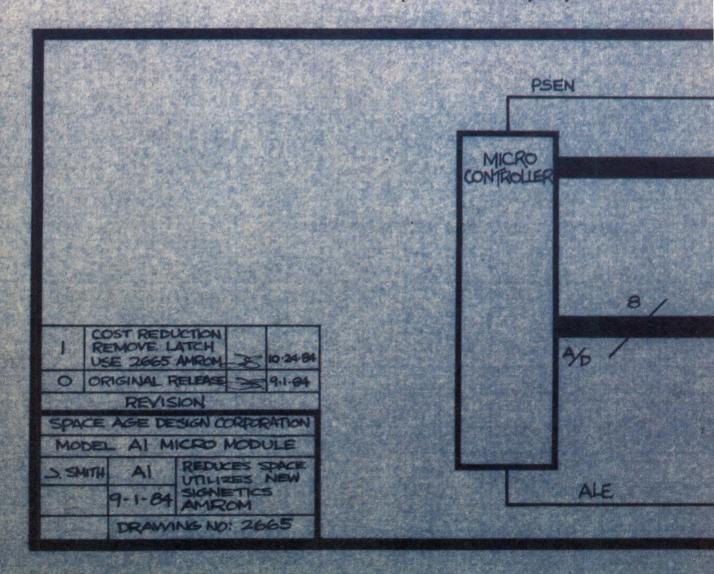

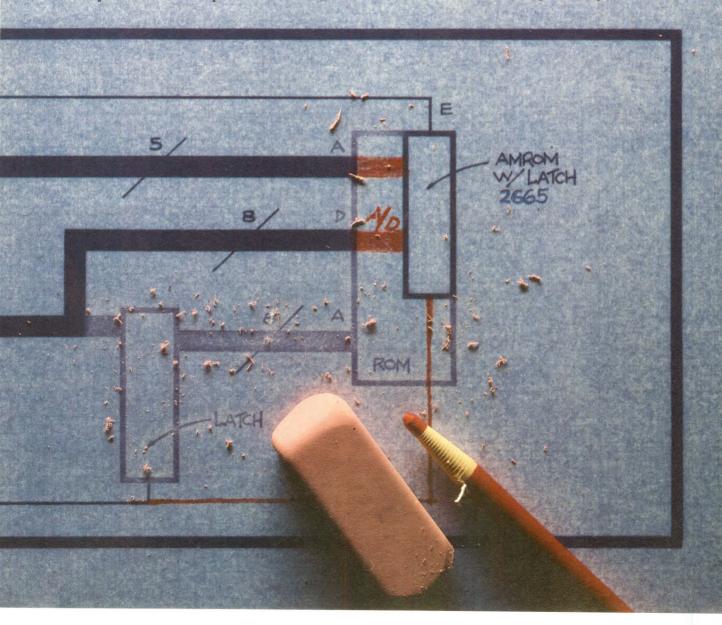

## ONE OF THE GREATEST ARCHITECTURAL BREAKTHROUGHS IN MEMORY.

At last, you can get a MOS ROM with on-board latches.

The 2665 AMROM™ from Signetics.

Now, your 8-bit microcontrollers won't have to go out of their way to access the memory. Which will save them time.

It will also save you space. We squeezed all 64K into a 20-pin thinline 300 mil DIP. Making it take up half the room of standard 8K x 8 ROMs.

That means more parts on your PC board. Or less real estate for your present system. Either way, you're going to cut costs.

But you won't be cutting performance. The 2665's address time is less than 150 ns. When deselected, it gets off the bus in less than 45 ns.

How did we get so much into so little? By multiplexing the address/data. And our ALE is programmable. That makes the AMROM compatible with a variety of byte-wide micro-

controllers and MPUs.

Quality is built in, too. AOQ level for 1984 is under 100 ppm. Next year, below 50 ppm.

1985 will be a big year for AMROMs. Our 128K and 256K parts are on the way. Count on us to help you deliver more and more advanced 8-bit systems, while using smaller and smaller boards.

Get on board now. Call us toll-free for the name of your nearest salesperson. Ask for data

sheets and free samples. Or write Signetics, MS 2527,811 E. Arques Avenue, P.O. Box 3409, Sunnyvale, CA 94088 — 3409.

And discover an architectural breakthrough you won't soon forget.

800-227-1817, Ext. 917F

VLSI from Signetics

AMROM is a trademark of Signetics Corp.

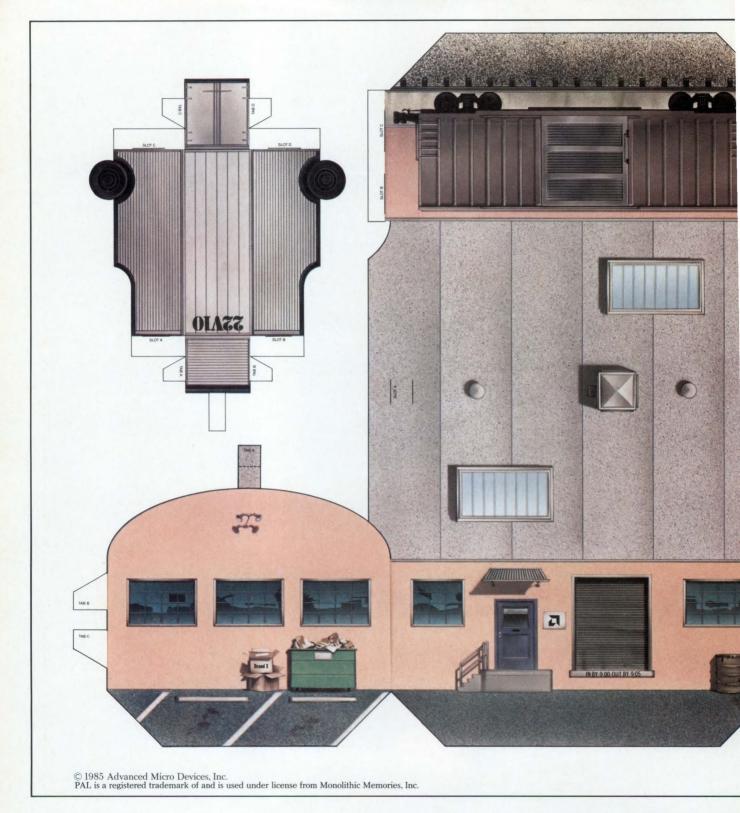

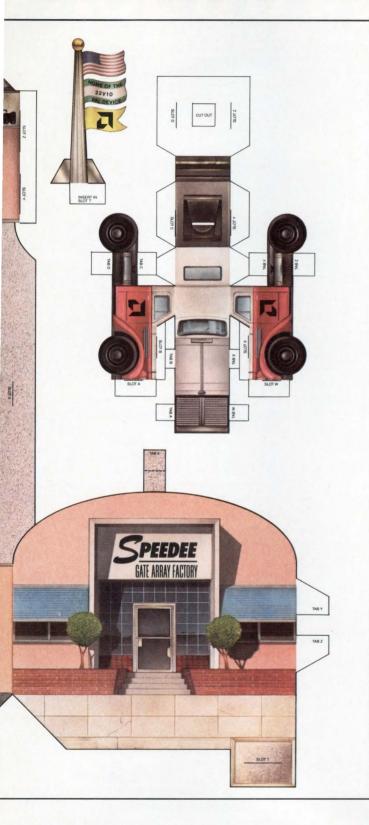

## BE YOUR OWN

## GATE ARRAY FACTORY.

Now you don't have to waste weeks waiting for custom gate arrays. Or face project-killing front end costs.

Get the AmPAL22V10 and be your own boss.

With our new 22V10 PAL\* device, you can make up as many logic devices as you need, for any number of gates up to a thousand.

And you can make as many of each design as you need. Or change your mind, and your design. Right on the spot.

#### The best pal a designer ever had.

The AmPAL22V10 not only gives you the room to do all this—it's one of the biggest PAL devices in the world—it gives you the flexibility. Its 132 product terms are distributed from 8 to 16 terms per output, just like you use them.

You determine the output architecture, too. Each output pin on a 22V10 can be either combinatorial

or sequential, active high or active low.

Which adds up to remarkable production efficiencies. Because you use fewer packages per design.

Like all AMD PAL devices, the 22V10 has an extra built-in testing circuit. They're fully tested at the factory to guarantee AC and DC specifications. As well as AMD's industry leading post programming functional yields (PPFY).

#### We'll put you as far ahead of the competition as we are.

Controllers. Memories. Bipolar and MOS microprocessors. Communications circuits. Signal processors. Nobody makes as many peripherals for as many microprocessors as AMD.

The International Standard of Quality guarantees a 0.05% AQL on all electrical parameters, AC and DC, over the entire operating range. And every single chip meets or exceeds the International Standard of Ouality.

So next time you can't wait to get a hot new design into production, don't. Call AMD and ask about our 22V10. We'll send you a punch-out model of your new factory by return mail.

Then you'll have everything you need to be first

out of the gate.

### Advanced Micro Devices 27

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088 (408) 749-5000, outside California, call toll-free (800) 538-8450, Ext. 5000.

## New SKY WARRIOR

15 MFLOP Array Processor cuts through \$1,000/MFLOP barrier!

At \$14,900\*, it's the most economical way yet to put mainframe number crunching into your microcomputer.

The 15 MFLOP SKY WARRIOR isn't simply a minor technological advance. It's nearly a revolution, fully twice as cost effective as anything else on the market. Capable of performing 15 million 32-bit floating point operations per second. And ½ million operations per second on 64-bit data.

Use it for 2-D Fast Fourier Transforms in imaging systems, in on-site seismic analyses, in 3-D graphics workstation transformations, in real time laboratory signal processing systems, or anywhere else requiring fast interaction with lots of data.

We're experienced veterans at porting hardware. We'll adapt SKY WARRIOR to your custom bus the

This easy-to-use, plug-in processor comes fully software supported by a rich library of user-callable subroutines.

All software developed for our popular, field proven Micro Number Krunchers will run on SKY WARRIOR, too.

You don't have to worry about delivery, performance or backup when you deal with SKY. We specialize in floating point products. Our customer list reads like a scientific and engineering Who's Who. Ask and we'll give you references. They'll tell you what they tell us, things like rock solid engineering, instant responsiveness, super technical support, and total product reliability.

For detailed technical information on our exciting new SKY WARRIOR or any of the other products in our LEGION of arithmetic processors, contact SKY Computers, Inc., Foot of John Street, Lowell, MA 01852, telephone (617) 454-6200.

\*Quantity 1. OEM discounts available.

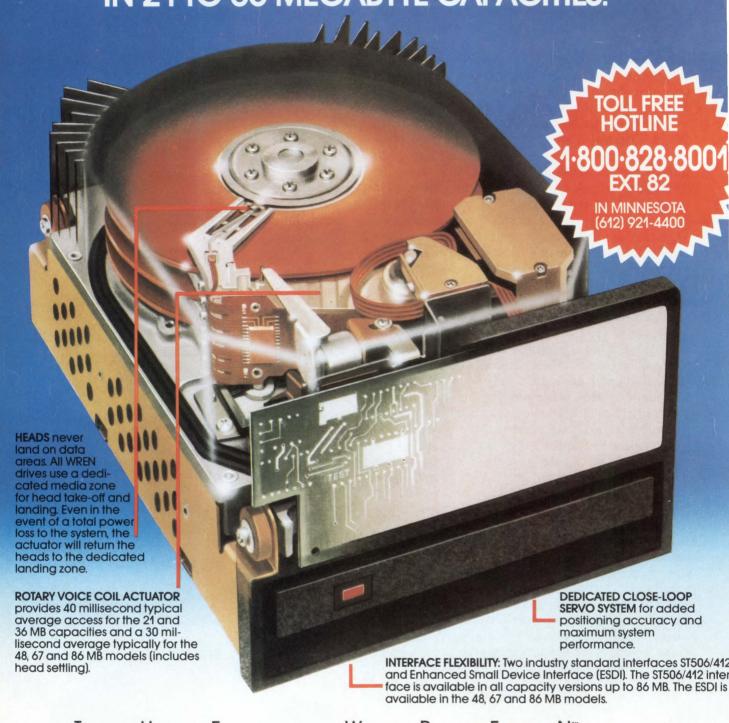

#### Shrinkage continues unabated—Winchesters settle in at 3½ in.

At only a quarter the size of the now ubiquitous 51/4-in. mini Winchesters, 3½-in. Winchesters with 10-Mbyte capacities are reaching the market in production quantities. Measuring 4 x 5.8 x 1.6 in. (10.2 x 14.6 x 4.1 cm), these 10-Mbyte drives may soon be overshadowed by units that pack 20 Mbytes into the same volume.

Despite the pressure for higher capacity, the major goal at this time is to produce reliable drives in the 10-Mbyte capacity range. To accomplish this while maintaining the low cost needed to compete successfully with 51/4-in. drives, the components used in manufacturing them must be readily available and designs must be eminently manufacturable. These criteria call for drives that use low cost stepper motor positioning systems, conventional ferrite head technology, and multiple sourced oxidecoated media.

Because these drives will ultimately be used in environments far more hostile than the computer room, considerable engineering effort has been made to ensure that they can survive abuse. Shock and vibration are probably the most common types of abuse. For this reason, the necessary protection is being designed into the drives. Power requirements are also being kept low to eliminate the need for a separate power supply. This allows the drives to operate off the power supply of the system into which they are designed.

In addition to reduced power consumption, the lower mass of the components used to build the drives cuts the total unit weight, making shock and vibration protection easier. Using a single multilayer PC board for drive control and electronics saves both power and space.

Efforts to achieve these savings in power and size are dictated by the compact nature of the systems into which the drives will go. In portable applications, for example, weight is a major system constraint. The results of these efforts can be seen in power specifications that range from 15 W down to 9 W, and in finished weights that range from 2.5 lb to less than 2 lb.

Another feature that these drives have in common is a standard interface. Their intended application in single-user portable and desktop computer systems allows effective use of the ST506/412 interface specification. This specification enables the units to provide the 10-Mbyte capacity deemed desirable for these applications on the surfaces of two platters. The linear and track densities needed for this capacity are within the range of the open-loop

stepper motor positioning systems dictated by cost constraints.

#### Doing things differently

Designers from Hewlett-Packard (Greeley, Colo) have chosen to implement the system-level Small Computer System Interface rather than the industry standard ST506/412 in their drives. Rotating at 3000 rpm rather than the typical 3600, the drive provides a 4-Mbit/s transfer rate rather than the more common 5 Mbits/s of the ST506 spec. Dubbed the Rugged One, the HP 97501A records at 12 kbits/in. and packs tracks at a density of 1100 tracks/in. Other drives in this form factor typically specify linear densities in the (continued on page 30)

components from shocks up to 40 G.

#### Shrinkage continues unabated (continued from page 29)

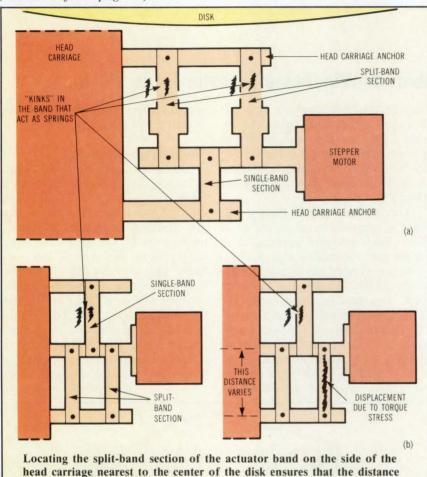

between the motor shaft and the carriage anchors stays the same (a). The traditional design reverses the location of the split-band section (b).

10-kbit range and track densities of under 650 tracks/in. Using these drives, Hewlett-Packard can put 10 Mbytes of data on a single platter, while other units require two disks.

Departing from both oxide-coated and thin-film plated media, this drive records on sputtered thinfilm media. Sputtered media, because of the closely controlled process with which it is manufactured, can provide areal densities of up to 30 kbits/in.2-more than double that possible with oxide-coated media—using monolithic read/write heads. It also supplies the hardness and resistance to abuse that is attributed to thin-film plated media.

To obtain the full potential from this media, the drive uses a closedloop servo positioning system to ensure accurate head placement. Servo data written in each sector on the disk's surface is fed back to the stepper-driven positioning mechanism. This allows the controller to compensate for thermal differentials and lets the read/write heads be positioned with sufficient accuracy to record reliably at the 1100 track/in. density.

A closed-loop servo is also used in the HH-312 from Microscience International (Mountain View, Calif). Providing a 10-Mbyte capacity on two thin-film plated platters, this drive embeds servo information to correct head positioning inaccuracies that result from thermal variations, stepper motor delays, and stepper settling factors. The HH-325, a 20-Mbyte version of this drive (introduced at Comdex last November), uses this closed-loop servo to further advantage.

Reference data is written in wedges on the data surface and is available

on every track rotation. Each servo byte consists of a 3-bit burst that contains a synchronizing pulse and positioning pulses. When initialized, the drive samples four tracks of servo information. This information is used to adjust the stepping operation before proceeding to the track following algorithm. The technique achieves high accuracy over various operating conditions.

Raising the ante in this form factor to 40 Mbytes with a 40-ms access time, Newbury Data Recording, Ltd (Staines, Middlesex, England) supplies the penny. "The main challenge in accomplishing this capacity," according to the company's international marketing manager, Dave Muir, "was to get four disks in the box so that linear density could maintain the ST506 data rate." This was achieved by using minimonolithic heads that are staggered to reduce the space between disks.

A brushless dc motor serves as the key to the drive's 40-ms access time. Effectively used as a voice coil, the motor provides fast, precise positioning. Its rotary motion is translated to linear motion for head positioning through a metal band that drives the actuator assembly.

Microcomputer Memories (Van Nuys, Calif) has also stretched the capacity of the 3½-in. form factor to 20 Mbytes. These drives write on four oxide or plated platters at 10,943 bits/in. using monolithic heads to attain this capacity. Miniscribe (Longmont, Colo) is also said to have 20-Mbyte units under evaluation.

#### Back to basics

Regardless of the capacities provided by drives of this caliber, the crux of the matter is how well the drive performs its intended function. Since 3½-in. Winchester drives are aimed at the storage needs of portable computers, the ultimate criterion becomes how well these drives resist damage from the various hazards they encounter when they are thrown into a car trunk and subjected to extremes in temperature.

And it seems that designers of these midget drives have also taken a serious look at the hazard potential of the portable environment. Specifications for these units cite shock levels up to 100 G and vibration to 1-G acceleration, 5 to 50 Hz. In addition, various methods are used to protect data stored on these disks against loss. Head and spindle locks, guard bands, and dedicated landing zones are used to ensure adequate protection.

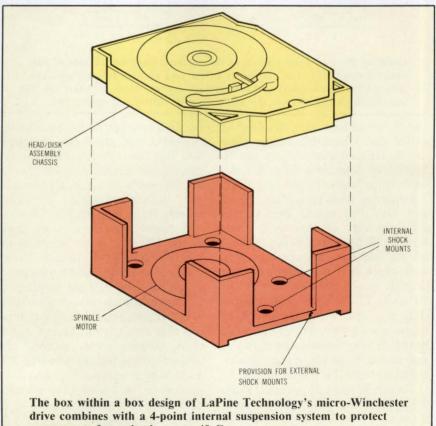

Designed to survive the abuse potential of the portable and desktop personal computer environment, LaPine Technology's (Santa Clara, Calif) drives claim to withstand shock loads of up to 100 G. A 4-point internal suspension system allows Ranger family units to survive shocks to 40 G. Additional external shock absorbers mounted on two sides bring specifications up to a shock load of 100 G with power off.

According to LaPine's vice president of marketing, Rick Brechtlein, "To put the technology where it is exposed to abuse and enable it to meet reliability requirements, extraordinary measures must be taken to reduce the effects of shock, vibration, and temperature changes." These extraordinary measures in LaPine's case resulted in a "box within a box" design. In such a design, the head/disk assembly is mounted within a frame such that it is shock mounted within itself.

Seagate (Scotts Valley, Calif) has paid particular attention to shock characteristics in designing its recently announced ST112 drive. According to product planning manager, Bob Toda, "In some regards shock pads may help shock aspects, but hurt vibration aspects of a design." Since shock and vibration are contrary to each other, attempts to dampen vibration may result in amplification and transmission of shock, Toda points out. To minimize the impact of both, it is necessary to make a compromise between the two.

Instead of focusing solely on shock and vibration, Seagate concentrated more on the use of low mass minislider heads to minimize the impact of shock during operation. Seagate

#### The half-height removable Winchester cartridge

Reducing a complex and precise product to pocket-sized dimensions is no easy task. Couple this problem with the requirement for removable rigid media in a package that will withstand abuse from unsophisticated users, and the challenge becomes even greater.

One major consideration faced by manufacturers of removable Winchesters is how to avoid head/media damage and data loss without violating size and cost restrictions. Because the typical environment subjects the drive to rough handling, protection of the delicate head and selection of durable media are paramount.

Along these lines, two trends have developed in removable Winchesters. One is to continue to use standard oxide media, and mechanically retract the heads from the head/disk assembly. This adds to the overall size of the drive, representing a trade-off into the larger 51/4-in. form factor. Another solution to the head/disk interface problem is to combine traditional design with variations on a Winchester theme.

Operating under the company philosophy that adding mechanical complexity often trades one problem for another, Syquest Technology (Fremont, Calif) has designed a simplified head/media control element into removable Winchester disk drives. When no cartridge is housed in a drive, a simple cam device keeps the heads out of contact with each other. This protects the heads during drive transport, and keeps the total size of the drive to a minimum. A failsafe cartridge interlock mechanism ensures correct cartridge insertion and disengages the heads when the drive door is opened. When the heads are delivered onto the media for read/write, a dash pot damper ensures a gentle, controlled landing.

For the media, Syquest has chosen to combine thin-film metallic plated disks with a microscopic sputtered layer of graphite over the disks' cobalt surface. Standard Winchester media are coated with ferrous oxide and have a hardness of 3.3 on the Mohr scale. Cobalt coated plated media have a hardness of 5.5. When coated with graphite, the cobalt media's characteristics for head takeoffs and landings improve more. The lubricating graphite also seals and protects the media from environmental reaction and contamination from dust or smoke particles.

Plated media provide improved magnetic switching that results in higher recording densities: 12.4 kbits/in. versus the 9300 associated with ferrous oxide media. The result is high data capacities on a small disk. Current half-height product offerings provide 10 Mbytes of removable storage on 100-mm cartridges.

designers believe that most of the damage incurred during handling results from the head slapping onto the media. Because of the smaller cross-sectional area and relatively low mass, the use of minislider heads reduces damage resulting from head slap.

Recognizing the abusive conditions under which these drives must operate, Microscience took steps to maintain accuracy under stress conditions. According to Ron Schlitzkus, director of marketing, accuracy is ensured by a unique actuator band design. Unlike typical designs, where the split band section is located on the back

side of the carriage head assembly, Microscience locates the single-band section toward the back. This, according to Schlitzkus, places the primary stress on the single stronger element of the band and allows a constant distance to be maintained between the stepper motor shaft and carriage anchor.

In addition to shock and vibration, temperature conditions also contribute to the abuse that these drives must endure. According to Brechtlein, "LaPine expended a lot of engineering time and detail to make sure that thermal characteristics could respond

(continued on page 32)

Shrinkage continues unabated (continued from page 31)

|                             | Seagate         | Rodime          | Microcomputer<br>Memories | Microscience    | Microscience    | LaPine          | Hewlett-Packard |

|-----------------------------|-----------------|-----------------|---------------------------|-----------------|-----------------|-----------------|-----------------|

| Model No.                   | ST112           | RO 352          | M-112/125                 | HH-312          | HH-325          | 3522            | HP 97501A       |

| Disks                       | 2               | 2               | 2/4                       | 2               | 2               | 2               | 1               |

| Heads                       | 4               | 4               | 4/8                       | 4               | 4               | 4               | 2               |

| Capacity<br>(in Mbytes)     | 10              | 10              | 10/20                     | 10              | 20              | 10              | 10              |

| Access time                 | 65 ms           | 92 ms           | 85 ms                     | 70 ms           | 80 ms           | 80 ms           | 75 ms           |

| Power requirements          | 13 W            | 13 W            | 12 W                      | 9 W             | 9 W             | 13 W            | 10 W            |

| Shock operating             | 40 G            | 30 G            | _                         | 10 G            | 10 G            | 50 G            | 50 G            |

| Temperature rough operating | 50 to<br>113 °F | 50 to<br>122 °F | 40 to<br>115 °F           | 40 to<br>122 °F | 40 to<br>122 °F | 40 to<br>122 °F | 32 to<br>122 °F |

| Weight                      | 2.5 lb          | 2.2 lb          | 1.7 lb                    | 2.25 lb         | 2.25 lb         | 2 lb            | 2.1 lb          |

to a wide range of temperature fluctuations." In the design, LaPine had the advantage of starting from scratch specifically to meet these requirements. The design achieves a balance between the thermal expansion and contraction of components "through careful selection of materials and attention to nitty gritty equations," says Brechtlein.

Rodime's (Mission Viejo, Calif) design relies on the same basic principles. In the RO 350 series, head/ track relationships are maintained by designing thermal variants such that thermal expansion of disk and positioners are balanced within the operating range. George Rea, marketing manager, says that the problems are minimized by the  $3\frac{1}{2}$ -in. form factor. A 3½-in. disk results in a smaller excursion since the radius is 11/2 in. as opposed to the 2½-in. radius of 5<sup>1</sup>/<sub>4</sub>-in. media. Rodime handles this by selecting materials with matching thermal characteristics (eg, aluminum substrate balanced by aluminum parts in the head assembly flexure).

Stepper motors are major contributors to problems of uneven thermal expansion. Microscribe minimizes these effects by thermally isolating the stepper motor from the head/disk assembly. This practice achieves greater reliability by allowing heat produced by the motor to be dissipated without affecting the disk or head positioning mechanism.

Another point that Seagate considers important in achieving high reliability is elimination of the dedicated landing zone used by many designs in favor of a purely random landing point. By landing the heads at random on the data surface of the disk, potential damage due to start/ stop effects can be minimized. Toda says that while some people express concern that this method might damage the data surface, extensive tests performed by Seagate show that having the heads land in random locations reduces the chance of damaging any one area. Also, the chance of head damage caused by abused media is less than when the heads always land within a certain area.

Instead of providing a shipping zone on which to park the heads during transportation as many drives do, some vendors feel that more extreme measures are required to prevent head/media damage. Rodime's RO 350, for example, provides brakes. The dual acting failsafe brake in this design automatically brakes the dc spindle motor at power off. It also acts as a transit lock for the spindle motor and locks the stepper motor to immobilize the actuator arm. These brakes release automatically when power is switched on to the drive.

LaPine's drives provide a further measure in this regard, both lifting the heads off the media's surface and locking them in a lifted position. According to Brechtlein, this is extremely important for shock and vibration protection when units are being moved. The proprietary mechanism used by LaPine acts similarly to that of a removable media device. "By lifting the heads off the media and holding them off," Brechtlein says, "the chance of head or disk damage is virtually eliminated."

While LaPine is starting to incorporate thin-film plated disks in its drives, it is not doing so because of the persistent arguments that thinfilm media provide harder surfaces and therefore are less susceptible to damage. Countering those contentions, Brechtlein states that "although plated media is more tolerant than oxide media as far as damage is concerned, there are also heads involved." When a device is subjected to movement and shock, the plated media may resist damage, but head cracking may result if impact occurs because of its relatively greater hardness. "You have to consider the head and the media as a combined system," says Brechtlein.

> -Peg Killmon, Senior Editor SYSTEM TECHNOLOGY (continued on page 40)

#### Zetaco's latest inventions make 86 disk and tape drives Data General BMC compatible.

Zetaco's BMX-1 disk drive controller and BMX-2 mag tape coupler give the user of Data General's high-speed BMC (Burst Multiplexor Channel) full compatibility with the newest high-speed, high-capacity, non-DG drives.

These two bright ideas let you choose virtually any high performance SMD-type disk drive or ½" tape drive to run on the BMC or Data Channel on DG's newest Eclipse or MV Series mini.

Each BMX-1 supports up to 4 SMD-interfaced hard disk drives. Each BMX-2 supports up to 8 streaming or start/stop tape drives.

Zetaco's full emulation of DG's 60XX and 61XX series disk and 6026 and 4307 tape subsystems means no software patching is required. E<sup>2</sup> PROMs eliminate switches, making drive configurations and functions selectable via downline loaded software. And Zetaco's exclusive

backplane cable design is plugand-go compatible with DG's FCC and non-FCC compliant chassis.

Discover the BMX Series from Zetaco, 6850 Shady Oak Road, Eden Prairie, MN 55344, (612) 941-9480. Telex 290975. European Headquarters: 9 High Street, Tring, Hertfordshire, HP23 5AB, England. (044282) 7011. Telex 827557. ZETACO G.

Controller Division, Custom Systems Inc.

# ADECLAIDE DATAINE

#### When In The Course Of Business Events ...

OEMs designing systems for today's businesses face two realities. One, data processing is rapidly becoming more decentralized. It is pushing outwards into individualized work units, defined more by job function and applications, performed by more people in

more places, demanding more data flexibility—more data independence.

Which brings OEMs face to face with a second reality. Winchesters. Because the prevailing mass storage technology—in the form of large storage units used for access or downloading, or smaller, high

capacity desk-top mechanisms—continues to head in

the opposite direction.

Rather than freeing users to operate effectively in the new environments of distributed data processing, Winchesters keep them device-dependent, keep them tied to a shared system of storage.

#### Slavery By Any Name ...

There are lessons here. That the central issue isn't more data, but more data dynamics. And that Winchesters are hardly data dynamic at all.

Consider the aggravations of "wait your turn" access, or the need for lots of "system savvy" on the user's part. Consider the time consumed in backing up and restoring data. And consider the ever-present risk of a system going down or files lost to expensive head crashes.

Now consider the alternative.

IOMEGA HAS REMOVED CAPAC

REGIONAL AND DISTRICT SALES OFFICES: SOUTHEAST (305) 755-1060; SOUTHCENTRAL (214) 458-2534;

# ATION OF PENDENCE.

#### IOMEGA's Distributed Data Storage: Freedom Of Information.

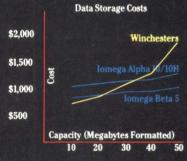

The IOMEGA family of data management/storage systems effectively matches today's distributed data processing reality with a new reality: *distributed data storage*. Because IOMEGA's reliability and performance specs often exceed Winchesters, particularly in access times and transfer

|                        | IOMEGA<br>BETA 5             | IOMEGA<br>ALPHA 10/10H       | TYPICAL WINCHESTER |  |

|------------------------|------------------------------|------------------------------|--------------------|--|

| Formatted<br>Capacity  | 5.0 Mbytes per<br>cartridge  | 10.0 Mbytes per<br>cartridge | 10.0 Mbytes fixed  |  |

| Data Transfer Rate     | 5.0 Mbits/Sec                | 9.0 Mbits/Sec                | 5.0 Mbits/Sec      |  |

| Average Access<br>Time | 50 msec<br>includes settling | 35 msec includes settling    | 85 msec            |  |

| Form Factor            | 5.25"                        | 8"/8" Half<br>Height         | 5.25"              |  |

rates. And they deliver cost-per-megabyte figures that Winchesters cannot figure at all.

The key is "in/out" simple—the IOMEGA cartridge. Think about downloading data and

software to a single 5- or 10-megabyte cartridge, then manipulating, updating, and uploading with maximum convenience and cost efficiency. And think about a total enterprise solution, about storing individual applications, complex software programs, or data sets—all of which can be passed along to others without expensive networking resources. And when you need more storage, you use more cartridges, not more hardware.

#### **Accept No Other Alternatives.**

IOMEGA's distributed data storage solutions—in full- and half-height 8-inch 10-megabyte solutions, and a 5-megabyte, 5¼-inch version as well—give OEMs Winchester performance and reliability, and floppy convenience and cost efficiency. They are proven, risk-free solutions. And of the few cartridge opportunities on the market today, IOMEGA's—besides being available—are the only ones that are rugged, absolutely interchangeable, and inexpensive. As such, they give OEMs the most precious commodity of all: *the freedom of designed-in freedom*. The freedom your customers require.

#### Take The Liberty.

Get in touch with an IOMEGA representative today. One is conveniently located in an area near you.

THE FUTURE IN DISTRIBUTED DATA STORAGE

IOMEGA CORPORATION 1821 West 4000 South Roy, Utah 84067 (801) 776-7330

HE MASS STORAGE ISSUE.

WESTERN (714) 855-1211, (408) 263-4476; NORTHEAST (617) 933-2000; MIDWEST (312) 397-4234; EASTERN (203) 359-9858.

CIRCLE 17

# INTEL CHMOS GIVES DATA EQUAL VOICE.

The telephone system of tomorrow will be digital end to end. Able to handle voice and data. Simultaneously.

Today, there's a shortcut to get you there.

Introducing the first two members of Intel's third generation Advanced Telecommunications

OFFICE IATC INT

Component (iATC<sup>™</sup>) family.