FEBRUARY 1988

Tony Zingale on tool integration

Concurrency in analog-digital simulation

Power distribution in sea-of-gates arrays

SYSTEMS DESIGN

The Magazine for Systems Design Using VLSI Technology

Can VLSI chips help designers tame graphics and imaging systems?

# THE POINT OF NO RETURN.

When you put a Fujitsu ASIC to When you put a Fujitsu ASIC to work, you can rest assured it will work the way it should. And keep on doing its job for a very long time to come. In fact, when you look at our performance record over the years, you'll be hard pressed to find any field failures at all.

This is no empty promise.

Product reliability has been a way of life for us for more than 15

vears.

That's why we always take a conservative approach to the design process. Giving you realistic worst case specs that no production device will exceed.

Guaranteeing a minimum 90% utilization of all gates. And giving you a simulation-to-production correlation of 99%.

It's also why we control every step of the production process. From design to wafer fab to assembly and final test, including 100% AC testing at frequency. So nothing is left to chance.

To us, reliability in the field is everything. And when you remember we've taken over 8,000 ASIC devices from design through mass production, you can see that we'll give you a level of confidence no one else can offer.

So count on parts that have longer life expectancies.

Call our Hot Line today at (800) 556-1234, Ext. 82; in California (800) 441-2345. Look into ASICs you can send out the door. Never to return again.

FUJITSU

FUJITSU MICROELECTRONICS, INC.

Technology That Works.

Editor/Editorial Director

Girish Mhatre

**Editor Emeritus**

Roderic Beresford

Editor-At-Large

Stan Baker

**Editors**

David Smith (Western Region) Mike Robinson, Acting Managing Editor

Ernest L. Meyer

**Directories Editor**

Michelle A. Losquadro Technical Advisers

John A. Darringer

Jeffrey T. Deutsch

Edward J. McCluskey

Alan F. Podell Daniel G. Schweikert Susan L. Taylor

**Editorial Production**

Patricia L. Gaynor, Sr. Production Editor Ingrid Atkinson, Production Editor

COVET

Mike Shenon, Art Director

Editorial Art

Marie D'Ippolito, Design Director

Manufacturing

David Getlen, Dir. of Manufacturing Marie Myers, Production Manager James Pizzo, Production Supervisor

Vance Hicks, Coordinator

#### Publisher

Norm Rosen

VLSI SYSTEMS DESIGN (ISSN 0279-2834) is published monthly with an extra issue in May by CMP Publications, Inc., 600 Community Drive, Manhasset, NY 11030. (516) 365-4600. VLSI SYSTEMS DESIGN is free to qualified subscribers. Subscriptions to others in the US: one year \$60.00, two years \$95.00; Canada and Mexico: one year \$90.00, two years \$165.00; Europe, Central and South America: one year \$120.00, two years \$225.00. Asia, Australia, Israel and Africa: one year \$150.00, two years \$285.00. Second-class (Requester) postage paid at Manhasset, NY and additional mailing offices. POSTMASTER: Send address changes to VLSI SYSTEMS DESIGN, 600 Community Drive, Manhasset, NY 11030. Copyright 1988, CMP Publications, Inc. All rights reserved.

VLSI SYSTEMS DESIGN was founded to explore, expand, and define the interrelations between very-large-scale integrated circuits (VLSI) and computer architecture, design strategies, costs, and aids, as well as the electronics industry as a whole. VLSI SYSTEMS DESIGN is unique in that it is written by and for the participants in this dynamic field. VLSI SYSTEMS DESIGN intends to be the communication focus of a new VLSI design community, encourage its development, and help define its directions.

Over 41,000 copies of this issue printed.

#### CMP ELECTRONICS GROUP

Electronic Buyers' News Electronic Engineering Times VLSI Systems Design Ken Cron, Vice President/Publishing Frank J. Burge, Vice President/Group Publisher Norm Rosen, Group Marketing Manager

CMP Publications, Inc. Gerard G. Leeds, President L.J. Leeds, Senior Vice President Michael S. Leeds, Vice President Pearl Turner, Vice President/Treasurer

Volume IX, No. 2, February 1988

#### S E MS E SIGN D

The Magazine for Systems Design Using VLSI Technology

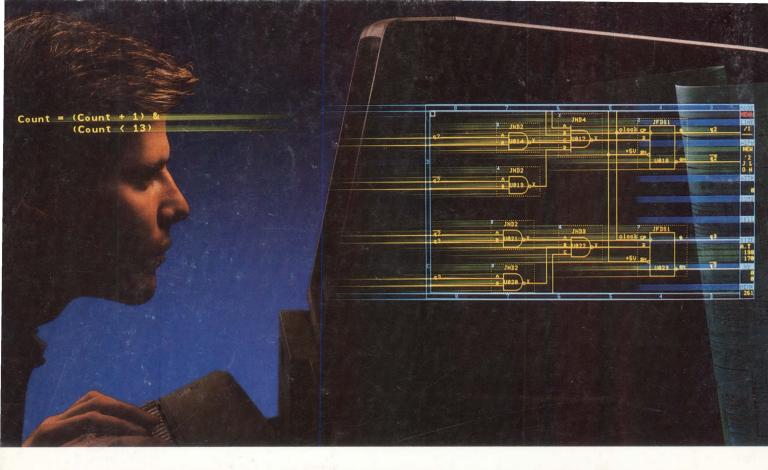

#### Cover

It hasn't been easy for VLSI devices to get a rope around the ornery demands of graphics and imaging systems. Evolving standards and seemingly endless customer demand for more throughput have made it difficult for IC vendors and systems designers alike to decide which functions should be set in silicon. Still, graphics processors and floating-point chips look as if they'll remain in the saddle. Computer graphics by Susan Felter, University of Santa Clara, CA.

#### Departments

- From the Editor **Breaking Down the Gates**

- Calendar

- News

Sea-of-Gates Arrays 32-Bit Architecture from Japan **Retargetable CASE Tools Design Tool Kit** 33-MFLOPS Chip Set

12 People

John Eurich Brings Engineers Together

**Industry Insights**

Tools vs. Data: The Debate for '88

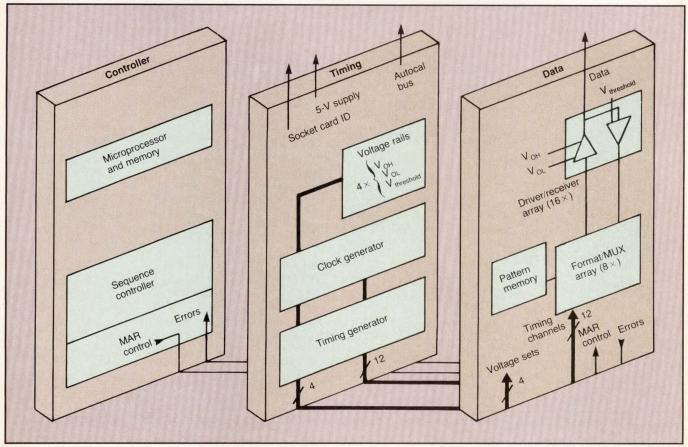

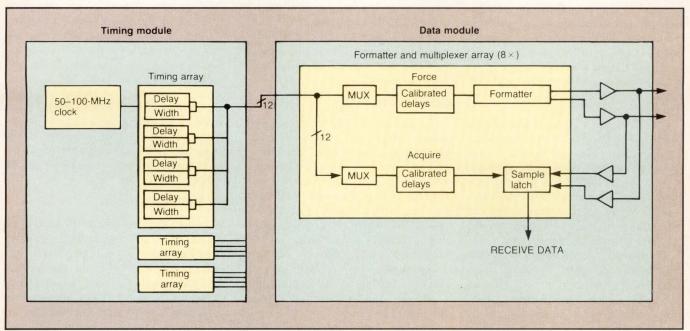

- Circuits In Systems **Building a Verification System for High-Performance ASICs**

- **Product Showcase** Mechanical Design and Thermal Analysis in a CAE Environment

- 72 Advertisers' Index

Page 64

#### Articles

Page 32

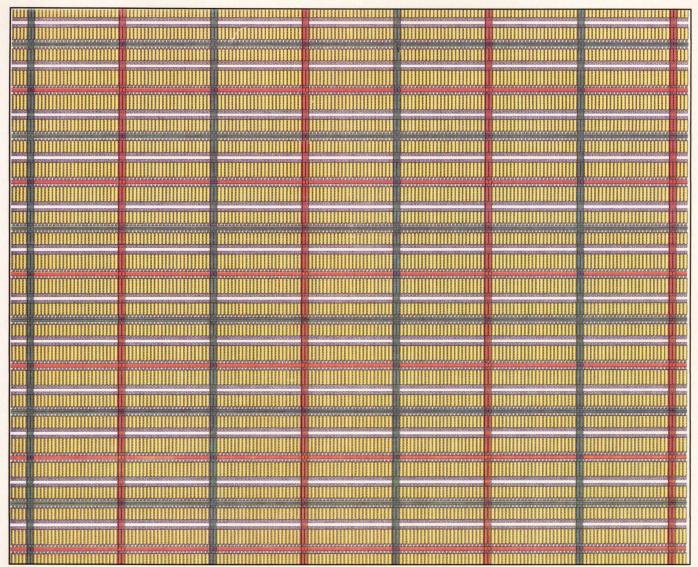

#### 16 **Aluminum Screen Gives Superior Power Distribution** in a Sea-of-Gates Array

Richard Blumberg and Charles Waggoner, SGS-Thomson Microelectronics

A 1.2-µm sea-of-gates array with 128,000 raw gates uses an augmented aluminum "screen of power" and a novel controlled-skew-rate I/O design to produce nearly foolproof power busing.

#### 22 The Integration of Graphics and Imaging Systems

David Smith, Western Regional Editor

Four architectural issues dominate the design of graphics and imaging systems and their constituent VLSI components: the choice of programmable or hardwired functions, variable formats and resolutions of data, the use of building-block ICs or one integrated chip, and the use of parallel processing and pipelines to enhance throughput.

Page 22

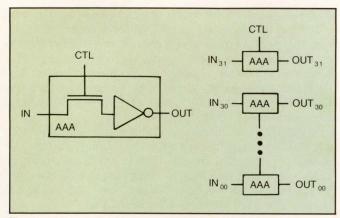

#### 32 A Smart System That Compiles RTL Models from Schematics

Arie Brish, Ronen Keinan, and Yiftach Ravid

Motorola Semiconductor Israel Ltd.

For accelerating simulation, register-transfer-level modeling offers some unique advantages. This article presents a set of model reduction and compaction rules that take a detailed network model and produce an RTL model. The method speeds simulation by an order of magnitude.

# Interface \_ GND

Page 38

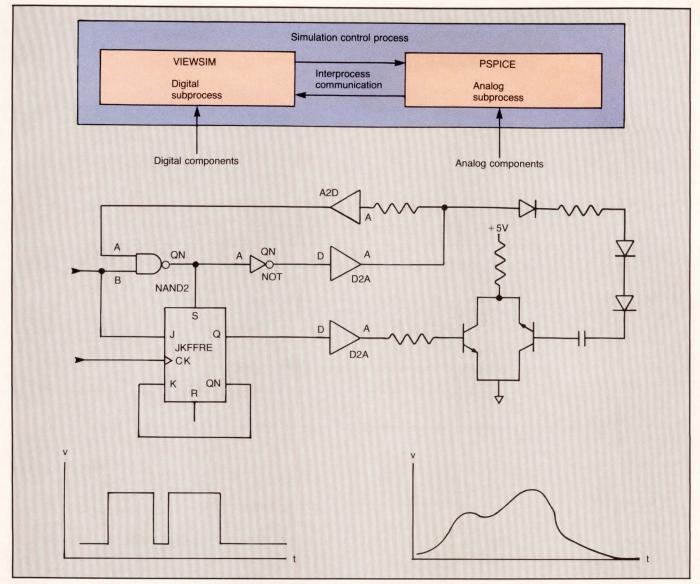

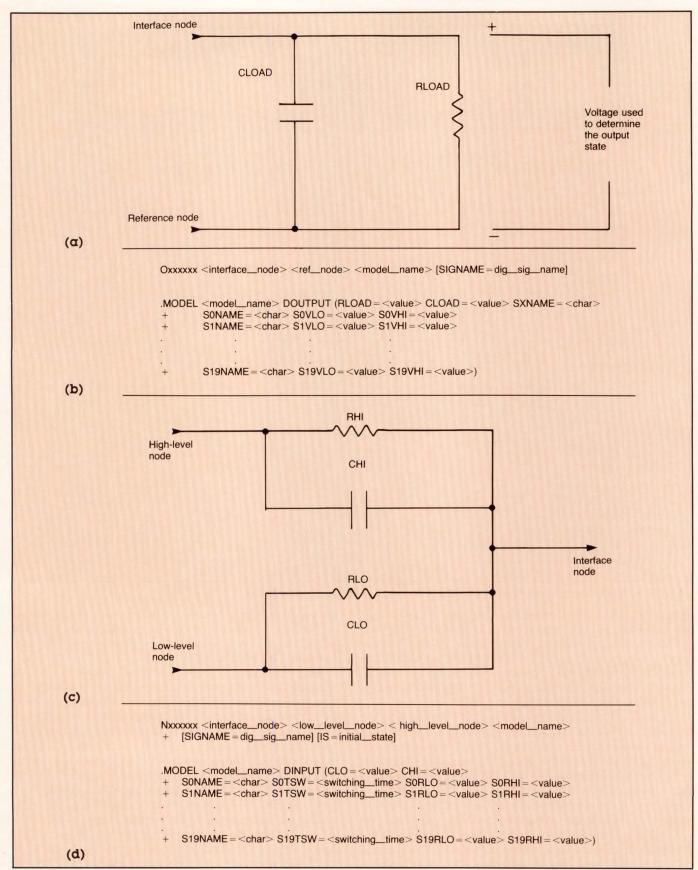

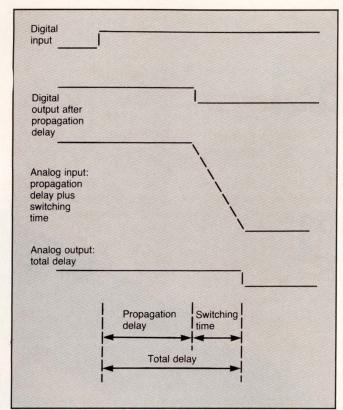

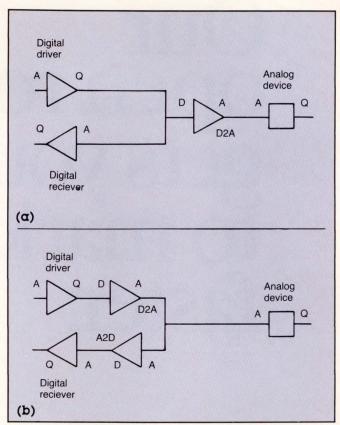

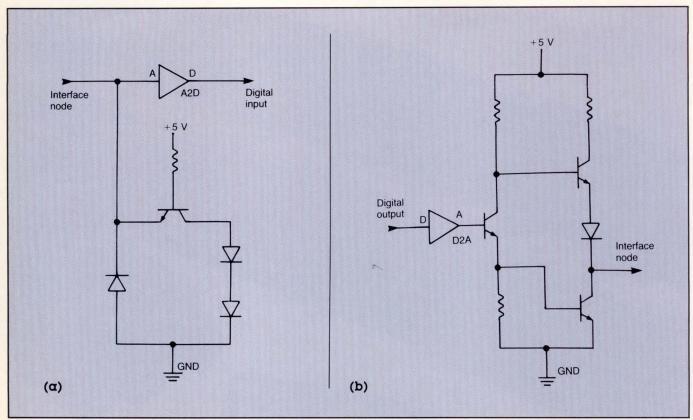

#### 38 Coupling a Digital Logic Simulator and an Analog Circuit Simulator

Tedd Corman, Viewlogic Systems Inc., Marlboro, MA Michael U. Wimbrow, MicroSim Corp., Laguna Hills, CA

To simulate circuits with analog and digital circuitry, an interface process passes state and timing information between a digital logic simulator and a circuit simulator. Concurrent execution of the simulators and user-configurable interface models let designers simulate mixed analog-digital circuits, even those with feedback loops.

#### 50 1988 Survey of Logic Simulators

VLSI Systems Design Staff

Our annual survey, based on information supplied by each primary vendor of a logic simulation product, highlights the salient features of these critical tools.

# Build your gate arrayon a solid foundation.

You want to implement your ASIC design quickly. With technology that meets your requirements. You need quality products and dependable delivery to maintain a competitive edge. In short, you expect a partnership built on a solid foundation. One you can count on for future designs as well.

And, that's precisely what you get with Mitsubishi. A solid partnership with a technology base that includes in-house wafer processing, advanced packaging, demonstrated production capabilities and long-term commitment to R&D.

Mitsubishi offers a broad range of gate array product capabilities, from 200 to 20,000 useable gates. And, continuing development work at Mitsubishi's research laboratories is leading to sub-micron CMOS and even more advanced ASIC materials and processes. Unique variable track masterslice (VTM), 1.3µm gate arrays provide an ideal architecture for mixed random logic and memory designs.

There's a broad range of packaging options: DIP and shrink DIP, SOP, PGA, as well as high pin count quad flat packages (QFP) and plastic leaded chip carriers (PLCC).

Mitsubishi is committed to supporting your ASIC needs with CAD/CAE design tools to help you develop designs fast. For maximum flexibility, you can design on Mitsubishi's workstations or your own. Remote access to Mitsubishi's proprietary mainframe CAD system allows design verification on any terminal with telephone access.

Mitsubishi's design centers, located in Sunnyvale, CA and Durham, NC, are networked with Regional Technical Centers and a gate array engineering support staff ready to assist in all phases of design.

Mitsubishi Electronics America, Inc. The solid foundation for all your ASIC needs.

#### PACKAGING:

Mitsubishi offers a broad range of industry-standard and proprietary packaging options. A leadership foundation in high pin count surface-mount packages includes quad flat packages (QFP), now available with 160 leads and soon over 200. Mitsubishi provides a cost-effective alternative to PGAs by mounting OFPs on a PC board adaptor.

#### PROCESS:

Low power,  $1.3\mu m$ , double metal CMOS technology is available today, with submicron levels on the way. Mitsubishi's patented\* gate isolation structure provides 10% to 20% faster performance, with a 15% to 25% higher gate density than conventional oxide isolation.

\*U.S. Patent No. 4,562,453

#### **MANUFACTURING** COMMITMENT:

Mitsubishi is committed to continued advancements in ASIC technology, quality and production capacity. Typical time from design to prototype is three to five weeks. Prototype approval to production is eight to ten weeks.

#### **DESIGN SUPPORT:**

At your workstation or Mitsubishi Design Centers, use industry-standard, advanced CAE tools with Mitsubishi's mainframe CAD system. Or, let Mitsubishi integrate your design.

#### **SERVICE:**

Mitsubishi offers design and applications support at centers in Sunnyvale, CA; Durham, NC and Regional Technical Centers.

# Quality through commitment.

**MITSUBISHI**

For further information, call or write Mitsubishi Electronics America, Inc., Semiconductor Division, 1050 E. Arques Avenue, Sunnyvale, CA 94086,

Semiconductor Division, 1050 E. Arques Avenue, Sunnyvale, CA 94086, 4(98) 730-5900.

U.S./CANADIAN REGIONAL SALES OFFICES AND TECHNICAL CENTERS: NW: Sunnyvale, CA (408) 730-5900, SW: Torrance, CA (213) 515-3993, N: Minnetonka, MN (612) 938-7779, NC: Mt. Prospect, IL (312) 298-9223, SC: Carrollton, TX (214) 484-1919, NE: Woburn, MA (617) 938-1220, MA: Hackensack, NJ (201) 488-1001, SA: Norcross, GA (404) 662-0813, SE: Boca Raton, FL (305) 487-7747, Canada: St. Laurent, Quebec (514) 337-6046.

U.S./CANADIAN AUTHORIZED SALES REPS: AL: Beacon Elect. (205) 881-531, AR: OM Assoc. (214) 690-6746, AZ: SMS & Assoc. (602) 998-0831, CA: Pathfinder Elect. (619) 578-2555, QCI (408) 432-1070, SC Cubed (805) 496-7307, SC Cubed (714) 731-9206, CO: Simpson Assoc. (303) 794-8381, CT: Comp Rep Assoc. (203) 269-1145, DE: Trinkle Sales (609) 795-4200, FL: Beacon Elect. (305) 997-5740, (813) 796-278, (305) 332-1940, GA: Beacon Elect. (404) 256-9640, Beacon Adv. Comp. (404) 662-8190, IA: Mid-Tec Assoc. (314) 275-8666, DI: ES/Chase (503) 292-8840, IL: Phase II Mktg. (312) 305-5092, IN: Carter, McCormick & Pierce (317) 244-1685, KS: Mid-Tec Assoc. (913) 541-0505, KY: Makin Assoc. (513) 871-2424, LA: OM Assoc. (214) 690-6746, MA: Comp Rep Assoc. (617) 329-3454, MD: Trinkle Sales

(609) 795-4200, ME: Comp Rep Assoc. (617) 329-3454, MI: Carter, McCormick & Pierce (313) 477-7700, MN: Gibb Elect. (612) 935-4600, MO: Mid-Tec Assoc. (314) 275-8666, MT: Simpson Assoc. (801) 566-3691, NC/8C: Beacon Elect. (919) 787-0330, ND/SD: Gibb Elect. (612) 935-4600, NE: Mid-Tec Assoc. (913) 541-0505, NH: Comp Rep Assoc. (617) 329-3454, NJ: Trinkle Sales (609) 795-4200, Win-Cor Elect. (516) 627-9474, NM: SMS & Assoc. (602) 998-0831, NV (Northern & Central): QCI (408) 432-1070, NV (Southern): SMS & Assoc. (602) 998-0831, NV: Win-Cor Elect. (516) 627-9474, Lamtec (315) 637-3788, OH: Makin & Assoc. (513) 871-2424, (614) 848-5424, (216) 248-7370, OK: OM Assoc. (214) 690-6746, OR: ES/Chase (503) 292-8840, PA: Trinkle Sales (609) 795-4200, PUERTO RICO: Beacon Elect. (809) 728-5040, RI: Comp Rep Assoc. (617) 329-3454, TN: Beacon Elect. (404) 256-9640, (205) 881-5031, TX: OM Assoc. (512) 388-1151, TN: Simpson & Assoc. (801) 566-3691, VT: Comp Rep Assoc. (617) 329-3454, VA: ES/Chase (206) 323-9535, WI: Gibb Elect. (612) 935-4600, Phase II Mktg (312) 303-5902, WV: Trinkle Sales (609) 795-4200, WY: Simpson Assoc. (801) 566-3691, VT: Comp Rep Lect. (416) 890-2903, (613) 225-9186, (514) 337-6046, (604) 254-2004, (604) 432-1788

### Breaking Down the Gates

t's getting more difficult for engineers to categorize and compare the various alternatives available for implementing a circuit in silicon. If you design a custom controller chip, for example, you may be able to implement it using a full-custom chip, a standard-cell IC, a "sea-of-gates" gate array, a conventional gate array, a logic cell array, a field-programmable logic sequencer, a registered PAL, an EPLD, an EEPLD, or any number of products with catchy names.

How does an engineer evaluate each type of device for its suitability for his design? He can compare the number of inputs and outputs on the devices with those on his design. He can compare manufacturers' specifications for maximum operating frequency with his design goals. But how can he evaluate the function density of a device whose specific function is not yet defined?

Ideally, the designer should be able to use the product and gauge its potential first-hand. Unfortunately, there are too many products and not enough time to evaluate all the possibilities.

Certain terms do exist to specify the utility of ASICs. The term gates is used most often to describe density. Unfortunately, a gate in a VLSI device may be four transistors, the ECL equivalent of a CMOS NAND gate, or the total number of transistors on the chip divided by 4, 5, or 6, depending on the vendor and technology.

Last month in our Industry Insights column, Andy Haines of Actel Corp. argued that a benchmark for density is necessary. He suggested four benchmark functions: a datapath block, a state machine, an arithmetic block, and a counter/ timer circuit. IC vendors would use these functions to describe the capacity of their user-specified ICs.

Benchmarks are a convenient way of comparing the capabilities of products. A benchmark should be a generic example of the tasks that the products are designed to perform. Its generic nature is equitable to all products. A designer looking at benchmark results is supposed to get an unbiased evaluation of the product, a true "apples-to-apples" comparison. When properly delineated, such benchmarks can yield more explicit information than a vague term like gates. For example, Andy's benchmark includes a counter/timer circuit. If one ASIC can implement four 8-bit counters and a designer has three 8-bit counters in his design, he can be reasonably certain that the ASIC can satisfy his need for counters. On the other hand, he can't compare the number of gates in his three counters with the number of gates in the ASIC and be certain that the ASIC has any counter resources.

The generic nature of a benchmark is also a liability. The benchmark may not exercise special features of a product that may enhance the use of a product for particular applications. By the time a set of benchmarks expands to incorporate all relevant details, it may be unwieldy. In addition, the designer may believe that a benchmark is the final word on density when in fact it is only another vardstick.

Although we acknowledge the problem, we're not completely sold on Andy's solution. Please write or call us with your opinions and, if you agree with Andy, your suggestions for density benchmark circuits.

David Smith

Western Regional Editor

# The One Week Analog ASIC.

#### The leading technology . . . the best support . . . go!

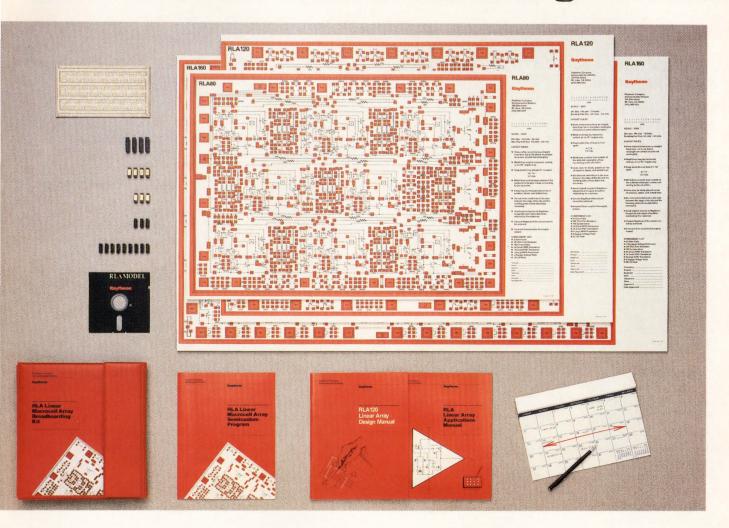

The leading analog ASIC family: RLA80, RLA120, and RLA160 user-configurable macrocell arrays. On-chip thin film SiCr resistors and dual-layer metal for ease of interconnect routing and maximum array utilization and performance. Wide supply voltage range —  $\pm 1V$  to  $\pm 16V$ . And simplified design procedures that take days, not weeks.

□ Configurable macrocells: 8, 12, or 15 gain blocks in any combination as general purpose op amps, open collector output comparators, or as input amplifiers with ground sensing function for single-supply systems. RLA160 has a preconfigured onboard adjustable ±30 ppm voltage reference.

□ Thin-film resistors: on-chip SiCr resistors exhibit 1% matching and temperature drift characteristics comparable to discrete film resistors. High performance and high values (1.25 kΩ to 150 kΩ) handle a wide variety of applications.

□ Design support: The RLA Breadboarding Kit contains complete design and applications documentation, 200x plots, a pre-drilled printed circuit board, and 23 ICs. Friendly RLAModel software includes menudriven user interface program for PSPICE¹, SPICE² model library for RLA series, documentation files, and full screen editor. Not to mention the attention you get from applications engineers who have 15 years experi-

ence meeting custom and semi-custom requirements.

Call Raytheon for access to RLA program information and details on the RLA Macrocell Array Breadboarding Kit. We promise you a week that will go down in history.

Raytheon Company Semiconductor Division 350 Ellis Street Mountain View, CA 94039-7016 (415) 966-7716

PSPICE is a trademark of MicroSim Corporation.

SPICE developed by University of California.

Access to the right technology

#### 1988 IEEE International Solid-State Circuits Conference February 17-19, 1988 San Francisco Hilton San Francisco, CA

The ISSCC, sponsored this year by the IEEE Solid-State Circuits Council, the IEEE San Francisco Section and Bay Area Council, and the University of Pennsylvania, provides the foremost global forum for the presentation of advances in solid-state circuits. Session topics will include high-speed digital circuit techniques, gate arrays, integrated signal-processing subsystems, nonvolatile memories, high-speed logic, static RAMs, analog techniques, A/D conversion, dynamic memory, and ASIC design and interface circuits. For further information, contact Lewis Winner, 301 Almeria Ave., Coral Gables, FL 33134. (305) 446-8193.

#### Fourth Annual Computer Graphics New York February 22-24, 1988 Jacob Javits Convention Center New York, NY

The Fourth Annual Computer Graphics New York is an exhibition and conference devoted to the latest computer graphics technology. Topics to be discussed will range from advanced turnkey graphics systems to low-cost PCbased solutions. Conference panels will cover applications in business presentations, CAD/CAM/CAE, desktop publishing, biomedical applications, AV and multimedia presentations, aerospace, and television graphics and electronic effects. For additional information, contact David J. Small, Exhibition Marketing and Management Inc., 8300 Greensboro Dr., Ste. 1110, McLean, VA 22102. (703) 893-4545.

#### Compcon Spring 88 February 29-March 4, 1988 Cathedral Hill Hotel San Francisco, CA

Sponsored by the IEEE Computer Society and the Institute of Electrical and Electronics Engineers Inc., Compcon Spring 88 will be a broad-based conference for computing professionals. Compcon will begin with a day of tutorials entitled Software Reuse Update,

VHDL Tutorial, Computer Architecture Choices, and Software Quality Control. As the conference progresses, it will feature topics such as processors, workstations, artificial intelligence, high-performance computer systems, parallel processing, software engineering, computer-aided design, legal issues, neural networks, and databases. Compcon will conclude with a day of tutorials entitled An Introduction to Artificial Neural Networks, Microchannel Interfacing, and Fault Tolerant Distributed Software. For additional information, contact Hasan AlKhatib, Dept. of EECS, Santa Clara University, Santa Clara, CA 95053. (408) 554-4485.

#### Southcon/88 March 8-10, 1988 Orange County Convention/ Civic Center Orlando, FL

Southcon is dedicated to facilitating the transfer of technology among electronics professionals. This seventh annual exhibition and convention will use as its theme "The Leading Edges of Technology" and will feature technical sessions and tutorials, as well as a special purchasing conference. Sessions will include Advances in High Performance Silicon Cache Controllers, Productivity and Computer Applications, Medical Electronics, Programmable Logic Based Sequencers, and PC Building Blocks for Industrial Applications. For more information, call Alexes Razevich at (213) 772-2965.

#### 2nd Annual ESD/SMI Expert Systems Conference and Exposition April 26-28, 1988 Hyatt Regency Dearborn, MI

This conference will assemble users with existing needs and applications, suppliers offering expert-system solutions, and researchers who are improving and expanding the capabilities of expert systems. Topics will include analysis, configuration, control factors, design, diagnosis, documentation, engineering, enhancement, integration into mainstream, operations, real-time systems, production, simulation, scheduling, scoping, system development,

training, user interfaces, and validation. Additional information may be obtained by calling the Expert Systems Planning Committee at (313) 832-5400.

#### 1988 International Symposium on Microelectronics October 17-19, 1988 Washington State Convention Center Seattle, WA

Papers are being solicited for presentation at the International Symposium on Microelectronics, sponsored by the International Society for Hybrid Microelectronics. Topics of interest include automation, hybrid design, interconnections, sensors, fiber optics, microwave, CAD/CAM, and manufacturing technology. Authors should submit abstracts by March 1 to ISHM '88 Call for Papers, P.O. Box 2698, Reston, VA 22090. Questions concerning the submission of abstracts should be directed to Charles Bauer at (503) 627-4908.

#### 1988 Government Microcircuit Applications Conference November 8-10, 1988 Riviera Hotel Las Vegas, NV

GOMAC is a government-sponsored conference established primarily to review developments in microelectronics applications for government systems. This year's conference, with the theme, "International Competitiveness: Its Impact on Government Electronics," is soliciting papers for presentation on topics such as VHSIC and MIMIC insertion, computer systems, fault-tolerant systems, ASICs, CAD/CAM/CAE, and signal processing. In addition, solutions to the unique requirements of government microelectronic systems in the following are being solicited: avionics, discontinued parts, quality assurance, and radiation hardness. By March 16, authors are requested to submit double-spaced summaries not exceeding 2 pages to Palisades Institute for Research Services, Attn: Jay Morreale (G-88), 201 Varick St., Rm. 1140, New York, NY 10014. For more information, contact C. Edward Holland Jr., GOMAC-88 Technical Program Chairman, Semiconductor Research Corp., Research Triangle Park, NC 27709. (919) 541-9400.

#### Sea-of-Gates Arrays

Oki Semiconductor Inc. (Sunnyvale, CA) and Gould Inc.'s Semiconductor Division (Santa Clara, CA) join the ranks of vendors of sea-of-gates gate arrays. Oki has adopted an architecture reminiscent of that from the now-defunct Integrated Logic Systems Inc. The arrays contain rows of dedicated flip-flops separated by 11 rows of sites for logic gates. Oki claims that its architecture heralds a "third generation" of sea-of-gates arrays whose special structures, including upcoming transmission gates built from polysilicide, create semicustom ICs as dense as those built from standard cells. The new arrays are built with 1.5-µm CMOS technology and can implement designs as large as 50,000 gates.

The GC series from Gould features nine arrays with gate capacities as high as 40,000 gates. The typical utilization is around 35%, so that designs as large as 14,000 gates can be implemented. Utilization is expected to double later this year as new design software becomes available. The parts are built with 1.2-µm drawn channel lengths, two layers of metal, and 100-MHz operation of D flip-flops.

#### 32-Bit Architecture from Japan

Hitachi Ltd., Fujitsu Ltd., and Mitsubishi Electric Corp. have implemented a 32-bit microprocessor and three peripheral chips that support Japan's bid for a new 32-bit architecture. The Real-Time Operating-System Nucleus (TRON) was developed by Ken Sakamura at Tokyo University to span a wide range of computing machines, from personal computers to supercomputers. It is regarded as the three companies' challenge to Motorola's and Intel's dominance of the 32-bit microprocessor market.

The microprocessor and support chips are called the GMICRO/200 family. The microprocessor is rated at 4 Whetstone MIPS and has a 32-bit, 4-GB physical address space. The most interesting peripheral is the DMA controller, which, with four DMA channels, handles data transfers between two buses and has a maximum transfer speed of 27 MB/s. A cache-tag RAM and an interrupt controller round out the chip set, which oper-

ates at 20 MHz and is fabricated in 1.2µm CMOS. The chips are scheduled to be complete (and, presumably, available for sampling) this summer.

#### **Retargetable CASE Tools**

Retargetable software development tools from Quantitative Technology Corp. (Beaverton, OR) can be customized by designers to produce code for custom hardware architectures. The Software Foundry comprises a compiler, an optimizer, a simulator, a symbolic debugger, and a combination of assembler, linker, and formatter.

The assembler-linker-formatter, available now, is customized by the designer, using a proprietary hardware description language. Once the designer has specified his architecture, the assembler produces object code for conversion into a program module by the linker and formatter for the target architecture.

The optimizer (available in May) compacts the microcode, taking into account parallel and pipelined operations specified in the designer's input of his hardware design and using a method called loop folding. It operates both automatically and interactively.

The rest of the tool suite will be available in September. It will cost \$50,000 for a workstation and \$90,000 for a VAX 8600 or 8800; it runs under the UNIX and VMS operating systems. Individual tools can be purchased separately.

#### Design Tool Kit

Sun Microsystems Inc. (Mountain View, CA) is releasing two more workstations based on its RISC processor, SPARC. The Sun-4/110 and -4/150 are similar to the Sun-3/110 and -3/150 models, with a SPARC CPU board replacing the 68020-based CPU board of the earlier workstations. The new machines are rated at about 7 MIPS and start at \$18,900. A Sun-4/110 with a floating-point accelerator, 327 megabytes of disk storage, tape backup, and a 19-inch monochrome monitor costs \$30,200. The Sun-4/150, which has additional slots for graphics options, will be available this summer; its introduction is delayed because of difficulty in getting memory devices.

With ACCESS, a software-resource controller program from Valid Logic

Systems Inc. (San Jose, CA), a user checks application software out from a network server and returns it when he is done. In contrast, most design software requires the user to be working on the network node that contains the software. ACCESS makes design software a shared network resource; a complete range of design software can be available to all users on a network without buying a version for each workstation. The company estimates that for an environment with 35 workstations, ACCESS can save \$125,000.

Aldec Co. (Newbury Park, CA) has reduced the price on its IBM PC-based SUSIE simulator to just \$295 and has removed its software protection. New options include modeling of PLDs from JEDEC fuse maps (\$795), a library of 160 types of RAM devices (\$795), and a model compiler that converts Boolean descriptions of a device into assembly language models (\$195). The simulator accepts designs created with the schematic capture tools from OrCAD.

SIMCOMPARE, from Logic Automation Inc. (Beaverton, OR), compares the output from different simulators and flags significant differences, according to parameters defined by the user. The results are formatted, classified, and presented as either functional or timing differences. The first license (for Apollo workstations) costs \$8000; subsequent licenses cost \$2000.

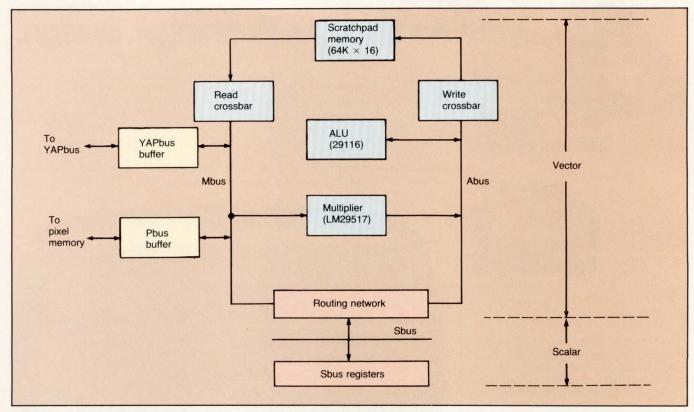

#### 33-MFLOPS Chip Set

A CMOS floating-point chip set from Integrated Device Technology Inc. (Santa Clara, CA), the IDT721264 multiplier and IDT721265 ALU, can execute 32-bit operations at 33 MFLOPS and 64-bit operations at 25 MFLOPS. It conforms to IEEE Standard 754 version 1.0 and is pin-compatible with Weitek's WTL 1264/1265 chip set.

The chips have a pipelined architecture that operates with 30-ns clock periods. Flow-through latency is 180 ns for 32-bit arithmetic and 270 ns for 64-bit arithmetic. Single- and double-precision operations run at 16.7 MFLOPS in the ALU; single- and double-precision multiplication occurs at 16.7 and 8.3 MFLOPS, respectively. The chips come in 144-pin PGAs and cost \$406 each (100).

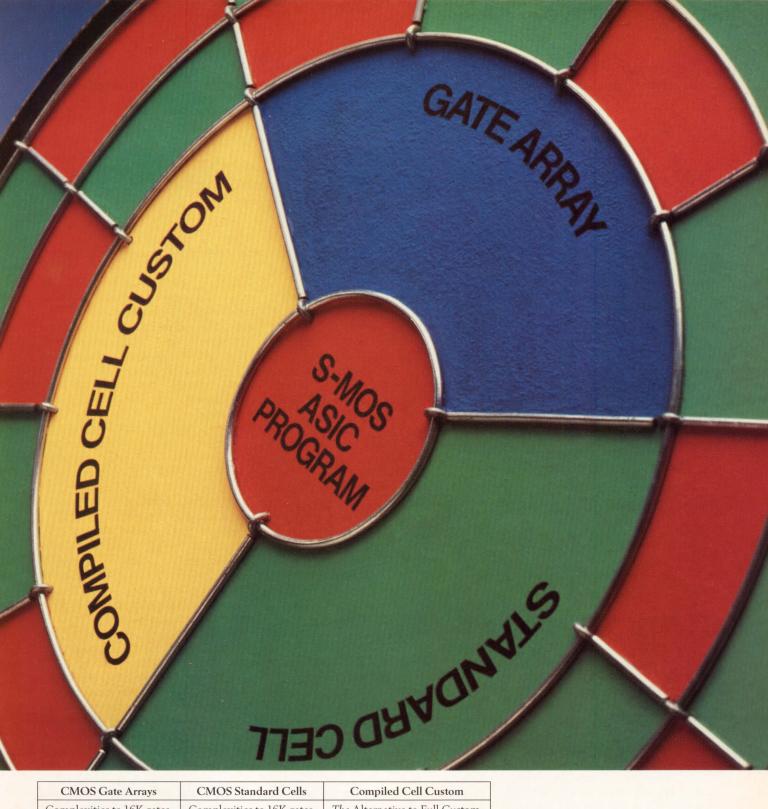

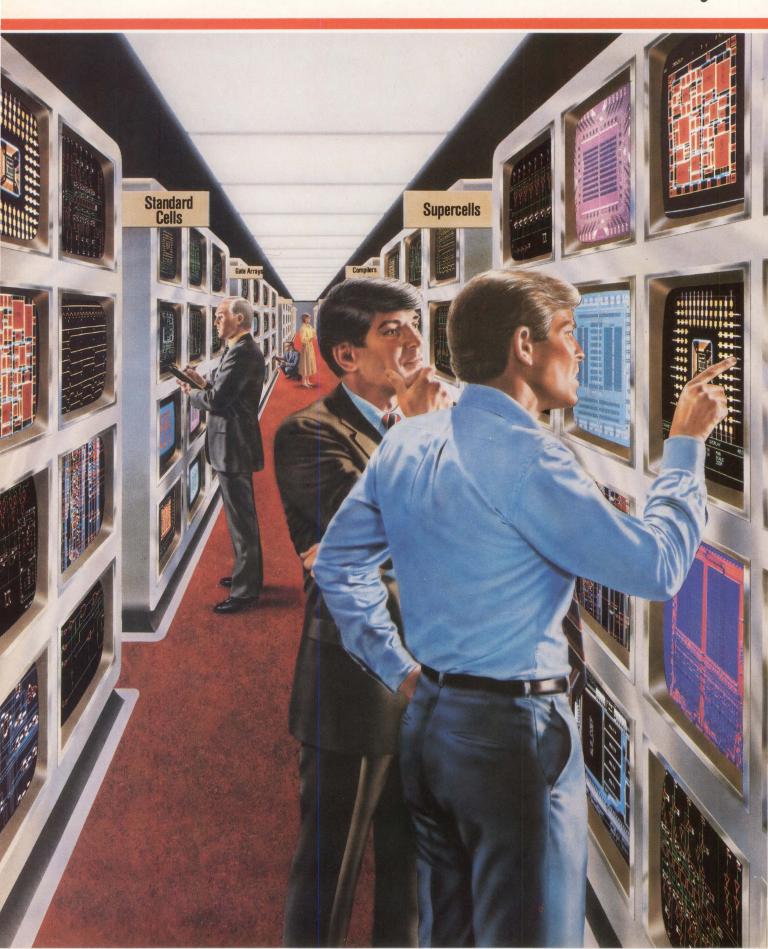

# In gate arrays, standard cells or Compiled Cell Custom, you'll always score with S-MOS.

Complete design tools.

S-MOS SYSTEMS supports a large and growing number of workstations, including Daisy, Mentor, Calma and PCbased systems using FutureNet, Orcad and Viewlogic. Our proprietary LADS simulator is one of the fastest in the world, and our engineering support will keep you ahead of the competition.

#### Advanced manufacturing.

Our manufacturing affiliate, Seiko Epson, is one of the world's most advanced CMOS IC manufacturers, with 18 years of CMOS experience. At our highly automated Class 10 facility in Japan, Seiko Epson can produce 40,000 4" wafers, 20,000 5" wafers and 20,000 6" wafers. Each month.

That's a total equivalent of about 23 million units a month.

High quality and total reliability.

With a product reject rate of less than .0001%, S-MOS and Seiko Epson deliver the ASICs you can depend on.

For a fully integrated ASIC program, call us. (408) 922-0200.

S-MOS SYSTEMS 2460 North First Street San Jose, CA 95131-1002

| CMOS Gate Arrays                                                                                                                                                                                       | CMOS Standard Cells                                                                                                                             | Compiled Cell Custom                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Complexities to 16K gates • SLA8000 (500ps)* 1.2 μ drawn, 0.95 μ Leff • SLA7000 (640ps)* 1.5 μ drawn, 1.2 μ Leff • SLA6000 (1.3ns)* 2.0 μ drawn, 1.7 μ Leff • SLA5000 (2.2ns)* 3.0 μ drawn, 2.3 μ Leff | Complexities to 16K gates  • SSC1000 (720ps)*  1.8µ drawn, 1.5µ Leff  • Fully migratable from S-MOS gate arrays  • RAM and ROM blocks available | <ul> <li>The Alternative to Full Custom</li> <li>1.5μ CMOS Process</li> <li>Can utilize dissimilar cell geometries</li> <li>3-button approach to custom design</li> <li>Currently over 300 fully characterized cells</li> <li>Fast 14-week implementation time</li> <li>Timing-driven TANCELL* Place-and-Route Software</li> </ul> |

| *Typical propagation delay of 2-input NAN                                                                                                                                                              | ID gate driving 1 internal load including 100                                                                                                   | $0\mu$ interconnect.                                                                                                                                                                                                                                                                                                               |

\*TANCELL is a registered trademark of Tangent Systems.

## John Eurich Brings Engineers Together

ohn Eurich has the ability to create consensus from a group of disparate ideas. In a room of people, brainstorming, he can often "put together the pieces" and build an understanding.

"I was never an R&D soloist," he says; "I've always been a team player." His career has been a string of assignments to pull together people and ideas to get the job done. His new job—president of DataXpress, a three-man company developing translation tools for engineering databases—builds on that string. DataXpress is a focal point for engineers needing to pull together design environments.

John himself is a focal point of ideas, a trait that has made him an effective manager. Even off the job, he reads textbooks instead of, say, novels for relaxation. Afraid he may miss important insights by not using his time wisely, he believes that "you never know what will trigger an idea."

John began to put together the pieces of his specialty after his education at San Diego State University and in the Navy. As a "grunt programmer" at Xerox in El Segundo, CA, he designed interfaces between the company's fledgling CAE

system and its manufacturing floor.

"I lived the problem" of database translation, he says. "It was hell."

For example, an interface between a CAE system and a piece of autoinsertion equipment must provide the physical height of every component, as well as its coordinates on the board. As John learned to create the interfaces that made such data interchange possible, he rose to become the manager of the group developing VLSI CAD tools.

In subsequent posts at Calma and then Daisy Systems, John continued to build design teams and manage technology development. While at Daisy, he was pulled into the committee developing the then embryonic Electronic Design Interchange Format, EDIF. Not surprisingly, he ended up heading the committee.

Upon leaving Daisy, John turned his hand to serving as a consultant about the use of EDIF as a translator for design environments. After almost a year, "I got so hooked on the whole problem that I started a company to continue the effort," he says. He founded DataXpress in early 1986.

"We want to own data translation," he boasts, although sometimes it seems that EDIF owns John. "I got caught up in data translation because of my work in EDIF. As long as there seems to be a path to take, I'll be taking it."

John explains that there's more to establishing EDIF than just coming up with the present version, EDIF 2.0. Expecting this version to leap into immediate use is "like handing someone a dictionary and telling him to learn English." To develop an EDIF translator, you have to have a good working knowledge of the standard.

DataXpress's flagship product is the EDI (Engineering Data Information) translator development environment. This environment includes an EDIF reader (parser), an EDIF writer, a syntax checker, a semantics checker, and the EDI database, which has its own proce-

dural interface for retrieving and storing

Users of EDI need only develop the readers and writers from their own database to the intermediate format. They don't have to worry about reading or writing EDIF files, creating data structures, and moving data into and out of the data structures (because of the procedural interface). "Let us worry about the more esoteric details of EDIF syntax," John says.

An intermediate format may seem redundant. When an interface designer has to map one data format to another, however, he won't get data out in the right format and sequence that he needs. As a result, interface designers spend most of their time creating a parser and determining what the temporary data structures will be. Designing the best data structures to solve the mapping problem is, according to John, "gut-wrenching."

He defends the EDIF standard against those who still think it is insufficient for translating CAE data. "EDIF can transfer symbols and logic models just fine," he says

He admits that there's a need for a standard for symbols, but whatever standard results, EDIF can support it. He suggests that one CAE company should offer its symbols as a standard, telling its customers to insist to other CAE companies that they support the same symbols. A consensus-building snowball effect, similar to that which doomed copy-protected software, should result.

"There is an EDIF effort because the industry has a need to transfer information," John reiterates. Engineers need to share design data with other engineers, design teams, and even engineering disciplines. Defining the methods and formats to make the interchange easy and accurate won't be easy, but John Eurich is positive, even reassuring: "I know there's a solution; we just have to get together and find it." —David Smith

### WHAT YOU SIMULATE IS WHAT YOU GET

#### Be sure product performance matches simulation

#### Get Optimal Accuracy in Circuit Simulation with HSPICE and ATEM

Accurate model equations and algorithms provided by HSPICE

Model Parameters derived from Silicon by ATEM

Advanced equations and algorithms have made **HSPICE** the logical choice for accuracy in simulation throughout the industry. Meta-Software now complements **HSPICE** with the **ATEM** system for generation of optimized model parameters.

**ATEM** is based on the **SUXES-10** parameter optimizer. The **MetaTestChip** provides all the data needed by SUXES-10 for complete HSPICE models with full temperature compensation. ATEM subsystems automatically take the necessary data from the MetaTestChip by driving HP and Tektronix laboratory equipment.

With ATEM, a complete process characterization can be completed in a single day.

ATEM provides complete and optimized CMOS, BIPOLAR and GaAs model parameters. If you are using BiCMOS and need accuracy in simulation, ATEM and HSPICE are the ideal answer.

CRITICAL PATH TIMING ANALYSIS: For path timing analysis of very large scale digital MOS designs, consider Circuit PathFinder (CPF). CPF has been successfully used to analyze circuits of over 500,000 transistors. CPF uses transistor level simulation based on HSPICE models for accuracy.

CPF provides an easier way to determine changes in critical path timings introduced by the layout process.

#### **NEW HSPICE FEATURES**

- Discrete Component Models based on lab measurement:

- \* A sample library is included free with HSPICE

- \* A large library is available for a fee

- Measure Statement: simplifies Cell Characterization

- BSIM, CASMOS and Fluke MOS models

- Statz GaAs model

- Additional temperature compensation for Bipolar and MOS models

- · Geometry-based MOS model selector

- Wire model

- Pole-Zero analysis

- Automatic Op Amp Macro generator

- Switches: Voltage controlled resistors

- Ideal Inverters

- "FAST" option for greater speed

- Interfaces to Tektronix and Mentor workstations

In-house evaluation copies of HSPICE are available to qualified customers. Contact Meta for details.

Meta-Software offers laboratory services for process characterization, based on the MetaTestChip, and for discrete device modelling.

#### Meta-Software, Inc.

### Tools vs. Data: The Debate for '88

Tony Zingale, EDA Systems Inc., Santa Clara, CA

ool users and vendors tend to focus on tool functionality-and rightly so! Functionality is the heart and soul of a good design tool. Productivity, efficiency, and migration also are fundamental issues-although perhaps secondary to functionality. However, while these four aspects of a tool can be improved, the data generated by the software is really more important to users. Isn't the data where the real value of the design is held? How is the data generated by the design process tracked and management? What tools focus on that dimension of design automation?

Data management issues have been festering in the design automation community for several years, for good reason. The Technology Research Group reports that the installed value of design data in 1987 was more than 10 times the value of the installed base of tools. Unfortunately, tool vendors are only just realizing the significance that the design data holds to users.

The value of the tools versus the value of the data the tools generate is best understood by the replacement cost of the two. To replace a tool, a user can purchase another copy of the software, with a minimal amount of down time. On the other hand, replacing the design data, if it is possible, requires an incredible time sink. In most cases, a company cannot afford the time.

Let's consider an example. A company buys a schematic entry package with its own user interface and a proprietary database from one vendor. It then buys a logic simulator with a textual user interface and a high-performance application database from another vendor. To exchange data, the buyer uses netlist interfaces or database translators, both of which are time-consuming to develop and even more costly to support and maintain. Companies usually focus on making the tools work instead of on maximizing the productivity of the entire process.

Some tool manufacturers have acknowledged that their tools will be used with tools from other vendors. Even so, users cannot be assured that a single supplier will provide the best tool for a future project. And even when one vendor has all the right tools, the design data is not necessarily well managed within the vendor environment. Users still have to distinguish between data compatibility and data management.

To achieve a system with real data management, a different approach is required. Some sort of electronic design automation "framework" is needed to support the infusion of tools from any source, even in-house proprietary tools, and manage them in the context of the entire design process. The framework should house design management tools that track the intricate relationships between the data, tools, projects, and users. It should be flexible enough to allow change. It should accommodate the reuse of portions of a project completed with a tool set from a previous project. Finally, it should be able to run on the user's choice of platforms and conform to the user's specifications.

Who best supplies such a framework? There are four potential sources: a design tool supplier, a computer manufacturer, an internal development team, or a third party who supplies only the framework and nothing else.

Design tool suppliers and computer manufacturers inevitably force a migration path on their users, or at least give a certain direction to them. Their main interest is in protecting the software or hardware purchases made through them, not to protect a user's data investment.

Some users therefore develop a solution internally. Many users can recount the nightmares associated with developing such a framework. It is a mammoth effort and a major time and resource drain. In most cases, the framework must be reworked for each project, because the problem is dynamic whereas the internally developed solution is static. The user's expertise is in designing, not in making the tools more manageable.

Independent framework suppliers, who supply only framework tools, have no vested interest in any particular tool or platform. It is their charter to provide an overall "open" framework that will let users plug in and manage the data on any tool they want. It is their charter to accommodate new and future tools as they become available and to manage those tools independent of platform, tool vendor, and database structure.

If progress is to be made, the data must be managed, the tools must be managed, and the overall design process must be managed. Framework suppliers are paving the way for that to happen in 1988.

Tony Zingale joined EDA Systems as director of business development in September 1986. Prior to that he spent three years in various management positions at Daisy Systems. Before that he worked for three years at Intel.

# For complex designs, HELIX is the "what if" simulator!

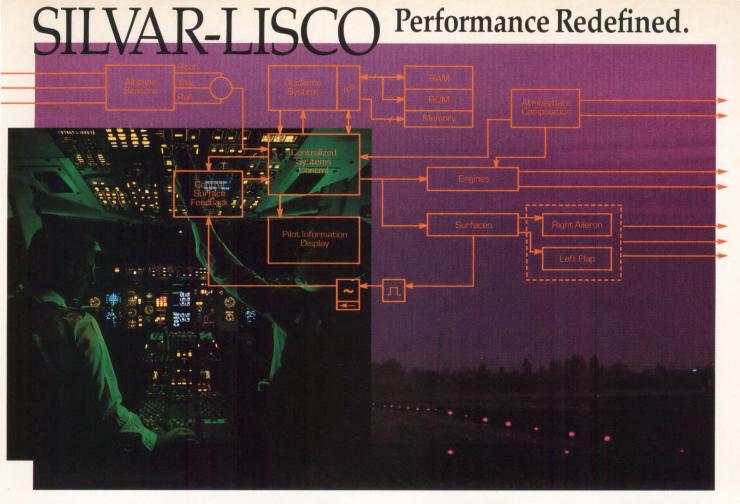

When designing large systems, printed circuit boards or VLSI/VHSIC chips, simulation becomes an invaluable aid. Logic, switch level and circuit simulators are excellent tools for validating design implementations. Silvar-Lisco's Helix Behavioral Simulator takes you one giant step further. In addition to design validation, system architects now can optimize the design itself through analysis of various implementation alternatives.

With Helix you can define and test your system concepts first. If the concept works, you move down to the register level. Then the gate level. Multi-level throughout. If it doesn't work, you can rethink the concept and probe Helix with additional design alternatives. In the end, you will get the best design. The first time.

Helix is a vital component of Silvar-Lisco's Architectural Design Series. Incorporating

design capture, simulation and design libraries, the Architectural Design Series gives you the competitive edge.

Be a design winner! Contact Silvar-Lisco today!

#### SILVAR-LISCO OFFICES

Corporate Headquarters 1080 Marsh Rd. Menlo Park, CA 94025 TEL: (415) 324-0700 WATS: 1 (800) 624-9978 TWX: 910-373-2056 FAX: (415) 327-0142.

European Headquarters Leuven, Belgium TEL: 32-16-200016

TWX: 221218 FAX: 32-16-236076

Far East

Nihon Silvar-Lisco Tokyo, Japan

TEL: 81-3-449-5831 FAX: 81-3-449-4040

Architectural Design Series

#### SILVAR-LISCO

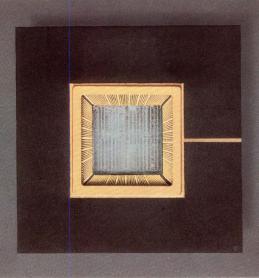

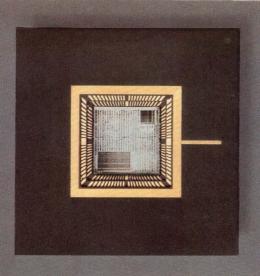

# Aluminum Screen Gives Superior Power Distribution in a Sea-of-Gates Array

Richard Blumberg and Charles Waggoner, SGS-Thomson Microelectronics, Carrollton, TX

oor power distribution schemes can cripple even the best sea-of-gates designs. They can result in difficult-to-test designs with poor yields and poor reliability. A good power distribution structure and methodology are far more likely to yield reliable first-pass silicon.

In designing a 1.2-µm sea-of-gates array with 128,000 raw gates, SGS-Thomson Microelectronics used an augmented aluminum "screen of power" and a novel controlled-skewrate I/O design to produce nearly bulletproof power busing.

Poor power distribution in a sea-of-gates array is not well recognized. Poor distribution on the chip results in noise at the system level. Unfortunately, there are no tools to help predict these problems before testing. The chips have unpredictable yields and the boards have unpredictable yields. When the customer gets the part, it sometimes works in his system and it sometimes doesn't.

One reason for the paucity of analytical tools is that each application places different demands on the distribution system. For example, the number of simultaneously switching internal circuits and drivers will vary with circuit topology and data flow. Therefore certain assumptions must be made. When an ASIC manufacturer designs the master slice of the array, he designs it for general use, with no specific application in mind, yet he has to provide a technology that any customer can use or, perhaps, abuse.

Power distribution problems are often first encountered during testing. That is when one finds that it becomes necessary to overdrive the inputs to make the ASIC work, and overdriving calls for broadening the drive specifications. The first clue that noise is being injected is that, when the I/Os or internal circuits are switching, the switching-current change causes the ground to rise, and V CC to collapse, reducing the voltage across the receiver, internal latches, and flip-flops.

#### Coping with Noise

Because the noise generated depends on the system-level environment, power distribution problems at the chip level are difficult to analyze. It is hard to determine, for example, how much inductance and decoupling the system will provide. One cannot know in advance if the part will be socketed or not, how well system power will be distributed, and how many drivers switch simultaneously.

Some designers are well aware of the problems of noise. Therefore they provide thick copper planes and well-decoupled power supplies. Others bring power in on a "yellow" wire and never think of decoupling capacitors. Thus even if there were an analytical tool, because of the vast differences in operating environments the array planner would never be completely sure what assumptions to make to use it. Further, the finished die may be housed in any of several packages, all with different inductances.

In sum, combining a highly inductive external environment with fast 1.2- $\mu$ m technology is bound to create transient switching problems. With on-chip delays of 300 ps, off-chip delays of 5 ns or less, and a voltage swing of 5 V, C × dV/dt produces a large current swing that must be accounted for.

Power distribution problems are aggravated by faster switching speeds and greater component density. Further, larger gate counts make it more likely that more internal circuits and I/Os will switch simultaneously. Larger arrays typically house circuits with wider data, address, and control buses—that is, 4- and 8-bit buses are giving way to 16- and 32-bit buses—again making simultaneous switching more likely. In short, high-performance, high-density sea-of-gates arrays are far less forgiving of power distribution problems than were their 2-µm-and-up forbears.

Power distribution in a double-layer metal ASIC is best accomplished on the second level, where the metallization is thicker and the resistance is the minimum. One leading sea-of-gates array distributes the power on the first level of metal. Then it automatically routes power on the second level, using wiring areas remaining after signal routing is completed. Unfortunately, as the array density (and hence the signal interconnection density) increases, fewer routable areas are available for power distribution. This approach clearly takes power distribution in the wrong direction.

#### Guessing about Abuse

A better approach is to make some assumptions about how the user will abuse the technology and to plan a conservative power distribution architecture and methodology that take those assumptions into account. It then becomes a question of making the right assumptions.

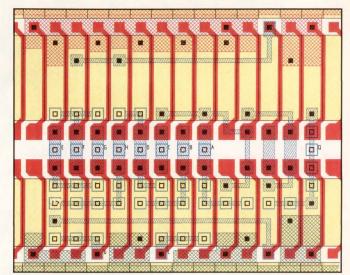

The architecture of the ISB12000 arrays shows the use of

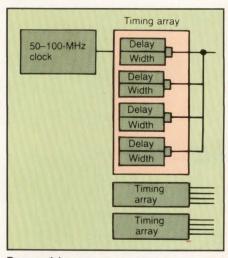

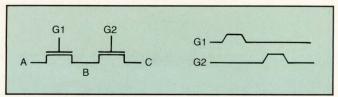

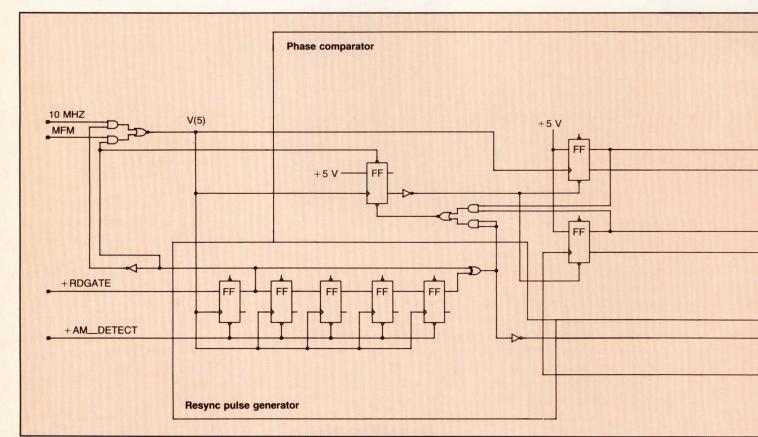

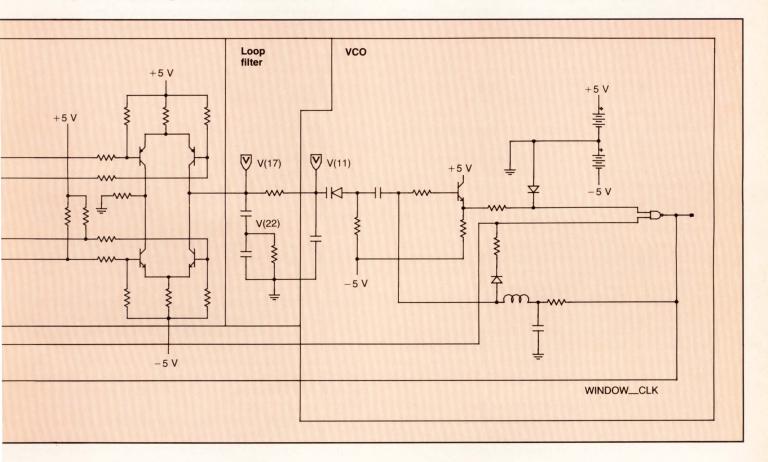

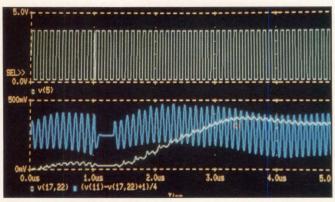

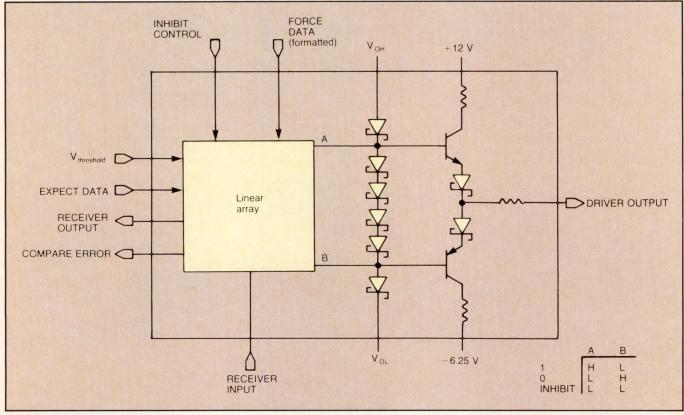

FIGURE 1. Power is distributed in this sea-of-gates array by a fine aluminum grid, then redistributed at every 25 columns of cells on metal layer two and between every row of cells on metal layer one.

reasonable assumptions. Power is distributed on a microlevel between cells by a fine aluminum power mesh. Figure 1 shows that power is distributed every 25 columns of cells on layer two and between every row of cells on layer one.

Instead of stacking cells, the cells are mirrored one on top of another. This arrangement allows for sharing power or ground buses between adjacent rows of cells, increasing the width of each bus to 4.6 µm and eliminating the need for the space between adjacent buses in stacked configurations. Wherever possible, this bus is widened further by the metallization associated with each macrocell.

But why is power distributed every 25 columns on level two? Once you decide to distribute power in fixed buses on level two (already a novelty), you must make some assumptions about the right periodicity of the power busing.

Three assumptions were made for the ISB12000. First, 40% of the raw gates will be used and a 10% safety margin left. Thus half the rows of gates are depopulated to allow for wiring interconnects. Second, the macro is assumed to be a 25-cell-wide inverter in a clock driver. Power is redistributed every 25 cells and a clock driver is used as a model because it gives the worst-case switching and transient currents. Third, the clock driver is assumed to switch rapidly, at 25 MHz.

A SPICE analysis showed that a single redistributed bus was sufficient to drive the clock driver while keeping the voltage drop and electromigration to acceptable levels. One 25-cellwide inverter/clock driver equals the bus periodicity of one redistributed second-level 10.8-µm-wide bus.

All the power used by the internal cell matrix originates at the power and ground pads at the chip periphery. Though the current feeding each row or each twenty-fifth column may be manageable on a microlevel, the currents are additive between buses. Without additional bus augmentation, by the time the currents approach the chip edges they will be excessive, so an additional set of buses is needed.

If current is forced to flow through small vias and narrow lands, electromigration will cause an outflow of aluminum ions, which will hurt reliability over time. Augmenting the

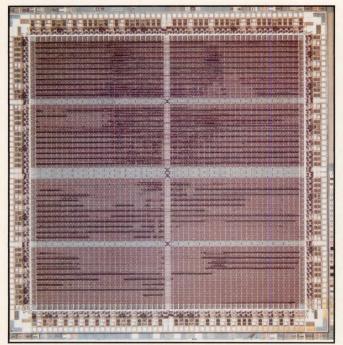

FIGURE 2. Augmented power buses appear here as three wide horizontal buses and one vertical bus.

power distribution buses helps prevents electromigration. A titanium barrier between the glass dielectric and the aluminum metallization provides further resistance to electromigration. It also prevents hillock formation between the silicon and the aluminum metallization.

To implement an augmented "coarser" mesh (one with larger pitch and wider conductors) requires the depopulation of both rows and columns. Typically, on the first level, two to four rows are depopulated every 20 to 40 rows to allow for a 150- to 300- $\mu$ m-wide bus. On the second level, 50 to 150 columns are depopulated in the center of the master slice to allow for a 300- to 900- $\mu$ m-wide bus. In Figure 2, 50 columns were depopulated in the center of the master slice.

This power distribution approach is particularly conservative. It minimizes design constraints, even for those who choose to operate the design out to the  $3-\sigma$  operating points. The scheme also allows operation under military environments without degrading performance.

There is more to the system than just the fine and coarse power grids that overlay the array. There is the effect on power distribution to the I/O cells and the matter of supplying power to the output buffers without affecting the array matrix or off-chip receiver circuits.

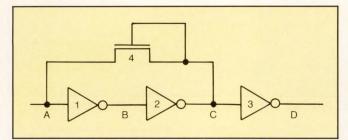

#### Six Power Rings

In the entire power distribution system, there are actually six power rings that surround the array core (see Figure 3). All six are distributed on second-level metal. The two outer rings supply power to the p-channel and the n-channel output transistors of the I/O drivers and are completely independent of the other power rings. The next four rings supply power to the internal matrix, and the predriver and receiver areas of the I/Os. The large output transistors can turn on simultaneously and not affect the internal matrix and receivers. The fine

FIGURE 3. The entire power distribution system of the ISB12000 sea of gates.

aluminum grid and the augmented power buses tie into the inner four rings. The augmented buses are then tied directly to the internal power supply chip pads.

Before proceeding further, one should evaluate the realestate penalty of an adequate power distribution system. Just how much silicon is sacrificed?

The best measure is the number of square mils per wirable gate. The ISB12000 achieves an average of 7 square mils per gate, an extremely attractive number using 1.2-µm design rules. Perhaps 6.5 square mils per gate might have been achieved with less attention to power distribution. But the additional area is a small price for predictable results.

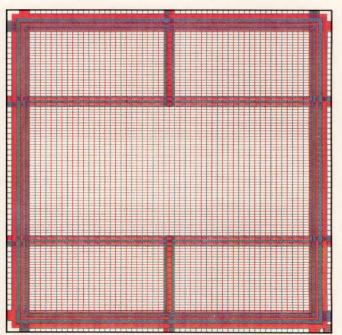

A desire to automatically generate master slices of various sizes had a major effect on the design of every macro cell. In particular, alignment of the macros with the power bus structure became an overriding concern, since the location of the cell contacts relative to fixed power buses could present a serious placement and routing problem.

The need to align cells with power buses is obvious. Another need was to be able to generate 10 arrays with 8000 to 128,000 raw gates without requiring a unique power distribution architecture for each array. The fixed grid and the array's symmetrical topology made it possible to use the Calma GDS II system's Graphic Programming Language to generate each master slice by simply defining the number of I/O cells on each side. The program automatically stepped the I/Os, the internal matrix, and the power distribution. The advantages of symmetrical geometry go far beyond the ability to rapidly generate master slices. It also simplifies coding for the place-and-route chip images; it makes the power distribution uniform over all cells, and hence it makes design rule checks (DRCs) constant between master slices. There is nothing unique in any one master slice.

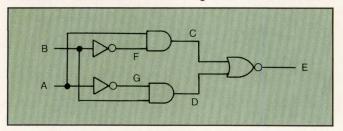

But what about cells that just happen to fall under a power bus? How do you connect to them if their connections are blocked? The second-level-metal power buses over the active internal matrix areas are two cells wide. Every internal macrocell is at least three cells wide. To ensure that every cell's input and output are accessible, even when the cell falls directly under a power bus, "antennas" are provided for each connection, as shown in Figure 4. One antenna carries at least three "hit" points, so that at least one hit point always sticks out. In fact, with macros, such as D flip-flops, that tend to use all the x-direction wires, there may be seven or eight different hit points per antenna for the A input, B input, Q output, D input, Reset, and so on. No matter where the cell falls relative to a second-level-metal power bus, the wiring program will always be able to make connection with every pin. In addition, the low-resistance polysilicide links that form the transistor gates facilitate interconnecting the macrocell metallization without using any second-level-metal routing channels.

The wiring program assumes that one hit point on each antenna is always a "protected" pin—a keep-out area during routing until the pin is connected. If the protected pin happens to fall directly under a power bus, the placement-and-routing software (Silvar-Lisco's Advanced GARDS) reassigns the protected pin to one of the unblocked pins.

#### Coping with Instantaneous Power

The fine and coarse aluminum power meshes and inner power rings distribute power to the inner array core, but we must also attend to the instantaneous power demanded by the output transistors, based on their slew rate. The ISB12000 has optional 2-mA, 4-mA, and 8-mA drivers without paralleling I/O cells. The 600-\(\mu\)m-wide drivers are capable of hefty slew rates of better than 200 mA/ns. If all the bits in a 16-bit or a 32-bit bus are firing simultaneously, an intolerably large current swing will result. This current swing can cause a dangerous noise spike. The best solution is to provide a slewrate control circuit in the I/O cell that limits the slew rate to approximately 20 mA/ns.

Using a slew-rate-controlled I/O also makes the off-chip delay almost independent of load. Whether you drive 20 pF or 100 pF, you get practically the same delay, because the slewrate control determines the rate at which the capacitance is charged or discharged. For example, if the slew rate is constant at 20 mA/ns, the driver delay is 6 ns  $\pm 1$  ns.

Besides slew-rate control in the I/O cells, the I/O pads have two clamp diodes electrically connected, one from the pad to V<sub>CC</sub> and one from the pad to ground. These clamp diodes prevent reflections from open-ended transmission lines from doubling and causing false switching and sharper waveforms. The driver circuit also contains short-circuit protection that limits the current through the output buffers during a lowimpedance fault.

#### Spare the Power and Spoil the Package

If attention is not paid to power distribution on chip, special attention will have to be paid at the package level to minimize package inductance, perhaps using ground planes in a custom-tooled package with fixed power and ground. As a direct benefit of careful attention to powering at the chip level, open-tooled packages can be purchased from off-the-shelf suppliers. One can easily satisfy an application requiring specific power pin assignments, and it is easy to provide additional power pins for bus-oriented designs with highpower output buffers.

FIGURE 4. "Antennas" at each connection ensure accessibility to each cell's input and output even if the cell falls directly under a two-cell-wide power bus.

At about \$15,000 in tooling costs per package, using custom-tooled packaging is expensive. With open-tooled packages, there is no packaging NRE and there is approximately a 50% saving in the per-piece price. Further, lead times for custom packages can extend to 26 weeks, whereas open-tooled parts may be available overnight.

#### Cutting Delays, Skewing

Good power distribution on chip also can reduce delay tolerances and clock skew, which can result from voltage distribution variations of as much as 0.5 V around the chip. Latch-up characteristics improve, too, for several reasons: First, the slew-rate control cuts noise. Second, one can tie down the substrate, the p wells, and the n wells so that the chip itself is less susceptible to noise-induced latch-up. In fact, one can push or pull more than 750 mA through any signal I/O without inducing latch-up.

#### About the Authors

Richard Blumberg, director of advanced array development, joined SGS-Thomson Microelectronics (formerly Thomson Components-Mostek Corp.) at its inception in November 1985. He was previously with UTC Mostek, and before that with IBM, where he managed the design and development of semicustom bipolar products. He earned a BSEE from George Washington University in 1968.

Charles Waggoner, senior design engineer of advanced array development at SGS-Thomson Microelectronics, joined predecessor UTC Mostek in June 1983. He has been involved in CMOS gate arrays and, from 1968 to 1983 at IBM, in the design and development of semicustom bipolar products.

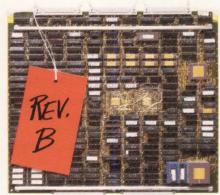

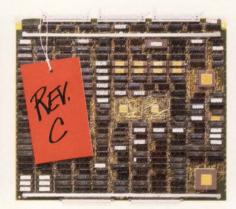

# ONE PROTOTYPE THREE PROT FIVE PROTOTYPE SEVEN PROTO

## Teradyne's new CAE tools help you get to market faster by

Designing VLSI circuit boards that work the first time isn't child's play. You can't do it without fast, accurate feed back on design and test quality.

Now count on Teradyne to help. With our new family of CAE products, you'll uncover flaws before they're cast in hardware. So you'll be able to jump from initial design directly to final prototype. And from design to manufacturing test.

Start with a firm design foundation.

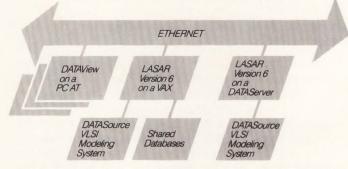

The process starts with DATAView our new design entry system. Running it on a standard AT-class PC, you can control the whole design process right at your desk. From schematic entry and waveform analysis on the PC to simulation and fault simulation on more powerful networked computers. All with the same mouse-and-menus, multiple-window interface.

You move from schematic capture to simulation effortlessly. DATAView's links with our LASAR Version 6 simulation system save hours of model compilation time.

Incremental compiling lets you revise a design and resimulate in minutes.

Make your design work together before it comes together.

LASAR Version 6 is the only sure way to avoid multiple trips to artwork as well as costly rework steps in manufacturing. Because its simulation accuracy is unmatched

Teradyne networks advanced CAE tools for convenience and performance.

# TWO PROTOTYPE, OTYPE FOUR, SIX PROTOTYPE, MORE.

## giving you a working prototype the first time.

for analyzing PC board designs prior to prototyping. For instance, LASAR takes full device timing specifications into account for true worst-case timing analysis. And it eliminates shared timing ambiguity in reconverging signals. Both of which mean LASAR finds real design errors reliably.

Finally, you can use LASAR fault simulation. It will uncover testability problems and untested circuit functions before it's too late.

#### Simulation without trial and tribulation.

LASAR also takes care of the board modeling problem. It includes models of over 4000 devices. And the most popular gate array libraries.

For new VLSI parts, our DATASource hardware modeling system uses actual devices instead of software models. A single system supports multiple users and concurrent fault simulation. With extraordinarily fast response

LASAR and DATASource work with any VAX. For

simulations up to 25 times faster, you can use our new parallel/multiprocessing host, DATAServer. It will give you quick results, with full LASAR precision.

#### Teradyne makes it easy.

If you want to avoid multiple prototypes and get to market faster with better products, Teradyne's new CAE system is the way. Why not call Daryl Layzer at (617) 482-2700, ext. 2808 for more information. Or write Teradyne, 321 Harrison Avenue, Boston, MA 02118.

VAX is a trademark of Digital Equipment Corp. AT is a trademark of International Business Machines Corp.

# The Integration of Graphics and Imaging Systems

David Smith, Western Regional Editor

orkstations are now the predominant form of computing power for technical and business professionals. They run application programs previously found only on supermincomputers and so put more powerful software in the hands of more people.

These applications require greater display quality and interactivity than the products previously running on the desktop. More information is presented at once, such as three-dimensional images, graphs, charts, and colors. Each of the new workstations has to have the image-rendering power once found only on terminals tied to a supermini.

These two reasons explain why all computers are becoming commodity items. Why put 10 MIPS into a workstation when you can't view the results in a meaningful, productive display? In addition, the cost of all other computer subsystems is coming down fast. A 1.5-MIPS workstation costs \$5000; five years ago it cost 10 times as much. Graphics and imaging systems are under the same pressures to deliver higher functionality at a lower price. However, the use of VLSI devices to reduce cost and improve throughput is hampered by the peculiarities of graphics and imaging architectures.

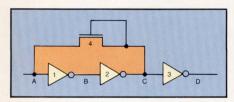

#### **Image Computing**

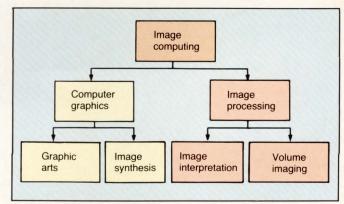

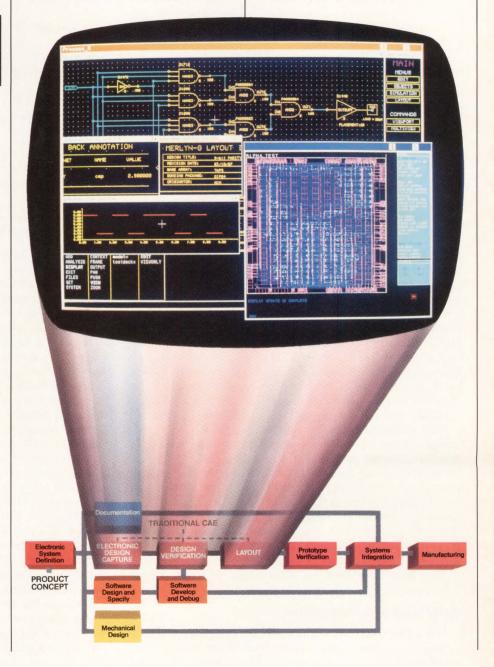

The terms *graphics* and *imaging* are sometimes used interchangeably. A convenient classification comes from Pixar Corp. (San Rafael, CA), which lumps both terms under *image computing* (see Figure 1). In Pixar's scheme, under computing graphics, two-dimensional systems are used for graphics arts, including CAD and publishing. *Image synthesis*, the 3D leg of computer graphics, includes the modeling of 3D images from mathematical models.

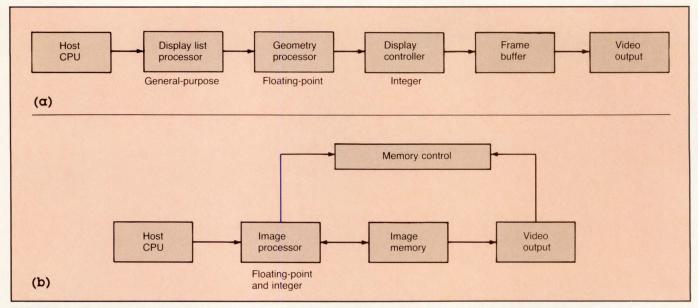

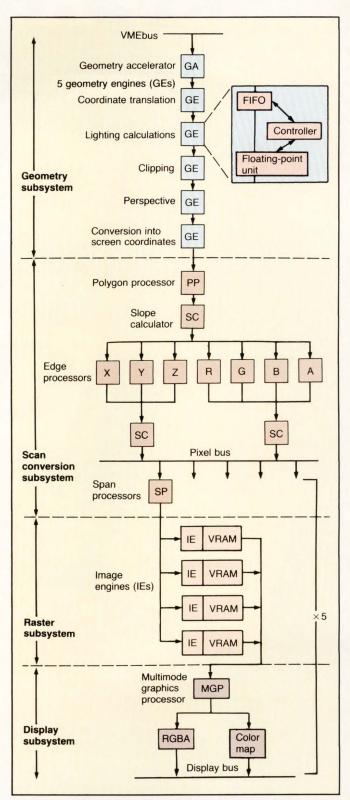

Under *image processing*, 2D image interpretation includes map making. Volume imaging, the 3D portion of image processing, includes medical imaging, in which 2D sections of a body are constructed into 3D representations. In this view, therefore, image processing differs from graphics in that the basic data is an image built of pixels, whereas graphics systems receive data as models. As shown in Figure 2b, the memory-processor interface is more closely linked in imaging systems. Figure 2a, the graphics pipeline, shows how the memory of graphics models, the display list, is just the beginning of a graphics pipeline. It feeds a succession of processing steps, many of which can be implemented as VLSI devices.

VLSI devices for the display end of the graphics pipeline are available because the drawing of pixel data on a givenresolution screen is a well-defined process. For example, memory devices that translate a pixel description into a color—color lookup tables—are combined with digital-to-analog converters to form complex analog-digital output devices.

VLSI devices also are used to control access to the memory that contains the pixel data—the *frame buffer*—from both the host CPU and the video output circuits. Such *display controllers*—the Hitachi 6845, for example, used in the IBM PC XT—can often perform rudimentary logical operations on the pixel data.

More advanced VLSI display controllers draw and manipulate pixel data, such as drawing lines, and may also fill in patterns and move images around the screen. These *graphics processors* are available from Advanced Micro Devices Inc. (Sunnyvale, CA), Hitachi Ltd. (Tokyo), Intel Corp. (Santa Clara, CA), National Semiconductor Corp. (Santa Clara), and Texas Instruments Inc. (Houston, TX). They perform integer and logical calculations while drawing the two-dimensional images.

To create the data that describes the 2D image, geometry processors accept mathematical models of objects and commands to alter the position and orientation of those objects. They calculate the position of the objects and the effects of lighting and clipping. Then they pass 2D coordinate and color information to a display controller for rendering in the frame buffer. Graphics processors must perform a variety of floating-point algorithms, such as  $4\times 4$  transformations. They are implemented, therefore, with general-purpose floating-point processors, like the 3332 from Weitek Corp. (Sunnyvale), and controlled by microcode that implements the designer's specific algorithms.

The retrieval of mathematical models and graphics commands is managed by the *display list processor*. The graphics system's host CPU, running the application software, usually constructs a list of objects called the display list. The display list processor receives the commands to be executed, retrieves the objects that the commands are to be executed on, and schedules execution of the rest of the pipeline. These processors are usually built from general-purpose chips like the 68000.

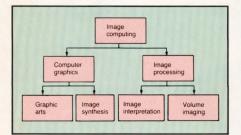

The graphics pipeline is sequential: The display list processor fetches models and commands, the geometry processor calculates model coordinates and attributes, the display controller constructs an image in the display buffer, and the video circuits display the frame buffer's contents on a screen. Image

processing, although often considered inherent in graphics, is largely more cyclical than sequential.

The raw data for image processing is usually in pixel form, a large collection of 3D coordinates and attributes, instead of mathematical models. Image-processing systems (see Figure 2b again) therefore fetch image data, perform operations on them such as filtering and convolution, and place them back in image memory. Although, like graphics systems, imageprocessing engines may move and scale object data, their more important function is the extraction of information from the image, rather than the extraction of an image from information (models).

Although the data flow and types of operations are different in image processing and graphics, the factors influencing the architecture of the systems are similar: The stability and portability of standard operations and data types influence the use of programmable or dedicated devices as processing engines. The abundance of resolution requirements, both within algorithms and in displaying data, create different datapath widths for different systems and for different parts of the same system. The need to tailor processing power and functionality affects the integration of circuits in either complete processors or building blocks. Finally, throughput and expandability requirements can force designers into creating parallel or highly pipelined architectures.

#### Programmable vs Hardwired

It has been difficult for manufacturers of standard VLSI components to create products for graphics and imaging systems because of the variety of formats and throughputs of these systems. For example, PC-based graphics systems may have to respond to commands in Extended Graphics Adapter (EGA), Hercules monochrome, Video Graphics Array (VGA), and Computer Graphics Interface (CGI) formats.

Higher-end workstations, if they support any standard software at all, can conform to Programmers' Hierarchical Interactive Graphics Standard (PHIGS) or Graphical Kernel Standard (GKS) commands for 2D graphics and PHIGS+ or GKS-3D for 3D applications. "If PHIGS or PHIGS + becomes widely accepted," postulates John Dalrymple, a principal scientist with Tektronix Inc.'s Graphic Workstation Division (Wilsonville, OR), "then there exists some opportunity for semiconductor manufacturers" to make standard VLSI devices for systems using those standards. Data and command formats for the most advanced graphics and imaging systems, however, can change with each successive model, as manufacturers try to expand the flexibility and throughput of their systems.

For these reasons, VLSI graphics processors implement a small set of primitive functions that are copied in many graphics systems. Texas Instruments' TMS 34010, perceived as the most programmable such chip, is a general-purpose microprocessor with graphics functions added—specifically block pixel moves and line drawing. Because it is a generalpurpose part, its performance is somewhat lower than that of other graphics processors, drawing 700,000 random vectors/s versus 2.5 million vectors/s for the more specialized Intel 82786.

More-specific graphics ICs, like Intel's, AMD's QPDM, and Hitachi's 63484, have instructions that implement more graphics functions, such as circle and arc drawing. If a graphics

FIGURE 1. Image computing encompasses computing graphics and imaging processing. as conceived by Pixar Corp.

operation maps directly onto these instruction sets, these chips are faster at those operations than the more generalpurpose, programmable parts.

The Intel 82786, for example, implements windowing functions in hardware. Pointer registers within the device enable it to keep track of the different areas of memory that contain the contents of windows displayed on the screen. If the application supports these pointers (as does Autocad, for example), then hardware windowing is more efficient than using block transfers of window data to build a screen image.

However, the more advanced a system is, the more likely that it contains specialized graphics functions such as shading. Such functions do not map directly into the instruction sets of the specialized ICs, therefore requiring the host CPU to build the image directly. Moreover, many such functions are the ones that make a product useful and unique. "Another problem with standard VLSI graphics chips," adds Gene Chao, president of Metheus Corp. (Hillsboro, OR), "is no product differentiation from your competitor.'

Even graphics system manufacturers have difficulty defining the exact instructions to implement in VLSI devices. For example, Metheus set out to implement its graphics pipeline, previously built with bit-slice components, in gate arrays for its UGA graphics card. Because of the need to remain compatible with earlier products while implementing new features, the company designed a general-purpose processor, in line with the philosophy of the TI part. The processor executes routines from microcode, performing calculations corresponding to the geometry processor in the graphics pipeline and handing off commands and vector coordinates to one or more custom datapath chips.

Similarly, in creating the new 4330 series of terminals, designers at Tektronix had to maintain compatibility with the older 4230 series. They used a general-purpose processor (the 59032 bit-slice processor from Waferscale Integration Inc., Fremont, CA) to processes the set of 4230-compatible graphics commands. They then used several gate arrays to implement specific functions that operate under control of the processor.

The algorithms used in imaging systems are as complex and mutable as those graphics. Most pioneering work in imaging therefore occurs on general-purpose mainframe and supercomputers. The wide range of imaging applications, including medical imaging, animation, and geographic survey, prevents the integration of much of the mathematics.

# Only Mentor Graphics maps symbols to silicon.

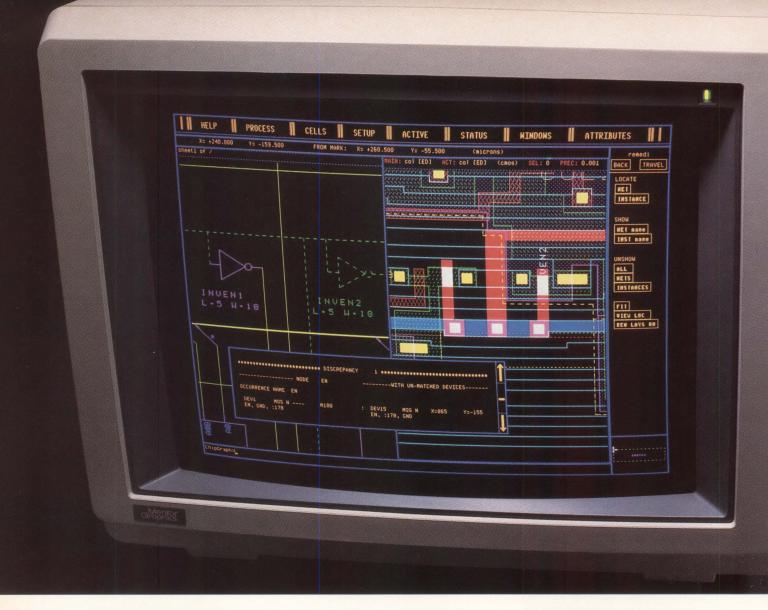

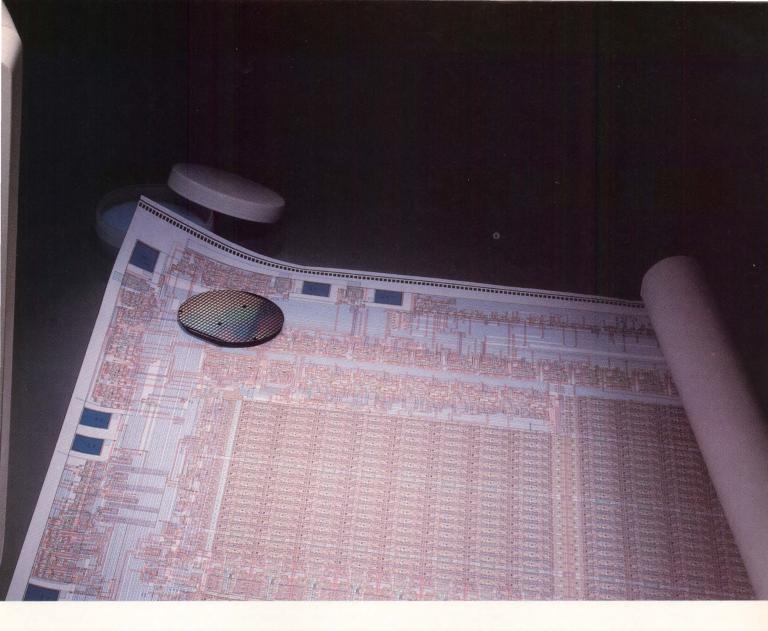

The bigger the IC design, the bigger the problem: you're trying to locate a discrepancy between the schematic and your IC layout, but all you have is an ASCII error report. It's like driving all over a strange city to find an address — without a map.

That's why Mentor Graphics created REMEDI,™ a graphical interface that helps debug complex layouts. REMEDI works with Dracula II,™ taking the leading layout verification package's layout-versus-schematic checks a step further. LVS errors detected with Dracula II can be quickly pinpointed on both

the layout and schematic using REMEDI's interactive graphical correlation capabilities.