ASIC FOUNDRIES: KEY PLAYERS IN CREATING YOUR SYSTEM

18

# DO YOU HAVE WHAT IT TAKES TO MAKE IT **BIG IN ASICS?**

Not long ago, designing ASICs wasn't even part of your job. ASIC Now it's the part everyone's counting on.

That's where Daisy comes in. Daisy CAE tools

are used by more ASIC designers than any other CAE workstations. Because from schematic creation through post-layout

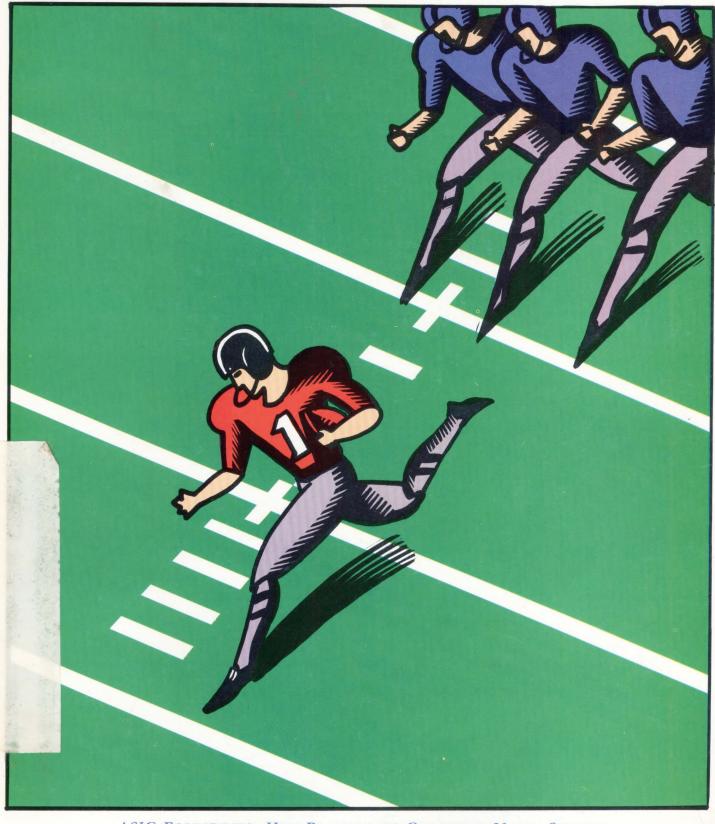

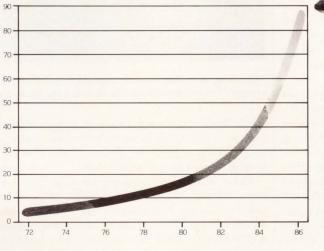

Simulation accelerator market share. Source: Prime Data, 1985 and 1986 unit shipments.

simulation, Daisy has what it takes to keep ASICs on time and on budget.

For example, our MegaLOGICIAN<sup>™</sup> simulation

is as well supported.

matic, so you can locate and correct design problems interactively. That means faster debugging and more time to improve the quality of your design. Plus no other accelerator

5.000

with more than 170 design kits supplied by 70 different vendors. So you can build productivity instead of libraries.

Which may explain why more MegaLOGICIANs are in use today than all other accelerators combined.

Speaking of combining, you

© 1988, Daisy Systems Corporation. MegaLOGICIAN is a trademark of Daisy Systems Corporation. \*Based on minimum 10x performance improvement compared to 32-bit workstations. Source for design kit estimates: VLSI Systems Design's Semicustom Design Guide, 1987.

can share a MegaLOGICIAN with a network of our 386based desktop workstations, for a high-powered low cost ASIC design environment.

And that's just the beginning. With our library of more

than 4,500 system-

level components, you can include your ASIC in complete "real world" system simulations to ensure that your designs will be ready for production, instead of revision.

All of which makes Daisy today's choice for no-sweat ASIC success.

But what about tomorrow? Gate counts are on the rise. If your tools run out of steam at 5,000 gates, so could your future.

No problem. Our ASIC design tools glide through 20,000-

without even breathing hard. In fact, new design kits already support arrays of over 100,000 gates.

gate designs

So you'll never have to worry about hitting a dead-end.

But don't take our word for it, listen to what Rockwell and other industry leaders have to say. For a free copy of "Making It Big In ASICs" call Daisy at 1 (800) 556-1234, Ext. 32. In California, 1 (800) 441-2345, Ext. 32.

European Headquarters: Paris, France (1) 45 37 00 12. Regional Offices: England (256) 464061; West Germany (89) 92-69060; Italy (39) 637251.

# Contents

# ARTICLES

# T OOLS

# 20 THE TUNING OF A LOGIC MINIMIZER

MICHAEL C. GALVIANO, Altera Corp.

When replacing a proprietary program with Espresso didn't work, an EPLD company undertook enhancements to increase the performance of its logic minimizer.

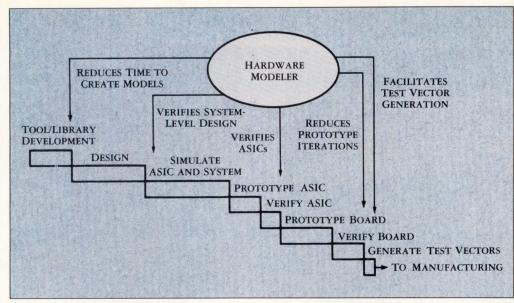

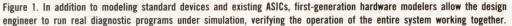

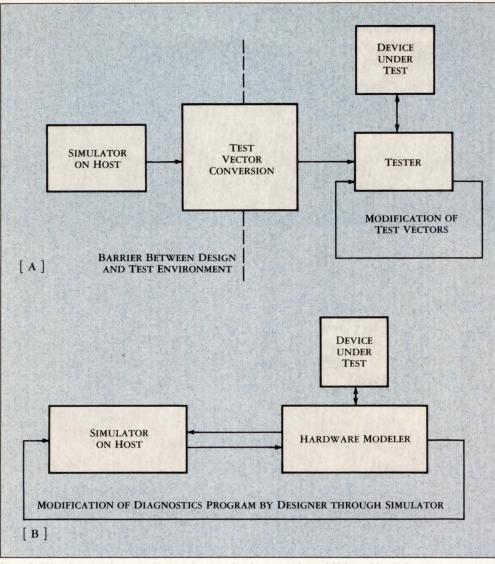

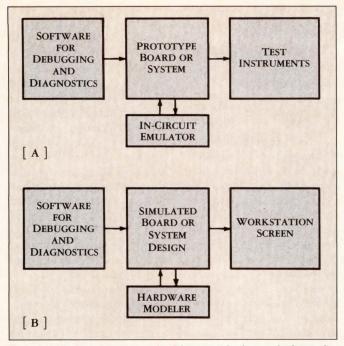

# **30** HARDWARE MODELING

# L. CURTIS WIDDOES JR. AND HOLLY STUMP, Logic Modeling Systems Inc. Hardware modeling can be a universal design tool for today's ASIC and system designers, but there are many misconceptions about the tool and its applications

# **C HIPS**

# **42** SURVEY OF SEMICONDUCTOR FOUNDRIES

# VLSI SYSTEMS DESIGN STAFF

In addition to providing an update of our usual information, this year's survey takes a look at military certification and qualification for ASICs.

# **S**TRUCTURES

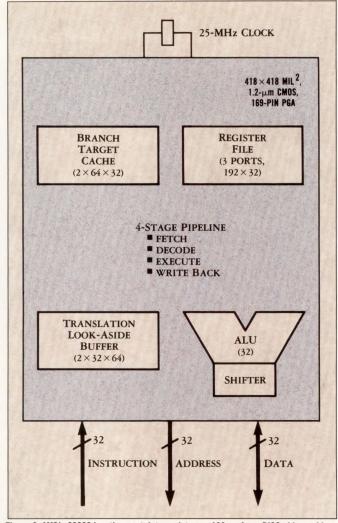

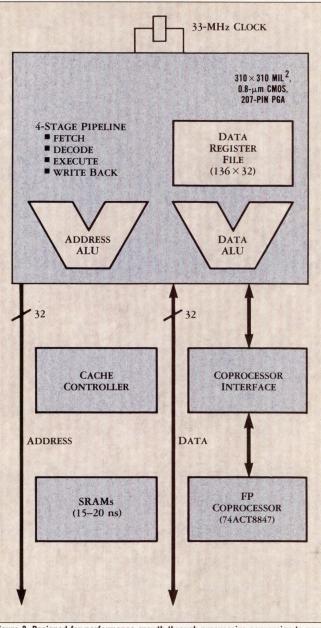

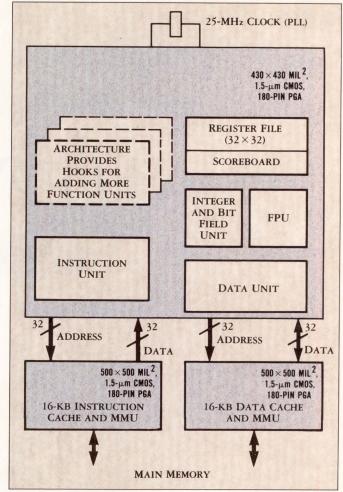

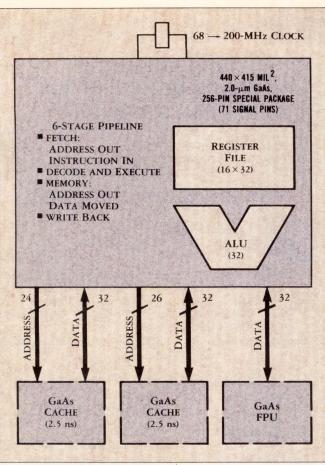

# **60** SURVEYING THE RISC REALM

BOB CUSHMAN, Senior Editor

The second article in our series on RISC microprocessors considers the general features of eight current implementations.

# C ODE

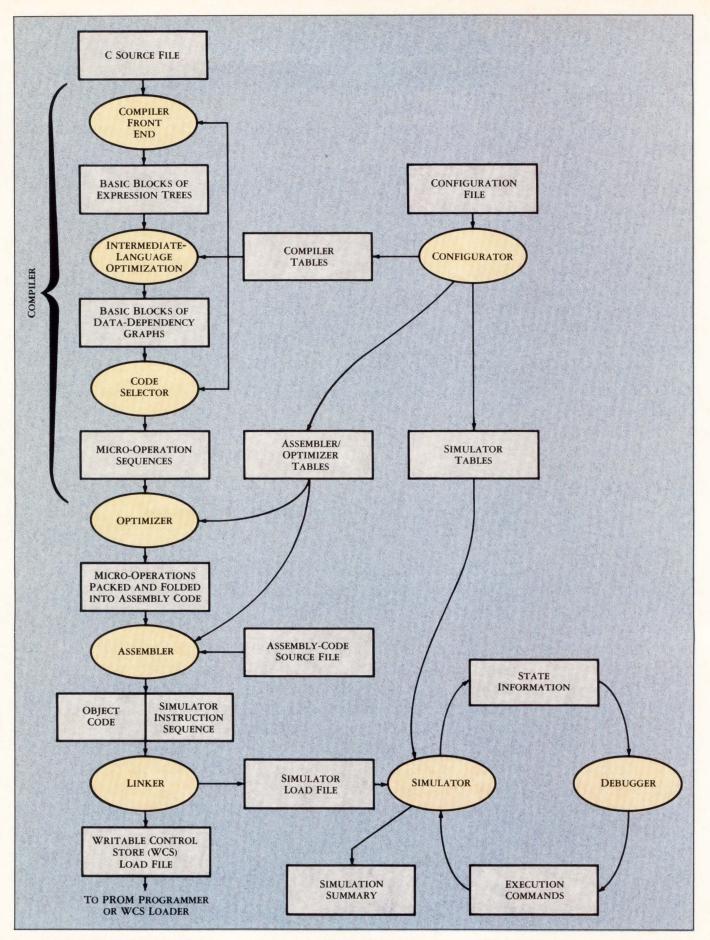

# 64 RETARGETABLE SOFTWARE DEVELOPMENT TOOLS

**BOB NORIN AND KEVIN NOLAN,** *Quantitative Technology Corp.* Retargetable software-development tools allow builders of custom architectures to program their applications in a high-level language.

# **SEMICUSTOM APPLICATIONS**

# **73** SPECIAL REPORT

This year's special comprises two contributed articles describing the design of two semicustom chips and a report on new applications for programmable devices. 64

Retargetable software tools come to the aid of microprogrammers

The capabilities of the ASIC foundry are critical to the success of highperformance systems

From PLDs to cell-based designs, semicustom ICs are handling more complex applications

# DEPARTMENTS

# **6** FROM THE EDITOR

DAC: The Signs of Maturity?

# 8 CALENDAR

# **10** BIT STREAM

Sony Launches Double-Barreled Threat . . .

. . . But Apollo Goes It 'One' Better Hewlett-Packard Emulates TI DSPs Allegro Is Accelerated

10 New microprocessor development tools serve TI's DSP chips

Zeiss Laser Focuses on Quality Control TTL-Compatible GaAs 22V10 Beats 10 ns

High-Voltage IC Drives Video Displays Cadnetix, HHB Systems: A \$77 Million Merger

# **12 NEWS ANALYSIS**

PLD Breakthroughs Threaten Standard Logic

# **16 PEOPLE**

John Birkner: Born to Innovate

# **18** LETTERS

Floorplanning Missing Cells

# **94** PRODUCT SHOWCASE

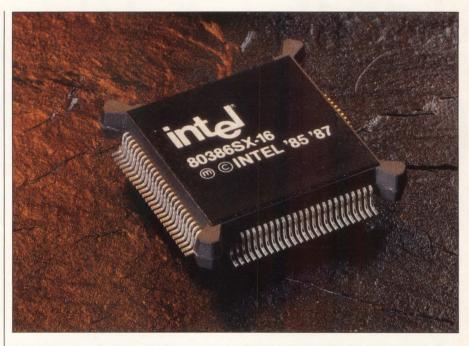

**VHDL**: Documentation or Development? 80386 Derivatives Aim at Low-Cost PCs and Embedded Systems

# **104** AD INDEX

A CMP Publication

EDITOR/EDITORIAL DIRECTOR Girish Mhatre EXECUTIVE EDITOR Roland C. Wittenberg MANAGING EDITOR Mike Robinson SENIOR EDITOR Bob Cushman EDITOR EMERITUS Roderic Beresford EDITOR-AT-LARGE Stan Baker WESTERN REGIONAL EDITOR David Smith DIRECTORIES EDITOR Michelle A. Losquadro **TECHNICAL ADVISERS** John A. Darringer Jeffrey T. Deutsch Edward J. McCluskey Alan F. Podell Daniel G. Schweikert Susan L. Taylor **EDITORIAL PRODUCTION** Patricia L. Gaynor, Sr. Production Editor Deborah Porretto, Ass't Production Editor EDITORIAL ART Sharon Anderson, Art Director Marie D'Ippolito, Design Director MANUFACTURING David Getlen, Dir. of Manufacturing Marie Myers, Production Manager James Pizzo, Production Supervisor Jane Mahoney, Asst. Production Supervisor Vance Hicks, Coordinator

### PUBLISHER Norm Rosen

VLSI SYSTEMS DESIGN (ISSN 0279-2834) is published monthly with an extra issue in May by CMP Publications, Inc., 600 Community Drive, Manhasset, NY 11030. (516) 562-5000. VLSI SYSTEMS DESIGN is free to qualified subscribers. Subscriptions to others in the US: one year \$60.00, two years \$95.00; Canada and Mexico: one year \$90.00, two years \$165.00; Europe, Central and South America: one year \$120.00, two years \$225.00. Australia, Israel and Africa: one year \$150.00, two years \$285.00. Second-class postage paid at Manhasset, NY and additional mailing offices. POSTMASTER: Send address changes to VLSI SYSTEMS DESIGN, Box No. 2060, Manhasset, NY 11030. Copyright 1988, CMP Publications, Inc. All rights reserved.

> **CMP ELECTRONICS GROUP** Kenneth D. Cron Vice President/Group Publisher Electronic Buyers' News **Electronic Engineering Times** VLSI Systems Design

**CMP PUBLICATIONS, INC.**

600 Community Drive Manhasset, New York 11030 (516) 562-5000 (J) 10/ JOZ-JOUD Publiaber of: Computer Systems News, Electronic Engineering Times, VLSI Systems Design, Computer Systems News, Computer Reseller News, VARBUSINESS, UNIX Today!, InformationWEEK, CommunicationsWeek, CommunicationsWeek International, Business Travel News, Tour & Travel News, Long Island Monthly, HealthWeek

Michael S. Leeds, President Pearl Turner, Vice President/Treasurer Daniel H. Leeds, Vice President

Lilo J. Leeds, Gerard G. Leeds Co-Chairpersons of the Board

20

Plackwell

An enhanced optimizer goes even further in reducing EPLD designs

# OurASIC line-u is on half the story.

When it comes to delivery of high-quality, reliable ASICs, S-MOS wrote the book.

We did it in collaboration with our manufacturing affiliate, Seiko Epson. With 18 years of CMOS experience, Seiko Epson is one of the world's most advanced CMOS IC manufacturers.

Through Seiko Epson's high-yield manufacturing technology, we ship millions of ASIC units a month, and with a reject rate of less than .0001%. That's our quality story.

Now we've added a new chapter on design. At our advanced R&D design facility, engineers from S-MOS and Seiko Epson are developing new software to simplify circuit design, simulation and the creation of new megacells for our extensive cell library.

Of course, you can still take advantage of our established design tools because S-MOS supports such workstations as Daisy, Mentor, Calma and PC-based systems using FutureNet, OrCAD and ViewLogic.

Our proprietary LADS simulator will speed up the design process. The S-MOS engineering team will support you from concept to production.

If you are looking for an ASIC program that can make your designs best sellers, call us. (408) 922-0200.

| A State of the second of the second sec |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| CMOS Gate Arrays                                                                                                                                                                                                                              | CMOS Standard Cells                                                                                                                                                | Compiled Cell Custom                                                                                                                                                                                                                                                                                                                          |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Up to 38,550 available gates<br>• SLA8000 (800 ps)*,<br>1.2μ drawn, 1.0μ Leff.<br>• SLA7000 (1.0 ns)*,<br>1.5μ drawn, 1.2μ Leff.<br>• SLA6000 (1.8 ns)*,<br>2.0μ drawn, 1.5μ Leff.<br>• SLA700B High Drive<br>Output<br>• SLA100L Low Voltage | Complexities to 16K gates**<br>• SSC1000 (1.4 ns)*,<br>1.8µ drawn, 1.4µ Leff.<br>• Fully migratable from<br>S-MOS gate arrays<br>• RAM and ROM<br>blocks available | <ul> <li>The Alternative to Full Custom</li> <li>1.8μ CMOS process</li> <li>Can utilize dissimilar cell geometries</li> <li>3-button approach to custom design</li> <li>Currently over 300 fully characterized cells</li> <li>Fast 14-week implementation time</li> <li>Timing-driven TANCELL<sup>®</sup> place-and-route software</li> </ul> | ~ |

SYSTEMS

S-MOS SYSTEMS, INC. 2460 North First Street San Jose, CA 95131-1002

TANCELL is a registered trademark of Tangent Systems. "Typical propagation delay of 2-input NAND gate driving 2 internal loads with 1mm of interconnect. "Maximum gate utilization depends on amount of interconnect used.

# **CIRCLE NUMBER 1**

The Design Automation Industry Is Beginning to Pay Attention to Important Details

# DAC: The Signs of Maturity?

By now the dust has settled on the 25th annual Design Automation Conference, held last month in Anaheim, Calif. It has become the premier event for the electronic design automation industry, and like the industry, it has changed its character over the two and a half decades that it's been around. Each succeeding conference seemed to be bigger and better than its predecessor. However, although this year's event ran smoother than ever, some of the excitement of past conferences seemed to be missing.

Logic synthesis and hardware description languages like VHDL were the subject of many papers, and related products were prominent on the exhibition floor. But most product unveilings were enhanced versions of existing tools. Joint agreements to port, link, or market were probably the most popular announcements. Perhaps it's a sign of maturity.

There was another sign of maturity in the industry: the increasing consolidation activity—in the form of mergers, acquisitions, or dropouts. Some of these consolidations were marriages holding great promise, but many were for the sake of survival. Some think these moves as a harbinger of bad times for the electronic design automation industry, but I don't. I see it as a growth plateau in which the industry regroups, reviews its strategy, and gets ready to move on to even greater heights.

Is this whistling in the dark? Not really; many of the mergers will benefit the system and chip designers. Vendors of heterogeneous tools that merge will be pressured by market forces to provide good working interfaces between these tools, rather than the token links or good intentions that have resulted from a number of the many highly touted "joint agreements."

In addition, those who closely follow the industry can testify that many vendors are now beginning to pay attention to the "not so little" things that are often neglected in a young and exploding market. These include such entities as databases, documentation, networking, testability, standards, and user-friendly universal interfaces. Attention to these "details" and the increasing system view taken by many of the players is good news, and it could provide the launching platform for reaching the next plateau in the design automation industry.

Colon Il the

ROLAND WITTENBERG EXECUTIVE EDITOR

# **Stop Wasting Power**

# New CMOS array features the lowest power dissipation: 8µW/Gate/MHz

Raytheon's newest CMOS array family, the RL1000, helps you achieve optimum power performance. It offers the lowest power dissipation available at high densities—without sacrificing speed.

□ Lowest Power: Ratheon's 8µW/gate/MHz CMOS arrays, with 1.0 micron effective channel lengths, have available densities ranging from 5670 to 20,440 gates. With 20 tracks per channel instead of the standard 16, gate utilization is typically 90 percent or better. □ **High Speed:** At 0.3 ns unloaded inverter delay, this low-power, high-speed array family is perfect for portable equipment or where power sources are limited.

□ Other features: The RL1000 series, with symmetrical switching delays, operates at 250 MHz flipflop frequency and is TTL/CMOS compatible.

□ **Packaging:** All packaging options are available. And Raytheon's design support includes an extensive macrocell library on major workstations. □ Also available in CMOS:

Approved VHSIC PHASE I gate array: RVG 1.25 family

Second source for LSI Logic Inc.'s LL7000 Series: RL7000

Call Raytheon for access to the right CMOS technology. Your success is our first priority.

Raytheon Company Semiconductor Division 350 Ellis Street Mountain View, CA 94039-7016 (415) 966-7716

**CIRCLE NUMBER 2**

Where quality starts with fundamentals.

# alendar

# INTERNATIONAL WORKSHOP on VLSI for Artificial Intelligence

July 20–22 University of Oxford Oxford, England

This workshop will provide a forum where AI experts and VLSI system designers can come to discuss trends in AI applications and their computational requirements, VLSI implementations, and computer architectures. Topics to be discussed will include alternative technologies, semantic and neural networks, functional-language architectures, knowledge-oriented machines, rule-based engines, Prolog and Lisp machines, and fifth-generation computers. Further information may be obtained by contacting Dr. Jose G. Delgado-Frias or Dr. Will R. Moore, Department of Engineering Science, University of Oxford, Parks Road, Oxford OX1 3PJ, England, U.K. Phone: (0865) 273188.

# SIGGRAPH '88

August 1–5 Atlanta, Ga.

The 15th annual conference on computer graphics and interactive techniques is sponsored by the Association for Computing Machinery's Special Interest Group on Computer Graphics in cooperation with the IEEE Technical Committee on Computer Graphics. It will feature panel sessions, courses, and exhibitions, as

well as a film and video show and an art show. Technical presentation topics will include fast polygon algorithms, applications of computer graphics, volume rendering, lighting models, user interfaces, physically based modeling, curves and surfaces, filtering and texturing, hardware systems, and animation. Courses on user interface management systems, computer graphics in science, and solids modeling will be featured. For further information about the conference, contact SIGGRAPH '88 Conference Management, Smith, Bucklin, and Associates Inc., 111 E. Wacker Drive, Suite 600, Chicago, Ill. 60601. (312) 644-6610.

# **OIS '88**

September 7–9 Washington Sheraton Washington, D.C.

S ponsored by Meckler Corp., the eighth annual Optical Information Systems Conference and Exhibition will focus on write-once and erasable optical storage systems and digital documentimage automation. Sessions are planned in such areas as electronic image and document storage systems, erasable optical disk media developments, erasable optical disk drives and systems, evaluating and selecting a WORM subsystem, write-once and erasable optical media manufacturing approaches, operating-system software for write-once optical disk, future trends and new developments, converging optical information technologies, and integrated system development. Additional information may be obtained by contacting Marilyn Reed, OIS '88 Conference Manager, Meckler Corp., 11 Ferry Lane West, Westport, Conn. 06880. (800) 635-5537.

# 7th VLSI and GaAs Packaging Workshop

September 12–14 San Jose, Calif.

This workshop is being sponsored by the IEEE's Components, Hybrids, and Manufacturing Technology Society and the National Bureau of Standards. Topics that will be addressed include package thermal design and interconnection options, GaAs IC packaging, die attachment solutions for large chips, VLSI and wafer-scale package design, new failure mechanisms in VLSI packaging, and VLSI package materials advances. Additional information may be obtained by contacting Paul Wesling, IEEE Council Office, 701 Welch Road, Suite 2205, Palo Alto, Calif. 94304. (415) 327-6622.

# INTERNATIONAL TEST Conference 1988

September 12–14 Sheraton Washington Hotel Washington, D.C.

The International Test L Conference provides a major forum for an exchange of information about the testing of electronic devices, assemblies, and systems. This year the conference focuses on the test techniques and equipment needed to meet the challenges of new technologies. Technical papers will be presented on such topics as analog devices, yield modeling and process diagnosis, testability analysis, education and training, application-specific devices, microcontrollers and microprocessors, printed circuit boards, wafer-scale assemblies, hardware and software, process and test data management, surface-mount assemblies, computer-aided engineering, quality and reliability, fault modeling and simulation, design for testability, contactless probing, fixturing, and computer-aided test generation. For additional information, contact Doris Thomas, Executive Secretary, International Test Conference, Millbrook Plaza, Suite 104D, P.O. Box 264, Mount Freedom, N.J. 07970. (201) 895-5260. .

# **PERFORMANCE**

# Wafer Foundry Capacity Available.

# Become our Performance Partner for COT, CFT, CST and receive On-Time, Reliable service.

Performance Partnership is a simple concept. You design the circuit (your performance); we implement your design on silicon, using advanced process technologies (our performance).

As our partner, you're welcome to monitor each step. Programs are flexible—wafers, tested die, packaged devices, you call the shots. We're cost-effective. Nonthreatening. And, we can be an interim or long-term solution.

Here's what you can expect from our performance.

| Capacity:    | >5,000 wafers per week |

|--------------|------------------------|

| Reliability: | <20ppm AOQL            |

| Delivery:    | 99% on time            |

| Pricing:     | Very Competitive       |

To demonstrate the flexibility of our services we offer these processes:

- P-Well and Twin-Tub, ISO-Planar CMOS

- · Linear and High-Speed Bipolar

- Silicon Gate NMOS

- Double-Poly Process for Mixed Signal Technology

- Double Metal Process for High Density Applications

- 2 Micron Stepper-based Processing

Whether your need is for commercial or military grade wafers, write today for more information. For faster service, call our President, **Paul Bhasin** at (602) 921-6011.

> California Micro Devices Corp. Microcircuits Division 2000 West 14th Street •Tempe, AZ 85281 (602) 921-6000 • FAX (602) 921-6598 • TLX 187202

Copyright © California Micro Devices Corp. 1988 1900-8014

**CIRCLE NUMBER 4**

# tream

# Sony Launches Double-Barreled Threat . . .

n a joint announcement with Motorola Inc., Sony Microsystems (Palo Alto, Calif.) unveiled a new workstation based on two 25-MHz 68030s and a 25-MHz 68882 floating-point coprocessor. Expected to be priced between \$35,000 and \$45,000, the NEWS 1800 series of platforms will run Sony's version of Unix 4.3 BSD and the X-11 Window System. Sony rates the platform at 5.3 Dhrystone MIPS (normalized to a VAX-11/780). With one 68030 dedicated to I/O processing, the machine is touted at excelling in applications with extensive I/O, networking, and graphics requirements.

# . . But Apollo Goes It 'One' Better

pollo Computer Inc. (Chelmsford, Mass.)-like Sony, Hewlett-Packard, and Masscomp-is eager to cash in on the wealth of applications running on 680x0based machines. The company's answer is two price/ performance-targeted systems, the Series 3500 and 4500, that are binary-compatible with the 3000 and 4000 series. Based for the end of the year.

on a single 68030, the 3500 uses the 25-MHz version and the 4500 a 33-MHz device.

The 3500 series, which claims a performance of 4 MIPS, starts at a low \$7,990, and the 4500 series, which promises 7 MIPS, sports price tags as low as \$18,990. The 3500 will be available this month; the 4500 is scheduled

# Hewlett-Packard Emulates TI DSPs

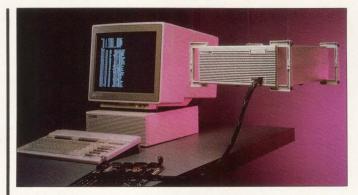

he HP 64700 series of emulator/analyzers from Hewlett-Packard Co. combines the company's "logic analyzer on a chip" with its new emulation technology to provide a set of high-performance microprocessor development tools for Texas Instruments' TMS-32020 and TMS320C25 digital signal processors.

The emulators deliver real-

time, no-wait-state execution up to 20 MHz for the 32020 and up to 32 MHz for the 320C25. They also support 64K words of dual-ported emulation memory, eight-level sequencing, and code coverage analysis. The optional integrated 16-channel logic analyzer functions as a 100-MHz state analyzer and 25-MHz timing analyzer.

## **Allegro Is Accelerated**

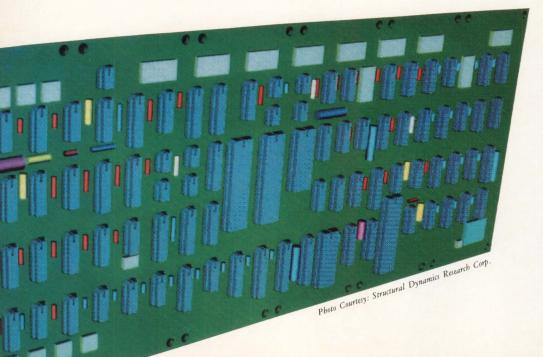

new release of the Allegro PC board design system from Valid Logic Systems Inc. (San Jose, Calif.) provides more than 30 new features that increase the support for highspeed design and analysis; 2D drafting; and manufacturing, testing, and other third-party interface applications.

Release 2.0's new and enhanced interfaces to mechanical design and analysis packages, such those offered by Structural Dynamics Research Corp., permit the designer to check PCB placement for mechanical interference and also to perform stress, vibration, and shock analysis.

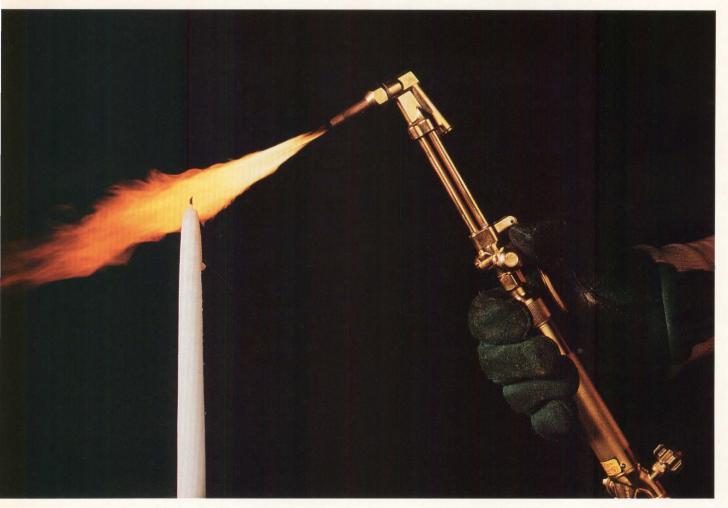

# **Zeiss Laser Focuses on Quality Control**

arl Zeiss Inc. (Thornwood, N.Y.) has built a new laser autofocus system into its Axiotron AF and Axiomos wafer inspection microscopes to allow real-time automatic focusing for precision inspection of semiconductors. The system

also provides for remote operation with a TV camera, as well as proportional manual speed control. The dual infrared pulsed-laser system can be operated at all magnifi-

cations without the necessity of realignment when changing objective lenses.

Continuous spot focusing is stage can run at a provided by the system as it 100 mm/s w tracks the surface of the speci- reproducibility.

### TTL-Compatible GaAs 22V10 Beats 10 ns

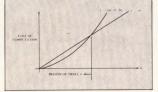

G (Santa Clara, Calif.) promised to put LSI-level functionality on GaAs standard products. The first product off the drawing board is a GaAs version of the 22V10 PLD with a 10-ns propagation delay (input to output), a 3.5-ns setup time, and a clock-to-output time of 7.5 ns.

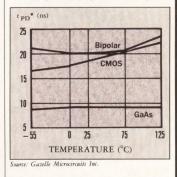

Not only is this GaAs part fast, its characteristics are roughly flat over the military temperature range. The figure shows a comparison of combinational input-to-outputdelay time vs. temperature for bipolar, CMOS, and the new GaAs device. The new part not only exhibits a temperature stable delay characteristic, but also provides less than half the men undergoing inspection. This feature provides a speed advantage over more conventional TV-based systems, in which the microscope's objective lens must arrive at the desired coordinates before the system attempts to focus.

The Axiotron microscope is designed for in-process inspection, quality control, and failure analysis on wafers and masks. The Axiomos system includes a software

package for controlling illumination, magnification, and stage position. Its motorized stage can run at speeds of up to 100 mm/s with 0.1-µm reproducibility.

delay of the other implementa-

tion technologies. By providing TTL-compati-

ble input and output circuits, the part can be easily dropped into any standard 22V10 circuit. The catch? For the near future, only Gazelle can program the \$55 parts, which can have a turnaround time as long as one week.

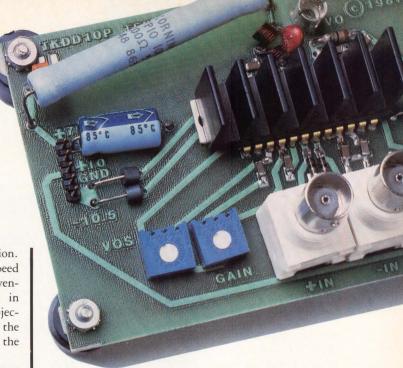

# **High-Voltage IC Drives Video Displays**

ektronix Inc. (Beaverton, Ore.) has rolled out a monolithic IC, the TKDD10P, that can drive a CRT with 50 V peak to peak at 175 MHz with up to a 6-pF load. Its gain can be varied linearly from 0 to 80 with an external potentiometer.

The display driver chip is based on Tektronix's proprietary Quickchip ASIC technology. Available in a 24-pin power tab package, it runs \$35 in 1,000-unit quantities. The chip is also available on an evaluation board, the TKDD10EB.

# Cadnetix, HHB Systems: A \$77 Million Merger

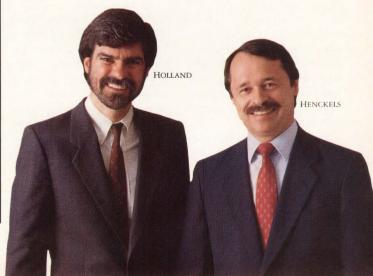

Bruce M. Holland, president and CEO of Cadnetix Corp. (Boulder, Colo.), and Lutz P. Henckels, president of HHB Systems (Mahwah, N.J.), shook hands on an agreement to merge the two design automation companies in a stock deal valued at \$77 million. Cadnetix is widely known for its strength in printed circuit board CAD tools, and HHB is strong in logic and fault simulation and automatic test generation. Under terms of the pact, Cadnetix will issue 1.4 shares of new common stock for each share of HHB, which will become a wholly owned subsidiary. Holland will retain his positions at Cadnetix and Henckels will be president of the new HHB subsidiary.

# News Analysis

# PLD Breakthroughs Threaten Standard Logic

hat has been keeping standard logic parts alive? Invented over 20 years ago, they established one of the most important standards in the industry. But their demise has been contemplated continuously for the past 10 vears. However, the 7400 functions, in their many implementations, from LS to AS, FAST, FACT, and ACT, hang in there in the face of competition from ASICs, both LSI and VLSI. Annual worldwide sales for standard logic parts is now about \$3.5 billion.

But advances in the speed of PALs that went to market for the first time last month may finally break the 7400 hold. Till now, PLDs could shrink the number of 7400 parts and bring cost savings at chip and board levels, but only at the cost of lower performance.

The result has been that the CMOS segment of the standard logic market is growing very slowly, and lower-speed bipolar versions—L and LS—are flat or shrinking. Only the faster, newer families, like FAST and AS are growing at reasonable rates. These growth rates indicate that the users of standard logic are going to the devices mainly for speed.

Indeed, speed has kept standard logic alive. That's why CMOS has grown slowly, even while LSI and VLSI counterparts in the technology are surging in sales.

Surely, though, there are

other attractions for the continued use of 7400 parts besides speed. For one, everyone is familiar with them, they're cheap, they have multiple sources, and they are commodities. (However, the speedy versions are not commodities.)

Now that breakthroughs in bipolar PALs are offering devices that are faster than the 7400 parts they can replace, the impact on standard logic will grow rapidly. That's because PALs or other PLDs, being field-programmable, easily replace scores of 7400 functions. If the standard-logic makers wanted to offer a new and complete line of standard logic with better speed, it would take many months and huge investments.

All the room for maneuvering is now held by PLDs. So far we have seen the fastest PLDs at 15 ns, 10 ns, and now Advanced Micro Devices Inc.'s new 7.5-ns series, offered in standard architectures. But soon, and probably first from AMD (Sunnyvale, Calif.), we will see the fastest-propagation-delay processes used to make more application-specific parts that can even compete with the higher-level LSI logic parts. This month, AMD will announce a new PAL with a 10ns propagation delay that will offer solutions for "common system timing problems." Filling out the line with an array of application-specific models appears to be an added direction for AMD.

Other companies, using the PAL structures, are already charging down the application-specific route, most notably Altera and Intel.

Another reason for PALs to become more important is that the inventiveness and aggressiveness that was exhibited by MMI for the last 10 years is now backed by the considerably larger manufacturing capability of AMD. MMI was always slow in ramping its latest PAL technology and was often production-limited. Staring at several hundred millions of dollars in hard investments to cure that problem is one big reason why MMI chose to merge with AMD.

# ■ WHY NOT GATE ARRAYS?

But what about gate arrays? Aren't they replacing those 7400 functions? Gate arrays have been around a long time, and standard-logic sales have still continued to climb. Andy Robin, marketing manager for PLDs at AMD, believes FAST and AS are still growing rapidly because gate arrays are having difficulty replacing them, typically becoming economically wise only gate ranges of 10,000 to 20,000 gates and higher, and that's a large commitment for most logic designers. Normally, they have been keeping tight control of their designs, particularly those sections that contain the most critical speed paths for a subsystem, using FAST or AS parts. Also, such designs are often not solidified until late in the system development cycle.

But while gate arrays have been having some trouble penetrating these critical applications, PALs have become popular choices because they can be programmed by the designer, often late in the design cycle, without the turnaround time and NRE costs of gate arrays. In addition, approvals to make this type of design change can usually be avoided. An engineer doesn't have to announce that he had problems with his design; the old PAL simply goes in the garbage can.

# ■ A BOUNTY OF SPEEDY PLDs

Over the last few weeks there has been a bounty of new, fast PLDs offered to the world, from AMD, Lattice Semiconductor, Gazelle Microcircuits, and Signetics.

The new AMD 7.5-ns PAL series consists of four standard 20-pin devices: the PAL16R8, PAL16R6, PAL16L8, and PAL16R4. They are rated at a maximum propagation delay of 7.5 ns from 0° to 75°C and an operating frequency of up to

# Feel trapped by one ASIC supplier? Reach for the Super Foundry.

Now you can design complex ASICs to meet your needs, not to fit one supplier's limited capabilities. The Super Foundry<sup>™</sup> offers the combined resources of the world's premier CMOS manufacturers. Our process independent design tools and production services give you maximum freedom and control—from concept through delivery. FREE. ASIC Estimating Kit.

What will it take to do your ASIC? With our free ASIC Estimating Kit, you can analyze design-process trade-offs and explore the performance, cost and scheduling implications of your design in a variety of processes. Take control of your ASIC design and avoid the single-supplier prison. Call the Super Foundry for your free ASIC Estimating Kit: 1-800-FOR-VLSI ext. 200.

THE SUPER FOUNDRY SEATTLE SILICON

3075-112th Ave NE., Bellevue, WA 98004, (206) 828-4422. Copyright 1988, Seattle Silicon Corp. Super Foundry is a trademark of Seattle Silicon Corp.

# DESKTOP GATE ARRAY DESIGN

Like desktop publishing is revolutionizing publishing, we are revolutionizing gate array design. Our *GATEAID PLUS/PC* gate array design software:

- runs on your PC/XT/AT/386

matches the power of workstation tools, and

- o costs \$945.

And unlike the logic supertankers of other suppliers, our gate arrays are *efficient building blocks* tailored for various functions such as:

- PLD replacement

- RAM and logic integration

- Bus logic integration, etc.

To order GATEAID PLUS/PC, or for more information on it or on our building block gate arrays, mail coupon below. Or call *1-800-338-GATE.*

| Mail to: | Matra Design Semiconductor<br>2840-100 San Tomas Expressway<br>Santa Clara, CA 95051                          |

|----------|---------------------------------------------------------------------------------------------------------------|

| PLL      | ke to order a copy of GATEAID<br>IS/PC on a 30-day trial basis. Bill me.<br>ude business card or letterhead). |

| Sen      | d me information.                                                                                             |

| Name     |                                                                                                               |

| Signatu  | re (Required)                                                                                                 |

| Phone    |                                                                                                               |

| Compa    | ny                                                                                                            |

| Addres   | S                                                                                                             |

|          |                                                                                                               |

| 1-8      | 00-338-GATE                                                                                                   |

| 1-8      | 00-338-GATE                                                                                                   |

**CIRCLE NUMBER 6**

# NEWS ANALYSIS

74 MHz. The frequency rating is important. It should be approximately double that of the latest microprocessors. This allows the devices to interface directly with the microprocessors without absorbing too much of their cycle time.

AMD has also upgraded the speed of the 22V10, the most popular of all PAL devices. The propagation delay has been reduced from 25 to 15 ns. Also, the company is now shipping 10-ns 20-pin PALs in volume.

Many users of the 22V10 have felt the pinch of speed, especially with microprocessors rapidly upgrading their performances. Moving from 25 ns to 15 ns is a It is a direct drop-in for the bipolar 22V10. But AMD's announcement of its 15-ns version took some of the spring out of Gazelle's leap into the market. One other drawback of the Gazelle chip is that it must be programmed at the factory using laser programming.

Gazelle cannot showcase its potential capabilities very well with the 22V10 equivalent because it is not dense enough. GaAs gives very fast gate transitions internally, but that can be lost with the I/O circuits, which have been purposely slowed down to emulate standard TTL I/Os. In denser circuits, it would take about 50 gates in series to increase the overall delay time appreciably, since the GaAs gates have transition times hovering around 100

|                           | PARAMETER         | FAST | AS   | PAL16R8-7 |

|---------------------------|-------------------|------|------|-----------|

| COMBINATORIAL FUNCTIONS   |                   |      |      |           |

| 74138 DECODER             | t <sub>PD</sub>   | 8.0  | 10.0 | 7.5       |

| ■ 74151 MULTIPLEXER       | t <sub>PD</sub>   | 11.0 | 15.0 | 7.5       |

| REGISTER, LATCH           |                   |      |      |           |

| ■ 74374 OCTAL REGISTER    | t <sub>co</sub>   | 10.0 | 9.0  | 6.5       |

| ■ 74373 OCTAL LATCH       | t <sub>PD</sub>   | 8.0  | 6.0  | 7.5       |

|                           | t <sub>LEO</sub>  | 13.0 | 11.5 | 7.5       |

| COUNTERS                  | The second second |      |      |           |

| ■ 74161 4-BIT COUNTER     | ts                | 5.5  | 8.0  | 7.0       |

|                           | t <sub>co</sub>   | 11.0 | 13.5 | 6.5       |

| ■ 74269/869 8-BIT COUNTER | ts                | 2.5  | 5.0  | 7.0       |

|                           | t <sub>co</sub>   | 10.0 | 11.0 | 6.5       |

major step, making the 22V10 more of a candidate to replace groups of SSI and MSI logic parts. AMD expects soon to boost the operating frequency from 28.5 to 50 MHz. That puts the rate at twice that of the new 20- and 25-MHz microprocessors, making the device very attractive for interfacing at these higher processor speeds.

A week after AMD made its 7.5-ns announcements in June, Signetics Corp. (Sunnyvale, Calif.) announced a line of 20pin and 24-pin PALs with 10-ns propagation delays. It also unveiled two of its own PLAs, devices that have much more logical flexibility but a 12-ns delay.

Lattice Semiconductor Corp. (Hillsboro, Ore.) also pushed the speed in its CMOS EEPLD end of the market. It now has GAL devices with 12-ns propagation delays that replace common 20- and 24-pin PAL devices. The new parts, the GAL16V8A-12 and GAL20B8A-12, both have a maximum power drain of 115 mA.

In addition, Gazelle Microcircuits Inc. (Santa Clara, Calif.) made its introduction of the 22V10 in gallium arsenide. The device has a typical 6-ns delay (10-ns maximum) but sports TTL I/O parameters. ps. However, Gazelle can use this part to demonstrate that GaAs is an good alternative for silicon logic at the MMI and LSI levels. That needs to be proven for GaAs to take off as a logic alternative mixed into the critical timing circuits of systems based on silicon.

Gazelle must also demonstrate its claim that GaAs will become as economical as silicon because it will use the same manufacturing equipment and the same design tools. Currently it delivers twice the speed of standard logic but for approximately twice the price. Thus Gazelle has a lot to prove. It will take a few years to convert the skeptical, of whom there are many. Along the way, watch for Gazelle to bring out a string of programmable parts of much higher density, in addition to moving toward application-specific solutions.

All in all, this has been a banner month for PLDs and especially PALs. When future dismantlers of today's systems examine them with an archaeologist's eye, they may also reckon 1988 as the time when the 7400 families first started their relentless downturn.

-Stan Baker

# ARRAY FOR BicNos!

# 180 MHz with low power.

It's cause for celebration. AMCC extends its lead as the high performance/low power semicustom leader with three exciting, new BiCMOS logic

arrays that optimize performance where today's designs need it most. In throughput (up to three times faster than 1.5µ CMOS).

Today, system designers look at speed, power and density. For

|                                | Q2100B      | Q9100B      | Q14000B       |

|--------------------------------|-------------|-------------|---------------|

| Equivalent Gates               | 2160        | 9072        | 13440         |

| Gate Delay* (ns)               | .7          | .7          | .7            |

| Maximum I/O<br>Frequency (MHz) | 180         | 180         | 180           |

| Utilization                    | 95%         | 95%         | 95%           |

| Power<br>Dissipation (W)       | 1.8         | 4.0         | 4.4           |

| I/O                            | 80          | 160         | 226           |

| Temperature<br>Range           | COM,<br>MIL | COM,<br>MIL | COM,<br>MIL   |

| *(2 loads, 2 mm of             | metal)      | †A          | vailable soon |

good reasons. As CMOS gate arrays become larger and faster, designers can't meet their critical paths due to fanout and interconnect delay. As Bipolar arrays become larger and faster, power consumption becomes unmanageable. So AMCC designed a BiCMOS logic array family that merges the advantages of CMOS's low power and higher densities with the high speed and drive capability of advanced Bipolar technology. Without the disadvantages of either.

Our new Q14000 BiCMOS arrays fill the speed/power/ density gap between Bipolar and CMOS arrays. With high speed. Low power dissipation. And, mixed ECL/TTL I/O compatibility, (something CMOS arrays can't offer).

For more information on our new BiCMOS logic arrays, in the U.S., call toll free (800) 262-8830. In Europe, call AMCC (U.K.) 44-256-468186. Or, contact us about obtaining one of our useful evaluation kits. Applied MicroCircuits Corporation, 6195 Lusk Blvd., San Diego, CA 92121. (619) 450-9333.

**CIRCLE NUMBER 7**

# EOPLE

Innovate

The Driving Force Behind the PAL Moves On

OHN Birkner has a fascination for electronics that could inspire zealots and fanatics. Continually drawn to innovations in digital computers, he became the driving force in the invention of programmmable array logic (PAL) devices at Monolithic Memories Inc. in the mid-1970s, and PALs propelled MMI to the front ranks of semiconductor makers.

Before MMI, Birkner was at Computer Automation Inc., where he designed an entire 16-bit processor on a half-card-sized board with only 80 ICs. Though the board was hailed as a great achievement at the time, Birkner knew there had to be a better way. "TTL was a helter-skelter collection of devices from different companies. PLAs were in fat 28-pin DIPs, cost \$20, had 60-ns delay times, needed \$10,000 programmers, and lacked design software-and there was a big education problem," he recalls. However, the sudden appearance of microprocessors convinced him to move from Newport Beach, Calif., in 1975 to where systems were being put onto silicon.

Birkner's contribution was that he brought a special vision to MMI in connecting applications to IC design. At MMI, he 'says, "it was like standing on a fence and seeing both sides." IC companies misunderstood the shortcomings of PLAs, but he saw an opportunity.Engineers at computer companies had told him, "If you give us PLAs in 20-pin packages with speeds close to that of TTL, we'll never use TTL again."

John Birkner: Born to

Birkner had his cause, and MMI had the wherewithal in PROM technology; a silicon design genius named H.T. Chua; and an applications manager, Clive Ghest, who supported Birkner. Out of this chemistry was born the PAL business.

The first priority was to make PLAs that were as fast as standard TTL logic. The PLA architecture was simplified to use only programmable OR gates, reducing the chip size and delay and making the new PAL parts easier to use. Then Chua innovated simpler, smaller device structures that enabled PALs to cover the functions of 8-bit octal devices—a key to success. The delay dropped quickly to 35 ns, putting the new PLDs in the TTL league.

To many, Birkner was a blond, bushy-haired hippie from Southern California. His first proposal for development of the PAL line got a ho-hum reception from MMI'smanagement. He gives Ghest, originally from Britain, credit for backing his ideas. "The English have a way of putting up with eccentrics," he says.

His hair has come under somewhat more control, but not his thirst for innovation. He ran his own company, Structured Design

# PEOPLE WILL GROW, BUT AS ORGANIZATIONS

GROW THEY WANT TO CONTROL THE ZEALOTS' Inc., part-time since 1979, while employed at MMI. It made design tools for PLDs but was eventually scaled back to serve only a few customers. It's now run by Birkner's wife, Noel Hendricks.

As a 12-year-old, Birkner was inspired by the *Boy's Book of Electronics.* He first used a digital computer at the University of California at Berkeley in 1964. In two weeks, he used all of the class's computer time, he relates with a tinge of embarrassment but no regret.

Birkner's leisure time is saved for his only child, 30-month-old Samantha. They hike mountains and fly kites on windy hills near the Pacific Ocean. At 45, he has geared down from the long-distance runs of a few years ago.

He is, however, gearing up more innovations. He left MMI in 1986 and recently formed Peer Research Inc. with Chua and some of the old PAL development team. "It will provide the spreadsheet, the Lotus 1-2-3, of ASICs and bring silicon compilation to desktop computers," he says. (He often refers to PALASM, the programming language developed at MMI for PAL design, as "the first silicon compiler.")

Why did Birkner leave MMI, a company that rewarded him and Chua with Porches and Mercedes Benzes? "PALs were doing OK. I had completed a cycle. People will grow, but as organizations grow they want to control the zealots. You can't outgrow the perceptions other's have about you. I'm an innovator, not an organization person; I have to have the hours alone to think. To many, I was always the bushy-haired hippie."

-STAN BAKER

When (Count < 9) & Clr | then Count := Count + 1 else Count := 0;

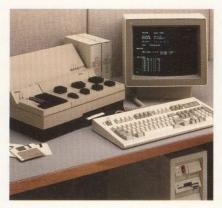

# **17 MILLION PLDS A MONTH BEGIN WITH DATA I/O.**

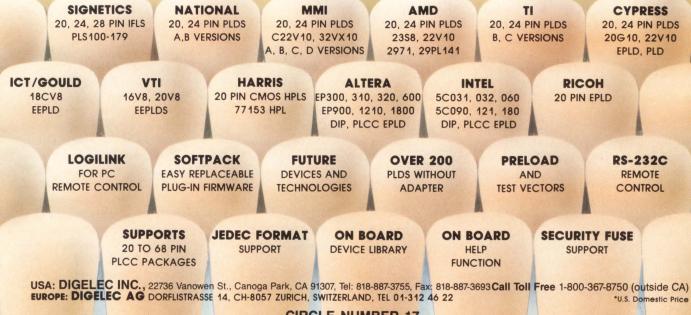

No company supports as many programmable logic devices as Data I/O<sup>®</sup>—virtually every PLD on the market. From design, to programming and test, Data I/O is the industry choice for PLD development tools.

UNIVERSAL SUPPORT FOR EVERY PLD MANUFACTURER. Data I/O gives you the freedom to choose the right PLD for your design—from any manufacturer. You can use our tools to design and program all PLD architectures, including PALs, FPLAs, PLEs and EPLDs, and all technologies from vertical-cell AIM, ECL, and CMOS to bipolar. And you can pick any package—DIP, PLCC, LCC or SOIC.

**UNIVERSAL DESIGN TOOLS.** ABEL™ 3.0, Data I/O's high-level design language, lets you describe your design with any combination of equations, state diagrams, or truth tables. For complete device testability, PLDtest<sup>®</sup> is our universal tool for automatic fault grading and test vector generation.

**UNIVERSAL PROGRAMMING TOOLS.** The UniSite<sup>™</sup> 40, our most sophisticated programmer, handles all devices—memory, logic, and microcontrollers—in a single site. The modular approach to logic programming is the 29B with a LogicPak<sup>™</sup>. Or for portable convenience, the 60A programs popular logic and memory devices. Add our handler and workstation software for complete programming support on the production line.

# UNIVERSALLY APPROVED BY PLD

MANUFACTURERS. When you use Data I/O tools, you can depend on the accuracy and reliability of your programmed PLD. We work with semiconductor manufacturers—long before devices are released—to develop, and obtain approvals for, our programming algorithms. So reliable support will always be ready when you need it.

### A CLOSER LOOK AT UNIVERSAL SUP-PORT. Call us today for more informa-

tion about Data I/O's complete line

of PLD development tools and qualify for your FREE copy of the ABEL 3.0 demonstration disk. Your PLDs will be off to a better start and a faster finish.

1-800-247-5700 Dept. 314

DATA I/O

Data I/O Corporation 10525 Willows Road N.E., P.O. Box 97046, Redmond, WA 98073-9746, U.S.A. (206) 881-6444/Telex 15-2167 Data I/O Canada 6725 Airport Road, Suite 302, Mississauga, Ontario L4V IV2 (416) 678-0761/Telex 06968133 Data I/O Japan Sumitomesimei Higashishinbash BIGU, JS, P.Z. 74, Higashi-Shinbashi, Minato-ku, Tokyo 105, Japan (03) 432-6991/Telex 2522685 DATAIO J

**CIRCLE NUMBER 8**

### ETTERS

# Floorplanning

IN YOUR April issue, David Hightower, in his Industry Insights "Floorplanning for the Future" (p. 18), states that a "sophisticated, highly interactive floorplanner is required. Even the 'automatic' placement tool in the floorplanner should be interactive; that is, it should have a 'human subroutine' through which it calls the operator from time to time to solve some local problem and then continues searching for the global solution."

Such a floorplanning tool was developed at IBM in 1984. It is described in the paper "CRAFT: A Customizable Refinable Algorithmic Floorplanning Tool" presented at the 1986 ICCD and written by Peter Van Dyke and me. The paper is primarily devoted to the algorithms, but the graphics are briefly described. We also discussed the ability to invoke the algorithms through the graphics interface and switch between interactive and automatic procedures.

The graphics tool displays the placement, histograms of wire congestion in the x and ydirections, the maximum congestion in x and y, the total wire length in the x and ydirections, and the x and ydimensions of the floorplan. Options are listed on the screen next to the placement.

The designer can invoke the automatic placement algorithm (for a user-specified number of moves), exchange objects at any level of the hierarchy with any other object at that level (including exchanges with an empty space in the hierarchy), rotate a macro (the lowest-level object in the hierarchy), and invoke a global channel program to space the macros apart for wiring.

The user-driven moves are

made in the context of the hierarchical structure on which the algorithm operates. As a result, the entire placement is modified in response to efficiently remove empty space. After any action the resulting placement and its corresponding statistics are displayed.

There is also a capability to change the scoring parameters driving the automatic placement. Consequently, the designer can tune the algorithm as he proceeds.

This tool was originally developed to observe the type of manual moves that would improve floorplans in order to create a function that would mimic these types of moves. Thus, in a sense, it is also an expert system.

The tool for the future I would like to see is one that would store information about the types of moves a designer makes and automatically modify the algorithm to produce these moves.

YEHUDAH RELIS IBM Corp. Poughkeepsie, N.Y.

# **Missing Cells**

ALTHOUGH I applaud the idea of your recent cell synthesis "rally" ("Cell Synthesis in Action," May, p. 52), I feel there were several problems in the way that it was conducted and the way that you represented our entry.

• When we received the benchmark schematic, we entered it into our tools using the SLICC language, and two bugs were detected immediately. We contacted your editor about the bugs and agreed on a revised circuit, which is the one you published.

• You did not publish our layout. Instead, you published Caeco's layout twice. •You mentioned that we submitted three layouts but did not explain why.There were three factors left open in the rally. First, since your benchmark did not specify transistor sizes, we ran ours once for minimum size, which gave a 28-ns cycle time; once with sizes optimized for speed by our TILOS sizer, which gave a 5-ns cycle time.

The second factor was the use of second-level metal. Although your rules said that second-level metal was available, several of the published layouts did not use it. Secondlevel metal reduces resistance and delay but may increase size a little bit in small layouts, since it has larger design rules. In big designs, though, it saves area and improves performance.

The third factor was the question of multiple strips of logic. Again, small layouts tend to be a little more compact in a single row, whereas bigger designs require multiple rows.

• You state that the SCS tool is the only system capable of producing multiple strips. Not only can SC2D do this, but several of the layouts published in your article demonstrate this capability.

You identified our entry only as "the AT&T system." In fact, it is called SC2D. The distinction is important, since SC2D is one of several research prototype cell layout tools being developed at AT&T for chip designs. These tools are compatible but distinct; they produce different styles of layout (for example, cell/stripbased, single/multiple devices per polysilicon column, abutted rows). SC2D is part of a much larger CAD system, called IDA, that includes editors, compacters, simulators, logic synthesis tools, and special-purpose generators.

• Finally, you failed to mention what is perhaps SC2D's biggest advantage: it regularly handles tens of thousands of individually sized transistors at one shot, synthesizing dozens of strips.

Thank you for allowing us to set the record straight on these issues.

DWIGHT D. HILL, DON SHU-GARD, and JACK FISHBURN AT&T Bell Laboratories Murray Hill, N.J.

EDITOR'S REPLY: The original idea of the article was to give our readers information about some of the different automatic cell layout systems that exist today. It was an informal project and there was no intention of running a "race" between the participating vendors. In the article, we discussed some of the features and results but deliberately avoided picking "winners" and "losers," since the ground rules were not defined well enough to provide a level playing field for all the players.

We included AT&T's tools, even though they are proprietary, since they offered another viewpoint on cell synthesis tools and included some advanced features that would be of interest to our readers.

However, we must apologize for the inadvertent error in mixing up AT&T's layout with that of another vendor.

We also agree that AT&T was the first to discover the bugs in the original circuit. As soon as the bugs were discovered, a corrected schematic was sent to all participants.

The original article was written by Ernest Meyer. Unfortunately, although Ernest received credit on the table of contents, his byline was omitted from the article itself.

# *Or...*

ANN ANN

The choice is really quite simple. Dozens of different PLDs expensively stocked to meet every need. Or the generic GAL® family of programmable high-performance logic devices.

# Reprogrammable CMOS.

Behind this family is our Generic Array Logic (GAL) architecture. First developed and produced by Lattice, this architecture lets one GAL device replace all common 20 or 24 pin PAL<sup>®</sup> devices.

Fabricated with Lattice's proprietary E<sup>2</sup>CMOS<sup>™</sup> technology, GAL devices give you bipolar speed and lower power. Half-power parts are available with maximum gate delays of 15ns. Quarter-power delays are 25ns. Both reduce heat without loss of performance.

Gone are discarded fuse-link parts caused by misprogramming. Gone is the need for expensive window packaging. Gone are long UVerase cycles. Instead, you simply plug your GAL device back into the programmer and erase and reprogram in less than a second. Design changes are simple and easy, too.

### **Inventory reductions.**

From a manufacturing and management perspective, the GAL family offers even more. Now PAL and other PLD inventories can be dramatically reduced. At the same time, design alternatives multiply.

Because GAL devices are reprogrammable, they are also reuseable. And last-minute design changes mean simple reprogramming rather than costly replacement.

# 100% tested.

Unlike other PLDs, GAL devices are 100% tested for optimum system quality. There is simply no need to overstock in anticipation of a high failure rate.

So forget about that pile of "Eithers." And learn more about the Lattice "Or." To find out how GAL devices fit all of your PLD needs, ask for a free copy of the Lattice GAL Data Book today.

E<sup>2</sup>CMOS is a trademark of Lattice Semiconductor. GAL is a registered trademark of Lattice Semiconductor. PAL is a registered trademark of Monolithic Memories, Inc

5555 N.E. Moore Ct. • Hillsboro, OR. 97124

The GAL Revolution Starts Here"

# The Tuning of a Logic Minimizer

MICHAEL C. GALVIANO, ALTERA CORP., SANTA CLARA, CALIF.

Upgraded tool reduces designs for EPLDs further and faster

Minimization of logic expressions is critical for the efficient use of PLD resources. If the needs of a designer's project exceed the fixed resources of a programmable logic device, the part becomes useless to the designer. Because designers' needs are growing, minimization programs must be upgraded to produce efficient designs in the short amount of time characteristic of PLDs.

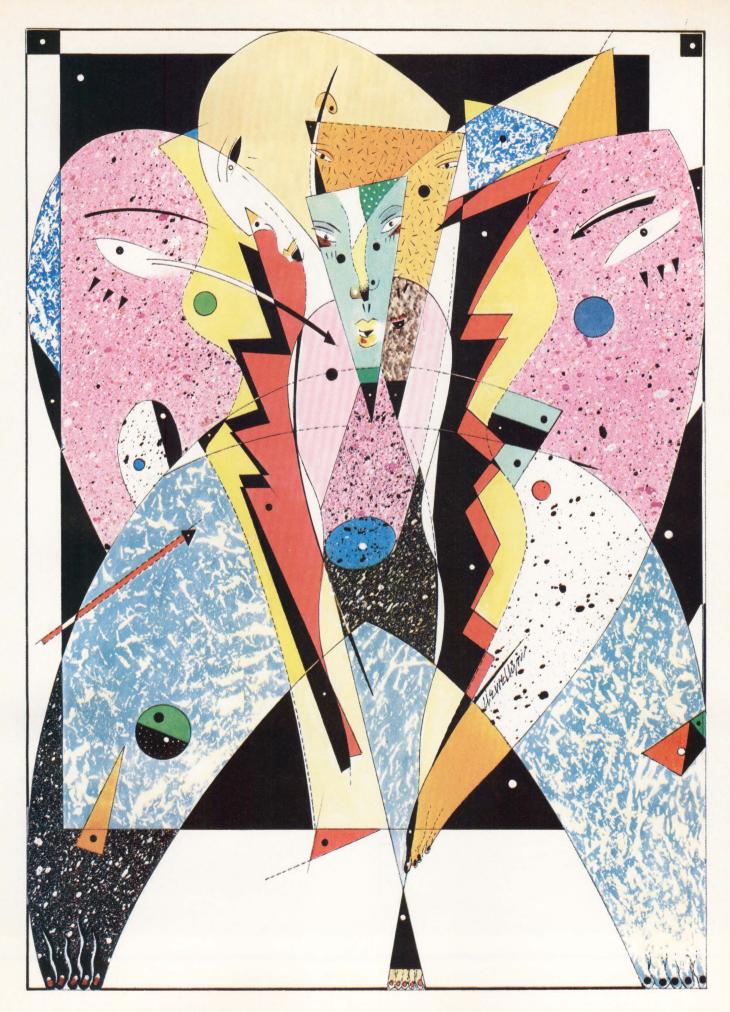

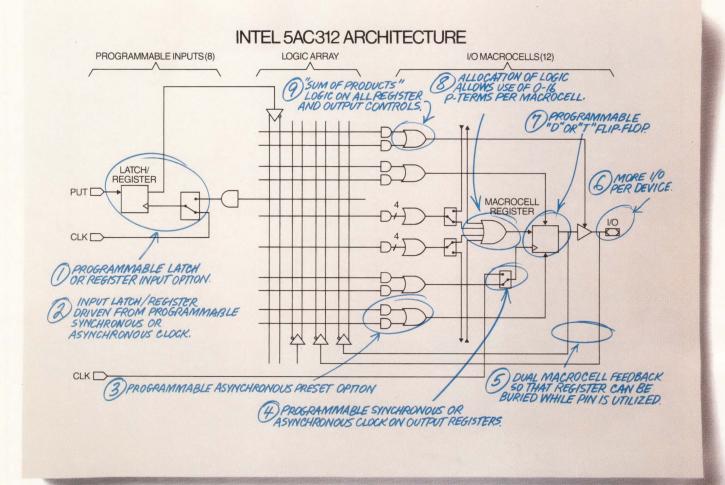

From the beginning of the development of the A + Plus software package, for use with the company's erasable PLDs, Altera has put significant effort into the functional module assigned the task of product-term minimization. This minimization module, called the Standard A + Plus Logic Simplification Algorithm (Salsa), is also found in Altera's Max + Plus design system (Figure 1).

We have reevaluated Salsa to judge the effectiveness of its results against a widely used and understood minimization program, Espresso. In addition, we have upgraded the algorithms within Salsa to increase its throughput. The enhanced Salsa now resides in Altera's design tools.

Salsa has gone through several incarnations since its first release in 1984. Each release was

# 17 MIPS. 210K transistors. And one chance to get it right.

1997

# To build the world's highest performance RISC microprocessor, AMD turned to Mentor Graphics IC layout tools.

It was a bold, ambitious project: build the fastest 32-bit  $\mu$ P in existence. One delivering a 5X to 7X performance improvement over existing 32-bit processors.

So Advanced Micro Devices turned to Mentor Graphics' Chip Station® to get the Am 29000 into silicon in a single iteration. Why? Because Chip Station provided the most advanced capabilities available, yet could also emulate AMD's existing tools.

# Sharpen your competitive edge.

Look inside Chip Station and you'll find features like advanced traversal capabilities that make moves through the hierarchy as simple as point and click. And polygon-based editing that prevents problems like self-intersecting data. Also, programmable stroke recognition, which immediately converts cursor movements into commands. And now, the industry's fastest VLSI color plotting solution.

# Complete compatibility with your existing environment.

Chip Station's programmable user interface shortens your learning curve by emulating the commands of your current system. At the same time, Mentor Graphics helps you adapt to the rich feature set of Chip Station and graduate to a truly advanced IC layout methodology.

Chip Station also brings you both the capacity and performance to deal with the coming generation of ULSI designs. Structured

1 Milling

DRACULA II is a trademark of Cadence.

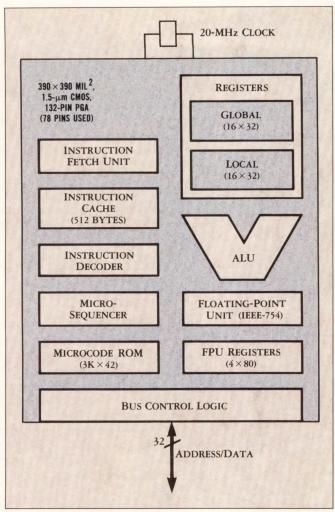

AMD's new RISC-based, 32-bit Am 29000 microprocessor operates at a 25 MHz clock rate with a 40 ns instruction cycle time. It can bit a peak execution rate of 25 MIPS, with a sustained performance of 17 MIPS. Because of its exceptional speed and price-performance ratio, the Am 29000 can be used in a wide range of applications—from embedded controller designs to engineering workstations.

Chip Design lets you represent cells symbolically so the organization and management of large designs is greatly simplified. And REMEDI<sup>™</sup> expands DRACULA II<sup>™</sup> LVS checks to include graphic correlation of errors in both schematics and layouts.

# The emerging standard.

Mentor Graphics' IC design and layout tools have already earned a solid reputation for productivity on large, complex VLSI projects. As a result, we're the world's fastest growing supplier of IC layout systems.

It's all part of a vision unique to Mentor Graphics, the leader in electronic design automation. Let us show you where this vision can take you.

Call us toll-free for an overview brochure and the number of your nearest sales office.

1-800-547-7390 (in Oregon call 284-7357).

Yourideas. Our experience.

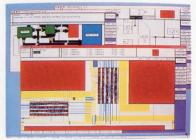

Figure 1. The A + Plus and Max + Plus design systems use the Salsa program to minimize the sum-of-products representations of designs that are targeted for Altera's EPLDs.

intended to improve the capabilities or speed of the program. When we became aware of the software offerings made available by the University of California at Berkeley, we had to decide whether to adopt its PLA minimization tool, Espresso, or to continue to refine Salsa. Espresso is a fine program that enjoys firm theoretical foundation. It has a reputation for being efficient and for producing results that were at least close to a given problem's optimum solution. The question of interest to us was whether it would improve our software's performance when used by our customers to create EPLD designs.

Because designers run the A + Plus and Max + Plus design software on personal computers, we needed to compare the code size and memory requirements of Espresso and Salsa. PC-DOS limits total code and data memory usage to 640 kilobytes. We found that although Espresso could be ported to run on DOS machines, its code was somewhat larger than Salsa's. We also know very precisely how much

data space Salsa requires because it has been tailored to work with the rest of Altera's design tool suite. The extent of Espresso's memory utilization depends on the particular problem being solved. It may use significantly more memory while processing complex expressions than it does for more simple ones.

We also needed to evaluate failure modes that resulted from expression complexity. Salsa always produces a logically correct expression—even if the expression is too complex to minimize sufficiently to fit within one of our EPLDs. If Espresso encounters an expression with too many prime product terms, or implicants, in either its complemented or uncomplemented form, the program aborts.

As mentioned above, Salsa was designed to work with the rest of Altera's tools. The I/O routines and file formats it uses fit comfortably into the tools' overall framework. We had some concern that processing speed would suffer and code size increase if we had to build special I/O routines for Espresso. We were confident, though, that this potential problem could be overcome, should Espresso prove the best choice based on other criteria.

Another area of concern was what we call "non-Boolean minimization." Our EPLDs feature fully programmable I/O architectures. In many cases, the A+Plus and Max + Plus software must determine which of the possible flip-flop configurations available on a particular macrocell result in the best utilization of an EPLD. Altera has added algorithms to Salsa that select the best I/O configuration for customers' designs. Obviously, Espresso was not designed to include this function. We could pull the non-Boolean minimization functions out of Salsa and add it as a separate routine to Espresso. Such an approach, however, could reduce processing speed and increase code size.

Finally, we needed to evaluate maintenance and reliability issues. In the event that a software defect is found, we must be in a position to provide a timely response