| · APPLIC  |           |     | REVISION            |          |          |

|-----------|-----------|-----|---------------------|----------|----------|

| NEXT ASSY | - USED ON | LTR | DESCRIPTION         | DATE     | APPROVED |

| 1020089   | 8510      | А   | RELEASE PER 8500-13 | 10/28/76 | 1/10.    |

| 1020090   | 8530      |     |                     |          |          |

8500

NOTES :

1. For Revisions See Sheet 2

NOV 01 1976

| UNLESS OTHERWISE SPECIFIED<br>DIMENSIONS ARE IN INCHES<br>TOLERANCES ARE: | CONTRACT NO.  |          | J.       | ANC       | 30      |           |         |                     |               |

|---------------------------------------------------------------------------|---------------|----------|----------|-----------|---------|-----------|---------|---------------------|---------------|

| FRACTIONS DECIMALS ANGLES                                                 | APPROVALS     | DATE     |          | SUNNYVALE | . CALIF | ORNIA     |         |                     |               |

| ± .XX ± ± .XXX ±                                                          | DRAWN W. ROMA | 10/7/76  |          | PRODUCT   | SPEC    | IFICATION | 1       |                     |               |

| MATERIAL                                                                  | CHECKED       | 10/19/76 |          | MODEL 8   | 500 D   | ISC MEMO  | RY      |                     |               |

|                                                                           |               |          | SIZE     | CODE IDEN | IT NO   | DRAWING N | ·       | -                   | Toes          |

| FINISH                                                                    |               |          | A        | CODE IDEN | n no.   |           | 1570013 |                     | REV<br>A      |

| DO NOT SCALE DRAWING                                                      |               | -        | SCALE    |           |         |           | SHEET 1 | OF 2                | 7             |

| BISHOP GRAPHICS/ACCUPRES<br>REORDER NO. A-7700                            | S             |          | <u> </u> |           |         |           |         | Made Control of San | Marian Caraca |

1570013

#### PAGE NUMBER

|   |   | 1       | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20                 | 21       | 22     | 23 | 24       | 25 | 26 | 27          | 28 |

|---|---|---------|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|--------------------|----------|--------|----|----------|----|----|-------------|----|

| = | A | Α       |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| _ |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - |   | !<br>!  |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| _ |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - | _ |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - |   | <u></u> |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    | -  |    | _  |                    |          | -      |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    | -  | -  |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    | -  | -  | -  |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    | -  |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

|   |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    | Ī  |    |    |                    |          |        |    |          |    |    |             | -  |

|   | • |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          | ,  |    |             |    |

|   |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

|   |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    | ,                  |          |        |    |          | -  |    | _           |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    | $\left  - \right $ |          |        | -  |          | -  |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    | -  |    |    |                    |          |        |    |          |    |    |             |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    | $\dashv$ |        |    | $\dashv$ |    |    | $\dashv$    |    |

| - |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          |        |    | 7        |    |    | 7           |    |

| 1 |   |         |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |                    |          | $\neg$ |    | $\dashv$ |    |    | <del></del> |    |

| SIZE  | CODE | IDEN | T NO. | DRAWING | NO |       | 70 | 013 | <br>REY<br>A |

|-------|------|------|-------|---------|----|-------|----|-----|--------------|

| SCALE |      |      |       |         |    | SHEET | 2  | 2   | <br>         |

#### TABLE OF CONTENTS

|                            |                                    | PAGE |

|----------------------------|------------------------------------|------|

| 1.0 INTRODUCTION           |                                    | 4    |

| 2.0 REFERENCE DOCUMEN      | TS                                 | 4    |

| 3.0 GENERAL SPECIFICATI    | ons                                | 5    |

| 4.0 ENVIRONMENTAL SPE      | CIFICATIONS                        | 6    |

| 5.0 POWER REQUIREMENTS     | S                                  | 7    |

| 6.0 MAJOR MEMORY SYST      | 'EM COMPONENTS                     | 8    |

| 7.0 PHYSICAL CHARACTER     | ISTICS                             | 11   |

| 8.0 INTERFACE SPECIFICAT   | TIONS - GENERAL                    | 11   |

| 9.0 INTERFACE SIGNAL DI    | EFINITION - DISC INPUT<br>SIGNALS  | 14   |

| 10.0 INTERFACE SIGNAL DE   | EFINITION - DISC OUTPUT<br>SIGNALS | 15   |

| LIST OF                    | TABLES AND FIGURES                 |      |

| TABLE 1 J2 INTERFACE SIGN  | NAL PIN ASSIGNMENT                 | 13   |

| FIGURE 1 TYPICAL DRIVER-RE | ECEIVER CONFIGURATION              | 18   |

| FIGURE 2 TIMING DIAGRAM    | , WRITE TIMING                     | 19   |

| FIGURE 3 TIMING DIAGRAM    | , CLOCK TIMING                     | 19   |

| FIGURE 4 TIMING DIAGRAM    | , READ TIMING                      | 20   |

| SIZE  | CODE IDEN | T NO. | DRAWING |       | 0013 | REV<br>A |

|-------|-----------|-------|---------|-------|------|----------|

| SCALE |           |       |         | SHEET | 3    |          |

#### 1.0 INTRODUCTION

#### 1.1 Scope

This specification describes a rotating memory designed for storage of data with an average access time of 8.3 milliseconds (3600 RPM), or 16.7 milliseconds (1800 RPM) and a maximum storage capacity of  $38.4 \times 10^{\circ}$  bits.

#### 1.2 Model Number

The Model Number is constructed as shown below:

|     | 85X0-Y                              |

|-----|-------------------------------------|

| X   | SPEED                               |

| 1   | 1800 RPM                            |

| 3   | 3600 RPM                            |

|     |                                     |

| Υ   | NUMBER OF TRACKS                    |

| 16  | Sixteen tracks                      |

| 32  | Thirty-two tracks                   |

| 48  | Fourty eight tracks                 |

| 64  | Sixty-four tracks                   |

| 96  | Ninety-six tracks                   |

| 128 | One hundred and twenty-eight tracks |

| 192 | One hundred and ninety two tracks   |

| 256 | Two hundred and fifty six tracks    |

#### 2.0 REFERENCE DOCUMENTS

- 2.1 Outline and Mounting Drawing DWG. No. 1520006

- 2.2 Power Supply Specification DWG. No. 1510017-01

| SI  | ZE  | CODE | IDENT | NO. | DRAWING | NO. | 1570013 | RE<br>A | V |

|-----|-----|------|-------|-----|---------|-----|---------|---------|---|

| SC. | ALE |      |       | ,   |         | S   | HEET 4  |         |   |

|     |       |                                                                                                  |                                     | < Mac.                      |

|-----|-------|--------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------|

| 3.0 | GENER | AL SPECIFICATIONS                                                                                | 8530 Series                         | 8510 Series                 |

|     | 3.1   | Storage Capacity (Maximum)                                                                       | $40.2 \times 10^6$ bits             | 40.2 x 10 <sup>6</sup> bits |

|     | 3.2   | Data Tracks (Maximum)                                                                            | 256 (plus 32 spares)                | 256 (plus 32 spares)        |

|     | 3.3   | <u>Bits/Track</u> (Unformatted absolute Maximum)                                                 | 157,000                             | 157,000                     |

|     | 3.4   | Gap between TO and 1st Sector                                                                    | 40 microseconds/<br>min.            | 40 microseconds min.        |

|     | 3.5   | Bits/Sector                                                                                      |                                     |                             |

|     |       | The maximum sector length is determined by the track capacity, from the following relationships: |                                     |                             |

|     |       | Case I: Track capacity < 12<br>Max Sector Length                                                 | - <del>-</del>                      |                             |

|     |       | Case 2: Track capacity > 12<br>Max Sector Length                                                 |                                     | C - 122000)                 |

|     | 3.6   | Preamble (written by Disc Memory)                                                                | 19 bits                             | 19 bits                     |

|     | 3.7   | Postamble-Write Guard Bits (written by Disc Memory)                                              | l bit                               | l bit                       |

|     |       | - Guard Space                                                                                    | 12 bits                             | 12 bits                     |

|     | 3.8   | Rotational Speed                                                                                 | 3600 <u>+</u> 95 RPM                | 1800 <u>+</u> 55 RPM        |

|     | 3.9   | Average Access Time                                                                              | $8.3 \pm 0.2$ milsec.               | 16.7 ± 0.4 milsec           |

|     | 3.10  | <u>Data Transfer Rate</u> (at 150,000 bits/tra                                                   | ack)<br>9.0 <u>+</u> 0.6 M Bits/sec | 4.5 <u>+</u> 0.3M Bits/     |

|     | 3.11  | Disc Diameter                                                                                    | 12 inch                             |                             |

|     | 3.12  | Recording Medium                                                                                 | NiCo with Rhodium protec            | ctive overcoat              |

|     | 3.13  | Recording Density (at 150,000 bits/track                                                         | 7448 Bits/Inch Maximum (track)      | innermost data              |

|     | 3.14  | MTBF                                                                                             | 10,000 hours for 85XX-25            | 6 models                    |

|     |       | SIZE                                                                                             | CODE IDENT NO. DRAWING NO.          | 1570013 REV                 |

SCALE

SHEET

5

3.15 MTTR

One hour

3.16 Error Rate

Recoverable Errors:

The occurrence of recoverable errors shall be less than one error in 10 11 bits read.

Non-recoverable Errors:

The occurrence of non-recoverable errors shall be less than one error in  $10^{12}$  bits read.

NOTE:

A non-recoverable error is defined as a single bit or many consecutive bits in error from which valid data cannot be recovered within three consecutive passes through the same data record.

3.17 Preventative Maintenance

The Disc pre-filter and power supply filters shall be replaced when they become dirty.

#### 4.0 ENVIRONMENTAL SPECIFICATIONS

#### 4.1 <u>Temperature</u>

Operating (assumes writing at one extreme 0 to 55°C and reading at the opposite extreme)

Non-operating (On Site) 0 to 65°C

Non-operating (Shipping and storage -30 to 65°C properly packed)

4.2 <u>Temperature Change</u>

Operating max. for data reliability 10°C per hour

4.3 Relative Humidity

Operating without condensation: 10% - 90%

Non-Operating without condensation 10% - 90%

| SIZE<br><b>A</b> | CODE IDEN | T NO. | DRAWING | N | o.<br>1570013 | REV |

|------------------|-----------|-------|---------|---|---------------|-----|

| SCALE            | ,         |       |         |   | SHEET 6       |     |

#### 4,4 Shock and Vibration

Vibration

Operating:

.040" double amplitude

displacement, 5-22 Hz;

1g acceleration max, 22 - 500 Hz

Non-operating

.040" double amplitude

dîsplacement, 5-30Hz;

2g acceleration max, 30 - 500 Hz

Shock:

Operating:

5g 11 Msec 1/2 sine wave

Non-operating

5g II Msec 1/2 sine wave

#### 4.5 Shipping

The packaged product to meet the approval of the NATIONAL SAFE TRANSIT COMMITTEE, Project IA. (100 lbs or less)

#### 4.6 Altitude

Operating:

10,000 feet

Non-operating:

25,000 feet

4.7 Atmosphere

Non-corrosive

#### 5.0 POWER REQUIREMENTS

#### 5.1 A.C. Power

| 5.1.1 | Voltage             | 88 - 108  | VAC RMS |

|-------|---------------------|-----------|---------|

|       | (single phase, rear | 105 - 130 |         |

|       | panel selectable)   | 192 - 240 |         |

210 - 260

5.1.2 Frequency 47 - 53 Hz 57 - 63 Hz

5.1.3 Start Current 8.3 amps maximum

(with 120 volts)

5.1.4 Run Current (with 120 volts)

2.7 amps maximum

| SIZE  | CODE IDEN | T NO. | DRAWING | 1 1   | 0013 | REV<br>A |

|-------|-----------|-------|---------|-------|------|----------|

| SCALE | ·         |       |         | SHEET | 7    |          |

20 seconds maximum

- 5.1.6 A toggle power ON/OFF switch provides power control for motor and D.C. power supply.

- 5.1.7 A single fuse protects the transformer. The fuse is located in the line cord receptacle at the rear of the unit.

#### 5.2 Power Loss

The system is capable of withstanding an A.C. power loss of 10 milliseconds without malfunction or data error.

#### 5.3 UL/CSA Approval

- 5.3.1 UL Component Recognition per UL-478 will be obtained and maintained, except for 50 Hz only units.

- 5.3.2 CSA Listing per C22.2 will be obtained and maintained, except for 50 Hz only units.

#### 6.0 MAJOR MEMORY SYSTEM COMPONENTS

The 8500 Series is composed of the following major component parts.

#### 6.1 Disc

A 12-inch diameter, .200 inch thick plated with nickel cobalt is mounted to the spindle assembly. The disc has a thin Rhodium overcoat to allow contact start - stop.

#### 6.2 Spindle

The disc is mounted to the spindle via a "zero - clearance" assembly which maintains the disc location throughout the machine's temperature range. The locking device is an impeller to provide filtered air for pressurizing the enclosure. The spindle is driven by means of a belt and step pulley.

#### 6.3 Drive Motor

A capacitive start, 50/60 Hz induction motor provides the power to the disc. A step pulley compensates for a change in line frequency. Separate motors are used for 1800 and 3600 RPM applications.

| SIZE  | CODE IDEN | T NO. | DRAWING | NO. /5 | 700/3 | REV |

|-------|-----------|-------|---------|--------|-------|-----|

| SCALE |           |       |         | SHEET  | 8     |     |

#### 6.4 Read/Write Head Assemblies

- 6.4.1 Standard triple transducer configuration read/write heads are used.

- 6.4.2 The transducers contact the disc when the disc is not rotating, and fly 12 ± 5 micro inches when the disc reaches operating speed.

#### 6.5 Memory Assembly

- 6.5.1 The basic memory assembly consists of the baseplate spindle, disc, head plate, and motor.

- 6.5.2 The memory assembly is supported by four shock mounts.

- 6.5.3 The rotating assembly is in a dust sealed enclosure which is pressurized by a filter impeller system; the minimum required pressures are:

.05 inches of water:

1800 RPM

.20 inches of water:

3600 RPM

6.5.4 The maximum allowable particle count in the rotating assembly is: less than 5 particles, 0.5 microns or larger over a 10 minute period and a flow rate of 0.01 cubic feet/minute.

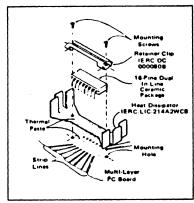

#### 6.6 Interface Electronics

- 6.6.1 The digital interface electronics are packaged on a vertically mounted P.C. Board (Interface Board) at the back of the package.

- 6.6.2 The Input/Output functions of the disc unit are transmitted and received by 7400 TTL family devices.

#### 6.7 Read/Write Electronics

With the exception of the Clock Preamplifier, the analog Read/Write and the head selection electronics are packaged on a P.C. board (Memory Board) which is mounted directly above the Disc Memory Sub Assembly.

| SIZE  | CODE IDEN | T NO. | DRAWING | NO. | 15.70 | 0013 | REV<br>A |

|-------|-----------|-------|---------|-----|-------|------|----------|

| SCALE |           |       |         |     | EET   | 9    |          |

#### 6.8 Bit Clock, Sector and Track Origin Generation

- 6.8.1 One triple transducer head assembly is mounted to detect the recorded bit clock, sector clock and track origin (TO).

- 6.8.2 Clocks are recorded on two tracks simultaneously for the purpose of having one identical spare.

- 6.8.3 Changing from one track to the spare set is accomplished by changing a wire wrap jumper.

- 6.8.4 The third track may be used to record an AMCOMP standard format.

- 6.8.5 Protection is provided to prevent erasure or alteration of these recorded timing signals.

#### 6.9 D.C. Power Supply

6.9.1 The D.C. Power Supply exhibits the following general characteristics.

6.9.2 The specifications of the power supply are documented in DWG. No. 1510017-01

#### 6.10 Other Assemblies

- 6.10.1 The tray assembly supports the Disc Meniory Sub Assy and also mount the A.C. input connector and inner slides.

- 6.10.2 The rear panel assembly mounts on the tray and holds the Interface Card. The rear panel assembly also mounts the I/O connectors for the active unit.

- 6.10.3 The RFI cover encloses the electronics and reduces both susceptibility to and emissions of stray magnetic fields.

The RFI cover is easily removed for access to the major electronics.

| SIZE  | CODE IDEN | IT NO. | DRAWING |    | 157  | 70013 | RE<br>L | EV<br>J |

|-------|-----------|--------|---------|----|------|-------|---------|---------|

| SCALE |           |        |         | SI | HEET | 10    |         |         |

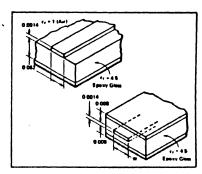

#### 7.0 PHYSICAL CHARACTERISTICS

- 7.1 Outline Dimension

- 7.1.1 Height 8.75 inches

- 7.1.2 Depth 22.00 inches

- 7.1.3 Mounting Width: Standard 19-inches

- 7.1.4 The outline dimensions and mounting details are documented in DWG No. 1520006.

- 7.2 Weight 95 lbs

#### 8.0 INTERFACE SPECIFICATIONS - GENERAL

- 8.1 Levels

- 8.1.1 The I/O signal levels and pertinent figures are defined as seen on the I/O connector.

- 8.1.2 Signal levels on the bus of the disc memory system are nominally 0 and +3.0 volts, which are compatible with both TTL and DTL family of circuits.

- 8.1.2.1 Interface logic levels are defined as shown below:

| LOGIC 0 | 0 volts nom.<br>+0.4 volts max.                        |

|---------|--------------------------------------------------------|

| LOGIC 1 | +2.4 volts min.<br>+3.0 volts nom.<br>+5.25 volts max. |

| SIZE  | CODE IDEN | T NO. | DRAWING |       | 70013 | REV<br>A |

|-------|-----------|-------|---------|-------|-------|----------|

| SCALE |           |       |         | SHEET | 11    |          |

8.1.3 Every line must be driven toward ground by a NPN transistor collector that is capable of sinking 48 ma and maintaining a maximum saturated output voltage of 0.4 volts.

The following integrated circuits are especially suited to these requirements:

|                    | <b>re</b> quirements                                               | <b>:</b>                                              |                                                          |  |  |  |  |

|--------------------|--------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|--|--|--|--|

|                    |                                                                    | Part Number                                           | Manufacturer                                             |  |  |  |  |

| 4                  |                                                                    | Sn 7438, SN75451                                      | Texas Instruments                                        |  |  |  |  |

| 8.1.4              | <del>-</del>                                                       | o and from the disc are neg<br>nd illegal address)    | gative true (except BUS                                  |  |  |  |  |

| 8.1.5              | All signal li                                                      | nes will also be terminated                           | at the controller.                                       |  |  |  |  |

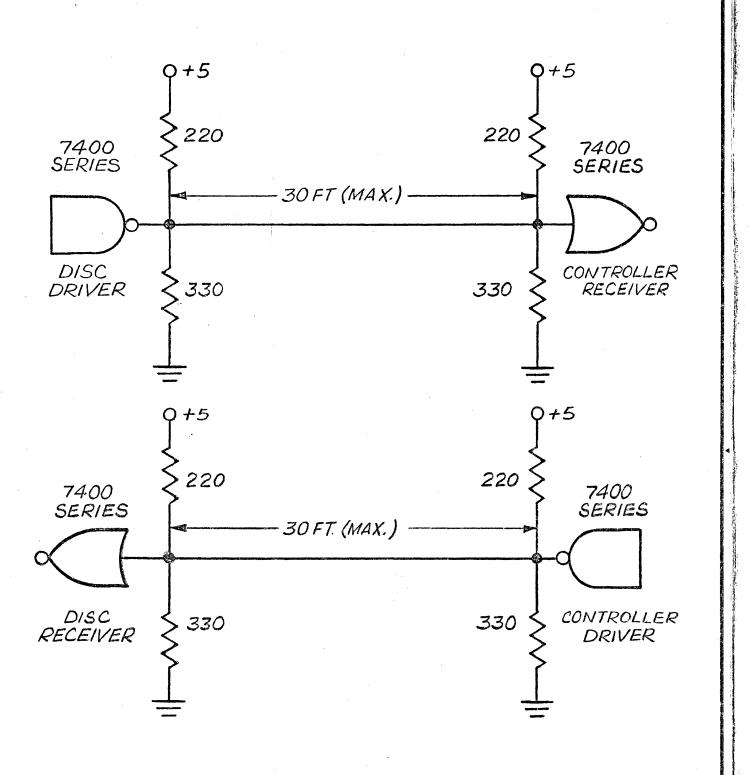

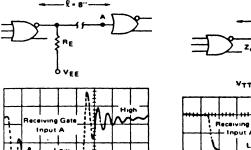

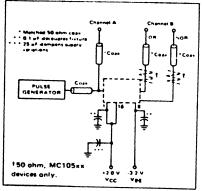

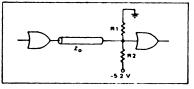

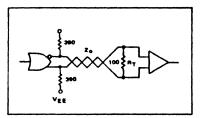

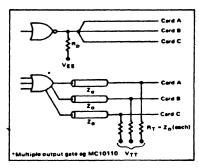

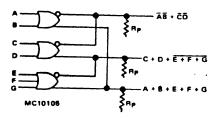

| 8.1.6              | .1.6 A typical Driver-Receiver configuration is shown in Figure 1. |                                                       |                                                          |  |  |  |  |

| <u>Daisy-Chain</u> | ning                                                               |                                                       |                                                          |  |  |  |  |

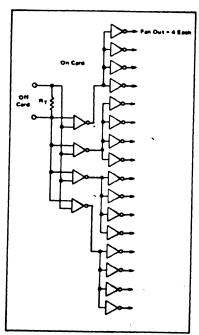

| 8.2.1              |                                                                    | e allows for (4) disc units t<br>I by one controller. | o be daisy-chained                                       |  |  |  |  |

| 8.2.2              | •                                                                  | em is designed for a maxima 9.0 M bit transfer rate.  |                                                          |  |  |  |  |

| Interface Co       | onnectors                                                          |                                                       |                                                          |  |  |  |  |

| 8.3.1              |                                                                    |                                                       | the rear panel assembly<br>nnector (Part No. 1090010-01) |  |  |  |  |

| 8.3.2              | The following                                                      | a table identifies the inter                          | face signal pin assignments.                             |  |  |  |  |

|   | SIZE  | CODE IDEN | T NO. | DRAWING | NO. | 157  | 70013 | REV<br>A |

|---|-------|-----------|-------|---------|-----|------|-------|----------|

| - | SCALE |           |       |         |     | HEET | 12    |          |

8.2

.8.3

| PIN NO.     | FUNCTION         | PIN NO. | FUNCTION        |

|-------------|------------------|---------|-----------------|

| 1:          | RETURN           | 42      | READ            |

| <b>18</b> / | DISC READ        | 43      | RETURN          |

| 34          | N/C              | 10      | WRITE           |

| 35          | TRACK ADDRESS-7  | 27      | RETURN          |

| 2           | TRACK ADDRESS-6  | 11      | READ DATA       |

| 19          | TRACK ADDRESS-5  | 28      | RETURN          |

| 3           | TRACK ADDRESS-4  | 44      | BUS TERMINATED  |

| 20          | TRACK ADDRESS-3  | 45      | RETURN          |

| 36          | TRACK ADDRESS-2  | 12      | WRITE DATA      |

| 37          | TRACK ADDRESS-1  | 29      | RETURN          |

| 4           | TRACK ADDRESS-0  | 13      | SPARE 1         |

| 21          | UNIT SELECT 3    | 30      | DC GROUND       |

| 5           | UNIT SELECT 2    | 46      | READ CLOCK      |

| 22          | UNIT SELECT 1    | 47      | RETURN          |

| 38          | UNIT SELECT 0    | 14      | SPARE 2         |

| 39          | RETURN           | 31      | RETURN          |

| 6           | ILLEGAL ADDRESS  | 15      | WRITE CLOCK IN  |

| 23          | RETURN           | 32      | RETURN          |

| 7           | NOT USED IN 8500 | 48      | SPARE 3         |

| 24          | RETURN           | 49      | RETURN          |

| 40          | TRACK ORIGIN     | 16      | WRITE CLOCK OUT |

| 41          | RETURN           | 33      | RETURN          |

| 8           | SECTOR CLOCK     | 17      | SHIELD GROUND   |

| 25          | RETURN           | 50      | SHIELD GROUND   |

| 9           | SECTOR WRITE     |         |                 |

| 26          | RETURN           |         |                 |

TABLE 1. J2 - INTERFACE SIGNAL PIN ASSIGNMENT

| SIZE  | CODE IDEN | T NO. | DRAWING  | NO. |      | 30010 | nestaline. | REV |

|-------|-----------|-------|----------|-----|------|-------|------------|-----|

| A     |           |       |          |     | 151  | 70013 |            | Α   |

| SCALE |           |       | <u> </u> | SH  | IEET | 13    |            |     |

#### 9.0 INTERFACE SIGNAL DEFINITION - DISC INPUT SIGNALS

#### 9.1 Unit Select

9.1.1 Four unit select lines are provided to support chaining up to four discs on a single cable assembly.

One line is assigned to a disc. Selection is made by the installation of a jumper assembly on the interface board.

All discs will be shipped with the Unit Select 1 jumper installed.

- 9.1.2 The proper unit select line must be set to logic zero to allow the disc to write, read, or change track address.

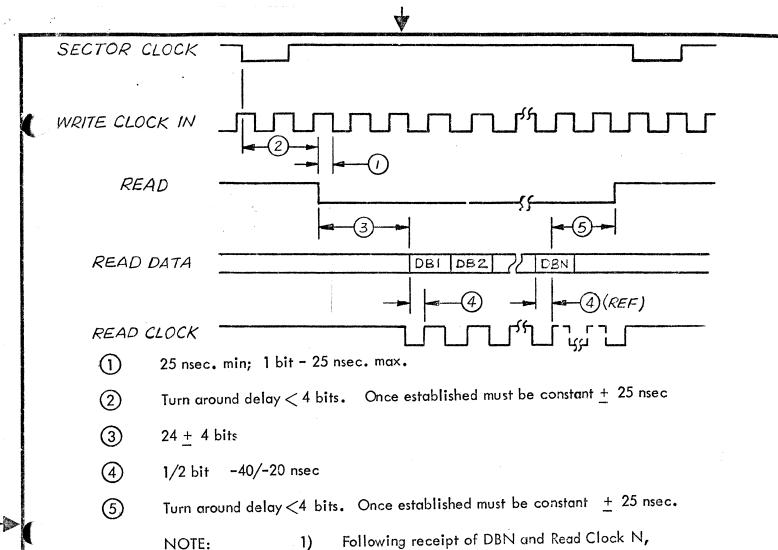

- 9.1.3 Following the end of a read operation, the unit must stay selected for at least 1 usec. See Fig. 4.

- 9.1.4 By adding a jumper from TP22 to TP58 the following additional functions are disabled by deselecting the unit.

Write Clock Out Sector Clock Disc Read Track Origin

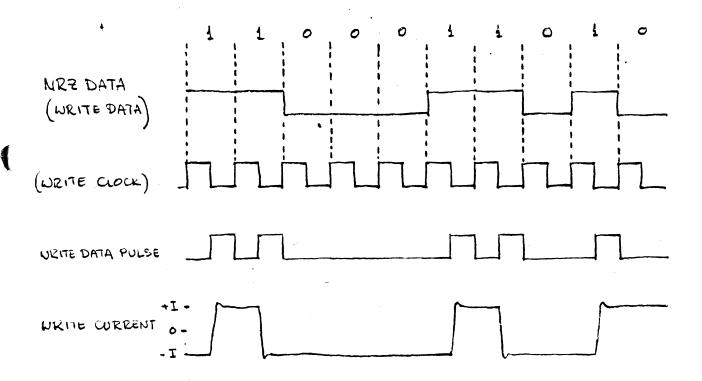

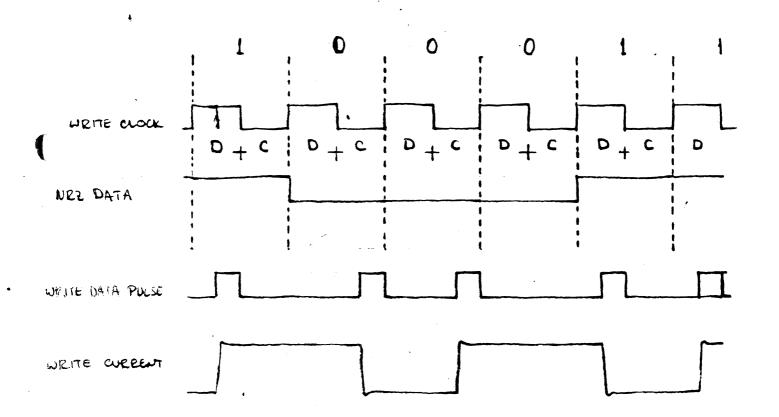

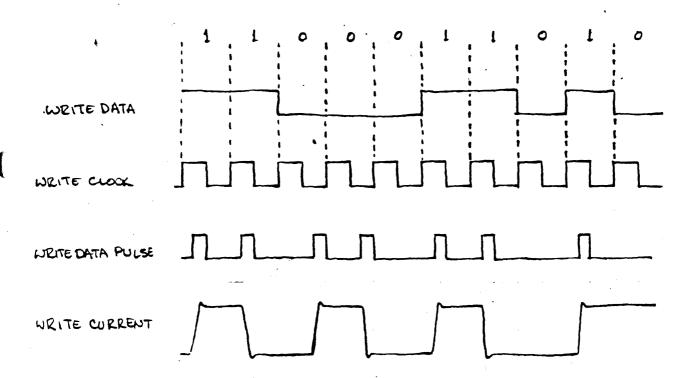

#### 9.2 Write

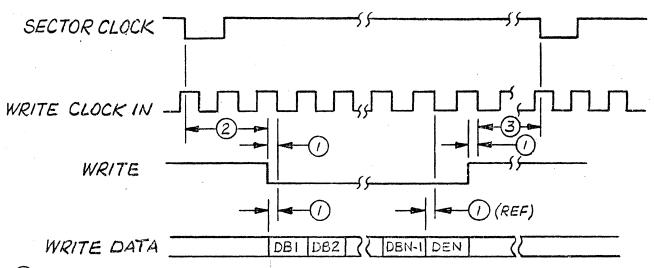

9.2.1 When the signal is set to a logic zero, data on the WRITE DATA line will be recorded on the selected disc track.

The WRITE signal must be set to a logic zero synchronized to the SECTOR CLOCK.

The WRITE command must remain at a logic zero until the last bit of data has been transmitted and then reset to a logic one (Ref. Figure 2)

#### 9.3 <u>Read</u>

9.3.1 When this signal is set to a logic zero, the READ DATA along with the READ CLOCK will be transmitted from the selected data head.

The READ signal must be set to a logic zero synchronized to the SECTOR CLOCK.

| SIZE<br>A | CODE I | DENT | NO. | DRAWING | NO. | 157  | 10013 | REV<br>A |

|-----------|--------|------|-----|---------|-----|------|-------|----------|

| SCALE     |        |      |     |         | s   | HEET | 14    |          |

The READ command must remain at a logic zero until the last bit has been received and then reset to a logic one (Ref. Figure 4).

#### 9.4 Write Data

9.4.1 When WRITE is a logic zero, this signal line will carry serial NRZ data to be recorded on the selected data head.

#### 9.5 Write Clock In

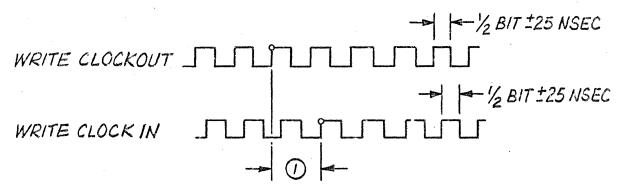

9.5.1 This signal is the cable delayed version of WRITE CLOCK OUT.

WRITE DATA is received in the disc electronics with this continuous clock (Ref. Fig. 3). WRITE CLOCK IN must be present for a min. of 20 bits after sending the last WRITE DATA bit.

#### 9.6 Track Address

9.6.1 These eight lines provide the binary address of the data head to which a write or read operation is to be performed.

These lines must be present and stable as long as a write or read operation is performed.

The full eight lines are to be used regardless of the specific number of heads installed in the disc (256 maximum, 16 minimum).

#### 9.7 Sector Write

9.7.1 The clock format can be written with this line, when the disc unit has been properly set up for initialization by a field engineer.

#### 10.0 INTERFACE SIGNAL DEFINITION - DISC OUTPUT SIGNALS

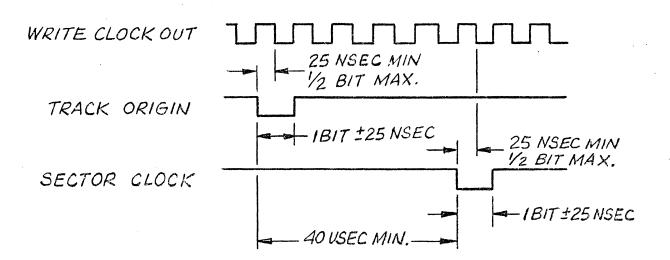

#### 10.1 Track Origin

10.1.1 The TRACK ORIGIN is a single pulse, one bit wide, defining the start of a disc revolution.

| SIZE  | CODE IDEN | T NO. | DRAWING |       | 10013 | REV<br>A |

|-------|-----------|-------|---------|-------|-------|----------|

| SCALE |           |       |         | SHEET | 15    |          |

This signal line, normally a logic one, is pulsed to a logic zero to indicate TRACK ORIGIN.

#### 10.2 Sector Clock

10.2.1 The SECTOR CLOCK is a single pulse, one bit wide, defining the start of a sector. All WRITE and READ commands are timed from the SECTOR CLOCK,

This signal line, normally a logic one, is pulsed to a logic zero to indicate SECTOR CLOCK (Ref. Figure 5).

#### 10.3 Read Data

10.3.1 When READ is a logic zero, this signal line will provide serial NRZ data from the selected data head in synchronism with the READ CLOCK. (Ref. Figure 4)

#### 10.4 Read Clock

10.4.1 The READ CLOCK defines each bit of data to be read on the READ DATA output line.

The READ CLOCK is only present when actual data is present on the READ DATA line. The READ CLOCK is a repetition pulse with a period of one bit (Ref. Figure 5).

#### 10.5 Write Clock Out

10.5.1 The WRITE CLOCK OUT is a continuous clock signal defining each bit cell on the track.

This signal shall be used to transmit WRITE DATA to disc unit and shall be returned to the disc unit as a WRITE CLOCK IN.

The WRITE CLOCK OUT can be used to strobe the Sector and Track Origin Clocks into the Controller.

#### 10.6 Disc Ready

10.6.1 When this signal is a logic zero, the disc unit is ready to reliably transmit or receive data.

| SIZE  | CODE IDEN | T NO. | DRAWING | NO. | 1570013 | REV<br>A |

|-------|-----------|-------|---------|-----|---------|----------|

| SCALE |           |       |         | SH  | HEET 16 |          |

The DISC READY will be set to a logic one under the following conditions:

- 1. DC voltages below acceptable limits

- Disc rotational speed below reliable operating range.

- 3. BUS TERMINATED is at logic zero.

#### 10.7 Illegal Address

11.7.1 This signal will be set to a logic one when the received address exceeds the maximum address of the machine or, in machines equipped withthe write lock-out feature, a write operation is attempted on a locked-out track.

#### 10.8 Bus Terminated

10.8.1 The BUS TERMINATED signal senses the power to the active disc interface terminations. A logic zero on this line indicates a loss of power to the signal line terminations. All other interface lines should be considered invalid.

| SIZE  | CODE IDEN | T NO. | DRAWING |       | 00/3 | REV |

|-------|-----------|-------|---------|-------|------|-----|

| SCALE |           |       |         | SHEET | 17   |     |

Figure 1. Typical Driver-Receiver Configuration

| SIZE<br><b>A</b> | CODE IDEN | T NO. | DRAWING | NO. | 15   | 700/3 | REV<br>A |

|------------------|-----------|-------|---------|-----|------|-------|----------|

| SCALE            |           |       |         | s   | HEET | 18    |          |

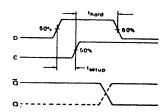

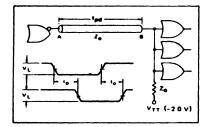

- 1 bit 25 nsec. max.

- 2 turn around delay<4 bits Once established must be constant + 25 nsec.

- 32 bits -2

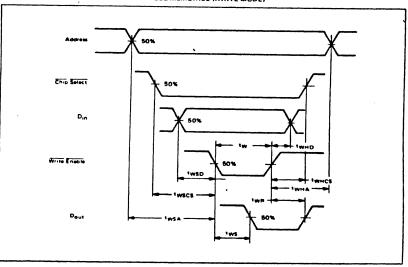

Figure 2. Timing Diagram, Write Timing

Round trip cable, driver/receiver delay. Once established must remain constant + 25 nsec.

Figure 3. Timing Diagram, Clock Timing

| SIZE  | CODE IDEN | T NO. | DRAWING |       | 0013 | REV<br>A |

|-------|-----------|-------|---------|-------|------|----------|

| SCALE |           |       |         | SHEET |      |          |

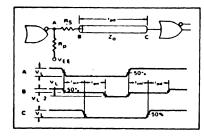

Sector Clock.

be ignored.2) Last Sector Clock to Truck-Origin is equal in time relations like a Sector Clock to the next

additional Read Clocks may occur due to turn around delay of Read reset. These clocks should

Figure 4. Timing Diagram, Read Timing

SIZE CODE IDENT NO. DRAWING NO. 1570013 REV A

Figure 5. Timing Diagram, Basic System Timing

| SIZE  |    | CODE | IDEN | T NO. | DRAWING | N |       | 0013 | e was to the | REV<br>A                     |

|-------|----|------|------|-------|---------|---|-------|------|--------------|------------------------------|

| SCALI | Ξ. |      |      |       |         |   | SHEET | 21   |              | marete on a shaka salka 2008 |

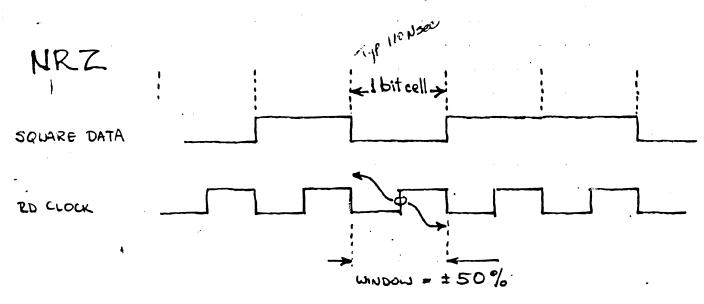

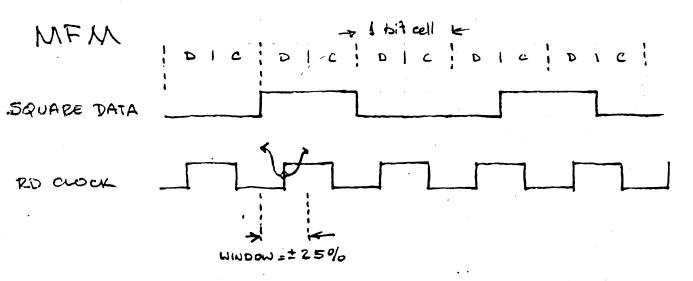

## RECORDING CODES IN THE 8500

- 1. NRZI

- Z MFM (AMCODE)

# WHICH ONE ?

### 1\_NRZI

- a) Simple to encode & decode

- b) large window

- c) Previously used in 8400

### 2. MFM

- a) NO JITTER PROBLEMS

- b) No sector size limitations

- c) Same ratio of fit to Bpi as NRZI, therefore no loss in density.

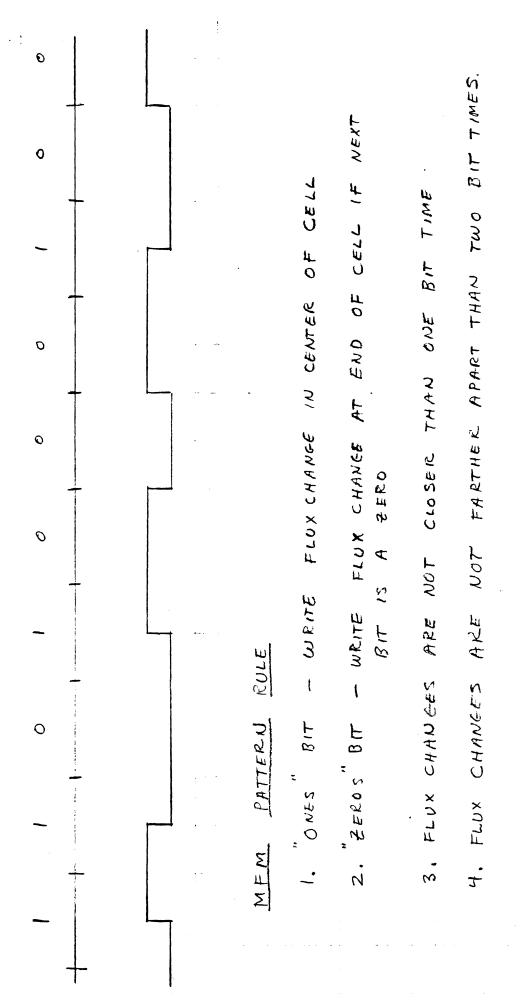

### ENCODING RULES

NRZI

A flux Change for every one'.

### ENCODING RULES

### WFM

- 1. A flux change in the "Data" half of the cell for every "one".

- 2. Aflux change in the "Clock" half of the cell for every "gero" except when a "gero" is followed by a "one".

# MFM PATTERN (same as NPRI pattern used previously)

WHAT IS THE WINDOW?

... The leading edge of clock can drift ±50% of the bit cell before it misses the data transition.

. The leading edge of the clock can drift  $\pm 25\%$  of the bit cell before it misses a transition in the Data half of the cell.

#### TYPICAL PATTERNS

### 10124 - QUAD TIL - ECL TRANSLATOR

Y / PACKAGE

10.231 - DUAL TYPE D FLIP FLOP

POSITIVE EDEE TRIBBER

POSITIVE LEVEL SET - RESET

10125 - QUAD DIFFERENTIAL INPUT ECL-TTL TRANSCATED

10164 - GUAD FND/NAND.

10116 - DIFFERENTIAL LINE RECEIVER

ASSUME NUMINAL LEVELS -0.9V TRUE -1.8V FALSE

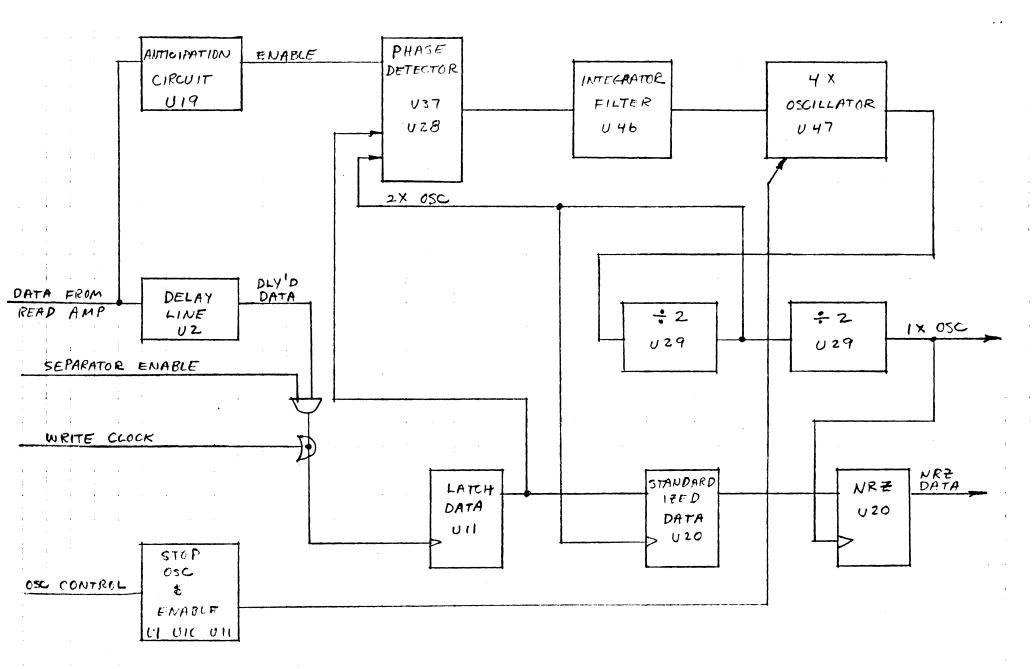

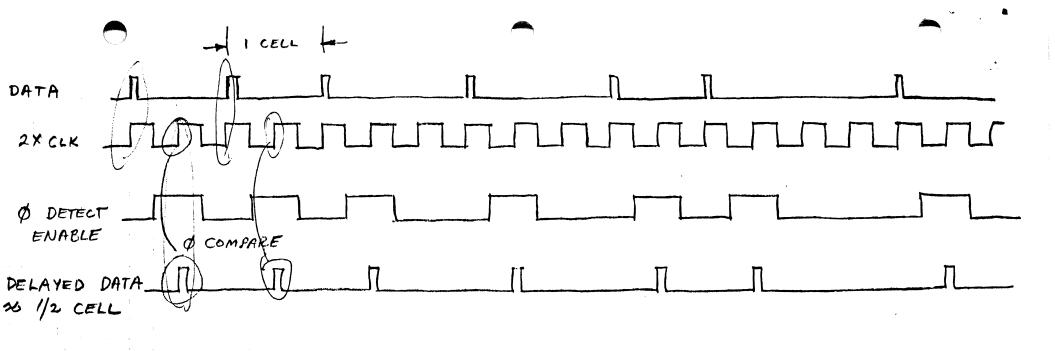

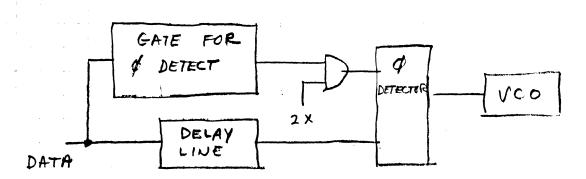

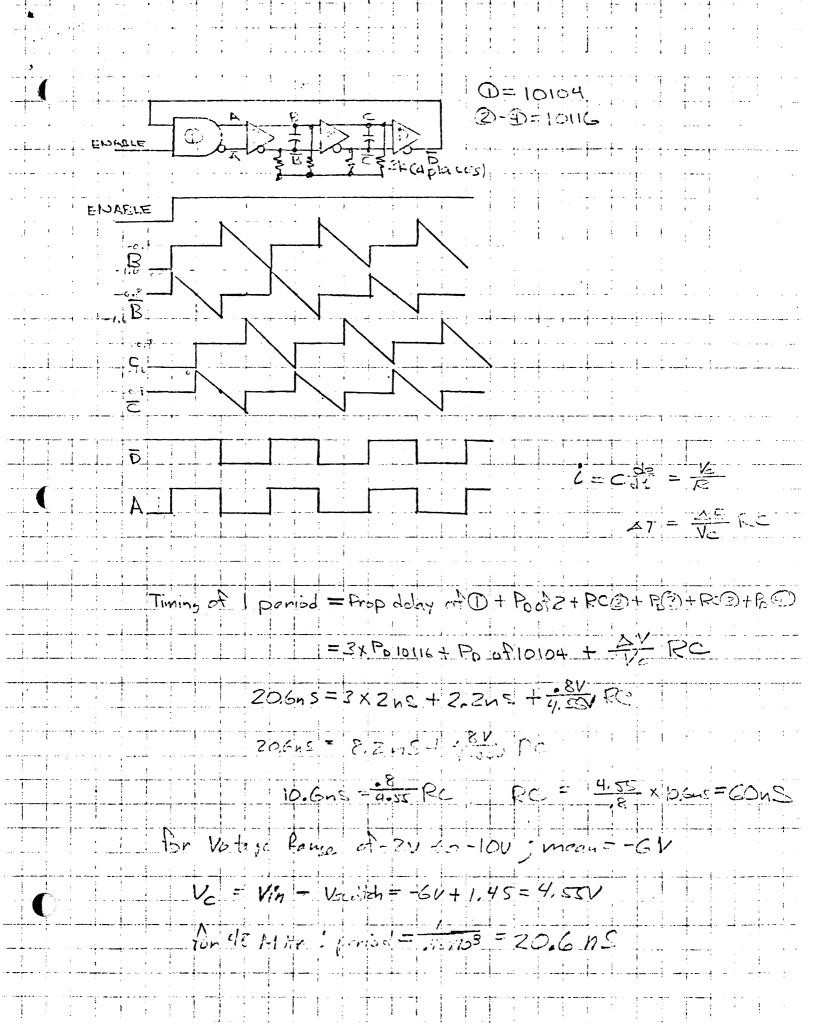

DATA SEPARATOR BLOCK

| CELL BOUNDARY              |     |     | 1 |        |

|----------------------------|-----|-----|---|--------|

| DATA U32-9 1               | 1 0 | 1 1 | 0 | 0. 1 0 |

| DATA U23-8                 |     |     |   |        |

| CLOCK U23-6                |     |     |   |        |

| MEM U32-5 TO WRITE DRIVER) |     |     |   |        |

| URITE DRIVER_0             |     |     |   |        |

|                            |     |     |   |        |

MFM WRITE ENCODE

| DATA HEAD PREAMBLE I.A. O DATA - MFM  WRITE CLOCK |

|---------------------------------------------------|

| READ                                              |

| EPARATOR ENABLE  STOP OSC                         |

| STOP OSC                                          |

| STOP OSC                                          |

|                                                   |

|                                                   |

| OSC ENABLE                                        |

| osc 11111                                         |

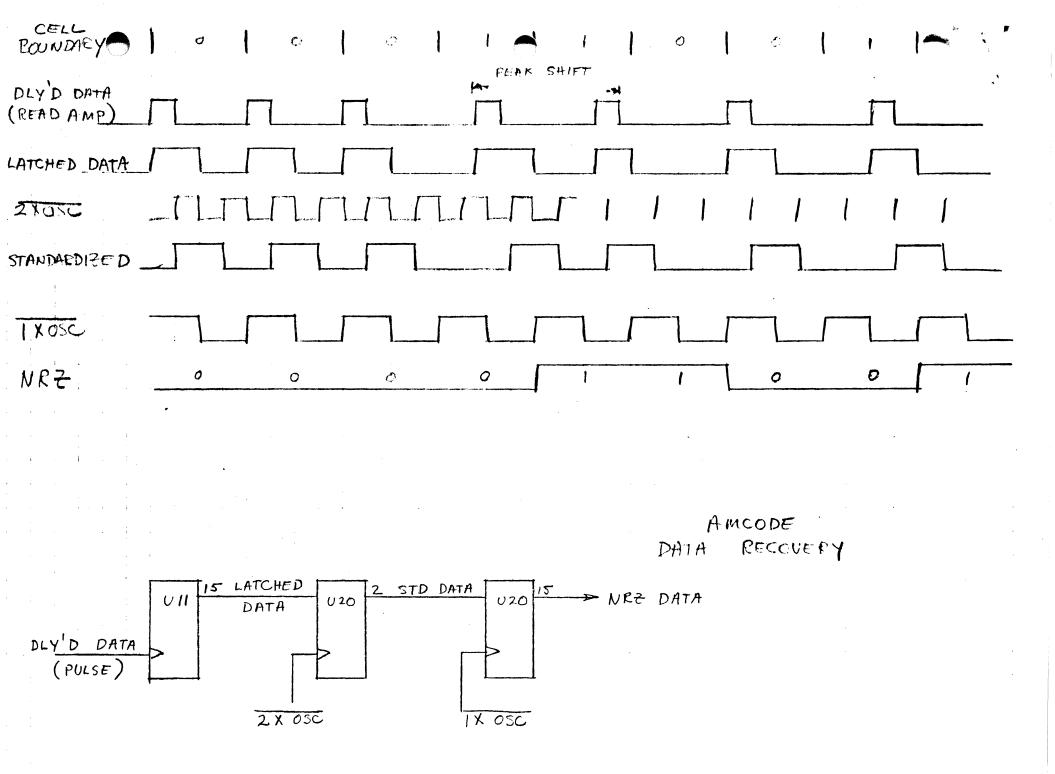

SEPARATOR SYNC

AMCODE DATA SEPARATOR

BASIC & DETECT

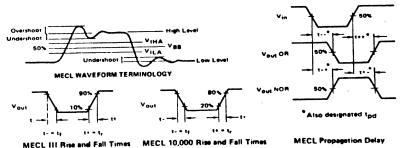

# GENERAL INFORMATION SECTION I — HIGH-SPEED LOGICS

High speed logic is used whenever improved system performance would increase a product's market value. For a given system design, high-speed logic is the most direct way to improve system performance and emitter-coupled logic (ECL) is today's fastest form of digital logic. Emitter-coupled logic offers both the logic speed and logic features to meet the market demands for higher performance systems.

#### MECL PRODUCTS

Motorola introduced the original monolithic emitter-coupled logic family with MECL I (1962) and followed this with MECL II (1966). These two families are now obsolete and have given way to the MECL III (MC1600 series), MECL 10,000 MECL 10800, and PLL (MC12000 series) families.

Chronologically the third family introduced, MECL III (1968) is a higher power, higher speed logic. Typical 1 in edge speeds and propagation delays along with greater than 500 MHz flip-flop toggle rates, make MECL III useful for high-speed test and communications equipment. Also, this family is used in the high-speed sections and critical timing delays of larger systems. For more general purpose applications, however, trends in large high-speed systems showed the need for an easy-to-use logic family with propagation delays on the order of 2 is. To match this requirement, the MECL 10,000 Series was introduced in 1971.

An important feature of MECL 10,000 is its compatibility with MECL III to facilitate using both families in the same system. A second important feature is its significant power economy — MECL 10,000 gates use less than one-half the power of MECL III. Finally, low gate power and advanced circuit design techniques have permitted a new level of complexity for MECL 10,000 circuits. For example, the complexity of the MC10803 Memory Interface Function compares favorably to that of any bipolar integrated circuit on the market.

The basic MECL 10,000 Series has been expanded by a subset of devices with even greater speed. This additional series provides a selection of MECL 10,000 logic functions with flip-flop repetition rates up to 200 MHz min. The MECL 10,200 Series is meant for use in critical timing chains, and for clock distribution circuits. MECL 10,200 parts are otherwise identical to their 10,000 Series counterparts (subtract 100 from the MECL 10,200 part number to obtain the equivalent standard MECL 10,000 part number).

Continuing technical advances led more recently to the development of the M10800 LSI processor family. The M10800 family combines the performance of ECL with the system advantages of LSI density. Architectural features of the M10800 family significantly reduce the component count of a high-performance processor system. The M10800 LSI family is fully compatible with the MECL 10,000 and MECL III logic families for a complete selection of system design components.

#### **MECL FAMILY COMPARISONS**

|                           | MECL 10,000                    |                                |             |               |

|---------------------------|--------------------------------|--------------------------------|-------------|---------------|

| Feeture                   | 10,100 Series<br>10,500 Series | 10,200 Series<br>10,600 Series | 10,800 LSI* | MECL III      |

| 1. Gate Propagation Delay | 2 ne                           | 1.5 ns                         | 1 - 2.5 ns  | 1 ns          |

| 2. Output Edge Speed      | 3.5 ne                         | 2.5 ns                         | 3.5 ns      | 1 ns          |

| 3. Flip-Flop Toggle Speed | 160 MHz                        | 250 MHz                        | N.A.        | 300 - 500 MHz |

| 4. Gate Power ,           | 25 mW                          | 25 mW                          | 2.3 mW      | 60 mW         |

| 5. Speed Power Product    | 50 pJ                          | 37 pJ                          | 4.6 pJ      | 60 pJ         |

<sup>\*</sup>Average for Equivalent LSI Gate.

#### FIGURE 1. - GENERAL CHARACTERISTICS

| Ambient<br>Temperature Range | MECL 10,000                                         | M10800         | MECL III       | PLL            |

|------------------------------|-----------------------------------------------------|----------------|----------------|----------------|

| 0° to 75°C                   | MCM10100 Series                                     | -              | MC 1697P       | MC12000 Series |

| -30°C to +85°C               | MC10100 Series<br>MC10200 Series                    | MC10800 Series | MC 1600 Series | MC12000 Series |

| -55°C to 125°C               | MC10500 Series<br>MC10600 Series<br>MCM10500 Series | -              | MC1648M        | MC12500 Series |

#### FIGURE 16 - OPERATING TEMPERATURE RANGE

| Package Style          | MECL 10,000      | M10800          | MECL III        | PLL             |

|------------------------|------------------|-----------------|-----------------|-----------------|

| 16-Pin Plastic DIP     | MC10100P Series  | -               | MC1658P         | MC12000P Series |

|                        | MC10200P Series  |                 |                 |                 |

| 16-Pin Ceramic DIP     | -MC10100L Series | MC10804L        | MC16001. Series | MC12000L Series |

|                        | MC10200L Series  | MC10807L        |                 | MC12500L Serie  |

|                        | MC10500L Series  |                 |                 | '               |

|                        | MC10600L Series  |                 |                 |                 |

|                        | MCM10100L Series |                 |                 |                 |

|                        | MCM10500L Series |                 |                 |                 |

| 16-Pin Flat Package    | MC10500F Series  | -               | MC1600F Series  | MC12513F        |

|                        | MC10600F Series  |                 |                 |                 |

|                        | MCM10500F Series |                 |                 |                 |

| 20 Pin Ceramic DIP     | -                | MC10805L        | -               | -               |

| 24-Pin Plastic Package | MC10181P         | -               | +               | -               |

| 24-Pin Ceramic DIP     | MC10181L,        | MC10802L        | -               | · -             |

|                        | MC10581L         |                 |                 |                 |

| 24 Pin Flat Package    | MC10581F         | -               | -               | -               |

| 48 Pin Ceremic Quil    | -                | MC10800L Series | -               | -               |

| 14 Pin Plastic DIP     | -                | -               | MC1648P         | MC12000P        |

|                        |                  |                 |                 | MC12002P        |

|                        |                  |                 |                 | MC12020P        |

|                        |                  | <u> </u>        |                 | MC12040P        |

| 14 Pin Ceramic DIP     |                  | ` -             | MC1648L         | MC12000L        |

|                        |                  |                 |                 | MC12002L        |

|                        |                  |                 |                 | MC12020L        |

|                        |                  |                 |                 | MC12040L        |

| 14 Pin Flat Package    |                  | -               | MC1648F         | MC12540F        |

| 8-Pin Plastic DIP      | -                | -               | MC1697P         | -               |

For package information see page 1-28.

#### FIGURE 1c - PACKAGE STYLES

#### MECL IN PERSPECTIVE

In evaluating any logic line, speed and power requirements are the obvious primary considerations. Figure 1 provides the basic parameters of the MECL 10,000, M10800, and MECL III families. But these provide only the start of any comparative analysis, as there are a number of other important features that make MECL highly desirable for system implementation. Among these:

-Complementary Outputs cause a function and its complement to appear simultaneously at the device outputs, without the use of external inverters. It reduces package count by eliminating the need for associated invert functions and, at the same time, cuts system power requirements and reduces timing differential problems arising from the time delays introduced by inverters.

1.2

1.3

High Input Impedance and Low Output Impedance permit large fan out and versatile drive characteristics.

Insignificant Power Supply Noise Generation, due to differential amplifier design which eliminates current spikes even during signal transition period.

Nearly Constant Power Supply Current Drain simplifies power-supply design and reduces costs. Low Cross-Talk due to low-current switching in signal path and small (typically 850 mV) voltage

swing, and to relatively long rise and fall times.

Wide Variety of Functions, including complex

functions facilitated by low power dissipation

(particularly in MECL 10,000 series). A basic

MECL 10,000 gate consumes less than 8 mW in

on-chip power in some complex functions.

Wide Performance Flexibility due to differential amplifier design which permits MECL circuits to be used as linear as well as digital circuits.

Transmission Line Drive Capability is afforded by the open emitter outputs of MECL devices. No "Line Drivers" are listed in MECL families, because every device is a line driver.

Wire-ORing reduces the number of logic devices required in a design by producing additional OR sate functions with only an interconnection.

Twisted Pair Drive Capability permits MECL circuits to drive twisted-pair transmission lines as long as 1000 feet.

Wire-Wrap Capability is possible with MECL 10,000 and the M10800 LSI family because of the slow rise and fall time characteristic of the circuits.

Open Emitter-Follower Outputs are used for MECL outputs to simplify signal line drive. The outputs match any line impedance and the absence of internal pulldown resistors saves power.

Input Pulldown Resistors of approximately 50 k11 permit unused inputs to remain unconnected for easier circuit board layout.

#### MECL APPLICATIONS

Motorola's MECL product lines are designed for a wide range of systems needs. Within the computer market, MECL 10,000 is used in systems ranging from special purpose peripheral controllers to large mainframe computers. Big growth areas in this market include disk and communication channel controllers for larger systems and high performance minicomputers.

The industrial market primarily uses MECL for high performance test systems such as IC or PC board testers. However, the high bandwidths of MECL 10,000, MECL III, and MC12,000 are required for many frequency synthesizer systems using high speed phase lock loop networks. MECL will continue to grow in the industrial market through complex medical electronic products and high performance process control systems.

MECL 10,000 and MECL III have been accepted within the Federal market for numerous signal processors and navigation systems. Full military temperature range MECL 10,000 is of-

fered in the MC10500 and MC10600 Series, and in the PLL family as the MC12500 Series.

# BASIC CONSIDERATIONS FOR HIGH-SPEED LOGIC DESIGN

High-speed operation involves only four considerations that differ significantly from operation at low and medium speeds:

- Time delays through interconnect wiring, which may have been ignored in medium-speed systems, become highly important at state-of-theart speeds.

- The possibility of distorted waveforms due to reflections on signal lines increases with edge speed.

- The possibility of "crosstelk" between adjacent signal leads is proportionately increased in high-speed systems.

- 4. Electrical noise generation and pick-up are more detrimental at higher speeds.

In general, these four characteristics are speedand frequency-dependent, and are virtually independent of the type of logic employed. The merit of a particular logic family is measured by how well it compensates for these deleterious effects in system applications.

The interconnect-wiring time delays can be reduced only by reducing the length of the interconnecting lines. At logic speeds of two nanoseconds, an equivalent "gate delay" is introduced by every foot of interconnecting wiring. Obviously, for functions interconnecting wiring. Obviously, for functions interconnected within a single monolithic chip, the time delays of signals travelling from one function to another are insignificant. But for a great many externally interconnected parts, this can soon add up to an appreciable delay time. Hence, the greater the number of functions perhip, the higher the system speed. MECL circuits, particularly those of the MECL 10,000 Series are designed with a propensity toward complex functions to enhance overall system speed.

Waveform distortion due to line reflections also becomes troublesome principally at state-of-the-art speeds. At slow and medium speeds, reflections on interconnecting lines are not usually a serious problem. At higher speeds, however, line lengths can approach the wavelength of the signal and improperly terminated lines can result in reflections that will cause false triggering (see Figure 2). The solution, as in RF technology, is to employ "transmission-line" practices and properly terminate each signal line with its characteristic impedance at the end of its run. The low-impedance, emitterfollower outputs of MECL circuits facilitate transmission-line practices without upsetting the voltage levels of the system.

----

The increased affinity for crosstalk in highspeed circuits is the result of very steep leading and trailing edges (fast rise and fell times) of the highspeed signal. These steep wavefronts are rich in harmonics that couple readily to adjacent circuits. In the design of MECL 10,000, the rise and fall times have been deliberately slowed. This reduces the affinity for crosstalk without compromising other important performance parameters.

From the above, it is evident that the MECL logic line is not simply capable of operating at high speed, but has been specifically designed to reduce the problems that are normally associated with high-speed operation.

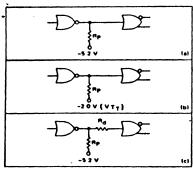

FIGURE 2a — UNTERMINATED TRANSMISSION LINE (No Ground Plane Used)

FIGURE 2b - PROPERLY TERMINATED TRANSMISSION LINE (Ground Plane Added)

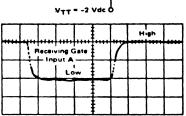

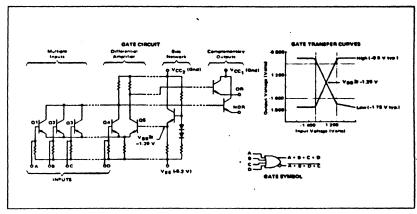

FIGURE 3 - MECL GATE STRUCTURE AND SWITCHING BEHAVIOR

#### ' CIRCUIT DESCRIPTION

The typical MECL circuit, Figure 3, consists of a differential-amplifier input circuit, a temperature and voltage compensated bias network, and emitter-follower outputs to restore dc levels and provide buffering for transmission line driving. High fanout operation is possible because of the high input impedance of the differential amplifier input and the low output impedance of the emitter follower outputs. Power-supply noise is virtually eliminated by the nearly constant current drain of the differential amplifier, even during the transition period. Basic gate design provides for simultaneous output of both the OR function and its complement, the NOR function.

Power-Supply Connections – Any of the power supply levels, VTT, VCC, or VEE may be used as ground; however, the use of the VCC node as ground results in best noise immunity. In such a case. VCC = 0, VTT = -20 V, VEE = -52 V.

System Logic Specifications — The output logic swing of 0.85 V, as shown by the typical transfer characteristics curve, varies from a LOW state of V<sub>OL</sub> = -1.75 V to a HIGH state of V<sub>OH</sub> = -0.9 V with respect to ground.

Positive logic is used when reference is made to logical "0's" or "1's." Then

"1" - -0.9 V - HIGH

Circuit Operation -- Beginning with all logic inputs LOW (nominal -1.75 V), assume that Q1 through Q4 are cut off because their P-N base-emitter junctions are not conducting, and the for-

ward-biased Q5 is conducting. Under these conditions, with the base of Q5 held at -1.29 V by the Vgg network, its emitter will be one diode drop (0.8 V) more negative than its base, or -2.09 V. (The 0.8 V differential is a characteristic of this P-N junction.) The base-to-emitter differential across Q1 — Q4 is then the difference between the common emitter voltage (-2.09 V) and the LOW logic level (-1.75 V) or 0.34 V. This is less than the threshold voltage of Q1 through Q4 so that these transistors will remain cut off.

When any one (or all) of the logic inputs are shifted upward from the -1.75 V LOW state to the -0.9 V HIGH state, the base voltage of that transistor increases beyond the threshold point and the transistor turns on. When this happens, the voltage at the common-emitter point rises from -2.09 V to -1.7 (one diode drop below the -0.9 V base voltage of the input transistor), and since the base voltage of the fixed-bias transistor (QS) is held at -1.29 V, the base-emitter voltage Q5 cannot sustain conduction. Hence, this transistor is cut off.

This action is reversible, so that when the input signal(s) return to the LOW state, 0.1-0.4 are again turned off and 0.5 again becomes forward biased. The collector voltages resulting from the switching action of 0.1-0.4 and 0.5 are transferred through the output emitter-follower to the output terminal. Note that the differential action of the switching transistors (one section being off when the other is on) furnishes simultaneous complementary signals at the output. This action also maintains constant power supply current

#### **DEFINITIONS OF LETTER SYMBOLS AND ABBREVIATIONS**

| Current: |                                                                                                                      | *INH   | HIGH level input current into a node                                                                                    |

|----------|----------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| lcc      | Total power supply current drawn from<br>the positive supply by a MECL unit under<br>test.                           | -11414 | with a specified HIGH level (VIH max) logic voltage applied to that node. (Same as I <sub>in</sub> for positive logic.) |

| (CBO     | Leakage current from input transistor on<br>MECL devices without pulldown resistors<br>when test voltage is applied. | *IINL  | LOW level input current, into a node with a specified LOW level (VIL min) logic voltage applied to that node.           |

| ICCH     | Current drain from VCC power supply with all inputs at logic HIGH level.                                             | 16     | Load current that is drawn from a MECL circuit output when measuring the output                                         |

| ICCL     | Current drain from VCC power supply with all inputs at logic LOW level.                                              |        | HIGH level voltage.                                                                                                     |

| IE       | Total power supply current drawn from a MECL test unit by the negative power supply.                                 | *10н   | HIGH level output current the current flowing into the output, at a specified HIGH level output voltage.                |

| lt       | Forward diode current drawn from an input of a saturated logic to-MECL translator when that input is at ground       | °10L   | LOW level output current: the current flowing into the output, at a specified LOW level output voltage.                 |

|          | potential.                                                                                                           | los    | Output short circuit current.                                                                                           |

| Im       | Current into the input of the test unit when a maximum logic HIGH (VIH max) is applied at that input,                | lout   | Output current (from a device or circuit, under such conditions mentioned in context).                                  |

| Current | (cont.) | : |

|---------|---------|---|

| IR | Reverse current drawn from a transistor<br>input of a test unit when VEE is applied<br>at that input. |

|----|-------------------------------------------------------------------------------------------------------|

| 'R | input of a test unit when VEE is applie                                                               |

ISC Short-circuit current drawn from a translator saturating output when that output is at ground potential.

Voltage:

VBB Reference bias supply voltage.

VBE Base-to-emitter voltage drop of a transistor at specified collector and base currents.

VCB Collector-to-base voltage drop of a transistor at specified collector and base currents.

VCC General term for the most positive power supply voltage to a MECL device (usually ground, except for translator and interface circuits).

VCC1 Most positive power supply voltage (output devices). (Usually ground for MECL devices.)

VCC2 Most positive power supply voltage (current switches and bias driver). (Usually ground for MECL devices.)

VEE Most negative power supply voltage for a circuit (usually 5.2 V for MECL devices).

VE Input voltage for measuring IF on TTL

VF Input voltage for measuring ip on interface circuits.

VtH Input logic HIGH voltage level (nominal value).

"VIH max Maximum HIGH level input voltage: The most positive (least negative) value of high-level input voltage, for which operation of the logic element within specification limits is guaranteed.

VIHA Input logic HIGH threshold voltage level.

VIHA min Minimum input logic HIGH level (threshold) voltage for which performance is specified.

"VIH min Minimum HIGH level input voltage: The least positive (most negative) value of HIGH level input voltage for which operation of the logic element within specification limits is guaranteed.

VIL Input logic LOW voltage level (nominal value).

"VIL max Maximum LOW level input voltage: The most positive (least negative) value of LOW level input voltage for which operation of the logic element within specification limits is guaranteed.

Input logic LOW threshold voltage level.

VILA max Maximum input logic LOW level (threshold) voltage for which performance is specified.

/IL min Minimum LOW level input voltage: The least positive (most negative) value of LOW level input voltage for which operation of the logic element within specification limits is guaranteed.

Vin Input voltage (to a circuit or device).

V<sub>max</sub> Maximum (most positive) supply voltage, permitted under a specified set of conditions.

\*VOH Output logic HIGH voltage level: The voltage level at an output terminal for a specified output current, with the specified conditions applied to establish a HIGH level at the output.

VOHA Output logic HIGH threshold voltage

VOHA min Minimum output HIGH threshold voltage level for which performance is specified.

VOH max Maximum output HIGH or high-level voltage for given inputs.

VOH min Minimum output HIGH or high-level voltage for given inputs.

Output logic LOW voltage level: The voltage level at the output terminal for a specified output current, with the specified conditions applied to establish a LOW level at the output.

VOLA Output logic LOW threshold voltage level.

VOLA max Maximum output LOW threshold voltage

given inputs.

VOL min Minimum output LOW level voltage for given inputs.

VTT Line load-resistor terminating voltage for outputs from a MECL device.

VOLS1 Output logic LOW level on MECL 10,000 line receiver devices with all inputs at

VEE voltage level.

VOLS2 Output logic LOW level on MECL 10,000 line receiver devices with all inputs open.

\*JEDEC, EIA, NEMA standard definition

1.6

1.7

#### **-**

1...

| Waveform rise time (LOW to HIGH), 10% |

|---------------------------------------|

| to 90%, or 20% to 80%, as specified.  |

| Waveform fall time (HIGH to LOW), 90% |

| to 10%, or 80% to 20%, as specified.  |

| Same as t+                            |

|                                       |

# ty Same as t-

Time Parameters:

| t.+             | Propagation Delay, see Figure 9.       |

|-----------------|----------------------------------------|

| <sup>1</sup> pd | Propagation delay, input to output fro |

|       | the 50% point of the input waveform at     |

|-------|--------------------------------------------|

| txtyt | pin x (falling edge noted by - or rising   |

|       | edge noted by +) to the 50% point of the   |

|       | Output waveform at pin y (falling edge     |

|       | noted by - or rising edge noted by +). (Cf |

|       | Figure 9 1                                 |

| Outp | ut wa | welorm | rise ti | me as | measure   |

|------|-------|--------|---------|-------|-----------|

|      |       |        |         |       | 0% point  |

|      |       | -      | .chaa.  |       | cified) a |

| t <sub>x</sub> . | Output waveform fall time as measured      |

|------------------|--------------------------------------------|

|                  | from 90% to 10% or 80% to 20% points       |

|                  | on waveform (whichever is specified) at    |

|                  | pin x, with input conditions as specified. |

| frog            | Toggle | frequency | of | flip-flop | or |

|-----------------|--------|-----------|----|-----------|----|

| counter device. |        |           |    |           |    |

| 4      | e          |       |       |           |

|--------|------------|-------|-------|-----------|

| fshift | Shift rate | tor a | shift | register. |

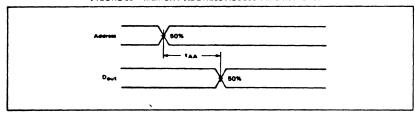

#### Read Mode (Memories)

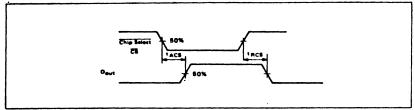

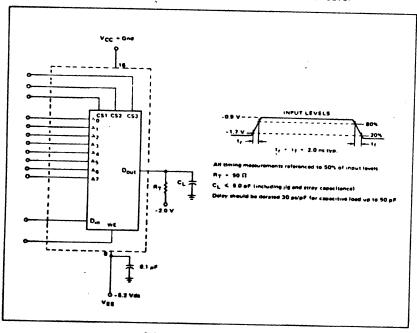

| IACS | Chip Select Access Time   |

|------|---------------------------|

| IRCS | Chip Select Recovery Time |

|      | A-4                       |

#### Write Made (Memories)

| .14  | AALLE L CLER AARTIN               |

|------|-----------------------------------|

| tws0 | Data Setup Time Prior to Write    |

| CHW  | Data Hold Time After Write        |

| tues | Address setup time prior to write |

| twhA  | Address hold time after write         |

|-------|---------------------------------------|

| twscs | Chip select setup time prior to write |

| twuce | Chin select hold time after write     |

Write disable time

Write recovery time

#### Temperature:

**twR**

| Tstg | Maximum temperature at which device<br>may be stored without damage or perfor-<br>mance degradation.                |

|------|---------------------------------------------------------------------------------------------------------------------|

| Ţj   | Junction (or die) temperature of an inte-<br>grated circuit device.                                                 |

| TA   | Ambient (environment) temperature existing<br>in the immediate vicinity of an integrated<br>circuit device package. |

| ØJA  | Thermal resistance of an IC package, junction to ambient                                                            |

| -JA  | Thermal resistance of an IC package, junction |

|------|-----------------------------------------------|

|      | to ambient.                                   |

| Ø.IC | Thermal resistance of an IC nackage junction  |

| )TC | Thermal resistance of an IC package | , junction |

|-----|-------------------------------------|------------|

|     | to case                             |            |

|     |                                     |            |

| · · p···· | Linear reet per minute.                 |     |  |  |

|-----------|-----------------------------------------|-----|--|--|

| ₽CA       | Thermal resistance of an IC package, of | ase |  |  |

|           | to ambient                              |     |  |  |

|           | to ambient.                                |

|-----------|--------------------------------------------|

| Miscellar | leous:                                     |

| eg        | Signal generator inputs to a test circuit. |

| TPin      | Test point at input of unit under test.    |

| TPout     | Test point at output of unit under test.   |

| D.U.T.    | Device under test.                         |

| Cin       | Input capacitance.                         |

| Cout      | Output capacitance.                        |

| Zout      | Output impedance.                          |

| *Pn       | The total do nower applied to a device     |

| •PD | The total dc power applied | d to a  | device, | not |

|-----|----------------------------|---------|---------|-----|

|     | including any power de     | livered | from    | the |

|     | device to a load.          |         |         |     |

| AL | • | Load | Resistance. |  |

|----|---|------|-------------|--|

| ЯL | ٠ | Load | Resistance. |  |

| RT Termination | ng (load) resistor. |

|----------------|---------------------|

|----------------|---------------------|

Rp An input pull-down resistor (i.e., connected to the most negative voltage).

P.U.T. Pin under test.

\*JEDEC, EIA, NEMA standard definition

## SECTION II - TECHNICAL DATA

# GENERAL CHARACTERISTICS and SPECIFICATIONS

(See pages 1-6 through 1-8 for definitions of symbols and abbreviations.)

In subsequent sections of this Data Book, the important MECL parameters are identified and characterized, and complete data provided for each of the functions. To make this data as useful as possible, and to avoid a great deal of repetition, the data that is common to all functional blocks in a line is not repeated on each individual sheet. Rather, these common characteristics, as well as the application information that applies to each family, are discussed in this section.

In general, the common characteristics of major importance are:

Maximum Ratings, including both dc and ac characteristics and temperature limits;

Transfer Characteristics, which define logic levels and switching thresholds;

DC Parameters, such as output levels, threshold levels, and forcing functions.

AC Parameters, such as propagation delays, rise and fall times and other time dependent characteristics.

In addition, this section will discuss general layout and design guides that will help the designer in building and testing systems with MECL circuits.

#### LETTER SYMBOLS AND ABBREVIATIONS

Throughout this section, and in the subsequent data sheets, letter symbols and abbreviations will be used in discussing electrical characteristics and specifications. The symbols used in this book, and their definitions, are listed on the preceding pages.

#### **MAXIMUM RATINGS**

The limit parameters beyond which the life of the devices may be impaired are given in Figure 4a. In addition, Table 4b provides certain limits which, if exceeded, will not demage the devices, but could degrade the performance below that of the guaranteed specifications.

#### MECL TRANSFER CURVES

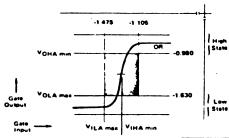

For MECL logic gates, the dual (complementary) outputs must be represented by two transfer curves: one to describe the OR switching action and one to describe the NOR switching action. A typical transfer curve and associated data for all MECL families is shown in Figure 5.

It is not necessary to measure transfer curves at all points of the curves. To guarantee correct operation it is sufficient merely to measure two sets of min/max logic level parameters.

#### FIGURE 4a - LIMITS BEYOND WHICH DEVICE LIFE MAY BE IMPAIRED

| Characteristic                       | Symbol | Unit | MECL 10,000 | M10800 LSI  | MECL III    |

|--------------------------------------|--------|------|-------------|-------------|-------------|

| Characteristic                       | VEE    | Vdc  | -8.0 to 0   | -8.0 to 0   | -8.0 to 0   |

| Supply Voltage (VCC = 0)             | VTT    | Vdc  | -           | -4.0 to 0   | -           |

| Input Voltage (V <sub>CC</sub> = 0)  | Vin    | Vdc  | 0 to VEE    | 0 to VEE    | 0 to VEE    |

| Input Voltage Bus (VCC = 0)          | Vin    | Vdc  | _           | 0 to -2.00  |             |

| Output Source Current<br>Continuous  | lout   | mAdc | 50          | 50          | 40          |

| Output Source Current Surge          | lout   | mAdc | 100         | 100         | _           |

| Storage Temperature                  | Tstg   | °C   | -55 to +150 | -55 to +150 | -55 to +150 |

| Junction Temperature Ceramic Package | T,     | °С   | 165         | 165         | 165③        |

| Junction Temperature Plastic Package | TJ     | °c   | . 150       | -           | 150         |

NOTES: 1) Input voltage limit is V<sub>CC</sub> to -2 volts when bus is used as an input and the output drivers are disabled.

②Maximum T<sub>J</sub> may be exceeded (< 250°C) for short periods of time (< 240 hours) without significant reduction in device life.</p>

<sup>(3)</sup> Except MC1666 - MC1670 which have maximum junction temperatures = 145°C.

| Characteristics                                        | Symbol              | Unit | MECL 10,000                               | M 10800 LSI       | MECL III                 |

|--------------------------------------------------------|---------------------|------|-------------------------------------------|-------------------|--------------------------|

| Operating Temperature Range Commercial ①               | TA                  | °C   | MC: -30 to +85<br>MCM: 0 to 75            | - 30 to +85       | -30 to +85               |

| Operating Temperature Renge MIL ①                      | TA                  | °c   | -56 to +125                               | -                 | -55 to +125<br>(MC1648M) |

| Supply Voltage (VCC = 0)                               | VEE                 | Vdc  | MC: -4.68 to -5.72<br>MCM: -4.94 to -5.46 | -4.68 to -5.72    | -4.68 to -5.72           |

| Supply Voltage (VCC = 0)                               | VTT                 | Vdc  | -                                         | -1.9 to -2.2      | -                        |

| Output Drive Commercial                                | -                   | n    | 50 Ω to −2.0 Vdc                          | 50 Ω to -2.0 Vdc  | 50 Ω to −2.0 Vdc         |

| Output Drive MIL                                       | -                   | n    | 100 Ω to −2.0 Vdc                         | 100 Ω to -2.0 Vdc | -                        |

| Maximum Clock Input Rise<br>and Fall Time (20% to 80%) | t <sub>r</sub> , tş | ns   | -                                         | 10                | 3                        |

NOTES: (1)With airflow > 500 Ifpm.

(2) Functionality only. Data sheet limits are specified for -5.2 V x 0.010 V.

3 10 ns maximum limit for MC1690, MC1697, and MC1699.

(4) Except MC1648 which has an internal output pulldown resistor.

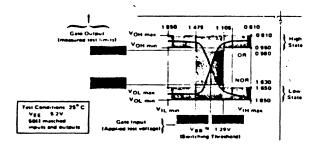

FIGURE 6 - MECL TRANSFER CURVES (MECL 10,000 EXAMPLE) and SPECIFICATION TEST POINTS

The first set is obtained by applying test voltages,  $V_{IL}$  min and  $V_{IH}$  max (sequentially) to the gate inputs, and measuring the OR and NOR output levels to make sure they are between  $V_{OL}$  max and  $V_{OL}$  min, and  $V_{OHmax}$  and  $V_{OHmin}$  specifications.

The second set of logic level parameters relates to the switching thresholds. This set of data is distinguished by an "A" in symbol subscripts. A test voltage, V<sub>1LA</sub> max, is applied to the gate and the NOR and OR outputs are measured to see that they are above the V<sub>OHA</sub> min and below the V<sub>OLA</sub> max levels, respectively. Similer checks are made using the test input voltage V<sub>1HA</sub> min.

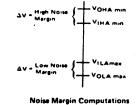

The result of these specifications insures that: a) The switching threshold (\* Vgg) falls within the darkest rectangle; i.e. switching does not begin outside this rectangle;

b) Quiescent logic levels fall in the lightest shaded ranges;

c) Guaranteed noise immunity is met.

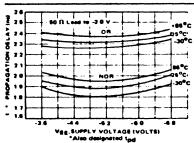

Figure 6 shows the guaranteed MECL 10,000 and MECL III logic levels and switching thresholds over specified temperature ranges. As shown in the Figure 6a Typical Transfer Curves, MECL outputs rise with increasing ambient temperature. All circuits in each family have the same worst-case output level specifications regardless of power dissipation or junction temperature differences to reduce loss of noise margin due to thermal differences.

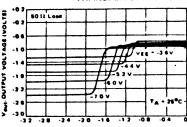

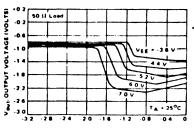

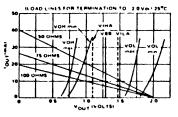

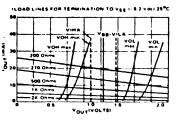

All of these specifications assume -5.2 V power supply operation. Operation at other power-supply voltages is possible, but will result in further transfer curve changes. Transfer characteristic data obtained for a variety of supply voltages are shown in Figure 7. The table accompanying these graphs indicates the change rates of output voltages as a function of power supply voltages.

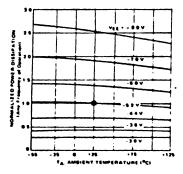

# FIGURE 6a — TYPICAL TRANSFER CHARACTERISTICS AS A FUNCTION OF TEMPERATURE (See tables below for data) OF TEMPERATURE (See tables below for data) OF TEMPERATURE (See tables below for data) OF TEMPERATURE (See tables below for data)

INPUT VOLTAGE (VOLTS)

| Forcing<br>Function | Parameter | -65°c①   | -30°c⊅  | 0°c ©    | 25°C    | 25°C①    | 75°C③    | 85°C®    | 125 <b>℃</b> ① |

|---------------------|-----------|----------|---------|----------|---------|----------|----------|----------|----------------|

|                     |           | MC10500  | MC10100 | MCM10100 | MC10100 | MC10500  | MCM10100 | MC10100  | MC10500        |

|                     |           | MC10600  | MC10200 |          | MC10200 | MC10600  |          | MC10200  | MC10600        |

|                     |           | MCM10500 | MC10800 | 1        | MC10800 | MCM10500 |          | MC10800  | MCM 10500      |

|                     |           | -0 880   | -0.890  | -0.840   | -0.810  | -0.780   | -0.720   | -0.700   | -0 630         |

| VIH max '           | VOHmax    | -1.080   | -1.060  | -1.000   | -0.960  | -0.930   | -0.900   | -0.890   | -0.825         |

|                     | VOHmin    | í        |         | -1.020   | -0.980  | -0.950   | -0.920   | -0.910   | -0.845         |

|                     | VOHAmin   | -1.100   | -1.080  | 1        |         |          | -1.045   | -1.035   | -1.000         |

| VIHAmin .           |           | -1.255   | -1.205  | -1.145   | -1.105  | 1.106    |          | <b>1</b> | -1,400         |

| VILAmex             | l         | -1.510   | -1.500  | -1.490   | -1.475  | -1.475   | -1.450   | -1.440   | 1              |