AGC-1

# **GENERAL INFORMATION**

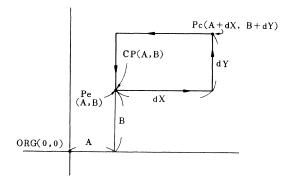

First Edition August 1986 PART NO. 800106

FORCE COMPUTERS Inc./GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted.

Copyright by FORCE Computers®

|  |  | 1                          |

|--|--|----------------------------|

|  |  |                            |

|  |  | 1<br>1<br>1<br>1<br>1<br>1 |

|  |  | ,                          |

|  |  |                            |

|  |  |                            |

|  |  |                            |

|  |  |                            |

#### NOTE

The information in this document has been carefully checked and is believed to be entirely reliable. FORCE COMPUTERS makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors that may appear in this document. FORCE COMPUTERS reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance or design.

FORCE COMPUTERS assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of FORCE COMPUTERS GmbH/Inc.

FORCE COMPUTERS does not convey to the purchaser of the product described herein any license under the patent rights of FORCE COMPUTERS GmbH/Inc. nor the rights of others.

FORCE COMPUTERS Inc. 727 University Avenue Los Gatos, CA 95030 U.S.A.

Phone: (408) 354 34 10

Telex: 172465

FAX : (408) 395 77 18

FORCE COMPUTERS GmbH Daimlerstrasse 9 D-8012 Ottobrunn/Munich West Germany

Phone: (089) 600 91-0 Telex : 524190 forc-d FAX : (089) 609 77 93

FORCE COMPUTERS FRANCE Sarl

ll, rue Casteja 92100 Boulogne France

Phone : (1) 4620 37 37 Telex : 206 304 forc-f

Fax : (1) 4621 35 19

FORCE Computers UK Ltd.

No. 1 Holly Court 3 Tring Road Wendover Buckinghamshire HP22 6NR England

Phone: (0296) 625456

Telex: 838033

Fax : (0296) 624027

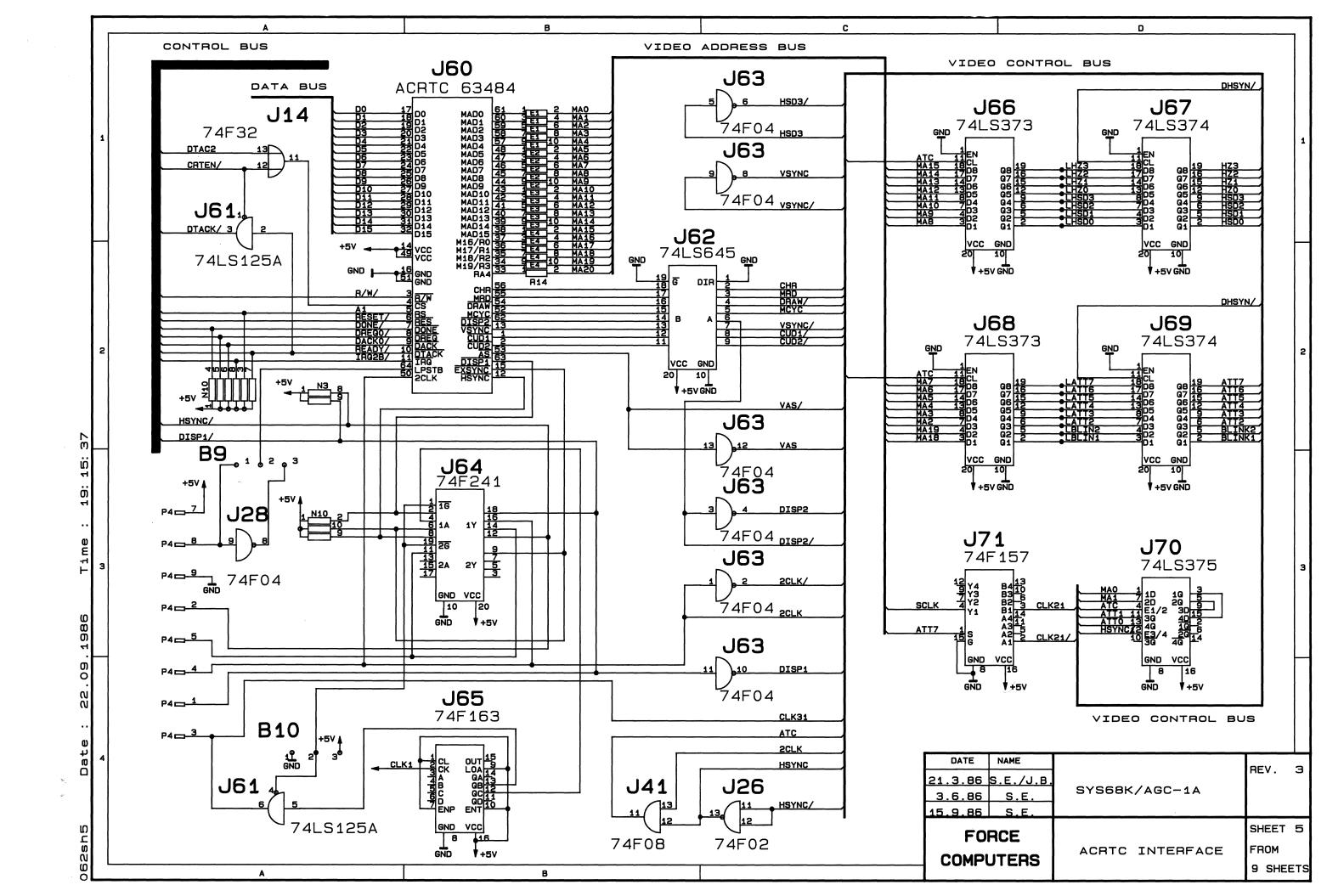

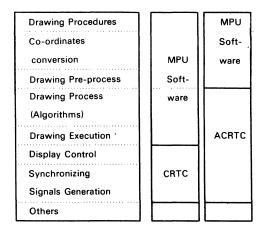

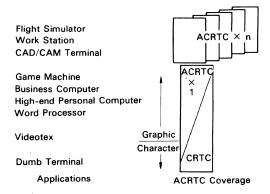

#### 1. GENERAL INFORMATION TO THE 63484 ACRTC

The ACRTC is a high performance graphics-controller, compatible to the 68000 family of microprocessors. The ACRTC concept is to incorporate major functionality with effective graphic commands.

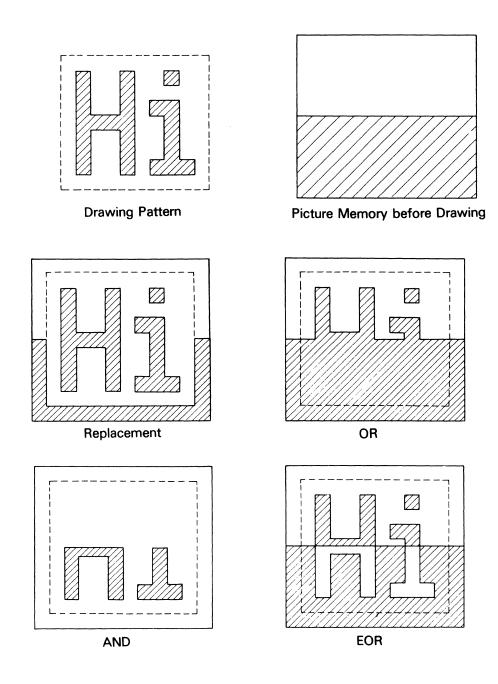

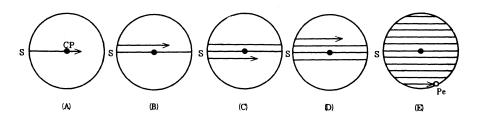

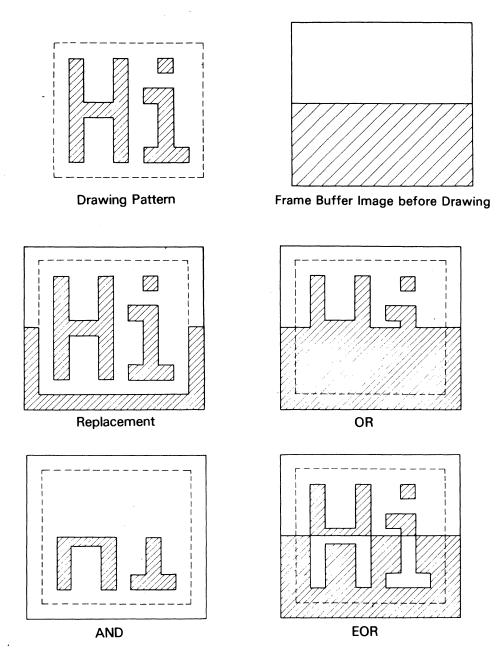

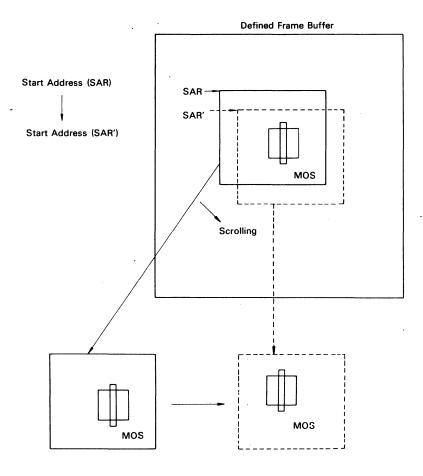

High level command language increases performance and reduces software development costs. In this way, the ACRTC converts logical x - y coordinates to physical frame buffer addresses. It supports 38 commands, including LINE, RECTANGLE, POLYLINE, POLYGON, CIRCLE, ELLIPSE, ARC, ELLIPSE ARC, FILLED RECTANGLE, PAINT, PATTERN and COPY. An on-chip 32byte pattern RAM can be used for powerful graphic environments. Conditional drawing functions are useful for drawing patterns, colour mixing and software windowing. The drawing area control supports clipping and hitting. The ACRTC is able to control four hardware windows, zooming and smooth scrolling in both vertical and horizontal directions. The capability of displaying up to 256 colours and the maximum drawing speed of 2 million Pixel per second in monochrome and colour applications allows high performance CAD terminals to be used.

#### Features of the 63484 ACRTC:

- Up to 4096 by 4096 bit map graphic display and/or 256 lines by 256 characters by 32 rasters character display.

- Separate bit map graphic (2Mbyte) and character (128Kbyte) address spaces with combined graphic/character display.

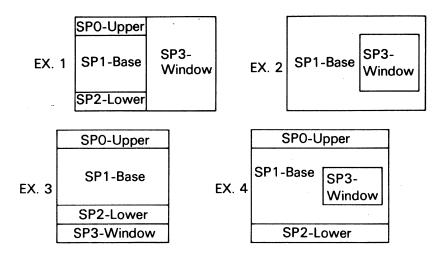

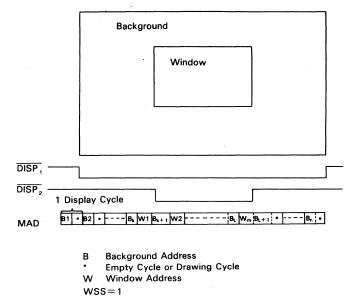

- Three horizontal split screens and one window screen.

Size and position fully programmable.

- Independent horizontal and vertical smooth scroll for each screen.

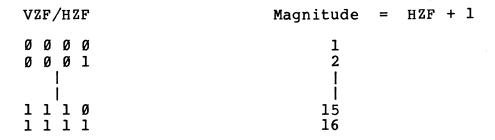

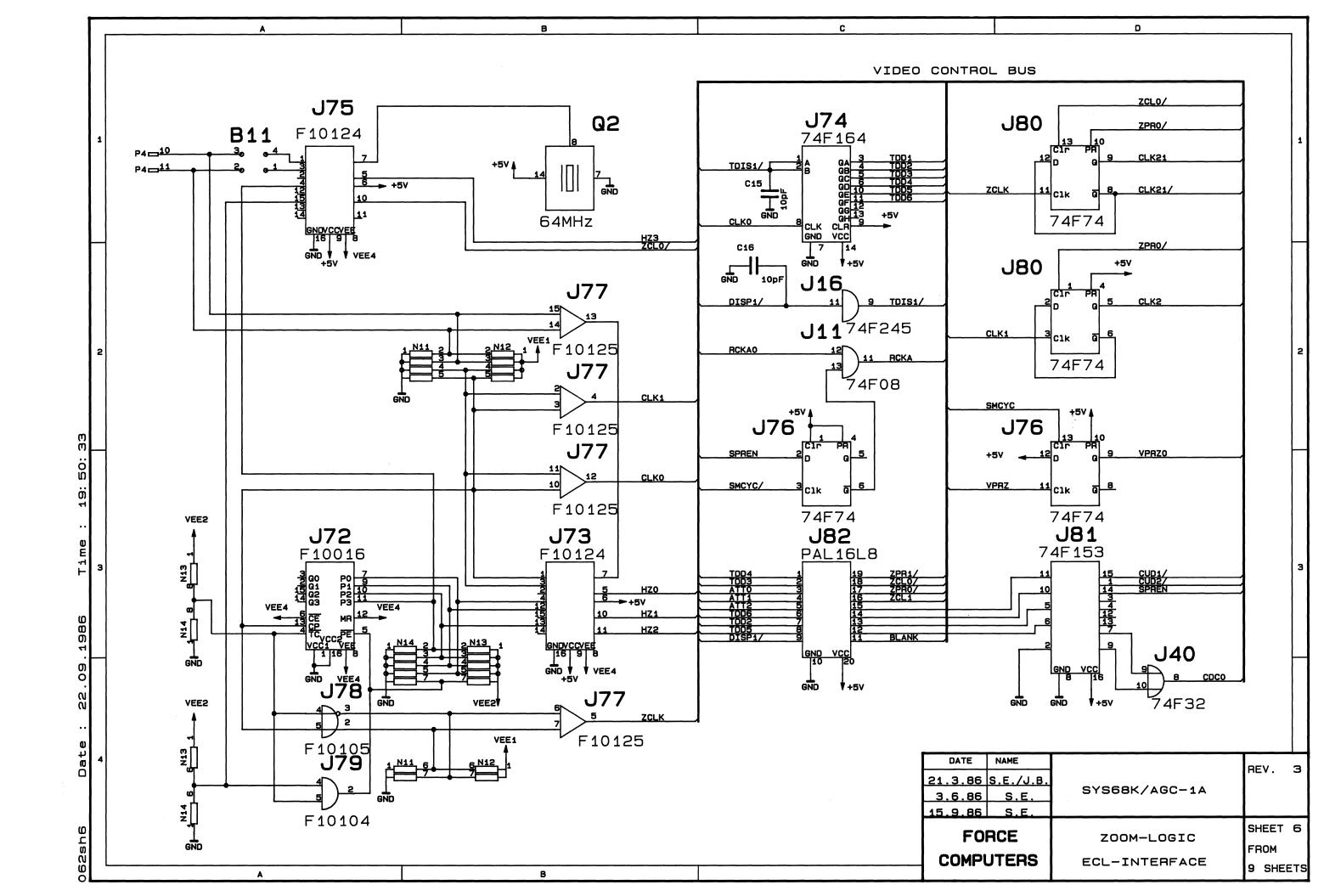

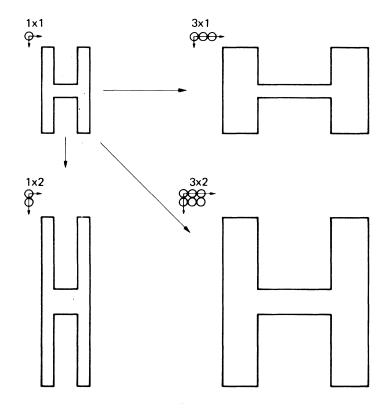

- 1 to 16 zoom magnitude independent x and y factors.

- Logical pixel specification as 1, 2, 4, 8 or 16 bits for monochrome, gray scale and colour displays.

- Programmable address increment supports frame buffer memory width up to 128 bits for video bit rates greater than 500 MHz.

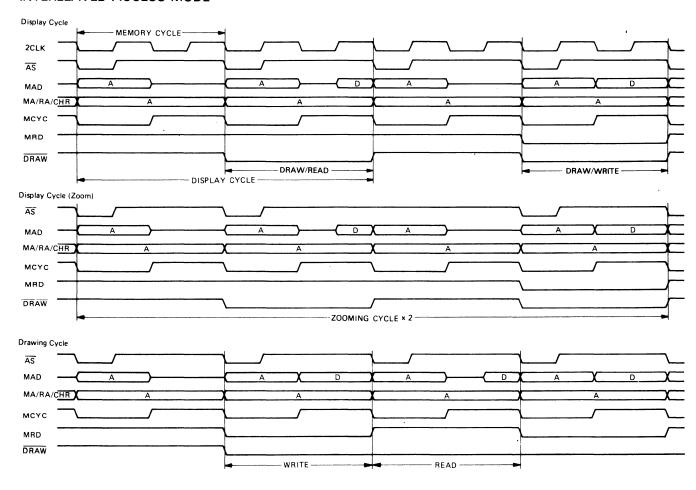

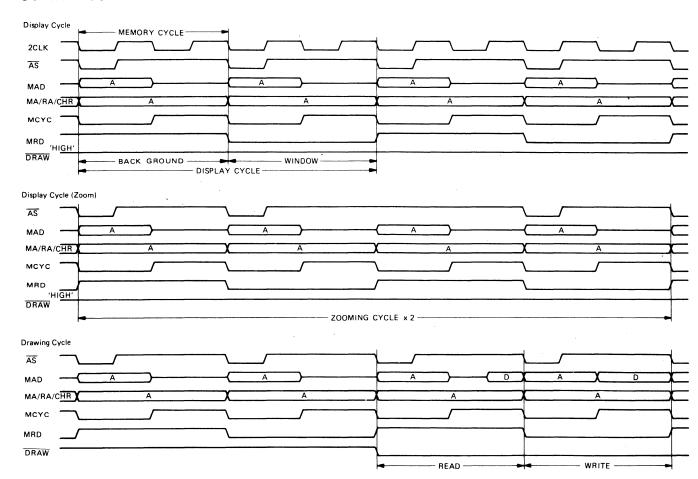

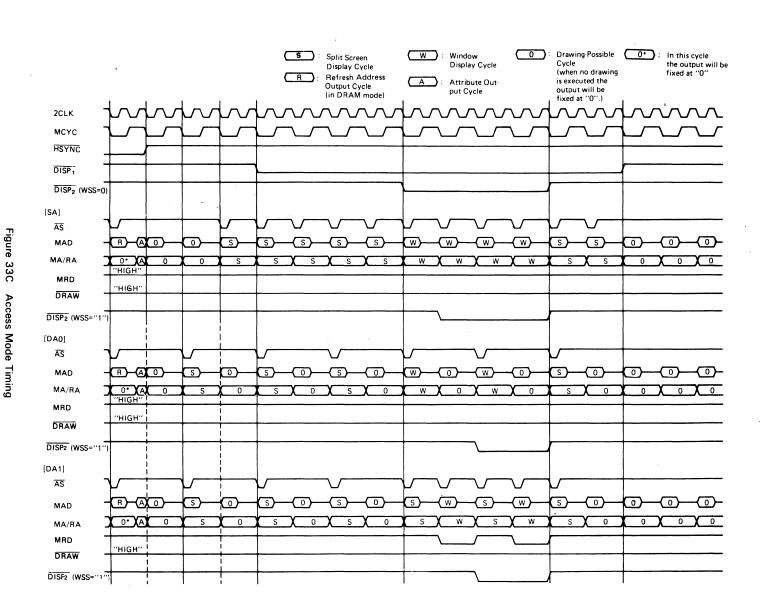

- Unique interleaved access mode for "flashless" displays.

- ACRTC provides dynamic RAM refresh.

- Asynchronous bus interface, optimised for the 68000 MPU family and the 68450 DMAC (16bit data bus).

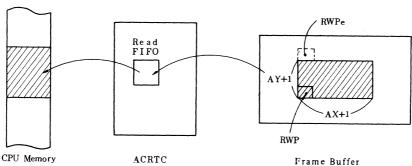

- Separate on-chip 16byte READ and WRITE FIFOs.

- Maskable interrupts including FIFO status.

- Full programmability of CRT timing signals.

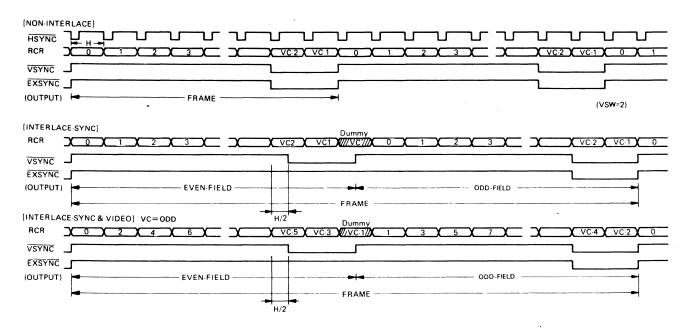

- Three raster scan modes.

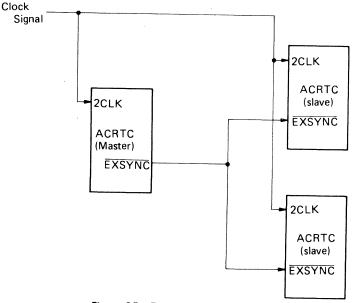

- Master or Slave synchronization to multiple ACRTCs or other video generating devices.

- Programmable cursor and display timing skew.

- Eight user definable video attributes.

- Light pen detection.

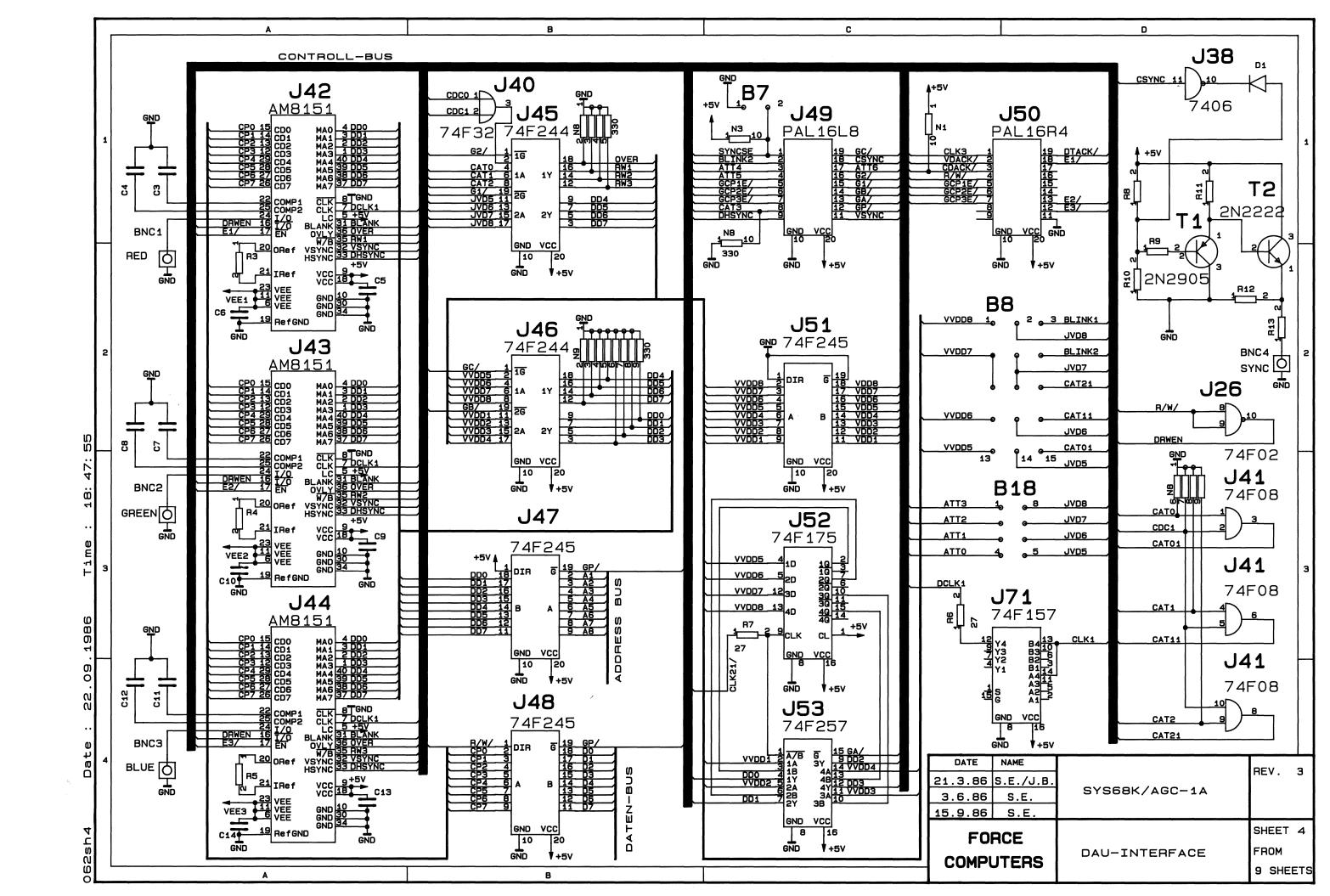

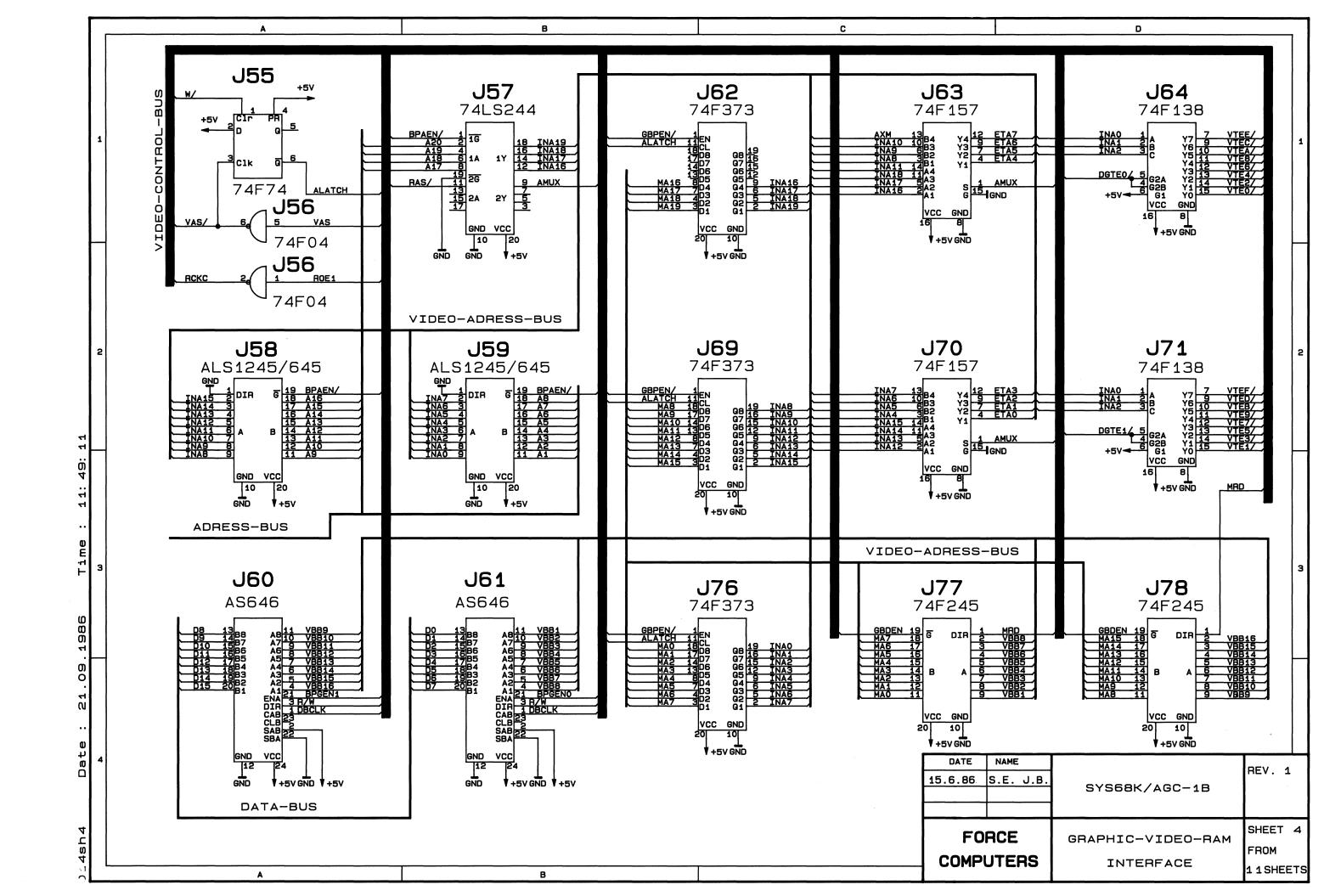

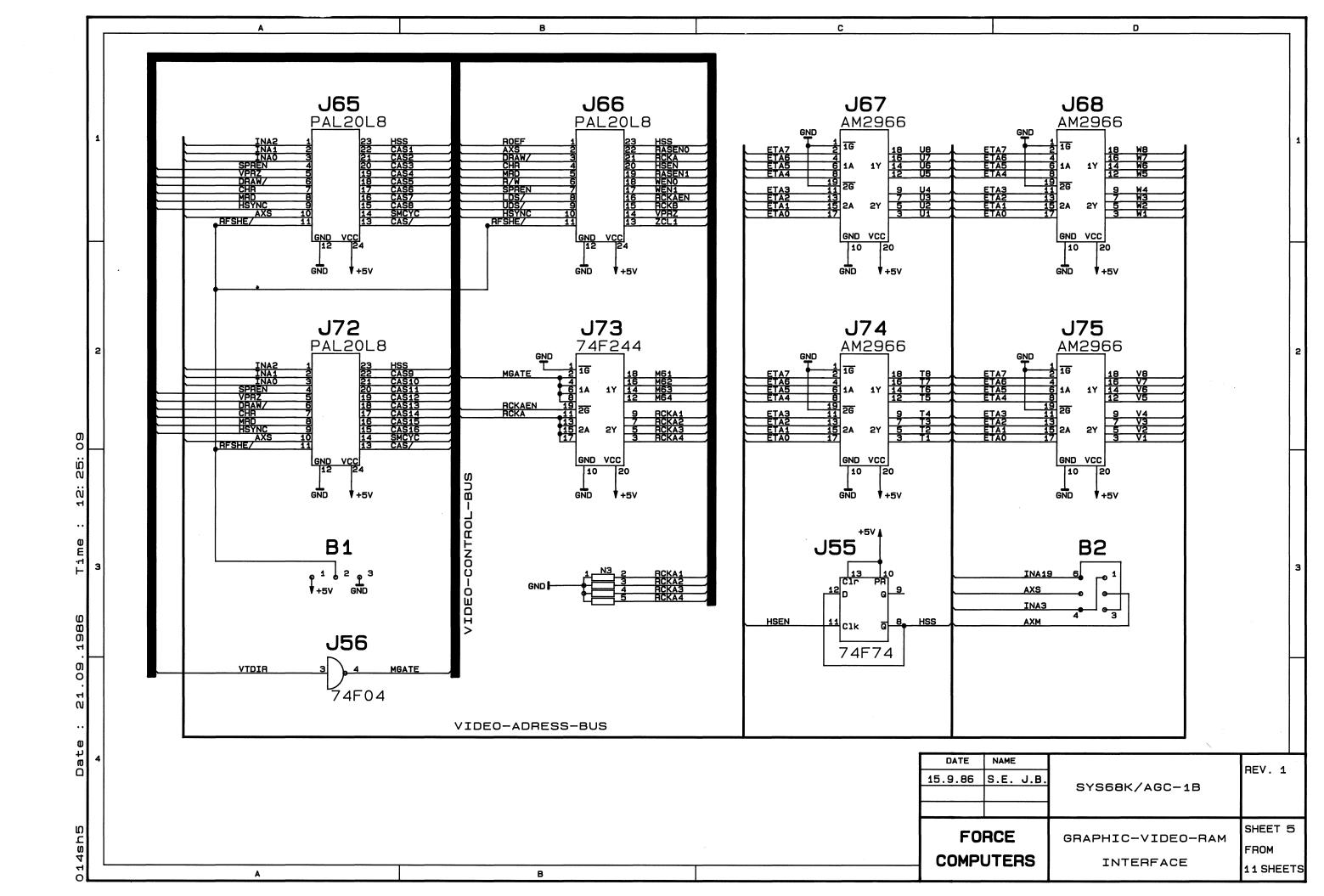

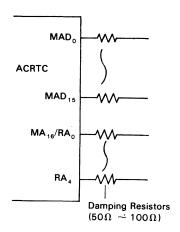

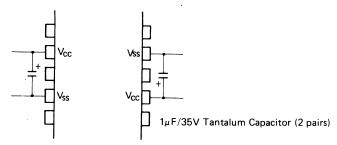

#### 2. IMPLEMENTATION OF THE 63484 ACRTC ON THE AGC-1

The AGC-1 is a highly integrated graphic-system on two double-euroboards, based on the 63484 ACRTC. With the optional SYS68K/AGC-1X board, it offers two bus interfaces and allows the board set to be used in single-processor as well as in high end multi-processor applications.

The board has a jumper selectable access address within the 16Mbyte address range. Also the VMEbus or VMXbus access is selectable. The on-board video RAM of 2Mbyte is dual ported and in this way directly accessible by either the processor or a DMA Controller for high speed display manipulation.

The Pixel clock of 64MHz offers resolutions up to 1024 X 800 non-interlaced with 4 bits per pixel. With the on-board colour palette, the user has the choice of up to 256 colours out of 16 million. With the implementation of the dual access mode, the ACRTC display and drawing accesses are interleaved and so the ACRTC reaches the maximum drawing speed without a "flashing" display. The complex attribute logic offers a great variety of display modes, e.g. blinking, inverse video, conditional blinking.

The AGC-lX board adds powerful character overlay with a separate character and attribute RAM, a software loadable character generator, the 68450 DMA Controller, which is used for VMEbus data transfers, two serial I/O interfaces for printer, mouse or digitizer and the VMXbus interface.

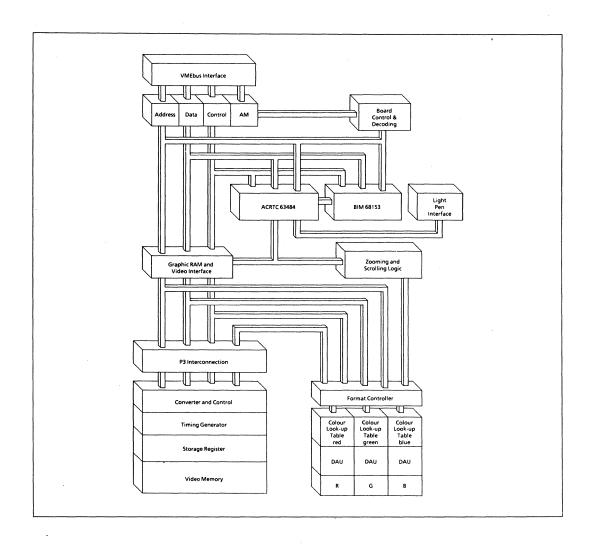

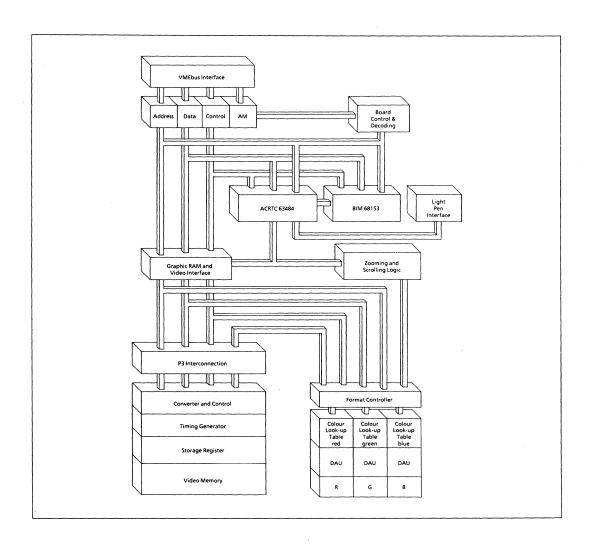

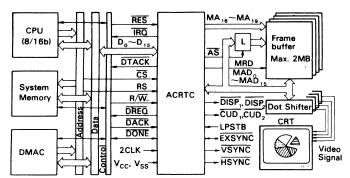

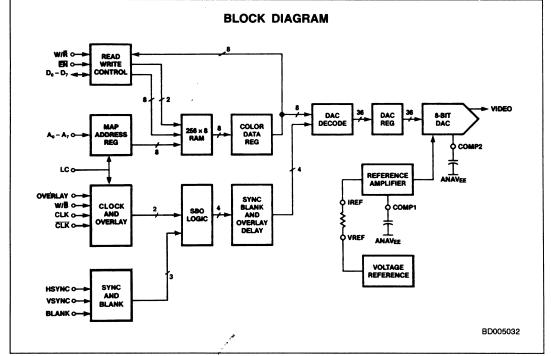

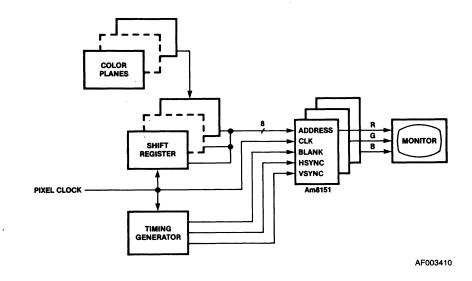

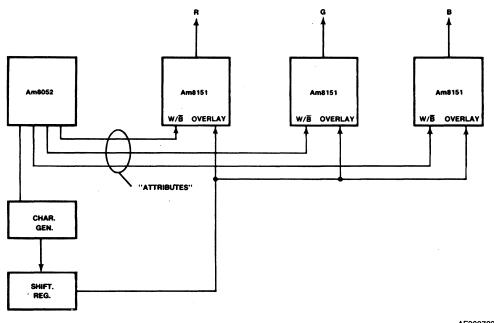

Figure 2-1: Block Diagram of the SYS68K/AGC-1

#### Features of the SYS68K/AGC-1:

- 63484 ACRTC with a clock frequency of 8MHz.

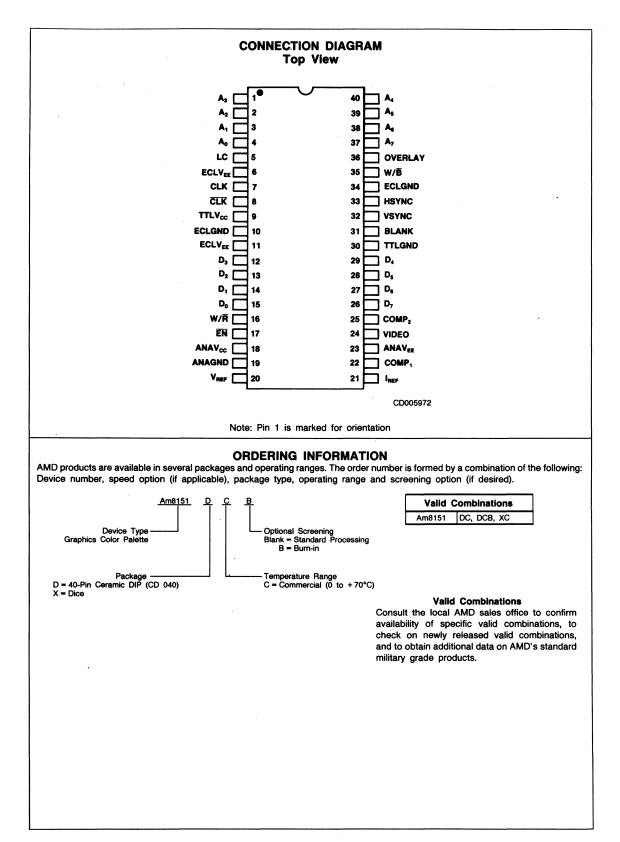

- 3 x AM8151 graphic colour palette with 16/256 entries.

- 68153 Bus Interrupter Module for all local interrupts.

- 2Mbyte of video RAM directly accessible from the VMEbus

- R-, G-, B- and composite SYNC output.

- External synchronization input/output for other AGCs.

- Light pen interface.

- Fully buffered local address, data and control bus.

- VME/P1014 interface (16 bit).

- Software selectable interrupt request level and programmable interrupt vector.

The following table shows the general memory lay-out of the SYS68K/AGC-1:

The board start address (BBA) is jumper selectable in 256Kbyte steps.

Table 2-1: The Address Map

| Start Address | End Address                | Memory Area                           |

|---------------|----------------------------|---------------------------------------|

| ВВА           | BBA + \$33FFF              | Occupied for the SYS68K/AGC-1X boards |

| BBA + \$34000 | BBA + \$35FFF              | BIM 68153<br>                         |

| BBA + \$36000 | BBA + \$37FFF              | GCP l red                             |

| BBA + \$38000 | BBA + \$39FFF              | GCP 2 green                           |

| BBA + \$3A000 | BBA + \$3BFFF              | GCP 3 blue                            |

| BBA + \$3C000 | BBA + \$3FFFF<br>(\$3DFFF) | ACRTC 63484                           |

| BBA + \$3E000 | BBA + \$3FFFF              | Interrupt-Register<br>  VMX-Option    |

| BBA + \$40000 | BBA + \$23FFFF             | Video-RAM                             |

The Board Base Address is set by default during manufacturing to C00000 (Start Address) / \$E3FFFF (End Address).

# **INSTALLATION**

FORCE COMPUTERS Inc./GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted.

Copyright by FORCE Computers®

Please read the complete installation procedure before the board is installed in a VMEbus environment, to avoid malfunctions and damage to components.

## TABLE OF CONTENTS

| 1. | GENE | RAL OVERVIEW                  | 1-1 |

|----|------|-------------------------------|-----|

|    | 1.1  | The Function Switch Positions | 1-2 |

|    | 1.2  | Connection of the RGB Monitor | 1-4 |

| 2. | INST | ALLATION IN THE RACK          | 2-1 |

|    | 2.1  | Power On                      | 2-2 |

|  | 1.4 |  |  |

|--|-----|--|--|

|  |     |  |  |

|  |     |  |  |

|  |     |  |  |

|  |     |  |  |

|  |     |  |  |

|  |     |  |  |

|  |     |  |  |

#### 1. GENERAL OVERVIEW

This manual only describes the function of the SYS68K/AGC-lA and SYS68K/AGC-lB boards. For all other functions of the SYS68K/AGC-lX board, please refer to the SYS68K/AGC-lX User's Manual.

Easy installation of the AGC-1 board set is provided because of the default jumper settings. It may be necessary to modify the board base address (BBA) to adapt the board to the various applications.

Both the main board and the slave board are screwed together and have the correct measurements to be plugged into a standard VMEbus backplane. Only the AGC-lA board contains the VMEbus interface.

#### 1.1 The Function Switch Positions

The board contains 2 function switches listed from the top to the bottom:

VME/VMX

RUN/HALT

The two positions of the switches are defined as "up" and "down".

The VMEbus interface will be enabled if all function switches are set to the position "down" (for first installation).

Please toggle each of the switches sometime before installing the board in the rack to detect any damage incurred during transportation.

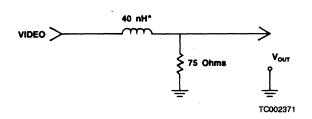

#### 1.2. Connection of the RGB-Monitor

The terminal has to be connected to the BNC connectors on the main board (right board of the package).

The RGB outputs are compatible to the RS343 standard for connection with RGB monitors. The composite SYNC signal is mixed on all colour outputs so that mostly there is no need for an extra SYNC connection.

Monitors with separate SYNC input must be connected to the SYNC output of the AGC-1.

The SYNC output can be configured to have a positive or negative SYNC signal. This is specified by the jumper settings of B7 (SYNCSEL).

For jumper settings, please refer to section 4.11.4 in the Hardware User's Manual (Register 3).

#### 2. Installation in the Rack

The main (AGC-lA) and the slave (AGC-lB) boards are screwed together and can immediately be mounted into a VME rack.

#### Caution

- A) Switch off power before installing the board to avoid electrical damage to the components.

- b) The main board contains a special ejector (the handles).

The boards have to be plugged in and the screws of the front panel must be tightened to guarantee proper installation.

#### 2.1. Power On

If the board is correctly installed, the switches are in the correct positions, the monitor is connected, the power for the VMEbus rack can be switched on.

If everything has worked, the green RUN LED and the yellow VME LED must turn on.

Now the AGC-1 is accessible from an VMEbus-MASTER under the selected board base address (\$C00000 is set by default during manufacturing.

For initialisation of the ACRTC, please refer to section 4.12 in the Hardware User's Manual (Register 3).

# HARDWARE USER'S MANUAL

FORCE COMPUTERS Inc./GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted.

Copyright by FORCE Computers®

|  |  | 1                                       |

|--|--|-----------------------------------------|

|  |  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|  |  |                                         |

|  |  |                                         |

|  |  |                                         |

|  |  |                                         |

|  |  |                                         |

# $\underline{\mathbf{T}} \ \underline{\mathbf{A}} \ \underline{\mathbf{B}} \ \underline{\mathbf{L}} \ \underline{\mathbf{E}} \qquad \underline{\mathbf{O}} \ \underline{\mathbf{F}} \qquad \underline{\mathbf{C}} \ \underline{\mathbf{O}} \ \underline{\mathbf{N}} \ \underline{\mathbf{T}} \ \underline{\mathbf{E}} \ \underline{\mathbf{N}} \ \underline{\mathbf{T}} \ \underline{\mathbf{S}}$

| 1. | GENERA        | L INFORM         | ATION1-1                                    |

|----|---------------|------------------|---------------------------------------------|

| 2. | GENERA        | L OPERAT         | ION2-1                                      |

| 3. | <b>THE 63</b> | 484 ACRT         | C DESCRIPTION3-1                            |

| 4. | ACCESS        | TO THE           | SYS68K/AGC-14-1                             |

|    | 4.1           |                  | ase Address Selection4-1                    |

|    |               |                  | Standard Memmory Space4-1                   |

|    |               |                  | Short I/O Space4-9                          |

|    | 4.2           |                  | ize Selection4-14                           |

|    | 4.3           |                  | Modifier Selection4-21                      |

|    | 4.4           | Function         | nal Groups on the SYS68K/AGC-14-25          |

|    | 4.5           |                  | to the Devices on the SYS68K/AGC-14-26      |

|    | 4.6           | Address          | ing the Colour Look-up Tables4-27           |

|    |               |                  | Colour Switch Mode4-31                      |

|    |               |                  | Blink Switch Mode4-35                       |

|    | 4.7           |                  | ing the BIM 681534-38                       |

|    |               |                  | Interrupt Structure of the SYS68k/AGC-14-38 |

|    | 4.8           | 4.7.2            | Programming the BIM on the SYS68K/AGC-14-43 |

|    | 4.8           |                  | ing the Video Memory4-44                    |

|    | 4.9           | 4.9.1            | ing the ACRTC 634844-53                     |

|    |               | 4.9.1            | Address Register4-59 Status Register4-60    |

|    |               | 4.9.3            | FIFO Entry4-62                              |

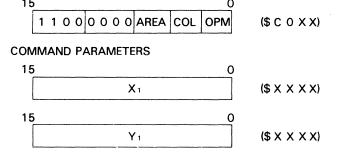

|    |               | 4.9.4            | Command Control Register4-63                |

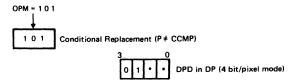

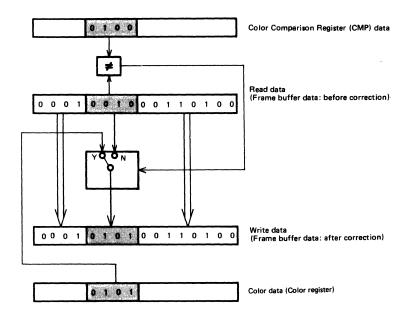

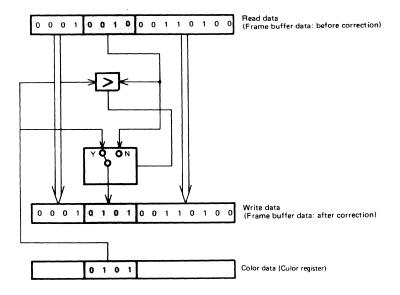

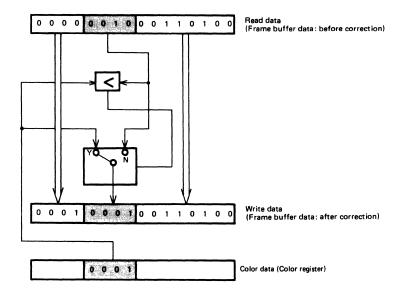

|    |               | 4.9.5            | Operation Mode Register4-66                 |

|    |               | 4.9.6            | Display Control Register4-70                |

|    |               | 4.9.7            | Raster Count Register4-75                   |

| *  |               | 4.9.8            | Horizontal Sync Register4-76                |

|    |               | 4.9.9            | Horizontal Display Register4-78             |

|    |               |                  | Horizontal Window Display Register4-78      |

|    |               | 4.9.10           | Vertical Sync Register4-80                  |

|    |               | 4.9.11           | Vertical Display Register4-81               |

|    |               | 4.9.12           | Vertical Window Display Register4-83        |

|    |               | 4.9.13           | Split Screen Width Register4-85             |

|    |               | 4.9.14           | Blink Control Register4-87                  |

|    |               | 4.9.15           | Memory Width Register4-88                   |

|    |               | 4.9.16<br>4.9.17 | Start Address Register4-89                  |

|    |               |                  | Zoom Factor Register                        |

|    |               | 4.9.18 Drawing   | Light Pen Address Register4-92              |

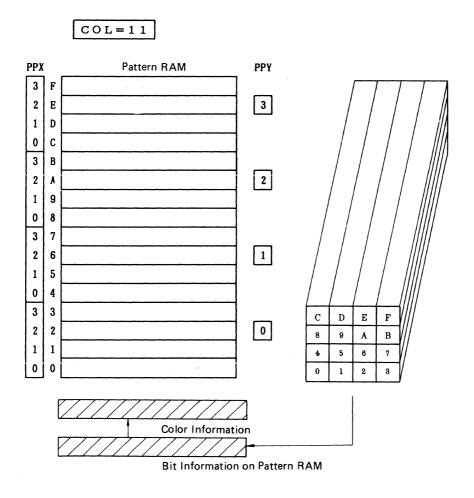

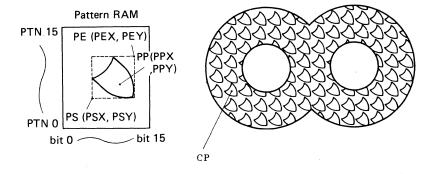

|    |               | 4.10.1           | Control Register4-93 Pattern RAM4-95        |

|    |               | 4.10.1           | Colour Ø Register4-96                       |

|    |               | 4.10.3           | Colour 1 Register4-96                       |

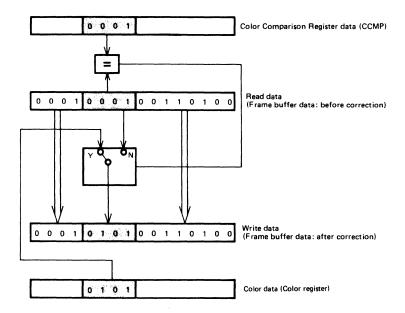

|    |               | 4.10.4           | Colour Comparison Register4-97              |

|    |               | 4.10.5           | Edge Colour Register4-97                    |

|    |               | 4.10.6           | Mask Register4-98                           |

|    |               | 4.10.7           | Pattern RAM Control Register4-99            |

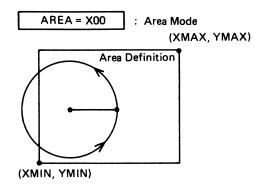

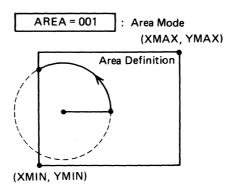

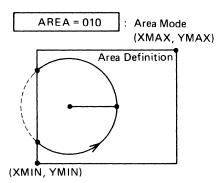

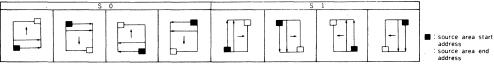

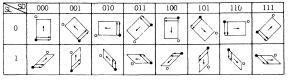

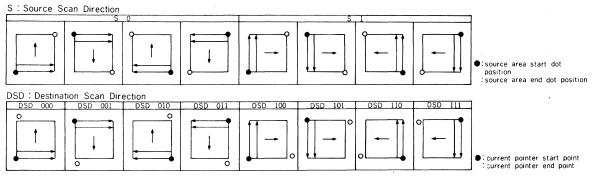

|    |               | 4.10.8           | Area Definition Register4-101               |

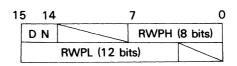

|    |               | 4.10.9           | Read-Write Pointer4-102                     |

|    |               | 4.10.10          | Drawing Pointer4-103                        |

|    |               | 4.10.11          | Current Ponter4-104                         |

## $\underline{T} \ \underline{A} \ \underline{B} \ \underline{L} \ \underline{E} \qquad \underline{O} \ \underline{F} \qquad \underline{C} \ \underline{O} \ \underline{N} \ \underline{T} \ \underline{E} \ \underline{N} \ \underline{T} \ \underline{S} \qquad \underline{Cont'd}$

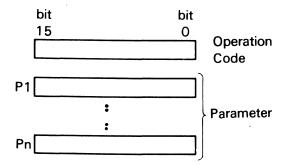

| 5. | COMMA | ND OVERVIEW5-1                   |

|----|-------|----------------------------------|

|    | 5.1   | Register Access Commands5-2      |

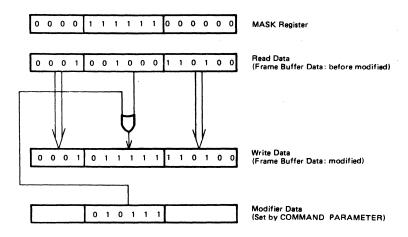

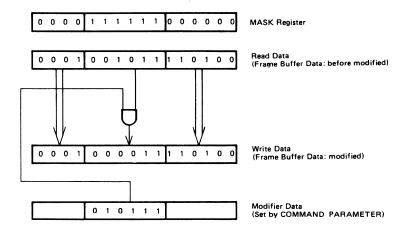

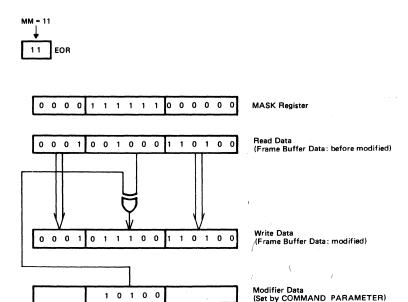

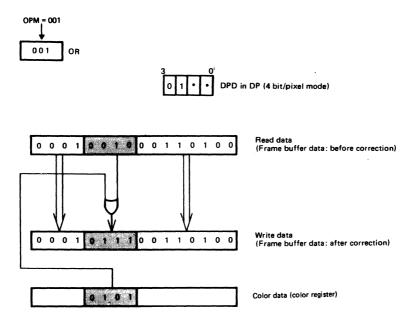

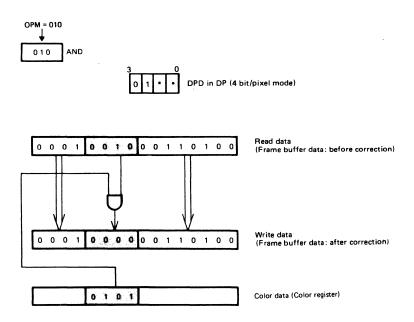

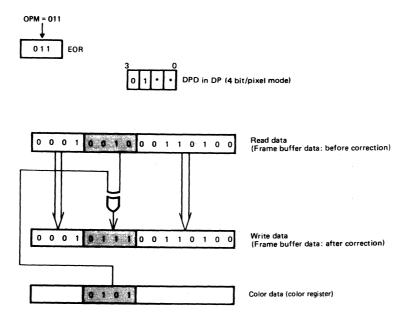

|    | 5.2   | Data Transfer Commands5-3        |

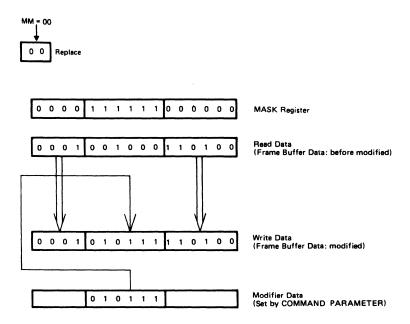

|    | 5.3   | Modify Mode5-4                   |

|    | 5.4   | Graphic Drawing Commands5-5      |

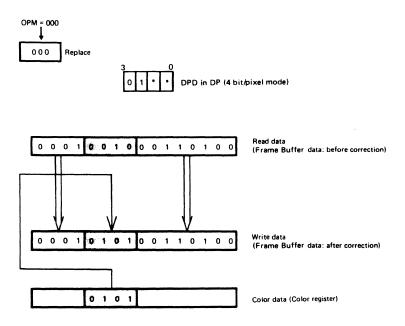

|    | 5.5   | Operation Mode5-7                |

|    | 5.6   | Colour Mode5-8                   |

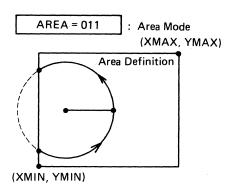

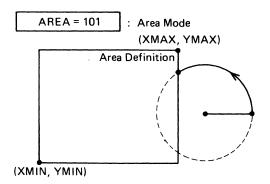

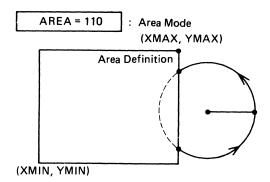

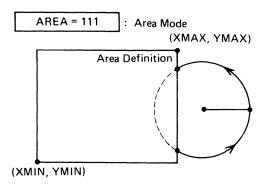

|    | 5.7   | Area Mode5-9                     |

|    |       |                                  |

| 6. | MISCE | LLANEOUS6-1                      |

|    | 6.1   | Miscellaneous Jumper Settings6-1 |

|    | 6.2   | Light Pen Interface6-4           |

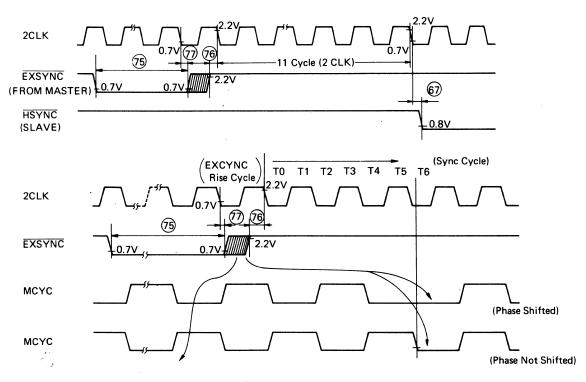

|    | 6.3   | External Synchronization6-6      |

|    | 6.4   | Display Monitor Interface6-8     |

| _  |       |                                  |

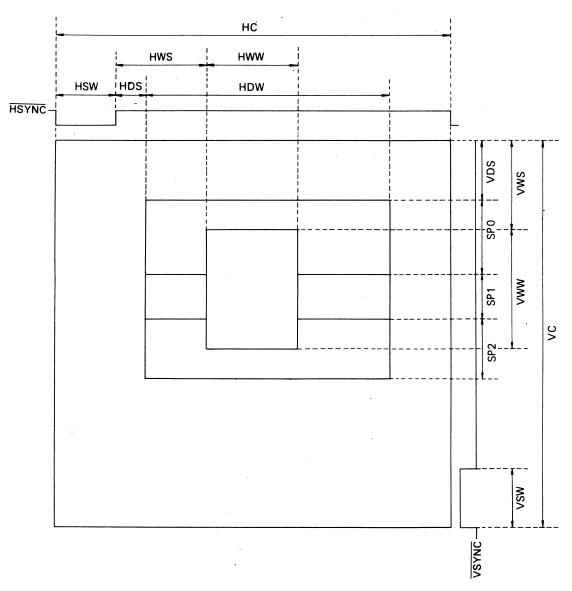

| 7. | CALCU | LATING THE SCREEN PARAMETERS7-1  |

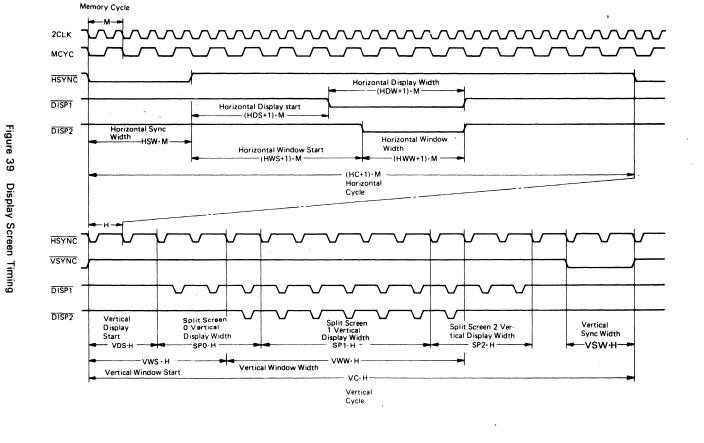

|    | 7.1   | Horizontal Timing7-4             |

|    | 7.2   | Vertical Timing7-7               |

|    | 7.3   | Display Control RAM7-9           |

|    | 7.4   | Control Registers7-12            |

### $\underline{L} \ \underline{I} \ \underline{S} \ \underline{T} \qquad \underline{O} \ \underline{F} \qquad \underline{F} \ \underline{I} \ \underline{G} \ \underline{U} \ \underline{R} \ \underline{E} \ \underline{S}$

1-1:

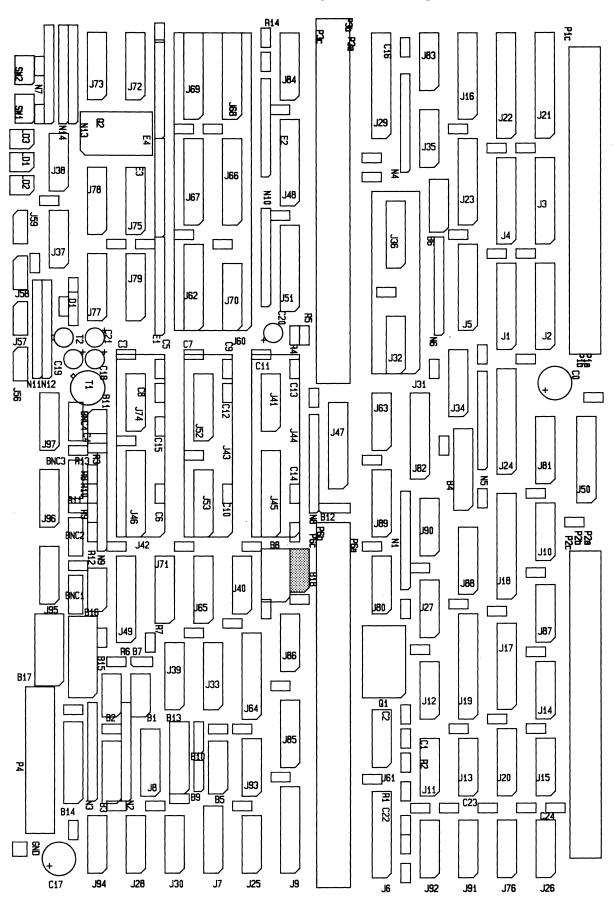

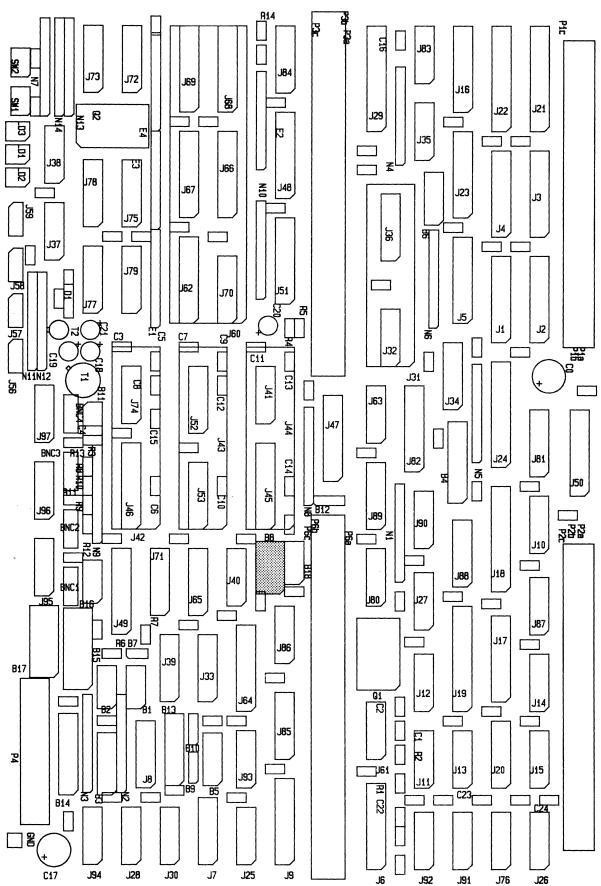

Photo of the SYS68K/AGC-1A Board......1-2

| 2-1:                                                                                                                          | Block Diagram of the SYS68K/AGC-12            | 2-2                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------|

| 4-1:<br>4-2:<br>4-3:<br>4-4:<br>4-5:<br>4-6:<br>4-7:<br>4-8:<br>4-9:<br>4-10:<br>4-11:<br>4-12:<br>4-13:                      | Jumper Location Diagram of Address Selection  | 1-11<br>1-15<br>1-22<br>1-29<br>1-36<br>1-39<br>1-45<br>1-45<br>1-49                        |

| 6-1:<br>6-2:<br>6-3:                                                                                                          | Jumper Location Diagram of RAS/CAS Generation | 5-7                                                                                         |

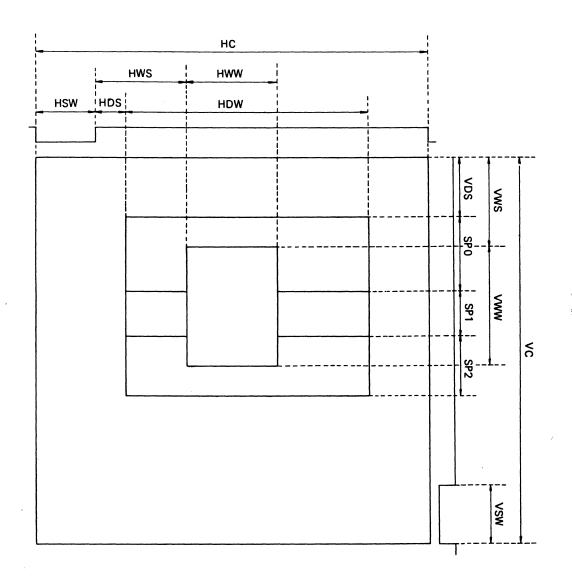

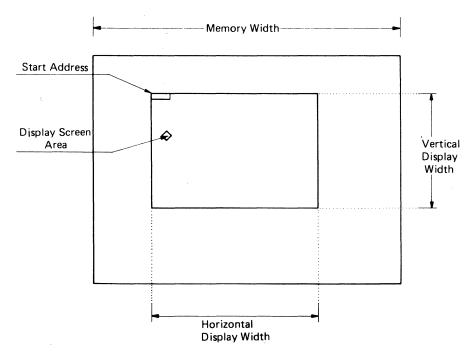

| 7-1:                                                                                                                          | Display Screen Specification                  | 7-3                                                                                         |

|                                                                                                                               | LIST OF TABLES                                |                                                                                             |

| 4-1:<br>4-2:<br>4-3:<br>4-4:<br>4-5:<br>4-6:<br>4-7:<br>4-8:<br>4-10:<br>4-11:<br>4-13A:<br>4-13B:<br>4-14:<br>4-15:<br>4-17: | Jumper Settings for Board Base Address        | l-8<br>l-12<br>l-13<br>l-19<br>l-23<br>l-37<br>l-42<br>l-42<br>l-48<br>l-48<br>l-52<br>l-54 |

| 5-1:                                                                                                                          | Graphic Drawing Commands5                     | 5-6                                                                                         |

| 6-1:<br>6-2:                                                                                                                  | Jumper Settings for RAS/CAS Generation        | 5-3<br>5-5                                                                                  |

#### 1. GENERAL INFORMATION

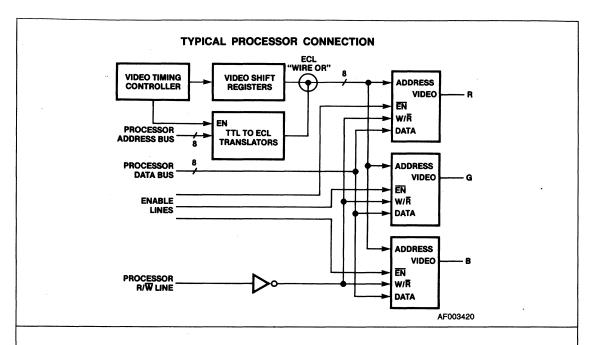

This high performance VMEbus-based GRAPHIC board combines the powerful graphic processor, the 63484 ACRTC with 2 Mbyte Video-RAM, 3 digital-to-analogue Converters and 3 colour-look-up tables with 256 entries each.

The implementation of the so called DUAL ACCESS MODE (see description of the 63484 ACRTC) allows Video-RAM accesses during display without `flashing' display and so speeds up drawing operations.

The also built-in direct Video-RAM access via the VMEbus during display supports very fast updating or loading of the FRAME BUFFER.

Two graphic bit modes in conjunction with the colour-look-up tables make it possible to simultaneously display up to 256 colours out of a total range of 16 million.

A sophisticated attribute logic offers a wide variety of display manipulation, such as blinking of specified colours or objects and switching the look-up tables. Also supported is a smooth scroll in horizontal and vertical directions and independent zooming in both directions.

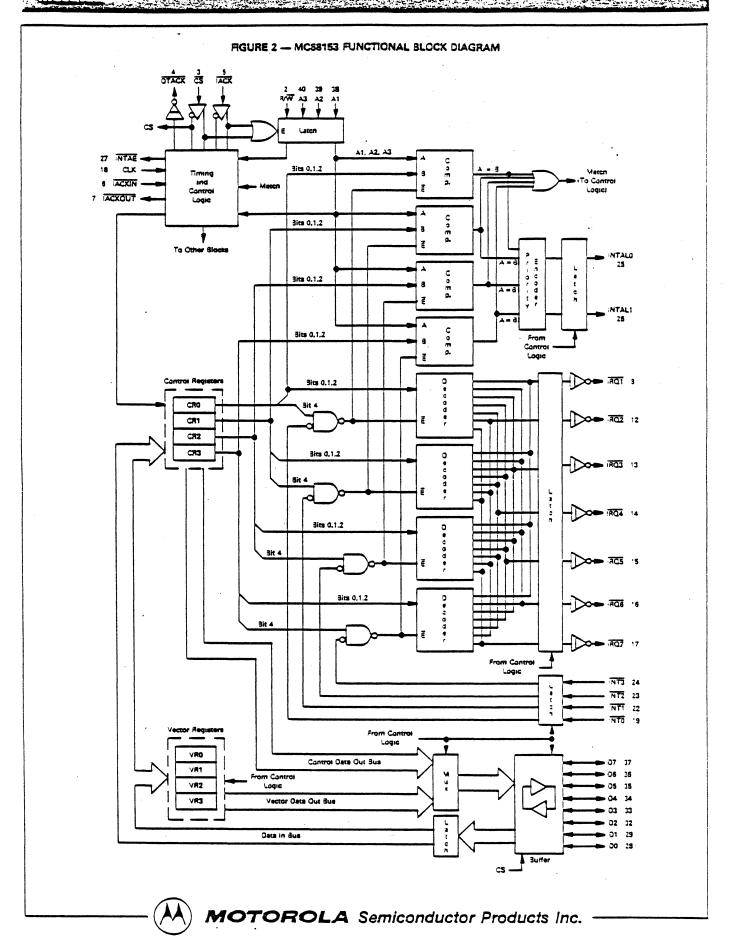

The local control, consisting of a Bus Interrupter Modul (BIM) offers software control for programming the ACRTC and updating the Frame Buffer or the colour-look-up tables during vertical retrace period.

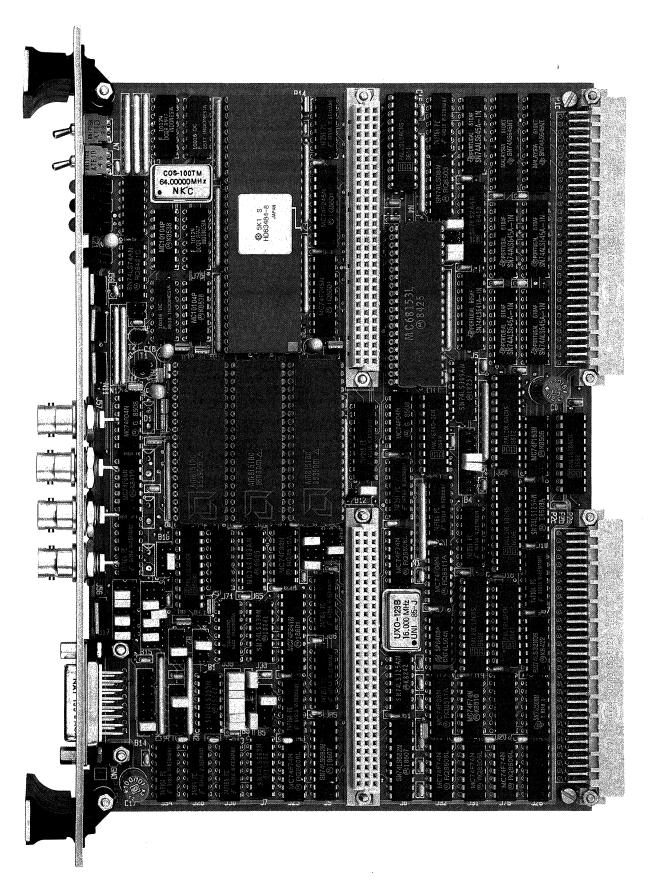

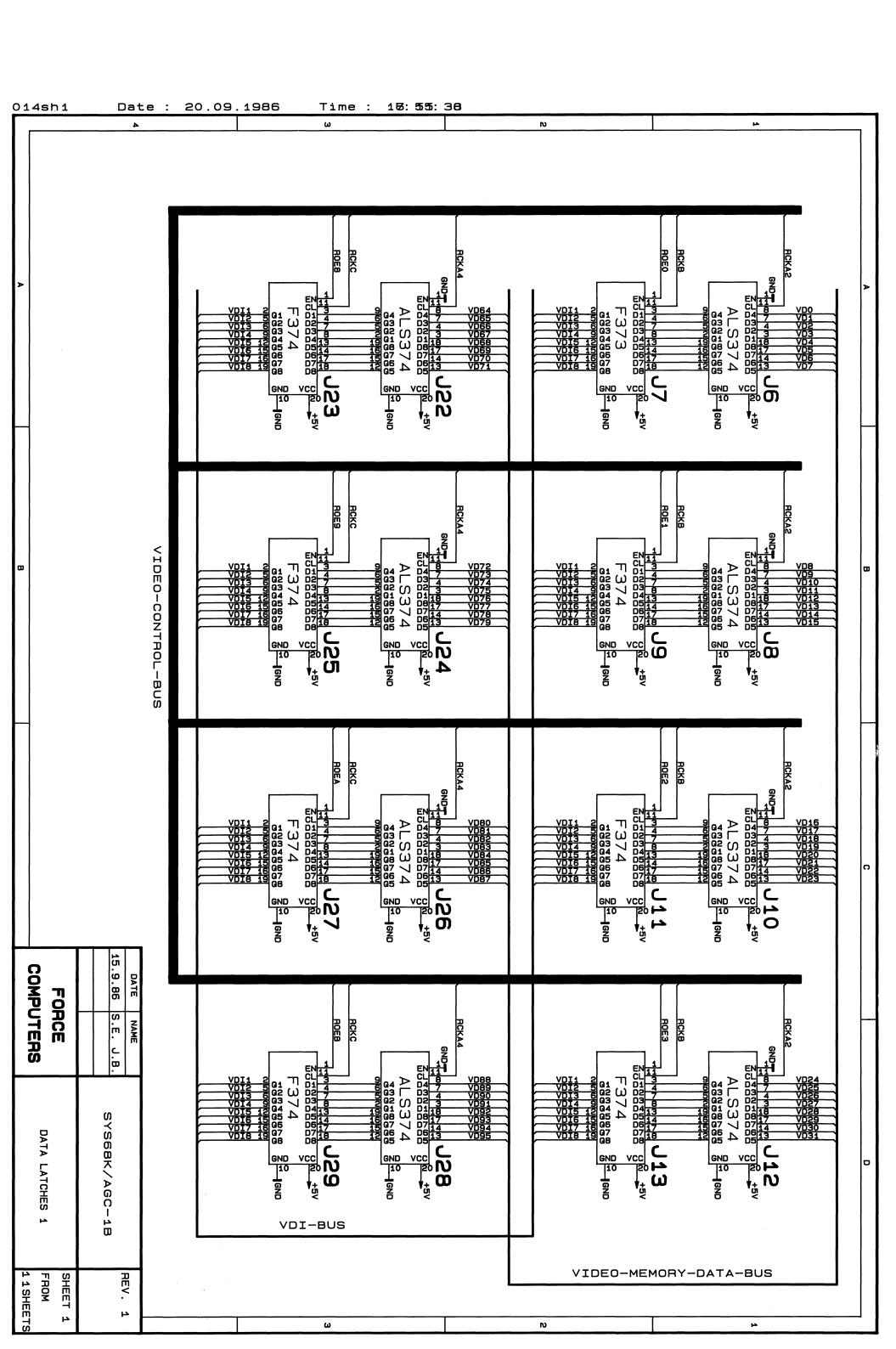

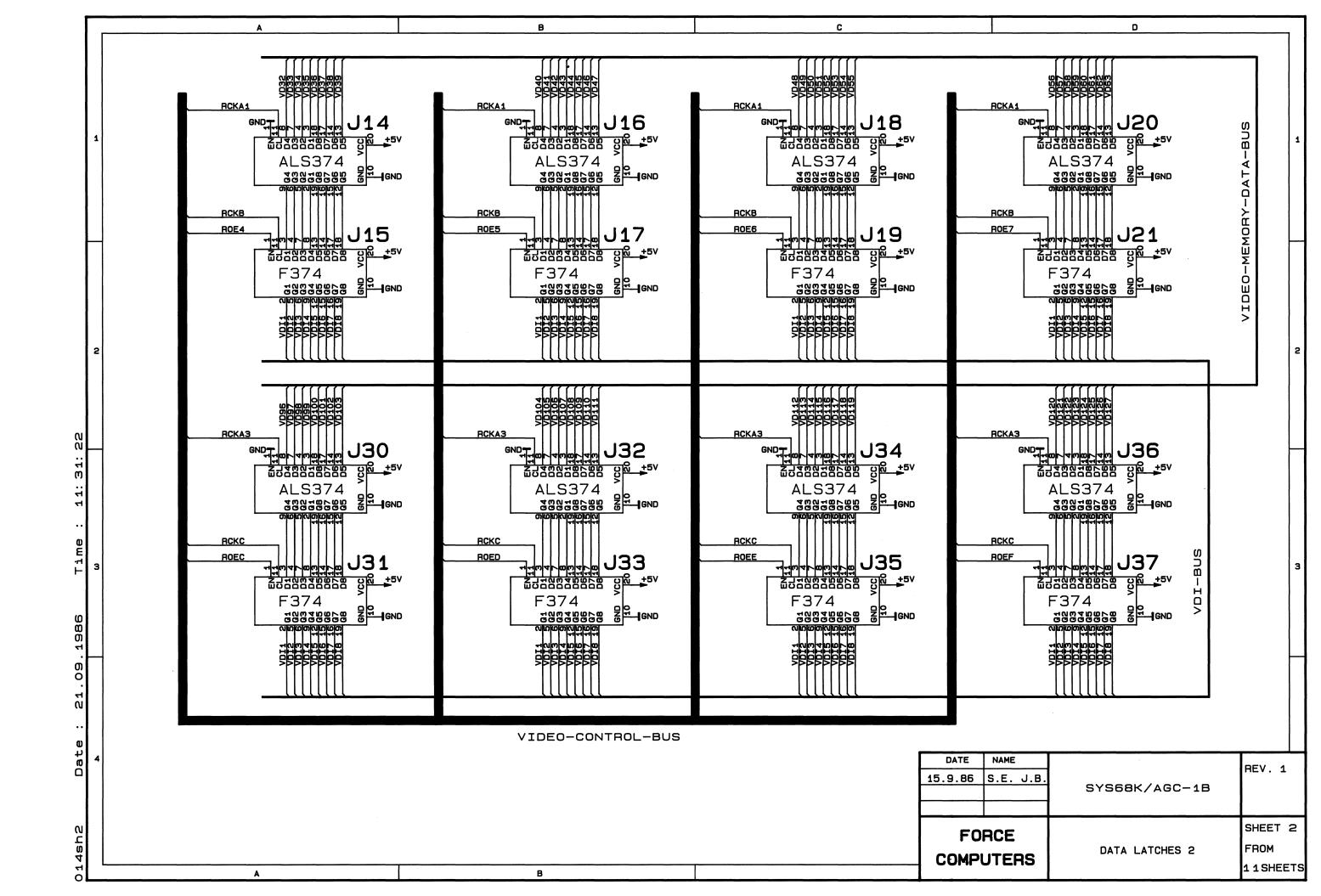

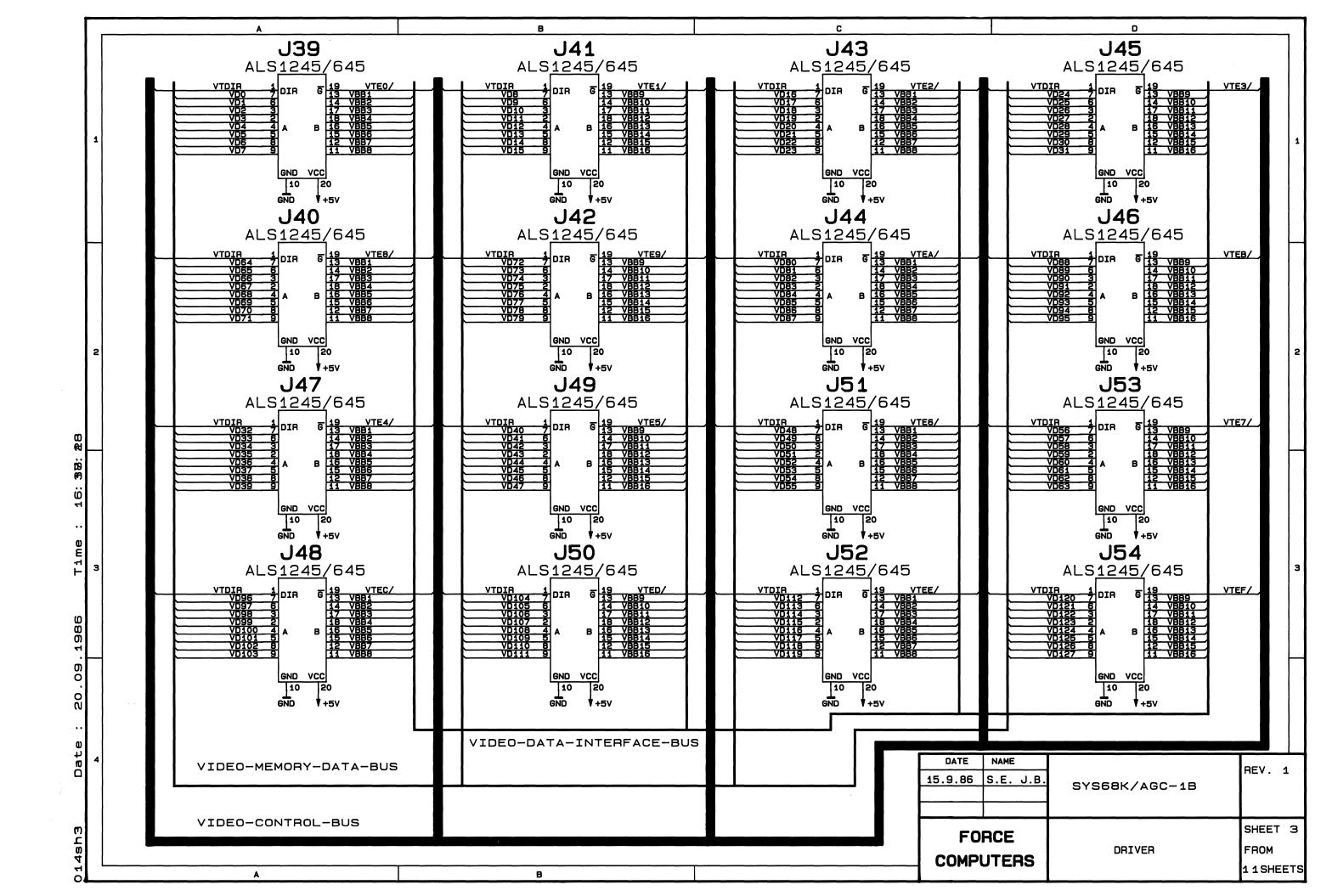

To provide all of these features, the AGC-1 consists of two double Eurocard boards, the main board and the slave board. On the main board the bus interface, the graphic processor, the colour-look-up tables and the Digital to Analogue coverters are installed.

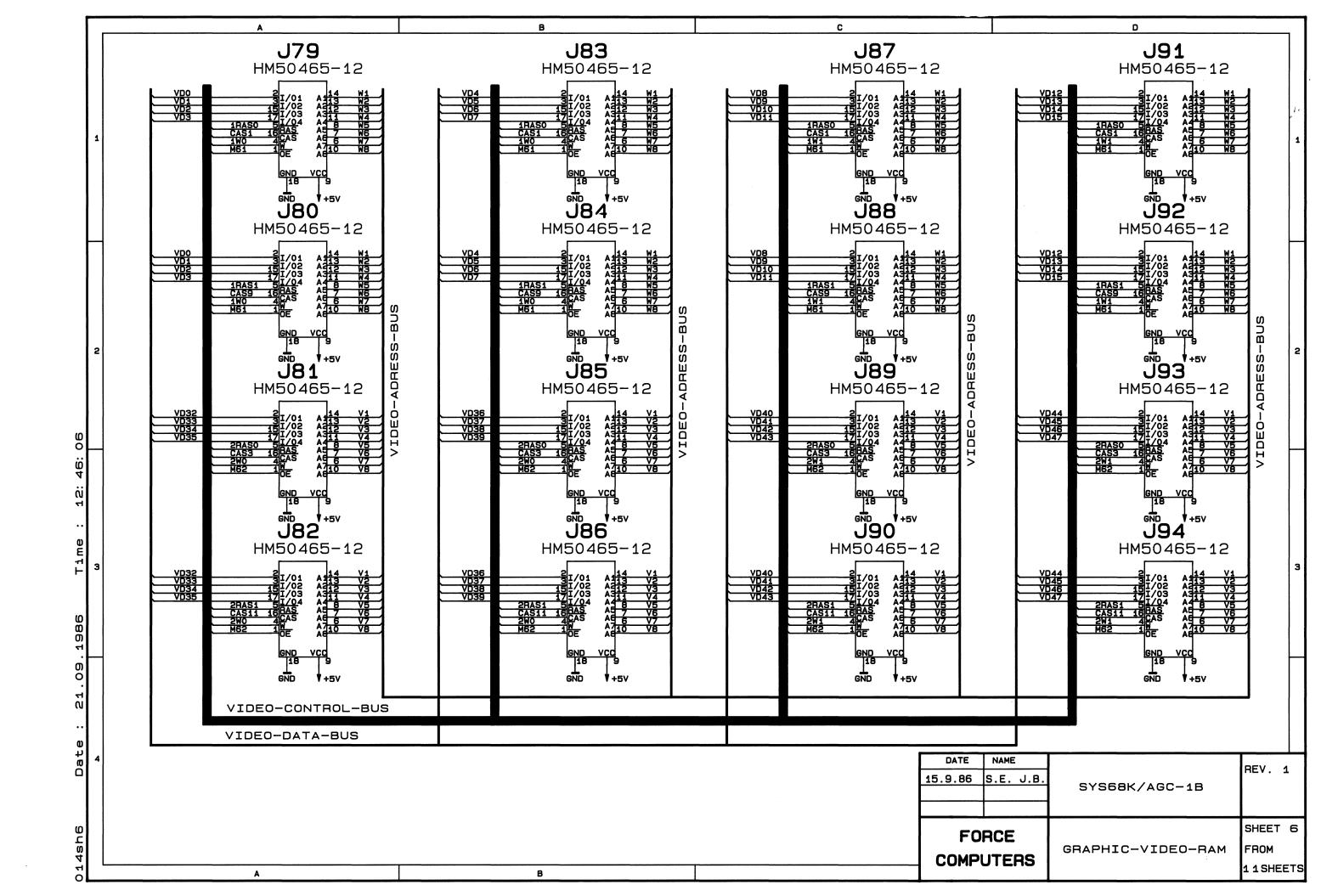

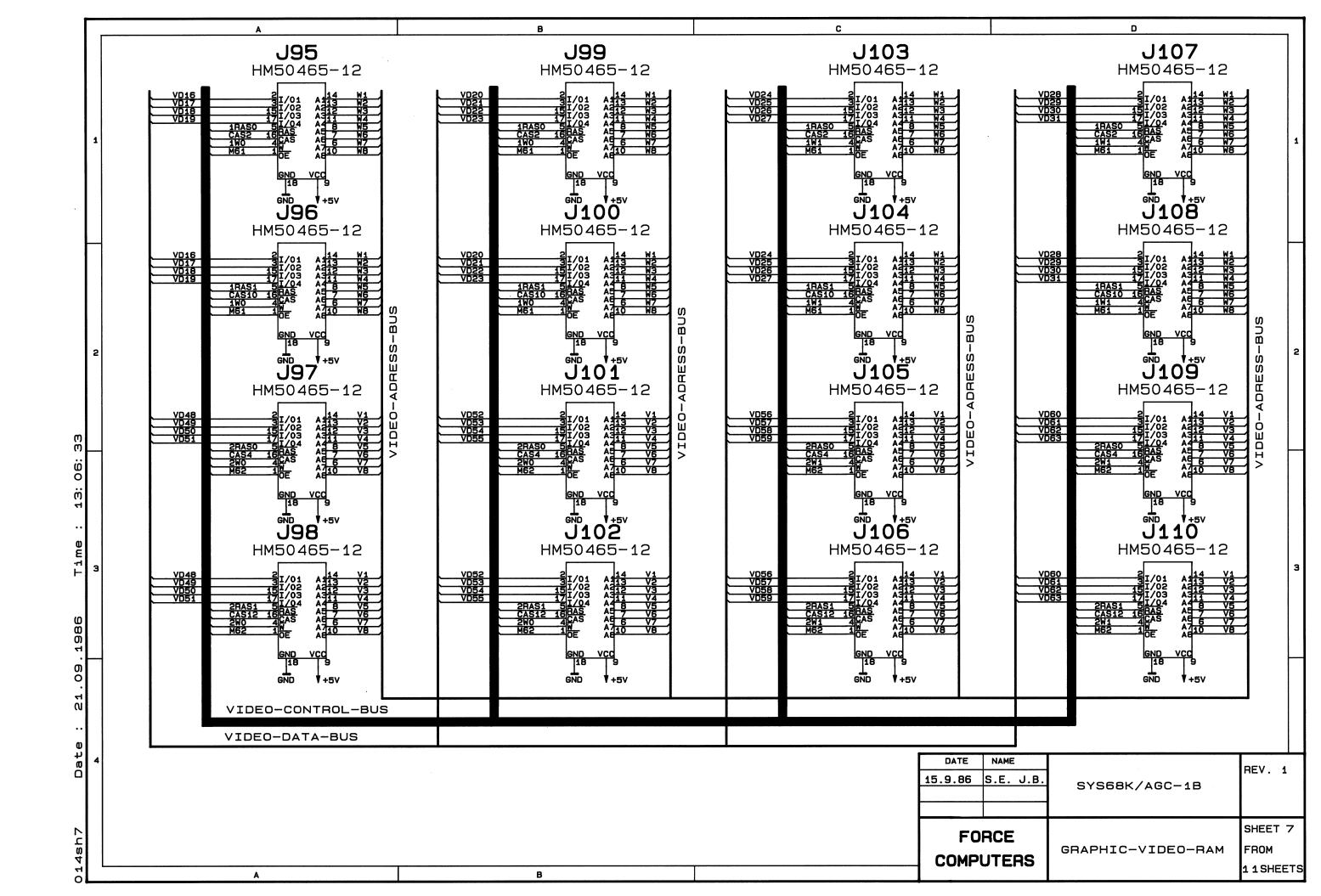

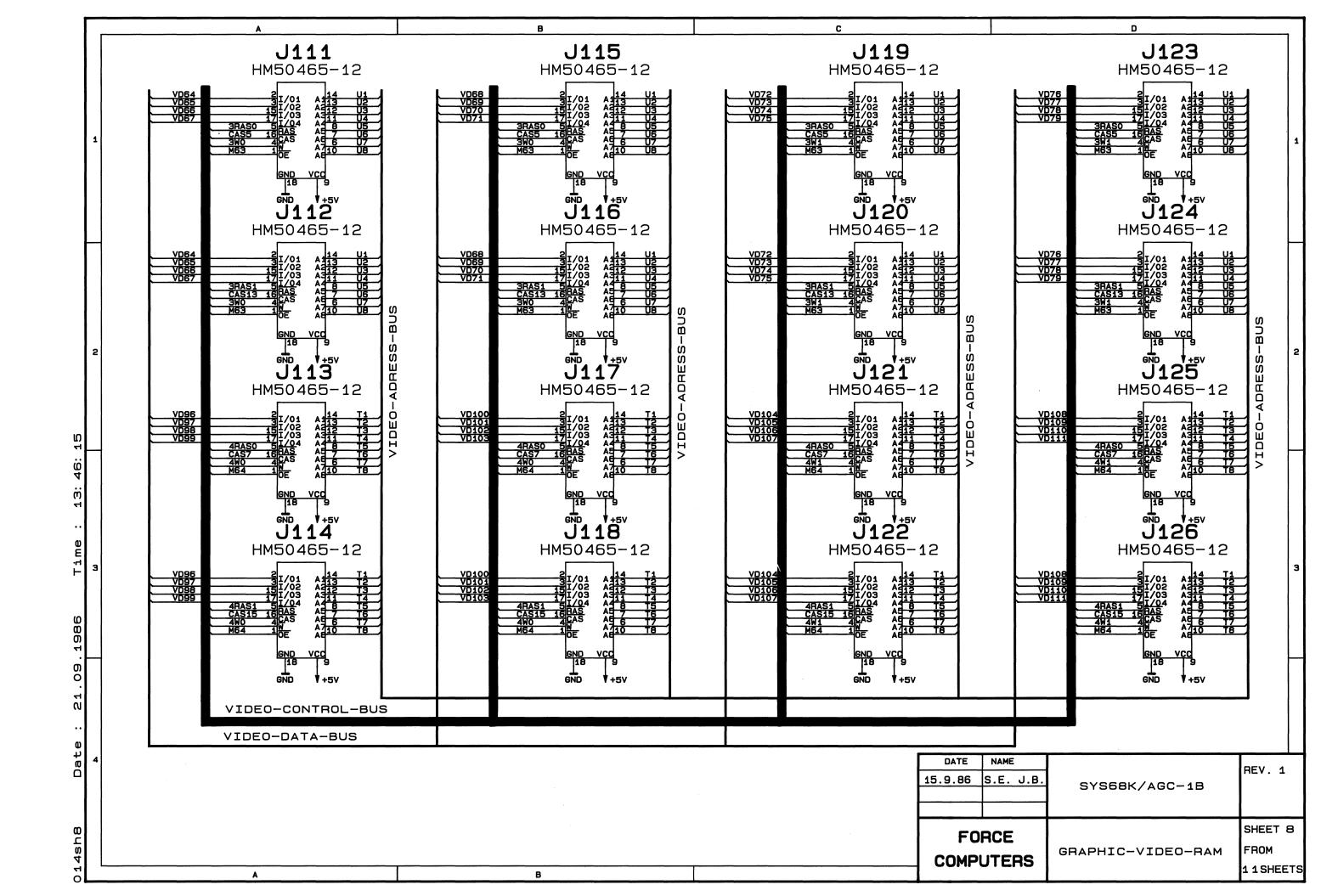

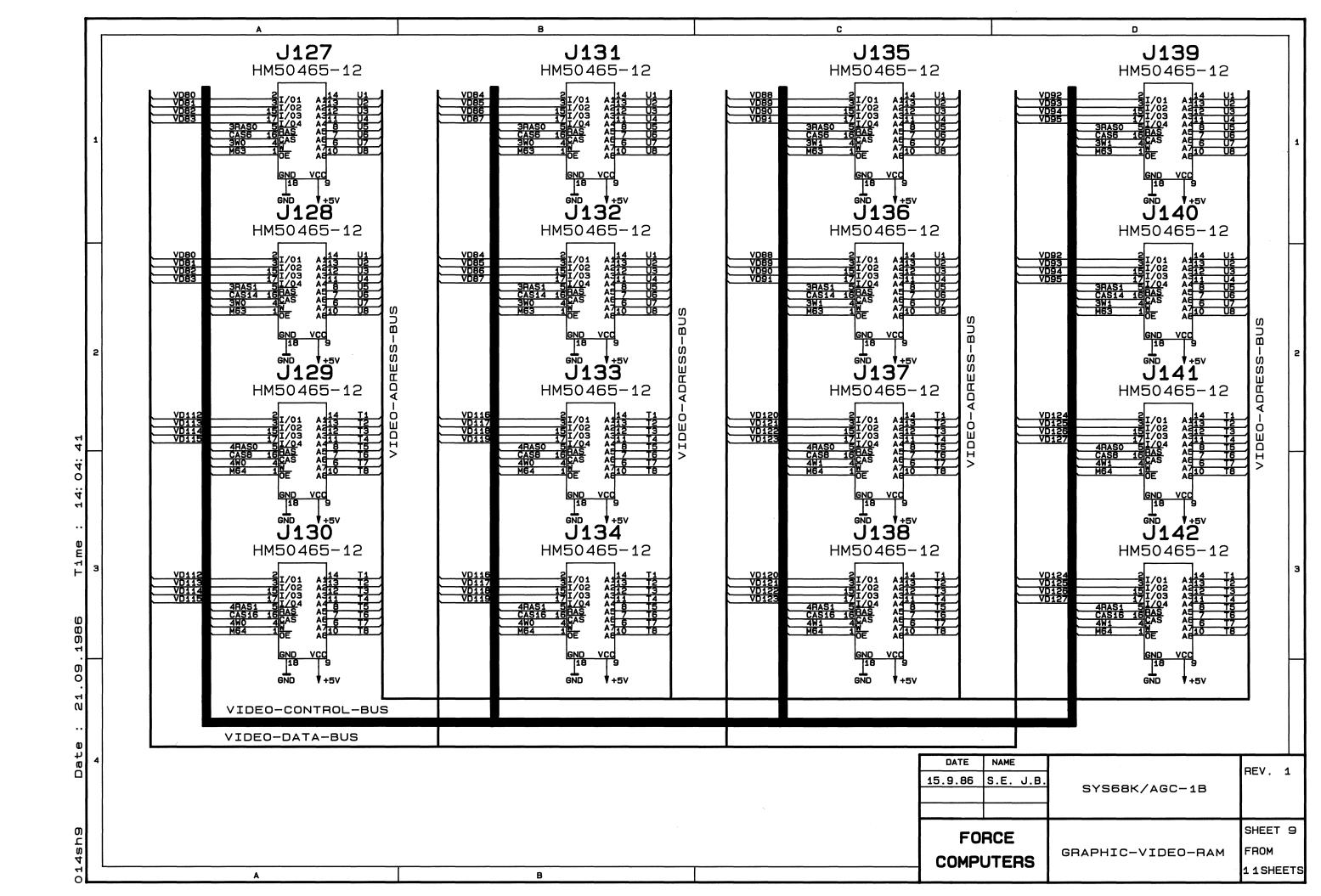

The slave board contains the 2 Mbyte Video-RAM as well as the parallel-to-serial shift registers.

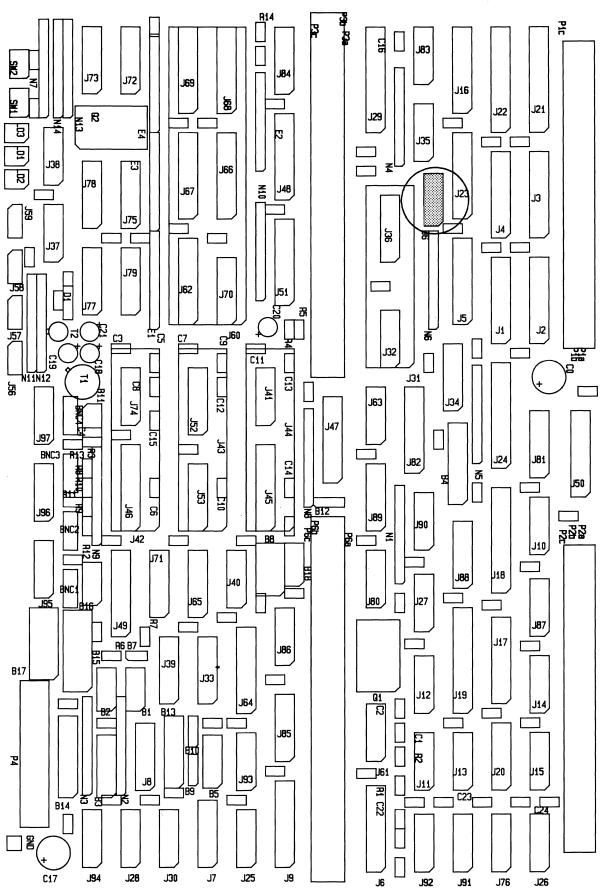

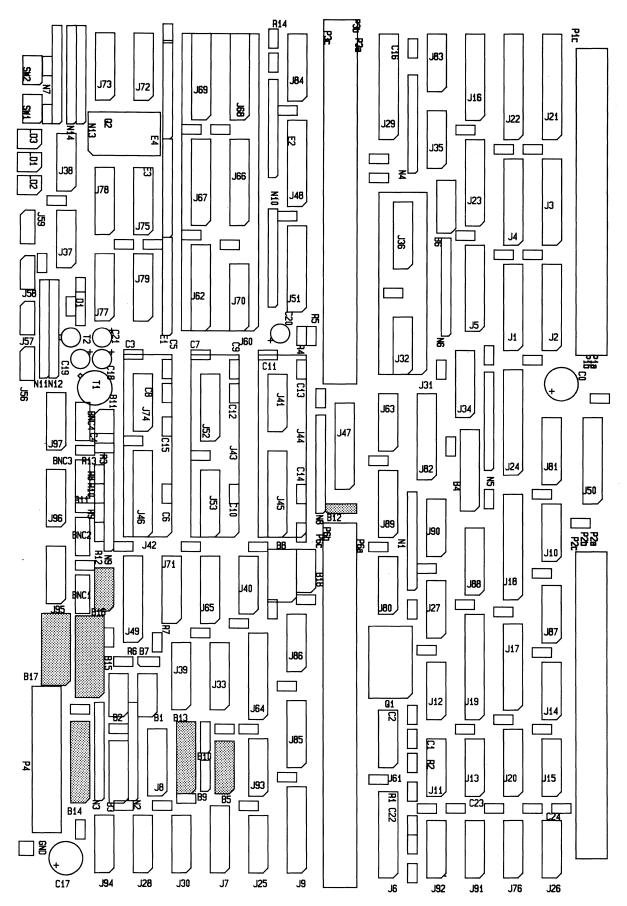

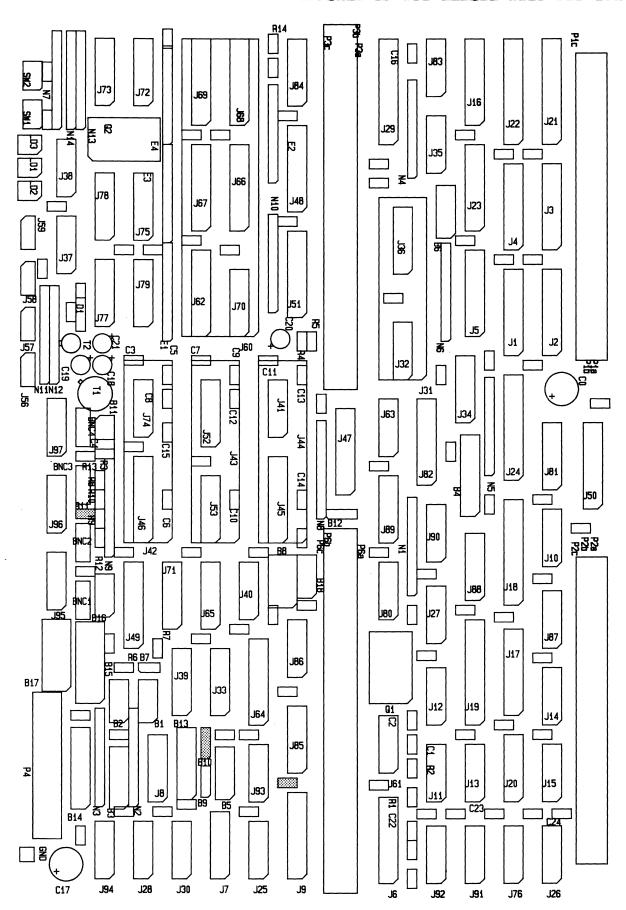

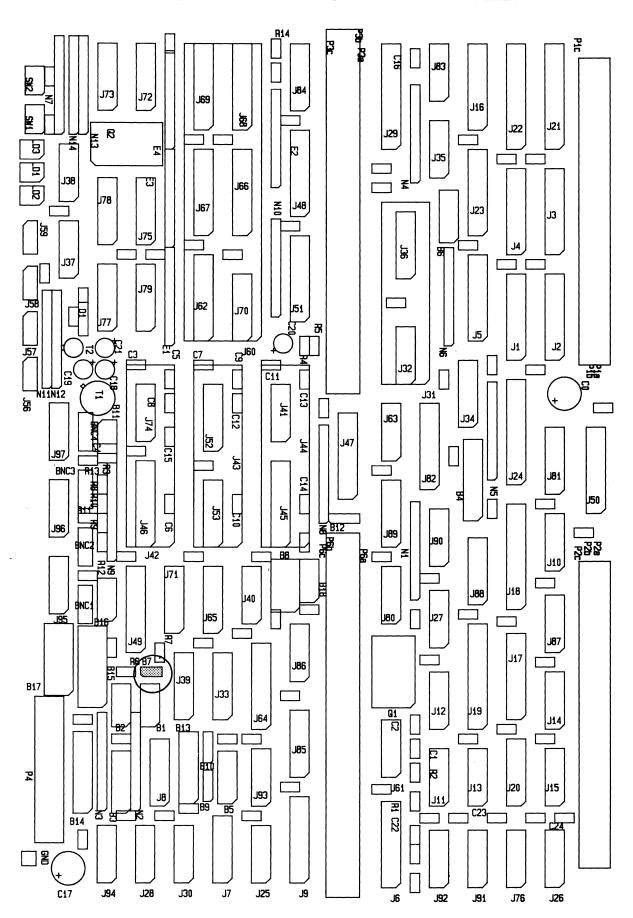

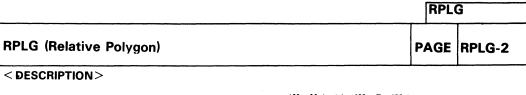

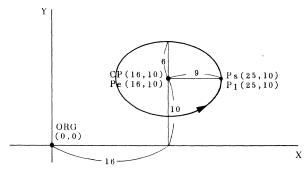

The photo of the SYS68K/AGC-1 shows the main board in detail, and Figure 1-1 outlines the block diagram of AGC-1.

This manual provides a general operating description of the SYS68K/AGC-l hardware. Follow manufacturer's installation instructions for use and troubleshooting.

Figure 1-1: Photo of the SYS68K/AGC-1A Board

#### 2. GENERAL OPERATION

The SYS68K/AGC-1 board set contains the powerful 63484 ACRTC with 2 MByte of Video-RAM, three DAC's with colour look-up tables and powerful attribut capabilities.

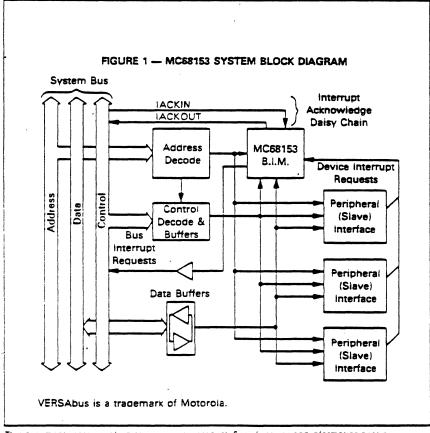

One BIM (68153 Bus Interrupter Module) is used to support fully asynchronous operation to the VMEbus.

The SYS68K/AGC-1 boards are fully VMEbus Rev. C (IEEE Pl014) compatible.

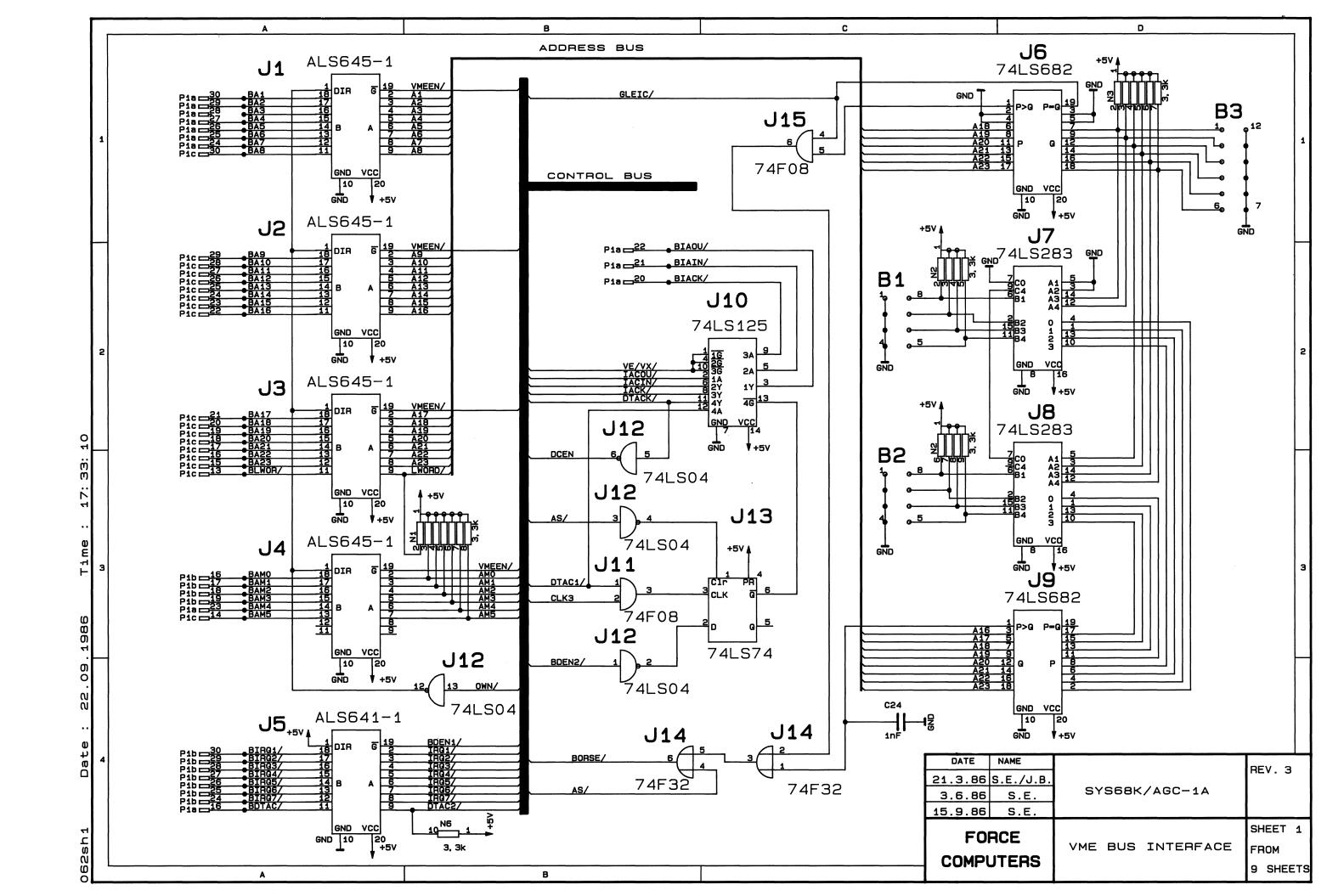

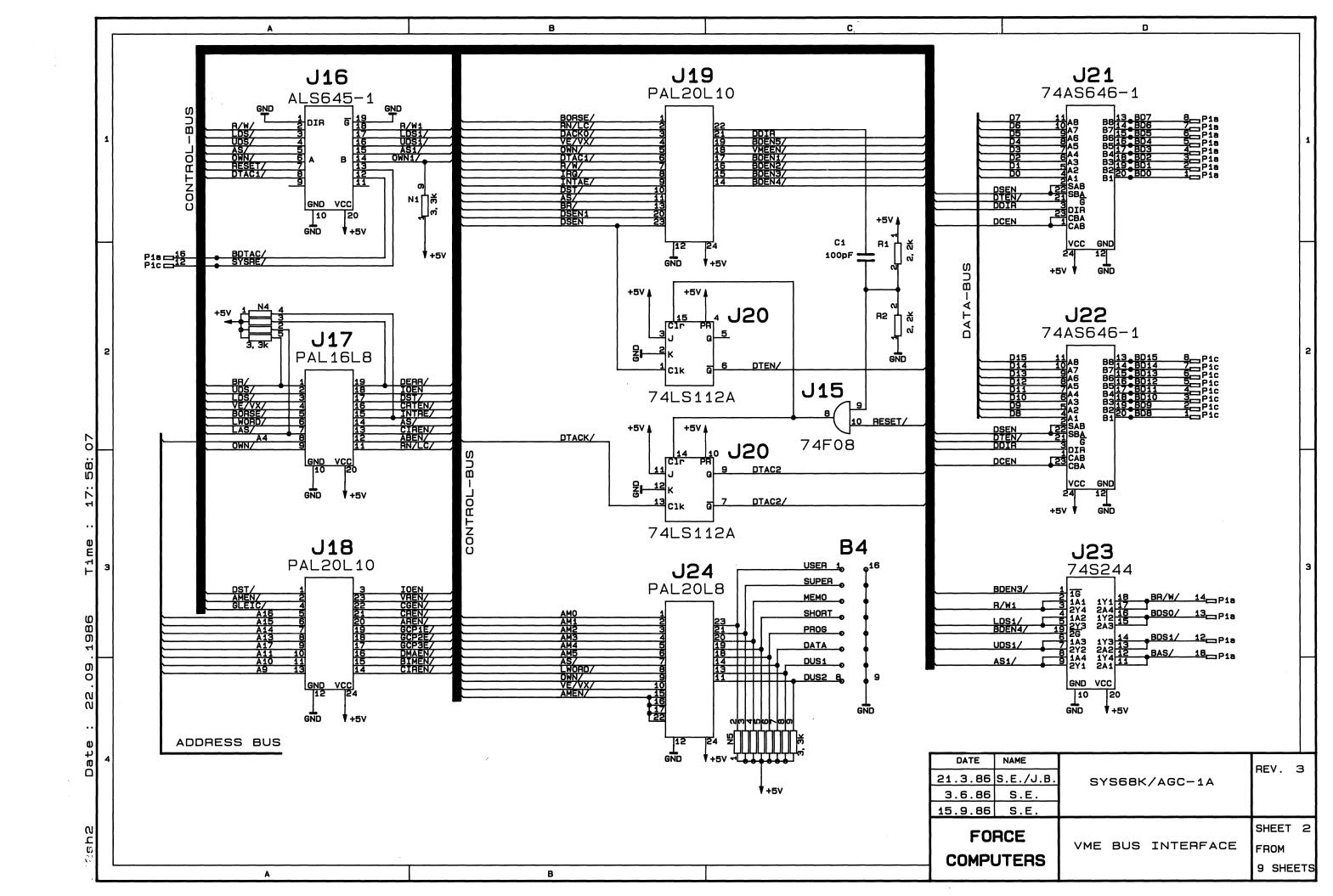

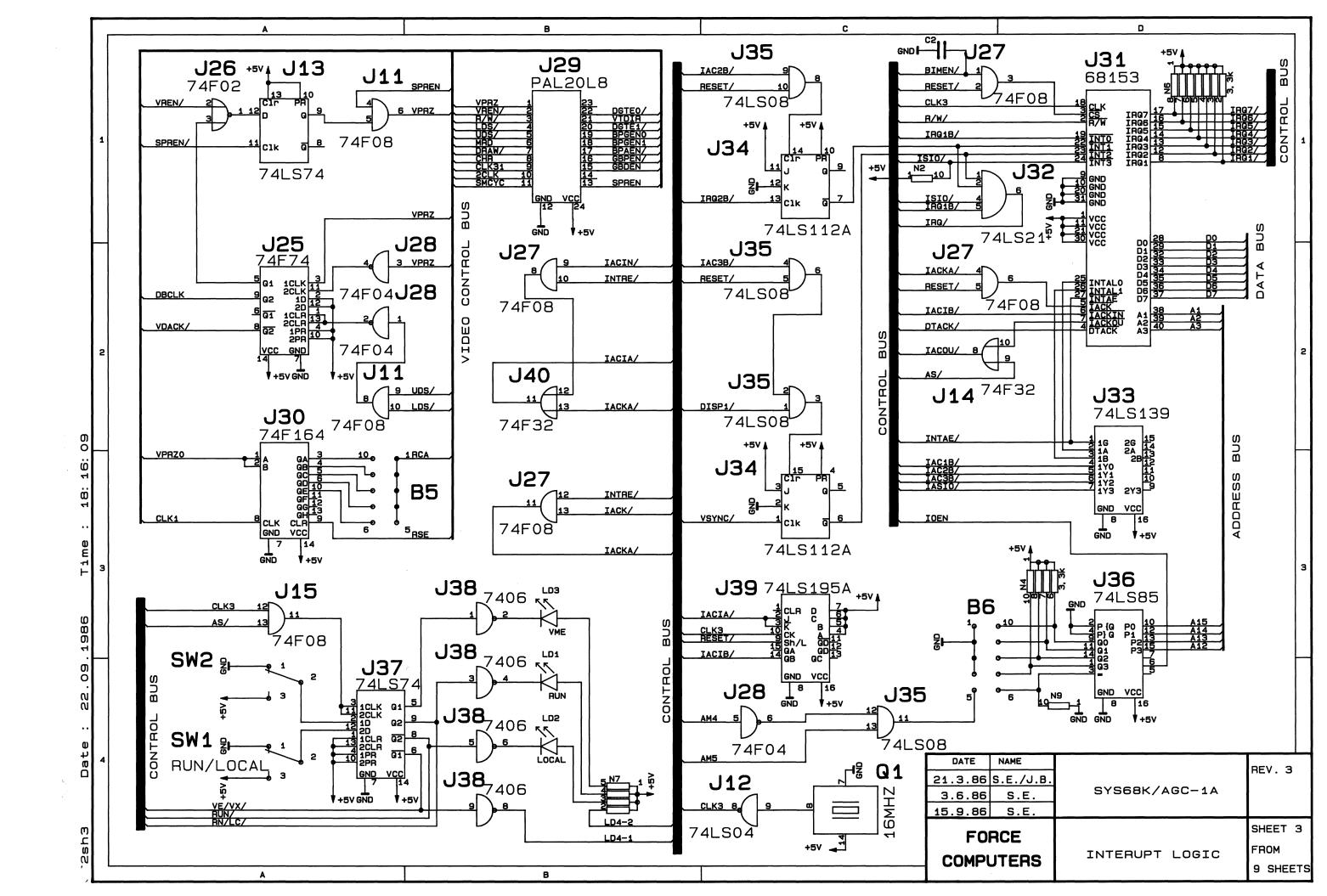

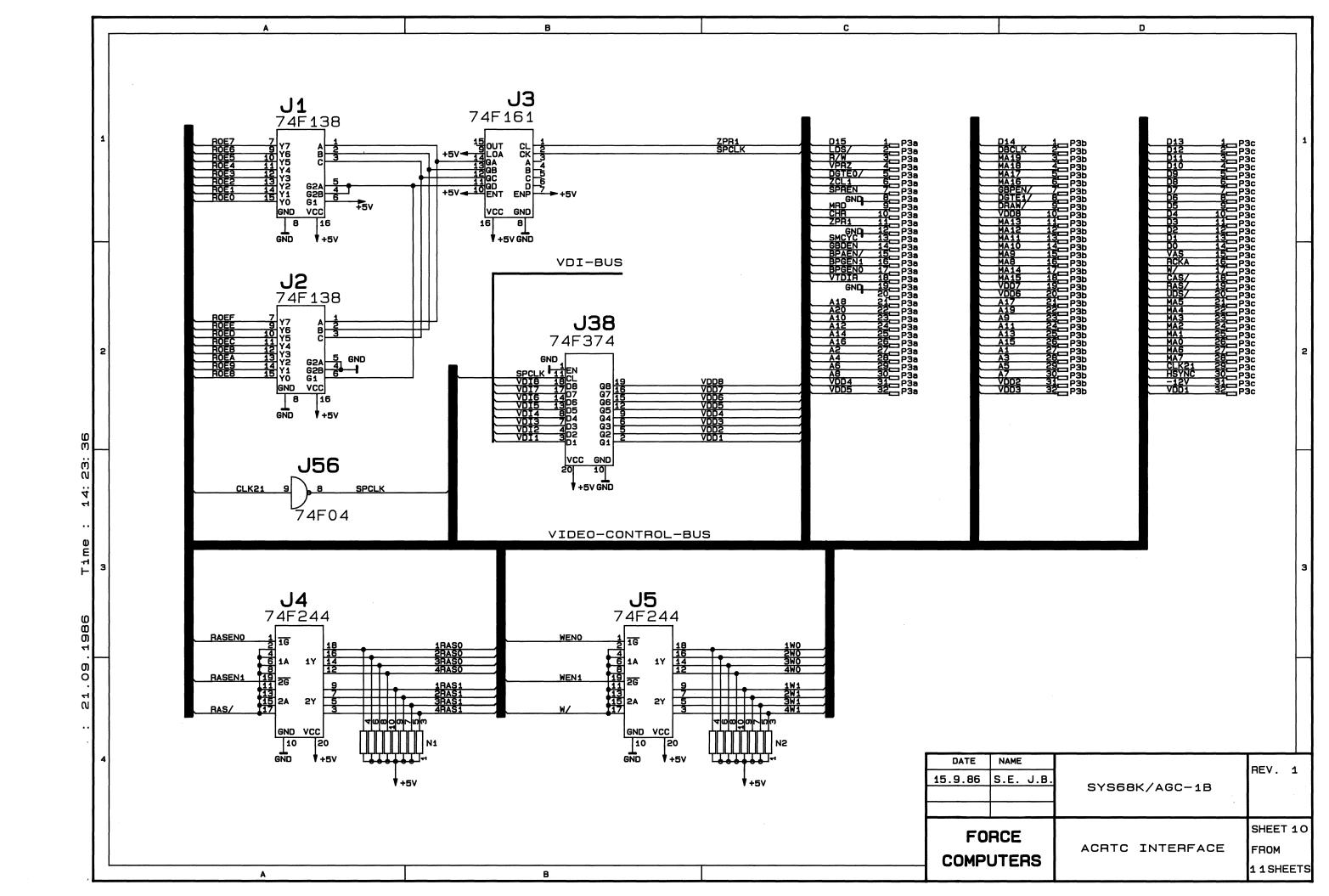

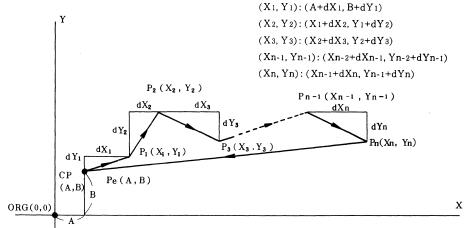

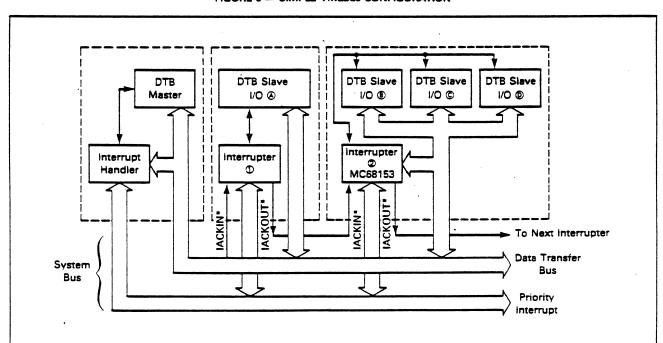

See Figure 2-1 for the general block diagram of the SYS68K/AGC-1 board set.

Figure 2-1: Block Diagram of the SYS68K/AGC-1

#### Features of the SYS68K/AGC-1

- 63484 ACRTC with 8 MHz Clock Frequency.

- 2 Mbyte dynamic Video-RAM with 120ns access time for up to 2048 \* 2048 pixel (in 4 bit/pixel mode).

- Direct video memory access from the VMEbus during display time.

- Zoom logic for magnification in horizontal and vertical direction (up to 16).

- Smooth scroll logic (pixel-wise) for vertical and horizontal direction.

- Video interface bus for upgrading with character overlay.

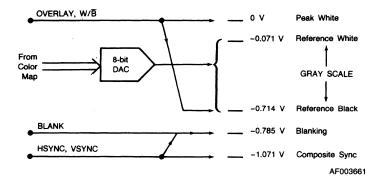

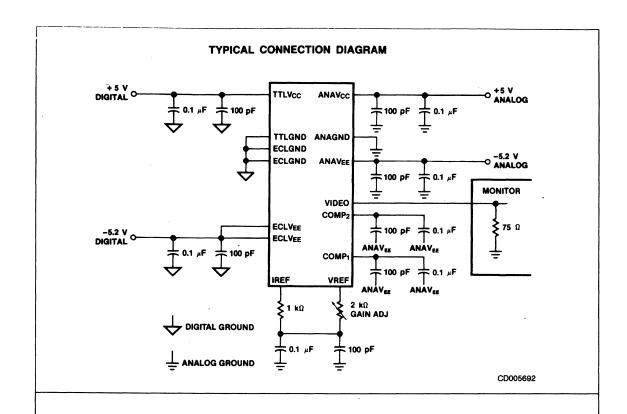

- 3 Graphic Colour Palette AM8151 with 256 entries for each colour and 64 MHz Pixel clock frequency.

- Bus Interrupter Module for all local Interrupt sources.

- Interrupt handling via programmable interrupt vectors.

- Each VMEbus IRQ level can be enabled/disabled via software.

- Fully decoding of the address modifiers.

- Jumper selectable access address for short I/O (Al6 mode) or standard memory (A24 mode).

- RUN/LOCAL switch for complete isolation from the VMEbus.

- Fully VMEbus Rev.C and IEEE Pl014 compatible

|  | * |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

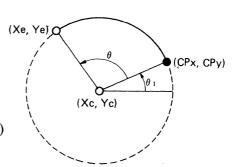

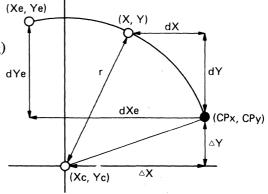

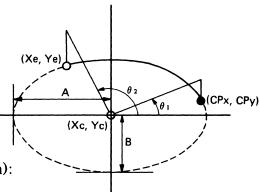

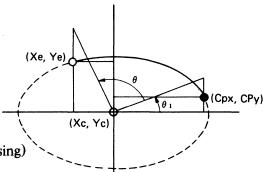

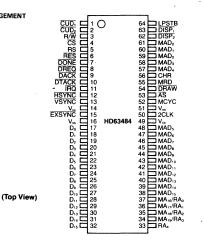

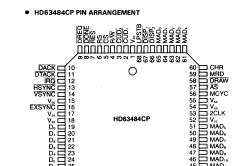

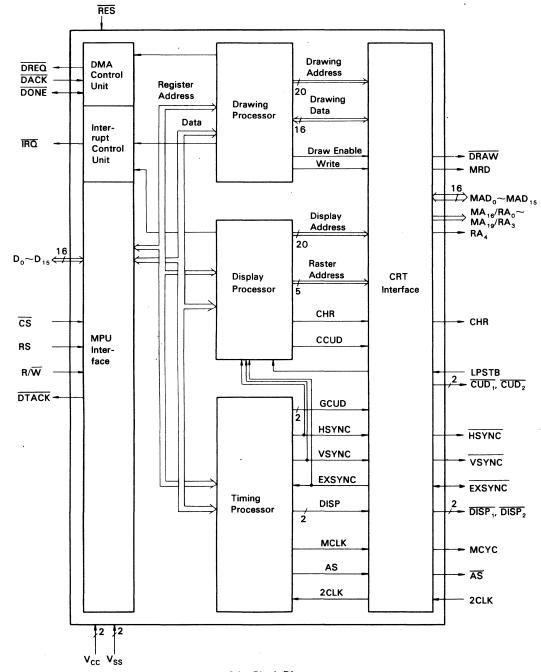

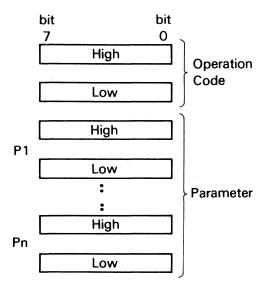

#### 3. THE 63484 ADVANCED GRAPHIC CONTROLLER DESCRIPTION

The 63484 ACRTC contains 38 high level commands including 23 drawing commands for fast generation of polylines, circles, ellipses, circle and ellipse arcs and filled areas. Fast copy and clear commands are very useful for animated graphics. The maximum drawing speed with 8 MHz clock is 2 Million Pixel/second.

He supports up to 2 MByte of video RAM and up to 128 KByte of character RAM.

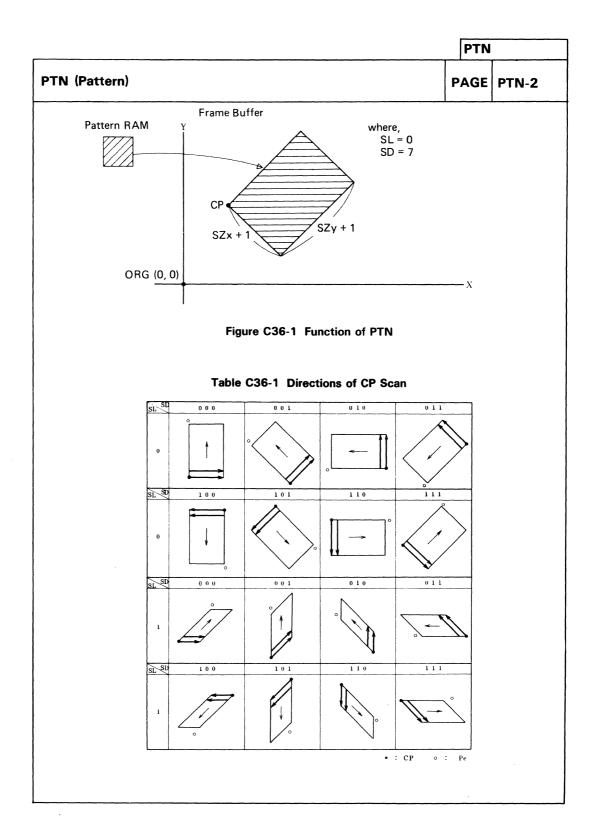

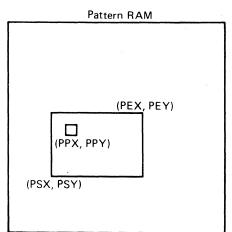

The built-in bit pattern RAM allows the generation of patterns with 16 \* 16 pixel or line-types with 256 pixel pattern length.

Also supported are four hardware windows and functions such as zooming, scrolling, hiting and clipping.

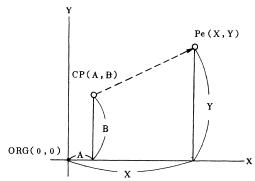

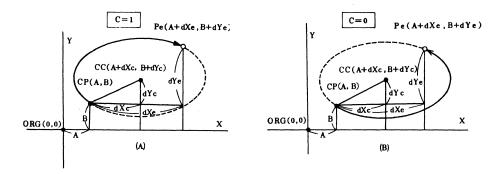

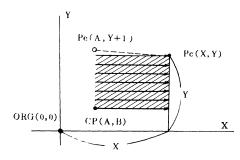

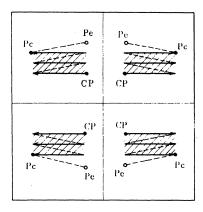

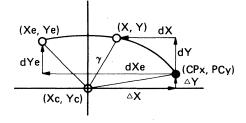

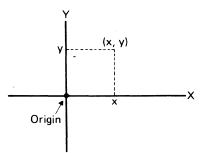

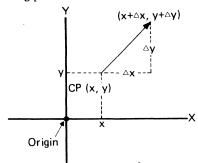

The automatic conversion from logical X/Y coordinates to physical frame buffer addresses eases the programming of graphics.

The non-multiplexed address and data bus are fully asynchronous to allow optimized hardware interfacing to the used VMEbus.

Two 16 Byte FIFO's (read an write) for commands and parameters speed up the accesses from a host processor as well as the DMA-interface for connection with a direct memory access controller.

#### 4. Access to the SYS68K/AGC-1

The SYS68K/AGC-l can be accessed when it is inserted in the VMEbus motherboard and the toggle switches on the front panel are switched to RUN (green LED lights) and VME (yellow VME LED lights).

To access the board, the address bits A18-A23 must match the Board Base Address jumper setting and the Address Modifier Code must match the Address Modifier decoding jumper settings. The SYS68K/AGC-l board is delivered with the default Board Base Address of \$C00000 and is accessible with any Address Modifier Code.

The SYS68K/AGC-1 board occupies an address range of 2.256 MBytes, beginning with the Board Base Address. Read, write and read-modify-write accesses are supported with byte and word operands.

An access to any location in the 2.256 MBytes address range is a legal bus cycle and no bus error will be forced.

#### 4.1 Board Base Address Selection

The Base Address of the SYS68K/AGC-1 board is jumper selectable mainly in two different ways described in Chapter 4.1.1 and 4.1.2.

#### 4.1.1 Board Base Address Selection in the STANDARD MEMORY SPACE

The Base Address of the SYS68K/AGC-1 is jumper selectable in 256kbyte steps within the 16 Mbyte address space. To select the board, the address on the address lines A18-A23 must match the base address jumper settings at jumperfield B3.

B3 is the jumper field defining the address bits A18 to A23 of the Board Base Address.

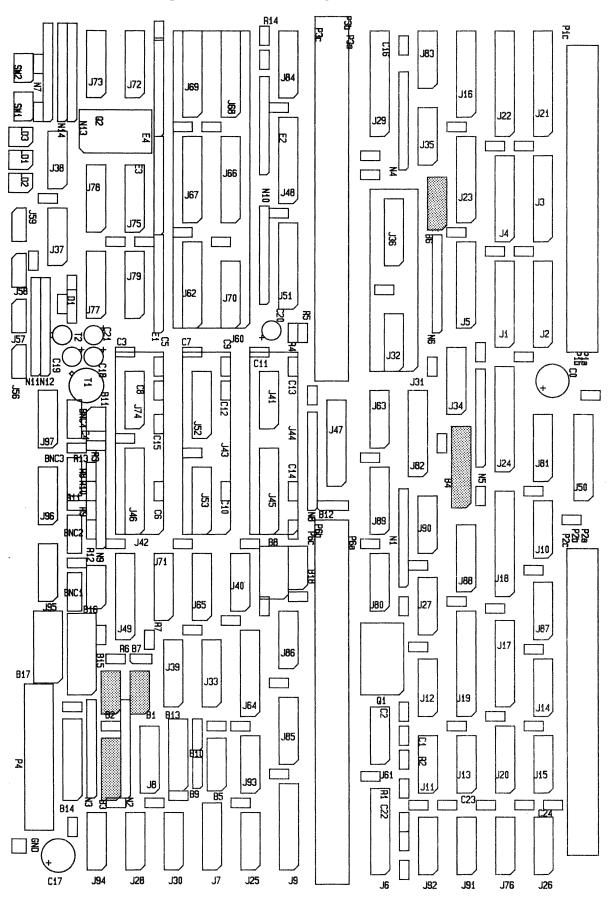

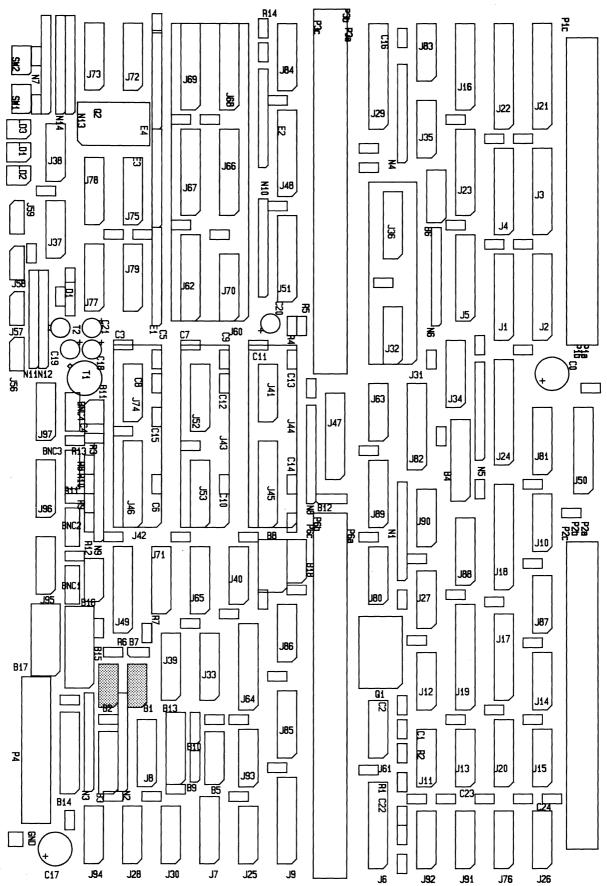

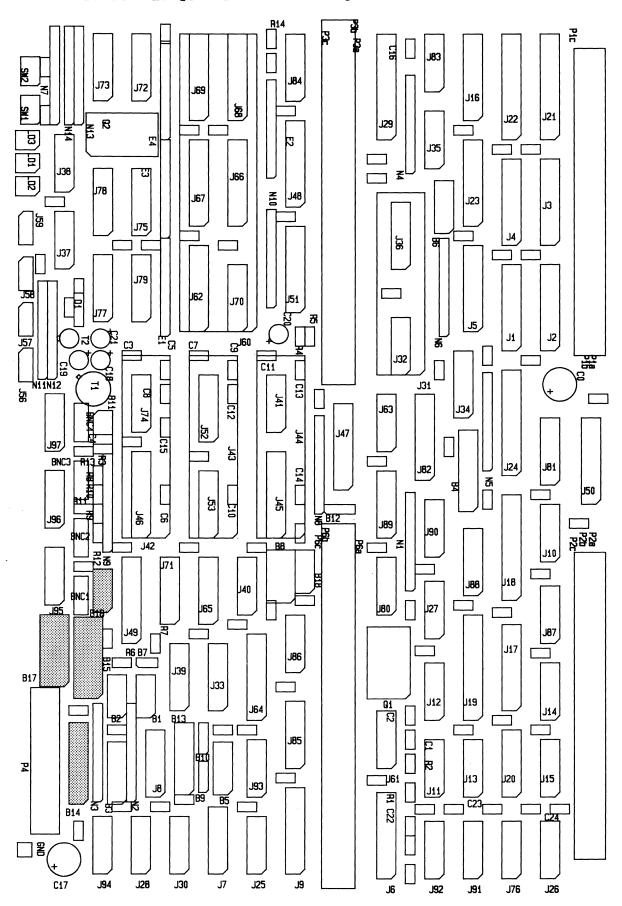

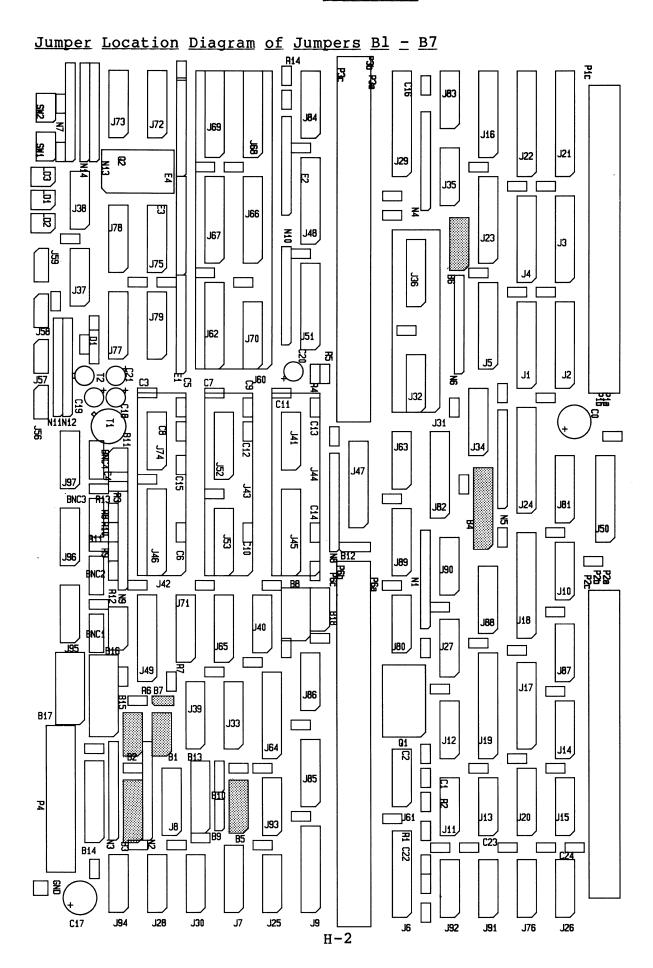

Fig. 4-1 displays the location of the jumper field on the PC board.

Table 4-1 shows the connection assignments and Table 4-2 shows the memory map for standard memory access.

Figure 4-1: Jumper Location Diagram A

## Jumper Description:

B1 and B2: BOARD SIZE SELECTION

B3: BOARD BASE ADDRESS SELECTION

B4: ADDRESS MODIFIER CODE SELECTION

B6 : SHORT I/O ADDRESS SELECTION

## <u>Table 4-1: Jumper Settings for Board Base Address (BBA)</u>

a) BBA=\$000000 b) BBA=\$040000 c) BBA=\$080000 d) BBA=\$0C0000

12

11

9

e) BBA=\$100000 f) BBA=\$140000 q) BBA=\$180000 h) BBA=\$1C0000

| 1 | <br>12      | 1 | 12 | 1 | 12 | 1 | 12 |

|---|-------------|---|----|---|----|---|----|

|   |             | 2 |    | 2 |    | 2 |    |

|   | <del></del> | 3 |    | 3 |    | 3 |    |

| 4 | <br>9       | 4 | 9  | 4 | 9  | 4 | 9  |

| 5 | <br>8       | 5 | 8  | 5 | 8  | 5 | 8  |

| 6 | <br>7       | 6 | 7  | 6 | 7  | 6 | 7  |

i) BBA=\$200000 j) BBA=\$240000 k) BBA=\$280000 l) BBA=\$2C0000

| 1 | 12 | 1 | 12 | 1 12 | 1 | 12 |

|---|----|---|----|------|---|----|

| 2 | 11 | 2 | 11 | 2 11 | 2 | 11 |

| 3 | 10 | 3 | 10 | 3 10 | 3 | 10 |

| 4 | 9  | 4 | 9  | 4 9  | 4 | 9  |

| 5 | 8  | 5 | 8  | 5 8  | 5 | 8  |

| 6 | 7  | 6 | 7  | 6 7  | 6 | 7  |

m) BBA=\$300000 n) BBA=\$340000 o) BBA=\$380000 p) BBA=\$3C0000

| 1 | 12 | 1 | 12 | 1 | 12 | 1 | 12 |

|---|----|---|----|---|----|---|----|

| 2 | 11 | 2 | 11 | 2 | 11 | 2 | 11 |

| 3 | 10 | 3 | 10 | 3 | 10 | 3 | 10 |

| 4 | -  | 4 | 9  | 4 | 9  | 4 | 9  |

| 5 | 8  | 5 | 8  | 5 | 8  | 5 | 8  |

| 6 | 7  | 6 | 7  | 6 | 7  | 6 | 7  |

q) BBA=\$400000 r) BBA=\$440000 s) BBA=\$480000 t) BBA=\$4C0000

## Table 4-1: Jumper Settings for Board Base Address (BBA)

| 1 | 12 | 1   | 12 | 1 | 12 | 1 | 12 |

|---|----|-----|----|---|----|---|----|

| 2 | 11 | 2 : | 11 | 2 | 11 | 2 | 11 |

| 3 | 10 | 3 3 | 10 | 3 | 10 | 3 | 10 |

| 4 | 9  | 4   | 9  | 4 | 9  | 4 | 9  |

| 5 | 8  | 5   | 8  | 5 | 8  | 5 | 8  |

| 6 | 7  | 6   | 7  | 6 | 7  | 6 | 7  |

## C) BBA=\$700000 D) BBA=\$740000 E) BBA=\$780000 F) BBA=\$7C0000

| 1 | 12 | 1 12 | 1 12 | 1 12 |

|---|----|------|------|------|

| 2 | 11 | 2 11 | 2 11 | 2 11 |

| 3 | 10 | 3 10 | 3 10 | 3 10 |

| 4 | 9  | 4 9  | 4 9  | 4 9  |

| 5 | 8  | 5 8  | 5 8  | 5 8  |

| 6 | 7  | 6 7  | 6 7  | 6 7  |

### G) BBA=\$800000 H) BBA=\$840000 I) BBA=\$880000 J) BBA=\$8C0000

#### K) BBA=\$900000 L) BBA=\$940000 M) BBA=\$980000 N) BBA=\$9C0000

## Table 4-1: Jumper Settings for Board Base Address (BBA, Jumper B3)

# Table 4-1: Jumper Settings for Board Base Address (BBA)

9) BBA=\$F00000 a) BBA=\$F40000 b) BBA=\$F80000 c) BBA=\$FC0000

| 1   | - 12 | 1 | 12 | 1 | 12 | 1 | 12 |

|-----|------|---|----|---|----|---|----|

| 2 - | - 11 | 2 | 11 | 2 | 11 | 2 | 11 |

| 3   | 10   | 3 | 10 | 3 | 10 | 3 | 10 |

| 4   | 9    | 4 | 9  | 4 | 9  | 4 | 9  |

| 5   | 8    | 5 | 8  | 5 | 8  | 5 | 8  |

| 6   | 7    | 6 | 7  | 6 | 7  | 6 | 7  |

The following table shows the memory lay-out of AGC-1 for Standard Memory Access:

The Board Base Address (BBA) is jumper selectable in 256K steps.

Table 4-2: MEMORY MAP FOR STANDARD MEMORY ACCESS

| Start Address | End Address    | Memory Area                                              |

|---------------|----------------|----------------------------------------------------------|

| BBA           | BBA + \$35FFF  | BIM 68153                                                |

|               |                | 13.824 times                                             |

| BBA + \$36000 | BBA + \$37FFF  | GCP 1 red                                                |

|               |                | l6 times                                                 |

| BBA + \$38000 | BBA + \$39FFF  | GCP 2 green                                              |

|               |                | le times                                                 |

| BBA + \$3A000 | BBA + \$3BFFF  | GCP 3 blue                                               |

|               |                | l6 times                                                 |

| BBA + \$3CØØØ | BBA + \$3FFFF  | ACRTC 63484                                              |

|               |                | 4096 times                                               |

| BBA + \$40000 | BBA + \$23FFFF | Video-RAM                                                |

| •             |                | l time                                                   |

| BBA + \$3C000 | BBA + \$3FFFF  | 16 times<br>  ACRTC 63484<br>  4096 times<br>  Video-RAM |

#### 4.1.2 Board Base Address Selection for SHORT I/O MEMORY

The second way of accessing the SYS68K/AGC-1 is by using the SHORT I/O address range.

All devices except the Video RAM area can be accessed via SHORT I/O addressing.

In this case the Board Size has to be defined to \$000000 (see Table 4-5)

The SYS68K/AGC-1 then occupies 3,5 Kbyte of the 64 Kbyte SHORT I/O memory.

The Board Start Address is then jumper selectable in 4 Kbyte steps.

For SHORT I/O addressing the address bits Al2-Al5 must match the Board Base Address for SHORT I/O (B6) and the Address Modifier Code must match the Address Modifier decoding jumper settings for SHORT I/O (see Section 4.2).

B6 is the jumper field defining bits 12 to 15 of the Board Base Address.

Fig. 4-2 shows the location of the jumper area B6 on the PC board.

Table 4-3 gives all possible jumper settings.

The default jumper setting of B6 is for STANDARD MEMORY access. Please be careful, especially that jumper position 5,6 is <u>disconnected</u> in this case.

Table 4-4 gives the memory map for short I/O access.

Figure 4-2 Jumper Location Diagram B

B6 : BOARD BASE ADDRESS SELECTION FOR SHORT I/O MEMORY

### Table 4-3: Board Base Address Selection for SHORT I/O Memory

a) STANDARD MEMORY b) BBA=\$FF0000 c) BBA=\$FF1000 d) BBA=\$FF2000

# Default Condition

e) BBA=\$FF3000 f) BBA=\$FF4000 g) BBA=\$FF5000 h) BBA=\$FF6000

| 1 | <br>10 |  |

|---|--------|--|

| 2 | <br>9  |  |

| 3 | 8      |  |

| 4 | 7      |  |

| _ | <br>6  |  |

j) BBA=\$FF8000 k) BBA=\$FF9000 l) BBA=\$FFA000

5 --

i) BBA=\$FF7000

- 1 -- 10 2 --3 --5 --5 --

- m) BBA=\$FFB000

- n) BBA=\$FFC000 o) BBA=\$FFD000 p) BBA=\$FFE000

3 --

4 --

5 --

5 --

4 --

d) BBA=\$FFF000

The following table shows the memory lay-out of AGC-1 for Short I/O Memory Access:

The Board Base Address (BBA) is jumper selectable in  $\,4\mbox{K}\,$  steps using the short I/O decoding.

Table 4-4: Memory Map for Short I/O Access

| Start Address   | End Address     | Memory Area         |

|-----------------|-----------------|---------------------|

| BBA             | BBA + \$5FF     | BIM 68153           |

|                 |                 | 96 times            |

| BBA + \$600     | BBA + \$7FF     | GCP l red           |

|                 |                 | l time              |

| BBA + \$800     | BBA + \$9FF     | GCP 2 green         |

|                 |                 | l time              |

| BBA + \$AØØ     | BBA + \$BFF     | GCP 3 blue          |

|                 |                 | 1 time              |

| BBA + \$C00     | BBA + \$DFF     | ACRTC 63484         |

|                 |                 | l 128 times         |

| only accessible | via ACRTC 63484 | <br>  Video-RAM<br> |

#### 4.2 Board Size Selection

For special applications it could be necessary to decrease the memory space occupied by the SYS68K/AGC-1 board. This could be done by setting the jumpers Bl and B2. In doing this it is possible to fade out the Video Memory or parts of it. Nevertheless the Video Memory can be accessed via the 63484 ACRTC.

The Board Size can be decreased in 64 Kbyte steps.

Fig. 4-3 displays the locations of the jumper fields on the PC board.

Table 4-5 shows the possible jumper settings for the Board Size (BS)

# Figure 4-3 JUMPER LOCATIONS DIAGRAM C

Bl and B2: BOARD SIZE SELECTION

### Table 4-5 Board Size Selection Jumper Settings

## Table 4-5 Board Size Selection Jumper Settings

### <u>Table 4-5</u> Board Size Selection Jumper Settings

### K) BS=\$000000

Table 4-6: Address Modifier Codes

| HEX                                                        | Address<br>  5 <b>4</b> 3                                                                                     |                         |                            | Function                                                                                                                                                                                                                                                   |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3F                                                         | <br>  H H H<br>  H H H                                            | H H H L L H L L         |                            | Standard Supervisory Block Transfer   Standard Supervisory Program Access   Standard Supervisory Data Access   Reserved   Standard Non-Privileged Block Transfer   Standard Non-Privileged Program Access   Standard Non-Privileged Data Access   Reserved |

| 37<br>  36<br>  35<br>  34<br>  33<br>  32<br>  31<br>  30 | H H L<br>  H H L                                                  | H H H L H L H L L H L H | L<br>H<br>L<br>H           | Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved                                                                                                                                                                           |

| 2F<br>  2E<br>  2D<br>  2C<br>  2B<br>  2A<br>  29<br>  28 | H L H<br>  H L H                                                  | H H H L H L H L H L H   | L<br>H<br>L<br>H           | Reserved Reserved Short Supervisory Access Reserved Reserved Reserved Short Non-Privileged Access Reserved                                                                                                                                                 |

| 27<br>  26<br>  25<br>  24<br>  23<br>  22<br>  21<br>  20 | H L L   H L L   H L L   H L L   H L L   H L L   H L L   H L L   H L L   H L L   H L L   H L L   H L L   H L L | H H H L H L L H L L     | H<br>L<br>H<br>L<br>H<br>L | Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved                                                                                                                                                                           |

L = low signal level H = high signal level

| HEX Code                                                              | Addre                                 | ss Mo                                  |                            |                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------|---------------------------------------|----------------------------------------|----------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1F<br>  1E<br>  1D<br>  1C<br>  1B<br>  1A<br>  19<br>  18            | L H L H L H L H L H L H               | H H H H H H H L H L H L                | H<br>L<br>L<br>H<br>H<br>L |                            | User Defined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17<br>  16<br>  15<br>  14<br>  13<br>  12<br>  11<br>  10            | L H                                   | L H L H L H L L L L L L                | H<br>L<br>H<br>H<br>L      | L<br>H                     | User Defined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <br> <br>  ØF<br>  ØE<br>  ØD<br>  ØC<br>  ØB<br>  ØA<br>  Ø9<br>  Ø8 | L L L L L L L L L L L L L L L L L L L | H H<br>H H<br>H H<br>H L<br>H L<br>H L | H<br>L<br>L<br>H<br>H<br>L |                            | Extended Supervisory Block Transfer   Extended Supervisory Program Access   Extended Supervisory Data Access   Reserved   Extended Non-Privileged Block Transfer   Extended Non-Privileged Program Access   Extended Non-Privileged Data Access   Reserved   Reserved   Extended Non-Privileged Data Access   Extended Data Acces |

| <br>                                                                  | L L L L L L L L L L L L L L L L L L L | L H L H L H L L L L L L                | L<br>H<br>H                | H<br>L<br>H<br>L<br>H<br>L | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

L = low signal level H = high signal level

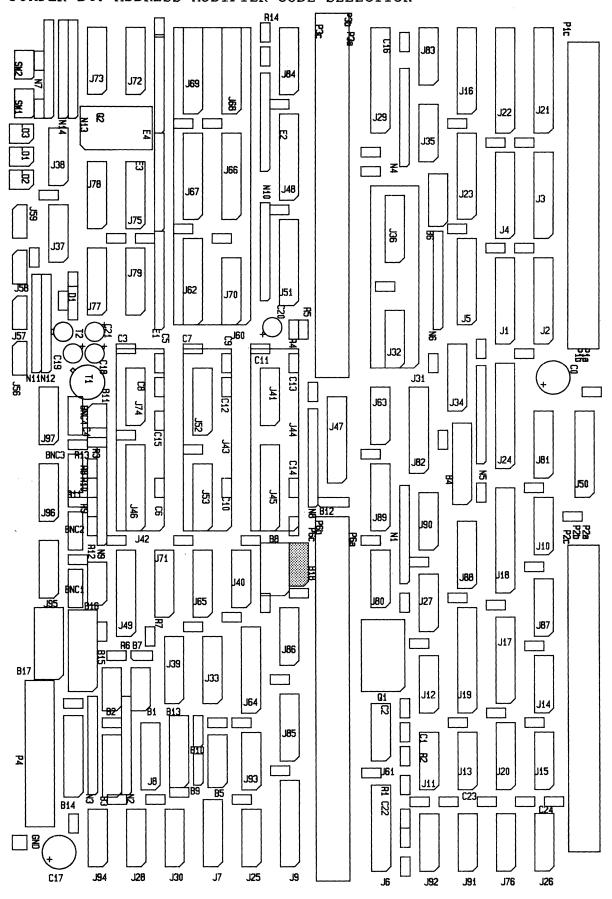

#### 4.3 Address Modifier Code Selection

The SYS68K/AGC-1 has a jumper selectable Address Modifier Code. Table 4-6 shows the VMEbus AM codes. Each allowed AM Code or combinations of allowed AM Codes can be set. The selection is coded by jumper settings in the field at B4.

Fig. 4-4 shows the location of the jumper field on the PC board.

Table 4-6 shows the VMEbus AM Codes.

Table 4-7 shows the jumper selectable connections.

When selecting the SHORT I/O AM Codes, the Base Address jumper selection on B3 is ignored. The Base Address for SHORT I/O access is jumpered with the jumper field B6. Please be make sure that the board size jumper setting is set to \$00000 for SHORT I/O access.

Figure 4-4: Jumper Location Diagram of Address Modifier Selection

JUMPER B4: ADDRESS MODIFIER CODE SELECTION

### TABLE 4-7: Address Modifier Code Selection

| 1 16 | 1 16 | 1 16 | 1 16 |

|------|------|------|------|

| 2 15 | 2 15 | 2 15 | 2 15 |

| 3 14 | 3 14 | 3 14 | 3 14 |

| 4 13 | 4 13 | 4 13 | 4 13 |

| 5 12 | 5 12 | 5 12 | 5 12 |

| 6 11 | 6 11 | 6 11 | 6 11 |

| 7 10 | 7 10 | 7 10 | 7 10 |

| 8 9  | 8 9  | 8 9  | 8 9  |

| 1 | 16 | 1 | 16 | 1 | 16 | 1 | 16 |

|---|----|---|----|---|----|---|----|

| 2 | 15 | 2 | 15 | 2 | 15 | 2 | 15 |

| 3 | 14 | 3 | 14 | 3 | 14 | 3 | 14 |

| 4 | 13 | 4 | 13 | 4 | 13 | 4 | 13 |

| 5 | 12 | 5 | 12 | 5 | 12 | 5 | 12 |

| 6 | 11 | 6 | 11 | 6 | 11 | 6 | 11 |

| 7 | 10 | 7 | 10 | 7 | 10 | 7 |    |

| 8 | 9  | 8 | 9  | 8 | 9  | 8 | 9  |

| 1 16 | 1 16 | 1 16 | 1 16 |

|------|------|------|------|

| 2 15 | 2 15 | 2 15 | 2 15 |

| 3 14 | 3 14 | 3 14 | 3 14 |

| 4 13 | 4 13 | 4 13 | 4 13 |

| 5 12 | 5 12 | 5 12 | 5 12 |

| 6 11 | 6 11 | 6 11 | 6 11 |

| 7 10 | 7 10 | 7 10 | 7 1Ø |

| 8 9  | 8 9  | 8 9  | 8 9  |

# Table 4-7: ADDRESS MODIFIER CODE SELECTION

| a) AM Code= 14                                              | b) AM Code=<br>3D,39                                                      | c) AM Code=<br>2D,29                                        | d) AM Code=<br>3A,39,38                      |

|-------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|

| 1 16<br>2 15<br>3 14<br>4 13<br>5 12<br>6 11<br>7 10<br>8 9 | 1 16<br>2 15<br>3 14<br>4 13<br>5 12<br>6 11<br>7 10<br>8 9<br>default se | 1 16<br>2 15<br>3 14<br>4 13<br>5 12<br>6 11<br>7 10<br>8 9 | 1 16 2                                       |

| a) AM Code= 3E,3D,3C                                        | b) AM Code=<br>3E,3A                                                      | c) AM Code= 3E<br>3F,3E,3D,3C<br>3B,3A,39,38                | d) AM Code=<br>don`t care                    |

| 1 16<br>2 15<br>3 14<br>4 13<br>5 12<br>6 11                | 1 16<br>2 15<br>3 14<br>4 13<br>5 12<br>6 11<br>7 10                      | 1 16<br>2 15<br>3 14<br>4 13<br>5 12<br>6 11                | 1 16<br>2 15<br>3 14<br>4 13<br>5 12<br>6 11 |

## 4.4 Functional Groups on the SYS68K/AGC-1

The SYS68K/AGC-1 board is considered to consist of the following functional groups:

- Graphics Processor

- 3 Colour Look-up Tables

- Video Memory

The Graphics Processor consists of:

- the ACRTC 63484

- two interrupt channels of the BIM

A Colour Look-up Table consists of:

- 256 Byte of colour value RAM

The Video Memory consists of:

- 2M Byte of DRAM

#### 4.5 Access to the Devices on the SYS68K/AGC-1 Board

There are six addressable devices installed:

| ACRTC     | 63484 |

|-----------|-------|

| BIM       | 68153 |

| GCP-red   | 8151  |

| GCP-green | 8151  |

| GCP-blue  | 8151  |

| Video-RAM |       |

All user accessible registers and RAM areas are directly addressable on the SYS68K/AGC-1.

All devices and the RAM area have a 16 bit wide data bus.

The BIM and the three GCP's are accessible only on the lower byte  $(D\emptyset-D7)$ .

Read, write and read-modify-write accesses are supported. (the limitations are documented in the device data sheets).

The access addresses of accessible Registers and RAM areas on the board are given in Chapter 4.1.

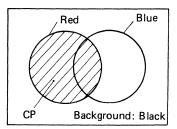

#### 4.6 Addressing of the Colour Look-up Tables

The 3 Colour Look-up tables for red, green and blue are fully independent of each other, and they are all identical in their functions.

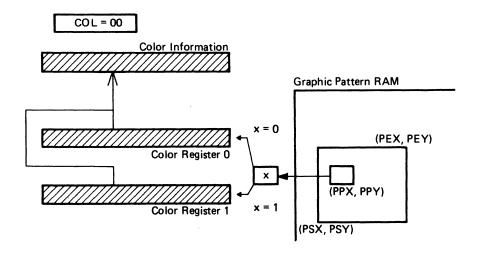

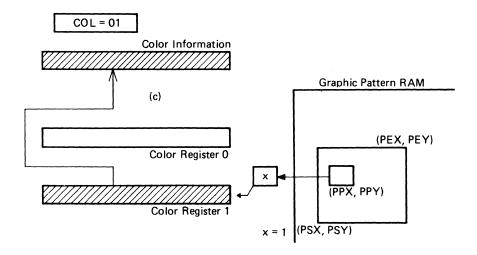

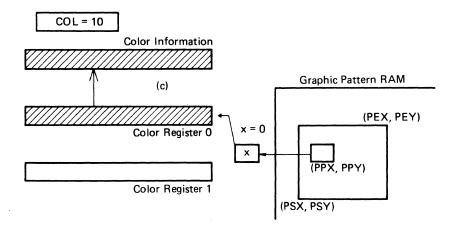

The 256 colour entries provide 256 colours (in 8 bit/pixel mode) or 16 different tables with 16 colours (in 4bit/pixel mode). This makes it possible to display 256 colours (16 colours in 4 bit/pixel mode) out of 16.777216 million.

The colour look-up tables are addressed in word mode. The lower byte contains the colour value, the upper byte is always \$FF. A byte-wide addressing is possible but then every even address represents a colour entry.

The bit value of a given pixel points on the respective colour entry of the colour look-up tables.

Example: The look-up table for the RED colour is located at address \$BFA000

#### 4 bit/pixel mode

| Pixel value | Look-up table address |  |  |

|-------------|-----------------------|--|--|

| \$04        | \$BFA008              |  |  |

| \$ØA        | \$BFA014              |  |  |

| \$ØF        | \$BFA01E              |  |  |

## 8 bit/pixel mode

| Pixel value | Look-up table address |

|-------------|-----------------------|

| \$10        | \$BFA020              |

| \$55        | \$BFAØAA              |

| \$FF        | \$BFA1FE              |

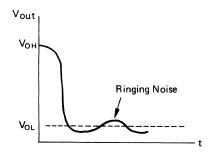

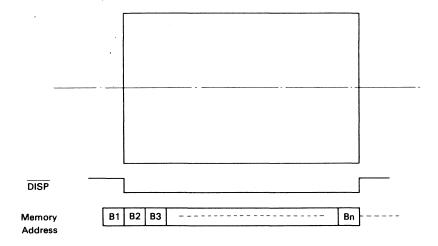

To avoid a `flickering' display the colour look-up tables should be loaded before the initialisation of the ACRTC or during the vertical retrace period. This could be done Interrupt-driven or by polling the Raster Count register of the ACRTC (see Chapter 4.7.1 and 4.9.7).

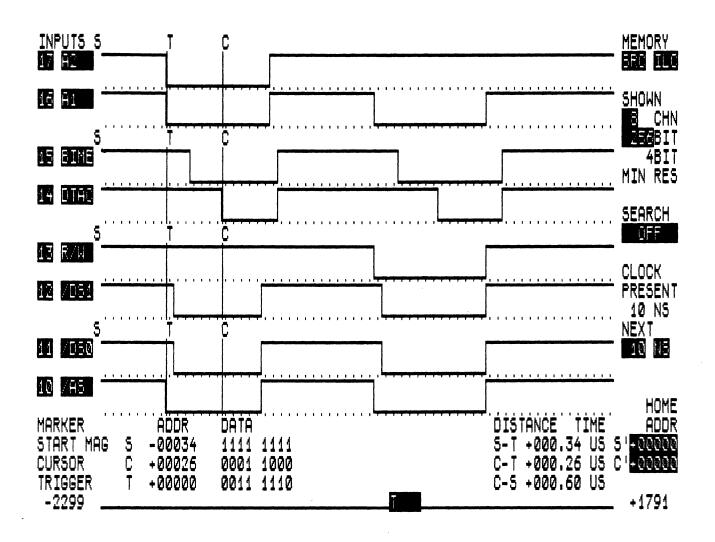

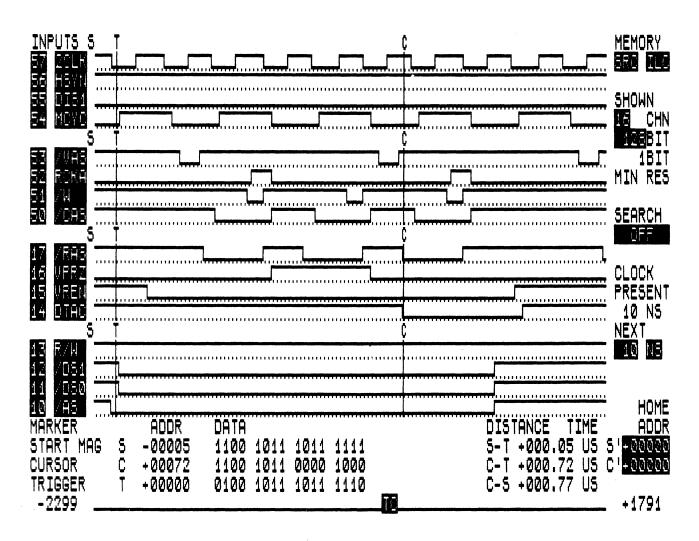

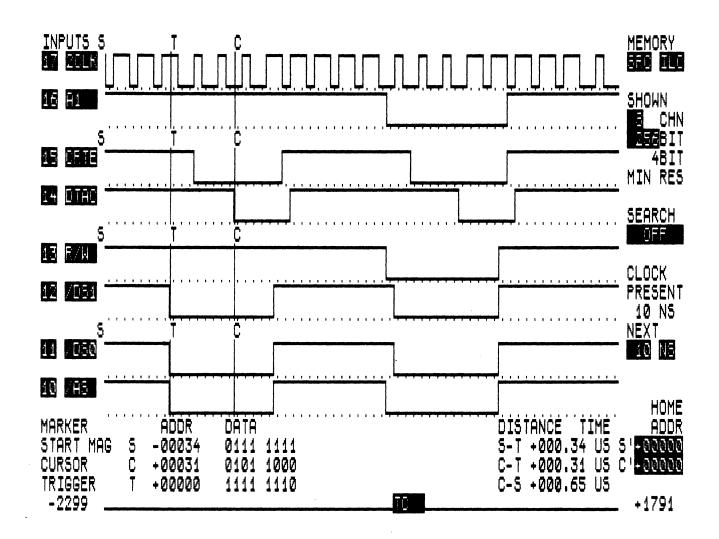

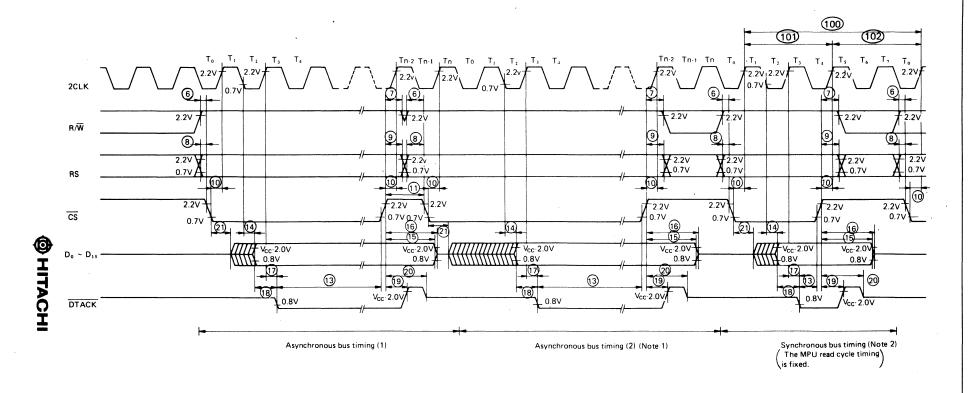

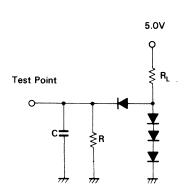

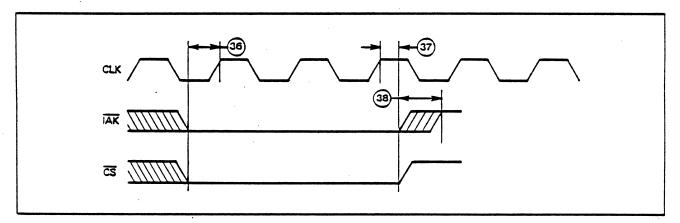

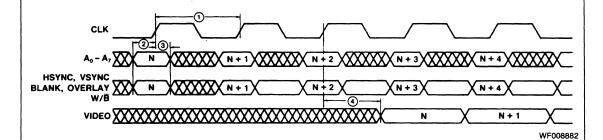

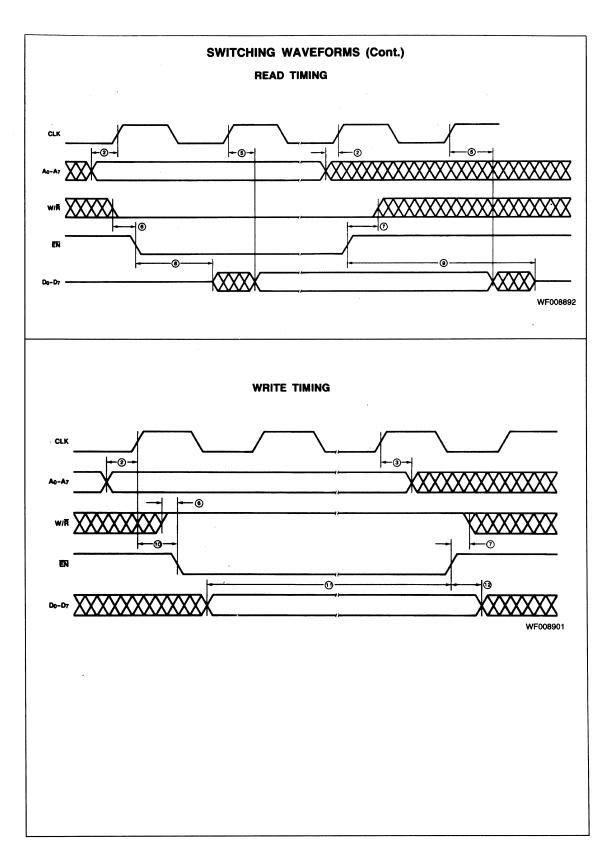

Figure 4-5 shows the timing diagram of an access to the colour look-up table access.

This page is intentionally left blank.

Figure 4-5: Access to the Colour Look-up Table

READ CYLE FOLLOWED BY WRITE CYCLE

| Characteristics                        | <br>  min.<br>  | max.  |

|----------------------------------------|-----------------|-------|

| AS low to DTACK low                    | <br>  250ns<br> | 310ns |

| DS low to DTACK low                    | <br>  230ns<br> | 290ns |

| AS low to GCPEN1 low                   | <br>  110ns<br> | 150ns |

| DS low to GCPEN1 low                   | <br>  110ns<br> | 150ns |

| Access Cycle Time AS low to DTACK high | 510ns           | 630ns |

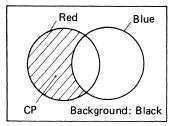

#### 4.6.1 Colour Switch Mode

In the 4 bit/pixel mode the look-up tables can be switched in the horizontal retrace period (see Chapter 4.9.8). By doing this it is possible to display 256 different colours in one picture using the 4 bit mode. The restriction is that only one colour look-up table set-up per line can be used. The switching is done by setting the attribut bits  $\emptyset$ -3 in the Display Control Register of the ACRTC to 1 (see Chapter 4.9.6).

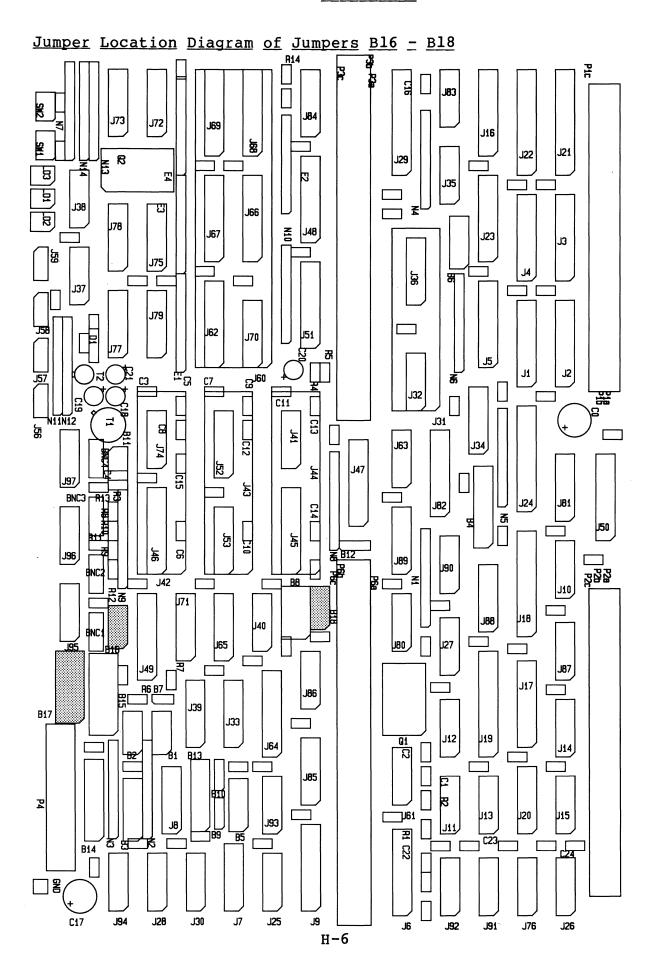

This switch colour mode can be chosen by the jumper settings of B18.

Fig. 4-6 shows the jumper location on the board.

Table 4-8 gives the correct jumper settings.

Figure 4-6: Jumper Location Diagram of Jumperfield B18

## Table 4-8: Jumper Settings of Bl8 (SCM)

- a)  $SCM = \emptyset$

- Number of tables = 1

DEFAULT

- 1 8 2 7 3 6

- b) SCM=1

- Number of tables = 2

- 1 8 2 7 3 6 4 -- 5

- c) SCM = 2

- Number of tables = 4

- d) SCM=3

- Number of tables = 8

e) SCM = 5

Number of tables = 16

#### 4.6.2 Blink Switch Mode

In this mode the Blink Feature of the ACRTC is supported (see Chapter 4.9.14). Depending on the Blink Mode of the ACRTC the Colour Look-up table is switched and so certain symbols or areas of the frame may appear in another colour. This feature can be used in the 4 bit/pixel mode. In the 8 bit/pixel mode the number of bits/pixel will be reduced respectively (see Chapter 4.9.6).

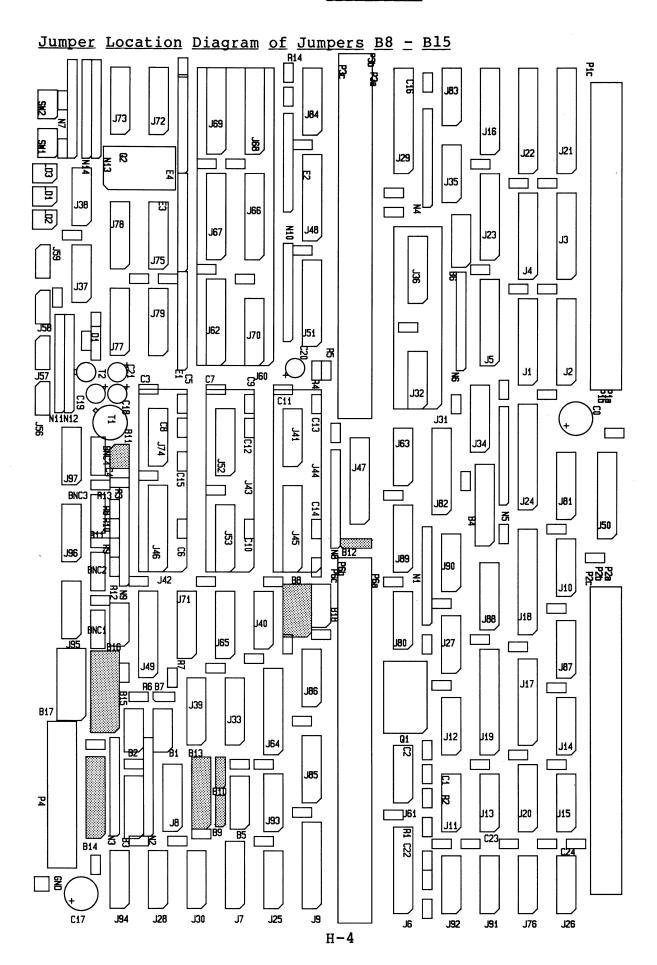

The Blink Switch Mode is enabled through the jumper settings of B8.

Fig. 4-7 shows the jumper location on the board.

Table 4-9 gives the correct jumper settings.

Figure 4-7: Jumper Location Diagram of B8 (Blink Switch Mode)

## Table 4-9: Jumper Settings of B8 (BCM)

a)  $BCM = \emptyset$

| BLINKl  | disabled |

|---------|----------|

| BLINK 2 | disabled |

- 1 -- 2 3 4 -- 5 6 7 8 9 10 -- 11 12 13 -- 14 15

- c) BCM = 2

BLINK1 disabled BLINK2 enabled

b) BCM=1

BLINK1 enabled BLINK2 disabled

- 1 2 -- 3 4 -- 5 6 7 8 9 10 -- 11 12 13 -- 14 15

- d) BCM=1

BLINK1 enabled BLINK2 enabled

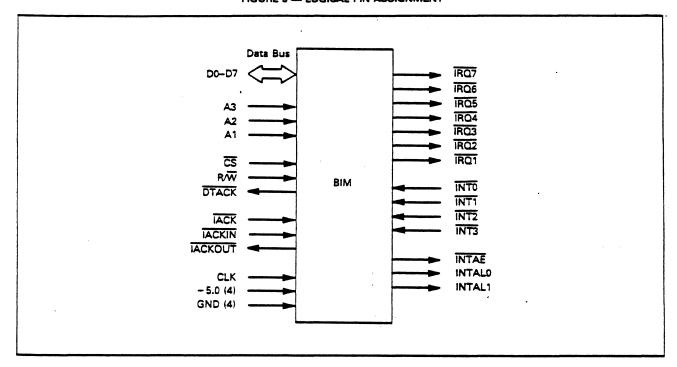

#### 4.7.1 Interrupt Structure of the SYS68K/AGC-1

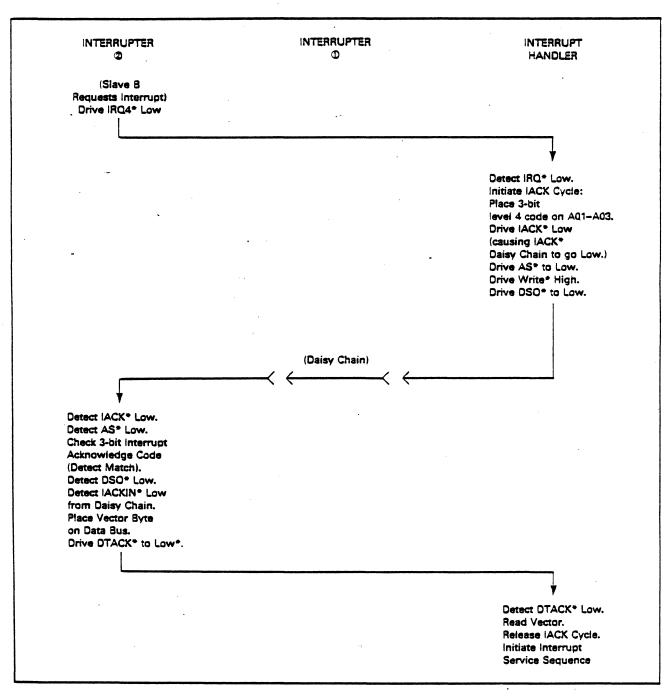

The VMEbus supports interrupting with seven interrupt request lines IRQ1-IRQ7. The seven lines represent seven interrupt request levels. IRQ1 has the lowest priority, IRQ7 has the highest. More than one board can access the same IRQ line at the same time, one board may request interrupts on several levels simultaneously.

When the interrupt handler enters the interrupt acknowledge cycle to honour an interrupt request, it asserts the /IACK line, puts the level code on the address lines Al-A3 and drives /AS low.

The interrupters have to decide which one has been acknowledged by the interrupt handler.

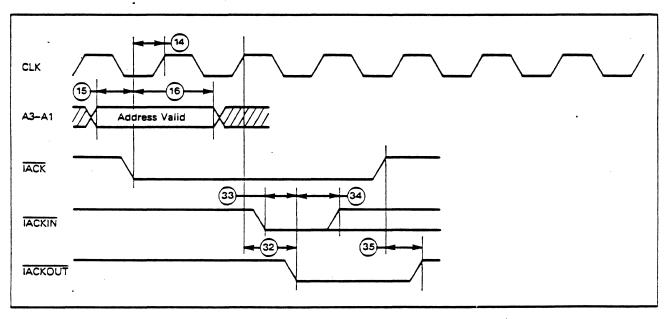

The VMEbus defines a Daisy Chain structure for the interrupters. Each interrupter has an /IACKIN and an /IACKOUT pin. The /IACKOUT pin of a slot is connected to the /IACKIN pin of the next slot on the motherboard. When the board has an interrupt pending on the level being acknowledged, it puts the Interrupt Vector onto the data bus and asserts the /DTACK line. The interrupt acknowledge cycle terminates when the interrupt handler clears the /AS line.

When an interrupter receives the /IACKIN input signal, and does not have an interrupt pending on the level being acknowledged, it asserts its /IACKOUT output signal.

The SYS68K/AGC-1 board can drive an interrupt request on each of the 7 IRQ lines of the VMEbus. Several lines may be asserted simultaneously.

Interrupt requests can be generated by the status report of the ACRTC as well as on the VSYNC phase of the display.

By the last for example, it is possible to load new colour look-up-tables during the vertical retrace period so as to avoid a `flashing' display.

The two not used channels of the BIM are reserved for expansion with the SYS68K/AGC-1X board.

The interrupt level and the interrupt vector is software programmable for both interrupts.

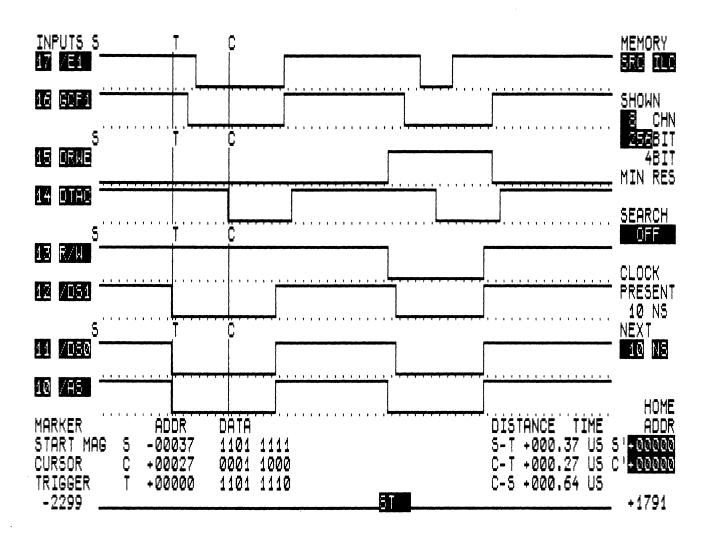

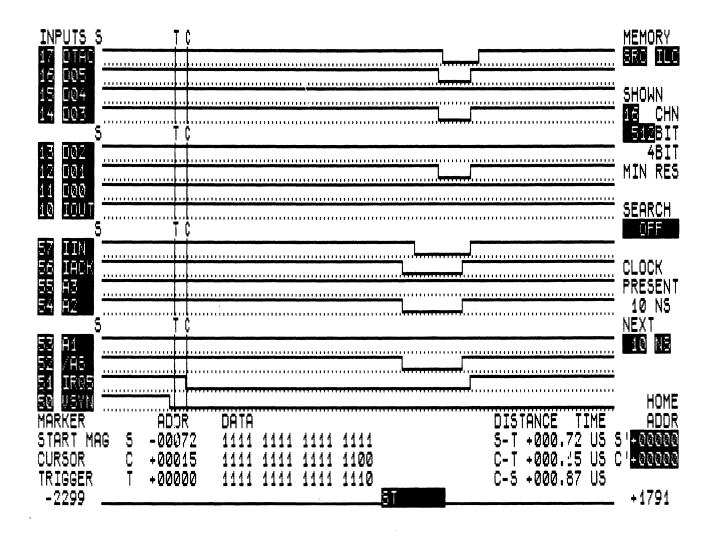

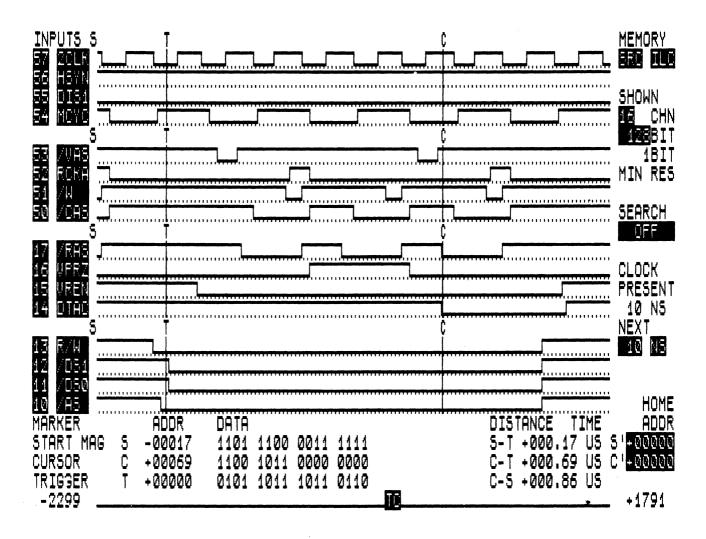

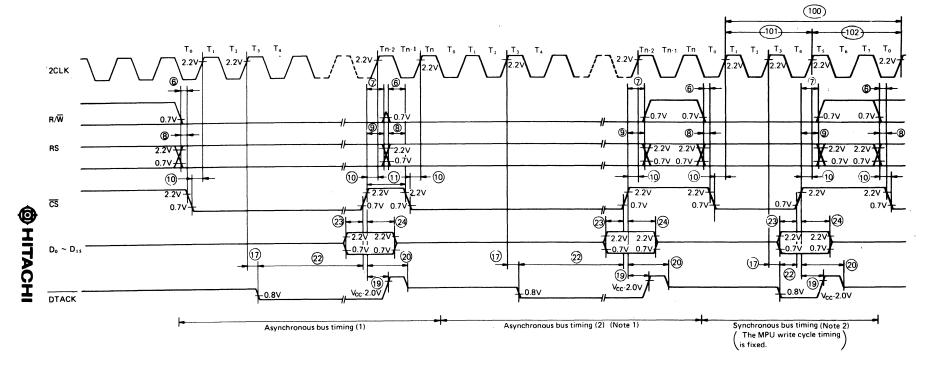

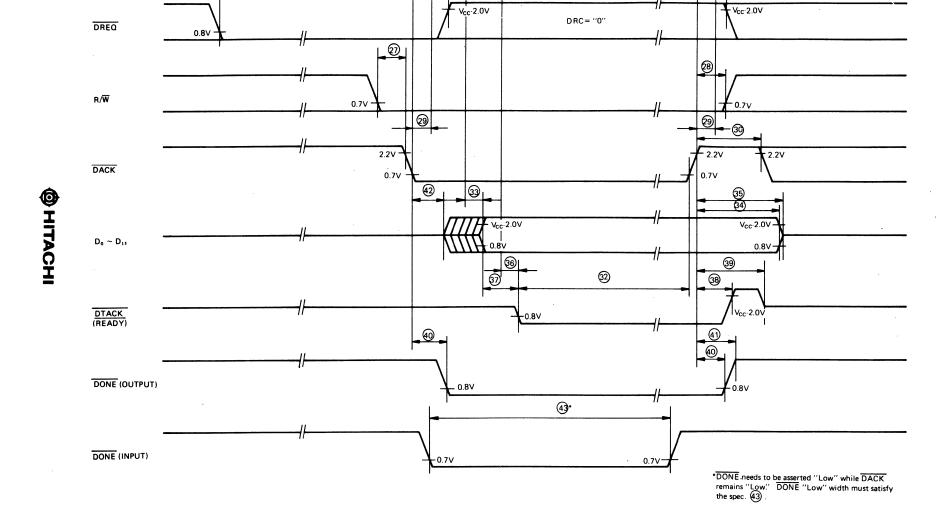

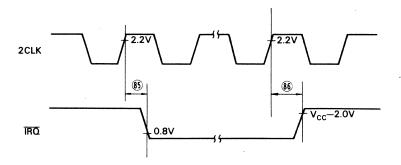

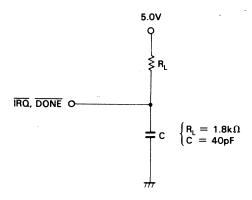

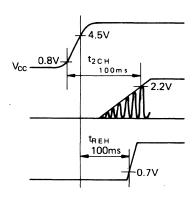

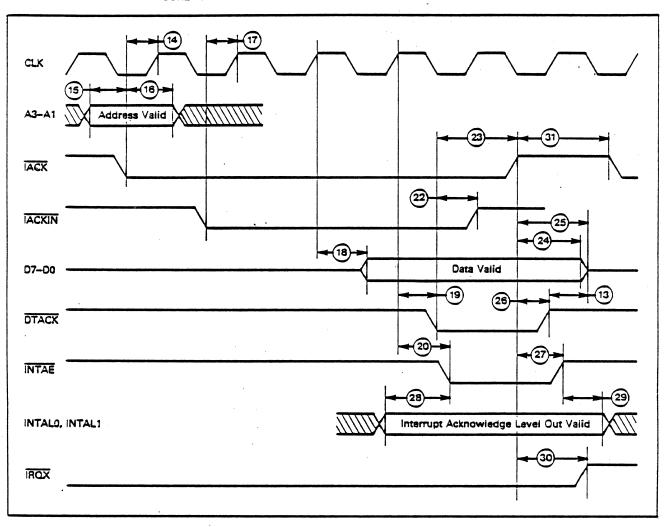

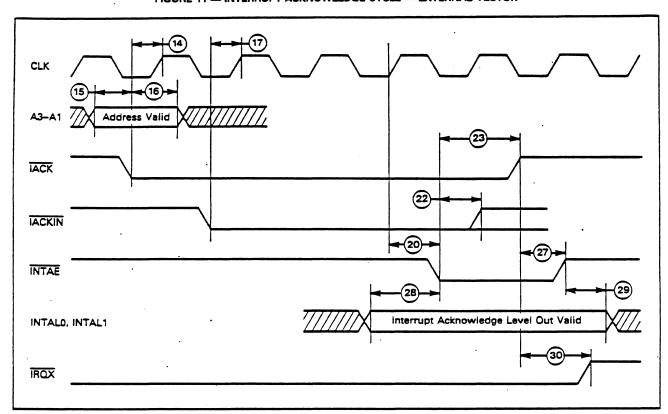

Figure 4-8 shows the BIM access timing diagram.

Figure 4-9 shows the Interrupt request timing.

Figure 4-8: Access to the BIM 68153

READ CYCLE FOLLOWED BY WRITE CYCLE

Table 4-10: Access Times for a Read Cycle to the BIM 68153

| <br>  Characteristics<br>                             | <br>  min.<br>  | max.  |

|-------------------------------------------------------|-----------------|-------|

| AS low to DTACK low                                   | <br>  260ns<br> | 300ns |

| DS low to DTACK low                                   | <br>  230ns<br> | 270ns |

| AS low to BIMEN low                                   | <br>  90ns      | 110ns |

| DS low to BIMEN low                                   | 70ns            | 90ns  |

| READ Cycle Time AS low to DTACK high                  | 58Øns           | 640ns |

| <br>  WRITE Cycle Time<br> <br>  AS low to DTACK high | 570ns           | 590ns |

Figure 4-9: Interrupt Cycle Timing of the BIM 68153

VSYNC REQUESTS FOR INTERRUPT

Table 4-11: Access Times of a Interrupt Acknowledge Cycle

Characteristics min. max. VSYNC low to IRQ low | 150ns | 180ns IACK low to DTACK low 370ns 430ns IACKIN low to DTACK low | 250ns | 270ns IACK low to IRQ high 650ns 710ns IACKOUT high to AS high | 10ns 20ns IACK Cycle Time 730ns 790ns IACK low to DTACK high |

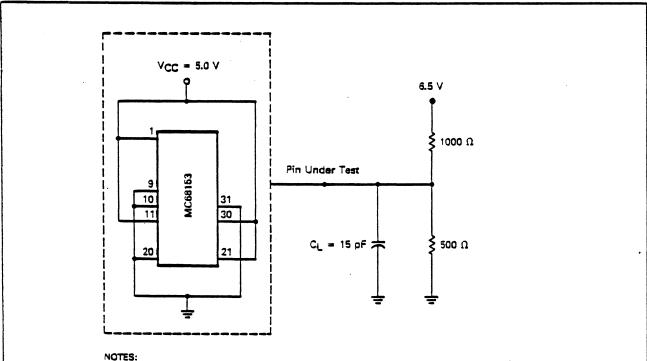

#### 4.7.2 Programming the BIM (68153) on the SYS68K/AGC-1

The Bus Interrupter Modul (BIM) on the board transmits Interrupt Request Signals of the ACRTC and the VSYNC signal to the VMEbus.

The reset state of the BIM blocks all interrupting activity from the board to the VMEbus. The initialisation allows the software selection of the interrupt level for each interrupt signal individually. The interrupt vector is supplied by the BIM and therefore the BIM Control Register have to be programmed for internal vector generation.

The BIM is accessed word by word, but only the lower 8 data bits contain the register values, the upper bits are always \$FF.

Table 4-12 shows the address locations of the respective registers.

Please refer to the Data Sheet of the BIM 68153 for programming the control and vector registers.

Table 4-12: Address Location of the BIM 68153

| <br>  BBA + \$0000     | CONTROL REGISTER 1 | reserved        |

|------------------------|--------------------|-----------------|

| BBA + \$0002           | CONTROL REGISTER 2 | ACRTC Interrupt |

| BBA + \$0004           | CONTROL REGISTER 3 | VSYNC Interrupt |

| <br>  BBA + \$0006     | CONTROL REGISTER 4 | reserved        |

| BBA + \$0008           | VECTOR REGISTER 1  | reserved        |

| <br>  BBA + \$000A     | VECTOR REGISTER 2  | ACRTC           |

| BBA + \$000C           | VECTOR REGISTER 3  | VSYNC           |

| <br>  BBA + \$000E<br> | VECTOR REGISTER 4  | reserved        |

#### 4.8 Adressing the Video Memory

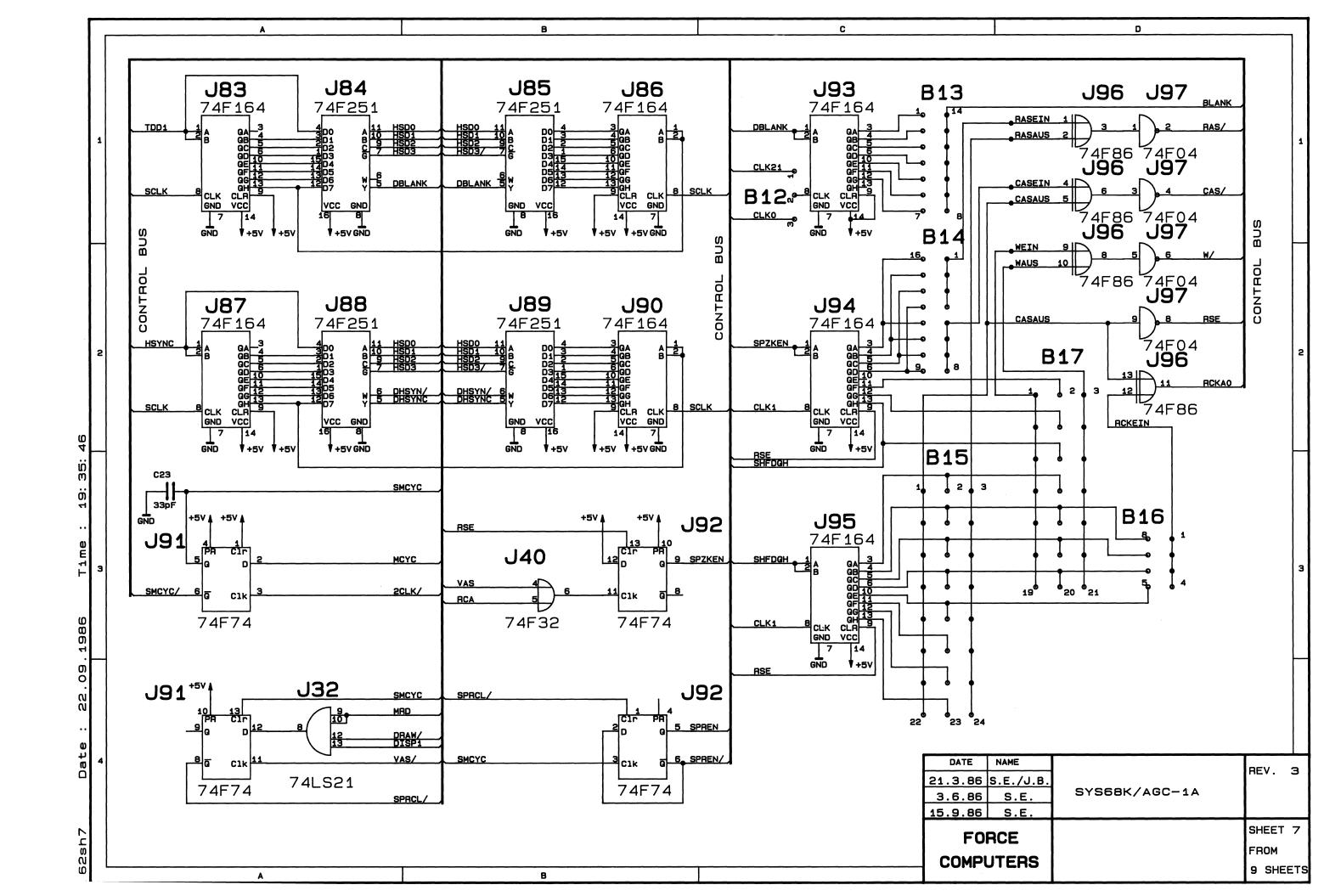

The Video Memory consists of 2M Byte contigous dynamic Memory. The correct RAS-, CAS- and WRITE- Timing is selected through the jumper settings of Bl4, Bl5, Bl6, Bl7. All jumper settings of this jumperfield must not be modified.

The correct jumper settings are given in Table 4-11.

The memory organisation is word by word, but byte accesses are although possible. Depending on the chosen pixel mode, up to 4 pixel can be modified with one Read-Modify-Write Access.

The video memory is accessible in two ways via the ACRTC or direct via the VMEbus interface.

The access through the ACRTC is always possible, the access via the VMEbus is only supported if the board is jumpered for Standard Memory Access and the Video Memory is not blanked out (see Chapter 4.1).

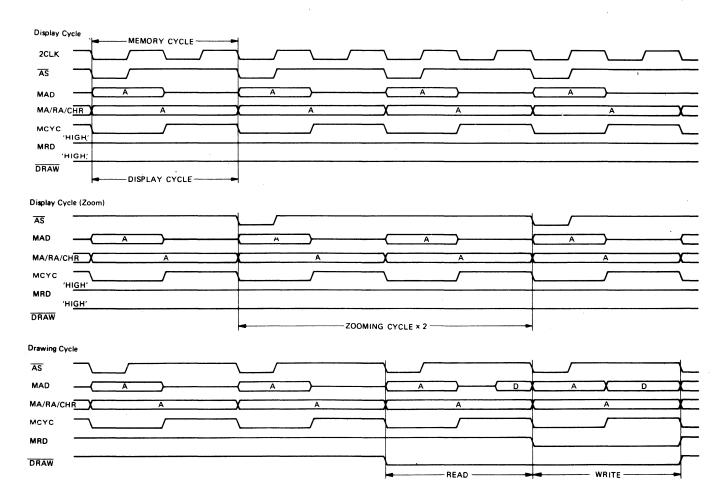

The implementation of the DUAL ACCESS MODE (see hardware manual ACRTC 63484) together with the `dual port` mechanism of the video RAM avoids a `flickering` display when there are accesses during the display period.

The video memory area is located at address BBA + \$40000.

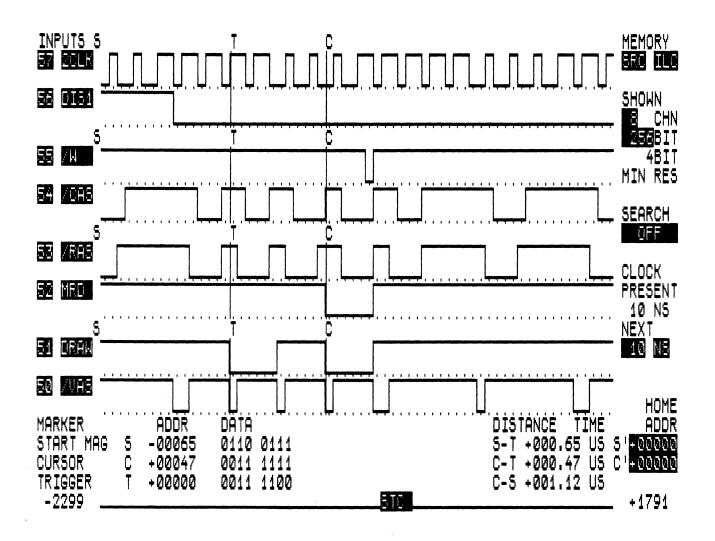

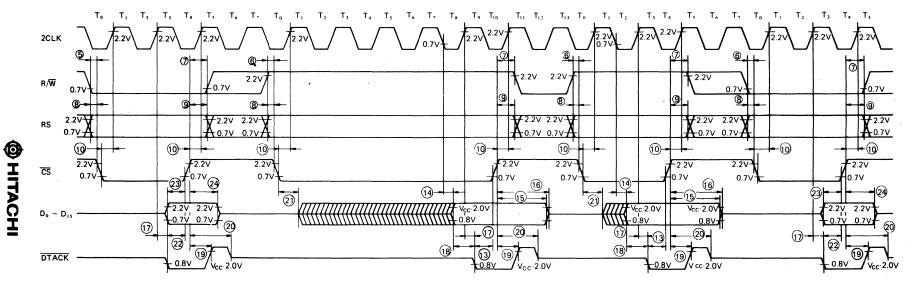

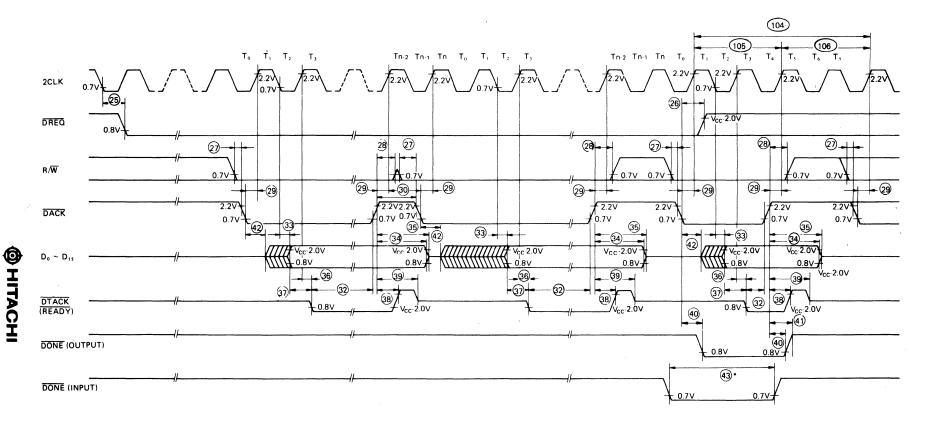

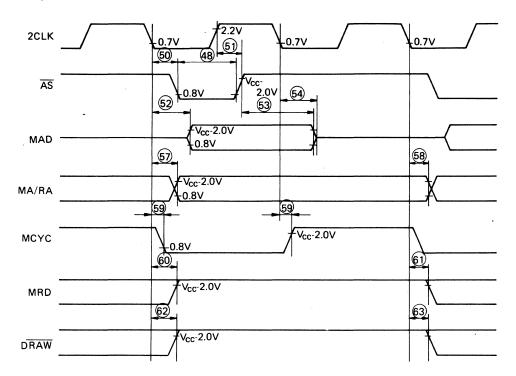

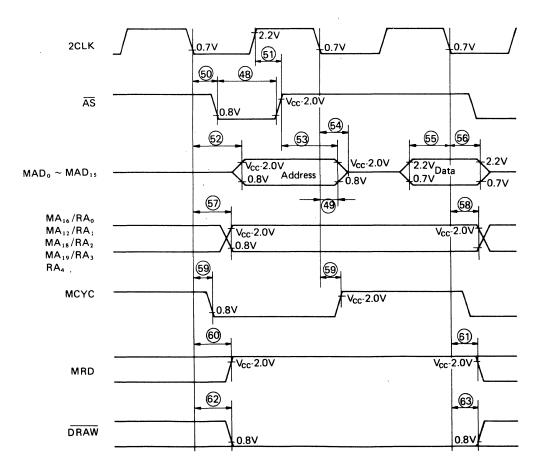

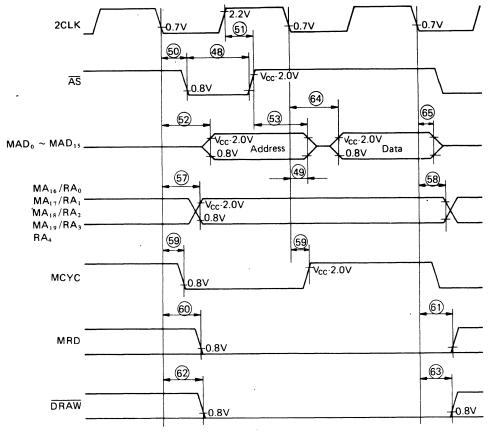

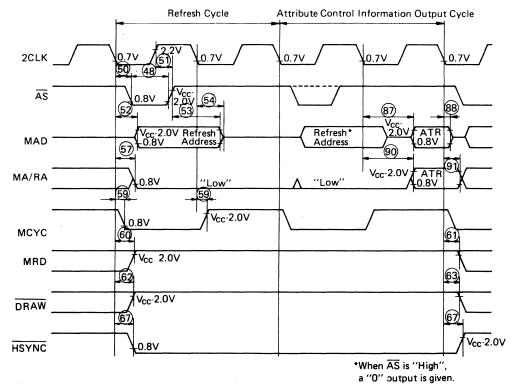

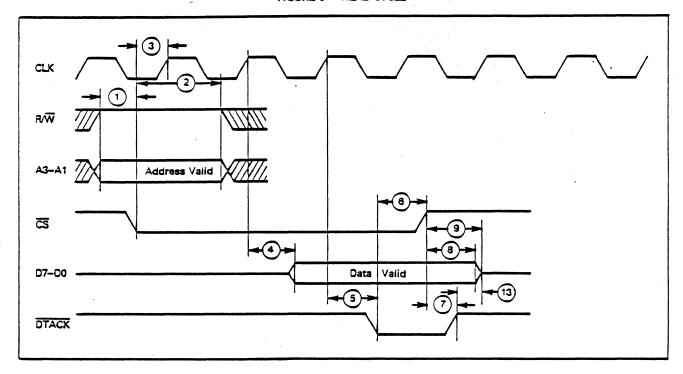

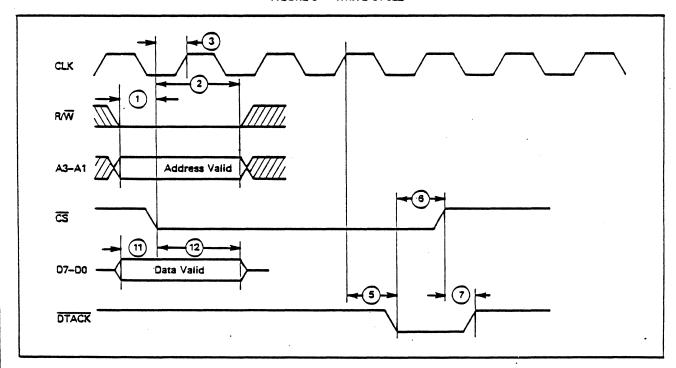

Fig. 4-10A and B shows the timing for the VMEbus access and Table 4-13A and B lists the time values.

The timing for the ACRTC access is shown in Fig.4-11 and the corresponding time values are outlined in Table 4-14.

Fig. 4-12 shows the jumper locations of Bl4, Bl5, Bl6 and Bl7.

Table 4-15 lists the correct jumper settings.

Figure 4-10: VMEbus Access to the Video RAM READ CYCLE

Table 13A: Time Values of a Video RAM Read Cycle

| Characteristics                               | <br>  min.<br>    | <br>  max.   |

|-----------------------------------------------|-------------------|--------------|

| AS low to DTACK low                           | <br>  750ns<br>   | <br>  1000ns |

| DS low to DTACK low                           | <br>  730ns<br>   | <br>  980ns  |

| AS low to RAS low                             | <br>  480ns<br>   | 700ns        |

| DS low to RAS low                             | <br>  460ns<br>   | 680ns        |

| READ Cycle Time<br>  AS low to DTACK high<br> | <br> <br>  1020ns | 1330ns       |

Figure 4-10: VMEbus Access to the Video RAM WRITE CYCLE

Table 4-13B: Time Values of a Video RAM Write Cycle

| Characteristics                                       | <br>  min.<br>  | max.         |

|-------------------------------------------------------|-----------------|--------------|

| AS low to DTACK low                                   | <br>  700ns<br> | 1180ns       |

| DS low to DTACK low                                   | <br>  680ns     | 1160ns       |

| AS low to RAS low                                     | 700ns           | <br>  1140ns |

| DS low to RAS low                                     | 68Øns           | 1120ns       |

| <br>  WRITE Cycle Time<br> <br>  AS low to DTACK high | 1010ns          | 1250ns       |

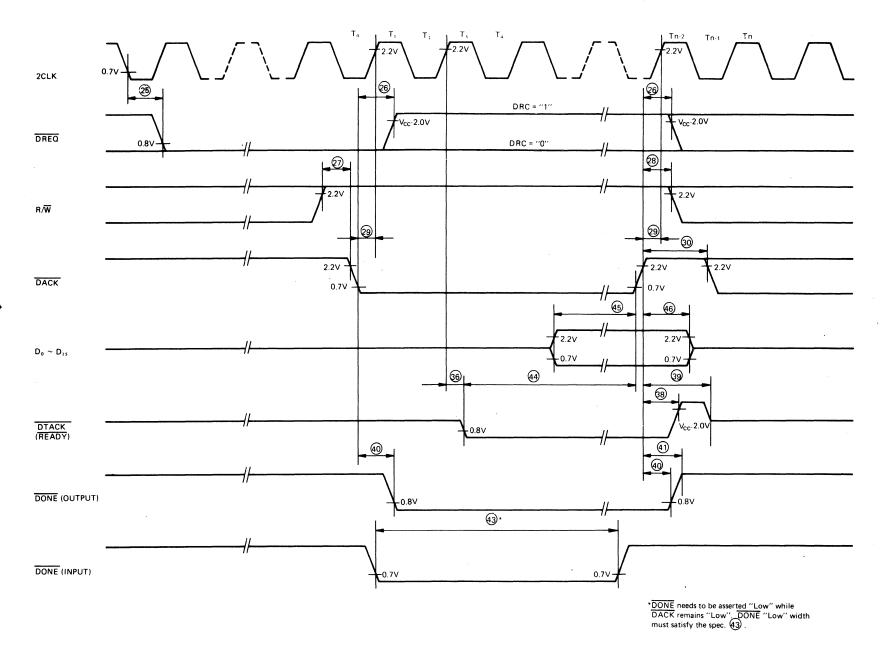

Figure 4-11: ACRTC Drawing Access to the Video RAM

READ-MODIFY-WRITE CYCLE

Table 4-14: Time Values of A ACRCT Drawing Cycle to the Video RAM

| Characteristics                | <br>  min.<br> | max.        |

|--------------------------------|----------------|-------------|

| VAS low to RAS low             | <br>  30ns<br> | <br>  60ns  |

| VAS low to CAS low             | <br>  50ns     | <br>  100ns |

| RAS low to CAS low             | <br>  20ns     | 40ns        |

| CAS low to WRITE low           | 90ns           | <br>  110ns |

| <br>  WRITE Pulse Duration<br> | 30ns           | 60ns        |

| RAS Recovery Time              | <br>  70ns     | <br>  120ns |

| RMW Cycle Time                 | 710ns          | 73Øns       |

Figure 4-12: Jumper Locations Diagram of B14, B15, B16 AND B17

# Table 4-15: Jumper Settings of Bl4, Bl5, Bl6 AND Bl7

| JUMPER  | B14       | Jt | JMPER 1 | 315       |

|---------|-----------|----|---------|-----------|

| DEFAULT | CONDITION | DI | EFAULT  | CONDITION |

| 1       | 16        | 1  | 2       | 3         |

| 2       | 15        | 4  | 5       | 6         |

| 3       | 14        | 7  | 8       | 9         |

| 4       | 13        | 10 | 11      | 12        |

| 5       | 12        | 13 | 14      | 15        |

| 6       | 11        | 16 | 17      | 18        |

| 7       | 10        | 19 | 20      | 21        |

| 8       | 9         | 22 | 23      | 24        |

|         |           |    |         |           |

| JUMPER  | B16       | JU | JMPER 1 | 317       |

| DEFAULT | CONDITION | DE | EFAULT  | CONDITION |

| 1       | 8         | 1  | 2       | 3         |

| 2       | 7         | 4  | 5       | 6         |

| 3       | 6         | 7  | 8       | 9         |

| 4       | 5         | 10 | 11      | 12        |

|         |           | 13 | 14      | 15        |

|         |           | 16 | 17      | 18        |

|         |           | 19 | 20      | 21        |

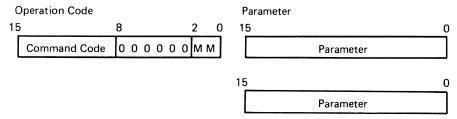

#### 4.9 Addressing the ACRTC 63484

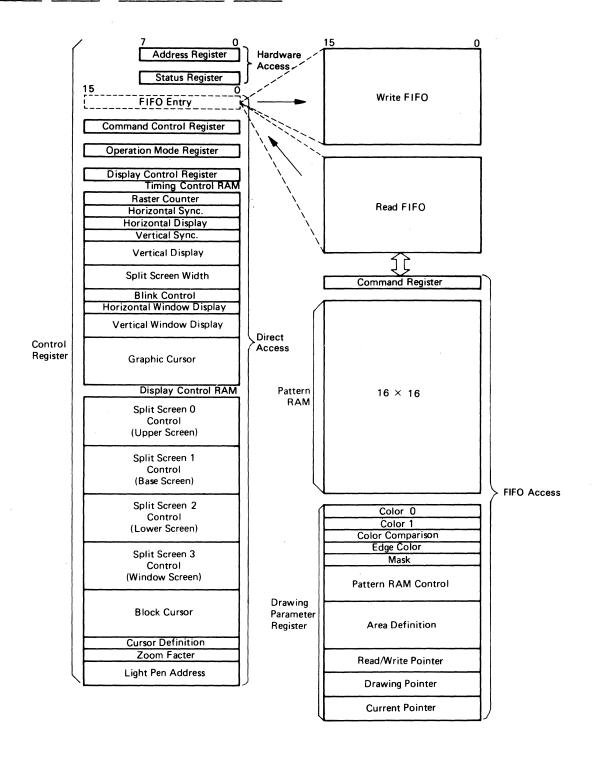

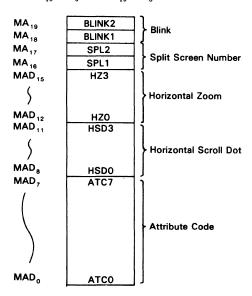

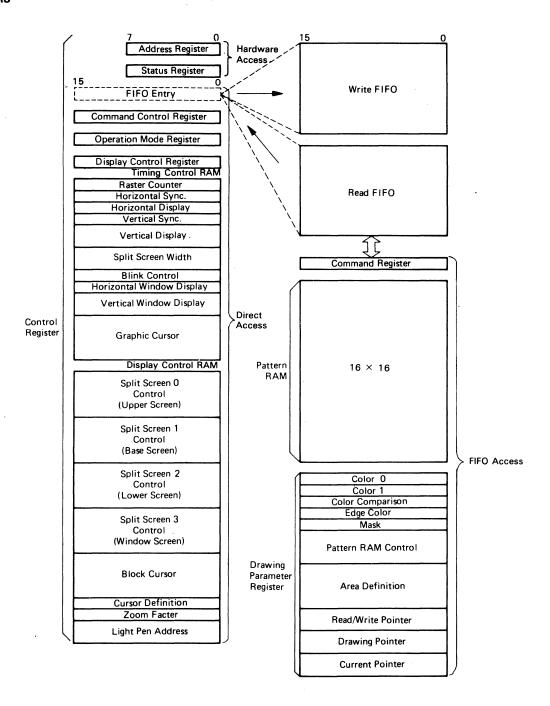

The ACRTC incorporates more than 200 byte of internal control registers and control RAM which is accessible by the host processor.

There is a distinction between two ways of accessing these registers. At first there are the direct addressable registers, the STATUS Register, the ADDRESS Register and the FIFO ENTRY. The STATUS and the ADDRESS register are distinguished by the R/W-Signal. The Status register is read-only and the Address registers are write only. The addresses of these registers are located at address BBA + \$3C000 for Standard Memory access (see Chapter 4-1).

The second group are the indirect addressable registers, which are partioned in two groups.

#### a) Directly Accesible Register

These registers are accessed by writing the register address into the ADDRESS register and reading and writing the data over the FIFO ENTRY.

#### b) FIFO Accessible Register

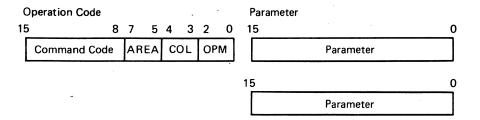

These registers are accessed by writing the FIFO address (\$00) into the ADDRESS register. After operation, the READ or WRITE PARAMETER REGISTER command with the respective register address written into the FIFO.

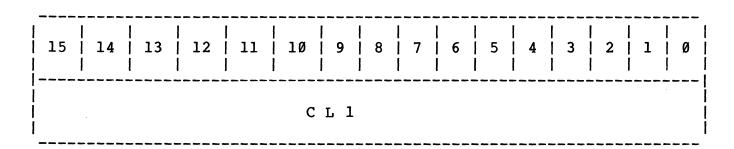

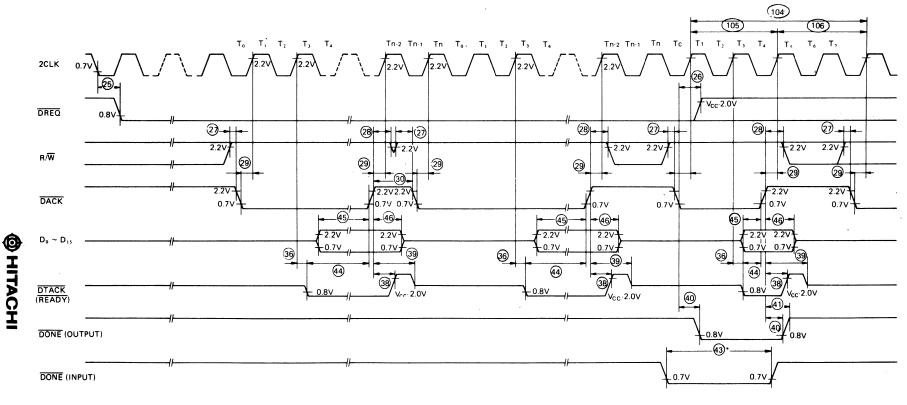

The programming model is shown in Table 4-16 and the time values are listed in Table 4-16.

Figure 4-13 shows the access timing from the VMEbus to the 63484 ACRTC.

For the detailed register descriptions in this chapter, the following terminology is used.

For directly accessible registers, the register address is shown as `rNN` where NN is interpreted as an 8 bit hexadecimal value. For example, the Zoom Factor register address is \$EA hexadecimal, so the ZFRs register address is shown as `rEA`.

For FIFO accessible Drawing Parameter registers, the register address is shown as `PrNN`. For example, the Colour Comparison register is addressed as parameter register \$2 hex, so the CMP register address is shown as `Pr02`.

When register diagrams are shown, unused bits will be marked with X. Unless stated otherwise, unused bits may be freely written with any value, and that value will be returned on subsequent reads of the register.

Table 4-16: PROGRAMMING MODEL

Table 4-16: (con't) Programming Model

| cs  | RS  | RW                | Reg.              | Re        | gister Name    | Abbre. | 1,5          |             |           | DATA      |            | 1.0    |    | Ι.,     |     |            |           | (L)  |       | , ,  | _   |  |

|-----|-----|-------------------|-------------------|-----------|----------------|--------|--------------|-------------|-----------|-----------|------------|--------|----|---------|-----|------------|-----------|------|-------|------|-----|--|

| _   | ļ   | H                 | No.               | ļī        | -              |        | 15           | 14          |           |           | 11 10      | 9      | 8  | 7       | 6   | 5          | 4         | 3    | 2     | 1    | 0   |  |

| 1   | 0   | -                 | - AD              | Addre     | Register       | AR.    |              |             |           |           |            |        |    |         |     |            | 4.2       |      |       |      |     |  |

| _   | 0   |                   |                   | Status I  |                | SR     |              |             |           |           |            |        |    | CEDI    | 400 | JOED       |           | ress | 050   | WED) | MIC |  |

| ч   | -   | 1/0               |                   | FIFO E    |                | FE     | ├            |             |           |           |            |        |    | E       | ARL | CED        | LPU       | KFF  | RFR   | MLK  | WI  |  |

| - 1 |     | 1/0               |                   |           | nd Control     | CCR    | ADT          | Dec         | DOM       | CDM       | DPC        | GBM    |    |         | ADE | CEE        | I DC      | DEE  | DDE   | WDE  | WE  |  |

|     |     | 1.0               |                   | Operation |                | OMR    |              |             |           |           |            |        |    |         |     |            | LPE       |      |       |      |     |  |

| ĺ   |     | 1/6<br>1/6        |                   | Display   |                | DCR    |              | SE1         |           | WSS<br>E0 | CSK<br>SE2 |        | SK | RAM     |     | GAI        |           | T R  | ,IVI  | RSM  |     |  |

|     |     | -                 | r08               | (undefin  |                | -      | USF          | SEI         |           | -0        |            |        | E3 |         |     |            |           |      |       |      |     |  |

| ì   |     | 1                 |                   | Raster    |                | RÇR    |              |             |           |           |            |        |    |         | R C |            |           |      |       |      |     |  |

| 1   |     | 1, ö              | r82               | Horizont  | al Sync.       | HSR    |              |             |           | Н         | С          |        |    |         |     |            |           |      | HSV   | /    |     |  |

| 1   |     |                   | r84               | Horizont  | al Display     | HDR    |              | HDS HDW     |           |           |            |        |    |         |     | O W        |           |      |       |      |     |  |

| - 1 |     | 1,0               | r86               | Vertical  | Sync.          | VSR    |              | v c         |           |           |            |        |    |         |     |            |           |      |       |      |     |  |

| 1   |     | 1/0               | r88               | Vertical  | Display        | VDR    |              |             |           |           |            |        |    |         |     | VSV        | 7         |      |       |      |     |  |

|     | i   | l,o<br>l,o<br>l,ó | r8A<br>r8C<br>r8E | Split Sc  | reen Width     | ssw    |              |             |           |           |            |        |    | S       | P   | )          |           |      |       |      | _   |  |

|     |     | > 0<br>1√0        |                   | Blink Co  |                | BCR    |              | BO          |           |           | - D        | DFF1   |    |         |     | 2<br>0N2   |           |      | BOF   |      |     |  |

|     |     |                   | r92               |           |                | HWR    |              | ВО          | 14.1      | ни        |            | Jr F I |    |         | В   | JNZ        | <u> </u>  | w w  | BUI   | r Z  |     |  |

| - 1 |     | 1/0               | r94               | Horizonta | Window Display | HWK    |              |             |           | H V       | 15         |        |    | l       |     | W W 0      |           | N W  |       |      |     |  |

|     |     | 1.0               |                   | Vertical  | Window Display | VWR    |              | • • • • • • |           |           |            |        |    |         |     | V W S      |           |      |       |      |     |  |

| İ   |     | 1/0               | r96               |           |                |        | -            |             | • • • • • |           |            |        |    |         |     | V W W      |           |      |       |      |     |  |

| 1   |     |                   | r98               |           | _              |        |              |             |           | C X       |            |        |    |         |     |            |           |      |       | _    |     |  |

| - 1 |     | 1/0               |                   | Graphic   | Cursor         | GCR    | C Y S        |             |           |           |            |        |    |         |     |            |           |      |       |      |     |  |

| 1   |     | 1,0               | r9C               |           |                |        | C Y E        |             |           |           |            |        |    |         |     |            |           |      |       |      |     |  |

|     |     | -                 | r9E<br>rA0<br>rBE | (undefin  | ed)            | -      |              |             |           |           |            |        |    |         |     |            |           |      |       |      |     |  |

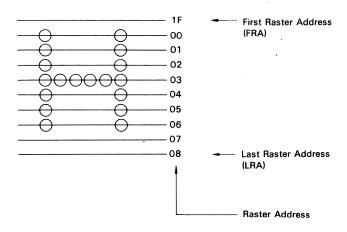

| 0   | 1   | 1.0               | rCO               |           | Raster Addr. 0 | RARO   | <del>†</del> |             |           | LRAO      |            |        |    |         |     |            | F         | RA   | 0     |      |     |  |

| ١,  | 1   | 1. 0              | rC2               | Upper     | Memory Width 0 | MWRO   | CHR          | R           |           |           |            |        |    | 4       | М   | W O        |           |      |       |      |     |  |

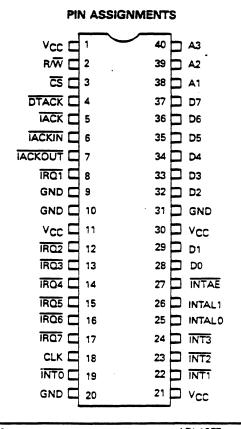

| - 1 |     |                   |                   | Screen    |                |        |              |             |           |           | S I        | ) A 0  |    |         |     |            | SAOH SRAO |      |       |      |     |  |