# FUJITSU SCIENTIFIC & TECHNICAL JOURNAL

# Spring 1991 VOL. 27, NO. 1

#### The Issue's Cover: Fluctuation by Hirofumi OHKUMA

In quantum mechanics, at any given time, particles existing in a small area have an equal probability of being found at any of their possible locations and are traveling at various speeds. Particles are in constant random motion.

FUJITSU Scientific & Technical Journal is published quarterly by FUJITSU LIMITED of Japan to report the results of research conducted by FUJITSU LIMITED, FUJITSU LABORATORIES LTD., and their associated companies in communications, electronics, and related fields. It is the publisher's intent that FSTJ will promote the international exchange of such information, and we encourage the distribution of FSTJ on an exchange basis. All correspondence concerning the exchange of periodicals should be addressed to the editor.

FSTJ can be purchased through KINOKUNIYA COMPANY LTD., 3-17-7 Shinjuku, Shinjuku-ku, Tokyo 160-91, (Telex No. 2424344, answerback KINOKUNI J).

The price is US \$7.00 per copy, excluding postage.

FUJITSU LIMITED reserves all rights concerning the republication and publication after translation into other languages of articles appearing herein.

Permission to publish these articles may be obtained by contacting the editor.

| FUJITSU LIMITED           | Tadashi Sekizawa, President |

|---------------------------|-----------------------------|

| FUJITSU LABORATORIES LTD. | Masaka Ogi, President       |

**Editorial Board**

EditorTakahiko MisugiAssociated EditorsShigeru SatoHideo TakahashiEditorial Representatives

Editorial Representatives

Tadashi Hasegawa Yoshimasa Miura Makoto Mukai Hajime Nonogaki Yasushi Nakajima Seiya Ogawa Hirofumi Okuyama Shinji Ohkawa Shinya Okuda Tohru Sato Yoshio Tago Shozo Taquchi Hirobumi Takanashi Mitsuhiko Toda Jyun'ichi Tanahashi Yutaka Yamaoka Toru Tsuda Itsuo Umebu Akira Yoshida

#### **Editorial Coordinator**

Kazuo Yono

FUJITSU LIMITED 1015 Kamikodanaka, Nakahara-ku, Kawasaki 211, Japan Cable Address: FUJITSULIMITED KAWASAKI Telephone: +81-44-777-1111 Facsimile: +81-44-754-3562

Printed by MIZUNO PRITECH Co., Ltd. in Japan © 1991 FUJITSU LIMITED (April 25, 1991)

# FUĴÎTSU

### SCIENTIFIC & TECHNICAL JOURNAL

Spring 1991 VOL.27, NO.1

#### CONTENTS

#### SYNOPSES (Reviews)

UDC 538.945:621.3.049.771 FUJITSU Sci. Tech. J., **27**, 1, pp. 1-27(1991)

Josephson Integrated Circuits I Fabrication Technology

• Takeshi Imamura

This paper reviews the fabrication technology developed for Josephson integrated circuits and describes the techniques used in the standard process for various circuit elements including Nb/AlO<sub>x</sub>/Nb junctions. These process techniques were verified based on the characteristics of the 8K-bit cell array chips fabricated for process evaluation as being applicable to Josephson circuits that include several thousand junctions. Without the process technology based on the reliable Nb/AlO<sub>x</sub>/Nb junctions, the recently demonstrated ultrahigh-speed operation of Josephson integrated circuits would not have been possible. This paper also introduces advanced process techniques developed for future Josephson LSI application.

#### UDC 538.945:621.3.049.771

FUJITSU Sci. Tech. J., 27, 1, pp. 28-58(1991)

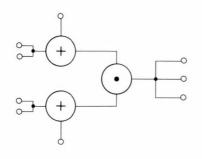

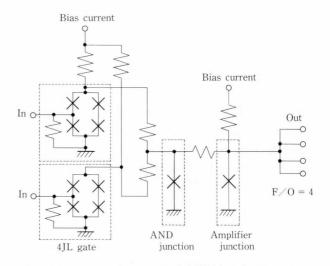

## Josephson Integrated Circuits II High-Speed Digital Circuits

Shinya Hasuo

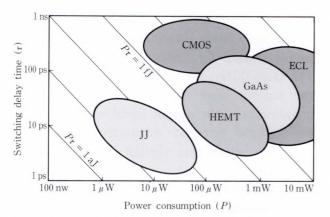

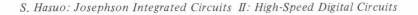

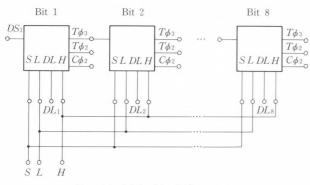

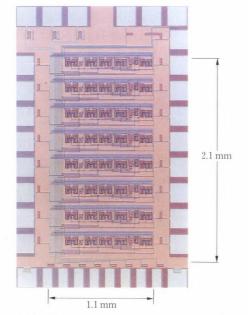

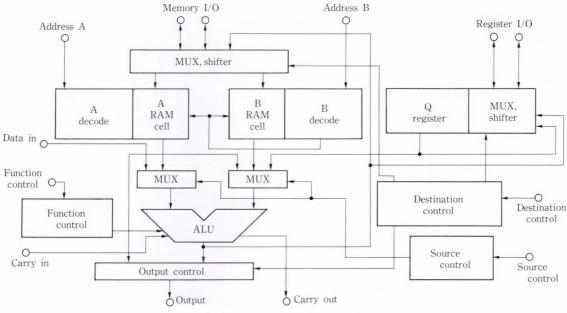

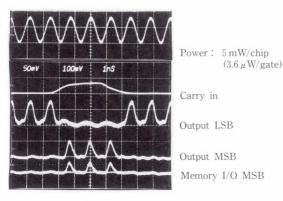

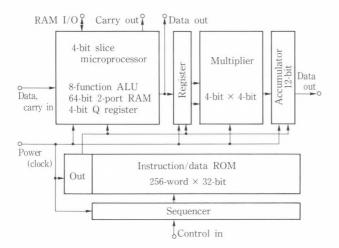

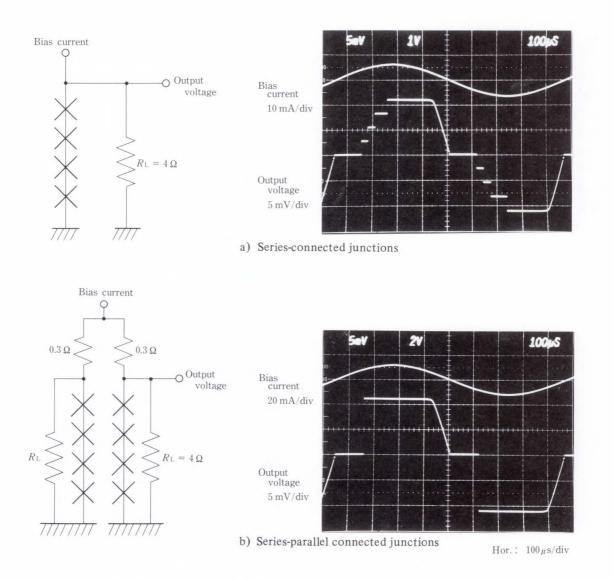

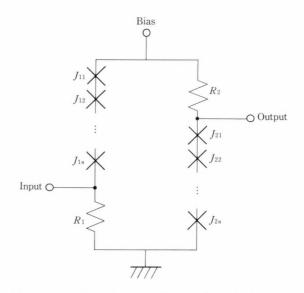

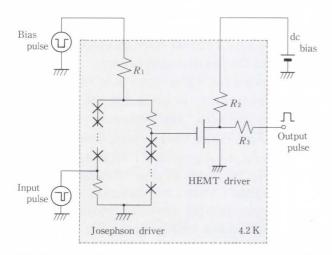

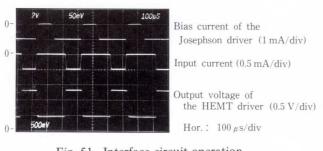

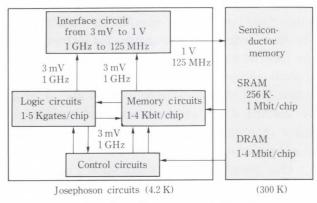

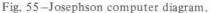

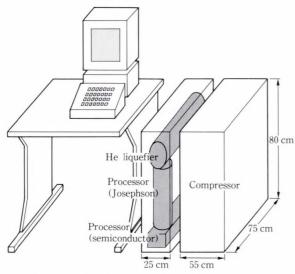

Josephson junctions with Nb/AlO<sub>x</sub>/Nb structures have made it possible to fabricate a variety of high-speed circuits, including an 8-bit digital signal processor and 4K-bit memory.

These circuits operate at ultrafast speeds and consume less power than any high-speed semiconductor circuits. An interface circuit which issues the signal from Josephson circuits to semiconductor circuits has also been fabricated. In short, it is possible to fabricate all components necessary for constructing a Josephson computer. Now the high-speed operation of the Josephson computer must be demonstrated.

UDC 538.945:621.3.049.771 FUJITSU Sci. Tech. J., **27**, 1, pp. 59-83(1991)

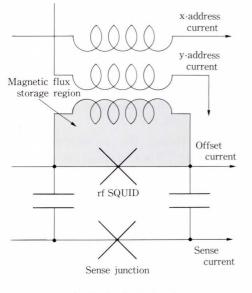

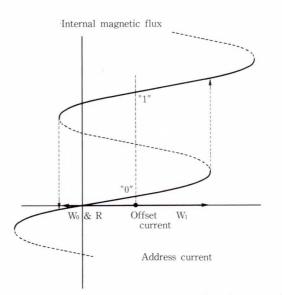

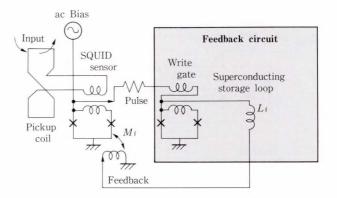

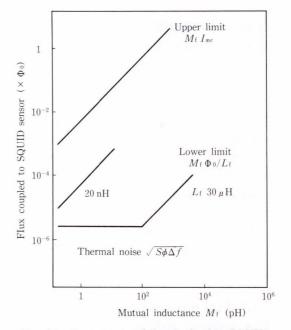

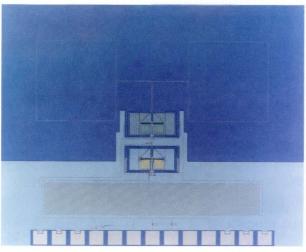

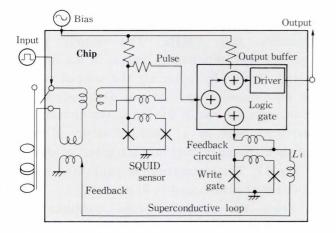

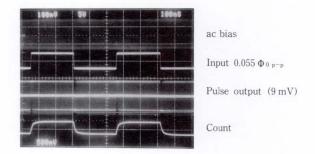

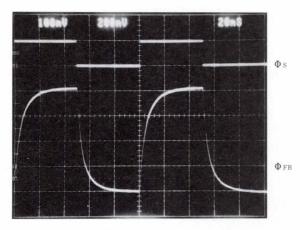

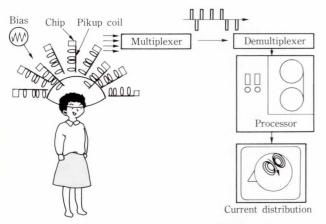

Josephson Integrated Circuits III A Single-Chip SQUID Magnetometer

• Norio Fujimaki

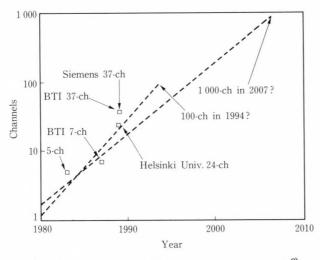

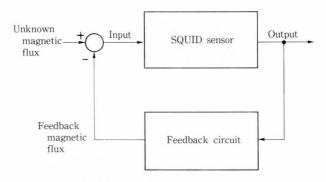

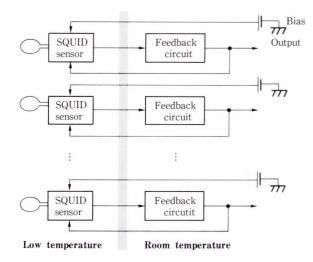

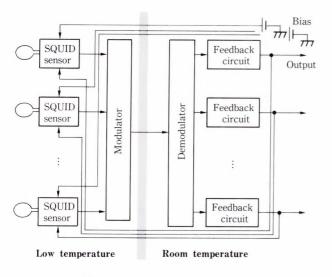

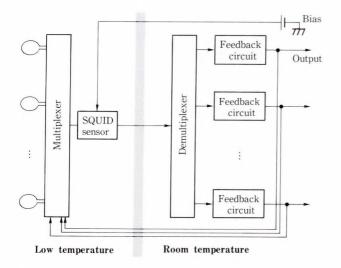

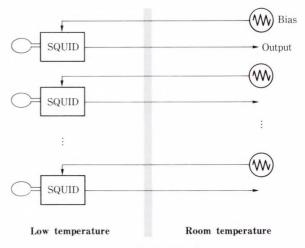

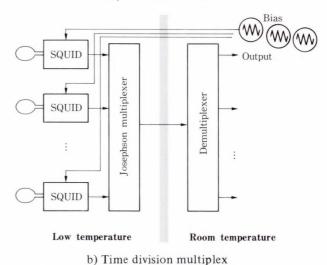

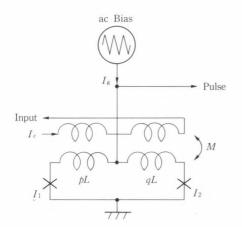

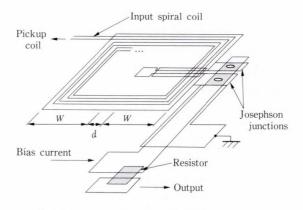

Superconducting Quantum Interference Devices (SQUIDs) can measure magnetic fields as low as femto tesla and have been used for biomagnetism, resource surveying, and physical or geophysical measurement. Unlike the conventional SQUID, the single-chip SQUID is the first device that intergrates both a SQUID sensor and a feedback circuit on the same chip. This reduces the number of external cables. Also, the output can be processed with Josephson digital circuits in the cryogenic environment. These advantages open up the possibility of constructing a multichannel system with an array of more than 100 SQUIDs, which is required to measure a magnetic field map in detail.

#### SYNOPSES (Papers)

UDC 621.383.52 FUJITSU Sci. Tech. J., **27**, 1, pp. 84-91(1991)

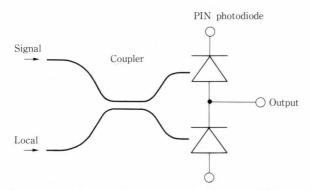

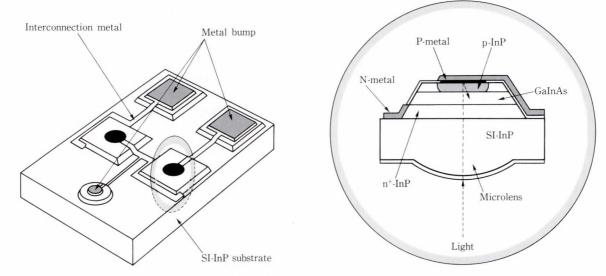

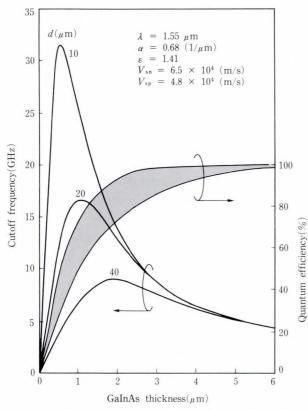

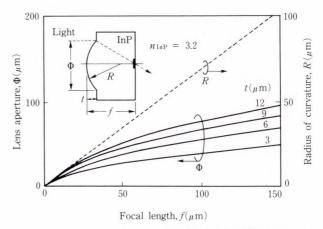

### High-Speed Monolithic GalnAs Twin PIN Photodiodes for Coherent Optical Receivers

• Masao Makiuchi • Hisashi Hamaguchi • Osamu Wada

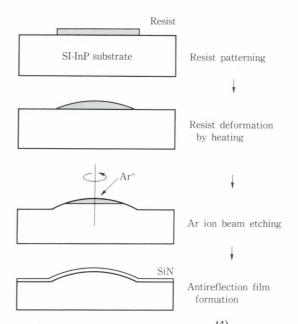

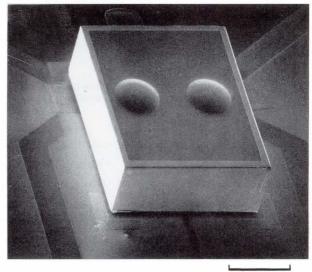

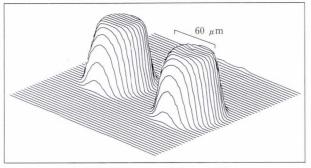

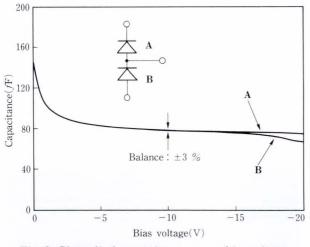

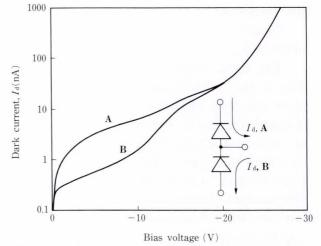

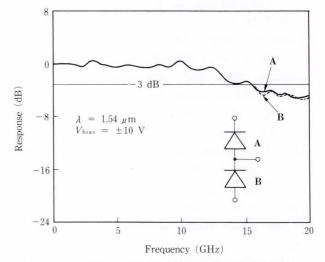

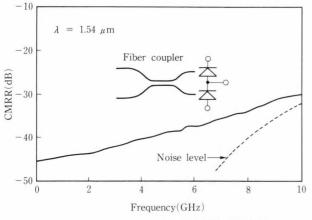

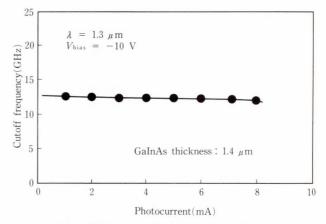

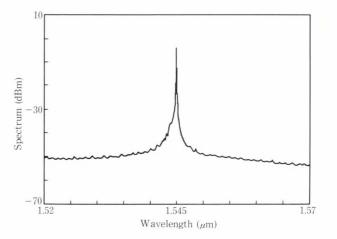

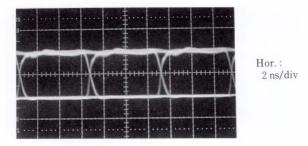

Monolithic GaInAs twin PIN photodiodes were fabricated to realize excellent dual-detector balanced optical receivers in coherent optical communication systems. Introducing a backilluminated, flip-chip structure gives these photodiodes a small junction capacitance of 80 fF, a quantum efficiency of 75 percent at a wavelength of 1.54  $\mu$ m, and a cutoff frequency better than 15 GHz. An optical input power level as high as 8 mW is obtained. A large fiber alignment tolerance of 60  $\mu$ m is achieved by integrating InP microlenses. The common-mode rejection ratio is better than -30 dB at a frequency of up to 10 GHz. The performance demonstrated is well suited to high-speed optical coherent communication systems.

### UDC 621.391.6:621.395.4

FUJITSU Sci. Tech. J., 27, 1, pp. 92-106(1991)

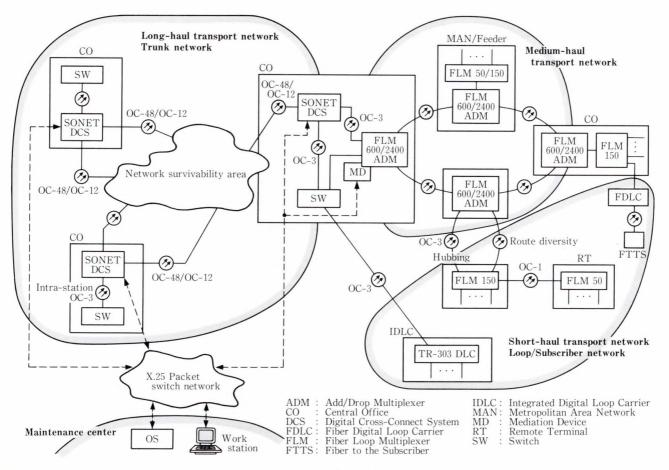

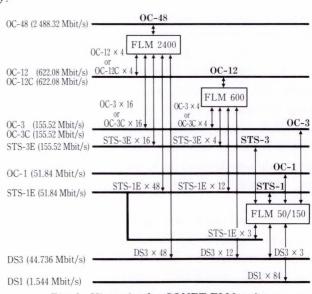

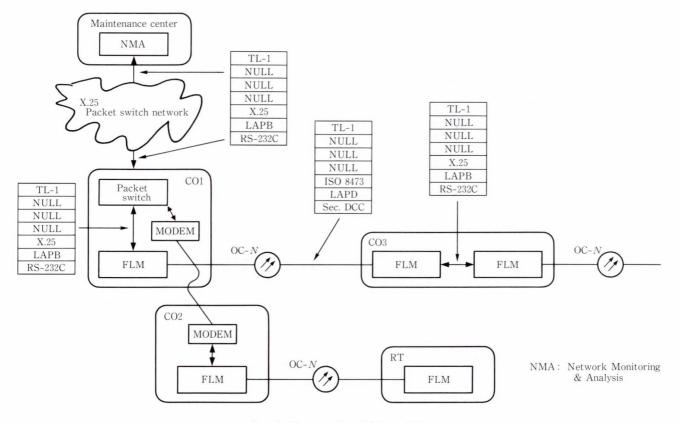

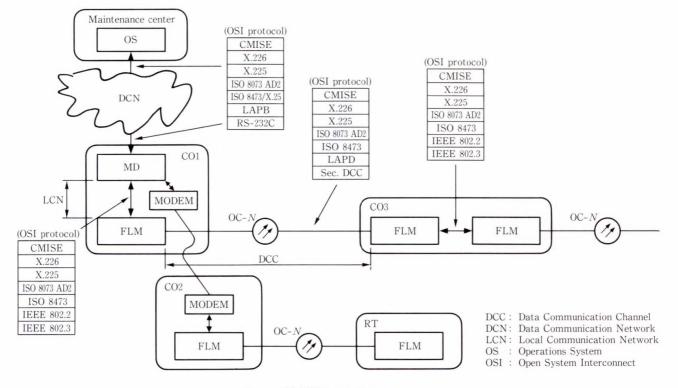

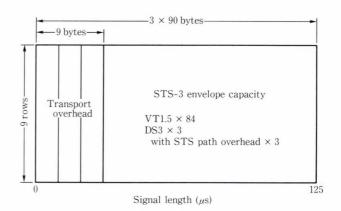

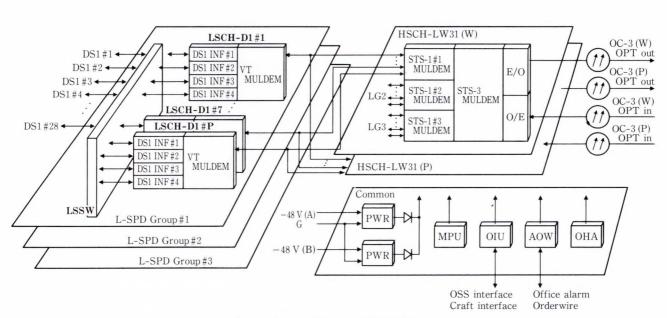

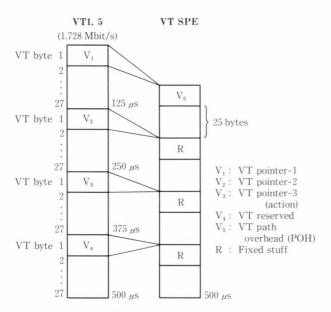

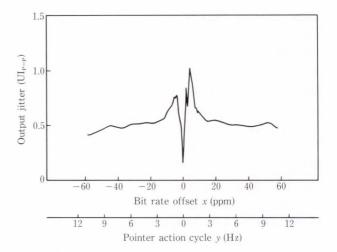

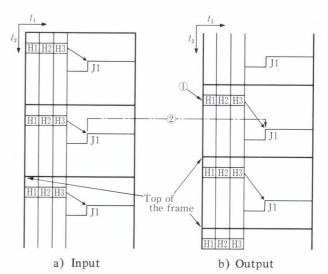

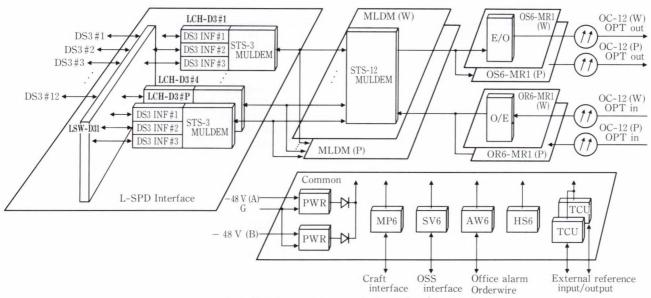

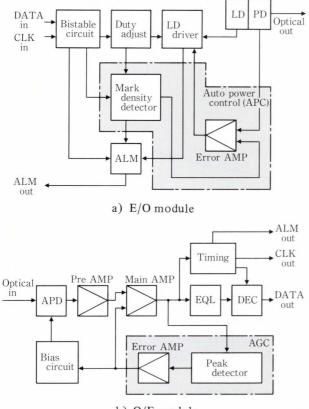

#### SONET System for North America

• Masahiro Shinbashi • Akihiko Ichikawa • Kenji Sato

In 1988, the Phase I standard of Synchronous Optical Network (SONET) was established by ANSI. Standards committees are planning for Phase II, which defines the functions for maintenance and operations, and which will be generally standardized in late 1990.

Fujitsu produced the Fiber Loop Multiplexer (FLM) series conforming to the Phase I standard for the Regional Bell Operating Companies (RBOCs) before its competitors. The FLM was well received.

This paper describes the SONET systems created by Fujitsu, Fujitsu's plan to upgrade to Phase II, and the key technologies used in the product.

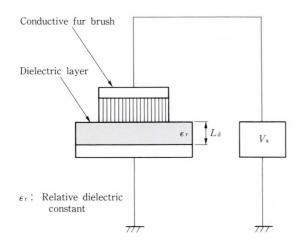

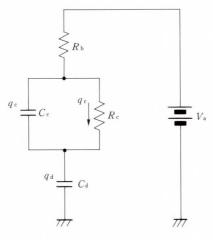

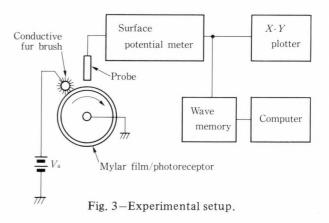

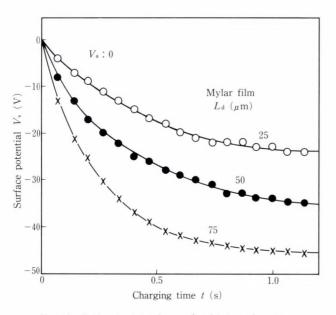

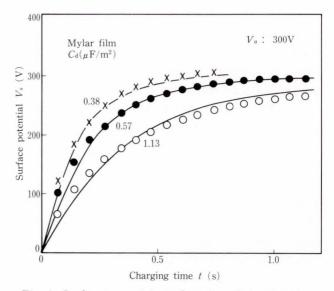

UDC 681.327.5:681.621.83

FUJITSU Sci. Tech. J., 27, 1, pp. 107-114(1991)

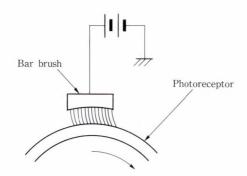

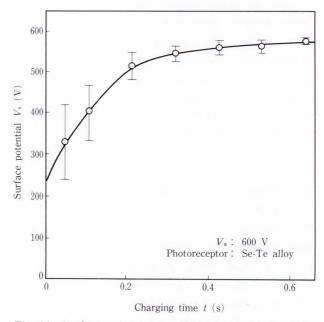

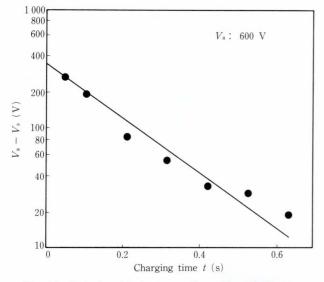

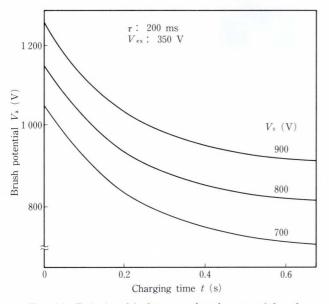

Conductive Fur Brush Charging of a Dielectric Surface

• Masahiro Wanou • Masatoshi Kimura

Charging of a dielectric surface without corona discharge has been achieved using a conductive fur brush to which an electrical potential of several hundred volts is applied. In this method, it was observed that brush charging is accomplished by direct charge transfer, gas discharge, and triboelectric charging. Direct charge transfer, the primary charging process, was analyzed using an ohmic contact model. The charged potential is nearly proportional to that of the brush. When the charging time exceeds 0.3 seconds, the charged potential on the surface of the photoreceptor saturates at almost the potential of the brush. Brush charging is, therefore, useful as a low-voltage charging technique.

UDC 681.7.03

FUJITSU Sci. Tech. J., 27, 1, pp. 115-131(1991)

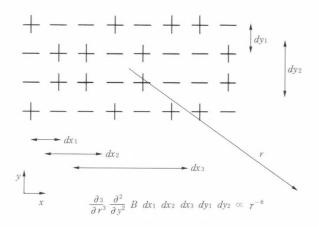

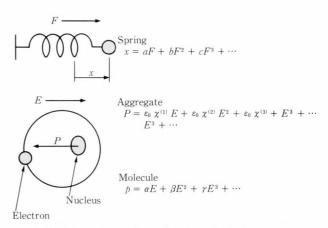

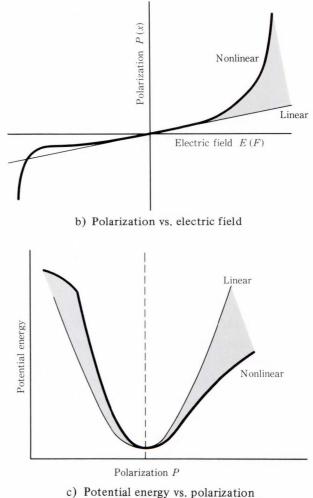

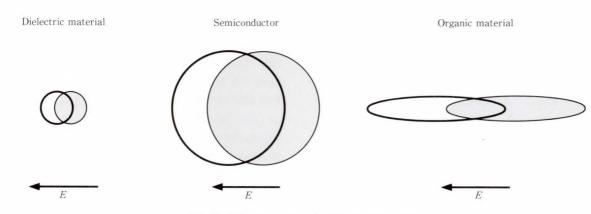

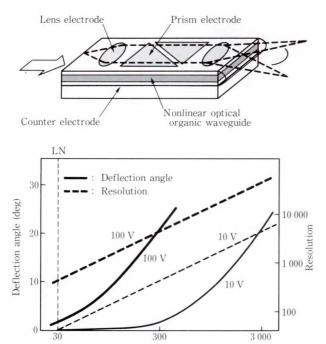

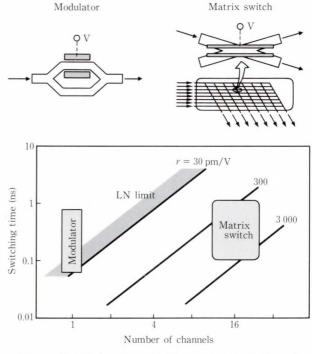

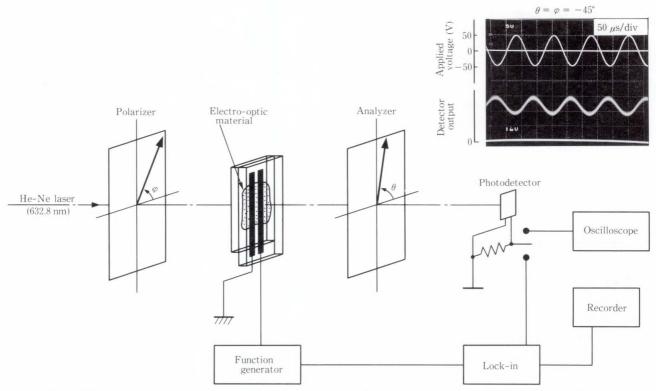

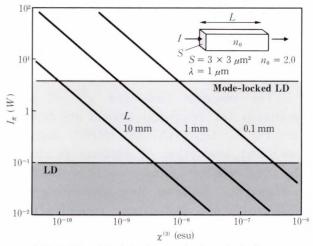

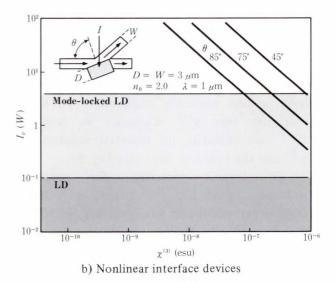

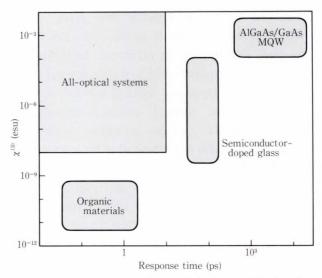

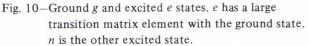

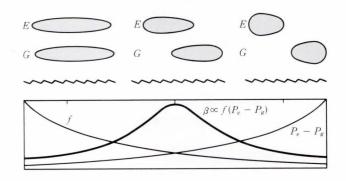

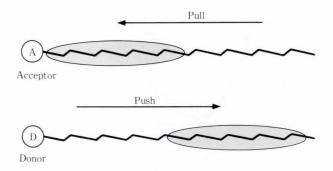

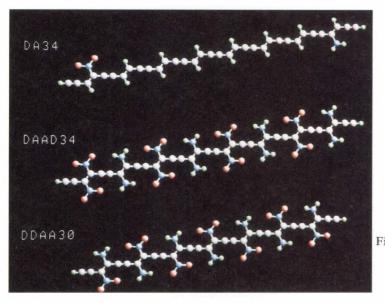

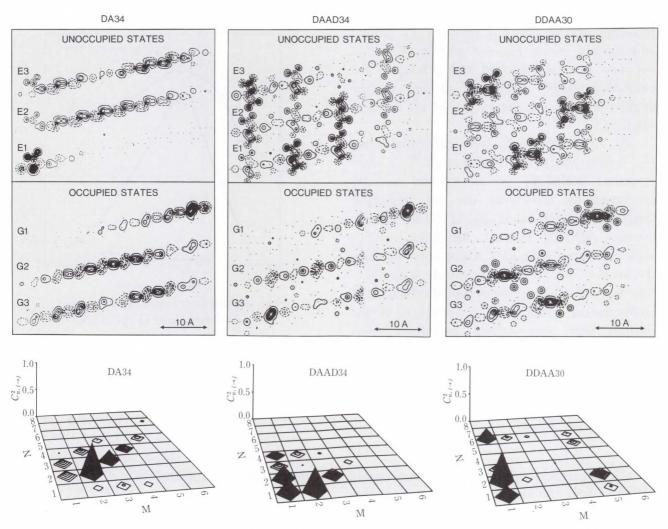

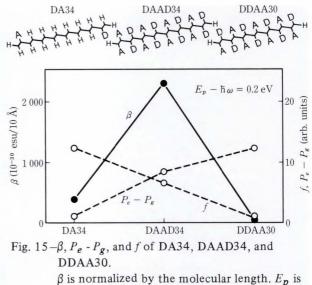

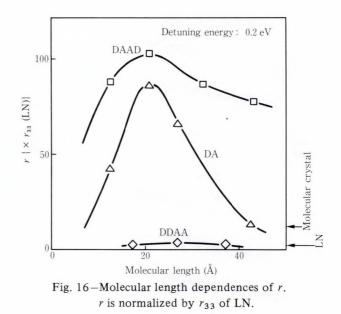

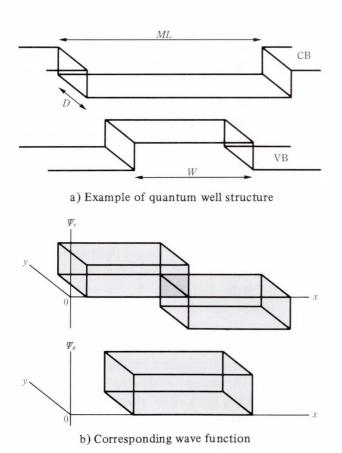

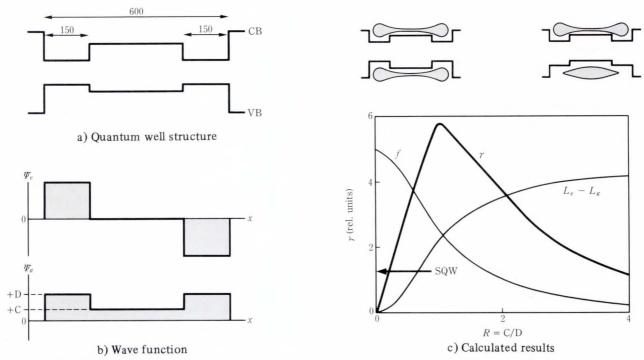

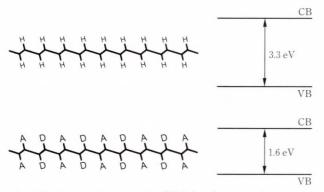

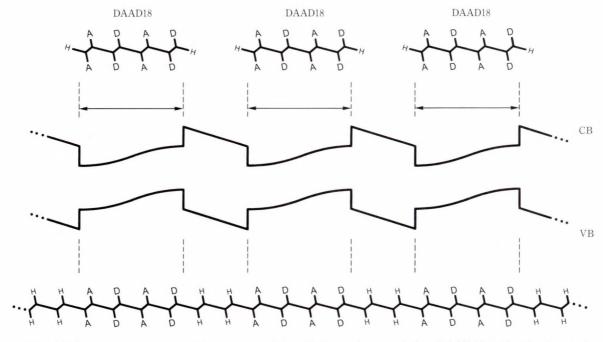

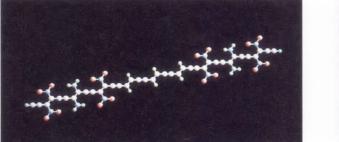

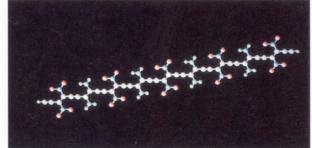

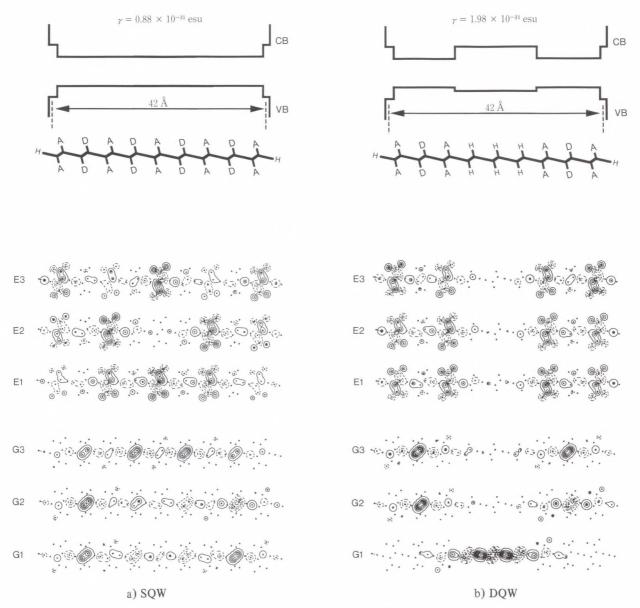

Design of Organic Nonlinear Optical Materials for Electro-Optic and All Optical Devices by Computer Simulation

• Testsuzo Yoshimura

This paper investigate the use of organic materials for nonlinear optical devices as a means to providing a breakthrough in optical nonlinearities. For electro-optic devices, an improvement in second-order nonlinearity 10-100 times as large as that of LiNbO<sub>3</sub> is needed.

For all-optical devices, an improvement in the third-order nonlinearity over 10 times as large as that of ordinary polydiacetylene (PDA) is required. To achieve these objectives, several organic materials were designed based on newly proposed guidelines requiring that the balance between wave function overlap and separation (or difference) be optimized. Computer simulations show that the objectives may be attainable by controlling the wave function and forming quantum wells through adjusting donor and acceptor substitution sites in one-dimensional conjugated systems. UDC 621.3.049.75.002.2:681.32 FUJITSU Sci. Tech. J., **27**, 1, pp. 132-140(1991)

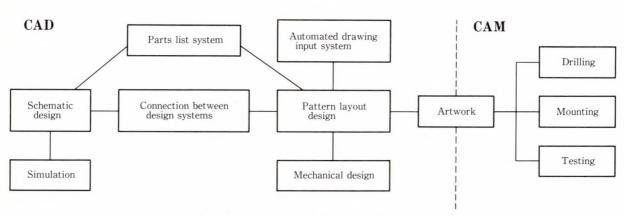

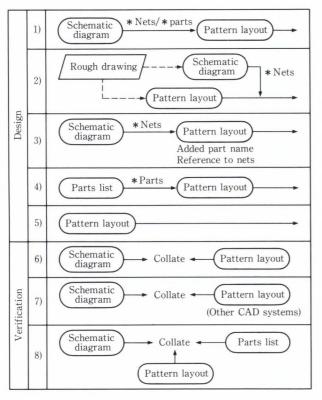

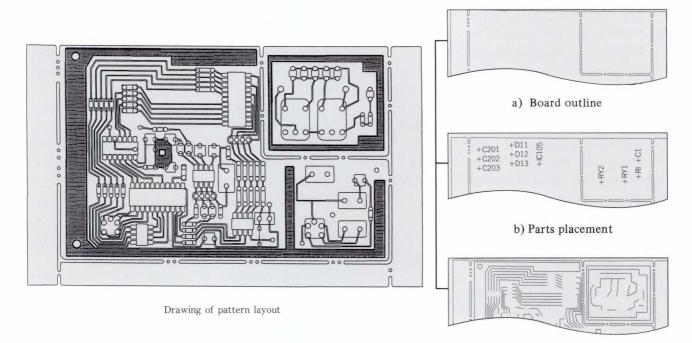

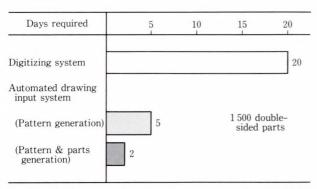

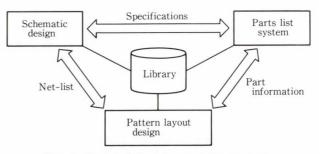

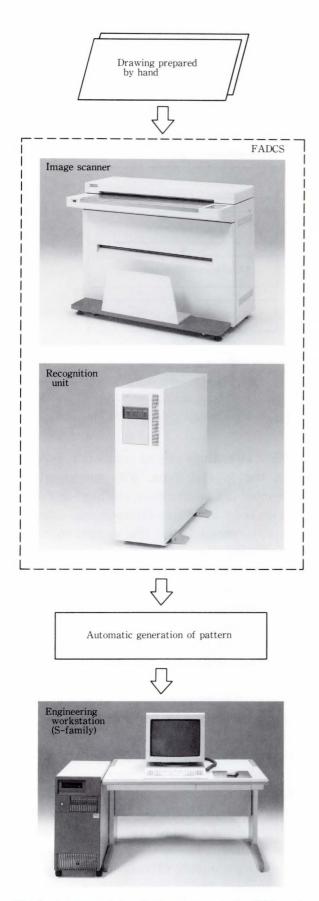

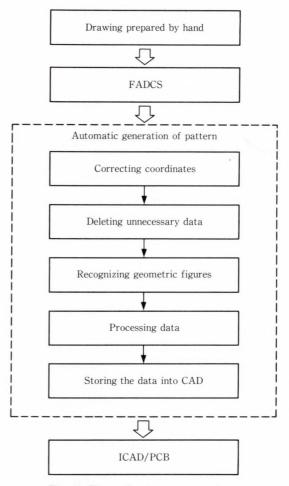

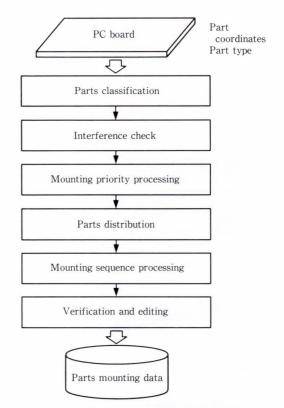

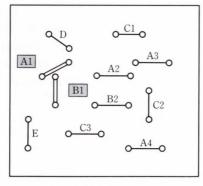

#### CIM System for PC Board Design and Manufacture

• Tsuyoshi Kobayashi • Hideaki Kuwabara

The importance of computer-integrated manufacture (CIM) in the design and manufacturing of printed circuit boards (PC boards) is widely acknowledged. It is difficult to increase the efficiency of schematic design, pattern layout design, or manufacturing using CAD/CAM separately. This paper discusses the construction of a PC board CIM system for use as a key system in a company. It describes the background and scope of CIM, and explains the concept of CIM construction, showing examples. It also introduces the automated drawing input system for PC board design and the supporting system for mounting the parts. This system is advanced technology related to CIM construction.

UDC 624.04:681.32

FUJITSU Sci. Tech. J., 27, 1, pp. 141-146(1991)

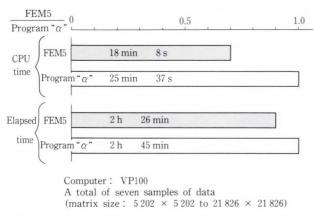

## High-Speed Structural Analysis Program: POPLAS<sup>®</sup> / FEM5 on Supercomputer

• Yasuhiro Komori • Katsuhiko Akahori

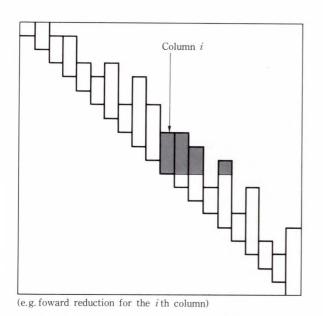

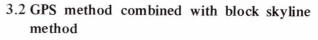

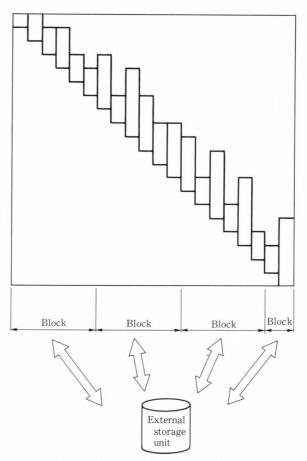

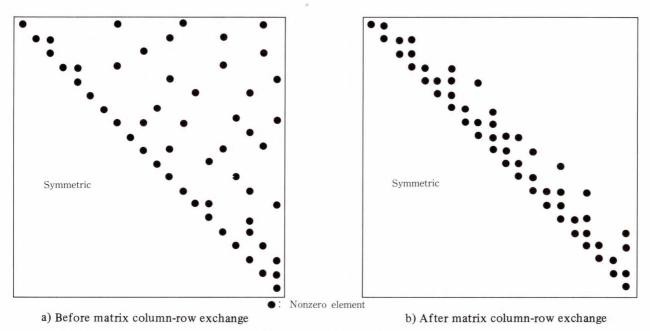

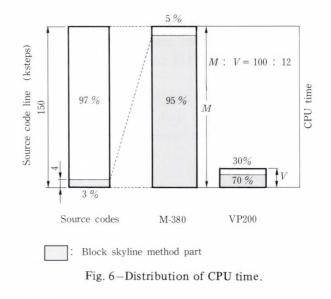

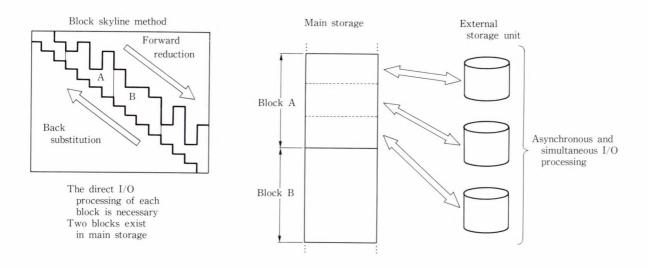

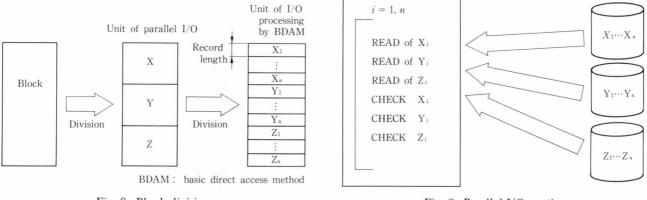

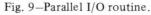

This paper describes the high-speed processing achieved by the development of the structural analysis program POPLAS<sup>®</sup>/FEM5 (called FEM5) on the multiple-pipeline architecture of the FUJITSU VP-series supercomputer.

The CPU time has been reduced by using a method of solving simultaneous linear equations that takes advantage of performance capabilities of a supercomputer. This method is combined with a matrix column-row exchange method. Concentrated vector tuning is also used.

The I/O time has been reduced by developing original I/O processing. As a result, FEM5 has achieved superlative high-level, highspeed processing in the structural analysis field. UDC 538.945:621.3.049.771

## Josephson Integrated Circuits I Fabrication Technology

• Takeshi Imamura (Manuscript received September 3, 1990)

This paper reviews the fabrication technology developed for Josephson integrated circuits and describes the techniques used in the standard process for various circuit elements including Nb/AlO<sub>x</sub>/Nb junctions. These process techniques were verified based on the characteristics of the 8K-bit cell array chips fabricated for process evaluation as being applicable to Josephson circuits that include several thousand junctions. Without the process technology based on the reliable Nb/AlO<sub>x</sub>/Nb junctions, the recently demonstrated ultrahigh-speed operation of Josephson integrated circuits would not have been possible. This paper also introduces advanced process techniques developed for future Josephson LSI application.

#### 1. Introduction

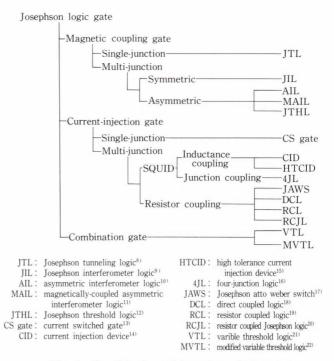

Superconductivity has been studied ever since 19111). Although current flow without power consumption in electronics applications is certainly appealing, it took another fifty years before the application of superconductivity to electronics finally began. This is because the microscopic theory of superconductivity has unknown for a long time. Without a theoretical basis, it was difficult to develop superconducting devices. Such difficulties were solved by two theoretical innovations introduced around 1960. One is the quantum theory of superconductivity proposed by Bardeen, Cooper, and Schrieffer in  $1957^{2}$ ). The other is the superconducting tunneling phenomenon theoretically predicted by Josephson in  $1962^{3}$ . This effect, called Josephson effect, was experimentally verified in 1963<sup>4</sup>). Based on such development in theoretical study, the application of superconductivity to electronics has begun in earnest<sup>5)-7)</sup>. The various types of proposed superconducting devices are divided into three groups: the cryotron<sup>8)</sup>, Josephson junction devices<sup>9)</sup>, and superconducting three-terminal devices<sup>10)</sup>. Among them, only the Josephson junction features high-speed performance, which

has been experimentally demonstrated. Much effort has been focused on Josephson circuit technology. Even now, the application of Josephson junctions is limited to such applications as voltage standard<sup>11)</sup>, magnetic sensor for medical use<sup>12)-14)</sup>, and a mixer for radio astronomy<sup>15)-16)</sup>. Discrete Josephson devices have been used in these applications. The integrated circuits for digital application remain in the research stage for two reasons: the ultrahigh performance not possible with semiconductors has not been readily demonstrated using Josephson LSI chips, and even a small superconducting digital computing system requires the further development of such peripheral technologies as packaging and cooling. Recently, however, significant progress has been made in Josephson circuit technology $^{17)-19}$ . We expect to introduce a small-scale superconducting computing system in the near future.

The Josephson junction devices use the superconducting tunneling effect, and, theoretically, should achieve high-speed, low-power operation not possible with semiconductors<sup>20),21)</sup>. Since the mid-1960s, IBM has spearheaded Josephson device research<sup>5)-7)</sup>. During the mid-1970s to early 1980s, many organizations also joined the race to develop a Josephson computer<sup>22)-27)</sup>. This work stopped abruptly when IBM ended its Josephson computer project in September 1983<sup>28)</sup> for two reasons. First, Josephson circuits were not much faster than semiconductor circuits. Secondly, it was difficult to develop a high-speed cache memory. Ever since IBM lost its enthusiasm for developing Josephson junctions for digital applications, others have followed in kind. Research in Japan, however, has continued all along. One of the problems posed by Josephson junctions used at that time was the instability of the junction materials - lead alloys<sup>29)-31)</sup>. For one thing, the critical current of the junction increased with time during storage at room temperature. For another, the scattering of critical current was too large, even for junctions on the same chip, making it very difficult to manufacture LSI circuits.

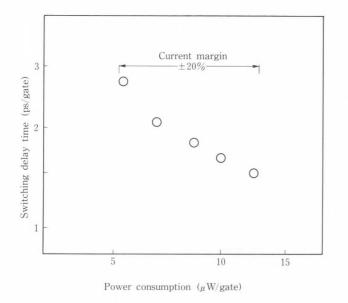

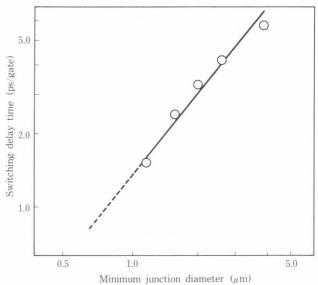

The introduction of reliable niobium (Nb/  $AlO_x/Nb$  junctions at the end of 1983 to replace the obsolete lead-alloy junctions changed the picture dramatically. The Nb/AlO<sub>x</sub>/Nb junction as developed by Gurvitch et al<sup>32)</sup>. was further improved by Morohashi et al<sup>33),34)</sup>. The introduction of niobium junctions solved most of the problems hindering process reliability. Many kinds of fabricated logic and memory circuits could operate at much higher speeds than semiconductor circuits. Recently, a Josephson gate established a 1.5-ps gate delay at a power dissipation of only  $12 \,\mu w^{35}$ . The world's first Josephson microprocessor operated at a clock frequency of 770 MHz<sup>36)</sup>. An 8-bit digital signal processor with 6 300 gates operated at 1 GHz<sup>37)</sup>. Josephson digital circuit technology was also applied to the superconducting quantum interference device (SQUID) magnetometer<sup>12)-14)</sup>, where the Josephson junction had been used as an analog magnetic sensor. This enabled us to develop a single-chip SQUID including a feedback circuit<sup>38)</sup>. These developments have been made possible by the high quality and excellent uniformity of junction characteristics.

This paper (Part I) reviews recent developments in Josephson circuit technology achieved

2

by our laboratories, and describes the fabrication technology of Josephson circuits based on Nb/AlO<sub>x</sub>/Nb junctions. Part II<sup>19</sup> describes the high-speed performance of fabricated Josephson integrated circuits, and Part III<sup>39</sup> describes the breakthrough made in SQUID magnetometers.

Chapter 2 of this paper (Part I) reviews the Josephson junction materials investigated thus far. Chapter 3 describes the standard fabrication process using Nb/AlO<sub>x</sub>/Nb junctions. Chapter 4 describes the advanced process technology being developed for future Josephson LSI application. In conclusion, chapter 5 summarizes this paper.

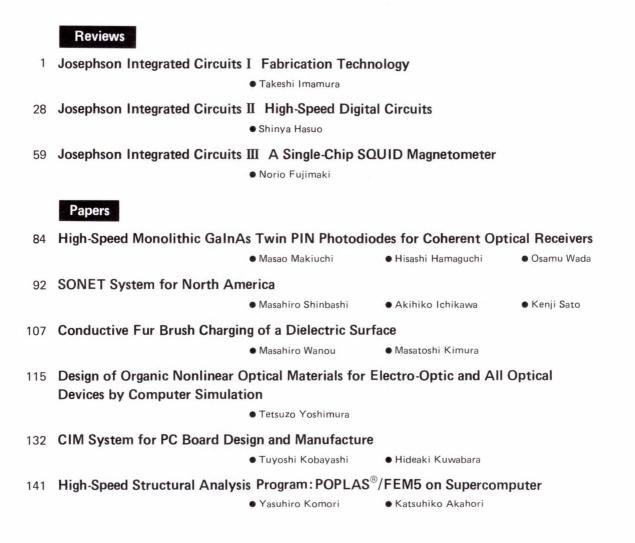

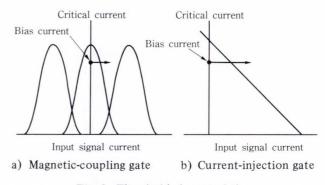

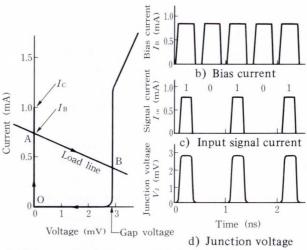

#### 2. Junction materials

The Josephson junction is made of a thin tunneling barrier sandwiched between two superconducting films called the base and counter electrodes. See references 40 and 41 for the principles of Josephson junction. Figure 1a) shows a cross section of the junction, and 1b) shows the current-voltage (I - V) characteristic. The maximum superconducting tunneling current is called critical current  $(I_c)$ . When the bias current exceeds  $I_c$ , the junction switches from zero-voltage state A to voltage state B. Thus,  $I_c$  is one of the most important device parameters used in circuit design. In most Josephson junctions, the tunneling barrier is as thin as a few nanometers. Since  $I_c$  decreases exponentially with the barrier thickness, barrier formation integrity is essential for obtaining good junctions.

Circuit fabrication requires the use of stable, uniform, high-quality, and reproducible junctions.

#### 1) Stable

The junction characteristic is stable against thermal cycling between 4.2 K and room temperature. Stability during long-term storage at room temperature is also crucial.

2) Uniform

$I_{\rm c}$  variation is small (typically less than ten percent) for junctions on a chip.

3) High-quality

Small leakage current in the sub-gap voltage region for the I-V characteristic. Parameter  $V_m$  is normally used to determine junction quality, as described later.

4) Reproducible

Expected junction characteristics, particularly the crirical current, are reproducible through the process.

Throughout the 1970s, lead alloy materials have been used as junction electrode materials. Native oxide grown by plasma oxidation was used for the junction barrier<sup>29)</sup>. Much effort has been focused on improving the reliability of lead-alloy junctions<sup>42)-45</sup>). By the early 1980s, however, it became clear that unreliable leadalloy junctions could not provide the Josephson integrated circuits required<sup>31)</sup>. For example, Ic of the junction continues changing during longterm storage even at room temperature, and excessive Ic variation hinders integrated circuit operation. Moreover, the initial junction yield is not high enough to facilitate use in circuits. Typically, one percent of the junctions is initially shorted. Such unreliable characteristics are due to large-grained, corrosive, and mechanically soft lead-alloy electrodes.

Much work has gone into replacing leadalloy electrodes with such refractory materials as Nb and NbN<sup>46)</sup>, which are much more finegrained, hard, and stable. Table 1 lists the "allrefractory" junctions reported thus far. "All-refractory" means that both the base and counter electrodes are made of refractory materials. The sequence indicated by slashes (/) refers to "counter electrode/barrier/base electrode".  $V_g$  is the gap voltage, and  $V_m$  is the quality parameter defined by the product of the critical current and subgap resistance at 2 mV. Recently,  $V_m$ for NbN junctions has been defined at 3 mV be-

| Junction                | $V_{g}(mV)$ | $V_{\rm m}^{\rm Note 1}({\rm mV})$ | Ref.   |

|-------------------------|-------------|------------------------------------|--------|

| Nb/oxide/Nb             | 2.8         | 6-8                                | 47, 51 |

| Nb/Au/oxide/Nb          | 2.6         | 26                                 | 54     |

| Nb/a-Si/Nb              | 2.8         | 28                                 | 55-58  |

| Nb/AlO <sub>x</sub> /Nb | 2.8-2.9     | 40-70                              | 32, 33 |

| Nb/ZrO <sub>x</sub> /Nb | 2.8         | 50                                 | 59     |

| Nb/YbO <sub>x</sub> /Nb | 2.8         | 15                                 | 60     |

| Nb/TaO <sub>x</sub> /Nb | 2.8         | 25                                 | 61     |

| $Nb/Si_x N_y/Nb$        | 2.8         | 16                                 | 62     |

| NbN/oxide/NbN           | 4.0-4.4     | 15-25                              | 63,64  |

| NbN/a-Si/NbN            | 4.4         | 10-12                              | 65,66  |

| Nb/p-Ge/NbN             | 4.0         | 35-48                              | 68     |

| NbN/MgO/NbN             | 5.1-5.4     | 45-50 Note 2)                      | 70-73  |

Table 1. All-refractory Josephson Junctions

Note 1):  $V_{\rm m}$  defined at 2 mV.

Note 2):  $V_{\rm m}$  defined at 3 mV.

cause the Nb junction has larger  $V_g$  than Nb junctions. Junctions to be used in Josephson integrated circuits require  $V_m$  exceeding ~30 mV to afford a wide circuit's operating margin enough for practical use.

In early studies, Nb was used for the base electrode alone, and the Nb<sub>2</sub>O<sub>5</sub> barrier enjoyed some success<sup>47)-50</sup>. Attempts to use all-refractory junctions, however, were less than successful. High-quality junctions feasible for circuit applications were difficult to fabricate, and  $V_{\rm m}$ was less than 10 mV<sup>47),51)</sup>. The subgap conductance was too large for use in circuits. This means that the tunneling barrier contains pinholes, inducing leakage current, apparently due to the chemical reaction between the Nb counter electrode and Nb, O, barrier. Studies on the interface between the Nb electrode and oxide barrier<sup>52),53)</sup> resulted in a thin Au layer being introduced to minimize subgap conductance<sup>54)</sup>. The highest attainable  $V_{\rm m}$  (26 mV) still proved insufficient for use in Josephson LSI.

Studies on artificial barrier materials other than native  $Nb_2O_5$  have been challenged. "Artificial" refers to the intentional depositing of barrier materials on the base electrode. Studies on barrier materials that react less at the interface with Nb electrodes have tended to take one of two approaches: Using a semiconductor barrier or using a metal oxide barrier. In the first approach, an amorphous silicon barrier offered the best characteristics  $V_{\rm m} = 28 \text{ mV})^{55)-58)}$ . With the second approach, some of the many metals studied were found to function as good junction barriers when adequately oxidized<sup>32),59)-62)</sup>. Among them, the AlO<sub>x</sub> barrier has outstanding quality<sup>32),33)</sup>.  $V_{\rm m}$  reproducibly exceeds 40 mV while  $I_{\rm c}$  uniformity and controllability are far superior to those of any other refractory junctions. Not surprisingly, recent developments in Josephson circuits have proceeded almost exclusively using Nb/AlO<sub>x</sub>/Nb junctions.

A possible Nb alternative also receiving much attention has been NbN<sup>46)</sup>. The use of NbN, which has a higher critical temperature, results in large  $V_{g}$  and smaller subgap conductance. NbN is also less chemically reactive than Nb and less sensitive to oxygen contaminants both advantages in making high-quality junctions – but the coherence length of NbN is shorter than Nb, necessitating the formation of a thinner tunneling barrier on NbN. The greater penetration depth in NbN also reduces the junction's switching sensitivity. Of the many barrier materials used for junctions with NbN electrodes<sup>63)-74)</sup>, MgO has shown the highest quali $ty - V_m$  of 45 mV to 50 mV<sup>70),71</sup>. Junction quality generally depends on the critical current density, particularly in NbN/MgO/NbN junctions. Thus, the  $V_{\rm m}$  in Table 1 is selected from junctions with a practical current density greater than 1 000 A/cm<sup>2</sup>.

The all-refractory junctions used to fabricate a variety of logic and memory circuits thus far are Nb/AlO<sub>x</sub>/Nb<sup>17),18)</sup>, NbN/oxide/NbN<sup>75)</sup>, and NbN/MgO/NbN<sup>76)</sup>. Most Josephson circuits, however, have been made of Nb/AlO<sub>x</sub>/Nb. We have made significant progress in Josephson circuit technology development based on Nb/ AlO<sub>x</sub>/Nb junctions, mainly due to their high quality and reproducibility.

The following chapters also introduce fabrication using the Nb/AlO<sub>x</sub>/Nb junctions developed in our laboratories. After a brief description of the standard integrated circuit fabrication process, this paper discusses the advanced techniques developed for future Josephson LSI application.

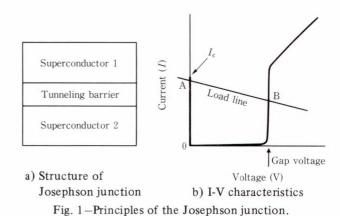

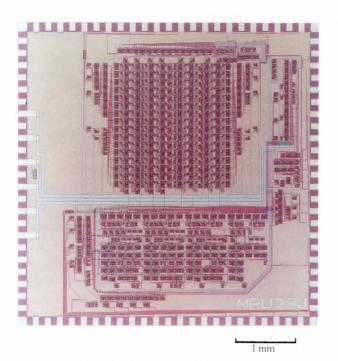

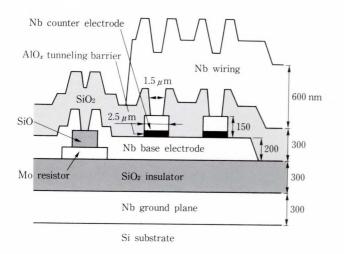

Fig. 2–Integrated circuits with Nb/AlO<sub>x</sub>/Nb Josephson junctions.

#### 3. Standard process

#### 3.1 Outline

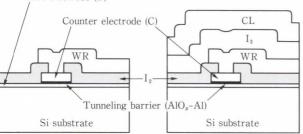

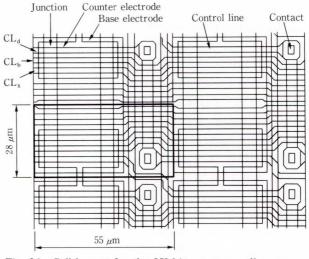

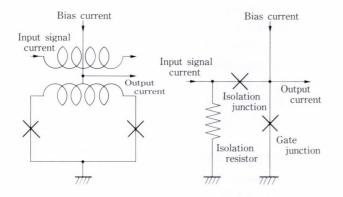

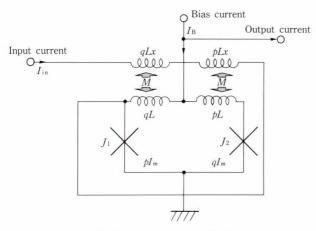

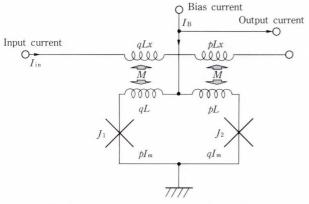

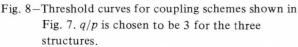

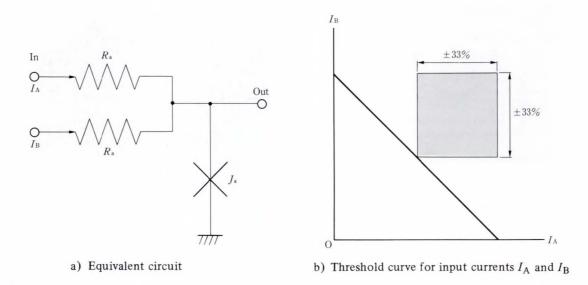

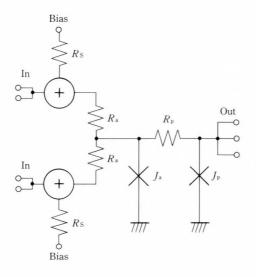

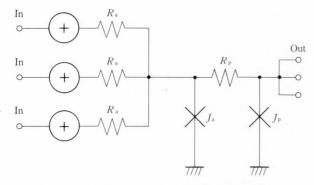

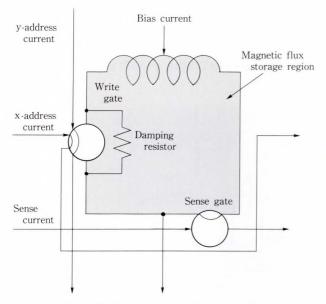

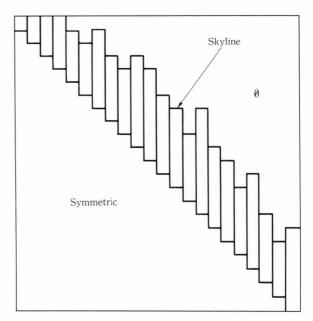

Josephson integrated circuits consist of the Nb/AlO<sub>x</sub>/Nb Josephson junctions, SiO<sub>2</sub> insulators, Mo resistors, Nb ground plane, and Nb wiring, usually formed in nine to eleven layers on Si substrates<sup>77)</sup>. Each layer is patterned through a photoresist mask by reactive ion etching (RIE).

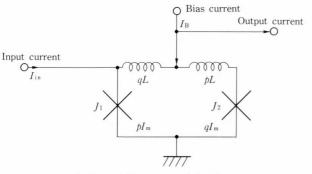

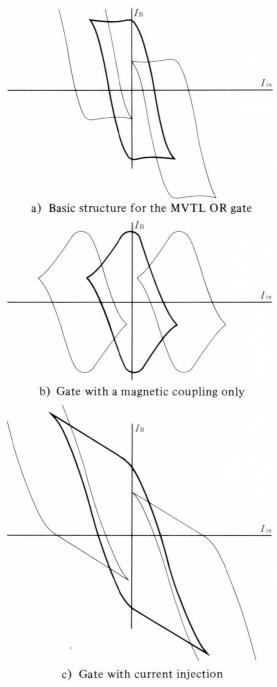

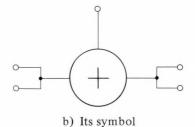

As shown in the typical cross section in Fig. 2, Josephson circuits are usually fabricated above a superconducting ground plane. The Nb wiring formed above the ground plane composes a superconducting strip line. This is necessary to enable high-speed signal transmission between adjacent junctions. Resistors that are used as loads or as damping resistors<sup>78)</sup> in junction switching contact the base electrode. Contact holes are formed in insulators above the junction counter electrodes to ensure electrical contact with subsequent wiring. The contacts between the base electrode and ground plane, which are not shown in Fig. 2, are necessary for Josephson circuits. Contact is enabled by the base electrode through a hole in the insulation layer above the ground plane. In logic circuits designed using the MVTL gate family<sup>79)</sup>, wiring is set in the top layer. In memory and some types of logic circuits, two additional layers are formed on the wiring, i.e. insulators and control lines.

Table 2 lists the layer materials and thicknesses. Nb, Al, Mo and  $SiO_2$  are deposited by sputtering under the conditions listed in Table 3. The  $SiO_x$  used as a protective (P) layer for Mo resistors during RIE of the Nb base electrode is

|                | Layer               | Material                | Thickness (nm) |

|----------------|---------------------|-------------------------|----------------|

| GP             | Ground plane        | Nb                      | 300            |

| $I_1$          | Insulation          | SiO <sub>2</sub>        | 300            |

| R              | Resistor            | Мо                      | 100            |

| Р              | Resistor protection | SiO or SiO <sub>x</sub> | 100            |

| В              | Base electrode      | Nb                      | 200            |

| _              | Tunneling barrier   | AlO <sub>x</sub> -Al    | 7              |

| С              | Counter electrode   | Nb                      | 100-200        |

| I <sub>2</sub> | Insulation          | SiO <sub>2</sub>        | 400            |

| WR             | Wiring              | Nb                      | 600            |

| I <sub>3</sub> | Insulation          | SiO <sub>2</sub>        | 800            |

| CL             | Control line        | Nb                      | 1 000          |

Table 2. Circuit layers

Table 3. Metal and insulation layer sputtering

| Material         | Ar pressure<br>(Pa) | Deposition rate<br>(nm/min) |

|------------------|---------------------|-----------------------------|

| Nb               | 1.3-2.3             | 200                         |

| Al               | 1.3                 | 8                           |

| Мо               | 0.67                | 130                         |

| SiO <sub>2</sub> | 1.3                 | 8                           |

Table 4. Metal and insulation layer patterning

| Material         | Reactive gas                             | Pressure<br>(Pa) | Power<br>density<br>(W/cm <sup>2</sup> ) |

|------------------|------------------------------------------|------------------|------------------------------------------|

| Nb               | CF <sub>4</sub> (5-20 % O <sub>2</sub> ) | 2.7-6.7          | 0.10                                     |

| Al               | Ar                                       | 0.7              | 0.15                                     |

| Mo               | CF <sub>4</sub> (5 % O <sub>2</sub> )    | 6.7              | 0.10                                     |

| SiO <sub>2</sub> | CHF <sub>3</sub> (0-15% O <sub>2</sub> ) | 2.0              | 0.20                                     |

deposited by evaporating SiO in an oxygen atmosphere<sup>80)</sup>. All layers except the P layer are patterned by RIE. Table 4 lists the reactive gases used in RIE. Because Al and  $AlO_x$  are not etched by reactive CF<sub>4</sub> and CHF<sub>3</sub>, they act as an etching stopper. The thin  $AlO_x$ -Al barrier is removed by Ar sputter etching. The SiO<sub>x</sub> used for the P layer is patterned by lift off<sup>31)</sup>.

Although the key process in Josephson LSI development is producing high-quality junctions, the other circuit elements are also important. These elements include the insulation layer, superconducting wiring resistors, and contacts between two Nb layers. The following sections briefly describe the standard fabrication process optimized for Nb/AlO<sub>x</sub>/Nb junctions, SiO<sub>2</sub> insulators, Nb wirings, contacts, and Mo resistor. The final section evaluates the standard process

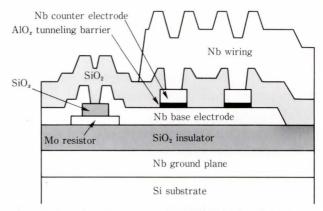

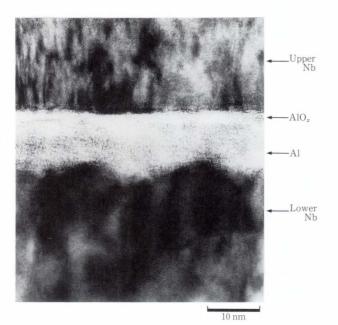

Fig.  $3 - Nb/AlO_x/Nb$  Josephson junction.

in full vertical structures from the ground plane to the control line, both at 300 K and 4.2 K.

#### 3.2 Nb/AlO<sub>x</sub>/Nb junctions

3.2.1 Excellence of Nb/AlO<sub>x</sub>/Nb junctions

Figure 3 shows a cross section of the Nb/  $AlO_{x}/Nb$  junction used in the standard process. The required junction characteristics are stability, uniformity, reproducibility, and high quality as described in Chap. 2. On these characteristics, the Nb/AlO<sub>x</sub>/Nb junctions offer the best I-V characteristics among all refractory junctions. This excellence of the Nb/AlO<sub>x</sub>/Nb junctions is due to the following four properties. First is the stability of refractory Nb with its fine-grain, smooth surface. Second is the affinity of the thin Al to the underlying Nb. An Al layer a few nanometers thick can wet the Nb surface<sup>81)-84)</sup>. Third is the integrity of the  $AlO_x$  barrier formed on Al. The uniform  $AlO_x$  2 nm thick is reproduced by introducing oxygen into a vacuum chamber. Fourth is that the  $AlO_x$  barrier is not damaged by the subsequent deposition of the counter Nb electrode. In addition to these inherent material properties, the development of the whole wafer process<sup>32),55)</sup> is vital to enhance junction process reliability. In this process, the  $Nb/AlO_x/Nb$  multilayered structure is deposited in a vacuum run to eliminate contaminants around the junction barrier.

To reproduce high-quality Nb/AlO<sub>x</sub>/Nb junctions, we have optimized the various process parameters listed in Tables 3 and 4. In particular, the deposition of the Nb/AlO<sub>x</sub>/Nb trilayer structure is essential to obtaining high-quality junctions. The depositing parameters of Nb and Al were observed to affect the junction charac-

T. Imamura: Josephson Integrated Circuits I: Fabrication Technology

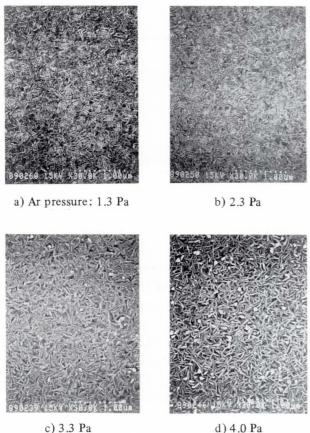

Fig. 4-SEM photographs of Nb films deposited at different Ar pressures. Film thickness is 600 nm.

teristics. Reference to details on optimization is made in some papers<sup>34),85)-87)</sup>. The following subsections briefly describe two points affecting the junction characteristics: the quality of Nb electrode<sup>85)</sup> and the coverage of thin Al on Nb<sup>86),87)</sup>. The standard process for junctions and their characteristics is described below.

#### 3.2.2 Nb electrodes

The Nb electrodes were deposited with dc and rf magnetron sputtering. A comparison of the junction characteristics concluded that junctions with dc-sputtered Nb are superior to those with rf-sputtered Nb<sup>34)</sup>. This difference is due to the interdiffusion between the lower Nb and thin Al layers. Based on these results, our research has focused on optimizing the parameters of dc-sputtered Nb.

The film characteristics of dc-sputtered Nb were studied in terms of surface morphology, stress, crystal structure, and superconductivity. These characteristics change depending on the

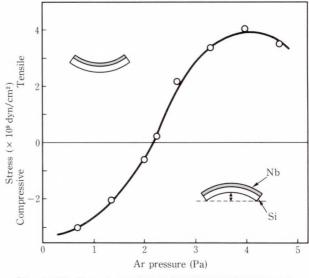

Fig. 5–Nb film stress versus Ar pressure during sputtering.

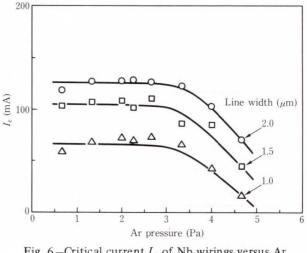

Fig. 6–Critical current  $I_c$  of Nb wirings versus Ar pressure.

sputtering parameters, typically on the Ar pressure.

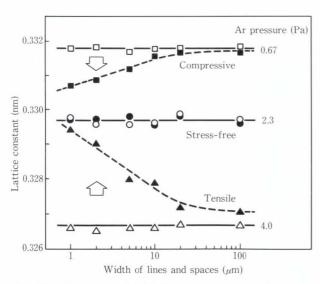

Sputtered Nb film has a columnar structure with polycrystalline grains, where the Nb(110) plane is oriented in parallel to the substrate surface. Figure 4 compares scanning electron microscopy (SEM) photographs of Nb deposited at different Ar pressures. The surface morphology of sputtered Nb features a fine filamentous texture. At higher Ar pressures, however, the surface morphology deteriorates as small grains of increased density appear in the texture. Figure 5 shows the intrinsic stress of sputtered Nb changes as a function of Ar pressure. The stress changes from compressive to tensile as the Ar pressure increases. At around 2.3 Pa, stress-free Nb is obtained. Figure 6 shows the superconducting critical current of 600-nm Nb wiring as a function of the Ar pressure. The superconductivity of Nb film gradually deteriorates above a threshold Ar pressure of 3 Pa.

When considering the surface morpholgy and superconductivity of sputtered Nb, films deposited at low Ar pressures are regarded more suitable for junction electrodes. Based on these results, the Ar pressure for the standard process was fixed at 1.3 Pa, although it is a little compressive. For the characteristics of junctions larger than 1  $\mu$ m, however, we observed no effects caused by the compressive stress of Nb film. To make junctions smaller than 1  $\mu$ m, the use of stress-free Nb was considered crucial to achieving high-guality junctions, as described in Sec. 4.1.

#### 3.2.3 Coverage of Al on Nb

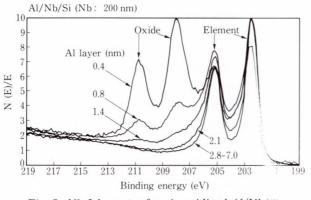

Since Al is several nanometers thick, its

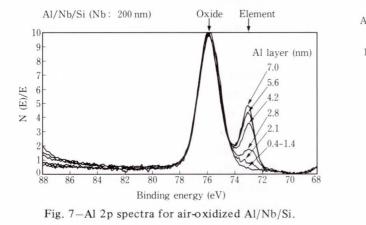

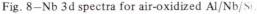

coverage on the underlying Nb is critical to grow a uniform  $AlO_x$  barrier without pinholes. The coverage of thin Al on Nb was studied by X-ray using photoelectron spectroscopy (XPS)<sup>86),87)</sup>. Figure 7 compares the Al 2p spectra for Al/Nb/Si of different Al thicknesses. Spectra are normalized by the peak height of Al oxide. For Al thicker than 2.1 nm, a peak of elemental Al is clearly observed. Figure 8 compares the Nb 3d spectra for the same samples. For Al thicker than 2.1 nm, peaks of  $Nb_2O_5$  disappear, and only the elemental Nb peaks remain. Figure 9 summarizes the film growth of thin Al on Nb based on the values above, with XPS studies on Al/Si samples also indicated. For Al thinner than 1.4 nm, the Al is completely oxidized, and underlying Nb is partly oxidized. For Al thicker than 2.8 nm, the Nb surface is compeletely covered by elemental Al. Consequently, the Nb is not oxidized. The Al formed on Nb should be thicker than 2.8 nm

T. Imamura: Josephson Integrated Circuits I: Fabrication Technology

Fig. 10–Nb/AlO<sub>x</sub>/Nb Josephson junction process sequence.

to obtain a clean Al/Nb interface. Conversely, when Al is deposited on Si, Al thicker than 7 nm can cover the Si surface. This indicates the affinity of Al to Nb is much better than that to Si. This enables formation of a thin Al barrier on Nb.

The I-V characteristics were examined for junctions of different Al thicknesses. Good characteristics were obtained for Al 2.8-10 nm thick. For Al thicker than 10 nm, the I-V characteristics gradually deteriorate due to the proximity effect on the Al/Nb interface. Based on these results, a standard Al thickness of 7 nm was established.

#### 3.2.4 Junction process

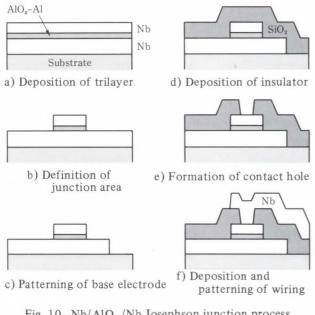

Item a) to f) in Fig. 10 indicate the sequence of  $Nb/AlO_x/Nb$  junction fabrication.

#### a) Deposition of trilayer

Before trilayer  $(Nb/AlO_x/Nb)$  deposition, substrates are etched by Ar sputtering to contact the Nb ground plane through contact holes. The trilayer is then deposited by sputtering on the substrates attached to a holder cooled by circulating water. To ensure good thermal contact, copper backing plates and indium foils are used as spacers between the substrates and holder. The base pressure is less than  $2 \times 10^{-5}$  Pa. After the Nb base electrode and 7-nm Al barrier

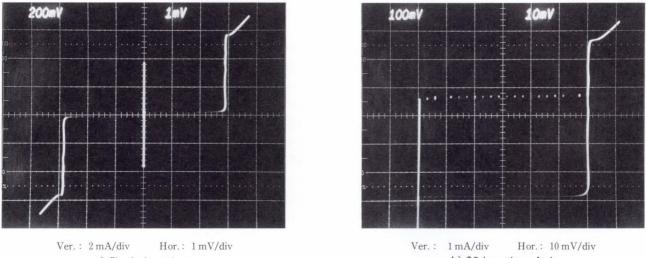

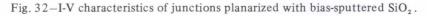

b) 100 serially connected gates

Fig. 11-I-V characteristics.

are sequentially deposited,  $Ar + 10\%O_2$  gas is introduced into the chamber to form a thin oxide 2 nm thick on the Al. The junction's critical current density ( $j_c$ ), depends on the pressure (usually 50-200 Pa) and oxidation time (typically 30-60 min).  $j_c$  ranges of 500-20 000 A/cm<sup>2</sup>. When  $j_c$  is designed at 2 000 A/cm<sup>2</sup>, the averages of  $j_c$  range of 1 500-2 500 A/cm<sup>2</sup> for different waters. After oxidation, the Nb counter electrode is deposited on the AlO<sub>x</sub> barrier. Next, the trilayer is trimmed into a device structure.

b) Definition of junction area

The junction area is defined by patterning the Nb counter electrode. In RIE,  $AlO_x$  and Al act as good etching stops against CF<sub>4</sub> gas. The remaining  $AlO_x$ -Al barrier is removed by Ar sputter etching.

#### c) Patterning of base electrode

The lower Nb is then etched into a base electrode pattern with  $\mathrm{CF}_4$ .

#### d) Deposition of insulator

Junctions are covered with an  $SiO_2$  insulation layer. Section 3.3 describes the sputtering of  $SiO_2$ .

e) Formation of contact holes

Contact holes above the counter electrodes are formed in the  $SiO_2$  by RIE with  $CHF_3$ .

f) Deposition and patterning of wiring

Nb is deposited and patterned as a wiring layer.

#### 3.2.5 Junction characteristics

The  $j_c$  uniformity is sufficient for circuit application. The standard deviation of  $j_c$  is about three percent for 2- $\mu$ m-square junctions on a chip. The variation of  $j_c$  in different fabricated waters increases even in the same lot.

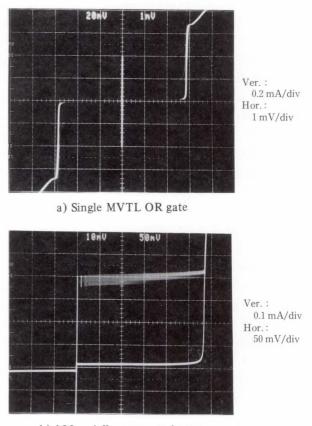

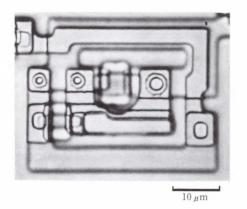

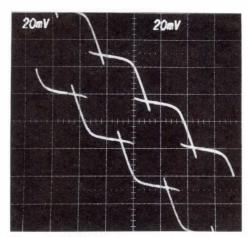

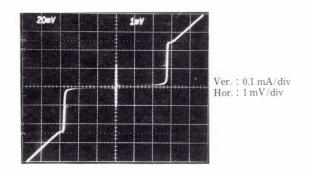

Figure 11 shows the I-V characteristics of modified variable threshold logic (VMTL) gates<sup>79)</sup>. The gate junction is paired, 2.5  $\mu$ m and 4.0  $\mu$ m in diameter. The gap voltage is 2.9 mV. Quality parameter  $V_{\rm m}$  exceeds 50 mV. The maximum-to-minimum spread of the critical current is ±5% for 100 gates.

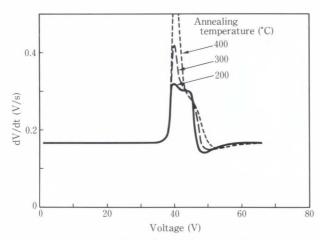

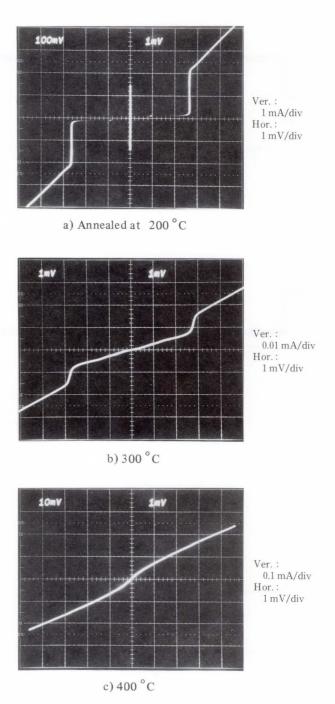

Nb/AlO<sub>x</sub>/Nb junctions are very stable in thermal cycles between 4.2 K and 300 K, and in storage at room temperature. The I-V characteristics do not change during the first few years of storage, but are affected by annealing. Figure 12 shows changes in  $j_c$  and  $V_m$  after 60 minutes of annealing in nitrogen at different

1.0 0.8  $V_{m0} = 1600 \text{ A/cm}^2$   $V_{m0} = 60 \text{ mV}$   $V_{m0} = 60 \text{ mV}$   $V_{m0} = 0.6$   $V_{m0} = 0.6$  $V_{m0} = 0$

Fig. 12-Deterioration of Josephson junctions after annealing.

temperatures. The junction starts deteriorating with annealing above 200 °C. Critical current density begins decreasing after annealing at 175 °C. These changes are considered caused by the change in  $AlO_x$  composition and/or the interdiffusion of Al and Nb<sup>34),83),88)</sup>.

Deterioration due to annealing is one of the most critical problems regarding the reliability of Nb/AlO<sub>x</sub>/Nb junctions. This makes it difficult to further develop Josephson circuit technology for two reasons. One is that the margin in process temperature is not very large;  $175 \,^{\circ}C$  is only 55  $^{\circ}C$  higher than the typical resist baking temperature. The other is that the annealing characteristic limits the application of various semiconductor process techniques.

Thus, the annealing characteristics should be improved for further development in Josephson circuit technology<sup>89)</sup>.

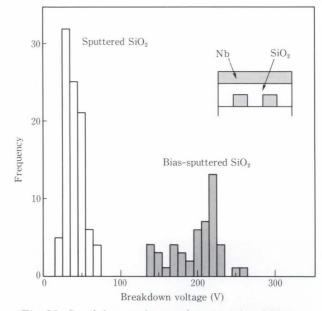

#### 3.3 SiO<sub>2</sub> insulators

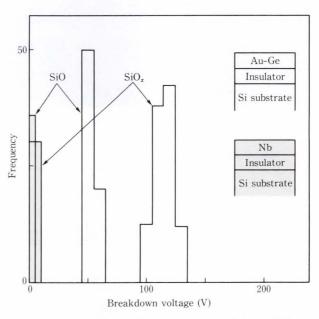

In lead-alloy Josephson circuits, SiO or SiO<sub>x</sub> films were used for insulation layers<sup>31)</sup>, but the integrity of such films is not sufficient for Nb circuits. Figure 13 shows the breakdown voltage in SiO and SiO<sub>x</sub><sup>90)</sup>. The insulator is 300 nm thick, and the electrode is 4 mm square. Using sputtered Nb for the upper electrode reduces the

Fig. 13–Breakdown voltage in 300-nm SiO and  $SiO_x$  films.

breakdown voltage to almost zero due to microcracks induced by heat or stress during refractory Nb deposition.

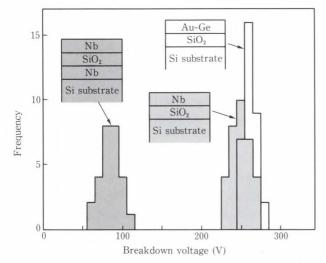

Sputtered SiO<sub>2</sub> was used as an insulator in  $Nb/AlO_x/Nb$  Josephson circuits<sup>77),90</sup>. The breakdown voltage in sputtered SiO<sub>2</sub> (see Fig. 14) exceeds 200 V even when Nb is used for the upper electrode. When Nb is used for both upper and lower electrodes, the breakdown voltage of the sandwiched SiO<sub>2</sub> is reduced to one third the above value, though still exceeding

Fig. 14-Breakdown voltage in 300-nm sputtered SiO<sub>2</sub> films.

Ver.: 0.2 mA/div

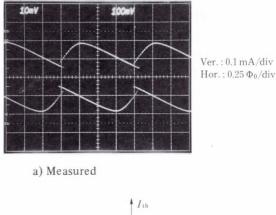

a) Without I<sub>3</sub> and CL layers b) With I, and CL layers Fig. 15-I-V characteristics and cross sections for junctions.

50 V. This is high enough for use in practical Josephson integrated circuits, where the junction voltage is only 3 mV. The deterioration of SiO<sub>2</sub> deposited on Nb is due to the differences in the initial SiO<sub>2</sub> film growth between on Si and on Nb.

The Nb/AlO<sub>x</sub>/Nb junction deteriorates when annealed at temperatures exceeding 200 °C. When depositing  $SiO_2$  on the junctions, thoroughly cooling the substrates during SiO<sub>2</sub> sputtering becomes critical for protecting the junctions against thermal damage. For this purpose, the deposition rate of SiO<sub>2</sub> was reduced to 8 nm/min. During sputtering, the substrates were attached to a water-cooled holder with indium foils. Through these measures, the application of SiO<sub>2</sub> in the junction process was found to cause no deterioration in the junction characteristics. Figure 15 compares junctions with and without an 800-nm SiO<sub>2</sub> insulation layer  $(I_3)$ . The junction quality  $(V_m)$ exceeds 40 mV for both junctions. No deterioration in the characteristics were observed after depositing a thick layer of SiO<sub>2</sub> on the junctions. Based on these results, sputtered  $SiO_2$  has been applied in the standard Josephson circuit process. The use of sputtered SiO<sub>2</sub> resulted in a significantly improved production yield for Josephson circuits. This was demonstrated in the yield evaluation for 8K-bit cell array chips<sup>91)</sup>, as described in Sec. 3.7.

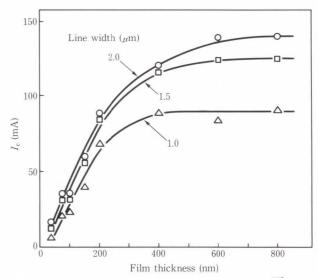

Fig. 16–Critical current  $I_c$  of Nb wiring lines<sup>77)</sup>.

#### 3.4 Nb wiring

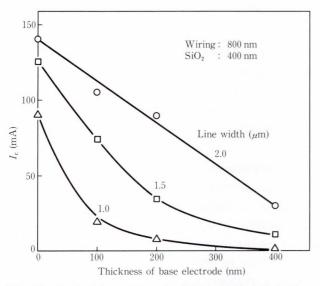

In Josephson circuits, superconducting Nb is used for the wiring. As circuits become more densely integrated, long, narrow wiring lines are needed for circuit construction. Figure  $16^{77}$ shows the superconducting critical current  $(I_c)$  measured for Nb wiring. The lines are  $1.0-2.0 \,\mu\text{m}$  wide and  $10.88 \,\text{mm}$  long. For films thicker than 400 nm,  $I_c$  only depends on line width, not film thickness. For films thinner than 200 nm, however,  $I_c$  changes linearly with the thickness, apparently due to supercurrent flowing in the film surface up to the London penetration depth<sup>40</sup>.

Fig.  $17-I_c$  of wirings versus the thickness of underlaying Nb base electrode.

Fig. 18–Changes in  $I_c$  of wiring after annealing.

The  $I_c$  of Nb wiring is much greater than the current level of Josephson gates (typically less than 1 mA). In actual circuits, however, Nb wiring should run over steps of underlying layers. The  $I_c$  decreases steeply with the thickness of underlying layers (see Fig. 17). This is due to an effectively decreased film thickness at steps. Thus, the  $I_c$  of wiring at steps will be enhanced by improving the Nb coverage at steps. This was actually verified by applying biassputtered Nb to wiring as described in Sec. 4.4.

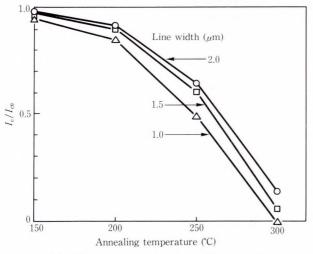

Another problem posed by Nb wiring is its annealing characteristics<sup>85)</sup>. The  $I_c$  of wiring decreases with the annealing temperature as shown in Fig. 18, even when annealed in nitrogen. The reduction in  $I_c$  was observed to be closely related to the oxygen diffusion in Nb<sup>85),89)</sup>.

#### 3.5 Contacts

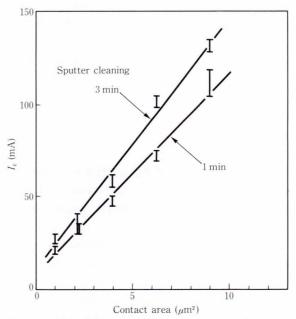

Josephson circuits require contacts between two Nb electrodes. With increased circuit integration, smaller contacts with higher critical currents are needed. Contacts are made through holes formed in the insulating  $SiO_2$  layers. The critical current of 200 serially connected contacts is plotted in terms of the contact area shown in Fig. 19<sup>77)</sup>. Before Nb wiring deposi-

Fig. 19–Critical current  $I_c$  in contacts formed between Nb electrodes<sup>77)</sup>.

T. Imamura: Josephson Integrated Circuits I: Fabrication Technology

Fig. 20-Sheet resistance in Mo resistors.

tion, the Nb base electrode is cleaned by Ar sputtering at 1.3 Pa for one to three minutes to remove the native oxide formed on Nb. The sputtering power density was  $1.9 \text{ W/cm}^2$ . The base electrode is 200 nm thick and the wiring layer 800 nm thick. The critical current for contacts changes almost linearly with the contact area. Even for small contacts 1.0  $\mu$ m square, the 20-mA critical current is much larger than the current flow in actual circuits. Also note that such contacts face the same problem as the wiring:  $I_c$  deterioration due to annealing. Section 4.4 describes how the annealing stability of contacts has been improved.

#### 3.6 Mo resistors

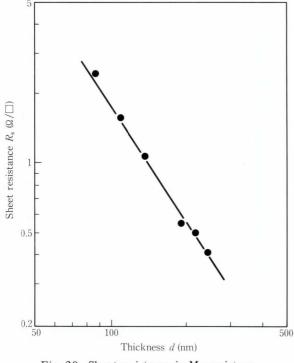

Mo films deposited by sputtering form resistors. Figure  $20^{77}$  shows the measured sheet resistance  $(R_s)$  plotted against thickness (d).  $R_s$  is proportional to  $d^{-1.6}$ . The spread of resistance on a wafer is as small as several percent, and the contact resistance between Mo and Nb is negligible.

The Mo resistor requires a protective layer of  $SiO_x$ , which is patterned by lift-off. The damping resistor used in the gates makes it

Fig. 21-Cell layout for the 8K-bit memory cell array chip. The unit cell is indicated by a bold rectangle.

difficult to reduce the gate size. Because the  $SiO_x$  lift-off enforces a rather large patterning margin. Thus we are developing new resistor material to make the protective layer of  $SiO_x$  unnecessary.

#### 3.7 Process evaluation

The previous sections described the independent evaluation of the elements composing Josephson circuits. In actual circuits, however, such evaluations are not independent, but affect each other in complex ways. Thus, it is necessary to evaluate the characteristics of each element in full vertical structures, including the layers from the ground plane to the control lines. For this purpose, we have evaluated 8K-bit memory cell array chips from the early stages of our Josephson research<sup>31</sup>). The junctions tested thus far are lead-alloy (Pb-Bi/Pb-In-Au) junctions, Pb-Bi/Nb junctions, and Nb/AlO<sub>x</sub>/Nb junctions<sup>77),91</sup>.

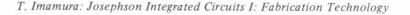

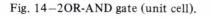

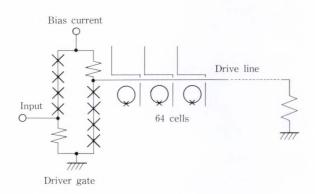

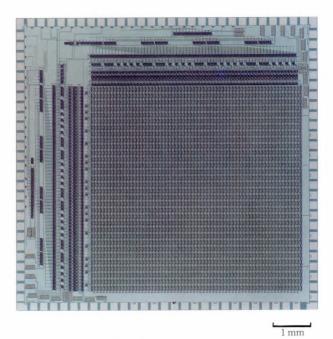

The tested cell is a 2-junction interferometer with three control lines (see Fig. 21). The junction size is  $5 \times 14 \,\mu\text{m}^2$  and the minimum line width is  $2 \,\mu\text{m}$ . Figure 22 shows the fabricated  $5 \times 5 \,\text{mm}^2$  cell array chip containing 8 192 cells and 87 pads. The fabricated chips were tested at two stages. First, the chip yield was measured at room temperature by using an automatic prober. Table 5 lists the test items.

Fig. 22-Microphotograph of the fabricated 8K-bit memory cell array.

|                     | Item | Content                          | Combinations<br>of pads |

|---------------------|------|----------------------------------|-------------------------|

|                     | SA   | SQUID array                      | 36                      |

| Continuity          | CL   | Control line                     | 32                      |

| CHECK               |      | Total                            | 68                      |

|                     | SG   | SQUID array-GP                   | 20                      |

| Insulation<br>check | CC   | CL <sub>i</sub> -CL <sub>j</sub> | 20                      |

|                     | SC   | SQUID array-CL <sub>i</sub>      | 48                      |

|                     | CG   | CL <sub>i</sub> -GP              | 12                      |

|                     |      | Total                            | 100                     |

Table 5. Tested items in the prober test at room temperature

The continuity of the interconnecting wiring was checked for 68 combinations of selected pads, and the insulation of the insulating layers was checked for 100 combinations. Secondly, the I-V characteristics were measured for the chips selected through room-temperature testing. The yield of cells without shorted junctions was evaluated, as well as variations in the cells'  $I_{\rm c}$ .

Table 6 lists the yields for checks made during the room-temperature testing. By using  $SiO_2$ , the yields are significantly improved. Figure 23 shows the yield of the insulation check plotted in terms of the area of the insulators sandwiched by two electrodes. Plots of  $SiO_2$  were obtained

Fig. 23–Yield of the insulation checks versus the area of the insulators.

Table 6. Yields for the tested items

| *                       | Insu-              |    | Yield (%) |    |    |    |    |

|-------------------------|--------------------|----|-----------|----|----|----|----|

| Junction                | lator              | SA | CL        | SG | CC | SC | CG |

| Nb/AlO <sub>x</sub> /Nb | SiO <sub>x</sub>   | 86 | 0         | 40 | 0  | 0  | 44 |

|                         | $SiO_x$<br>$SiO_2$ | 94 | 12        | 77 | 17 | 15 | 83 |

Table 7. Yields for combinations of the tested items

| <b>T</b>                |                  | Yield | 1 (%) | No. of        |  |

|-------------------------|------------------|-------|-------|---------------|--|

| Junction                | Insulator        | SA*   | CL*   | perfect chips |  |

| Pb-Bi/Pb-In-Au          | SiOx             | 0     | 0     | 0             |  |

| Pb-Bi/Nb                | $SiO_X$          | 9     | 0     | 0             |  |

| Nb/AlO <sub>x</sub> /Nb | SiO <sub>2</sub> | 52    | 10    | 6             |  |

for the Nb/AlO<sub>x</sub>/Nb junctions, and plots of  $SiO_x$  and SiO were obtained for the Pb-Bi/ Pb-In-Au junctions. The defect density (*D*) of the insulators was obtained from the slope of plots:  $0.06 \text{ mm}^{-2}$  for SiO<sub>2</sub>,  $0.3 \text{ mm}^{-2}$  for SiO<sub>x</sub>, and  $1.0 \text{ mm}^{-2}$  for SiO. These results are consistent with the breakdown voltages for SiO<sub>2</sub>, SiO<sub>x</sub> and SiO.

The total yield for the SQUID array and control line (SA\* and CL\*) are calculated by the yield obtained for related checks;

$$SA^* = SA \times SG \times SC,$$

$CL^* = CL \times CC \times SC \times SG$

T. Imamura: Josephson Integrated Circuits I: Fabrication Technology

| Chip No. | No. of cells | No. of shorted cells | Failure rate<br>(%) |

|----------|--------------|----------------------|---------------------|

| 1        | 8 1 9 2      | 2                    | 0.024               |

| 2        | 8 1 9 2      | 0                    | 0                   |

| 3        | 8 1 9 2      | 4                    | 0.048               |

| 4        | 8 1 9 2      | 0                    | 0                   |

| 5        | 8 1 9 2      | 0                    | 0                   |

| 6        | 8 1 9 2      | 2                    | 0.024               |

| Total    | 49 1 5 2     | 8                    | 0.016               |

Table 8. Failure rates of the Nb/ $AlO_x/Nb$  cells

Table 9. Average cell failure rates for three kinds of the junction material

| Junctions      | No. of cells<br>measured | No. of shorted cells | Failure rate<br>(%) |

|----------------|--------------------------|----------------------|---------------------|

| Pb-Bi/Pb-In-Au | 24 576                   | 260                  | 1.06                |

| Pb-Bi/Nb       | 65 536                   | 83                   | 0.13                |

| $Nb/AlO_x/Nb$  | 49 152                   | 8                    | 0.016               |

Table 7 lists SA\* and CL\*, along with the results for the Pb-Bi/Pb-In-Au and Pb-In-Au/Nb junctions. The yield for Nb/AlO<sub>x</sub>/Nb junctions proved sufficiently high to obtain six perfect chips among the 64 tested.

The low-temperature characteristics were measured for the selected six chips. Eight cells were observed to be shorted in 49 152 cells (see Table 8). Thus, three of the six chips had no cell failure. The average cell failure rate was 0.016 percent. From these results, we estimated a practical yield of 27 percent for the 8K-bit cells.

Table 9 compares the cell failure rates for the three kinds of junction materials. The use of refractory Nb for the base and counter electrodes decreases the failure rate by one order.

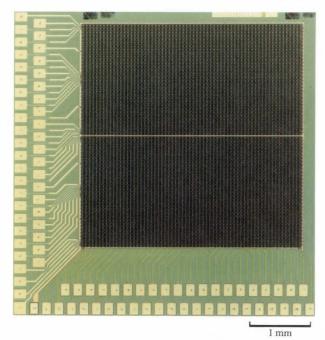

Figure 24 shows the  $I_c$  distribution of 8 192 cells. All cells are within the range of ±13%, and the standard deviation of  $I_c$  distribution is 3.3 percent.

The evaluation of the 8K-bit cell array chips demonstrated that our standard process is feasible to Josephson integrated circuits including several thousand junctions.

#### 4. Advanced processes

The standard process described in the previous chapter enables high-speed opera-

Fig.  $24-I_c$  distribution for 8 192 cells on a chip.

tion of Josephson logic and memory circuits described in Part  $II^{(19)}$  to be verified. Josephson device potential is very high, however, current circuit design and process techniques remain relatively primitive when compared to semiconductor devices. To keep pace with semiconductor device development, Josephson circuit process technology must be further developed to achieve higher circuit density and enhance process reliability, for example. Four advanced techniques have process been recently developed: the fabrication of submicrometer junctions<sup>92),93)</sup> three-dimensional Josephson circuits<sup>92),94),95)</sup>, anodization to characterize the thin tunneling barrier<sup>96),97)</sup>, and bias-sputtered Nb applied to wiring<sup>98)</sup>. The microstructure of  $Nb/AlO_x/Nb$  junctions was also studied by using transmission electron microscopy (TEM)<sup>99)</sup>.

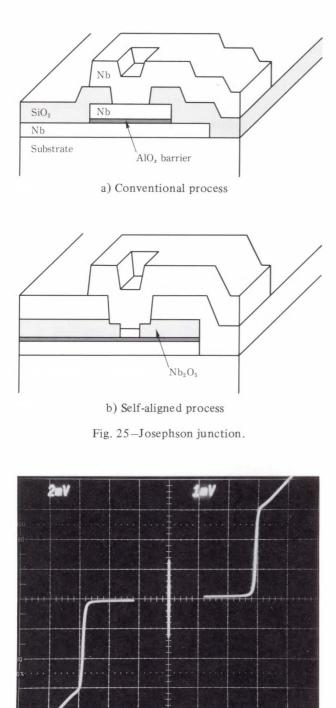

#### 4.1 Submicrometer junction

Figure 25 compares the cross section of the conventional junction with a new junction structure developed through miniaturization<sup>92),93)</sup>. A contact hole in the insulator is formed above the junction in the conventional structure. A submicron junction is difficult to make because the contact hole size must be smaller than the junction size. In the new structure, the junction area is defined by anodizing the Nb counter electrode. The anodized film thickness is *in-situ* monitored by the anodization profile methods<sup>97)</sup> described in Sec. 4.3. The anodized Nb, also

acting as an insulator between the base electrode and wiring, enables formation of self-aligned contact holes. Thus, a small junction can be defined independently of the contact hole size.

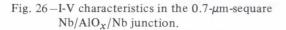

Figure 26 shows an I-V characteristic for a

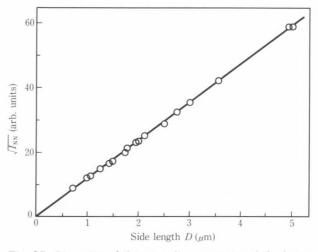

Fig. 27-Linearity of the tunneling current and the junction area.  $I_{\rm NN}$  is the tunneling current at 4 mV, and D is the side length of square junctions.

0.7- $\mu$ m-square junction. The junction has one excellent characteristic:  $V_{\rm m}$  exceeds 30 mV. Here, electron beam lithography is used to make the resist pattern defining the junction area. The tunneling current at 4 mV is plotted against the junction size shown in Fig. 27. Linearity is observed for junction sizes of 0.7-5  $\mu$ m. Pattern deviation in the junction size is estimated at only 0.02  $\mu$ m.

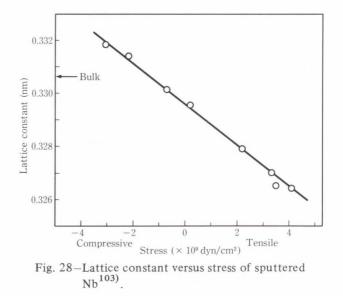

To achieve high-quality submicron junctions, another technical problem had to be solved – the intrinsic stress in Nb film<sup>100)</sup>. Sputtered Nb film reportedly contains stress apparently related to the junction characteristics<sup>101)</sup>. Such stress varies with the Ar pressure during sputtering (see Fig. 5). Stress-free Nb attained by optimizing the Ar pressure was used for junction electrodes to make submicrometer junctions<sup>93)</sup>. The high-quality characteristics are due to the use of stress-free Nb electrodes.

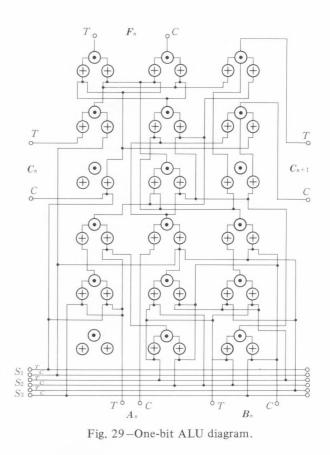

The stress observed was related to the microscopic crystal structure of sputtered Nb. The lattice constant of Nb is plotted against the film stress in Fig. 28<sup>102)</sup>. The linear relationship indicates that the crystal structure of Nb is distorted in proportion to the stress. How Nb stress deteriorates small-junction quality is not yet clear, but stress relaxation was observed during Nb film patterning<sup>102)</sup>. As shown in Fig. 29, the lattice constant of compressive and tensile Nb clearly changes when the film is patterned, and shifts more markedly as the pattern size decreases. In contrast, stress-free Nb exhibits no change. These results suggest that film stress relaxes at the periphery in patterned Nb, thus adversely affecting small-junction quality.

#### 4.2 Planarization and three-dimensional circuits

As mentioned before, the sputtered  $SiO_2$ insulator helps improve the production yield of Josephson circuits. But,  $SiO_2$  integrity is not yet sufficient to increase circuit integration to the

Fig. 29-Changes in the Nb lattice constant during patterning (Hollow symbols: before patterning, solid symbols; after patterning).

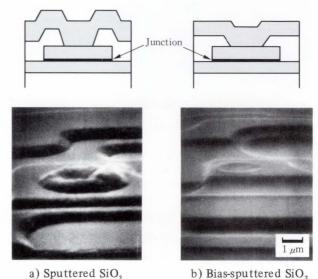

VLSI level. This is mainly due to the poor step coverage of SiO<sub>2</sub> deposited on the patterned Nb. Planarizing the step of the underlying layer must be developed. One possibility is to use biassputtered SiO<sub>2</sub><sup>103)</sup>. Figure 30 compares the breakdown voltages of sputtered and biassputtered SiO<sub>2</sub> deposited on the patterned Nb<sup>95)</sup>. The breakdown voltage, increased by a factor of 2 or 3, indicates the improved step coverage of bias-sputtered SiO<sub>2</sub>. The production

Fig. 30-Breakdown voltages of sputtered and bias sputtered SiO<sub>2</sub> films deposited on patterned Nb films.

Fig. 31–SEM photographs of junctions.

yield was verified as being improved by changing the insulator from sputtered to bias-sputtered  $SiO_2$ .

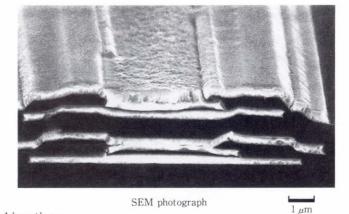

Figure 31 shows SEM photographs of junctions made with sputtered SiO2 and biassputtered SiO2; the steps of underlying Nb

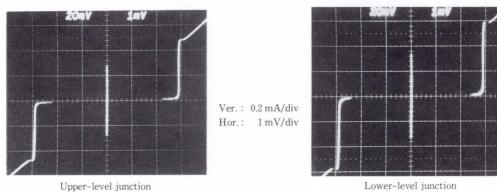

a) Single junction

Lower-level junction

a) I-V characteristics

Cross section

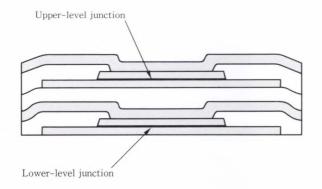

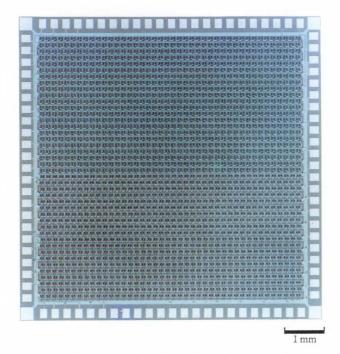

Fig. 33-Vertically stacked junctions.

electrodes are planarized to obtain a smoother device surface. Figure 32 shows the I-V characteristics of the junctions planarized with biassputtered  $SiO_2$ . Although bias-sputtering accompanies additional ion bombardment, no deterioration was observed in the I-V characteristics.

We tried to stack other junctions above the junctions planarized by using bias-sputtered

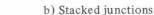

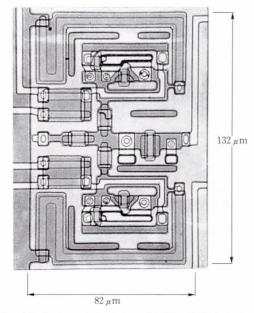

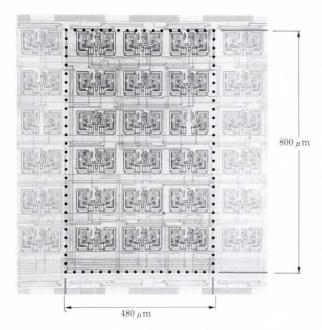

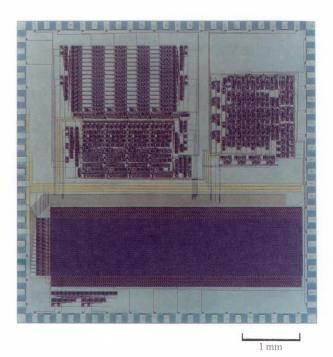

Fig. 34-Three-dimensional 10-Kgate array chip, 7.8 mm square. A 5 292 gates are integrated in both upper- and lower-level circuits.

$SiO_2^{94}$ . Figure 33 shows a cross section of the vertically stacked junction, and the I-V characteristics for the upper-level and the lower-level junctions. By using 600-nm bias-sputtered SiO<sub>2</sub>, high-quality characteristics could be obtained, even for the upper-level junctions.

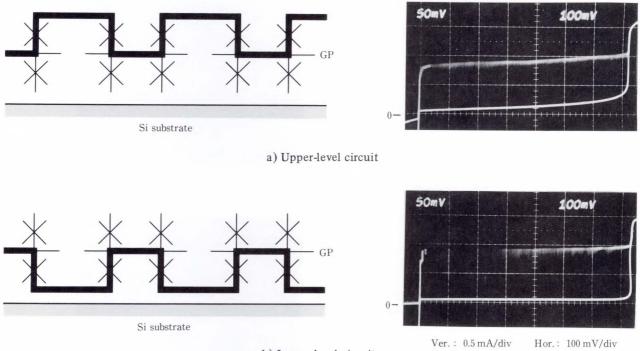

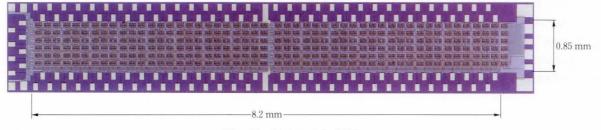

Planarization increases the possibilities of developing three-dimensional Josephson circuits<sup>17)</sup>. A gate array including 10 584 gates was fabricated as a test device for the first three-dimensional Josephson circuits (see Fig. 34). The upper-level and lower-level circuits both contain 5-K Josephson gates. Figure 35 shows an SEM photograph of the vertically stacked gate array. A common ground plane is sandwiched between the lower- and upper-level circuits. Lower-level gates are set upside down to the upper-level gates. The high quality of the 252-gate chains was verified for both the upper-and lower-level gates (see Fig. 36).

#### 4.3 Junction barrier diagnosis

Josephson junction characteristics largely depend on the formation of a uniform, highquality tunneling barrier. Since the Josephson effect only appears at such low temperatures as 4.2 K, junctions cannot really be evaluated until processing is completed. It is also difficult to diagnose the thin  $AlO_x$ -Al barrier using conventional analytical methods because the barrier is very thin and sandwiched between two Nb electrodes. These are serious problems hindering the

Fig. 35-SEM photograph of a vertically stacked gate array.

b) Lower-level circuit

Fig.36-Wiring diagram and I-V characteristics for 252-gate chain.

Fig. 37-Anodization profile for a Nb/AlO<sub>x</sub>/Nb junction. The upper Nb and Al layers are 30 nm and 7 nm thick.

development of improved Josephson process techniques.

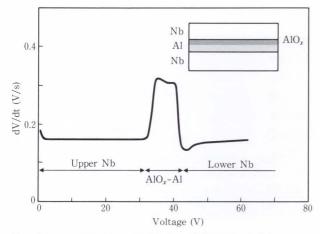

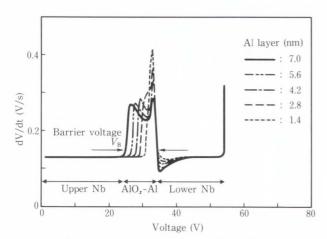

An anodization profile<sup>104)</sup> proposed for evaluating multilayered structures was applied to Nb/AlO<sub>x</sub>/Nb<sup>+</sup> junction structures<sup>96),97)</sup>. Many junction structures were studied by using the anodization profiles. Figure 37 shows an anodization profile for the Nb/AlO<sub>x</sub>/Nb junction. The anodization proceeds in proportion to the

Fig. 38-Anodization profile for a Nb/Al/Nb structure.

voltage: 0.85 nm/V for Nb and 0.88 nm/V for Al. From the profile, the sharpness of interfaces in multilayered structures can be estimated within an accuracy of 0.5 nm. Such a precise analysis is not possible by using conventional methods of analysis.

Figure 38 shows a profile of the Nb/Al/Nb structure. Without the  $AlO_x$ , diffusion between the upper Nb and Al is clearly observed. As evident in Figs. 37 and 38,  $AlO_x$  prevents the

Fig. 39–Anodization profiles of Nb/AlO<sub>x</sub>/Nb junctions annealed for 30 min.

Fig. 41–Anodization profiles of Nb/AlO<sub>x</sub>/Nb junctions with five different Al thicknesses. The upper and lower Nb are 30 nm and 15 nm thick.

diffusion of Al and the upper Nb. In other words, the  $AlO_x$  barrier is not damaged during deposition of the upper Nb.

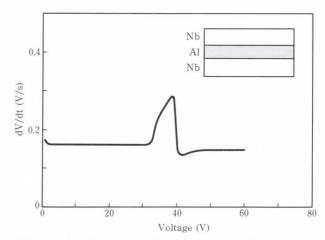

Figure 39 compares the anodization profiles for annealed junctions. By annealing, two changes occur in the profiles. One is the diffusion between Al and the lower Nb. The other is the increased peak height of  $AlO_x$ . Figure 40 shows the I-V characteristics of annealed junctions. Changes in the characteristics feature a reduced  $I_c$  and increased leakage current. Both changes are related to changes in the anodization profiles.

Figure 41 compares the anodization profiles with Al from 1.4 nm to 7.0 nm thick. Al barriers as small as a few nanometers thick can definitely be observed. From the barrier anodization volt-

Fig. 40-I-V characteristics of junctions.

age width  $(V_B)$ , we can calculate the thickness of Al to be oxidized into  $AlO_x$  as about  $1 \text{ nm}^{105}$ .

The anodization profile has been verified as an effective tool for accurately analyzing junction barriers with high precision.

#### 4.4 Bias-sputtered Nb for wiring

Using Nb wiring in Josephson circuits poses

T. Imamura: Josephson Integrated Circuits I: Fabrication Technology

Fig. 42-Cross-sectional SEM photographs of Nb deposited on  $SiO_2$  steps. Nb and  $SiO_2$  are 500 nm thick.

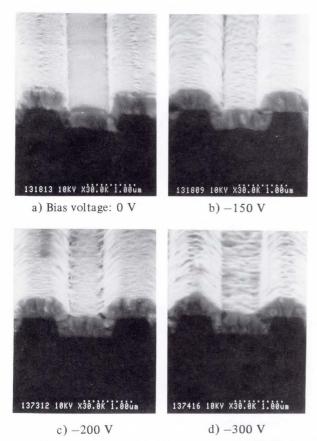

Fig. 43–Critical current  $I_c$  of bias-sputtered Nb films.

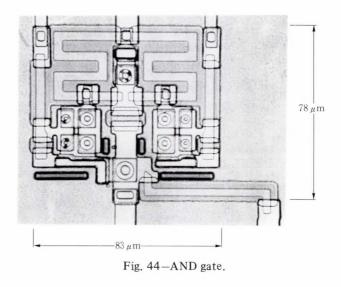

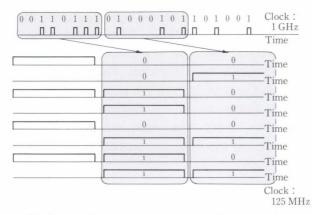

Fig. 44–Critical current  $I_c$  of contacts versus bias voltage during Nb sputtering.

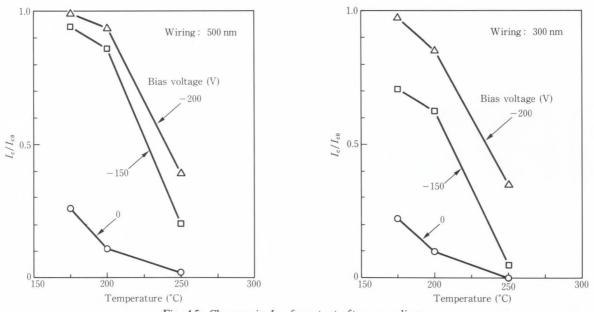

two problems: reduced  $I_c$  of wiring at steps and after annealing. This is due to the effectively reduced thickness of Nb wiring running over the steps. To enhance Nb wiring reliability, we developed bias-sputtered Nb for wiring in circuits<sup>98)</sup>. The step coverage of Nb is improved by adding the bias voltage during sputtering (see Fig. 42). Figure 43 shows the superconducting critical current  $(I_c)$  of bias-sputtered Nb film. For bias voltage less than -150 V, the deterioration in superconducting characteristics is negligible. Based on these rusults, bias-sputtered Nb was applied to the wiring used in Josephson circuits. We confirmed that the Nb/AlO<sub>x</sub>/Nb junction was not affected by using the bias-sputtered Nb. The characteristics of contacts were also improved before and after annealing. The wiring running over the steps also showed improvement in terms of their superconducting characteristics.

Figure 44 shows the  $I_c$  of contacts as a function of the bias voltage during wiring sputtering. The Nb base electrode is 200 nm thick, the SiO<sub>2</sub> insulator is 300 nm thick, and the Nb wiring is T. Imamura: Josephson Integrated Circuits I: Fabrication Technology

Fig. 45–Changes in  $I_c$  of contact after annealing.

Fig. 46-Lattice image of Nb/AlO<sub>x</sub>/Nb junction structure.

300 nm to 500 nm thick. By applying bias voltage,  $I_c$  is increased by factors of 2 to 10. In addition, the contacts with bias-sputtered Nb were observed to be stable against annealing. Figure 45 shows changes in  $I_c$  after annealing. The  $I_c$  decreases with the annealing temperature. The contacts with bias-sputtered Nb, however, are much more stable than those with sputtered Nb. These improvements in contact characteristics before and after annealing are due to the effectively increased Nb thickness at the steps. Thus, the bias-sputtered Nb offers promise for wiring use in Josephson LSI application.

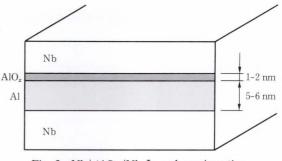

## 4.5 Cross-sectional TEM observation of junction structures

The microstructures of the  $Nb/AlO_x/Nb'$ junction were studied through cross-sectional TEM observation<sup>99)</sup>. Figure 46 shows the lattice image of the Nb/AlO<sub>x</sub>/Nb junction structure. The upper and lower Nb are 20-200 nm, with Al 14 nm thick. From the lattice image, two interesting pieces of information were obtained. One is the crystallization of Nb and Al (thin Al as well as Nb are polycrystalline films with columnar structures). Most grains are oriented to a certain plane; Nb(110) planes are parallel to the substrate. The orientation of Nb(110) is consistent with the results obtained by X-ray diffraction. Al is also oriented to the (111) plane. Thus, the crystalline Al grown on Nb is considered critical to producing highquality junctions. Also note that the upper Nb features a good crystalline structure just above the  $AlO_x$  barrier. This indicates that diffusion did not occur between the upper Nb and  $AlO_x$ barrier.

The other piece of information obtained concerns the Al and Nb interfaces. The interface between the lower Nb and Al is rough and wavy due to the rough surface of the lower Nb. The other interface between the upper Nb and  $AlO_x$  is sharp and clear. This indicates that AI planarizes the lower Nb surface. Consequently, the planarized Al surface is considered essential to growing an  $AlO_x$  barrier without pinholes.

The TEM studies indicated that a material combination of Nb, Al and  $AlO_x$  is nearly ideal for the Josephson junctions.

#### 5. Conclusion

This paper reviewed the fabrication technology developed in our laboratories for Josephson integrated circuits, and described the techniques used in the standard process for various circuits elements, Nb/AlO<sub>x</sub>/Nb junctions, SiO<sub>2</sub> insulators, Nb wiring, contacts, and Mo resistors. The key process to producing Josephson circuits is obtaining reliable and high-quality junctions. The characteristics of  $Nb/AlO_x/Nb$  junctions were found to satisfy these requirements almost perfectly. Therefore, a combination of Nb, Al and  $AlO_x$  is deemed the best one for Josephson junctions. This paper also described how process techniques were verified as being practical for Josephson circuits that include several thousand junctions, based on the characteristics of the 8K-bit cell array chips fabricated for process evaluation. Without the process technology based on the reliable  $Nb/AlO_x/Nb$  junctions, the ultra-high-speed operations recently achieved in Josephson integrated circuits would not have been possible. This paper also introduced the advanced process technology developed for future Josephson LSI application. These techniques satisfy demanding requirements to enhance circuit integration and improve process reliability even more.

Existing Josephson process technology was developed by several researchers. Although this technology may appear primitive when compared to semiconductor technology, the high-speed and low-power operation made possible when using Josephson logic and memory circuits are not possible with semiconductors. This verifies the potential application of Nb/AlO<sub>x</sub>/Nb Josephson junctions as digital devices in future high-speed computers. Based on the

$Nb/AlO_x/Nb$  junction technology, Josephson computer development may now be seriously undertaken. To achieve this lofty goal, many technical breakthroughs in process technology must be made, particularly in terms of reliability and uniformity. Perhaps a greater research effort should be initiated in the field of superconductive electronics.

#### References

- 1) Kammerlingh Onnes H.: Leiden Comm., 120b, 122b (1991).

- 2) Bardeen, J., Cooper, L.N., and Schrieffer, J.R.: *Phys. Rev.*, **108**, p. 1175 (1957).

- Josephson, B.D.: Possible new effects in superconductive tunnelling. *Phys. Lett.*, 1, pp. 251-252 (1962).

- Anderson, P.W., and Rowell, J.M.: Probable observation of the Josephson superconducting tunneling effect. *Phys. Rev. Lett.*, 10, 6, pp. 230-232 (1963).

- Matisoo, J.: Sub nanosecond pair tunneling to single-particle tunneling transition in Josephson junctions. *Appl. Phys. Lett.*, 9, 4, pp. 167-168 (1966).

- Matisoo, J.: The Tunneling Cryotron A Superconductive Logic Element Based on Electron Tunneling. *Proc. IEEE*, 55, 2, pp. 172-180 (1967).

- Anacker, W.A.: Potential of Superconductive Josephson Tunneling Technology for Ultrahigh Performance Memories and Processors. *IEEE Trans. Magnetics.*, MAG-5, pp. 968-975 (1969).

- Buck, D.A.: The cryotron A superconductive computer component. *Proc. IRE*, 44, pp. 482-493 (1956).

- Hayakawa, H.: Computing. "Superconducting Devices", Ruggiero, S.T. and Rudman D.A., ed., London, Academic Press, 1989, pp. 101-134.

- Kleinsasser, A.W., and Gallagher, W.J.: Threeterminal devices. "Superconducting Devices", Ruggiero, S.T. and Rudman D.A., ed., London, Academic Press, 1989, pp. 325-372.

- 11) Hamilton, C.A., McDonald, D.G., Sauvageau, J.E., and Whiteley S.R.: Standards and high-speed instrumentation. *Proc. IEEE*, **77**, 8, pp. 1224-1232 (1989).

- Williamson, S.J., and Kaufman, L.: Biomagnetism. J. Magnetism Magnetic Materials, 22, pp. 129-201 (1981).

- 13) Clarke, J.: SQUIDs, brains and gravity waves. *Physics Today*, **39**-3, pp. 32-44, (1986).

T. Imamura: Josephson Integrated Circuits I: Fabrication Technology

- 14) Ilmoniemi, R., Knuutila, J., Ryhänen, T., and Seppä, H.: "Multi-SQUID devices and their applications". Progress in Low Temperature Physics, Vol. XII Brewer, D.F., ed., Noth-Holland, 1989, pp. 271-339.

- Quing Hu and Richards, P.L.: Quasiparticle mixers and detectors. "Superconducting Devices", Ruggiero, S.T., and Rudman D.A., ed., London, Academic Press, 1989, pp. 169-196.

- Payne, J.M.: Millimeter and submillimeter wavelength radio astronomy. *Proc. IEEE*, 77, 7, pp. 993-1017 (1989).

- 17) Hasuo, S., and Imamura, T.: Digital logic circuits. *Proc. IEEE*, 77, 8, pp. 1177-1193 (1989).

- Wada, Y.: Josephson memory technology. Proc. IEEE, 77, 8, pp. 1194-1208 (1989).

- Hasuo, S.: Josephson Integrated Circuits II: High-Speed Digital Circuits. *FUJITSU Sci. Tech. J.*, 27, 1, pp. 28-58 (1991).

- Zappe, H.H., and Grebe, K.R.: Dynamic behavior of Josephson tunnel junctions in the subnanosecond range. J. Appl. Phys., 44, pp. 865-874 (1973).

- Harris, E.P.: Turn-on delays of Josephson interferometer logic devices. *IEEE Trans. Magnetics.*, MAG-15, pp. 562-565 (1979).

- 22) Anacker, W.: Josephson computer technology: An IBM Research project. *IBM J. Res. Dev.*, 24, pp. 107-112 (1980).

- Matisoo, J.: Overview of Josephson technology logic and memory. *IBM J. Res. Dev.*, 24, pp. 113-129 (1980).

- 24) Fulton, T.A., and Dunkleberger, L.N.: A Josephson multiplier, *Bell Syst. Tech. J.*, **61**, pp. 931-933 (1982).

- 25) Hasuo, S., Suzuki, H., and Dazai, K.: A parallel full adder circuit using Josephson junctions. *IEEE J. Solid-State Circuits*, SC-16, pp. 43-48 (1981).

- 26) Sone, J., Yoshida, T., Tahara, S., and Abe, H.: Resistor coupled Josephson logic full adder circuit. Tech. Dig. Int. Electron Devices Meet., 1982, pp. 762-765.

- 27) Ichimiya, Y., Yamada, H., and Ishida, A.: Josephson Two-bit Full Adder Utilizing Wide Margin Functional Gates. *IEEE Trans. Magnetics.*, MAG-19, pp. 1178-1181 (1983).

- 28) Robinson, A.L.: IBM Drops Superconducting Computer Project. Science, 222, pp. 492-494 (1983).

- 29) Greiner, J.H.: Oxidation of lead films by rf sputter

etching in an oxygen plasma. J. Appl. Phys., 45, pp. 32-37 (1974).

- 30) Greiner, J.H., Kircher, C.J., Klepner, S.P., Lahiri, S.K., Warnecks, A.J., Basavaiah, S., Yen, E.T., Baker, John M., Brosious, P.R., Huang, H.-C.W., Murakami, M., and Ames, I.: Fabrication Process for Josephson Integrated Circuits. *IBM J. Res. Dev.*, 24, pp. 195-205 (1980).

- 31) Imamura, T., Hoko, H., Tamura, H., Yoshida, A., Suzuki, H., Morohashi, S., Ohara, S., Hasuo, S., and Yamaoka, T.: Fabrication technology for leadalloy Josephson devices for high-density integrated circuits. J. Appl. Phys., 59, pp. 1720-1748 (1986).

- 32) Gurvitch, M., Washington, M.A., and Haggins, H.A.: High quality refractory Josephson tunnel junctions utilizing thin aluminum layers. *Appl. Phys. Lett.*, 42, pp. 472-474 (1983).

- 33) Morohashi, S., Shinoki, F., Shoji, A., Aoyagi, M., and Hayakawa, H.: High-quality Nb/Al-AlO<sub>X</sub>/Nb Josephson Junction. *Appl. Phys. Lett.*, 46, pp. 1179-1181 (1975).

- 34) Morohashi, S., and Hasuo, S.: Experimental investigations and analysis for high-quality Nb/Al-AlO<sub>X</sub>/Nb Josephson junctions. J. Appl. Phys., 61, pp. 4835-4849 (1987).

- 35) Kotani, S., Imamura, T., and Hasuo, S.: A 1.5-ps Josephson OR gate. Tech. Dig. Int. Electron Devices Meet., San Fransicso, 1988, pp. 884-885.

- 36) Kotani, S., Fujimaki, N., Imamura, T., and Hasuo, S.: A Josephson 4b Microprocessor. Dig. Tech. Papers Int. Solid-State Circuits Conf., 1988, pp. 150-151.

- 37) Kotani, S., Inoue, A., Imamura, T., and Hasuo, S.: A 1GOPS 8b Josephson Digital Signal Processor. Dig. Tech. Papers 1990 Int. Solid-State Circuits Conf., San Fransicso, 1990, pp. 148-149.

- 38) Fujimaki, N., Tamura, H., Imamura, T., and Hasuo, S.: A Single-chip SQUID magnetometer. *IEEE Trans. Electron Devices*, 35, 12, pp. 2412-2418 (1988).

- 39) Fujimaki, N.: Josephson Integrated Circuits III: A Single-Chip SQUID Magnetometer. *FUJITSU Sci. Tech. J.*, 27, 1, pp. 59-83 (1991).

- Solymar, L.: Superconductive Tunneling and Applications. London, Chapman and Hall, 1972, p. 405.

- Van Duzer, T., and Turner, C.W.: Principles of superconductive Devices and Circuits, New York, North Holland, 1981, p. 369.

- 42) Basavaiah, S., and Greiner, J.H.: An investigation

of thermal cycling of Pb-alloy Josephson tunneling gates. J. Appl. Phys., 48, 11, pp. 4630-4633 (1977).

- Lahiri, S.K., Basavaiah, S., and Kircher, C.J.: Lead alloy Josephson junctions with Pb-Bi counterelectrodes. *Appl. Phys. Lett.*, 36, 4, pp. 334-336 (1980).

- 44) Murakami, M., and Basson, J.H.: Thermal stability of Pb-alloy Josephson junction electrode materials: V. Effects of repeated cycling between 298 and 4.2 K of Pb-Bi counter electrode. J. Appl. Phys., 53, pp. 346-352 (1981).

- 45) Imamura, T., Hasuo, S., and Yamaoka, T.: Thermal cycling stability of lead-alloy Josephson junctions with double layer base electrode. *IEEE Trans. Magnetics.*, MAG-21, 2, pp. 122-125 (1985).

- 46) Raider, S.I.: Josephson tunnel junctions with refractory electrodes. *IEEE Trans. Magnetics.*, MAG-21, pp. 110-117 (1985).

- 47) Broom, R.F., Raider, S.I., Oosenbrug, A., Drake, R.E., and Walter, W.: Niobium oxidebarrier tunnel junction. *IEEE Trans. Electron Devices*, ED-27, pp. 1998-2008 (1980).

- 48) Broom, R.F., Oosenbrug, A., and Walter, W.: Josephson junctions of small area formed on the edges of niobium films, *Appl. Phys. Lett.*, 37, pp. 237-239 (1980).

- 49) Gallagher, W.J., Raider, S.I., and Drake, R.E.: Electrical characterization of Nb/Nb oxide/ PbAuIn Josephson tunnel junctions. *IEEE Trans. Magnetics.*, MAG-19, pp. 807-810 (1983).

- 50) Michikami, O., Tanabe, K., Kato, Y., and Takenaka, H.: Nb and Nb-based A15 compound tunnel junctions fabricated using a new CF4 cleaning procedure. *IEEE Trans. Magnetics*, MAG-21, pp. 528-531 (1985).

- 51) Broom, R.F., Laibowitz, R. B., Mohr, Th. O., and Walter, W.: Fabrication and properties of niobium Josephson tunnel junctions. *IBM J. Res. Dev.*, 24, pp. 212-222 (1980).

- 52) Kuan, T. S., Raider, S.I., and Drake, R. E.: Structure of a Nb Oxide tunnel barrier in a Josephson junction. J. Appl. Phys., 53, pp. 7464-7470 (1982).

- 53) Raider, S.I., Johnson, R.W., Kuan, T.S., Drake, R.E., and Pollak, R.A.: Characterization of Nb/Nb oxide structures in Josephson tunnel junctions. *IEEE Trans. Magnetics*, MAG-19, pp. 803-806 (1983).

- 54) Latta E.E., and Gasser, M.: Barrier composition and electrical properties of high-quality all-niobium

Josephson tunnel junctions. J. Appl. Phys., 54, pp. 1115-1119 (1983).

- 55) Kroger, H., Smith, L.N., and Jillie, D.W.: Selective niobium anodization process for fabicating Josephson tunnel junctions. *Appl. Phys. Lett.*, **39**, pp. 280-282 (1981).