# FUJITSU

# SCIENTIFIC & TECHNICAL JOURNAL

# Summer 1991 VOL.27, NO.2 Special Issue on Supercomputer VP2000 Series

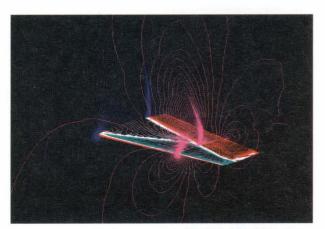

The Issue's Cover : Light by Hirofumi OHKUMA From nothing, an explosion of immense energy brings forth the universe. This idea is our continual inspiration.

FUJITSU Scientific & Technical Journal is published quarterly by FUJITSU LIMITED of Japan to report the results of research conducted by FUJITSU LIMITED, FUJITSU LABORATORIES LTD., and their associated companies in communications, electronics, and related fields. It is the publisher's intent that FSTJ will promote the international exchange of such information, and we encourage the distribution of FSTJ on an exchange basis. All correspondence concerning the exchange of periodicals should be addressed to the editor.

FSTJ can be purchased through KINOKUNIYA COMPANY LTD., 3-17-7 Shinjuku, Shinjuku-ku, Tokyo 160-91, (Telephone : +81-3-3439-0162, Facsimile : +81-3-3706-7479).

The price is US\$7.00 per copy, excluding postage.

FUJITSU LIMITED reserves all rights concerning the republication and publication after translation into other languages of articles appearing herein.

Permission to publish these articles may be obtained by contacting the editor.

| FUJITSU LIMITED           | Tadashi Sekizawa, President |

|---------------------------|-----------------------------|

| FUJITSU LABORATORIES LTD. | Masaka Ogi, President       |

Editorial Board Editor Takahiko Misugi Associated Editors Shigeru Sato Hideo Takahashi Editorial Representatives Tadashi Hasegawa Yoshimasa Miura Maku Yasushi Nakajima Hajime Nonogaki Seiya

Shinji Ohkawa Tohru Sato Jyun'ichi Tanahashi Toru Tsuda Akira Yoshida Yoshimasa Miura Hajime Nonogaki Shinya Okuda Yoshio Tago Hirobumi Takanashi Itsuo Umebu Makoto Mukai Seiya Ogawa Hirofumi Okuyama Shozo Taguchi Mitsuhiko Toda Yutaka Yamaoka

#### **Editorial Coordinator**

Yukichi Iwasaki

FUJITSU LIMITED 1015 Kamikodanaka, Nakahara-ku, Kawasaki 211, Japan Cable Address : FUJITSULIMITED KAWASAKI Telephone : +81-44-777-1111 Facsimile : +81-44-754-3562

Printed by MIZUNO PRITECH Co., Ltd. in Japan © 1991 FUJITSU LIMITED (June 20, 1991)

# FUjitsu

#### SCIENTIFIC & TECHNICAL JOURNAL

# Summer 1991 VOL.27, NO.2

Special Issue on Supercomputer VP2000 Series

CONTENTS

|     | <b>Featuring Papers</b>      |                                         |                                    |                    |

|-----|------------------------------|-----------------------------------------|------------------------------------|--------------------|

| 147 | Preface                      | ● Toshio Hiraguri                       |                                    |                    |

| 149 | System Overview of FUJITSL   | J VP2000 Series                         |                                    |                    |

|     |                              | ●Nobuo Uchida<br>●Kazuyuki Shimizu      | ●Yuji Oinaga                       | ● Hiroshi Tamura   |

| 158 | Hardware Technology for FU   | JITSU VP2000 Series                     |                                    |                    |

|     |                              | ●Akira Kaneko<br>●Takanobu Kano         | ●Kiyoshi Kuwabara                  | ●Shun-ichi Kikuchi |

| 169 | Semiconductor Devices for F  | UJITSU VP2000 Serie                     | es                                 |                    |

|     |                              | ●Ken-ichi Ohno<br>●Katsuhiko Suyama     | ●Kazuo Ooami                       | ● Hideo Itoh       |

| 179 | Multilayer Glass-Ceramic-Con | nposite Circuit Board                   | for FUJITSU VP2000                 | Series             |

|     |                              | ●Koichi Niwa                            | <ul> <li>Yukichi Takeda</li> </ul> |                    |

| 187 | Design Automation System for | or FUJITSU VP2000                       | Series                             |                    |

|     |                              | ● Hirofumi Hamamura<br>● Toshihiko Tada | ●Akihiko Hanafusa                  | ● Minoru Saitoh    |

| 197 | Basic Software for FUJITSU   | VP2000 Series                           |                                    |                    |

|     |                              | <ul> <li>Koh-Ichiro Hotta</li> </ul>    | ●Takashi Kunai                     | ●Yoshio Honma      |

| 211 | Atomic-Scale Simulations for | Semiconductors by S                     | upercomputer                       |                    |

|     |                              | ●Minoru Ikeda<br>●Masuhiro Mikami       | ●Kumiko Furuya                     | ●Takahiro Yamasaki |

| 222 | Computational Fluid Dynami   | ics and Computers                       |                                    |                    |

|     |                              | ●Satoru Ogawa                           | ●Yoko Takakura                     |                    |

| SYNOPSES (Featuring Papers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UDC 681.32<br>FUJITSU Sci. Tech. J., <b>27</b> , 2, pp. 149-157(1991)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | UDC 658.512.2:681.32<br>FUJITSU Sci. Tech. J., <b>27</b> , 2, pp. 187-196(1991)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| System Overview of FUJITSU VP2000 Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Design Automation System for FUJITSU VP2000 Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ● Nobuo Uchida ● Yuji Oinaga ● Hiroshi Tamura<br>● Kazuyuki Shimizu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ● Hirofumi Hamamura ● Akihiko Hanafusa ● Minoru Saitoh<br>● Toshihiko Tada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

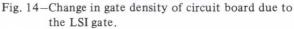

| The demand for high performance supercomputing has been<br>growing especially in the last several years. To meet this demand,<br>Fujitsu has developed the FUJITSU VP2000 series pipelined<br>supercomputers. This series has a maximum performance of<br>5 GFLOPS for a single processor. This paper describes the fea-<br>tures, system configuration, and functional outline of the VP2000<br>series.                                                                                                                                                                                                                                                                          | The performance of the FUJITSU VP2000 series computers is<br>high because they incorporate advanced technologies; for example,<br>ECL 15k-gate very-large-scale integrated circuits and multilayer<br>glass-ceramic-composite circuit boards. The VP2000 series was<br>developed using a design automation system (DA) that enabled the<br>ultrahigh-speed technology used in the series to be fully exploited.<br>This paper mainly describes the features of this DA system.                                                                                                                                                                                                                                                                  |

| UDC 681.32<br>FUJITSU Sci. Tech. J., <b>27</b> , 2, pp. 158-168(1991)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | UDC 681.32.06<br>FUJITSU Sci. Tech. J., <b>27</b> , 2, pp. 197-210(1991)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Hardware Technology for FUJITSU VP2000 Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Basic Software for FUJITSU VP2000 Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ● Akira Kaneko ● Kiyoshi Kuwabara ● Shun-ichi Kikuchi<br>● Takanobu Kano                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ● Koh-Ichiro Hotta ● Takashi Kunai ● Yoshio Honma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

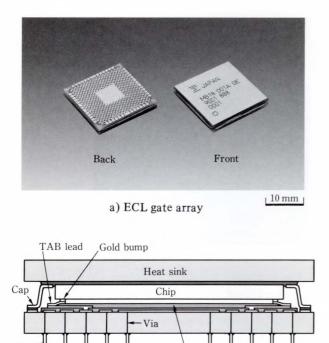

| Fujitsu has developed new packaging, cooling, and power supply<br>technology for new high-speed and high-density LSIs. This paper<br>introduces an ultra-miniature LSI package, a ceramic board on<br>which two million gates can be mounted, and high-performance<br>cooling and water-cooled power supply technology.                                                                                                                                                                                                                                                                                                                                                           | Since the first shipment of the FUJITSU VP-series, Fujitsu's policy regarding system software for supercomputers has been to supply systems that are as easy to use as a general purpose computer. Since then, the size of application programs has increased more and more, and progress made in computer networks has significantly changed the supercomputer environment. When the FUJITSU VP2000 series was released, new system software for the current environment was also developed. In this paper, the new system software is outlined.                                                                                                                                                                                               |

| UDC 621.3.049.774:681.32<br>FUJITSU Sci. Tech. J., <b>27</b> , 2, pp. 169-178(1991)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | UDC 548.5:681.32<br>FUJITSU Sci. Tech. J., <b>27</b> , 2, pp. 211-221(1991)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Semiconductor Devices for FUJITSU VP2000 Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Atomic-Scale Simulations for Semiconductors by Super-<br>computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • Ken-ichi Ohno  ● Kazuo Ooami  ● Hideo Itoh<br>• Katsuhiko Suyama                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ● Minoru Ikeda ● Kumiko Furuya ● Takahiro Yamasaki<br>● Masuhiko Mikami                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

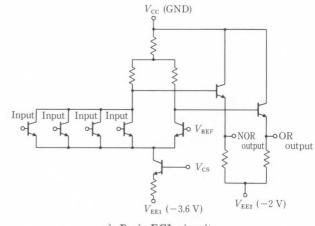

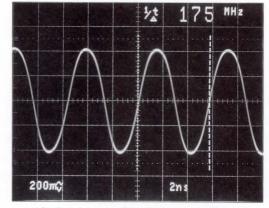

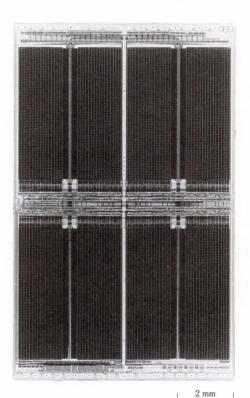

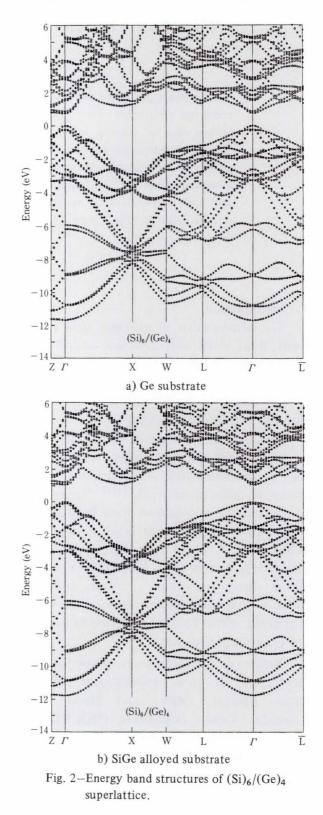

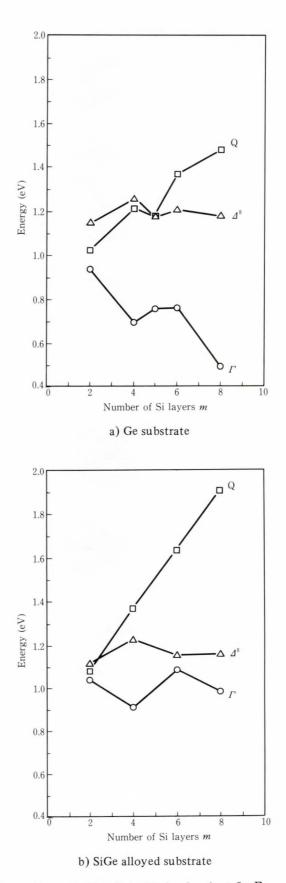

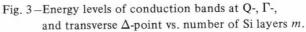

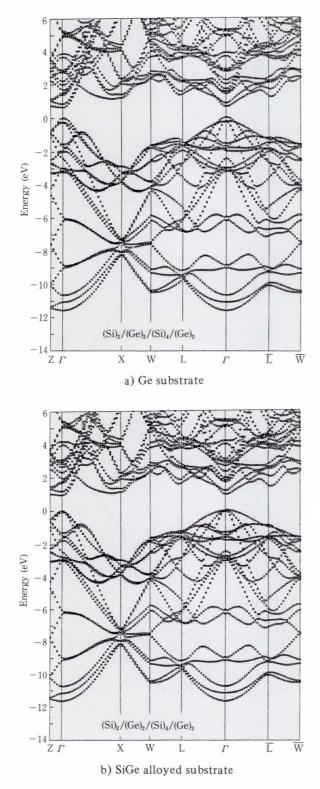

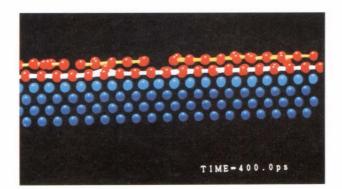

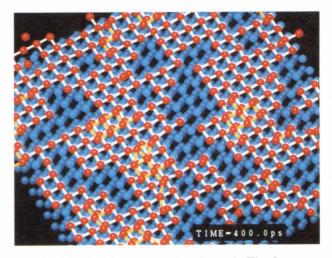

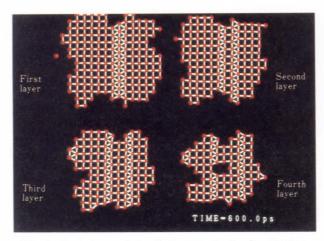

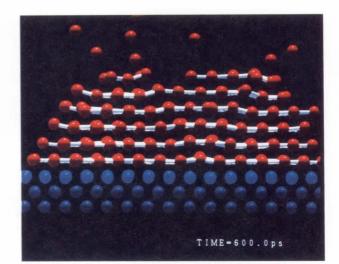

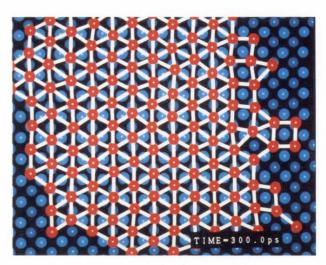

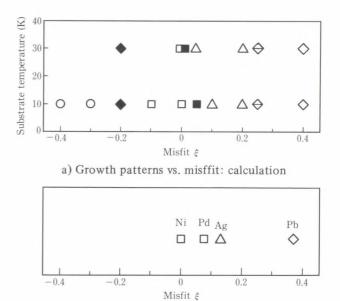

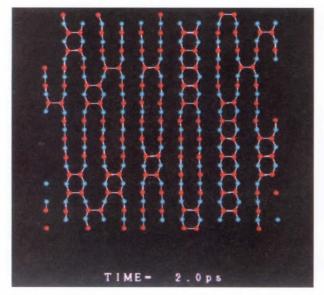

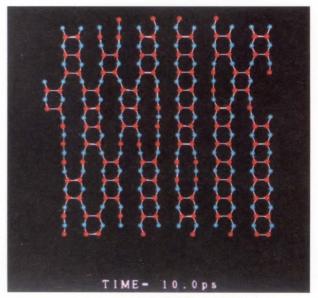

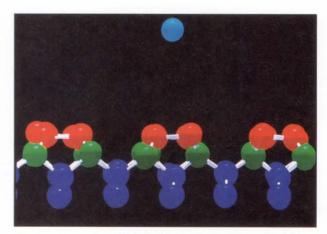

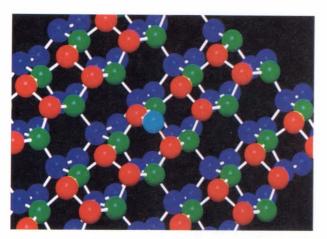

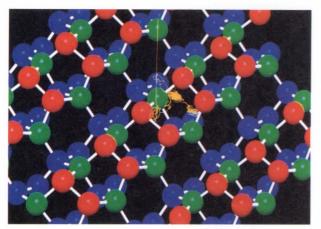

| Advanced silicon and GaAs technologies have been developed<br>and used in the high-speed, high-density LSIs of the FUJITSU<br>VP2000 series. The main LSIs are 15 000-gate ECL array with<br>a 70 ps propagation delay, 3 500-gate ECL array with 64-Kbit<br>STRAM and a 1.6 ns maximum access time, 1-Mbit static RAM<br>with a maximum access time of 35 ns, and 1 200-gate GaAs line<br>driver/receiver with a 60 ps propagation delay time.                                                                                                                                                                                                                                   | The electronic structure and crystal growth of semiconductor materials were studied using computer simulations. First, the energy bands and transition probability of Si-Ge superlattices were investigated. It was found that direct transition can be realized in $(Si)_5/(Ge)_5$ on a Ge substrate by zone folding and by breaking the inversion symmetry. Then, crystal growth by Molecular Beam Epitaxy was simulated for Lennard-Jones systems by applying molecular dynamics. The lattice mismatch produced various growth patterns, which agree well with experiments on metallic hetero-structures. It was found that Si adatoms on a reconstructed Si(100) surface diffuse anisotropically and make new stable dimers when they meet. |

| UDC 621.3.049:681.32<br>FUJITSU Sci. Tech. J., <b>27</b> , 2, pp. 179-186(1991)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UDC 532.5.01:681.32<br>FUJITSU Sci. Tech. J., <b>27</b> , 2, pp. 222-232(1991)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

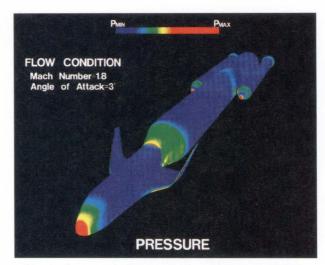

| Multilayer Glass-Ceramic-Composite Circuit Board for FUJITSU VP2000 Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Computational Fluid Dynamics and Computers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| • Koichi Niwa • Yukichi Takeda                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • Şatoru Ogawa   • Yoko Takakura                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

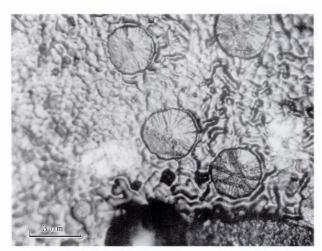

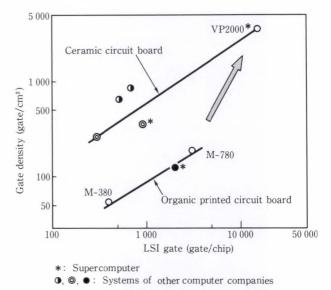

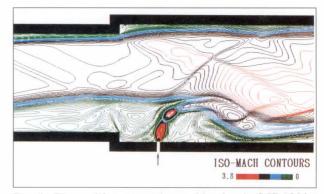

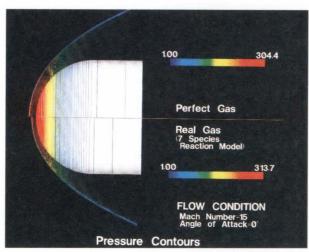

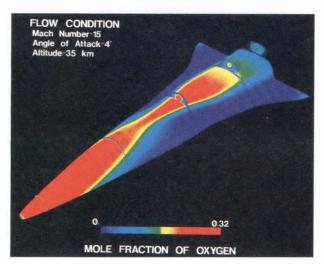

| A new glass-ceramic-composite material has been developed and<br>applied to the circuit board of the FUJITSU VP2000 series super-<br>computer. The composite material exhibits low dielectric constant<br>and low thermal expansion coefficient. These two characteristics<br>are capable of satisfying both present and future requirements of<br>high-speed signal propagation and high-density packaging of LSIs.<br>Copper conductors are used for the circuit wiring, which yields<br>low resistivity conductor wiring for as many as 61 layers. The gate<br>density of the VP2000 series is ten times higher than that of con-<br>ventional organic printed circuit boards. | This paper describes the participation of computational fluid<br>dynamics (CFD) and computers. First, the history and outline of<br>CFD are briefly explained. Next, advanced researches (computa-<br>tions of transonic flow with large separation, supersonic flow<br>around complex configulations, supersonic flow with combustion,<br>and hypersonic flow of real gas) in Computation laboratory of<br>National Aerospace Laboratory are shown. Finally, turbulence and<br>the future problems of CFD are described as impacted by com-<br>puter performance.                                                                                                                                                                              |

#### Preface

### Special Issue on Supercomputer VP2000 Series

#### Toshio Hiraguri

Managing Director, Computer Systems Group

Initially, supercomputers had only limited use in universities and national research centers, since then however, they have rapidly gained acceptance in a wide variety of industry applications. In universities, research centers and industries, research and development is being conducted making full use of leading edge technology. For the analysis of phenomena which is microscopic, momentary or heretofore unknown, the supercomputer plays an indispensable role. The challenge is to produce the highest speed computational machines, as well as a system environment that integrates supercomputers with workstations and personal computers to obtain the greatest benefit.

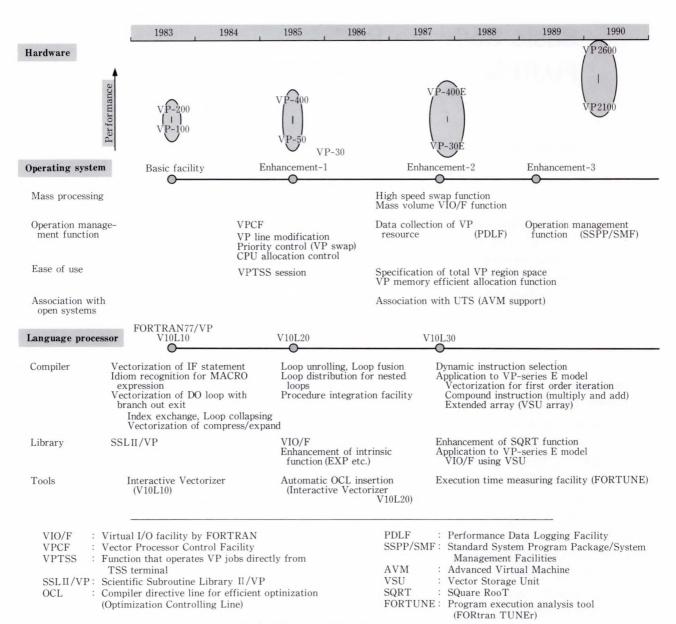

Fujitsu, a pioneer in developing supercomputers in Japan, shipped the FACOM 230-75 array processor in 1977. Based on the development experience gained with the predecessor, the FUJITSU VP-100 and VP-200 series were developed and shipped in 1983. Since then, the VP-30, VP-50, VP-400 and later the VP-E series have followed. Now Fujitsu offers the VP2000 series of supercomputers. Announced at the end of December 1988, the first shipments started in March 1990. About 30 of the VP2000 series have been installed around the world and over 120 systems are currently operating within the entire VP range. This success results from the high effective performance of application programs, compatibility with the FUJITSU M-series general-purpose computers and user-friendly systems. The new series incorporates these features and provides added power and functionality for today's research and development.

In this special issue, the development philosophy and features of the FUJITSU VP2000 series are described.

#### Super high-speed processing

The design target was to greatly improve not only the maximum performance but also the effective performance, as well as system expansibility. A performance of 5 GFLOPS, the highest order in the world for a single processor, has been achieved. Dual scalar processor (DSP) and quadruple scalar processor (QSP) multiprocessor architecture has also been implemented. The additional scalar unit significantly increases system performance, thereby dramatically improving the cost performance ratio and added flexibility to the system configuration. By using a new storage unit (system storage unit), the processing time of applications that have I/O intensive functions can be reduced, and the number of active TSS terminals using vector processing functions can be increased.

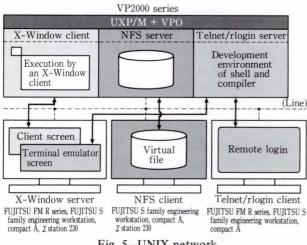

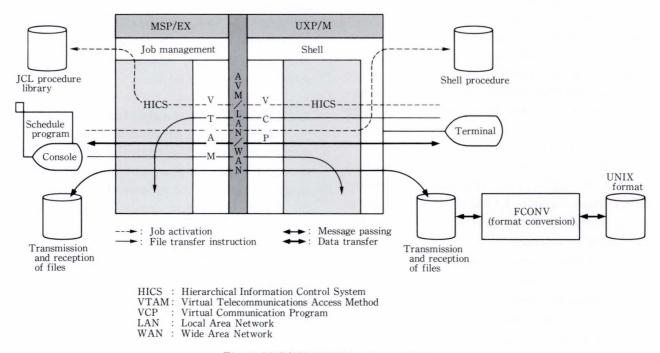

#### Adaption to the UNIX<sup>Note</sup>) environment

Workstations and open systems based on UNIX are spreading in research and development centers. To meet this requirement, Fujitsu's mainframe UNIX operating system, UXP/M, has a vector processor support option. All the operations for vector processing, from program development to high-speed vector execution, are supported in a UNIX environment. MSP/EX, Fujitsu's proprietary operating system has also been enhanced for UNIX compatibility by incorporating UNIX functions into MSP/EX and can be run with UXP/M under advanced virtual machine (AVM).

#### Enhancement to language processing system

A high level optimizing function for the compiler is required to achieve a high effective performance for program execution. The new FORTRAN compiler has improved vectorizing and optimizing capability to achieve this. The compiler also provides a sophisticated parallel processing facility to reduce elapsed time of execution of programs when run in a DSP or QSP environment. Fujitsu also provides an enhanced interactive tuning tool to improve performance of applications.

This special issue also discusses new technologies introduced with the VP2000 series. The last part of the issue contains two papers on supercomputer applications. The first paper, Atomic-Scale Simulations for Semiconductors by Supercomputer, discusses the use of supercomputers in the study of semiconductor materials. The second paper, Computational Fluid Dynamics and Computers, describes the application of supercomputers to computational fluid dynamics (CFD), which is a method widely used in engineering fields. These are two areas which have greatly benefited through the introduction of supercomputers.

Researchers and developers place a continuous demand for higher and higher levels of performance and Fujitsu is now targeting performance levels in the tera-FLOPS range. Fujitsu will continue to develop leading edge hardware and software technology for massively parallel processing. Fujitsu also supports open systems and is enhancing the user's interface. Furthermore, Fujitsu will substantially increase the body of application software available.

Fujitsu is continually developing supercomputers that can meet the current requirements and future needs of our researchers and engineers.

Note: The UNIX operating system was developed and is licensed by UNIX System Laboratories, Inc.

UDC 681.32

# System Overview of FUJITSU VP2000 Series

• Nobuo Uchida • Yuji Oinaga • Hiroshi Tamura • Kazuyuki Shimizu

(Manuscript received December 19, 1990)

The demand for high performance supercomputing has been growing especially in the last several years. To meet this demand, Fujitsu has developed the FUJITSU VP2000 series pipelined supercomputers. This series has a maximum performance of 5 GFLOPS for a single processor. This paper describes the features, system configuration, and functional outline of the VP2000 series.

#### 1. Introduction

The rapidly growing field of technical calculation is boosting the demand for highperformance supercomputers. Many users in various fields require supercomputers that are more efficient and easier to use than conventional systems. This is especially true in the fields of fluid dynamics, image processing, resource exploration, meteorological forecasting, molecular dynamics, and energy analysis.

For more versatile applications, it has become necessary to link UNIX<sup>Note)</sup> systems (prevalent in research and development areas), and to create easy-to-use open systems of linked workstations. The new FUJITSU VP2000 series are efficient, easy-to-use supercomputers. They have been developed using the latest technology and the experience gained from developing the preceding VP-series<sup>1)</sup>.

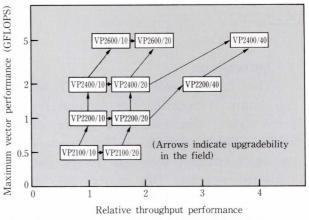

The VP2000 series consists of the following basic models (in descending order of vector performance): VP2600 (high-end model), VP2400, VP2200, and VP2100 (low-end model). There are three types of scalar processor configurations: the uni-processor (model 10), dual scalar processor (model 20), and quadruple scalar processor (model 40). In total, there are ten models, all of which can be upgraded in the field.

#### 2. Features of VP2000 series

#### 2.1 High-speed operation

The VP2000 series features superb performance based on super-high-speed, highdensity technologies and an improved pipeline structure. The instruction set is efficient enough to extend the vector processing range<sup>2)</sup>. Therefore, the parallel processing level of vector processing is raised and software can fully exploit the hardware functions. At 5 GFLOPS, the VP2600/10 has the highest performance for a single processor. This figure is about triple the performance of the previous VPseries.

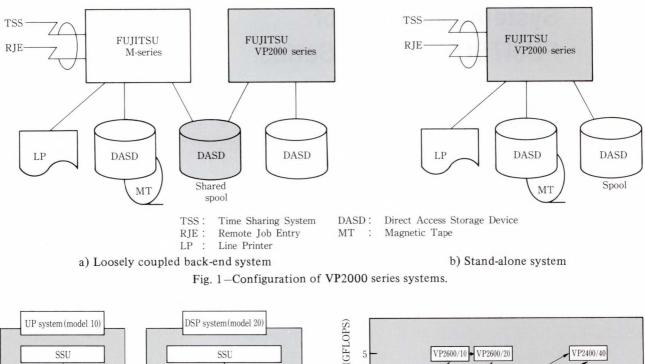

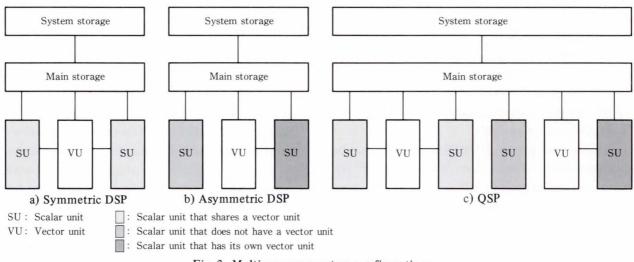

#### 2.2 Flexibility

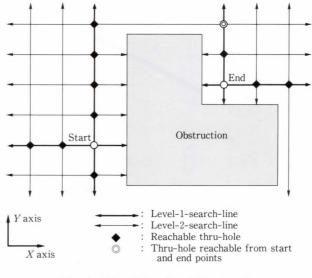

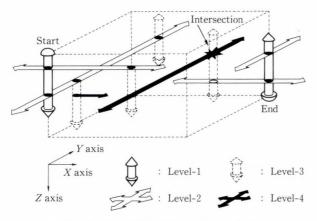

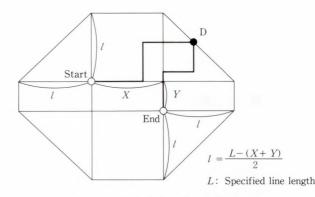

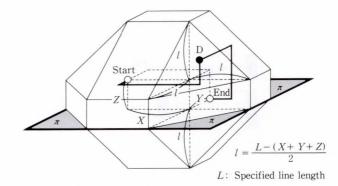

There are two types of VP2000 series systems that operate under the MSP operating system. These are the stand-alone system and the loosely coupled back-end system (see Fig. 1). In the back-end system, the functions and workloads can be distributed optimally by connecting a front-end processor. This type enables the VP2000 series models to run

Note: The UNIX operating system was developed and is licensed by UNIX System Laboratories, Inc.

N. Uchida et al.: System Overview of FUJITSU VP2000 Series

Fig. 2–Processor configuration of each system.

at their full super-high-speed as processors for high-speed operations. In the stand-alone system, the VP2000 series executes processing, from program development to high-speed execution, in the same way as a general purpose system.

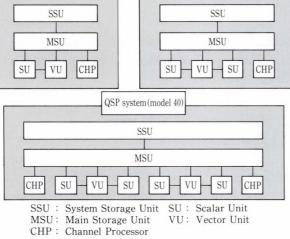

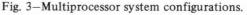

The VP2000 series computers have one, two, or four scalar processors. These configurations are called the uni-processor (UP), dual scalar processor (DSP), and quadruple scalar processor (QSP) configurations respectively. The UP is the basic configuration, and has a scalar unit and a vector unit. The DSP is a new type of multiprocessor system in which two scalar units share a vector unit. The QSP is

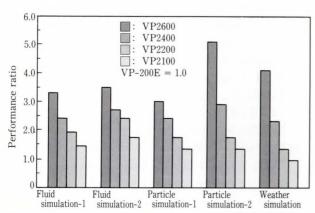

Fig. 3-Overall performance of VP2000 series models.

multiprocessor system having four scalar units and two vector units. These systems can be controlled by software in the same way as an ordinary multiprocessor system without the need to consider the vector unit shared between two scalar units.

The VP2000 series maintains complete upward compatibility with the previous VPseries and consists of ten models. Figure 2 shows the processor configuration of each system. Figure 3 compares the overall performance of the each models.

#### 2.3 High cost-performance

The VP2000 series models are high performance supercomputers that require a small installation space and low operating power. This series consumes about three-quarters of the power consumed by the previous VPseries uni-processor system. This reduction has been achieved by developing advanced LSI, packaging, and high-performance cooling technologies. These new technologies have nearly tripled the ratio of maximum performance to power consumption. They have also reduced the installation space to about 2/3 that of the previous VP-series. For example, the new scalar unit is contained on a single 24.5 cm square board<sup>3)</sup>. The ratio of maximum performance to installation area has been increased 3.5 times.

#### 3. Outline of VP2000 series models

#### 3.1 System configuration

Figure 2 shows the processor configuration of each VP2000 series computer. Figure 3 compares the overall performance of the ten models. As the figure shows, overall performance increases with vector performance and the number of scalar units.

Since the DSP and QSP systems have two

or four scalar units, the job load distribution can be optimized. For example, in the DSP system, scalar jobs not requiring the vector unit can be entered on a scalar unit while the other scalar unit uses the vector unit to execute highly vectorized jobs. Or, to ensure a high vector unit operating efficiency, mediumvectorized jobs can be entered on both scalar units in order to share the vector unit between jobs.

#### 3.2 Components

The VP2000 series models consists of the following units:

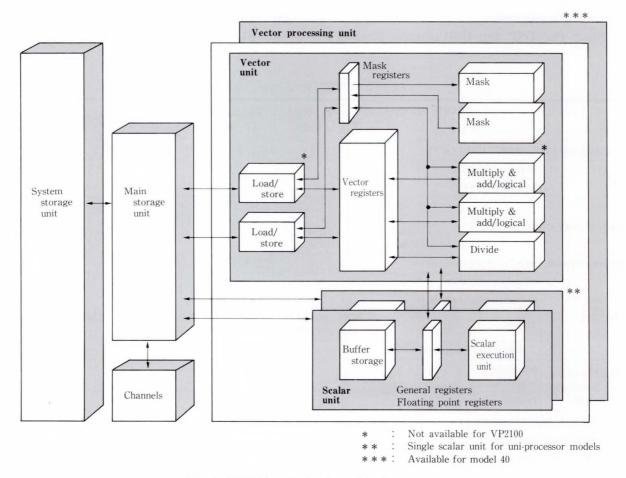

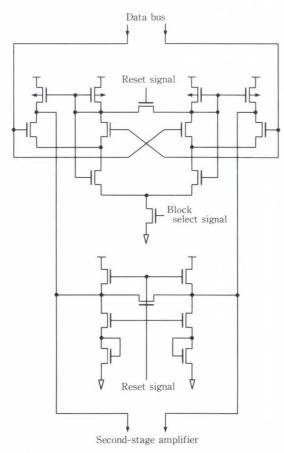

1) Vector processing unit (VPU)

The VPU can be compared to the central processing unit (CPU) of a general-purpose computer. It consists of a scalar unit (SU) and a vector unit (VU) that contain 15 000-gate ECL LSIs, and 64-Kbit RAM & logic LSIs<sup>4</sup>). The SU fetches scalar and vector instructions, and executes scalar instructions, interrupt processing, and machine check processing. The SU has a 128-Kbyte high-speed buffer

| Item                             | Model                     | VP2100/<br>10, 20                                                                                   | VP2200/<br>10, 20                 | VP2400/<br>10, 20    | VP2600/<br>10, 20          | VP2200/40 | VP2400/40                  |  |

|----------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|----------------------------|-----------|----------------------------|--|

| Vector peak p                    | erformance (GFLOPS)       | 0.5                                                                                                 | 1                                 | 2                    | 5                          | 2         | 5                          |  |

| CDU                              | Number of VUs             | 1                                                                                                   |                                   |                      |                            | 1         | 2                          |  |

| CPU Number of SUs                |                           | 1-2                                                                                                 |                                   |                      |                            | 4         |                            |  |

| Main storage o                   | capacity (Mbyte)          | 64, 128<br>192, 256<br>384, 512<br>768, 1024                                                        | 128, 256<br>384, 512<br>768, 1024 | 256, 512<br>768,1024 | 512, 1 024<br>1 536, 2 048 |           | 512, 1 024<br>1 536, 2 048 |  |

| System storag                    | e capacity (Gbyte)        |                                                                                                     |                                   | 1, 2, 4, 6, 8, 1     | 12, 16, 24, 32             |           |                            |  |

| Number of CHPs                   | 1                         |                                                                                                     |                                   | 1-2                  |                            |           |                            |  |

|                                  | Number of channels        | Max 128                                                                                             |                                   |                      |                            | Max 256   |                            |  |

| Channel                          | Types                     | MXC, BMC (4.5 Mbyte/s), High speed optical (36 Mbyte/s)<br>Optical (9 Mbyte/s), HIPPI (100 Mbyte/s) |                                   |                      |                            |           |                            |  |

|                                  | Throughput (Gbyte/s)      | Max 1                                                                                               |                                   |                      |                            | Max 2     |                            |  |

| Number of<br>arithmetic          | Multiply &<br>add/logical | 1 2                                                                                                 |                                   | 4                    |                            |           |                            |  |

| pipelines                        | 5 Divide 1 1              |                                                                                                     | 2                                 |                      |                            |           |                            |  |

| Number of load/store pipelines   |                           | 1                                                                                                   | 1 2                               |                      | 4                          |           |                            |  |

| Vector pipeline throughput/cycle |                           | 1                                                                                                   |                                   | 2                    | 4                          | 1         | 2                          |  |

| Capacity of ve                   | ector register (Kbyte/SU) | 3                                                                                                   | 2                                 | 64                   | 128                        | 32        | 64                         |  |

| Capacity of bu                   | affer storage (Kbyte/SU)  |                                                                                                     |                                   | 12                   | 28                         |           |                            |  |

Table 1 VP2000 series specifications

storage for quick processing. Vector instructions are issued from the SU and executed in the VU. The VU consists of large-capacity vector registers and plural vector pipelines.

2) Main storage unit (MSU)

This unit uses high-speed 1-Mbit static RAMs to process multiple memory accesses from the VPU at high speed. The maximum capacity in the system is 2 Gbytes.

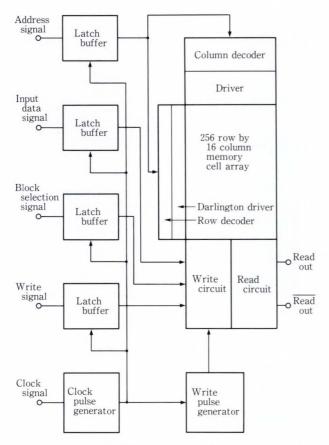

3) System storage unit (SSU)

The SSU is a large-capacity storage unit positioned above the MSU. This is the first time the SSU has been provided in a system. The SSU uses 4-Mbit DRAMs to achieve a maximum capacity of 32 Gbytes. It can be used as the swapping area for jobs, and as a virtual filling area for I/O operations to achieve a higher system throughput. GaAs LSIs with 1 200 gates are used in the data bus logic to attain a higher throughput between the SSU and the MSU.

4) Channel processor (CHP)

There are four types of channels: the 4.5 Mbyte/s electrical channel, 9 Mbyte/s optical channel, 36 Mbyte/s high-speed-optical channel, and 100 Mbyte/s HIgh Performance Parallel Interface (HIPPI)<sup>N ote)</sup> channel. A total throughput of 2 Gbyte/s can be attained using the maximum configuration of 256 channels. Peripheral devices can be placed as far as 2 km away using optical channels.

#### 3.3 Performance and specifications

Table 1 gives the specifications of the VP2000 series. Figure 3 compares the overall performance of each model in the series and the four levels of vector performance that are available (i.e. from 0.5 GFLOPS to 5 GFLOPS).

#### 4. Vector processing unit (VPU)

The VPU executes vector and scalar opera-

Note: An interface specification of the ANSI standards.

Fig. 4-VP2000 series hardware block diagram.

tions and has the same FUJITSU M-series architecture that is used in Fujitsu's general purpose computers. This chapter describes the features of the advanced hardware for high speed processing in the VPU.

#### 4.1 Hardware configuration

Figure 4 shows the hardware block diagram of the VP2000 series. The VPU is connected to the MSU so that it can fetch instructions and data from the MSU and transfer data to the MSU. The SU has a buffer storage unit, registers, and a scalar arithmetic unit. Instructions and data from the MSU are stored in the buffer storage, and then transferred to the scalar arithmetic unit for high-speed processing of scalar instructions.

The VU has vector registers, mask registers, and plural vector pipelines. The basic configuration of vector registers can have up to 256 8-byte registers, numbered from 0 to 255. Each model has the specified number of elements per register (64 for VP2600, 32 for VP2400, and 16 for all other models). The vector register is between the MSU and the vector operation pipelines. This register contains a large amount of vector data so that access to the MSU can be minimized. As with previous supercomputers, to fully utilize the total capacity, the vector registers may be concatenated to form the following configurations: 64 (number of elements)  $\times$  256 (number of registers),  $128 \times 128$ ,  $256 \times 64$ , ...,  $2048 \times 8$ .

Up to 256 mask registers, numbered from 0 to 255, are available. These mask registers are 1-bit registers. As with the vector registers, each model consists of the specified number of elements, and the mask registers can also be concatenated.

As well as simple DO loops with only four arithmetic rules, a FORTRAN program can also have many complicated DO loops with conditional statements (IF statements). Therefore, masked operation, compress/expand, and list vector functions can be used as required to vectorize IF operations and to improve the execution efficiency<sup>1)</sup>. The mask register keeps the mask data for the arithmetic mask function that specifies each masking or vectorization. (The vector pipelines execute operations on elements corresponding to vector data according to 1/0 patterns in the mask data.) This approach extends the vector processing range.

The load/store pipeline processes access to the main storage data specified by vector instructions. Load or store data is transferred between the MSU and the vector/mask registers. The logical addresses used for access to the MSU are rapidly translated into real addresses by the predetermined hardware address translation table under the specified page size<sup>1)</sup>.

The mask pipeline operates on mask data. All models have two mask pipelines: one for total summation/retrieval processing and the other for logical operations.

The multiply & add/logical operation pipeline is the so-called universal pipeline. This pipeline executes the multiply, add, multiply & add, first order recurrence, and logical operation functions. This pipeline enables hardware to execute vector instructions flexibly according to various program sequences.

The divide pipeline executes divide instructions exclusively.

#### 4.2 Instruction control

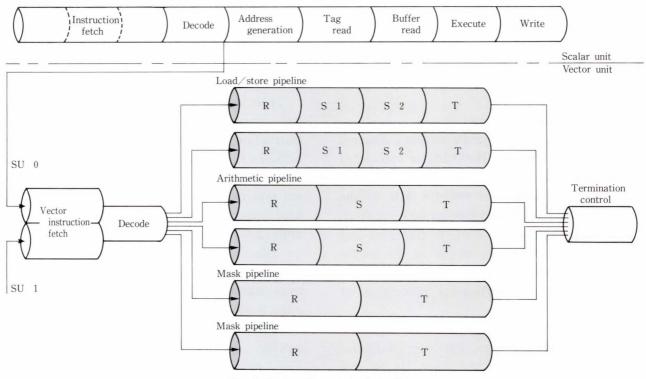

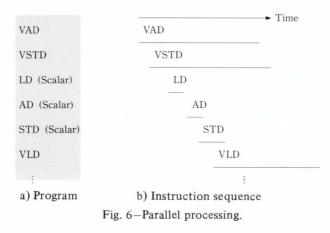

Figure 5 shows the control instruction pipeline of the VPU. The VP2000 series VPU has arithmetic control pipelines to concurrently execute vector and scalar instructions, or vector and vector instructions.

#### 1) Parallel instruction execution

Scalar instructions are executed in the SU. Vector instructions are issued to the VU. The VU controls instruction execution by transmitting the instruction to the vector control pipeline appropriate to the execution type. In the VU, two load/store pipelines (one for VP2100), two mask pipelines, and two of the three arithmetic operation pipelines (one of two for VP2100) can operate concurrently. The SU and at up to six of the seven vector pipelines (up to four for VP2100) can, therefore, operate concurrently (see Fig. 6). Also available is a linkage facility which allows two pipelines to be connected logically for continuous operations as N. Uchida et al.: System Overview of FUJITSU VP2000 Series

Fig. 5-Instruction control pipeline.

if they were a single pipeline. By using this facility, a vector instruction can start to read the vector register or the mask register written by the preceding instruction without waiting for completion of the preceding instruction. 2) Continuous instruction execution

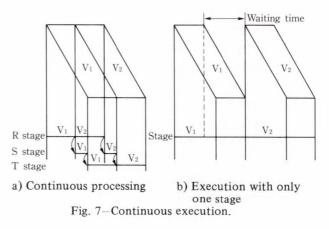

Each instruction control pipeline in the VU consists of an R, S, and T stage. A vector instruction is controlled and executed through the register at an appropriate stage in the pipeline. The R stage controls the fetching of operand data and the start of instruction execution. The T stage controls the storage of operand

data and the termination of instruction processing. The S stage is an intermediate stage between R and T. When a vector instruction completes the R stage, the information required for instruction control is retained in the S stage until the instruction moves into the T stage. This allows the next instruction to be executed immediately in the R stage after the preceding instruction is issued (see Fig. 7).

#### 4.3 High speed processing functions

Some vector instructions write data into a scalar register. When the SU detects this type of instruction, it checks whether the next scalar instruction will need the register operand. If the next instruction needs the data, the instruction must wait until the vector instruction finishes writing data into the register. If the next instruction does not need the register operand, it can be executed immediately. If a subsequent instruction needs to read to scalar register written by the previous vector instruction, it can use the data by bypassing the next data to be written into the VU without having to wait until the register has been set.

A vector instruction that randomly accesses the main storage address may access the same address repeatedly. To avoid these wasteful accesses to the main storage unit in high-speed processing, only one access is required. In the VP2000 series, high performance is realized by using these unique functions to control the hardware.

#### 5. Main storage unit (MSU)

A supercomputer must have a main storage unit with a large capacity, high-speed access, and high throughput. The RAS function is also important for stabilizing the system operation.

#### 5.1 Capacity and performance of main storage

A capacity of 64 Mbytes per array card and 512 Mbytes per unit has been achieved using new technologies. Models VP2600/10, VP2600/ 20, and VP2400/40 have a maximum main storage capacity of 2 Gbytes. The large-capacity MSU is accessed from the SU, VU, and CHP. For the VU, the throughput between the MSU and the vector registers is important. That is, the MSU must supply the necessary data to the vector register according to the operational capacity of the vector operation pipelines. Therefore, each VP2000 series supercomputer has a data bus suitable for the operation capacity between the MSU and the VU. The VP2600 and VP2400/40 models also have sufficient interleave for 512 ways (units of independent access to memory).

#### 5.2 RAS function

The MSU has an extended error checking and correction (ECC) function that automatical-

ly corrects single-bit errors and detects all double-bit errors and multi-bit errors in a single block (four bits). The MSU also has a function that detects single-bit fixed errors in a RAM and automatically replaces the RAM with a spare chip. This function, called the automatic alternate memory allocation function, assures a high immunity against fixed errors.

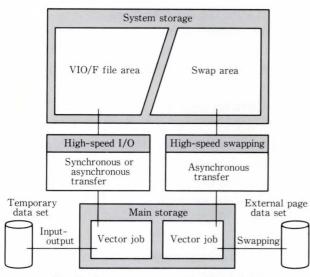

#### 6. System storage unit (SSU)

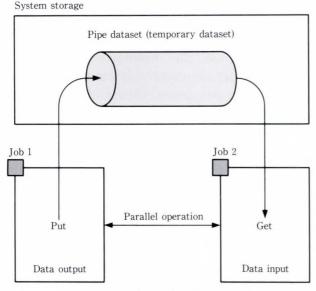

The new SSU used in the VP2000 series has a large storage capacity for the vector processing swap area and the I/O virtual file area<sup>5)</sup>. The SSU further enhances the system throughput.

#### 6.1 Capacity and performance

The SSU has a capacity of 1 Gbyte to 32 Gbytes and can exchange data with the MSU. The speed of data transfer between the SSU and the MSU must be sufficient for large amounts of data. The VP2600 can transfer data between the SSU and the MSU at up to 2 Gbyte/s.

#### 6.2 Transfer instruction

Two types of transfer instructions are used: synchronous and asynchronous.

#### 1) Synchronous transfer instructions

In this type of instruction, the instruction and the transfer operate synchronously. Data transfer begins at the start of the transfer instruction, and the instruction terminates after the data transfer is completed. The VPU waits until the instruction finishes.

#### 2) Asynchronous transfer instructions

This type of instruction transfers data asynchronously. Data transfer begins at the end of the transfer instruction. The data transfer is executed independently and its termination is reported by an interruption. When an asynchronous transfer instruction is issued, the VPU executes the next instruction independently without waiting for the termination of the data transfer. This releases the VPU from transfer instructions so that it can process high-speed arithmetic instructions concurrently with the data transfer. N. Uchida et al.: System Overview of FUJITSU VP2000 Series

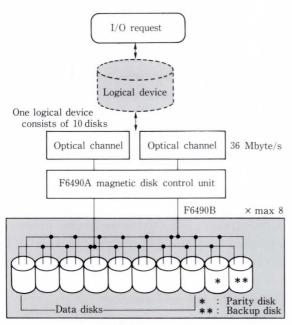

Fig. 8-Disk array subsystem.

#### 6.3 RAS function

The SSU has an ECC function for automatic detection and correction of all single-bit errors and for detection of all double-bit errors.

To prevent a single-bit error from becoming a double-bit error, the memory patrol function periodically reads data from storage and corrects any detected single-bit errors. Also, if a single-bit fixed error is detected in the RAM, the automatic alternate memory allocation function replaces the RAM with a spare one. This function improves immunity against fixed errors.

#### 7. New channels

The VP2000 series computers have two new types of high-throughput channels that improve the I/O transfer rate and simplify connection to an open network.

#### 7.1 High-speed optical channel

The 36 Mbyte/s optical channel can connect the F6490 large-capacity high-speed disk unit<sup>6)</sup>. F6490 contains an array of ten disks (see Fig. 8). The 8-byte data is distributed among eight of these disks (1 byte per disk). The remaining two disks are used as a parity disk and a backup disk. If a fixed error occurs in one of the eight disks, an alternate allocation function replaces the disk with the backup disk. This method enables a higher throughput and higher reliability than conventional type disk units.

#### 7.2 HIPPI channel

A HIPPI channel with a 100 Mbyte/s throughput can be connected to the Ultra-Net<sup>N ote)</sup>, the high-speed, multi-vender LAN. This connection enables high-speed data transfer between a VP2000 series supercomputer and workstations under a multi-vender environment.

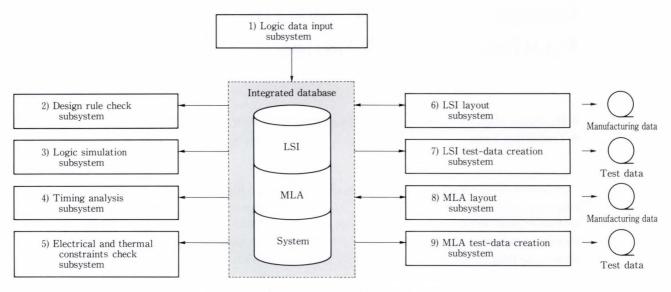

#### 8. Multiprocessor system

The multiprocessor system improves the overall system performance. There are two types of multiprocessor system: the dual scalar processor (DSP) and the quadruple scalar processor (QSP).

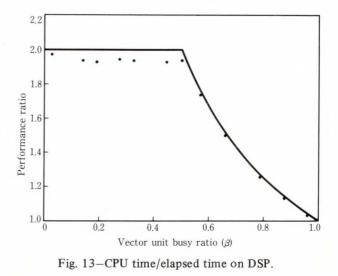

#### 8.1 Dual scalar processor (DSP)

The DSP is a new architecture for multiprocessor systems. It increases system performance by attaching another scalar unit.

In ordinary vectorized application programs, the use-rate of the VU rarely reaches 100 percent. For example, a program with a vectorization ratio as high as 90 percent uses the VU for less than 50 percent of the total CPU time. Therefore, an extra SU that shares one VU can be attached in order to increase system performance.

The VU has a programmable register for each SU (see Table 1). This hardware allows software to control the system in the same way as in an ordinary multiprocessor system. Vector instructions issued by the two SUs are alternately selected by hardware (SU 0 and SU 1 each correspond to the SU in a DSP system), and are then transmitted to the pipelines for execution (see Fig. 5).

If all jobs are scalar jobs, a DSP system has double the throughput of a UP system. However, this advantage decreases in proportion to the vectorization ratio of programs. If all jobs are vector jobs, the throughputs of these two systems are the same. For example, if the vector vs scalar speedup factor is ten and there is no

Note: Ultra-Net is a registered trademark of Ultra Network Technologies, Inc. USA.

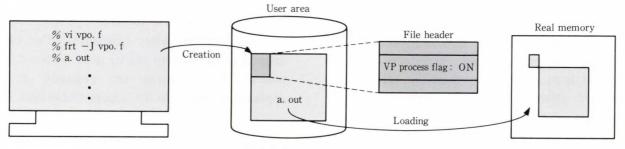

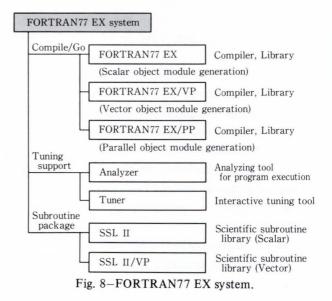

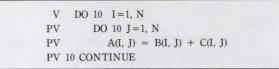

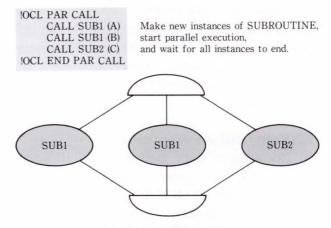

contention of vector unit usage, a DSP system will have double the throughput even if both programs running on the DSP system have a 91 percent vectorization ratio.

#### 8.2 Quadruple scalar processor (QSP)

In the VP2200 and VP2400 models, there is another type of multiprocessor system, the QSP. The QSP system uses four SUs and two VUs, and is configured as a multiprocessor with two DSP systems tightly coupled to the MSU. In this configuration, the software can regard the system as an ordinary multiprocessor with four processors. In the QSP system, multi-tasking can be performed by distributing the tasks of a single job to the processors<sup>5</sup>.

#### 9. Conclusion

This paper introduced the features, system configurations, and functions of the VP2000 series. There is an enormous demand for highspeed processing of large-scale scientific and technical calculations. To satisfy this demand, faster and larger systems must be realized. This can be achieved by increasing the processing speed, developing new parallel processing architectures, creating parallel large-scale systems, generating advanced software, and developing new devices and technologies.

By incorporating high-speed channels, high-

speed disks, and image processing for high-speed I/O operations, Fujitsu will continue to develop open systems that are adaptable to the standard UNIX culture. Also, Fujitsu intends to perfect a multi-vendor environment that will support equipment ranging from EWSs to supercomputers.

#### References

- Tamura, H., Shinkai, Y., and Isobe, F.: The Supercomputer FACOM VP System. *FUJITSU Sci. Tech. J.* 21, 1, pp. 90-108 (1985).

- Uchida, N.: Architecture of VP2000 Series. InfoJapan'90 Information Technology Harmonizing with Society, Inf. Proc. Soc., Jpn., 1990, pp. 247-253.

- 3) Kaneko, A. et al.: Hardware Technology for FUJITSU VP2000 Series, *FUJITSU Sci. Tech. J.*, 27, 2 (Special Issue on Supercomputer VP2000 Series), pp. 158-168 (1991).

- 4) Ohno, K., et al.: Semiconductor Devices for FUJITSU VP2000 Series, *FUJITSU Sci. Tech. J.*, 27, 2 (Special Issue on Supercomputer VP2000 Series), pp. 169-178 (1991).

- Hotta, K. et al.: Basic Software for FUJITSU VP2000 Series, *FUJITSU Sci. Tech. J.*, 27, 2 (Special Issue on Supercomputer VP2000 Series), pp. 197-210 (1991).

- Oyama, T., Ogawa, Y., and Sugiyama, K.: F6490 Magnetic Disk Subsystem: DIA. *FUJITSU Sci. Tech. J.*, 26, 4 (Special Issue on Fujitsu File Devices), pp. 291-295 (1991).

Nobuo Uchida Computer Engineering Dept. Main Frame Div. FUJITSU LIMITED Bachelor of Electrical Eng. Waseda University 1982 Specializing in Computer Engineering

Hiroshi Tamura Computer Engineering Dept. Main Frame Div. FUJITSU LIMITED Bachelor of Electrical Eng. Yokohama National University 1969 Specializing in Computer Engineering

Yuji Oinaga Computer Engineering Dept. Main Frame Div. FUJITSU LIMITED Bachelor of Science Eng. Hokkaido University 1974 Specializing in Computer Engineering

Kazuyuki Shimizu Processor Development Div. FUJITSU LIMITED Bachelor of Electronic Eng. Nagoya Institute of Technology 1966 Specializing in Computer Engineering

UDC 681.32

# Hardware Technology for FUJITSU VP2000 Series

• Akira Kaneko • Kiyoshi Kuwabara • Shun-ichi Kikuchi • Takanobu Kano

(Manuscript received December 27, 1990)

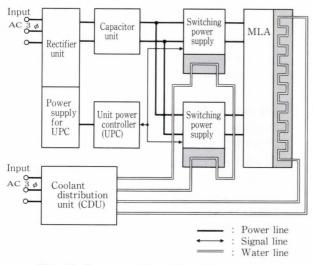

Fujitsu has developed new packaging, cooling, and power supply technology for new highspeed and high-density LSIs. This paper introduces an ultra-miniature LSI package, a ceramic board on which two million gates can be mounted, and high-performance cooling and water-cooled power supply technology.

#### 1. Introduction

Supercomputer performance depends primarily on hardware technology. Especially, semiconductor technology improvements and packaging technology advancements have contributed to the rapid progress of supercomputer performance by increasing the clock speed and making high-density gate packaging possible.

The clock cycle time is closely related to the signal propagation delay in LSIs and the board on which LSIs are mounted. In order to develop the FUJITSU VP2000 series high-speed super-computer, high-speed LSIs, high-density ceramic boards, a high-performance cooling system and water-cooled power supply have been developed.

The major part of the VP2000 was built with ECL technology to achieve the fastest commercially available gate delay. In addition to the high-speed ECL LSI, a GaAs LSI was developed for signal transmission from large capacity strage unit to the vector processing unit. Details of the LSI technology are explained in another paper in this journal<sup>1)</sup>.

As the LSI gate count increases, it is necessary to increase the LSI pin count, and it is important to keep the board signal pattern length short for the high-speed clock system. A material that offers not only high density but also low dielectric constant is required for highspeed signal transmission on the board. In order to satisfy these two requirements, a glassceramic-composite board was developed.

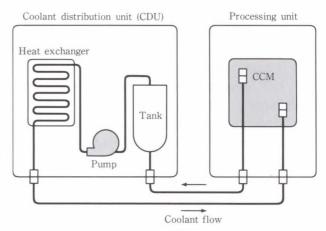

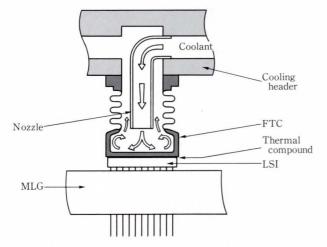

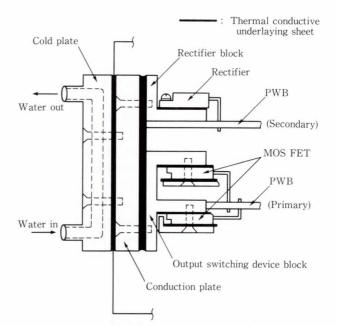

As the gate count of the LSI increase, the LSI dissipates more power. On the other hand, LSIs are mounted on increasingly smaller board areas so that power density on the board has increased drastically. It was required to develop a high efficiency LSI cooling technology to effect improved cooling performance. Cooling technology capable of handling thirty watts per LSI and 4.6 kW per board was developed for the VP2000.

To keep the system cabinet small, it is also important to decrease the volume occupied by the power supply. A water-cooled power supply was, therefore, developed.

#### 2. Packaging technology

The high-performance LSIs listed in Table 1 were developed for the VP2000. To accommodate the LSI's high speed, it was necessary to improve various factors in the new packaging design. Especially, the following two problems had to be solved.

First, the pattern density of the board had to be increased to compensate for the increase in pin density of the LSI. Second, it was desirable to reduce the dielectric constant of the board as well as to reduce the wiring length between LSIs. In order to solve these two problems, Fujitsu developed a new packaging technology for the VP2000.

#### 2.1 Computer packaging history

Fujitsu has been developing unique highdensity packaging technologies for four generations of computers, the FUJITSU M-190, M-380, M-780 and VP2000, to meet the demand for rapid increases in computer performance. Table 2 compares the packaging technologies for these four generations.

A planer packaging technology was developed for the FUJITSU M-190, which was intro-

| LSI                | cation                                                                          |                                                                 |

|--------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Logic LSI          | Circuit type<br>Gate count<br>Propagation delay<br>Power dissipation<br>Package | ECL<br>15 000 gates<br>70 ps/gate<br>30 W<br>462 pin PGA        |

| RAM &<br>logic LSI | Circuit type<br>Capacity<br>Address access time<br>Power dissipation<br>Package | ECL<br>64 Kbits+3 500<br>gates<br>1.6 ns<br>30 W<br>462 pin PGA |

| GaAs LSI           | Circuit type<br>Gate count<br>Propagation delay<br>Power dissipation<br>Package | BFL<br>1 200 gates<br>60 ps/gate<br>5.5 W<br>180 pin FPT        |

| Static RAM         | Capacity<br>Address access time                                                 | 1 Mbits<br>35 ns                                                |

Table 1. LSI for VP2000

PGA: Pin Grid Array BFL: Buffered FET Logic FPT: Flat lead Package Type duced in 1974<sup>2)</sup>. Forty-two printed circuit boards, called multi-chip carriers (MCC), were mounted on laminated bus plates, and were arranged in seven rows by three columns on both sides. Fourty-two LSI packages were mounted on each MCC. Each MCC had 664 signal pins, and the signal connections between the MCCs were provided by high-speed coaxial cables to minimize the signal propagation delay between the MCCs.

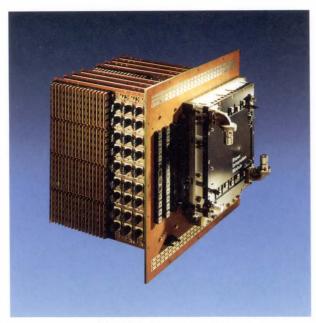

The FUJITSU M-380 was introduced in 1981. A unique three-dimensional stack structure was developed to shorten the signal wiring length between the  $MCCs^{3}$ . Each MCC accommodated 121 LSI packages, and 12 MCCs (with 768 signal pins each) were stacked in a 50 cm cube. The signal connections and power supply were facilitated through two side panels.

The single-board CPU packaging technology was developed for the FUJITSU M-780 to eliminate the critical delay path between two boards. Up to 336 LSI packages were mounted on both sides of a 488 mm  $\times$  540 mm printed circuit board called the sub-system carrier (SSC)<sup>4),5)</sup>.

Subsequently, the number of printed wiring boards (PWB) needed to form the CPU was significantly reduced over a ten-year period from 42 to only one, so that the size of the M-780 CPU unit could be reduced to 1/12 of the

| General-purpose<br>computer | M-190      | M-380             | M-780             | M-1800            |

|-----------------------------|------------|-------------------|-------------------|-------------------|

| Supercomputer               | -          | VP-100            | -                 | VP2000            |

| -                           | Planer     | Three-dimensional | Single-board      | Single-board      |

| CPU volume                  |            |                   |                   |                   |

| Size (cm × cm)              | 138 × 70   | 50 x 50           | 55 x 54           | 30 x 30           |

| Number of PWBs              | 42         | 12                | 1                 | 1                 |

| Volume ratio                | 100        | 13                | 8                 | 1                 |

| Cooling                     | Forced air | Forced air        | Conductive liquid | Conductive liquid |

Table 2. Trends in packaging technologies

A. Kaneko et al.: Hardware Technology for FUJITSU VP2000 Series

| Item                                | VP-100 | M-780 | VP2000 |

|-------------------------------------|--------|-------|--------|

| Pin density (pins/mm <sup>2</sup> ) | 0.16   | 0.28  | 1.29   |

|                                     | (1.0)  | (1.8) | (8.1)  |

| Package density (%)                 | 30.9   | 80.2  | 80.9   |

|                                     | (1.0)  | (2.6) | (2.6)  |

| Silicon density (%)                 | 4.0    | 15.0  | 51.0   |

|                                     | (1.0)  | (3.8) | (12.8) |

Table 3. Comparison of packaging complexity

#### M-190 CPU volume.

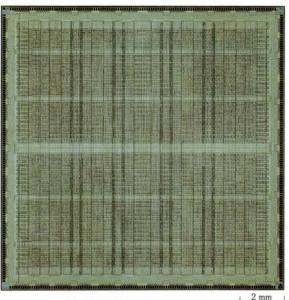

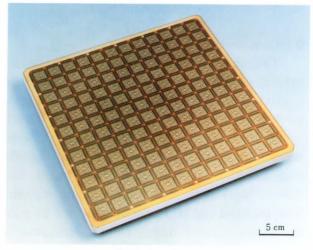

For the VP2000, Fujitsu developed highdensity packaging with a glass-ceramic-composite board called the multilayer glass-ceramiccomposite board  $(MLG)^{6)-8}$ , to decrease board size and increase LSI pin density. It was possible to reduce the board size to 1/4 that of the M-780 SSC. The various units of the VP2000, including the vector execution unit (VXU), vector control unit (VCU), scalar unit (SU), input/output processor (IOP), and memory access control unit (MAC) are all accommodated on the MLG.

#### 2.2 Packaging density

The packaging density trend of the three generations is listed in Table 3. The two factors to be considered for estimation of packaging density are pin density and silicon percentage, which is a unique new index, and it is calculated with Equation (1).

Silicon percentage =

$$SCHIP/SBOARD$$

, (1)

where,

SCHIP: sum of LSI silicon die area on board, SBOARD: board area – board peripheral area.

The VP2000's pin density per unit area on a board is five times greater than that of the M-780. Silicon percentage of the VP2000 is fifty one percent. This means that more than a half of the board surface is covered with silicon chips, and this value is difficult to achieve even if bare chips are embedded on the substrate. This high density is achieved by new packaging technology with ultra-miniature LSI packages and the MLG.

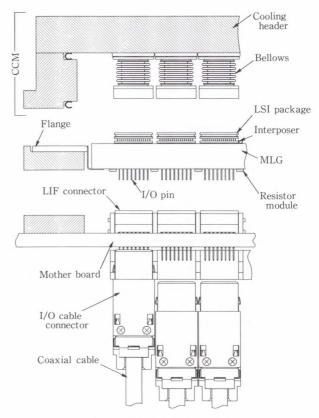

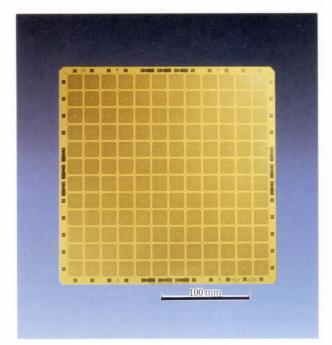

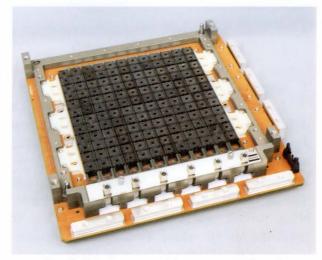

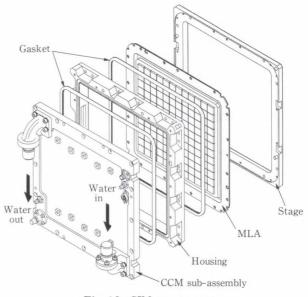

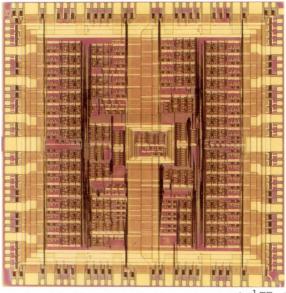

Fig. 1-MLG assembly.

Fig. 2-Packaging overview.

#### 2.3 Board assembly

The MLG assembly (MLA), mother board assembly, and conductive cooling module are shown in Fig. 1. The center portion shows the MLA. On the right-hand side, there is a mother board assembly, and on the left is a conductive cooling module. The MLG is mounted on a mother board, which supplies power to the MLG, with the light insertion

| Item         | <b>M-</b> 780     | VP2000                 |

|--------------|-------------------|------------------------|

| Chip size    | 9.5 mm x 9.5 mm   | 13.5 mm × 13.5 mm      |

| Package type | Flat lead package | Pin grid array package |

| Package size | 22 mm × 22 mm     | 17 mm × 17 mm          |

Table 4. LSI chip and package

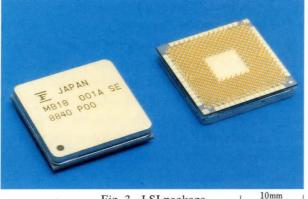

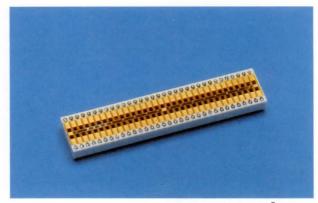

Fig. 3–LSI package.

#### force connector (LIF).

Figure 2 illustrates a cross-sectional view of the packaging hierarchy. On the top side of the MLG are mounted the LSI package and interposer, a very thin plate placed between the LSI package and the MLG. Interconnections between MLA units are made by using specially designed I/O connectors with high-speed coaxial cables.

#### 2.4 Packaging components

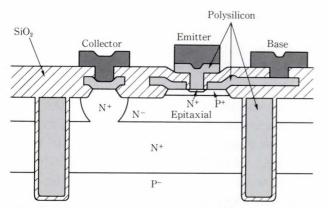

#### 2.4.1 LSI package

Table 4 compares LSI chips and packages between the M-780 and the VP2000. Although the silicon chip size of the VP2000's LSI increased to about twice that of the M-780's, it was possible to reduce the overall package size to about half that of the M-780 by developing the high-density pin grid array (PGA) type package.

Figure 3 shows a PGA type LSI package. It has 462 I/O pins; 320 are for signals, 140 for power and ground, and two dummy pins are provided for alignment. The package size is 17 mm square, with a height of 3.6 mm, and pins 1 mm long. I/O pins are arranged in a 0.45 mm staggered pitch pattern. The chip size is 13.5 mm square, with 100  $\mu$ m pitch TAB leads. In order to minimize the thermal ex-

| Item                | Specification   |

|---------------------|-----------------|

| Board size          | 245 mm x 245 mm |

| Board thickness     | 12.9 mm         |

| Number of layers    | 61 (signal: 36) |

| DC resistance       | 100 mΩ/cm (Cu)  |

| Dielectric constant | 5.7             |

| Tpd                 | 80 ps/cm        |

| Number of LSIs      | 144             |

Table 5. MLG features

pansion mismatch between chip and MLG, aluminum nitride (AIN) is used for both heat sink and substrate. This LSI package is reflowsoldered by the butt-soldering method.

#### 2.4.2 MLG and MLA

The primary advantage of using ceramic boards is the ability to make thick boards. When working with organic boards, it is difficult to make a thick board that can be drilled with fine drill sizes, which means that the organic board technology is limited from the standpoint of high density.

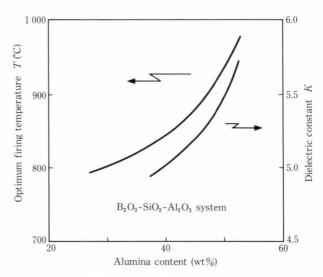

For the VP2000, glass-ceramic-composite was newly developed for the board material instead of conventional alumina material. Advantages of glass-ceramic-composite are as follows. First, alumina, the common material for printed circuit boards, has a relatively high dielectric constant, of about ten. The signal propagation speed on the board pattern was improved by about 25 percent by making use of the new glass-ceramic-composite material, the dielectric constant of which is 5.7.

The second advantage of glass-ceramiccomposite is its low firing temperature. Because the firing temperature is around 1000 °C, copper can be used for internal conductors. With the conventional alumina substrate, only tungusten (W) or molybden (Mo) could be used for the conductor material. The use of low resistivity copper assures low DC voltage drops, even when the board size becomes larger, which is required for enabling one-board CPU packaging.

The major features of MLG are listed in Table 5. The outer dimension is 245 mm square, and the board thickness is 12.9 mm. The total

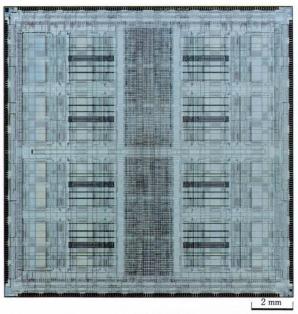

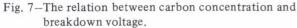

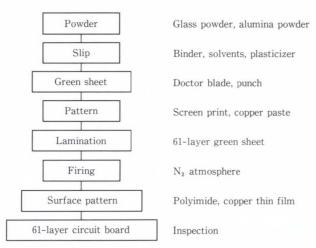

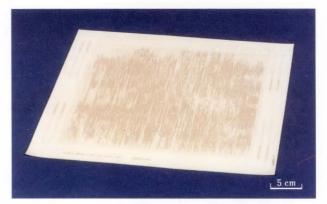

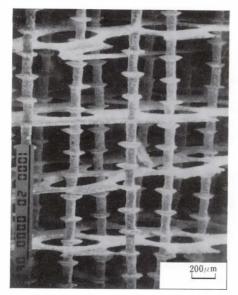

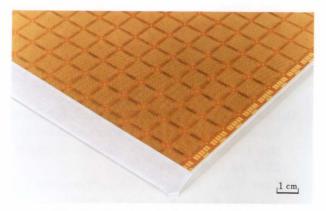

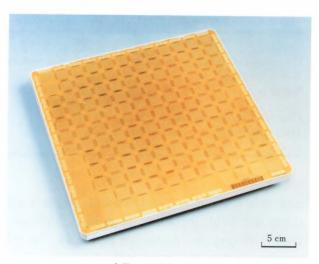

layer count is 61, with 36 layers used for signals. The internal conductor material is copper, and the DC resistance of signal trace is about 100 m $\Omega$ /cm. The dielectric constant of this board is 5.7, and the propagation delay time (*T*pd) is 80 ps/cm. Figure 4 shows the MLG. The basic grid pitch of this board is 0.45 mm, and there is one routing channel between 0.45 mm grids The via diameter is 80  $\mu$ m, and the signal patterns is 95  $\mu$ m wide and 45  $\mu$ m thick.

LSI packages are arranged in a  $12 \times 12$  matrix,

Fig. 4-MLG row board.

the center spacing of the LSI package is 18.9 mm. On the bottom of the MLG, 312 resistor modules and 144 I/O pin blocks are mounted. The I/O pin blocks are arranged in a  $12 \times 12$  matrix. There are 60 pins in each block, so the total I/O pin count is 8 640. The center spacing of I/O pin blocks is 18.9 mm.

#### 2.4.3 Resistor module

Figure 5 shows the resistor module. A total of 312 modules can be mounted on an MLG. This module has 66 circuits, and each resistance is  $65\Omega$ . The resistance element is made by thin-film process. On the other side of this module are 83 solder bumps. By making a distance shorter than that of flat lead types, it is possible to decrease the inductance and noise. The outside dimension is 15 mm  $\times$  3 mm with a 1 mm height.

Fig. 5-Resistor module.

5 mm

Fig. 6-New concept of connector.

#### 2.4.4 Mother board

The fully assembled MLG is mounted on the mother board. On the mother board, LIF connectors are interconnected to the I/O pins of the MLG, and the coaxial connectors used for clock signals and terminals for supplying power are mounted.

The internal conductor material is copper, and 0.5 mm thick copper plates are used for the power planes. It was possible to hold the voltage drop in the MLG to less than 15 mV.

All electric components are reflow-soldered at one time. The dimensions of the board outline are  $359 \text{ mm} \times 340 \text{ mm}$  and 7 mm thick. The total layer count is 13.

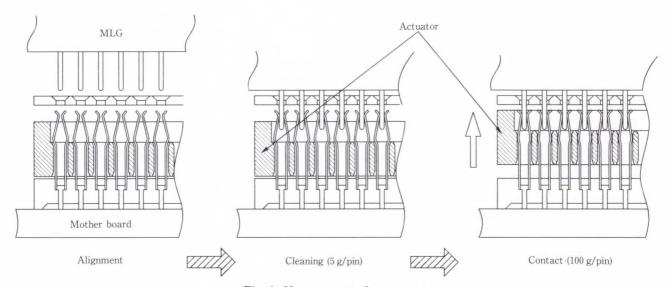

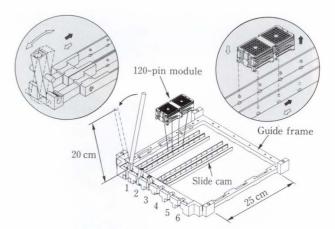

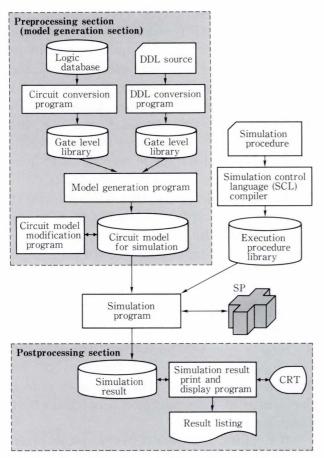

#### 2.4.5 LIF connector