# HP 1000 A900 Computer

## Reference Manual

## HP 1000 A900 Computer

### Reference Manual

# FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE STATEMENT

The Federal Communications Commission (in Subpart J, of Part 15, Docket 20780) has specified that the following notice be brought to the attention of the users of this product.

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

## **PRINTING HISTORY**

The Printing History below identifies the Edition of this Manual and any Updates that are included. Periodically, Update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this Printing History page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past Updates, however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as all Updates.

To determine what software manual edition and update is compatible with your current software revision code, refer to the appropriate Software Numbering Catalog, Software Product Catalog, or Diagnostic Configurator Manual.

| First Edition  | Dec 1982 |                                        |

|----------------|----------|----------------------------------------|

| Update 1       | Dec 1982 |                                        |

| Second Edition | Jun 1983 |                                        |

| Update 1       | Dec 1983 |                                        |

| Update 2       | May 1984 |                                        |

| Reprint        | May 1984 | Update 1 and 2 has been incorporated.  |

| Update 3       | Dec 1984 |                                        |

| Update 4       | Apr 1985 |                                        |

| Reprint        | Apr 1985 | Updates 3 and 4 has been incorporated. |

| Update 5       | Oct 1986 |                                        |

|                |          |                                        |

#### **NOTICE**

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another program language without the prior written consent of Hewlett-Packard Company.

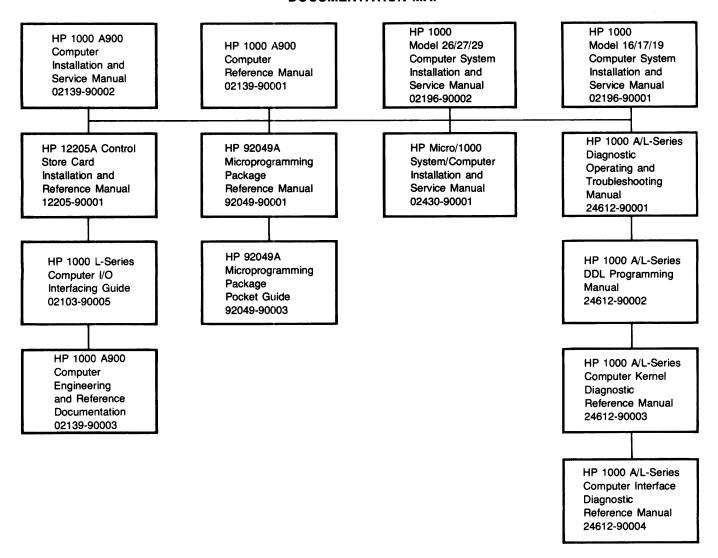

#### **DOCUMENTATION MAP**

# **CONTENTS**

| Section I GENERAL FEATURES            | Page        | Direct and Indirect Addressing         |              |

|---------------------------------------|-------------|----------------------------------------|--------------|

| Architecture                          | 1 1         | Memory Mapping                         |              |

| Floating Point Hardware               |             | Virtual Memory Area                    |              |

| User Microprogramming                 |             | Base-Relative Addressing               |              |

| Virtual Control Panel                 |             | Reserved Memory Locations              |              |

| Bootstrap Loaders                     |             | Nonexistent Memory                     |              |

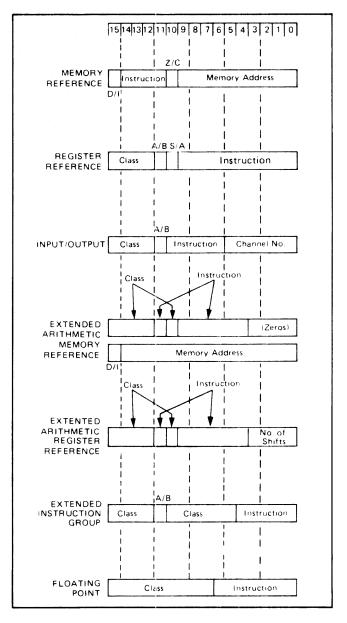

| Self-Test Routines                    |             | Base Set Instruction Formats           |              |

| Time Base Generator                   |             | Memory Reference Instructions          |              |

| Power Supply                          |             | Register Reference Instructions        |              |

| Input/Output                          |             | Input/Output Instructions              |              |

| Memory                                |             | Extended Arithmetic Memory Reference   |              |

| Cache Memory                          |             | Instructions                           | 3-5          |

| Software                              |             | Extended Arithmetic Register Reference |              |

| HP Interface Bus                      |             | Instructions                           | 3-5          |

| Computer Network                      |             | Extended Instructions                  |              |

| Expansion and Enhancement             |             | Floating Point Instructions            | 3-5          |

| Specifications                        |             | Language Instruction Set               |              |

|                                       |             | Double Integer Instructions            |              |

| Section II                            | Page        | Virtual Memory Instructions            |              |

| OPERATING FEATURES                    | 1 age       | Operating System Instructions          | 3-6          |

| Hardware Registers                    | 2-1         | Scientific Instruction Set             | 3-6          |

| A-Register                            |             | Vector Instruction Set                 | 3-6          |

| B-Register                            |             | CDS Instructions                       | 3-6          |

| P-Register                            |             | Base Set Instruction Coding            |              |

| Extend (E) Register                   |             | Memory Reference Instructions          |              |

| Overflow (O) Register                 |             | Register Reference Instructions        |              |

| Central Interrupt Register            |             | Shift/Rotate Group                     |              |

| Violation Register                    |             | Alter/Skip Group                       |              |

| Parity Violation Register             |             | Input/Output Instructions              | 3-13         |

| Interrupt System Register             |             | Extended Arithmetic Memory Reference   |              |

| X- and Y-Registers                    |             | Instructions                           | 3-1 <b>5</b> |

| WMAP Register                         |             | Extended Arithmetic Register Reference |              |

| IMAP Register                         | <b>2</b> -2 | Instructions                           |              |

| C- and Q-Registers                    | <b>2</b> -2 | Extended Instruction Group             |              |

| Z-Register                            | <b>2</b> -2 | Index Register Instructions            |              |

| IQ-Register                           | <b>2</b> -2 | Jump Instructions                      |              |

| Virtual Registers                     | <b>2</b> -2 | Byte Manipulation Instructions         |              |

| M-Register                            |             | Bit Manipulation Instructions          |              |

| T-Register                            |             | Word Manipulation Instructions         |              |

| Controls and Indicators               |             | Floating Point Instructions            |              |

| Self-Test                             |             | Single Precision Operations            |              |

| Bootstrap Loaders                     |             | Double Precision Operations            |              |

| Loader Selection for Auto-Boot        |             | Double Integer Instructions            |              |

| Program Starts                        |             | Virtual Memory Instructions            |              |

| VCP ReEntry for Extended Boot Loading |             | Operating System Instruction Set       |              |

| Device Parameters and Media Formats   |             | Execution Times                        |              |

| Virtual Control Panel                 |             | Scientific Instruction Set             |              |

| VCP Program Operation                 |             | SIS Execution Times and Interrupts     |              |

| Loader Commands                       |             | Vector Instruction Set                 |              |

| VCP User Considerations               |             | VIS Execution Times and Interrupts     |              |

| VCP Slave Functions                   | Z-b         | Assembly Language                      |              |

|                                       |             | RTE Implementation                     |              |

| Section III                           | Page        | · · · · · · · · · · · · · · · · · · ·  | •            |

| PROGRAMMING INFORMATION               |             |                                        | _            |

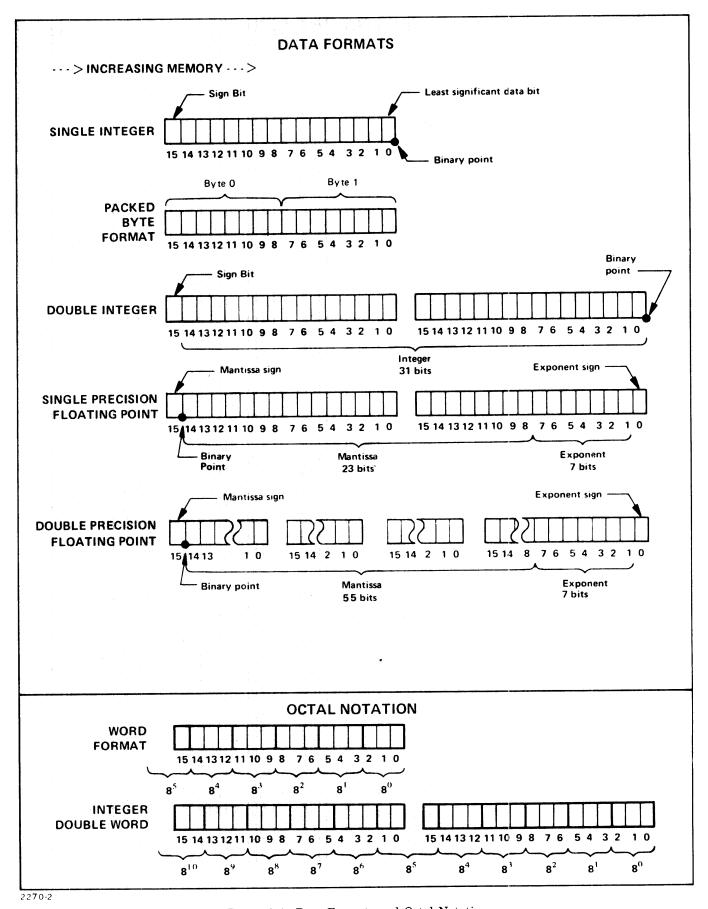

| Data Formats                          |             | Section IV                             | Page         |

| Addressing                            |             | DYNAMIC MAPPING SYSTEM                 |              |

| Paging                                | 3-1         | Memory Addressing                      | 4-1          |

Update 5

# **CONTENTS** (Continued)

| General Descriptions 4-1                      | Flag Bits                                   |

|-----------------------------------------------|---------------------------------------------|

| Page Mapping Register Instructions 4-1        | Data Buffer Register7-4                     |

| Working Map Instructions 4-1                  | Control Register                            |

| Cross-Map Instructions                        | Direct Memory Access                        |

| Detailed Descriptions4-3                      | Control Word 1                              |

| DMS Instruction Execution Times 4-10          | Control Word 2                              |

| Assembly Language and RTE Implementation 4-10 | Control Word 3                              |

|                                               | DMA Transfer Initialization                 |

| Section V Page                                | Self-Configured DMA7-5                      |

| CODE AND DATA SEPARATION                      | DMA Data Transfer7-7                        |

| Code and Data Addressing5-1                   | Non-DMA Data Transfer7-7                    |

| General Description 5-1                       | Input Data Transfer (Interrupt Method)7-7   |

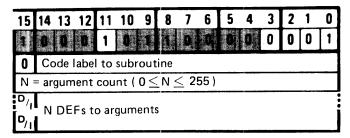

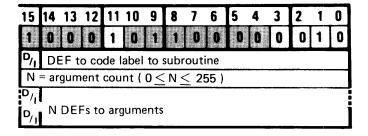

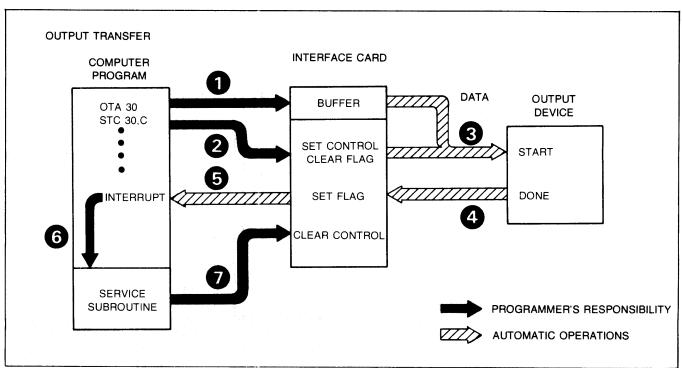

| Procedure Call Instructions 5-1               | Output Data Transfer (Interrupt Method) 7-8 |

| Procedure Exit Instructions 5-2               | Non-Interrupt Data Transfer                 |

| C, Q, Z, and IQ Instructions5-2               | Input                                       |

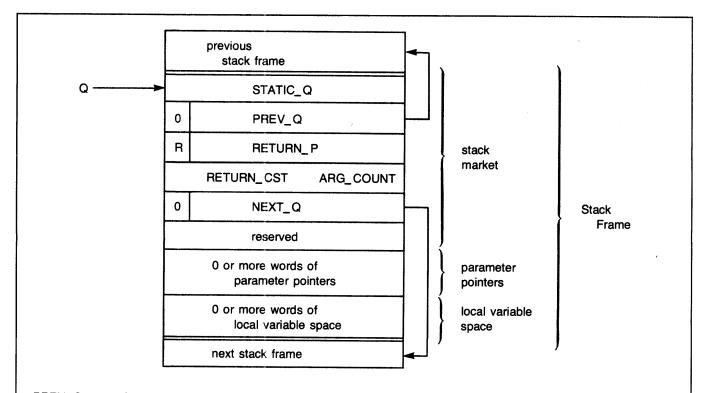

| Stack Frame Description5-2                    | Output                                      |

| Detailed Descriptions5-4                      | Diagnose Modes7-10                          |

| Assembly Language and RTE Implementation 5-10 | Diagnose Mode 1                             |

| Execute Times                                 | Diagnose Mode 2                             |

|                                               | Diagnose Mode 3                             |

| Section VI Page                               |                                             |

| INTERRUPT SYSTEM                              | Section VIII Page                           |

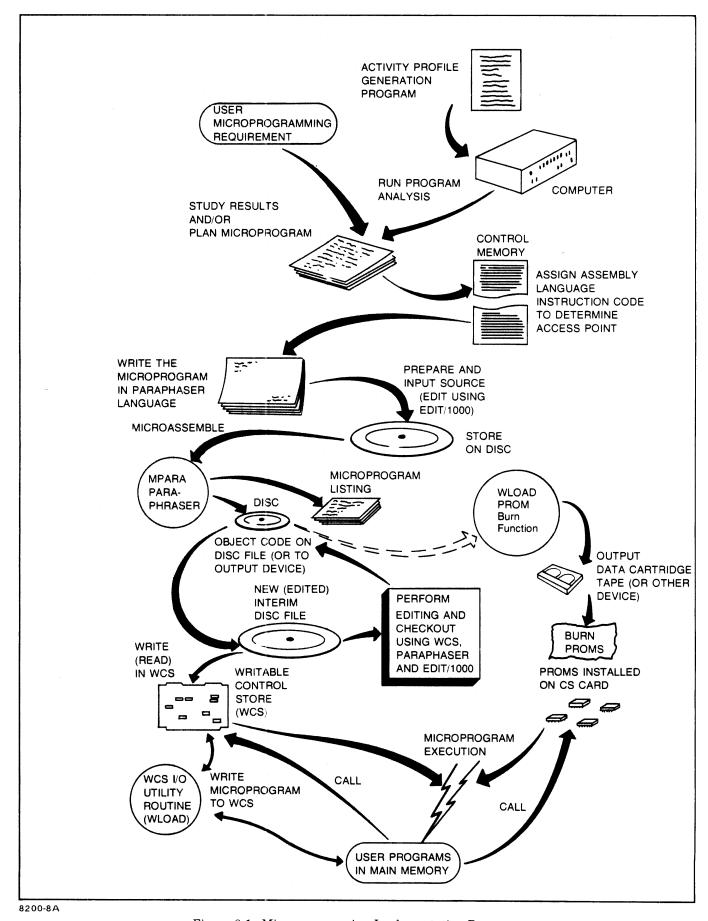

| Power Fail Interrupt 6-1                      | MICROPROGRAMMING                            |

| Multiple-Bit Error Interrupt 6-3              | The Microprogrammed Computer8-1             |

| Memory Protect Interrupt 6-3                  | The Microprogrammable Computer8-1           |

| Unimplemented Instruction Interrupt 6-4       | Customized Instructions 8-1                 |

| Time Base Generator Interrupt 6-4             | System Speed                                |

| Virtual Memory Area Interrupt6-4              | Memory Space and Security8-1                |

| CDS Segment Interrupt 6-4                     | Developing Microprograms8-2                 |

| Input/Output Interrupt 6-5                    | Support for the Microprogrammer8-2          |

| Interrupt Priority 6-5                        | FPP Microprogramming8-2                     |

| Central Interrupt Register6-5                 | Conclusion                                  |

| Processor Status Register6-5                  |                                             |

| Interrupt Type Control                        | Appendix Page                               |

| Instruction Summary 6-5                       | Character Codes                             |

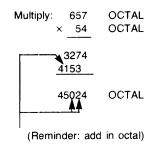

| D                                             | Octal Arithmetic                            |

| Section VII Page                              | Octal/Decimal Conversions                   |

| INPUT/OUTPUT SYSTEM                           | Mathematical Equivalents                    |

| Input/Output Addressing                       | Octal Combining Tables                      |

| Input/Output Priority                         | Instruction Codes in Octal                  |

| Interface Elements                            | Base Set Instruction Codes in Binary A-11   |

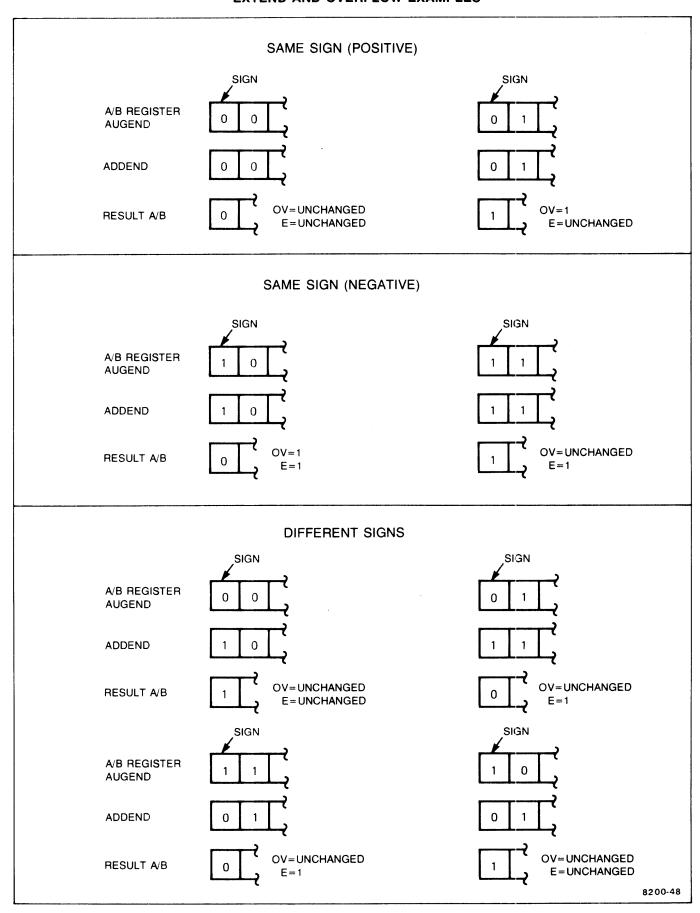

| Global Register                               | Extend and Overflow Examples A-16           |

| Control Bits                                  | Interrupt and Control Summary               |

# **ILLUSTRATIONS**

| Title                                      | Page                                                                                                                                                                                                                                                                       |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stack Frame General Layout                 | 5-3                                                                                                                                                                                                                                                                        |

| Input/Output System                        | 7-2                                                                                                                                                                                                                                                                        |

| I/O Priority Assignments                   |                                                                                                                                                                                                                                                                            |

| Priority Linkage (Simplified)              | 7-3                                                                                                                                                                                                                                                                        |

| Interrupt Sequence                         | 7-3                                                                                                                                                                                                                                                                        |

| General Bit Definitions for Control Word 1 | 7-6                                                                                                                                                                                                                                                                        |

| DMA Input Data Transfer                    | 7-7                                                                                                                                                                                                                                                                        |

| Input Data Transfer (Interrupt Method)     | 7-8                                                                                                                                                                                                                                                                        |

| Output Data Transfer (Interrupt Method)    | 7-9                                                                                                                                                                                                                                                                        |

| Microprogramming Implementation Process    | 8-3                                                                                                                                                                                                                                                                        |

|                                            | Stack Frame General Layout Input/Output System I/O Priority Assignments Priority Linkage (Simplified) Interrupt Sequence General Bit Definitions for Control Word 1 DMA Input Data Transfer Input Data Transfer (Interrupt Method) Output Data Transfer (Interrupt Method) |

# **TABLES**

| Title Page                                  | Title Page                                        |

|---------------------------------------------|---------------------------------------------------|

| Options and Accessories 1-5                 | Typical Base Set Instruction Execution Times 3-34 |

| Specifications                              | SIS Instruction Error Codes                       |

| Start-Up Switch Settings                    | Instructions and Opcodes for RTE                  |

| Sample VCP Loader Call Back Checkout        | Implementation                                    |

| Program2-4B                                 | Dynamic Mapping Instructions Execution Times 4-11 |

| ID Numbers for Interface Cards2-4B          | CDS Instructions Execution Times 5-10             |

| VCP Characters and Associated Registers 2-5 | A900 Interrupt Assignments 6-1                    |

| VCP Commands                                | Sample Power Fail Subroutine 6-2                  |

| VCP Loader Command Errors 2-11              | Instructions for Select Codes 00 through 07 6-6   |

| Memory Paging 3-3                           | Noninterrupt Transfer Routines                    |

| Reserved Memory Locations                   | Diagnose Mode 1                                   |

| Shift/Rotate Group Combining Guide          | Diagnose Mode 2                                   |

| Alter/Skip Group Combining Guide 3-11       |                                                   |

vi Update 5

### **ALPHABETICAL INDEX OF STANDARD INSTRUCTIONS**

| INSTRU      | CTION                    | AGE          | INSTRUC        | CTION PAGE                                                           |

|-------------|--------------------------|--------------|----------------|----------------------------------------------------------------------|

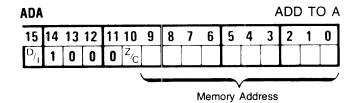

| ADA         | Add to A                 | 3-6          | DLD            | Double Load 3-15                                                     |

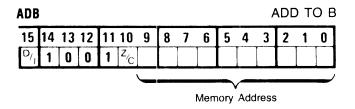

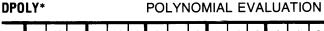

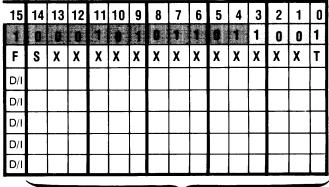

| ADB         | Add to B                 |              | DPOLY          | Polynomial Evaluation                                                |

| ADQA        | Add Q to A               |              | DST            | Double Store                                                         |

| ADQB        | Add Q to B               | . 5-9        | DSX            | Decrement X and Skip if Zero 3-19                                    |

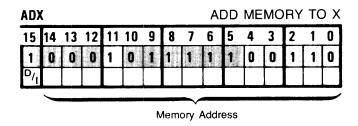

| ADX         | Add Memory to X          | 3-18         | DSY            | Decrement Y and Skip if Zero3-19                                     |

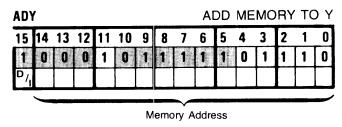

| ADY         | Add Memory to Y          |              | DVABS          | Vector Absolute Value                                                |

| ALF         | Rotate A Left Four       |              | DVADD          | Vector Add                                                           |

| ALOG        | Natural Logarithm        |              | DVDIV          | Vector Divide 3-42                                                   |

| ALOGT       | Common Loagrithm         |              | DVDOT          | Vector Dot Product 3-45                                              |

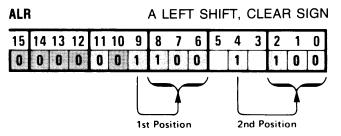

| ALR         | A Left Shift, Clear Sign |              | DVMAB          | Vector Maximum Absolute Value 3-45                                   |

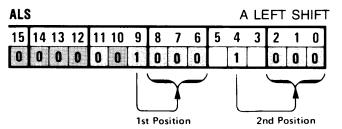

| ALS         | A left Shift             |              | DVMAX          | Vector Maximum Value                                                 |

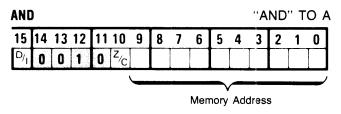

| AND         | "And" to A               |              | DVMIB          | Vector Minimum Absolute Value 3-46                                   |

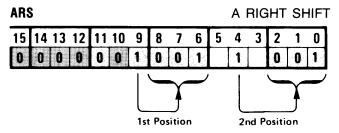

| ARS<br>ASL  | A Right Shift            |              | DVMIN<br>DVMOV | Vector Minimum Value         3-46           Vector Move         3-46 |

| ASR         | Arithmetic Shift Left    |              | DVMOV          | Vector Multiply                                                      |

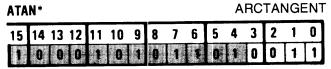

| ATAN        | Arctangent               |              | DVNRM          | Vector Norm                                                          |

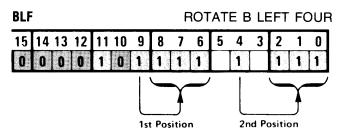

| BLF         | Rotate B Left Four       |              | DVPIV          | Vector Pivot                                                         |

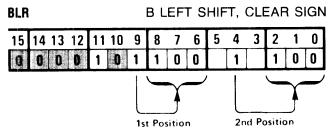

| BLR         | B Left Shift, Clear Sign |              | DVSAD          | Scalar-Vector Add                                                    |

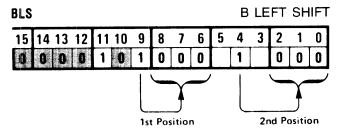

| BLS         | B Left Shift             |              | DVSDV          | Scalar-Vector Divide                                                 |

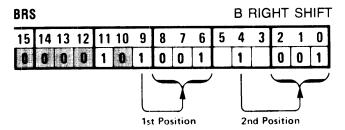

| BRS         | B Right Shift            |              | DVSMY          | Scalar-Vector Multiply                                               |

| CACQ        | Copy A to C and Q        |              | DVSSB          | Scalar-Vector Subtract 3-43                                          |

| CAX         | Copy A to X              |              | DVSUB          | Vector Subtract 3-41                                                 |

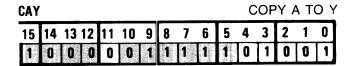

| CAY         | Copy A to Y              |              | DVSUM          | Vector Sum                                                           |

| CAZ         | Copy A to Z              |              | DVSWP          | Vector Swap                                                          |

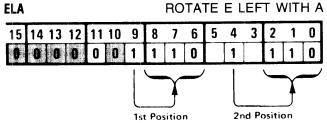

| CBCQ        | Copy B to C and Q        |              | ELA            | Rotate E Left with A 3-10                                            |

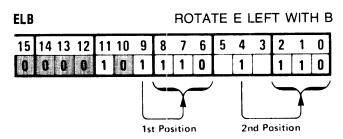

| CBS         | Clear Bits               | 3-24         | ELB            | Rotate E Left with B3-10                                             |

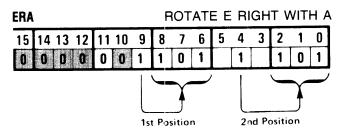

| CBT         | Compare Bytes            | 3-22         | ERA            | Rotate E Right with A3-10                                            |

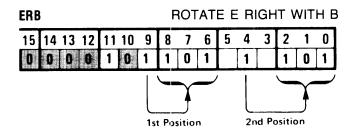

| CBX         | Copy B to X              | 3-18         | ERB            | Rotate E Right with B3-10                                            |

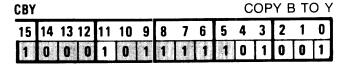

| CBY         | Copy B to Y              |              | EXIT           | Procedure Exit 5-7                                                   |

| CBZ         | Copy B to Z              |              | EXIT1          | Procedure Exit With One Skip 5-7                                     |

| CCA         | Clear and Complement A   |              | EXIT2          | Procedure Exit With Two Skips 5-7                                    |

| CCB         | Clear and Complement B   |              | EXP            | E to the Power X                                                     |

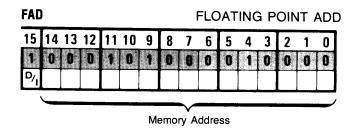

| CCE         | Clear and Complement E   |              | FAD            | Floating Point Add                                                   |

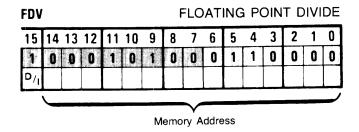

| CCQA        | Copy C and Q to A        |              | FDV            | Floating Point Divide                                                |

| CCQB        | Copy C and Q to B        |              | FIX            | Floating Point to Single Integer 3-26                                |

| CIQA        | Copy Interrupted to A    |              | FLT            | Single Integer to Floating Point 3-26                                |

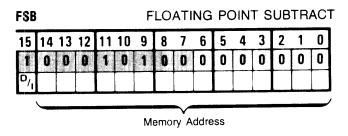

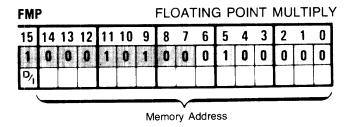

| CIQB<br>CLA | Copy Interrupted to B    |              | FMP<br>FSB     | Floating Point Multiply                                              |

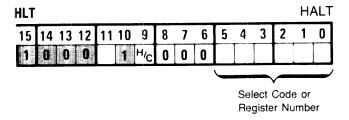

| CLB         | Clear B                  |              | HLT            | Halt                                                                 |

| CLC         | Clear Control            |              | INA            | Increment A                                                          |

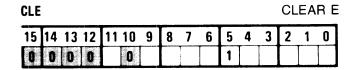

| CLE         | Clear E                  |              | INB            | Increment B                                                          |

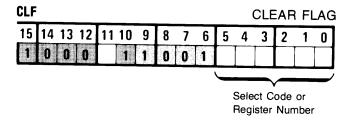

| CLF         | Clear Flag               |              | IOR            | "Inclusive Or" to A                                                  |

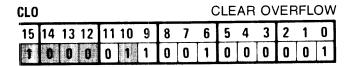

| CLO         | Clear Overflow           |              | ISX            | Increment X and Skip if Zero 3-19                                    |

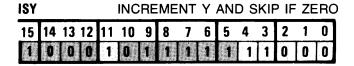

| CMA         | Complement A             |              | ISY            | Increment Y and Skip if Zero 3-19                                    |

| CMB         | Complement B             |              | ISZ            | Increment and Skip if Zero3-7                                        |

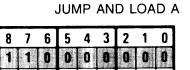

| CME         | Complement E             |              | JLA            | Jump and Load A 3-22                                                 |

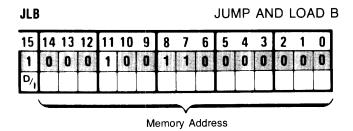

| CMW         | Compare Words            |              | JLB            | Jump and Load B 3-22                                                 |

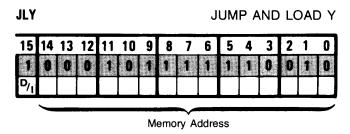

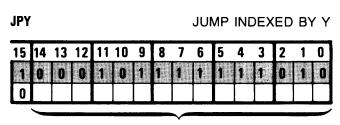

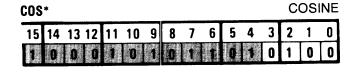

| cos         | Cosine                   |              | JLY            | Jump and Load Y                                                      |

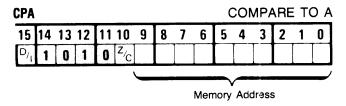

| CPA         | Compare to A             |              | JMP            | Jump 3-7                                                             |

| CPB         | Compare to B             | . 3-7        | JPY            | Jump Indexed by Y 3-21                                               |

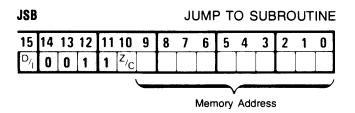

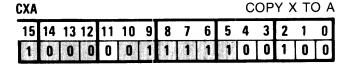

| CXA         | Copy X to A              |              | JSB            | Jump to Subroutine                                                   |

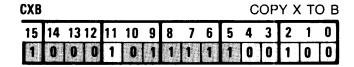

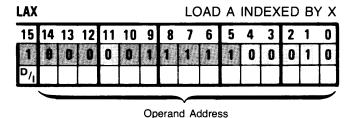

| CXB         | Copy X to B              |              | LAX            | Load A Indexed by X                                                  |

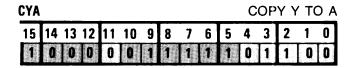

| CYA         | Copy Y to A              |              | LAY            | Load A Indexed by Y                                                  |

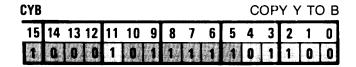

| CYB         | Copy Y to B              |              | LBT            | Load Byte                                                            |

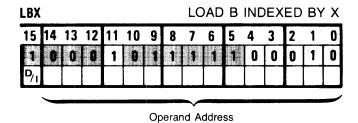

| CZA         | Copy Z to A              |              | LBX            | Load B Indexed by X                                                  |

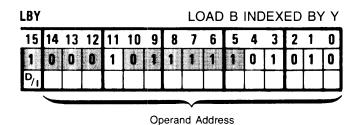

| CZB         | Copy Z to B              |              | LBY            | Load B Indexed by Y                                                  |

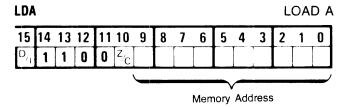

| DIV         | Divide                   | <b>ა-1</b> ე | LDA            | Load A                                                               |

### **ALPHABETICAL INDEX OF STANDARD INSTRUCTIONS (Continued)**

| INSTRU       | CTION PAGE                                                                       | INSTRU       | CTION PAGE                                                       |

|--------------|----------------------------------------------------------------------------------|--------------|------------------------------------------------------------------|

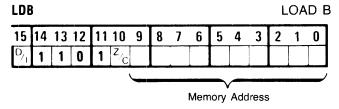

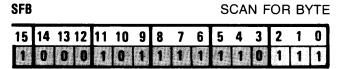

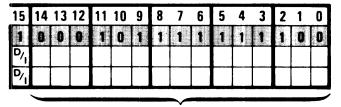

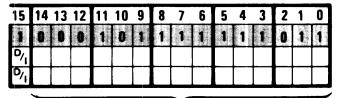

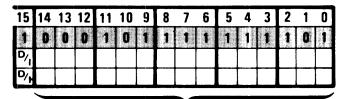

| LDB          | Load B3-8                                                                        | SFB          | Scan for Byte 3-23                                               |

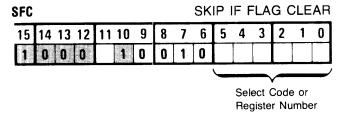

| LDMP         | Load A Map                                                                       | SFC          | Skip if Flag Clear 3-14                                          |

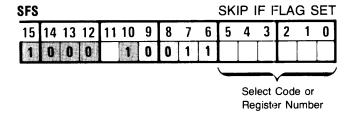

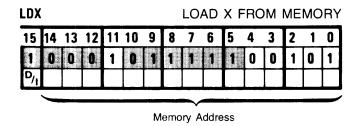

| LDX          | Load X from Memory 3-20                                                          | SFS          | Skip if Flag Set 3-15                                            |

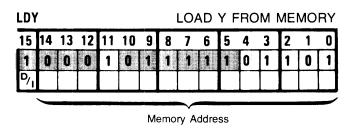

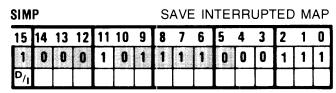

| LDY          | Load Y from Memory3-20                                                           | SIMP         | Save Interrupted Map 4-4                                         |

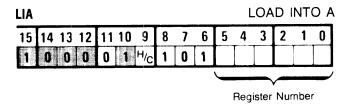

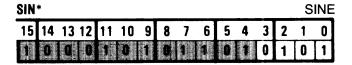

| LIA          | Load Input to A                                                                  | SIN          | Sine 3-39                                                        |

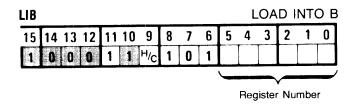

| LIB          | Load Input to B                                                                  | SLA          | Skip if LSB of A is Zero 3-11, 3-12                              |

| LPMR         | Load Page Mapping Register4-3                                                    | SLB          | Skip if LSB of B is Zero 3-11, 3-13                              |

| LSL          | Logical Shift Left (32)                                                          | SOC          | Skip if Overflow Clear                                           |

| LSR          | Logical Shift Right (32)3-16                                                     | SOS          | Skip if Overflow Set3-15                                         |

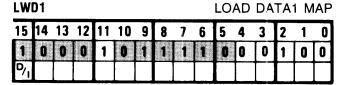

| LWD1         | Load DATA1 Map4-5                                                                | SPMR         | Store Page Mapping Register4-3                                   |

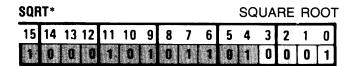

| LWD2         | Load DATA2 Map4-5                                                                | SQRT         | Square Root                                                      |

| MB00         | Cross Move Bytes, Execute to Execute 4-9                                         | SSA          | Skip if Sign of A is Zero                                        |

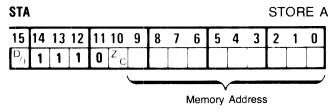

| MB01         | Cross Move Bytes, Execute to DATA1 4-9                                           | SSB<br>STA   | Skip if Sign of B is Zero                                        |

| MB02         | Cross Move Bytes, Execute to DATA24-10                                           | STB          | Store B                                                          |

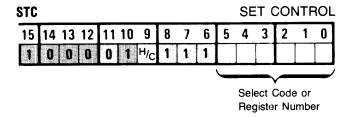

| MB10<br>MB11 | Cross Move Bytes, DATA1 to Execute 4-10<br>Cross Move Bytes, DATA1 to DATA1 4-10 | STC          | Set Control                                                      |

| MB12         | Cross Move Bytes, DATA1 to DATA2 4-10                                            | STF          | Set Flag                                                         |

| MB20         | Cross Move Bytes, DATA2 to Execute 4-11                                          | STMP         | Store A Map4-4                                                   |

| MB21         | Cross Move Bytes, DATA2 to DATA1 4-11                                            | STO          | Set Overflow 3-15                                                |

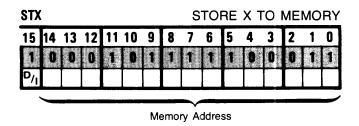

| MB22         | Cross Move Bytes, DATA2 to DATA2 4-11                                            | STX          | Store X to Memory                                                |

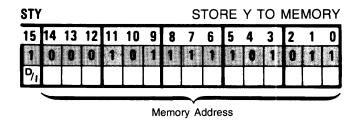

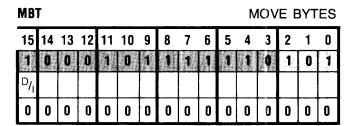

| MBT          | Move Bytes                                                                       | STY          | Store Y to Memory                                                |

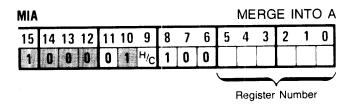

| MIA          | Merge Into A 3-14                                                                | SWMP         | Save Working Map4-4                                              |

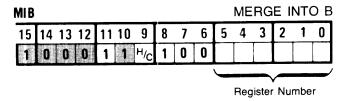

| MIB          | Merge Into B                                                                     | SZA          | Skip if A is Zero 3-13                                           |

| MPY          | Multiply                                                                         | SZB          | Slip if B is Zero                                                |

| MVW          | Move Words 3-25                                                                  | TAN          | Tangent 3-35                                                     |

| MW00         | Cross Move Words, Execute to Execute 4-7                                         | TANH         | Hyperbolic Tangent                                               |

| MW01         | Cross Move Words, Execute to DATA1 4-7                                           | TBS          | Test Bits                                                        |

| MW02         | Cross Move Words, Execute to DATA2 4-8                                           | VABS         | Vector Absolute Value                                            |

| MW10         | Cross Move Words, DATA1 to Execute 4-8                                           | VADD         | Vector Add                                                       |

| MW11         | Cross Move Words, DATA1 to DATA1 4-8                                             | VDIV         | Vector Divide                                                    |

| MW12         | Cross Move Words, DATA1 to DATA2 4-8                                             | VDOT<br>VMAB | Vector Dot Product                                               |

| MW20<br>MW21 | Cross Move Words, DATA2 to Execute 4-9 Cross Move Words, DATA2 to DATA1 4-9      | VMAX         | Vector Maximum Value                                             |

| MW22         | Cross Move Words, DATA2 to DATA1 4-9                                             | VMIB         | Vector Minimum Absolute Value 3-46                               |

| NOP          | No Operation                                                                     | VMIN         | Vector Minimum Value 3-46                                        |

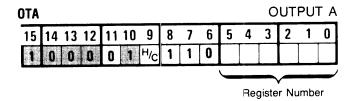

| OTA          | Output A                                                                         | VMOV         | Vector Move                                                      |

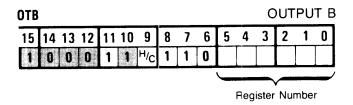

| OTB          | Output B                                                                         | VMPY         | Vector Multiply                                                  |

| PCLAI        | Internal Procedure Call5-4                                                       | VNRM         | Vector Norm                                                      |

| PCALN        | Procedure Call, .ENTN Compatible 5-6                                             | VPIV         | Vector Pivot 3-44                                                |

| PCALR        | Procedure Call, .ENTR Compatible 5-6                                             | VSAD         | Scalar-Vector Add 3-42                                           |

| PCALV        | Variable External Procedure Call 5-5                                             | VSDV         | Scalar-Vector Divide                                             |

| PCALX        | External Procedure Call 5-4                                                      | VSMY         | Scalar-Vector Multiply                                           |

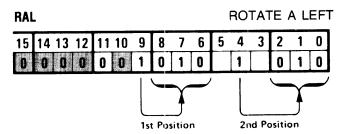

| RAL          | Rotate A Left                                                                    | VSSB         | Scalar-Vector Subtract                                           |

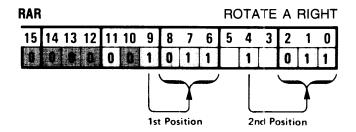

| RAR          | Rotate A Right3-11                                                               | VSUB         | Scalar Subtract                                                  |

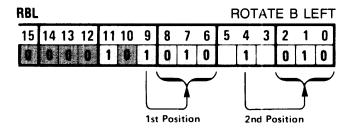

| RBL          | Rotate B Left                                                                    | VSUM         | Vector Sum                                                       |

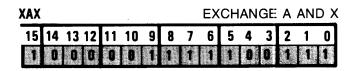

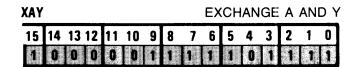

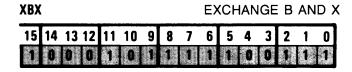

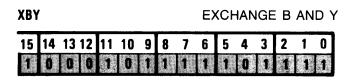

| RBR          | Rotate B Right                                                                   | VSWP<br>XAX  | Vector Swap         3-47           Exchange A and X         3-21 |

| RRL<br>RRR   | Rotate Left (32)                                                                 | XAY          | Exchange A and Y                                                 |

| RSS          | Rotate Right (32)         3-18           Reverse Skip Sense         3-12         | XBX          | Exchange B and X                                                 |

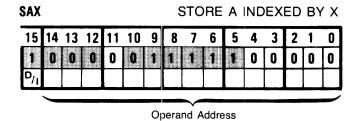

| SAX          | Store A Indexed by X                                                             | XBY          | Exchange B and Y                                                 |

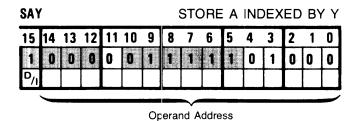

| SAY          | Store A Indexed by Y                                                             | XCA1         | Cross Compare A through DATA1 Map . 4-6                          |

| SBS          | Set Bits                                                                         | XCA2         | Cross Compare A through DATA2 Map . 4-7                          |

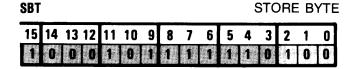

| SBT          | Store Byte                                                                       | XCB1         | Cross Compare B through DATA1 Map . 4-7                          |

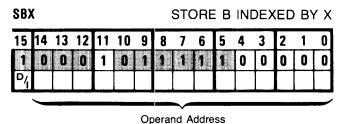

| SBX          | Store B Indexed by X 3-20                                                        | XCB2         | Cross Compare B through DATA2 Map . 4-7                          |

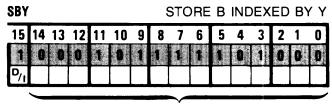

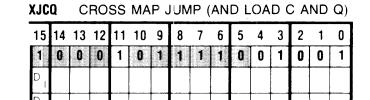

| SBY          | Store B Indexed by Y                                                             | XJCQ         | Cross Map Jump (and Load C and Q) 4-4                            |

| SDSP         | Store Display 5-7                                                                | XJMP         | Cross Map Jump 4-4                                               |

| SEZ          | Skip if E is Zero 3-12                                                           | XLA1         | Cross Load A through DATA1 Map 4-5                               |

### ALPHABETICAL INDEX OF STANDARD INSTRUCTIONS (Continued)

| INSTRU | CTION PAGE                             | INSTRU | OCTION PAGE                                  |

|--------|----------------------------------------|--------|----------------------------------------------|

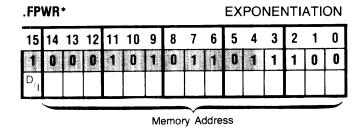

| XLA2   | Cross Load A through DATA2 Map 4-5     | .FPWR  | Exponentiation                               |

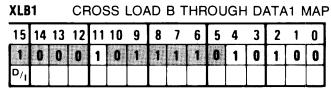

| XLB1   | Cross Load B through DATA1 Map 4-5     | .FWID  | Firmware Identification                      |

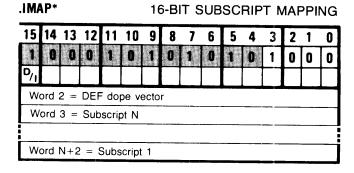

| XLB2   | Cross Load B through DATA2 Map 4-5     | .IMAP  | 16-Bit Subscript Mapping                     |

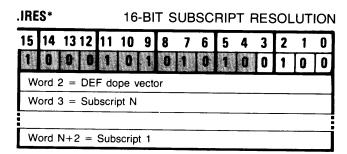

| XOR    | "Exclusive Or" to A                    | .IRES  | 16-Bit Subscript Resolution 3-33             |

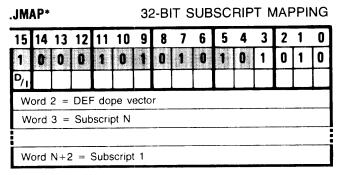

| XSA1   | Cross Store A through DATA1 Map 4-6    | .JMAP  | 32-Bit Subscript Mapping3-34                 |

| XSA2   | Cross Store A through DATA2 Map 4-6    | .JRES  | 32-Bit Subscript Resolution 3-34             |

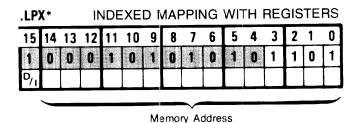

| XSB1   | Cross Store B through DATA1 Map 4-6    | .LBP   | Mapping with Registers 3-35                  |

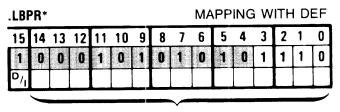

| XSB2   | Cross Store B through DATA2 Map 4-6    | .LBPR  | Mapping with DEF                             |

| .BLE   | Single Floating Point to Double        | .LPX   | Indexed Mapping with Registers 3-34          |

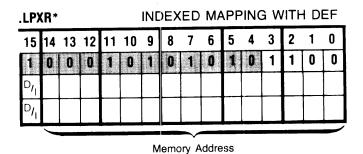

|        | Floating Point                         | .LPXR  | Indexed Mapping with DEF3-34                 |

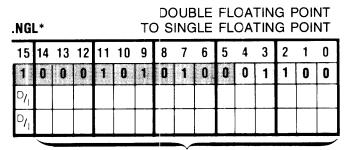

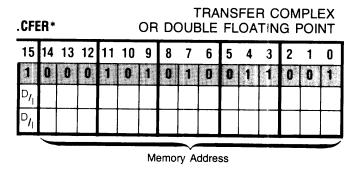

| .CFER  | Transfer Complex or Double Floating    | .NGL   | Double Floating Point to Single              |

|        | Point                                  |        | Floating Point                               |

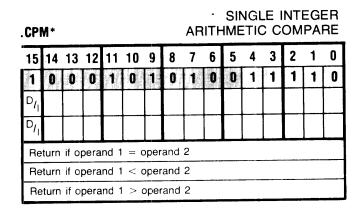

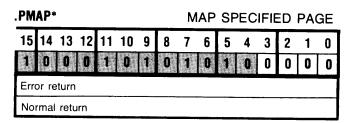

| .CPM   | Single Integer Arithmetic Compare 3-30 | .PMAP  | Map Specified Page                           |

| .CPUID | Processor Identification               | .SETP  | Sev A Table                                  |

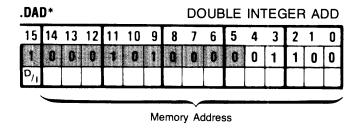

| .DAD   | Double Integer Add3-31                 | .SIP   | Skip if Interrupt Pending 3-35               |

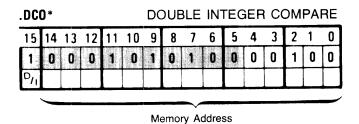

| .DCO   | Double Integer Compare                 | .TADD  | Double Floating Point Add 3-27               |

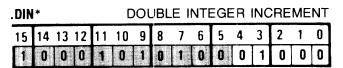

| .DDE   | Double Integer Increment               | .TDIV  | Double Floating Point Divide 3-27            |

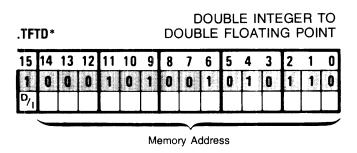

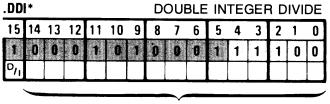

| .DDI   | Double Integer Divide 3-31             | .TFTD  | Double Integer to Double                     |

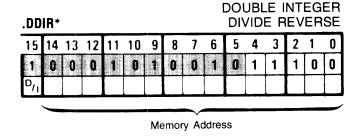

| .DDIR  | Double Integer Divide Reverse 3-32     |        | Floating Point                               |

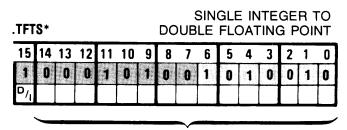

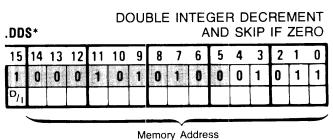

| .DDS   | Double Integer Decrement and Skip      | .TFTS  | Single Integer to Double                     |

|        | if Zero3-32                            |        | Floating Point                               |

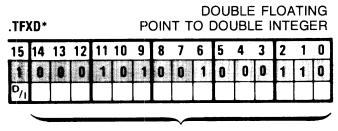

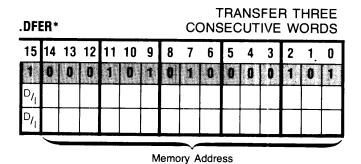

| .DFER  | Transfer Three Consecutive Words 3-29  | .TFXD  | Double Floating Point to                     |

| .DIN   | Double Integer Increment               |        | Double Integer                               |

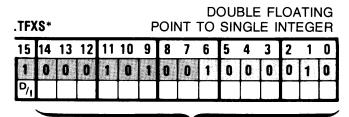

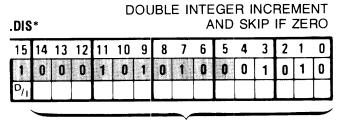

| .DIS   | Double Integer Increment and Skip      | .TFXS  | Double Floating Point to Single Integer 3-27 |

|        | if Zero3-32                            | .TMPY  | Double Floating Point Multiply 3-27          |

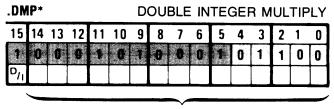

| .DMP   | Double Integer Multiply                | .TPWR  | Exponentiation                               |

| .DNG   | Double Integer Negate                  | .TSUB  | Double Floating Point Subtract 3-27          |

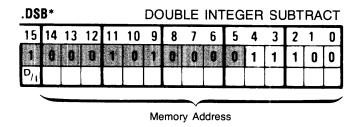

| .DSB   | Double Integer Subtract                | .WFI   | Wait for Interrupt                           |

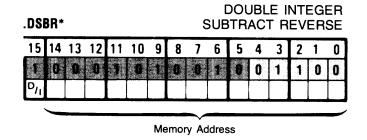

| .DSBR  | Double Integer Subtract Reverse 3-31   | .XFER  | Transfer Three Consecutive Words 3-29        |

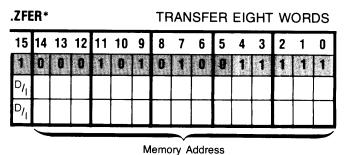

| .ENTC  | Transfer Parameter Addresses 3-29      | .ZFER  | Transfer Eight Words                         |

| .ENTN  | Transfer Parameter Addresses 3-29      | FCM    | Complement and Normalize Single              |

| .ENTP  | Transfer Parameter Addresses 3-30      |        | Floating Point                               |

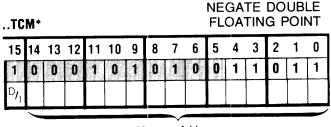

| .ENTR  | Transfer Parameter Addresses 3-30      | TCM    | Complement and Normalize Double              |

| .FIXD  | FLoating Point to Double Integer 3-26  |        | Floating Point                               |

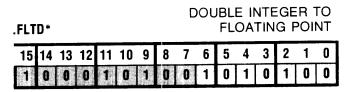

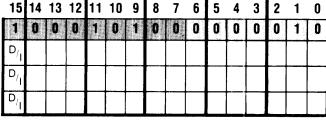

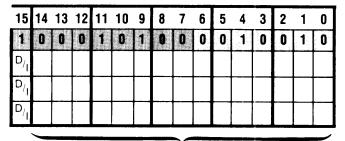

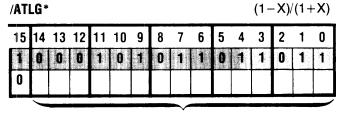

| .FLTD  | Double Integer to Floating Point 3-26  | /ATLG  | (1-X)/(1+X)                                  |

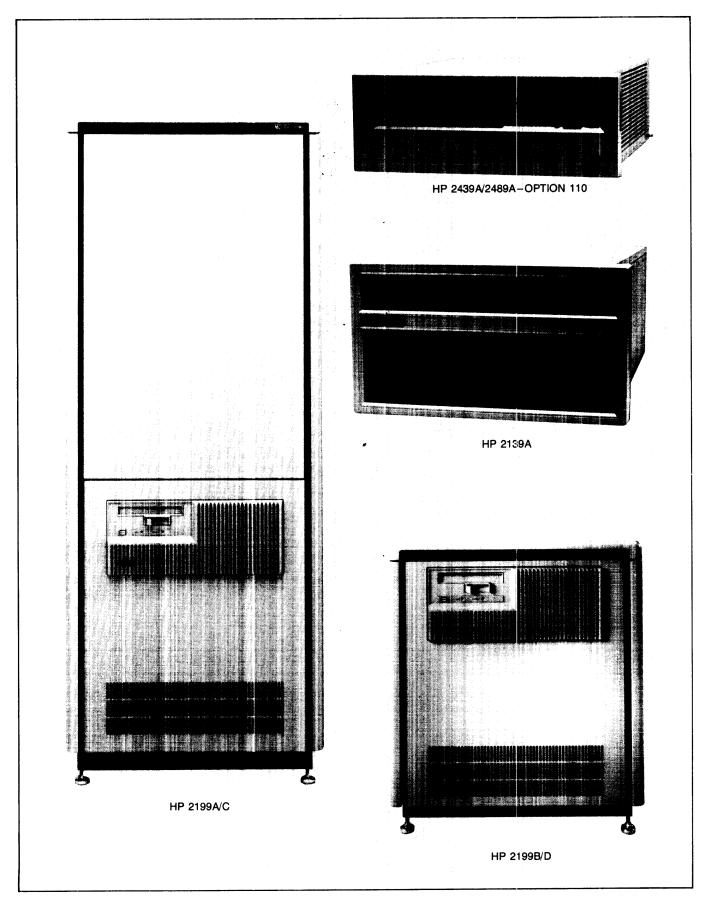

Figure 1-1. HP 1000 A900 Computers

## GENERAL FEATURES

The HP 1000 A900 Computer and Computer System (hereafter referred to as A900 computers) are the most powerful members of the HP 1000 A-Series Computer family. The A900 computers deliver full minicomputer power to a wide variety of applications, and maintain software compatibility with previous HP 1000 Computers. The A900 hardware is available as HP 2139A/2439A Computers (boxes) and computer system processor units (HP 2199A/B/C/D and HP 2489A). (See Figure 1-1.)

#### 1-1. ARCHITECTURE

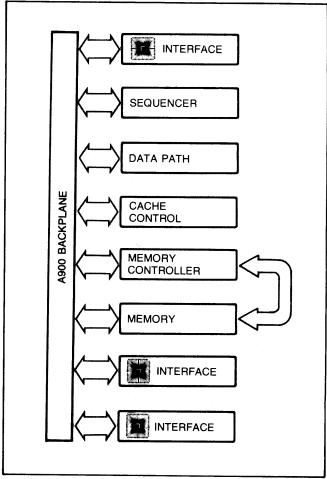

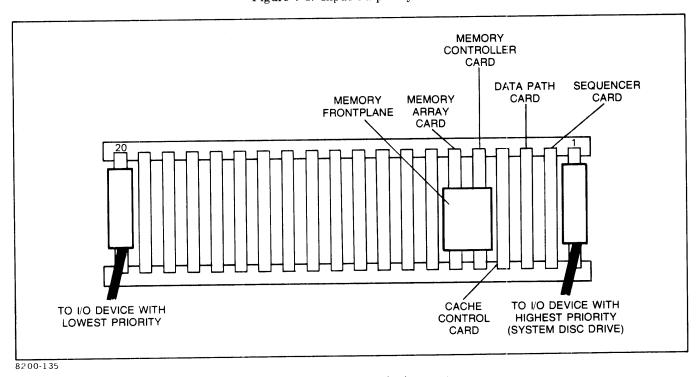

The A900 computer architecture is based on a distributed intelligence concept that separates the processing of input/output (I/O) instructions from that of other instructions. The central processor unit (CPU) features a microprogrammed control processor and resides on four printed-circuit cards called the sequencer, data path, cache control, and memory controller cards. The computer has cache memory for fast access to instructions and data, and uses pipelining for fast processing. The CPU executes the powerful HP 1000 instruction set, including index instructions and a full complement of instructions for logical operations as well as bit and byte manipulation. The A900 computer base instruction set also includes floating-point, double-integer, and virtual memory addressing instructions, and a language instruction set that substantially increases program execution speed for such high-level languages as FORTRAN and Pascal. The CPU also performs several system level functions, including memory protect, power fail/auto restart, time base generation, memory error interrupt, and extensive self-tests. The A-Series architecture also includes a feature called Code and Data Separation (CDS) which accommodates programs that have up to 4 million words of code.

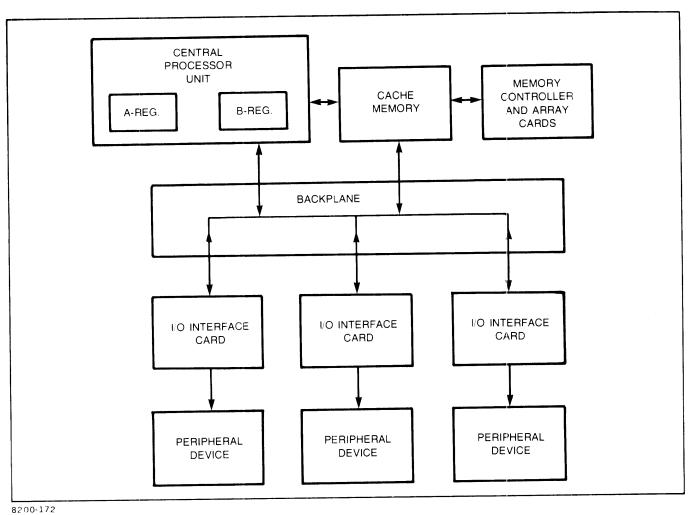

All input/output instructions are executed by custom silicon-on-sapphire (SOS) input/output processor (IOP) integrated circuit chips that reside on the individual I/O interface cards. The instructions are fetched from memory and decoded by the processor cards. When an instruction is decoded as being of the I/O type, it is broadcast on the backplane for execution by the appropriate I/O processor chip. Because each I/O card is capable of operating independently of the CPU, the A900 can perform direct memory access (DMA) I/O transfers very efficiently. An I/O card interacts with the CPU only on DMA initiation and completion; beyond that, the entire high-speed transfer is handled by the I/O card, leaving the CPU free to work on other tasks. This achieves high efficiency in CPU and I/O throughput. Figure 1-2 is a simplified block diagram of the A900 computer.

8200-137

Figure 1-2. A900 Computer Simplified Block Diagram

#### 1-2. FLOATING-POINT HARDWARE

The A900 includes as a standard feature high-speed dedicated logic that performs floating-point arithmetic operations. The floating-point logic has three custom SOS chips and provides exceptionally fast execution of single precision (32-bit) and double precision (64-bit) floating point operations. Microcoded firmware implements a powerful Scientific Instruction Set (SIS) that performs trigonometric, logarithmic, and other transcendental functions. The A900 also includes a Vector Instruction Set (VIS) which uses the floating-point chips as a computing resource to perform vector and matrix arithmetic and to process large data arrays. The floating-point hardware achieves extremely high accuracy with computational speeds that are 6 to 30 times faster than comparable software routines.

#### 1-3. USER MICROPROGRAMMING

The power and flexibility of microprogramming is made available to the A900 computer user through a microinstruction set of microorders. Microprogrammers have access to special scratch pad registers in addition to the other internal registers of the A900, and can address up to 32K 48-bit words of control store. A900 computers also support up to 14 levels of nested subroutines in microprograms. Microprogramming offers the advantages of speed and security as well as the ability to expand the instruction set to meet a variety of special computing needs.

Microprogramming is supported by Hewlett-Packard through a software package and customer training courses. A paraphraser microassembler allows the user to write microprograms in a versatile free-format style that greatly enhances program readability and documentation compared to traditional microprogramming techniques. User-developed microprograms can be dynamically loaded into optional Writable Control Store (WCS) for execution, and permanently fused into programmable read-only memory (PROM) chips for mounting on the optional Control Store card. (Refer to Section VIII for more information on microprogramming.)

#### 1-4, VIRTUAL CONTROL PANEL

The Virtual Control Panel (VCP) program is an interactive program that enables an external device (such as a terminal) to control the CPU in a manner similar to a conventional computer control panel and also provides additional features. That is, it allows the operator to access the various registers (A, B, etc.), examine or change memory, and control execution of a program. The VCP program is stored in PROM on the cache control card. In a typical application, the VCP could be an HP 262x or HP 264x Terminal interfaced by an HP 12005 Asynchronous Serial Interface Card. When not being used as the VCP, the VCP-assigned terminal can be used in the same way as any other terminal connected to the system. When the A900 computer is operating as a node in a computer network via DS/1000-IV, the VCP can be an adjacent computer in the network.

#### 1-5. BOOTSTRAP LOADERS

There are several bootstrap loaders stored in PROM on the cache control card. The loaders provide program loading from several sources including disc drives, PROM storage modules, a DS/1000-IV network link, HP mini-cartridge tapes, magnetic tape drive, and cartridge tapes of the HP 7908/11/12/14 Disc Drives. The first three loaders can be selected for auto-boot by switches on the data path card; any of the loaders can be selected by operator commands via the Virtual Control Panel.

#### 1-6. SELF-TEST FIOUTINES

Two self-test routines are standard in the A900 computer and are stored in PROM on the sequencer and cache control cards. These routines are executed whenever computer power is turned on, providing a convenient confidence-check of the processor cards and memory cards. Execution of both routines can also be initiated by a switch on the sequencer card, and execution of the second routine can be initiated by operator command via the Virtual Control Panel.

#### 1-7. TIME BASE GENERATOR

The memory controller card includes a time base generator that can be used to time external events or to create a real-time clock in software. The time base generator (TBG) can generate an interrupt every 10 milliseconds. The TBG, which can be enabled and disabled by standard I/O instructions, is disabled at power up.

#### 1-3. POWER SUPPLY

A900 computers have a power supply designed to continue normal operation in environments where ac input line voltages and frequencies may vary widely without affecting the operation of the computer. An optional battery backup card and battery pack can be installed area to sustain memory for up to 180 minutes in the event of a complete power failure, thus providing an automatic restart capability. Another power supply option provides two 25-kHz voltages that can be rectified at the load and used to power accessory plug-in cards used for measurement and control applications.

#### 1-9. INPUT/OUTPUT

The input/output system for A900 computers features a custom SOS chip on each I/O card, enabling each card to process its own I/O instructions and handle direct memory access (DMA) data transfers. The I/O system has a multilevel vectored priority interrupt structure with 53 distinct interrupt levels, each of which has a unique priority assignment. Any I/O device can be selectively enabled or disabled, or all I/O devices can be enabled or disabled under program control.

Data transfer between the computer and I/O devices can take place under DMA control or program control. The DMA capability provides a direct link between memory and I/O devices. The total bandwidth through multiple DMA channels is 3.7 million bytes (1.85 million words) per second.

The A900 computer backplane provides the link between the processor, memory, interface cards, and the power supply. In the card cage of the HP 2439A/89A, the backplane has 16 plug-in card slots, of which two are reserved for the optional battery backup card and 25-kHz

A900 General Features

power module. Three slots must be used for the processor cards, one for the memory controller card, and one for each memory array card. Thus, in the HP 2439A, there are nine slots available for I/O cards (if only one memory array card is installed) or eight slots available (if the maximum of two array cards is installed), provided that the battery backup card is not installed. In addition to the three processor cards and the two memory cards, the HP 2489A System Processor Unit (SPU) includes as standard a terminal interface card and an HP-IB interface card (for a disc drive), leaving either six or seven slots available for I/O cards.

In the HP 2139A and 2199A/B/C/D the backplane has 20 plug-in card slots. With the three processor cards and two memory cards installed, the HP 2139A has up to 15 slots available for I/O cards, depending upon the number of additional memory array cards installed. In addition to the five basic processor and memory cards, the HP 2199A/B/C/D SPU includes as standard a terminal interface card and an HP-IB interface card (for a disc drive), leaving up to 13 slots available for I/O cards. An SPU that has the full complement of six million bytes of memory still has six slots available for additional I/O cards. The number of available I/O slots may be increased by using an HP 12025A/B I/O Extender with the A900 computer.

The A900 computer uses standard HP A/L-Series I/O cards. An important feature of these cards is a common-content Global Register which can be loaded with the select code of a specific I/O card. When the Global Register is enabled all I/O instructions are executed only by the I/O card whose select code is in the Global Register. This not only facilitates setting up DMA transfers but also makes reconfiguration of an I/O driver a simple matter of changing the Global Register to the appropriate select code. Also, since the Global Register can direct I/O instructions to a specific I/O card, the I/O-instruction address bits can be used to access registers on an I/O card.

About one-third of the area on all A/L-Series I/O cards is occupied by identical logic called the I/O Master, consisting of an I/O processor chip and its associated logic. The I/O Master is also available in breadboard form for users who wish to design their own I/O cards. The I/O Master is described in detail in the HP 1000 L-Series Computer I/O Interfacing Guide, part no. 02103-90005.

#### 1-10 MEMORY

A900 computers are available with semiconductor memory systems based on 64k-bit and/or 256k-bit dynamic RAM (random-access memory) chips. The memory system consists of a memory controller card with error-correction capability, up to eight HP 12220A/21A Memory Array Cards, and a memory frontplane. The 12220A card uses 64k-bit chips and provides 768 kilobytes of memory, while the 12221A card uses 256k-bit chips and provides three megabytes of memory; both cards may be used together in the same computer. The data is stored in memory as two

16-bit words with 7-bit error correction to detect errors. Data is transferred over the frontplane to the memory controller, and all data transfers occur 39 bits at a time (two 16-bit words and 7 check bits).

The error-correcting memory system provides fault-secure memory operation for the A900 computers. The system is capable of correcting all single-bit errors, and of detecting all double-bit errors and many multiple-bit errors. The memory controller card logs the physical address and error syndrome of single-bit errors, and an LED on each memory array card will indicate a multiple-bit error that occurs on that card after the last power-on. The error-correcting system is particularly valuable in computer systems with large amounts of memory, or where fault-secure operation is essential.

The maximum memory size available in A900 computers is 24 megabytes. Addressing physical memory configurations larger than 64k bytes is made possible by the use of the Dynamic Mapping System (DMS), which is standard in the A900 and is described in Section IV. The DMS is a powerful memory management scheme that allows A900 computer users to address up to 32 megabytes of memory and provides either write or read-and-write protection of each individual 2048-byte page.

#### 1-11. CACHE MEMORY

For high performance, the A900 utilizes high-speed, 4k-byte, single-set cache memory with write-to and readbefore-write features. This provides single-cycle access to memory for both reads and writes for the CPU when the requested data is in the cache. If the data is not in the cache, then the cache must wait for four CPU cycles before completing the request. Since the probability of the data being in cache (hit) is much more likely than its not being there (miss), the effective memory access time is close to one CPU cycle. The exact ratio of hits to total cycles varies according to what type of program is running and how localized its requests are. The average hit ratio is expected to be around 88 percent but is highly variable.

The main memory for the A900 is not connected to the computer backplane. DMA requests from I/O cards are buffered by the cache memory, and the CPU can still use memory (cache) during high DMA traffic. Likewise, CPU memory operations do not go across the I/O backplane; therefore, DMA does not get held back by a high rate of CPU memory requests. This parallelism makes the A900 ideal for applications where both DMA rate and processor throughput are very important.

For its address, the cache memory takes a 15-bit logical address plus a 5-bit map set select address and translates these via the Dynamic Mapping System into a 24-bit physical address. It also checks for violations of protected memory.

Update 4 1-3

#### 1-12. SOFTWARE

Software support for the A900 computer begins with RTE-A, a member of HP's family of Real-Time Executive (RTE) operating systems. RTE-A is a real-time multiprogramming, multi-user system designed to take full advantage of the A900 I/O structure to enhance overall CPU and I/O throughput. RTE-A offers a wide range of configurations, from a small, memory-based, execute-only system to a full disc-based system with on-line program development. Utilizing the A900 mapped memory system, RTE-A supports user partitions of up to 64k bytes and memory sizes from 128k bytes to 24 megabytes. Memory can be divided into fixed and dynamically allocated partitions at system generation time. Critical programs can be made resident in fixed partitions to ensure fastest possible response to requests for their execution. Other programs can be assigned partitions from the dynamic memory pool according to need, using the smallest available block of memory.

RTE-A also supports Virtual Memory Addressing (VMA) for access to data arrays much larger than main memory (up to 128 megabytes). The disc functions as an extension of main memory so far as data is concerned, in a manner that is transparent to the user and does not require any special programming. In addition, RTE-A supports a special case of VMA, called Extended Memory Area (EMA). With EMA, up to two megabytes of a program's data can be in main memory at once, which affords faster processing of data arrays small enough to use the EMA capability. The programmer chooses the data array handling mode at program load time.

Disc-based RTE-A systems support program development in FORTRAN 77, Pascal/1000, BASIC, and Macro/1000 Assembly Language. Program development for the A900 can also be performed on an HP 1000 System under RTE-6/VM or RTE-IVB.

The HP 92078A software accessory package provides software support, via the Code and Data Separation (CDS) feature, for programs that have up to 4M words of code. With CDS, a large application program is automatically segmented by the LINK loader program into one or more code segments, in addition to a data segment which may be up to 31k words in size; the program may also access a VMA area. The code segments may reside on disc or in memory, and the process of accessing code segments in physical memory, or loading a code segment from disc into physical memory, is automatically handled by a combination of microcode and software. CDS is described further in Section V.

The diagnostic packages listed in Table 1-1 may be used for testing and fault location.

#### OF HP INTERFACE BUS

Among the I/O interface cards available for the A900 computer is the HP 12009A HP-IB Interface Card which can interface the A900 computer to a variety of HP peripherals and other equipment compatible with the Hewlett-Packard Interface Bus (HP-IB). (HP-IB is the Hewlett-Packard implementation of IEEE standard 488-1978, "Digital Interface for Programmable Instrumentation".) A single HP 12009A can control up to 14 HP-IB instruments, and several can be used to achieve concurrent operation of multiple HP-IB instrumentation clusters under the RTE-A multiprogramming operating system.

#### 1-14 COMPLITED NETWORK

The user can configure the A900 computer into an HP DS/1000-IV Distributed System by using either an HP 12007A or an HP 12044A HDLC Interface. Both of these interfaces support the high-level data link communications (HDLC) protocol, functioning as a preprocessor to handle low and medium levels of protocol processing. The A900 computers can be easily mixed with other members of the HP 1000 family in a single computer network. The HP 12042A Programmable Serial Interface allows the sophisticated OEM to design his own customized protocol for networks. Hewlett-Packard offers a customer training course on how to program the PSI card.

#### 1-15. EXPANSION AND ENHANCEMENT

Table 1-1 lists accessory products available to expand or enhance the A900 computers.

#### 1-16 SPECIFICATIONS

Complete specifications for the A900 computers and system processor units are given in a data handbook available from your nearest Hewlett-Packard Sales and Service Office. (These offices are listed at the rear of this manual.) Table 1-2 provides an abridged set of A900 specifications. Except where indicated, the specifications are applicable to both the computers and the system processor units. Both the computers and the SPUs meet the safety standards of the Underwriters' Laboratories (UL), the Canadian Standards Association (CSA), and the International Electrotechnical Commission (IEC). The A900 computers and SPUs also meet the Federal Communications Commission (FCC) Class A and Verband Deutscher Elektrotechniker (VDE) Level A standards for electromagnetic interference (EMI).

Table 1-1. Options and Accessories

| DESCRIPTION                                                                     | HP PRODUCT NO. | OPTION NO |

|---------------------------------------------------------------------------------|----------------|-----------|

| Removes standard memory array card                                              |                | 014       |

| 230 Vac Operation                                                               |                | 015       |

| 768k Byte Memory Array Card                                                     | 12220A         |           |

| 3M Byte Memory Array Card .                                                     | 12221A         | 1.35      |

| Memory Frontplane for one memory array card                                     | 12222A         |           |

| Memory Frontplane for two memory array cards                                    | 12222B         |           |

| Memory Frontplane for three memory array cards                                  | 12222C         |           |

| Memory Frontplane for four memory array cards                                   | 12222D         |           |

| Memory Frontplane for five memory array card                                    | 1222E          |           |

| Memory Frontplane for six memory array cards                                    | 12222F         |           |

| Memory Frontplane for seven memory array cards                                  | 12222G         |           |

| Memory Frontplane for eight memory array cards                                  | 12222H         |           |

| Asynchronous Serial Interface                                                   | 12005B         |           |

| Parallel Interface                                                              | 12006A         |           |

| HDLC Interface (modern operation)                                               | 12007A         |           |

| PROM Storage Module                                                             | 12008A         |           |

| HP-IB Interface                                                                 | 12009A         |           |

| Intelligent Breadboard                                                          | 12010A         |           |

| Extender Board (for memory and I/O cards)                                       | 12011A         |           |

| Extender Board (for processor cards)                                            | 12240A         |           |

| Priority Jumper Card                                                            | 12012A         |           |

| Input/Output Extender                                                           | 12025A/B-001   |           |

| 8-Channel Asynchronous Multiplexer                                              | 12040B         |           |

| Programmable Serial Interface                                                   | 12042A         |           |

| HDLC Interface (hard-wired operation)                                           | 12044A         |           |

| High-Level Analog Input Card                                                    | 12060A         |           |

| Expansion Multiplexer Card                                                      | 12061A         |           |

| Analog Output Card                                                              | 12062A         |           |

| 16-In/16-Out Isolated Digital I/O Card                                          | 12063A         |           |

| DS/1000-IV Data Link Slave Interface                                            | 12072A         |           |

| DS/1000-IV Modern Interface to HP 3000                                          | 12073A         |           |

| AP-B Network Interface                                                          | 12075A         |           |

| DS/1000-IV Direct Connect Interface to HP 3000                                  | 12082A         |           |

| Sattery Backup Card                                                             | 12154A**       |           |

| Battery Backup Module                                                           | 12157A         |           |

| 25 kHz Sine Wave Module                                                         | 12158A         |           |

| 25 kHz Power Module                                                             | 12159A**       |           |

| Control Store Card                                                              | 12205A         |           |

| Diagnostic Package for A900 processor and interfaces                            | 24612A*        |           |

| Diagnostic Package for A900-compatible hard disc drives and magnetic tape units | 24398B*        |           |

<sup>\*</sup>Included with the HP 2199A/B/C/D and HP 2489A System Processor Units.

<sup>\*\*</sup>For HP 2439A and 2489A only.

Table 1-2. Specifications

#### SPECIFICATIONS COMMON TO THE HP 2139A, 2199A/B/C/D, 2439A, and 2489A

#### **CENTRAL PROCESSOR**

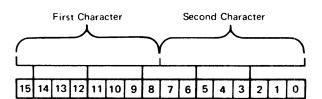

Word Size: 16 bits

Instruction Set: 292 standard instructions

Memory Reference:14Register Reference:43Input/Output:13Extended Arithmetic:10Index:34

Index: 34

Bit, Byte, Word Manipulation: 10

Floating Point: 16

Scientific: 14

Language: 14

Dynamic Mapping: 40

Vector Instructions: 38

Double Integer: 12

Virtual Memory: 9

Operating System: 4

Code and Data Separation: 21

Registers:

Accumulators: Two (A and B), 16 bits each. Implicitly addressable, also explicitly addressable as

memory locations.

Index: Two (X and Y), 16 bits each

Memory Register: One (P), 15 bits

**Base:** One (Q), 15 bits; one (C), 1 bit.

Bounds: One (Z), 16 bits

Supplementary: Two (overflow and extend), one bit each

**Power Fail Provisions:**When primary line power falls below a predetermined level while the computer is running, a power fail warning signal from the computer power supply causes an

running, a power fail warning signal from the cornputer power supply causes an interrupt to memory location 00004. This location is intended to contain a jump-to-subroutine (JSB) instruction to a user-supplied power fail subroutine. A minimum

of 5 milliseconds is available to execute the power fail subroutine.

Time Base Generator Interrupt: A time base generator interrupt is provided for maintaining a real time clock. The

interrupt request is made when the CPU signals, at 10-millisecond intervals, that its internal clock is ready to roll over. Timing accuracy of the time base generator

is ±2.16 seconds per 24-hour day.

**MEMORY**

Implementation: 64k or 256k dynamic RAM

Cache Size: 4k bytes

Cache Cycle Time: 133 nanoseconds

Cache Fault Processing Time: 532 to 931 nanoseconds

Main Memory Cycle Time: Read: 532 nanoseconds

Write: 400 nanoseconds

**Average Effective Memory**

Access Time:

Memory Structure:

Approximately 181 nanoseconds, assuming 88% cache hit rate.

32 pages of 2048 bytes per page, with direct access to current page or base page (page 0), and indirect or indexed access to all pages. With CDS enabled, a 15-bit

base register is added to addresses on base page.

Memory Expansion: Paged memory address space expandable to 16k pages of 2048 bytes with

standard Dynamic Mapping System. Maximum physical memory capacity is cur-

rently 12k pages (24 megabytes).

#### Table 1-2. Specifications (Continued)

#### SPECIFICATIONS COMMON TO THE HP 2139A, 2199A/B/C/D, 2439A, and 2489A (Continued)

INPUT/OUTPUT

Determination of I/O Address: I/O address select code is set for each interface card by select code switches on

the card and is therefore independent of interface card position in the card cage.

I/O Device Interrupt Priority: Depends upon I/O interface card position in the card cage with respect to the

processor cards.

Interrupt Masking: The I/O Master Logic includes an interrupt mask register which provides for

selective inhibition of interrupts from specific interfaces under program control. This capability can be programmed to temporarily cut off undesirable interrupts from any combination of interfaces when they could interfere with crucial transfers.

Interrupt Latency (without DMA interference):

3.7 to 19 microseconds. 4 microseconds typical. (Interrupts cannot be serviced until a DMA cycle or an instruction in progress has completed execution.) The worst-case latency of 19 microseconds is based upon the longest uninterruptible

time.

Direct Memory Access (DMA): The I/O processor chip supports DMA capability on each I/O interface, which re-

duces the number of interrupts from one per data item (byte or word) to one per

complete DMA block.

Data Packing Under DMA: When byte mode is specified in Control Word instructions, the I/O processor chip

automatically packs or unpacks bytes.

Maximum Achlevable DMA Rate: 1.85 million words (3.7 megabytes) per second for input transfers; 1.5 million

words (3.0 megabytes) per second for output transfers.

SAFETY AND RFI QUALIFICATION: HP 1000 A900 products meet the safety standards of the Underwriters' Laboratories (UL), the Canadian Standards Association (CSA), and the International Electrotechnical Commission (IEC). The A900 also complies with the RFI

standards of the Federal Communications Commission (FCC) and Verband

Deutscher Electrotechniker (VDE).

VIBRATION AND SHOCK: HP 1000 A900 products are type tested for normal shipping and handling shock

and vibration. (Contact factory for review of any application that requires operation

under continuous vibration.)

Table 1-2. Specifications (Continued)

#### SPECIFICATIONS COMMON TO THE HP 2139A, 2199A/B/C/D

#### **POWER SUPPLY**

Output: DC voltages and tolerances

+5V ±2% +12V +6/-3% -12V ±6%

Optional AC Voltages and

Tolerances:

27V rms  $\pm 8\%$ , 25 kHz nominal, split phase from three pins on backplane-mating

connector. Total harmonic distortion: <10%.

**Maximum Output Current**

Ratings:

+5V +5M 70A 10.0A

+12V 5.6A -12V 3.5A 25 kHz 1.5A

**Short Circuit Protection:**

All dc and ac power outputs are fault protected for short circuits. The power supply will shut down if any of the outputs are short circuited at turn on.

+5V Output Overvoltage

Protection:

The +5V output is sensed for overvoltage and the +5V supply shuts down if its output voltage exceeds 5.5V. The ac power switch must be cycled to reset the

+5V output.

DC Current Available for

I/O Interfaces:

The power supply provides enough current for any combination of compatible HP

interfaces and other HP plug-ins.

**BATTERY BACKUP**

12157-60001 Battery Backup Module

1420-0304 Battery Pack

The Battery Backup System provides from 15 to 75 minutes of sustaining power depending upon the number of memory array cards (5 maximum), state of charge, and temperature; additional hold-up time can be achieved by connecting an ex-

ternal battery.

**Recharge Time:**

24 hours for fully discharged battery pack

**Battery Type:**

Sealed lead acid

#### Table 1-2. Specifications (Continued)

#### SPECIFICATIONS APPLICABLE ONLY TO THE HP 2139A COMPUTER

#### **ELECTRICAL SPECIFICATIONS**

**AC Power Required**

Line Voltage:

86-138V (115V -25%/+20%) standard;

178-276V (230V -23%/+20%) option 015.

Line Frequency:

47.5 to 66 Hz

**Maximum Power Required:**

800 watts

#### PHYSICAL CHARACTERISTICS

**Dimensions**

Height:

266 mm (10.5 in)

Width:

483 mm (19 in)

Depth:

610 mm (24 in)

Weight:

29.1 kg (64 lb)

Ventilation:

Air intake is in through the front; exhaust is out through the rear.

Volume:

Approximately 10.7 cubic metres/min. (380 CFM).

#### **ENVIRONMENTAL SPECIFICATIONS**

**Temperature**

Operating:

0° to 55°C (32° to 131°F) to 3048 metres (10,000 ft); 0° to 45°C (32° to 113°F) to 4,572

metres (15,000 ft).

Non-operating:

-40° to 75°C (-40° to 167°F)

-40° to 60°C (-40° to 140°F) with Battery Backup

**Relative Humidity:**

5% to 95% non-condensing

**Altitude**

Operating:

To 4.6 km (15,000 ft)

Non-operating:

15.3 km (50,000 ft)

#### SPECIFICATIONS APPLICABLE ONLY TO THE HP 2199A/B/C/D

#### **ELECTRICAL SPECIFICATIONS**

Standard Line Voltage and Line

Frequency

Line Voltage (With HP 7908R):

88-127V (115V nominal)

Line Voltage (With HP 7911R,

90-105V (100V nominal) or

HP 7912R, or HP 7914R):

108-126V (120V nominal)

Line Frequency:

With HP 7908R: 47.5 to 66 Hz

With HP 7911/12/14R: 54 to 66 Hz.

Option 015 Line Voltage and

Line Frequency

Line Voltage (With HP 7908R):

180-255V (230V nominal)

Line Voltage (With HP 7911R,

198-231V (220V nominal) or

7912R, or 7914R):

216-252V (240V nominal)

Line Frequency:

With HP 7908R: 47.5 to 66 Hz

With HP 7911/12/14R: 47.5 to 55 Hz

Table 1-2. Specifications (Continued)

#### SPECIFICATIONS APPLICABLE ONLY TO THE HP 2199A/B/C/D (Continued)

**Power Requirements:** Requires at least 20-ampere grounded power receptacle for 115 Vac operation, or

> at least 10-ampere grounded power receptacle for 230 Vac operation (option 015). The HP 2199A/C requires split-phase power; the HP 2199B/D requires singlephase power. An additional power receptacle is required for the system

console.

**Maximum Current Required:** HP 2199A/C: 16 amperes per phase

HP 2199B/D: 16 amperes

PHYSICAL CHARACTERISTICS

**Dimensions**

Height: HP 2199A/C: 1613 mm (63.4 in)

HP 2199B/D: 720 mm (28.3 in)

Width: 635 mm (25 in) Depth: 813 mm (32 in)

Weight

Without Disc Drive: HP 2199A/C: 139.7 kg (307.5 lb)

HP 2199B/D: 94.3 kg (207.5 lb)

HP 7908R Disc Drive adds:

37.0 kg (81.6 lb)

HP 7911R/12/14R Drive adds:

67.3 kg (148 lb)

Ventilation:

Perforations in the HP 2199B/D cabinet and in the lower part of the HP 2199A/C cabinet facilitate front-torear ventilation driven by the fans in the computer and sys-

tem disc.

Four 120 CFM fans at the top rear of the HP 2199A/C cabinet draw in air through a filter at the bottom rear of the upper section, providing bottomto-top airflow of approximately 11.3 cubic metres per minute (400 CFM). The actual value of air flow depends upon the configuration of user equipment racked in the upper section

of the cabinet.

The additional spece in the top half of the HP 2199A/C cabinet is intended for user **Racking Limitations:**

equipment installed on rails and not on slides.

**ENVIRONMENTAL SPECIFICATIONS**

**Temperature**

Operating (with HP 79xxR

Disc):

$0^{\circ}$  to  $40^{\circ}$ C (32° to  $104^{\circ}$ F), rate of change is <10°C (18°F) per hour.

Non-operating:

-40° to 60°C (-40° to 140°F)

Relative Humidity:

With HP 79xxR Disc:

20% to 80% non-condensing

**Altitude**

Operating:

To 4.6 km (15,000 ft)

Non-operating:

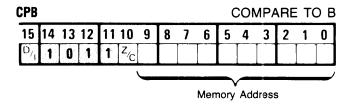

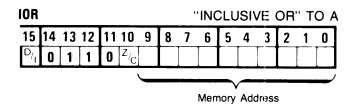

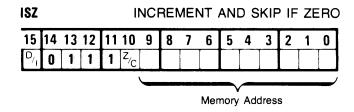

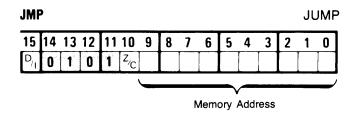

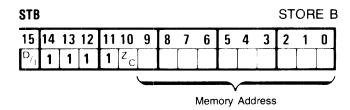

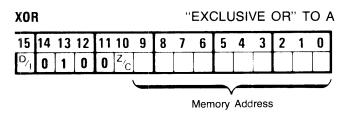

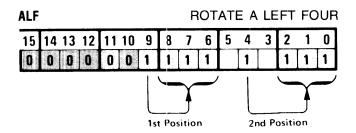

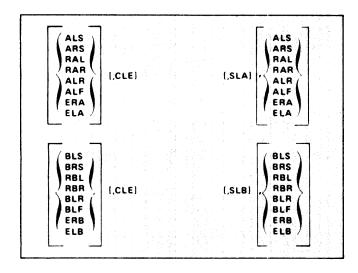

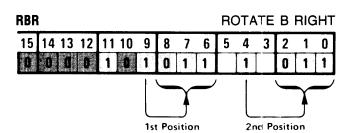

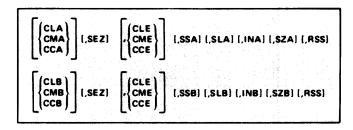

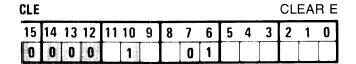

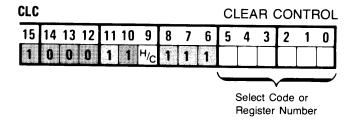

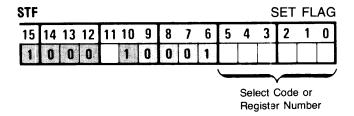

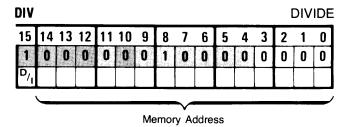

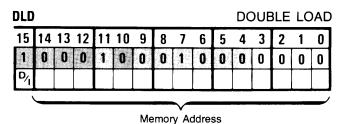

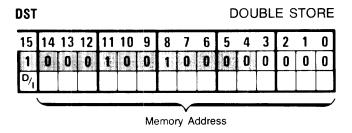

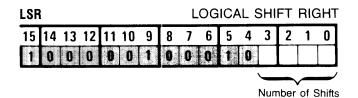

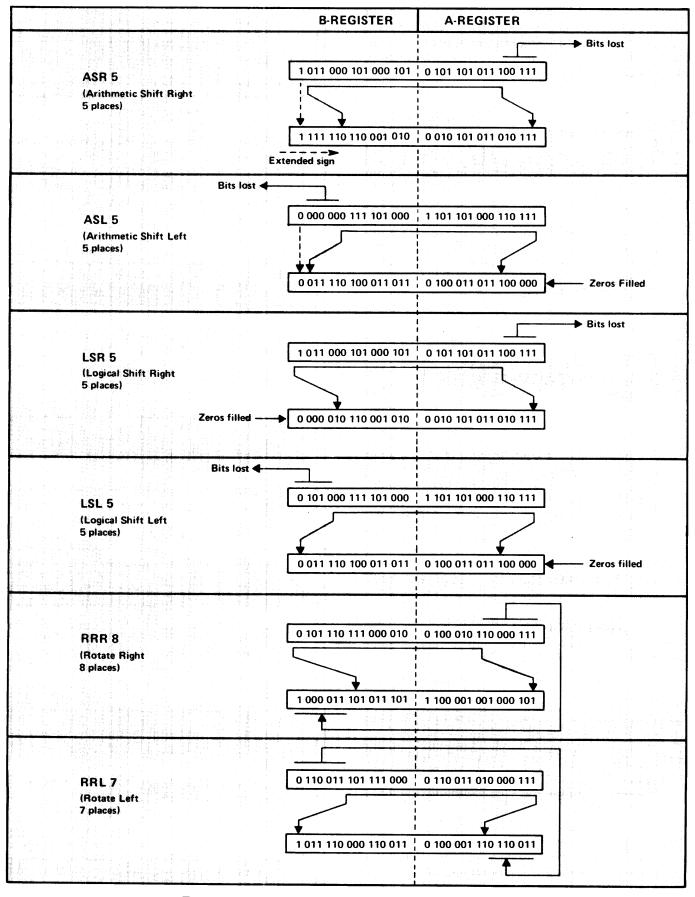

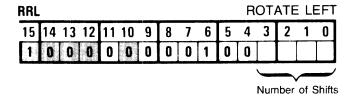

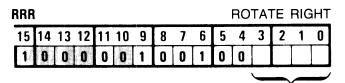

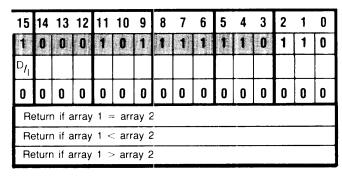

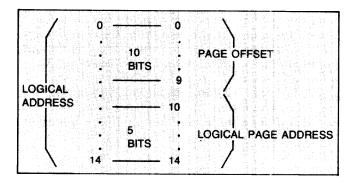

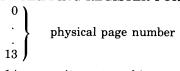

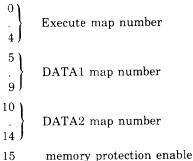

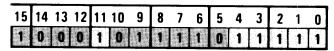

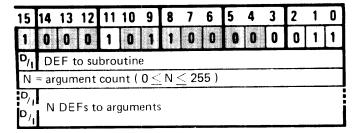

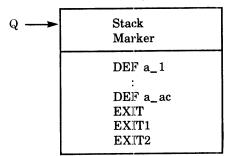

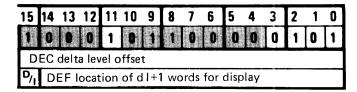

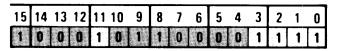

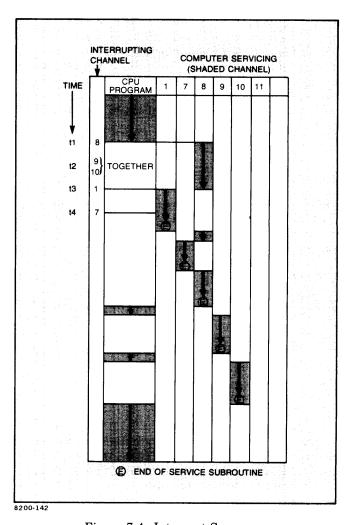

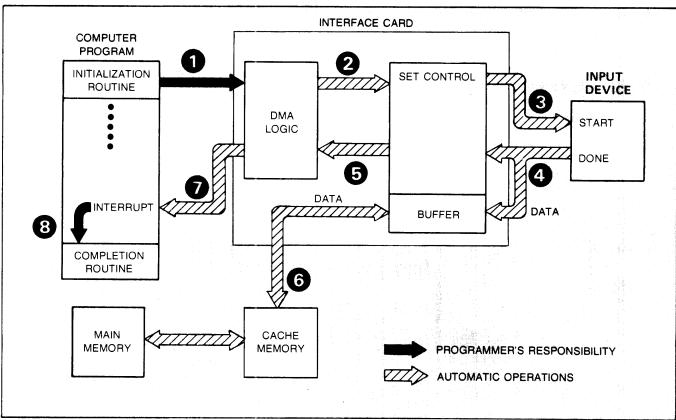

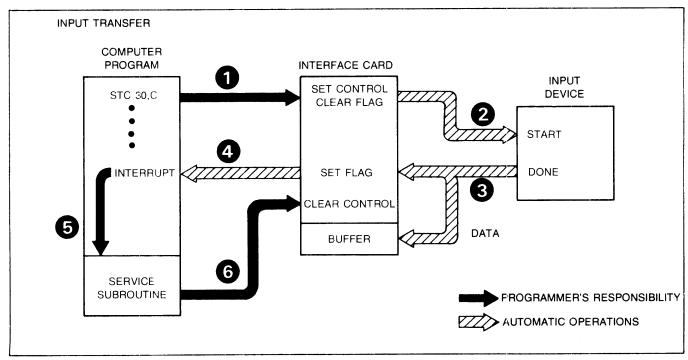

To 15.3 km (50,000 ft)