OF THE

# **1973 SAGAMORE COMPUTER CONFERENCE**

ON

# **PARALLEL PROCESSING**

Syracuse University

in cooperation with

IEEE

# PROCEEDINGS OF THE 1973 SAGAMORE COMPUTER CONFERENCE ON PARALLEL PROCESSING

Papers presented on August 22-24, 1973

Department of Electrical & Computer Engineering

SYRACUSE UNIVERSITY in Cooperation with

IEEE

ACM

Copyright (2) 1973 by the Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, N.Y. 10017

IEEE Catalog Number 73 CH0812-8 C

Additional copies available from IEEE, 345 East 47th Street, New York, N.Y. 10017. Price: \$12.00 per copy

# PREFACE

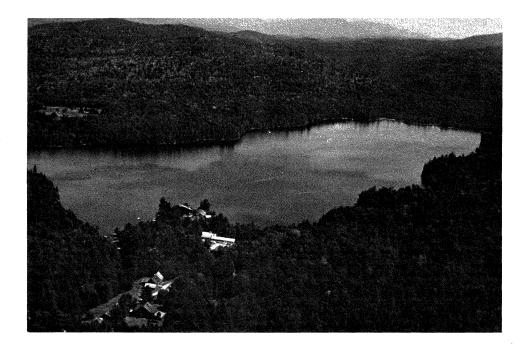

The 1973 Sagamore Computer Conference on Parallel Processing was held on August 22-24, 1973 at the former Vanderbilt summer estate in the Central Adirondack Mountains. The Conference was conceived to provide a secluded environment, a 1300-acre preserve surrounding the private Sagamore Lake, for the participants with excellent opportunities for exchanging ideas and learning each others research activities. Thus, informative discussions may be made not only during the technical sessions but also throughout the various sports and social gatherings provided by the Conference.

The enthusiastic cooperation and response that we received throughout the Conference and during its preparation was indeed most heartening. We not only received many more papers than we could possibly schedule, but also the number of requests to attend exceeded the Sagamore accomodations. Thus, there seems to be a popular demand for such a conference in parallel processing. Another conference is being scheduled for the next year — August 21-23, 1974.

The success of such a conference requires the vigorous support of many individuals. In this respect, we are most grateful to all the authors who submitted their papers for consideration. It is our deep regret that not all qualified papers could be scheduled for the Conference. We are also much indebted to all the reviewers who, in order to meet the stringent review deadlines, put aside their own busy work schedule to carefully evaluate the papers sent for their judgement. Their valuable comments not only resulted a set of high-quality papers for the Conference, but also were sincerely appreciated by many authors. The generous help we received from the session chairmen also contributes much to the success of the Conference. In addition, we wish to acknowledge the excellent cooperation provided to us by IEEE, IEEE Computer Society, ACM, their local chapter chairmen, as well as the staff of various technical magazines. In particular, we are indebted to Mr. James J. Andover, Mr. Charles Casale, Dr. W. Smith Dorsey, Prof. Michael J, Flynn, Prof. Caxton C. Foster, Mrs. Irene Hollister, Mr. David Jacobsohn, Mr. John L. Kirkley, Mr. E. D. MacDonald, Prof. Harold S. Stone, and many others for their assistance in achieving such a cooperation. Special thanks are also due to members of various committees. Their time and effort devoted to the Conference are indeed invaluable.

> Tse-yun Feng Department of Electrical & Computer Engineering Syracuse University

The Secluded Environment of Sagamore

The Main Lodge

# TABLE OF CONTENTS

| SESSION 1: SEQUENTIAL-PARALLEL TRANSFORMATION AND MODELLING                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Chairman: Professor R. M. Keller                                                                                                                                                                  |    |

| The Coordinate Method for the Parallel Execution of DO Loops<br>L. Lamport                                                                                                                        | 1  |

| Modelling for Parallel Computation: A Case Study<br>J. L. Baer                                                                                                                                    | 13 |

|                                                                                                                                                                                                   | 15 |

| Measurement of Parallelism in Ordinary FORTRAN Programs<br>D. J. Kuck, P. B. Budnik, SC. Chen, E. W. Davis, J. CC. Han,<br>P. W. Kraska, D. H. Lawrie, Y. Muraoka, R. E. Strebendt, R. A. Towle • | 23 |

| SESSION 2: LANGUAGES<br>Chairman: Mr. D. E. McIntyre                                                                                                                                              |    |

| A Language for Controlling Parallel Processes<br>B. R. Hays                                                                                                                                       | 37 |

| The Transformation of Flow Diagrams into Maximally Parallel Form<br>G. Urschler                                                                                                                   | 38 |

| Formal Transformations for Parallel Processing Logic<br>E. P. Stabler                                                                                                                             | 47 |

| A Structured Approach to Concurrent Process Synchronization<br>S. K. Shrivastava                                                                                                                  | 54 |

| SESSION 3: PARALLEL PROCESSING TECHNIQUES<br>Chairman: Dr. P. M. Kogge                                                                                                                            |    |

| Parallelism in Tape-Sorting<br>S. Even                                                                                                                                                            | 55 |

| A Parallel Algorithm for Maximum Flow Problem<br>Y. K. Chen, T. Feng                                                                                                                              | 60 |

| Parallel-Sequential Processing of Finite Patterns<br>W. I. Grosky, F. Tsui                                                                                                                        | 61 |

| Parallel Implementation of a Two-Dimensional Model<br>V. Kransky, D. Giroux, G. Long                                                                                                              | 69 |

| SESSION 4: SOFTWARE DESIGN<br>Chairman: Professor E. P. Stabler                                                                                                                                   |    |

| A Parallel Assembler for ILLIAC IV<br>J. M. Randal                                                                                                                                                | 78 |

| Process Communication Pre-Requisites or the IPC-Setup Revisited<br>M. J. Spier                                                                                                                    | 79 |

| The Experimental Implementation of a Comprehensive Inter-Module Communication<br>Facility                                                                                                         |    |

| M. J. Spier                                                                                                                                                                                       | 89 |

# TABLE OF CONTENTS (CONT'D.)

| SESSION 5: PROCESSOR COMPONENTS<br>Chairman: Captain A. R. Klayton                                        |     |

|-----------------------------------------------------------------------------------------------------------|-----|

| A Novel Method of Constructing Sorting Networks<br>R. M. Keller                                           | ~ ~ |

| R. M. Keller                                                                                              | 90  |

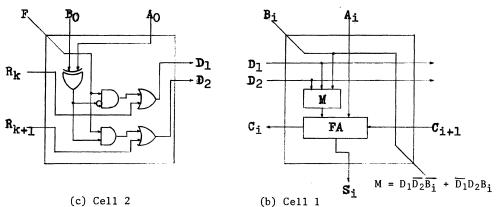

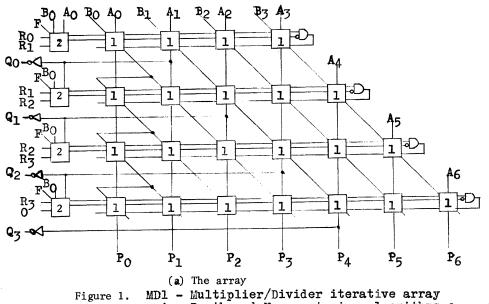

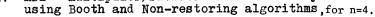

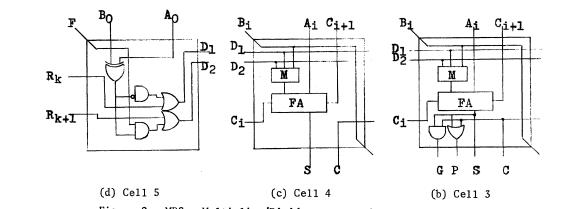

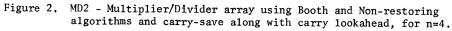

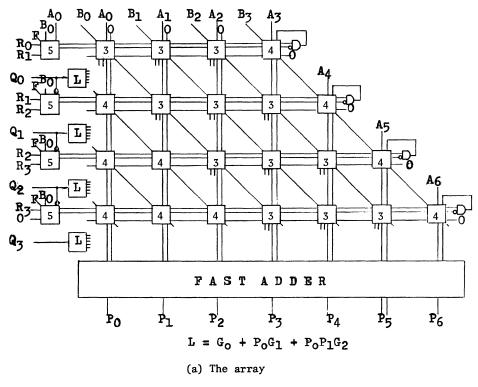

| High-Speed Multipler/Divider Iterative Arrays<br>V. C. Hamacher, J, Gavilan                               | 91  |

| A Versatile Data Manipulator<br>T. Feng                                                                   | 101 |

| An Array of Computing Memory Cells<br>T. Della Torre, J. Roitman                                          | 102 |

| SESSION 6: PROCESSOR ORGANIZATIONS<br>Chairman: Professor G. J. Lipovski                                  |     |

| An Efficient Associative Processor Using Bulk Storage                                                     |     |

| H. H. Love, Jr                                                                                            | 103 |

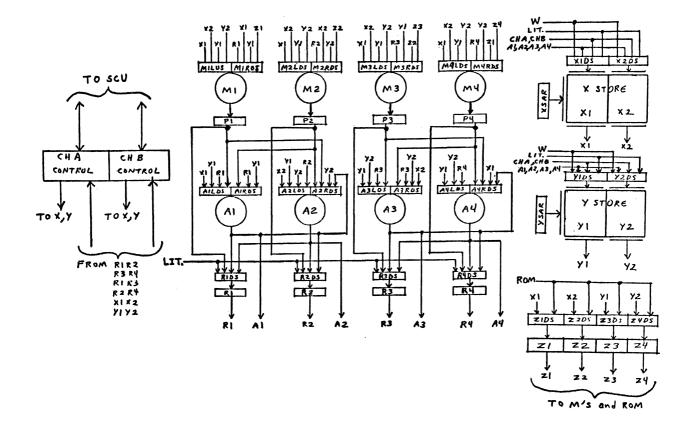

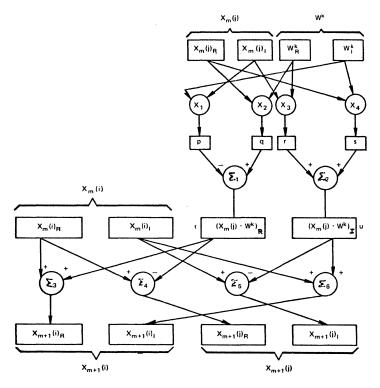

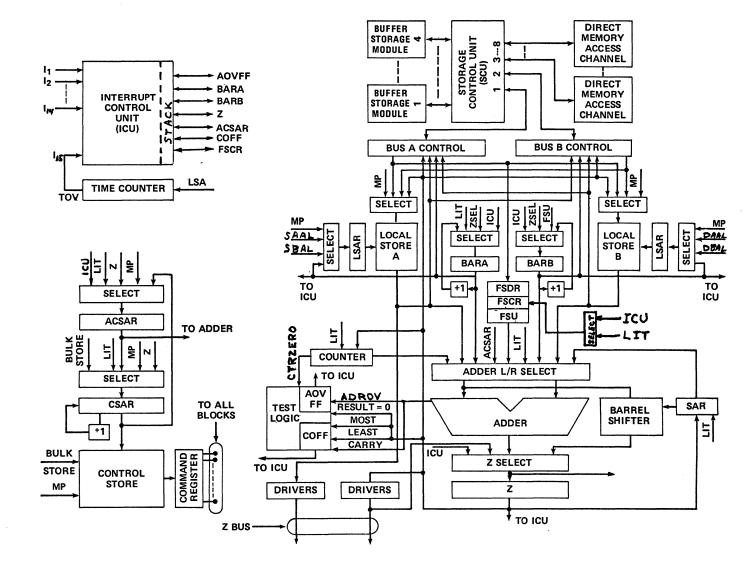

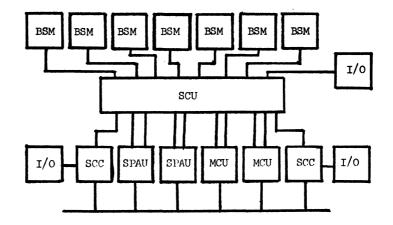

| The Use of Two Levels of Parallelism to Implement an Efficient Programmable<br>Signal Processing Computer |     |

| J. P. Ihnat, T. G. Rauscher, B. P. Shay, H. H. Smith, W. R. Smith                                         | 113 |

| Asynchronous Network of Specific Micro-Processors<br>F. Dromard, G. Noguez                                | 120 |

| SESSION 7: SCHEDULING<br>Chairman: Professor J. L. Baer                                                   |     |

| An Approach to a Restricted Scheduling-Problem for Multiprocessor Systems<br>S. Schindler, H. Ludtke      | 121 |

| A Scheduling Model for Computer Systems with Two Classes of Processors<br>R. E. Buten, V. Y. Shen         | 130 |

| Scheduling in a Multiprocessor Environment<br>J. Gwynn, R. J. Raynor                                      | 139 |

| SESSION 8: RADCAP                                                                                         | 207 |

| Chairman: Mr. J. L. Previte                                                                               |     |

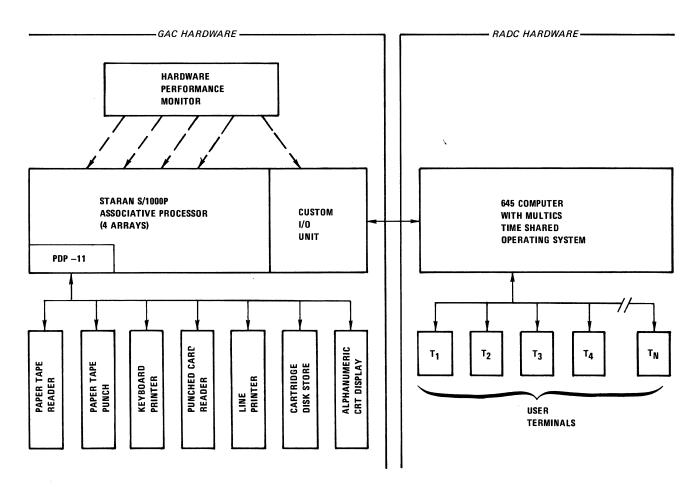

| RADCAP: An Operational Parallel Processing Facility<br>J. D. Feldman, O. A. Reimann                       | 140 |

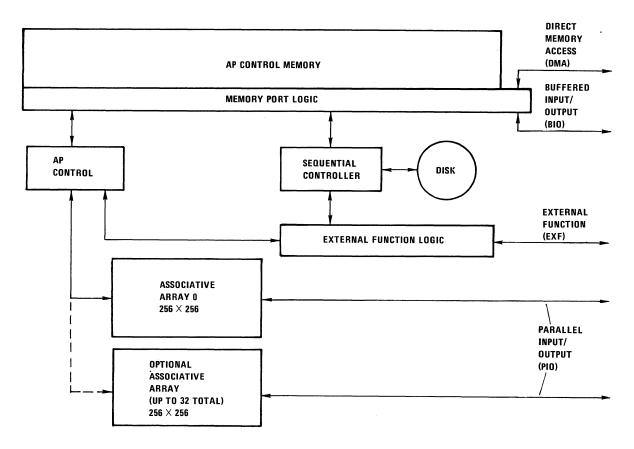

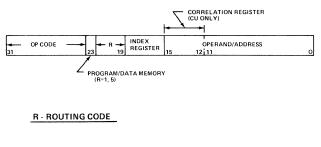

| STARAN/RADCAP Hardware Architecture<br>K. E. Batcher                                                      | 147 |

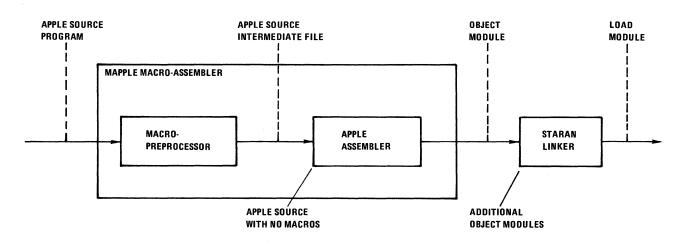

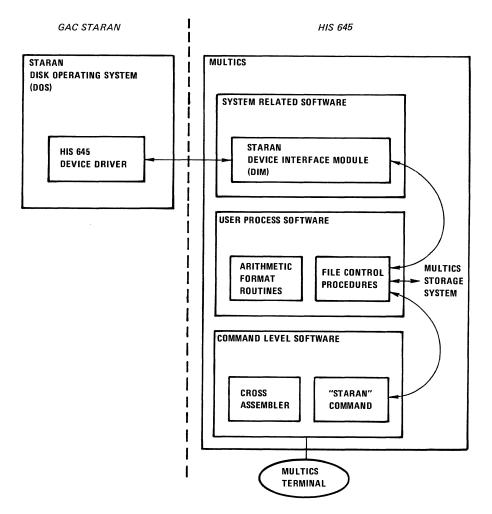

| STARAN/RADCAP System Software<br>E. W. Davis                                                              | 153 |

| Application of STARAN to Support Region Analysis for a Mechnical Robot<br>J. M. Plante, D. J. Gondek      | 160 |

| A Data Management System Utilizing the STARAN Associative Processor<br>R. Moulder                         | 161 |

# TABLE OF CONTENTS (CONT'D.)

| SESSION 9: PEPE<br>Chairman: Mr. J. A. Cornell                                                                                         |     |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

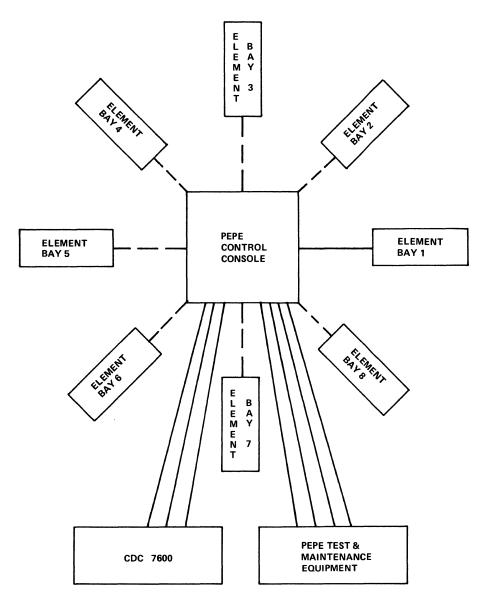

| Introduction to the Architecture of a 288-Element PEPE<br>A. J. Evensen, J. L. Troy                                                    | 162 |

| Operating System and Support Software for PEPE<br>J. R. Dingeldine, H. G. Martin, W. M. Patterson •••••••••••••••••••••••••••••••••••• | 170 |

| Process-Construction for a Parallel-Sequential Computer Architecture<br>A. L. Barrett                                                  | 179 |

| A Comparison of a Parallel and Serial Implementation of a Large Real Time Problem<br>P. T. Alexander, R. O. Parker                     | 180 |

| Computer Simulation of PEPE and its Host at the Instruction Level<br>J. L. Troy                                                        | 187 |

| AUTHOR INDEX                                                                                                                           | 188 |

| REVIEWERS                                                                                                                              | 189 |

| COMMITTEES                                                                                                                             | 190 |

# THE COORDINATE METHOD FOR THE PARALLEL EXECUTION OF DO LOOPS

# Leslie Lamport

Massachusetts Computer Associates Wakefield, Massachusetts 01880

Abstract -- An algorithm is presented which translates a program with nested sequential DO loops into one suitable for execution on a parallel array or vector computer. If necessary, extensive rearrangement of the program's structure is made.

# Introduction

We consider the problem of compiling ordinary sequential programs for execution on a parallel array or vector computer such as the Illiac IV or the CDC Star-100. This problem is of practical importance for the following reasons:

(1) There exist sequential programs which one would like to run on these parallel computers.

(2) If a program is to be run on two different machines, it might be best to write it in sequential form and let each compiler find the most efficient parallel execution for its computer.

(3) A compiler may be able to find more parallelism in a program than the programmer can.(See [1].)

The methods which we introduce should also be useful in other areas of program optimization.

We consider a FORTRAN program containing DO loops, and describe a method of translating it into an extended FORTRAN program in which one or more of the DO loops is executed in parallel. This is an obvious approach, and has been used in [2] - [4]. The method presented here generalizes the coordinate method of [4], and is more general than the analogous methods of [2] and [3]. Al-though our exposition is self-contained, it is best to read [4] first.

We specify parallel execution with a DO SIM statement of the following form: DO 99 SIM FOR ALL I  $\epsilon$  3,

where **8** is a set of integers. The statements in its range are executed one after another as usual. However, each statement is executed simultaneously for all of the indicated values of I. An assignment statement is executed by first computing the right-hand side for each value of I, then simultaneously performing the assignments. Thus, the statement

A(I) = A(I - 1) + B(I)

would simultaneously set A(i) equal to the original value of A(i - 1) plus B(i) , for each value of i in § .

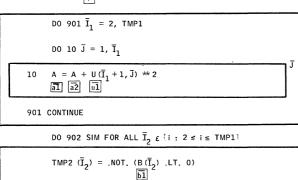

The coordinate method tries to change DO loops to DO SIM loops. We show that it suffices to consider one DO loop at a time. The basic method is the coordinate algorithm, which we illustrate by an example. Suppose we are given the following program.

Program 1:

This is a nonsensical program, but it will serve to illustrate most details of the algorithm. Each occurrence of a non-index variable is given a name, which appears in a box beneath it. Loop bodies are boxed and labeled for legibility. The L loop might have been changed from a DO to a DO SIM loop by a previous application of the algorithm.

The coordinate algorithm can translate Program 1 into the following equivalent program.

TMP1 = P

D0 920  $\overline{K}$  = 2, MAXIMUM ({TMP3(i): 2 ≤ i ≤ TMP1 ,AND, TMP2(i)})

| D0 904 SIM FOR ALL $\overline{I}_4 \in \{i : \overline{K} \leq TMP3(i)$<br>.AND. $2 \leq i \leq TMP1$ .AND. $TMP2(i)$                                                                                                                                                                                                                                                                                |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $TMP4 (\overline{I}_{4}) = U (\overline{I}_{4} + 1, \overline{K})$ $[U]5$ $U (\overline{I}_{4}, \overline{K}) = 2 * U (\overline{I}_{4}, \overline{K} - 1)$ $[U]2$ $B (\overline{I}_{4}) = B (\overline{I}_{4}) + (U (\overline{I}_{4} - 1, \overline{K}) - TMP4 (\overline{I}_{4})) ** 2$ $[U]52$ $TMP5 (\overline{I}_{4}) = \overline{K} * U (\overline{I}_{4}, \overline{K})$ $[U]6$ 904 CONTINUE | Ī4 |

| D0 905 Ī <sub>5</sub> = 2, TMP1                                                                                                                                                                                                                                                                                                                                                                      |    |

| IF (TMP2( $\overline{I}_5$ ) .AND. $\overline{K} \equiv TMP3(\overline{I}_5)$ )<br>C( $\overline{K}$ ) = C( $\overline{K}$ ) + TMP5( $\overline{I}_5$ )<br>$\overline{c1}$ $\overline{c2}$                                                                                                                                                                                                           | Ī  |

| 905 CONTINUE                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 920 CONTINUE                                                                                                                                                                                                                                                                                                                                                                                         |    |

(a) We need only assume that we know which data can be modified by a subroutine or function call, but this would complicate matters.

DO 903 Ī<sub>3</sub> = 2, TMP1

903 CONTINUE

IF (TMP2( $\overline{I}_3$ )) D = D + B( $\overline{I}_3$ )  $d\overline{1}$   $d\overline{2}$   $b\overline{4}$

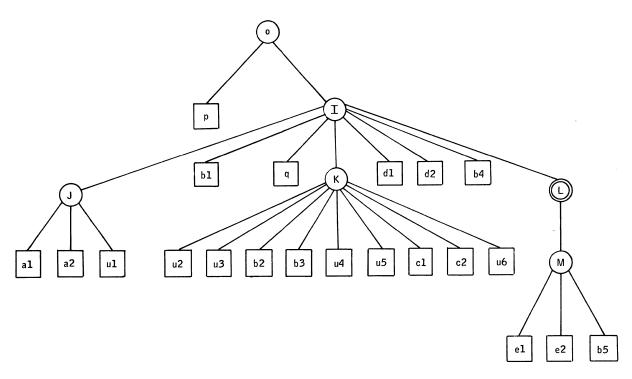

Observe that the I loop of Program 1 has been split into the five  $\overline{I}_1, \ldots, \overline{I}_5$  loops. Two of these are DO SIM loops, so Program 2 has more parallel execution than Program 1. Note the extensive rearrangement of Program 1 needed to achieve this parallelism. The L/M loop has been moved before the K loop; statement 20 has been split into two parts which appear inside different loops; the u5 occurrence has been moved; etc. Of course, this example is contrived to demonstrate the power of the algorithm.

Ī3

In general, we consider an extended FORTRAN program containing DO and DO SIM loops, with the following restrictions.

1. There is no backward transfer of control other than that implied by the DO loops. Thus, if all DO and DO SIM statements were removed, then the resulting program would have no loops. (Techniques for translating programmed loops into DO loops are described in [3].)

2. There is no I/O statement. We assume that input/output is done with the initial/final values of variables.

3. The increment of every DO loop is a constant which is known at compile time.

4. There is no transfer of control from inside the range of a DO or DO SIM loop to outside its range - i.e., no premature exits from loops.

5. There is no subroutine call, and no function call which can change the value of a variable. The value of a function must depend (-)

only on the values of its arguments.<sup>(a)</sup> The program which we consider here may be any portion of an actual FORTRAN program having a single entry point. In particular, it may consist of a single DO loop. Hence, these re-

strictions are reasonable. Space limitations require that we eliminate many details, including the proofs of theorems.

# Representation of the Program

For our analysis, we need a way of representing a program which is more convenient than the original FORTRAN representation. To simplify the exposition, we assume that all DO loop increments equal 1. The generalization to arbitrary increments is described later.

# The Program Tree

They will appear in [5].

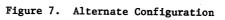

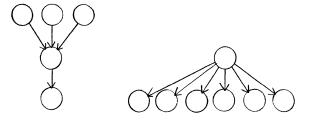

The first part of our representation is the program tree, which describes a program's nested loop structure. The terminal nodes of the tree represent occurrences of variables. (Occurrences of DO and DO SIM index variables are excluded.) The non-terminal nodes represent the DO and DO

SIM loop bodies. A dummy node, labeled o, is placed at the top of the tree.

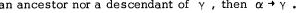

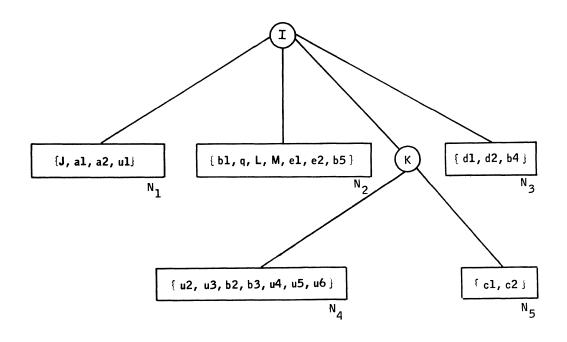

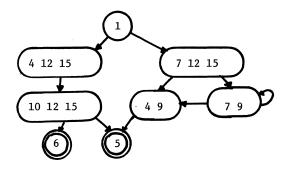

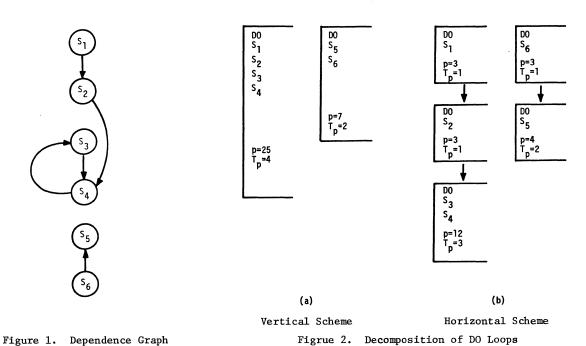

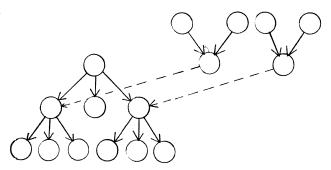

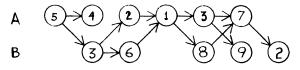

The program trees of Programs 1 and 2 are shown in Figures 1 and 2, respectively. (For Program 2, we have excluded occurrences of TMP1, ..., TMP5 from the tree.) Occurrence nodes are denoted by boxes. Loop nodes are denoted by circles and labeled by the index variable name. (We assume that each loop has a unique index variable.) DO SIM nodes are distinguished by concentric circles.

We use paternity relations to describe tree structure. In Figure 1, the J node is the <u>father</u> of the ul node and the <u>son</u> of the I node. The o node is an ancestor of all other nodes.

We let  $\underline{\mathcal{N}(3)}$  denote the set of all nodes of a tree 3, and  $\underline{\mathcal{O}(3)}$  denote the set of all terminal nodes. If  $\alpha$  is any node of a tree, then  $\underline{\mathfrak{I}}(\alpha)$  denotes the subtree headed by  $\alpha$ . We let  $\underline{\mathfrak{N}}(\alpha)$  and  $\underline{\mathfrak{O}}(\alpha)$  denote  $\mathfrak{N}[\mathfrak{I}(\alpha)]$  and  $\mathfrak{O}[\mathfrak{I}(\alpha)]$ , respectively. In Figure 2,  $\mathcal{O}(\overline{I}_2) = \{\overline{b1}, \overline{q}, \overline{e1}, \overline{e2}, \overline{b5}\}.$ A non-empty sequence of nodes  $\alpha_1, \ldots, \alpha_n$  is called a <u>branch</u> of a tree if o is

the father of  $\alpha_1$ , and each  $\alpha_k$  is the father of  $\alpha_{k+1}$  . Three branches of Figure 1 are: (1) I, K; (2) I, J, a2; and (3) p.

If  $\alpha$  and  $\beta$  are two nodes of a tree, we let  $\alpha \cap \beta$  denote their most recent common ancestor. In Figure 1, we have  $a1 \cap a2 = J$ , u3  $\cap$  J = I and p  $\cap$  q = o. We define  $\alpha \cap \alpha$ to be the father of lpha .

Let f and g be occurrences in a program. We say that f precedes g if there is a flow path from f to g in which each DO loop is executed at most once. In Program 1, u3 precedes u2, u5, e2, etc. By restriction 1, if f precedes g then g cannot precede f.

The motive for the following definition comes from considering  $f \rightarrow g$  to mean that the occurrence f must precede the occurrence g.

Then  $\hat{\rightarrow}$  contains precedence relations on the loop nodes implied by  $\rightarrow$ .

<u>Definition 1</u>: Let 3 be a tree and let → be any relation on  $\mathcal{O}(\mathfrak{I})$  . The tree completion of  $\rightarrow$  is the smallest relation  $\stackrel{*}{\rightarrow}$  on  $\mathcal{N}(\mathfrak{I})$  which satisfies the following conditions:

(1) If  $f \rightarrow g$  then  $f \stackrel{*}{\rightarrow} g$ .

(2) If  $\alpha \stackrel{*}{\rightarrow} \beta$ ,  $\beta \stackrel{*}{\rightarrow} \gamma$  and  $\alpha$  is neither an ancestor nor a descendant of  $\gamma$ , then  $\alpha \stackrel{*}{\rightarrow} \gamma$ .

1973 SAGAMORE COMPUTER CONFERENCE ON PARALLEL PROCESSING

(3) If  $\alpha \stackrel{*}{\rightarrow} \beta$ ,  $\alpha \neq \beta$ ,  $\alpha'$  is either the father of  $\alpha$  or else  $\alpha' = \alpha$ ,  $\beta'$  is either the father of  $\beta$  or else  $\beta' = \beta$ , and  $\alpha' \neq \beta'$ ; <u>then</u>  $\alpha' \stackrel{*}{\rightarrow} \beta'$ . The relation  $\rightarrow$  is said to be <u>tree incon-</u> <u>sistent</u> if  $\alpha \stackrel{*}{\rightarrow} \alpha$  for some node  $\alpha$ . Otherwise,  $\rightarrow$  is said to be <u>tree consistent</u>.

A <u>partition</u> of a set is a collection of pairwise disjoint subsets whose union equals the whole set. Let  $P = \{S_1, \ldots, S_n\}$  be a partition of a set S, and let  $\rightarrow$  be a relation on S. The relation  $\overline{\rightarrow}$  <u>induced</u> on P by  $\rightarrow$  is defined by  $S_i \xrightarrow{+} S_j$  if and only if  $S_i \neq S_j$  and there exist  $s \in S_i$  and  $t \in S_j$  such that  $s \rightarrow t$ . A <u>tree partition</u> P of a tree J is a partition  $\{N_1, \ldots, N_r\}$  of  $\mathcal{N}(J)$  satisfying the

following property: If  $\boldsymbol{\alpha} \in N_i$ ,  $\beta$  and  $\gamma \in N_j$ ,  $N_i \neq N_j$  and  $\alpha$  is the father of  $\beta$ , then the father of  $\gamma$  is contained in either  $N_i$  or  $N_j$ . We give  $\boldsymbol{\rho}$  a tree structure by letting the father/son relation be the one induced on  $\boldsymbol{\rho}$  by the father/son relation of  $\Im$ .

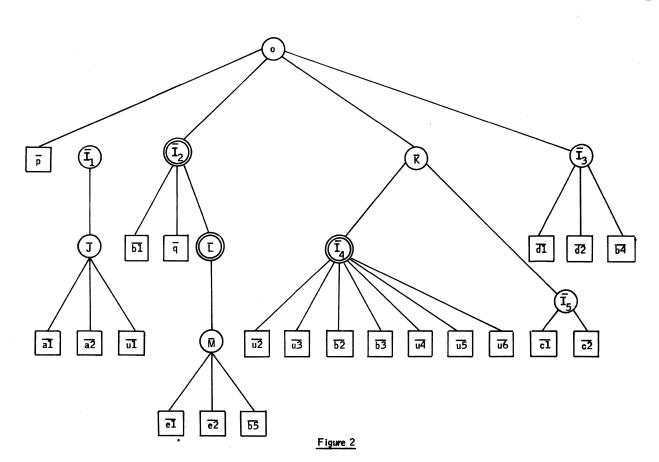

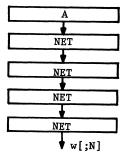

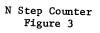

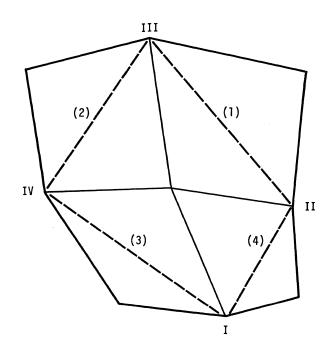

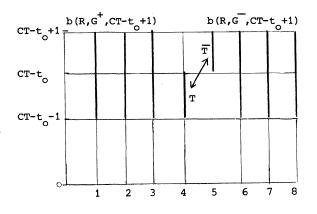

As an example, let 3 be the subtree  $\Im(\overline{I_2})$  of Figure 2. Then  $\{\overline{b1}\}, \{\overline{I_2}, \overline{q}, \overline{L}\}, \{\overline{M}, \overline{e1}, \overline{b5}\}, \{\overline{e2}\}$  is a tree partition of 3. Its tree structure is shown in Figure 3.

# Index Sets

Let  $\mathbb{Z}^n$  denote the set of all n-tuples of integers, with the usual operations of addition and subtraction, and let  $\vec{0} = (0, 0, ..., 0)$ . We define  $\mathbb{Z}^0 = \{0\}$ .

Let  $\alpha$  be a loop node of a program tree, and let  $I^1, \ldots, I^n$  be the branch with  $I^n = \alpha$ . Then  $|\alpha|$  is defined to equal n. We define  $\mathbb{Z}$  to be the set  $\mathbb{Z}[\alpha]$

$\mathbb{Z}_{\alpha}$  to be the set  $\mathbb{Z}^{|\alpha|}$ . The relations  $\sim$  and  $\prec$  on  $\mathbb{Z}_{\alpha}$  are defined as follows. Let  $I^{1}, \ldots, I^{k}$  be the DO

nodes among the  $I^{j}$  (the remaining  $I^{j}$  being DO SIM nodes), with  $j_{1} < \ldots < j_{k}$ . For any ele-

ments  $(a^1, \ldots, a^n)$  and  $(b^1, \ldots, b^n)$  of  $\mathbb{Z}_{\alpha}$ , we let

(1)

$$(a^{1}, ..., a^{n}) \sim (b^{1}, ..., b^{n})$$

if

$(a^{1}, ..., a^{k}) = (b^{1}, ..., b^{k})$ .

(2)  $(a^{1}, ..., a^{n}) \prec (b^{1}, ..., b^{n})$  if

$(a^{j_1}, \ldots, a^{j_k})$  is lexicographically smaller than  $(b^{j_1}, \ldots, b^{j_k})$ , reading the components from left to right.

In Figure 1, we have

$$|M| = 3$$

,  $\mathbb{Z}_{M} = \mathbb{Z}^{3}$ ,

and  $(3, 7, 2) \sim (3, 10, 2) \prec (3, -1, 4)$ .

The element

$$A = (a^1, \ldots, a^{11})$$

of  $\mathbb{Z}_{\alpha}$  re-

presents a possible execution of the body of the  $\alpha$  loop for  $I^1 = a^1, \ldots, I^n = a^n$ . For any element B of  $\mathbb{Z}_{\alpha}$ , A ~ B if the executions of the  $\alpha$  loop body for A and B occur simultaneously, and A < B if the execution for A precedes the execution for B. Note that this defines the meaning of a DO loop inside a DO SIM loop. (It is not the meaning one might expect if the lower DO limit depends upon the DO SIM index variable.

We define |o| = 0, and let the relation  $\sim$  on  $\mathbb{Z}_{o} = \{0\}$  be defined by  $0 \sim 0$ . If f is an occurrence node whose father is  $\alpha$ , then we let  $|f| = |\alpha|$  and  $\mathbb{Z}_{f} = \mathbb{Z}_{\alpha}$ . An element of  $\mathbb{Z}_{f}$  represents a possible execution of the occurrence f.

Now let the I<sup>j</sup> be as above and let  $\beta = I^k$ ,  $k \leq n$ . We define the projection mapping  $\Pi^{\boldsymbol{\alpha}}_{\boldsymbol{\beta}} : \mathbb{Z}_{\boldsymbol{\alpha}} \to \mathbb{Z}_{\boldsymbol{\beta}}$  by  $\Pi^{\boldsymbol{\alpha}}_{\boldsymbol{\beta}}(a^1, \ldots, a^n) = (a^1, \ldots, a^k)$ . If an occurrence node f is the son of  $\boldsymbol{\alpha}$ , then we let  $\Pi^f_{\boldsymbol{\beta}} = \Pi^{\boldsymbol{\alpha}}_{\boldsymbol{\beta}}$ . In Figure 1,  $\Pi^{e1}_{I} : \mathbb{Z}^3 \to \mathbb{Z}^1$  is defined by  $\Pi^{e1}_{I}(i, \ell, m) = (i)$ .

The reader can verify the following fact.

$\begin{array}{l} \frac{Proposition\;2}{P\;\epsilon\;\;\mathbb{Z}_f\;\;\mathrm{and}\;\;Q\;\;\epsilon\;\;\mathbb{Z}_g\;\;.} \mbox{ The execution of $f$ for $P$ precedes the execution of $g$ for $Q$ if either $(i)\;\;\Pi^f_{f\cap g}(P)\;<\;\Pi^g_{f\cap g}(Q)$, or $(ii)\;\;\Pi^f_{f\cap g}(P)\;<\;\Pi^g_{f\cap g}(Q)$ and $f$ precedes $g$.} \end{array}$

For any node  $\alpha$ , we define the <u>index set</u>  $\mathscr{I}_{\alpha}$  to be the subset of  $\mathbb{Z}_{\alpha}$  consisting of those elements for which  $\alpha$  is actually executed. In Program 1, we have:

$$\begin{split} \vartheta_{a1} &= \vartheta_{J} = \{(i,j): 2 \leq i \leq P \text{ and } \\ & 1 \leq j \leq i \} \\ \vartheta_{q} &= \{(i): 2 \leq i \leq P \text{ and } B(i) \geq 0 \} \\ \vartheta_{u2} &= \vartheta_{K} = \{(i,k): 2 \leq i \leq P, 2 \leq k \leq Q(i) \\ & \text{ and } B(i) \geq 0 \} \end{split}$$

Note that in general,  $\Im_{\alpha}$  may depend upon the initial values of variables, and often will not be known at compile time.

# Occurrences

An occurrence of a variable is called a <u>generation</u> if it appears on the left-hand side of an assignment statement, otherwise it is called a <u>use</u>. A <u>relevant occurrence pair</u> is an ordered pair of occurrences of a single variable, at least one of which is a generation. In Program 1, there are three relevant pairs of occurrences of the variable E: (1) e1, e2; (2) e2, e1; and (3) e1, e1.

Execution of the occurrence b5 of Program 1 for an element (i,  $\ell$ , m) in  $\mathscr{I}_{b5}$  references the (i+1) element of the array B. This defines the <u>occurrence mapping</u>  $T_{b5}:\mathscr{I}_{b5} \to \mathbb{Z}^1$  given by  $T_{b5}(i, \ell, m) = (i+1)$ . In general, let f be an occurrence of a k-dimensional array variable. (A scalar is considered to be a 0-dimensional array.) Then  $T_f:\mathscr{I}_f \to \mathbb{Z}^k$ . The mapping  $T_f$  may not be known at compile time.

We define  $\langle f, g \rangle$  to be some fixed subset of  $\mathbb{Z}_{f \cap g}$ , known at compile time, which contains  $\langle f, g \rangle >$ .

An element X of << f, g >> implies the existence of elements  $P \in \vartheta_f$  and  $Q \in \vartheta_g$  such that the executions of f for P and g for Q reference the same array element. Since A < B if  $B - A > \vec{0}$ , Proposition 2 implies that the reference by f precedes the reference by g if either (i)  $X > \vec{0}$  or (ii)  $X \sim \vec{0}$  and f precedes  $\vec{a}$

$$\begin{array}{l} X > 0 \quad \text{or (ii)} \ X \sim 0 \quad \text{and } f \text{ precedes } g \text{.} \\ \text{Some } << f, g >> \text{ sets for Program 1 are:} \\ << e1, e2 >> = \{(1, -1, 3)\} \\ << u1, u2 >> = \{(1)\} \quad \text{if } \mathcal{S}_K \neq \emptyset \ (c) \\ << b2, b3 >> = \{(0, k): 2-Q(i) \leq k \leq \\ Q(i) - 2 \text{ for some } i \in \mathcal{S}_V \} \ . \end{array}$$

The set  $\langle f, g \rangle$  is the best "upper bound" on the set  $\langle f, g \rangle$  which the compiler can find. Computing these sets is a major implementation problem which we will not discuss. We assume that the compiler finds the following  $\langle f, g \rangle$  sets for Program 1.

(b) If f appears in a DO SIM set expression, then  $T_f$  could be a multi-valued mapping. To handle this case, replace any statement in this paper of the form "...  $T_f(P)$  ..." by "there exists an X  $\epsilon$   $T_f(P)$  such that ... X ...".

(c) We let 🖋 denote the empty set.

# Precedence Relations

The FORTRAN representation of a program usually specifies more precedence relations among the occurrences than are necessary. For example, b2 need not precede cl in Program 1. We now describe all the precedence relations that are necessary in order to specify the correct execution of a program. These are of two types. The first, denoted by  $\Rightarrow$ , describes those precedence relations which are logically necessary for a meaningful execution of the program.

Definition 4: For occurrences f and g in a FORTRAN program, we write  $f \Rightarrow g$  in any of the following cases:

> 1. (a) g is a generation and f appears on the right-hand side of the assignment statement of g.

> (b) f appears in a subscript expression of g.

2. (a) f appears in the conditional expression of a conditional branch, and g appears in a statement whose execution is conditional upon which branch is taken.

(b) f appears in the limits of a DO statement, or in the index set expression of a DO SIM statement, whose range contains q.

In 2(a), we consider a conditional assignment statement to consist of a conditional branch and an assignment statement.

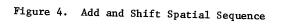

The relations ⇒ for Program 1 are indicated in Figure 4. E.g., the  $\Rightarrow$  in the a2 row, al column denotes the relation  $a^2 \Rightarrow a^2$ .

The second form of precedence relation, denoted by  $\rightarrow$ , is necessitated by data conflicts. If a generation and any other occurrence reference the same array element, then the order of the references must be specified. Our previous remarks then lead to the following definition.

Definition 5: For each relevant pair of occurrences f, g with  $f \neq g$ , we let  $f \rightarrow g$  if and only if f

precedes g and there exists an element  $X \epsilon < f, q > \text{ with } X \sim \vec{0}$ .

The relations → for Program 1 are shown in Figure 4.

We let  $\implies$  denote the union of the relations  $\rightarrow$  and  $\Rightarrow$ , so  $f \Rightarrow g$  if  $f \rightarrow g$  or  $f \Rightarrow g$ . Then ⇒ gives all precedence relations necessary for the proper execution of the program. It can be used to determine, for example, that during an iteration of the I loop of Program 1, the J and K loops can be executed concurrently by two independent processors. This yields a generalization of the methods of [6]. However, this type of parallelism will not be discussed here.

# The Complete Representation

We define a program specification & to consist of the following:

> S1. A program tree, also denoted by 8. S2. The precedence relations  $\rightarrow$  and  $\Rightarrow$ . S3. A specification of the occurrence mapping for each occurrence. S4. A specification of the index set of each occurrence and of the assignment values for each generation, in terms of occurrences.

Part S4 is quite vague. For Program 1, it might include the following:  $\beta_q = \{(i) : 2 \le i \le p \text{ and } bl \ge 0\}$  al = a2 + ul\*\*2.

S3 is also vague if we consider occurrences like A(B(I), J). We will not need to define S3 and S4 any more precisely because our translation procedure will leave these parts of the specification essentially unchanged.

There are many criteria which must be met for S1-S4 to be a valid program specification. However, if S3 and S4 are assumed to be valid. then the following conditions are sufficient to insure that the entire specification is valid.

<u>L1</u>. (a) For each relevant pair of occurrences f, g with  $f \neq g$ : if there exists an  $X \in \langle \langle f, g \rangle \rangle$  with  $X \sim 0$ , then either  $f \rightarrow g$  or g→f.

(b) For each generation g: if X

$\epsilon \ll q, q \gg$  and  $X \sim \vec{0}$ , then  $X = \vec{0}$ .

<u>L2</u>. The relation  $\implies$  is tree consistent.

Note that to verify L1, it suffices to verify it with each set << f, g >> replaced by

< f, g > . Given a valid program specification, we can use it to write an extended FORTRAN program. For example, we define a program specification as follows:

S1. The program tree is given by Figure 2.

S2. We let  $\overline{f} \rightarrow \text{ or } \Rightarrow \overline{q}$  if the relation

$f \rightarrow or \implies g$  appears in Figure 4. We also add the following relations:  $\overline{u1} \rightarrow \overline{u2}, \ \overline{u2} \rightarrow \overline{u4},$  $\overline{u5} \rightarrow \overline{u2}$ , and  $\overline{b5} \rightarrow \overline{b2}$ .

|           | р | al  | a2 | ul | <b>b</b> 1 | q  | u2 | u3 | b2      | b3 | u4 | u5 | cl  | c2  | u6 | dl | d2 | b4       | el       | e2 | b5 | I | J | K | L | м |    |

|-----------|---|-----|----|----|------------|----|----|----|---------|----|----|----|-----|-----|----|----|----|----------|----------|----|----|---|---|---|---|---|----|

| р         |   | Ĵ   | Î  | Î  | ĥ          | -> | ⇒  | ⇒  | Þ       | ĥ  | Ų  | ⇒  | ĥ   | ĥ   | ĥ  | ⇒  | î  | ⇒        | ⇒        | ⇒  | ⇒  |   |   |   |   |   | р  |

| al        |   | >   | >  |    |            |    |    |    |         |    |    |    |     |     |    |    |    |          |          |    |    |   |   |   |   |   | al |

| a2        |   | ¶+¦ | *  |    |            |    |    |    |         |    |    |    |     |     |    |    |    |          |          |    |    |   |   |   |   |   | a2 |

| ul        |   | ĥ   | *  |    |            |    | >  |    |         |    | *  |    | *   | *   | *  |    |    |          |          |    |    |   |   | * |   |   | ul |

| bl        |   |     |    |    |            | ⇒  |    | -> | ∩<br> + | -  | ĥ  | -> | ⇒   | =>  | ⇒  | ⇒  | ⇒  | <b>⇒</b> |          |    |    |   |   | * |   |   | b1 |

| q         |   |     |    |    |            |    | ⇒  | ⇒  | ⇒       | ĥ  | Ŷ  | ⇒  | ⇒   | ⇒   | ⇒  | *  | *  | *        |          |    |    |   |   | * |   |   | q  |

| u2        |   |     |    |    |            |    |    |    |         |    | >  |    | *   | *   | -+ |    |    |          |          |    |    |   |   |   |   |   | u2 |

| u3        |   |     |    |    |            |    | ÷  |    | *       |    | *  |    | *   | *   | *  | *  | *  | *        |          |    |    |   |   |   |   |   | u3 |

| b2        |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    | *  | *  | -        |          |    |    |   |   |   |   |   | b2 |

| b3        |   |     |    |    |            |    |    |    | ⇒<br>+  |    |    |    |     |     |    | *  | *  | *        |          |    |    |   |   |   |   |   | b3 |

| u4        |   |     |    |    |            |    |    |    | ⇒       |    |    |    |     |     |    | *  | *  | *        |          |    |    |   |   |   |   |   | u4 |

| <u>u5</u> |   |     |    |    |            |    | >  |    | ⇒       |    | *  |    | *   | *   | *  | *  | *  | *        |          |    |    |   |   |   |   |   | u5 |

| cl        |   |     |    |    |            |    |    |    |         |    |    |    | >   | - 4 |    |    |    |          |          |    |    |   |   |   |   |   | cl |

| c2        |   |     |    |    |            |    |    |    |         |    |    |    | ¶~↑ | *   |    |    |    |          |          |    |    |   |   |   |   |   | c2 |

| u6        |   |     |    |    |            |    |    |    |         |    |    |    | ĥ   | *   |    |    |    |          |          |    |    |   |   |   |   |   | u6 |

| dl        |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    | >  | >  |          |          |    |    |   |   |   |   |   | dl |

| d2        |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    |    | *  |          |          |    |    |   |   |   |   |   | d2 |

| b4        |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    | ⇒  | *  |          |          |    |    |   |   |   |   |   | b4 |

| el        |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    |    |    |          |          |    |    |   |   |   |   |   | el |

| e2        |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    |    |    |          | ⇒        |    |    |   |   |   |   |   | e2 |

| b5        |   |     |    |    |            |    |    |    | >       |    |    |    |     |     |    | *  | *  | *        | <b>⇒</b> |    |    |   |   | * | · |   | b5 |

| 1         |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    |    |    |          |          |    |    |   |   |   |   |   | 1  |

| J         |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    |    |    |          |          |    |    |   |   | * |   |   | J. |

| К         |   |     |    |    |            |    |    |    |         |    |    |    |     |     |    | *  | *  | *        |          |    |    |   | 1 |   |   |   | к  |

| L         |   |     |    |    |            |    |    |    | *       |    |    |    |     |     |    | *  | *  | *        |          |    |    |   |   | * |   |   | L  |

| М         |   |     |    |    |            |    |    |    | *       |    |    |    |     |     |    | *  | *  | *        |          |    |    |   |   | * |   |   | м  |

|           | p | al  | a2 | ul | <b>b1</b>  | q  | u2 | u3 | b2      | b3 | u4 | u5 | cl  | c2  | u6 | d1 | d2 | b4       | el       | e2 | b5 | 1 | J | к | L | м |    |

Figure 4

S3, S4. We obtain this from the specification of Program 1 in the obvious way. E.g., we have

$$\overline{a1} = \overline{a2} + \overline{u1} * 2$$

$T_{\overline{u3}}(k, i) = T_{\overline{u3}}(i, k) = (i, k-1)$ .

The reader can check that this specification satisfies L1 and L2. A simple-minded translation of this specification into an extended FORTRAN program gives Program 2. (A more efficient translation is possible.)

As this example shows, the problem of going from a valid program specification to a FORTRAN program can be difficult. However, it is always possible. A compiler would probably not do this, but would translate the program specification into an internal form suitable for generating code.

# **Program Mappings**

## Linear Program Mappings

Our basic idea is to transform a given pro gram specification  $\mathfrak{s}$  into a new one  $\overline{\mathfrak{s}}$  which produces the same results, but has more parallel computation. The tree of  $\overline{\mathfrak{s}}$  will be obtained by splitting apart and rearranging loop nodes of  $\mathfrak{s}$ . In the following definition,  $\theta^{-1}(\alpha)$  is the set of nodes into which the loop node  $\alpha \in \eta(\mathfrak{s})$  is split.

<u>Definition 6</u>: Let **S** and  $\overline{\mathbf{S}}$  be program trees. A linear tree mapping  $\Omega : \mathbf{S} \rightarrow \overline{\mathbf{S}}$  consists of:

(1) A surjective mapping

$$\theta : \eta(\overline{\mathbf{s}}) \to \eta(\mathbf{s})$$

such that:

(a)  $\theta$  is a 1-1 correspondence between  $\mathcal{O}(\overline{\mathbf{S}})$  and  $\mathcal{O}(\underline{\mathbf{S}})$ .

(b) If  $\overline{\alpha}$  is an ancestor of an occurrence node  $\overline{f}$  of  $\overline{s}$ , then  $\theta(\overline{\alpha})$  is an ancestor of  $\theta(\overline{f})$ .

(c) For each

$$\overline{\mathbf{f}} \in \mathcal{O}(\overline{\mathbf{S}}) : |\theta(\overline{\mathbf{f}})| = |\overline{\mathbf{f}}|$$

.

We denote  $\theta(\overline{f})$  by f for each  $\overline{f} \in \mathcal{O}(\overline{s})$ .

(2) For each  $f \in \mathcal{O}(S)$ , a linear 1-1 correspondence  $\Omega_f : \mathbb{Z}_f \to \mathbb{Z}_{\overline{f}}$  satisfying the following condition: For any  $f, g \in \mathcal{O}(S)$ , the mapping  $\Omega_{< f,g >} : \mathbb{Z}_{f \cap g} \to \mathbb{Z}_{\overline{f \cap g}}^{-}$  defined by

$$\Omega_{< f, g >} = \prod_{\overline{f} \cap \overline{g}}^{\overline{f}} \circ \Omega_{f} \circ \left( \prod_{f \cap g}^{f} \right)^{-1}$$

is single-valued, and  $\Omega_{<\rm f,\ g>}$  =  $\Omega_{<\rm g,\ f>}$ .

As an example, let  $\mathfrak{S}$ ,  $\overline{\mathfrak{S}}$  be the trees of Figures 1 and 2, respectively. We define the linear tree mapping  $\Omega: \mathfrak{S} \to \overline{\mathfrak{S}}$  as follows. Let  $\theta(\overline{I}_1) = \ldots = \theta(\overline{I}_5) = I$ ,  $\theta(\overline{J}) = J$ ,  $\theta(\overline{\mathfrak{a}1}) = \mathfrak{a}1$ , etc. Let  $\Omega_f$  be the identity mapping unless f is a descendant of K, in which case let  $\Omega_f(\mathbf{i}, \mathbf{k}) = (\mathbf{k}, \mathbf{i})$ . We then have  $\begin{aligned} &\Omega_{< u2, u3>}(i, k) = (k, i) \\ &\Omega_{< u2, c1>}(i, k) = (k) \\ &\Omega_{< a1, c1>}(i) = 0 \end{aligned} .$

<u>Definition 7</u>: Let \$,  $\overline{\$}$  be program specifications.

A linear program mapping  $\Omega: \$ \rightarrow \overline{\$}$  consists of a linear tree mapping  $\Omega$  from the tree of \$ to that of  $\overline{\$}$  such that:

(1) For each  $f \in \mathcal{O}(\mathbb{S})$ , f and  $\overline{f}$  are occurrences of the same variable, and  $T_f = T_{\overline{f}} \circ \Omega_f$ .

(2)  $f \Rightarrow g$  in S if and only if  $\overline{f} \Rightarrow \overline{g}$  in S.

(3) Replacing each occurrence f by  $\overline{f}$

in S4 of the specification § gives S4 of  $\overline{\textbf{s}}$  .

Part 3 of the definition is as vague as our definition of S4 of the program specification. However, its meaning should be clear from our example. The mapping  $\Omega$  defined above gives a linear program mapping from the specification of Program 1 to that of Program 2.

We say that two program specifications are <u>equivalent</u> if they produce the same output when run with the same legal input values. (Re-

call restriction 2.) Let  $\Omega: \mathbb{S} \to \overline{\mathbf{S}}$  be a linear program mapping. To obtain the equivalence of  $\mathbb{S}$  and  $\overline{\mathbb{S}}$ , we will assume that  $\Omega$  satisfies the following condition.

<u>EL</u>. For each relevant pair of occurrences f, g in  $\Re$ : <u>if</u> there exists an element  $X \in \{f, g\}$ such that either (i)  $X > \vec{0}$  or (ii)  $X \sim \vec{0}$  and  $f \rightarrow g$ , <u>then</u> either (i)  $\Omega < f$ ,  $g > (X) > \vec{0}$  or (ii)  $\Omega < f$ ,  $g > (X) \sim \vec{0}$  and  $\overline{f} \rightarrow \overline{g}$ .

<u>Theorem 8:</u> Let <sup>§</sup> be a valid program specification, let  $\overline{S}$  be a specification satisfying L2, and let  $\Omega: \overline{S} \to \overline{S}$  be a linear program mapping satisfying EL. Then

(1)  $\overline{\mathbf{g}}$  is a valid program specification.

(2) § and  $\overline{\$}$  are equivalent.

(3) For each relevant occurrence pair f,

g of § : <<  $\overline{f}$ ,  $\overline{g}$  >> =  $\Omega_{< f}$ , g > ( << f, g >>).

Part 3 of the theorem allows us to choose

$< \overline{f}, \overline{g} >$  to be  $\Omega_{< f, g >} (< f, g >)$ . The reader can check that Theorem 8 implies the equivalence of Programs 1 and 2.

# **Two Applications**

We now describe two simple ways of ob-

taining a new program specification  $\overline{S}$  from a given specification S. We leave it to the reader to verify that Theorem 8 implies the equivalence of

\$ and \$.

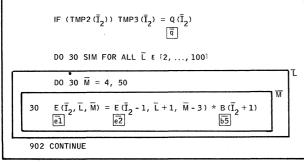

1. Interchange a tightly nested DO/DO SIM pair of nodes. E.g., let § be the specifica-

tion of the L loop of Program 1. Then  $\overline{S}$  is the specification of the program:

DO 30 M = 4, 50

DO 30 SIM FOR ALL L € {2, ..., 100} 30 E(I, L, M) = E(I-1, L+1, M-3) \* B(I + 1).

2. Split a single DO SIM node into several - one for each son. Applying this to the above specification  $\overline{\overline{s}}$  then gives the specification  $\overline{\overline{s}}$

- of the following program: DO 33 M = 4, 50

- DO 31 SIM FOR ALL  $L_1 \in \{2, ..., 100\}$  $\text{TMPl}(L_1) = E(I-1, L_1+1, M-3)$

DO 32 SIM FOR ALL  $L_2 \in \{2, ..., 100\}$

32  $\text{TMP2}(L_2) = B(I+1)$ DO 33 SIM FOR ALL  $L_3 \in \{2, ..., 100\}$

33

$$E(I, L_2, M) = TMP1(L_2) * TMP2(L_2)$$

.

Note that this new version describes one way that the L loop of Program 1 might actually be executed by an array computer, TMP1 and TMP2 representing arithmetic registers.

In general, repeated application of these two rewriting procedures shows that DO SIM loops can always be rewritten in terms of vector assignment statements.

# Coordinate Mappings

31

The mapping  $\Omega_{f}$  for a linear program map-

ping  $\Omega$  may be any linear 1-1 correspondence. This allows a generalization of the hyperplane method of [4], which will be done in a later paper. For the coordinate method, we restrict  $\Omega_f$  to be a permutation of the coordinates.

To form the tree of  $\overline{s}$  , we allow a DO node to be changed into one or more DO and/or DO SIM nodes, which may be moved lower in the tree. DO SIM nodes may not be changed, and no other rearrangement of nodes is allowed.

#### Definition 9: A linear program mapping

$\begin{array}{l} \Omega: \$ \to \overline{\$} \hspace{0.1 in} \text{is a } \underline{\text{coordinate mapping if there is a subset } C \hspace{0.1 in} \text{of the } DO \hspace{0.1 in} \text{nodes of } \$ \hspace{0.1 in}, \hspace{0.1 in} \text{called the set of} \end{array}$ changed nodes, satisfying the following conditions (where  $\theta$  is as in Definition 6):

(1) For each f  $\epsilon$  O(S) , let  $\overline{I}^1$  , ...,  $\overline{I}^n$  ,  $\overline{f}$

be a branch of  $\overline{s}$ , let  $I^j = \theta(\overline{I}^j)$ , and let  $\pi$  be the permutation such that  $I^{\pi(1)}$ , ...,  $I^{\pi(n)}$ , f is a

branch of § . Then

(a) If

$$j < k$$

and  $\pi(j) > \pi(k)$ , then

$I^{\pi(j)} \in \mathbb{C}$  and  $I^{\pi(k)} \notin \mathbb{C}$ .

(b)  $\Omega_f(x^{\pi(1)}, \ldots, x^{\pi(n)}) = (x^1, \ldots, x^n)$ .

(2) For each loop node  $\alpha$  of \$ with

$\alpha \not\in \mathbb{C}$ :  $\theta^{-1}(\alpha)$  consists of a single node of the same type (DO or DO SIM) as  $\alpha$ .

The mapping  $\Omega$  defined above from the specification of Program 1 to that of Program 2 is a coordinate mapping with  $C = \{I\}$ . Thus, only the I node of Program 1 is changed by  $\Omega$  .

For a coordinate mapping  $\Omega: \mathbf{S} \rightarrow \mathbf{\overline{S}}$ , we introduce the following condition.

(2) For each  $X \in \langle f, g \rangle$  with  $X \geq \vec{0}$ ,

either

(a)

$$\Omega_{< f, g>}(X) > \vec{0}$$

, or

(b)  $\Omega_{< f, g>}(X) \sim \vec{0}$  and  $\vec{f} \neq \vec{g}$ .

The reader can verify that if a coordinate mapping satisfies EC, then it satisfies EL. Theorem 8 then gives the following result.

Theorem 10: Let S be a valid program specification and  $\Omega: \mathfrak{F} \to \overline{\mathfrak{F}}$  a coordinate mapping satisfying EC. If  $\overline{\$}$  satisfies L2, then it is a valid program specification and is equivalent to \$ . For any relevant occurrence pair  $\overline{f}, \overline{g}$  of  $\overline{\$}$ , we can let  $<\overline{f}, \overline{g}>$  equal  $\Omega_{<f,g>}(<f,g>)$ .

The following result shows that any coordinate mapping can be obtained from a sequence of coordinate mappings, each of which changes just one node.

Theorem 11: Let S , S be valid program speci-

fications and  $\Omega: \mathfrak{S} \rightarrow \overline{\mathfrak{S}}$  a coordinate mapping satisfying EC. Let  $\alpha$  be any DO node of S which is changed by  $\Omega$  such that no descendant of  $\alpha$  is changed by  $\Omega$  . Then there exists a valid program specification  $S^{\prime}$  and coordinate mappings

$\Omega' : \mathbb{S} \to \mathbb{S}'$  and  $\Omega'' : \mathbb{S}' \to \overline{\mathbb{S}}$  satisfying EC such that  $\Omega'$  changes only  $\alpha$  .

# The Coordinate Algorithm

We now describe the <u>coordinate algorithm</u>. Given a program specification \$ and a DO node I of S , the coordinate algorithm generates a program specification  $\overline{s}$  and a coordinate mapping  $\Omega: \mathbf{S} \to \overline{\mathbf{S}}$  such that (i)  $\Omega$  changes only I and satisfies EC, and (ii) \$ satisfies L2. Theorem 10 implies that  $\overline{\mathbf{S}}$  is equivalent to  $\mathbf{S}$ . The algorithm can find any possible coordinate mapping satisfying (i) and (ii). By Theorem 11, we want to apply the algorithm repeatedly, starting from the innermost loop nodes.

We now describe, explain and illustrate the five major steps of the algorithm.

l. Let >>, ≈ be the relations >, ~ on \$ which would result if the I node were changed to a DO SIM node. Define the relation ---> on O(I) and the subset B of N(I) as follows. For each relevant pair of occurrences f, g in O(I), and each X € < f, g > with X > 0: (a) If X ≈ 0, then include the relation f ---> g.

(b) If  $X \prec \overline{0}$ , then: for each descendant J of I which either equals or is an ancestor of  $f \cap g$ , if  $\Pi_{J}^{f \cap g}(X) \prec \overline{0}$ , then let J be an element of  $\beta$ .

The relations  $\rightarrow$  are the additional relations  $\rightarrow$  required if we were to simply change the I node to a DO SIM node. The existence of an X satisfying (b) immediately precludes this possibility.

The nodes in  $\beta$  are "blocking nodes". This means that for each J  $\epsilon \beta$ , J cannot appear inside a DO SIM I node, and none of the nodes into which I is changed can be moved below J. Applying step 1 to the I node of Program 1 gives the relations ---> shown in Figure 4. It finds  $\beta = \{J\}$ . E.g., for the occurrence pair u2, u4 we have (1, 0)  $\epsilon < u2$ , u4 >, (1, 0) >  $\vec{0}$  and (1, 0)  $\approx \vec{0}$ . Hence, (a) gives u2 ---> u4.

For the occurrence pair al, al: for any i > 0 we have  $(i, 0) \in \langle al, al \rangle$ ,  $(i, 0) \succ \vec{0}$  and

(i, 0)  $\approx \vec{0}$ . Hence (a) gives al ---> al. For any j < 0, we have (i, j)  $\epsilon < al, al >$ , (i, j) >  $\vec{0}$  and (i, j) <<  $\vec{0}$ . Since  $\Pi_{J}^{al\cap al}(i, j)$ = (i, j), part (b) places J in  $\beta$ .

Note that if L were a DO node, then step l applied to el, e2 would place L in  $\beta$ . This shows why the algorithm should be applied to inner loops first.

2. Let ==> denote the relation on  $\mathcal{O}(I)$ formed by the union of the relations  $\Rightarrow$ ,  $\rightarrow$  and  $\xrightarrow{*}$ , and let ==> denote its tree completion. Complete the set  $\beta$  as follows: for each node  $\alpha$  of  $\mathcal{N}(I)$ , if  $\alpha ==> \alpha$  then add  $\alpha$  to  $\beta$ .

For Program 1, every relation  $\alpha \stackrel{=}{=} \beta$  on  $\eta(I)$  for which  $\alpha \stackrel{=}{=} \beta$  does not hold is indicated by an "\*" in Figure 4. Step 2 then adds the following nodes to  $\beta$ : al, a2, cl, c2, dl, d2.

3. <u>Choose a tree partition P of J(I)</u> <u>such that:</u>

(a) <u>Any non-terminal node of P consists of a single loop node of N(I)</u> <u>which is not in B</u>.

(b) <u>The relation induced on O(P) by</u> <u>==> is tree consistent.</u>

To obtain the maximum amount of parallellism, the partition P should be chosen to satisfy the following conditions as well: (1) For any  $\alpha \in \mathcal{N}(I)$ : if  $\alpha \notin \beta$  and  $\mathcal{N}(\alpha) \cap \beta \neq \phi$ , then  $\{\alpha\}$  is one of the sets of  $\mathcal{P}$ . (2) For any  $\alpha, \beta \in \mathcal{N}(I)$ : if  $\mathcal{N}(\alpha) \cap \beta = \phi$

and  $\beta \in \beta$ , then  $\alpha$  and  $\beta$  belong to different sets of  $\beta$ .

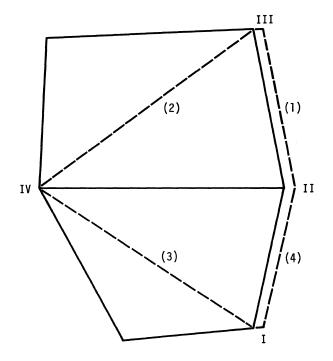

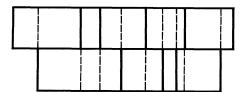

There is an algorithm for choosing such a  ${\rm P}$ . Applying it to our example, and then combining the resulting sets {d1, d2} and {b4} into a single set, gives the tree partition  ${\rm P}$  shown in Figure 5. In general, finding the best tree partition  ${\rm P}$  is a major implementation problem.

4. Let N<sub>1</sub>, ..., N<sub>m</sub> be the terminal nodes of P. Define the program tree of s as fol lows:

(a) <u>n(s) = { α : α ∈ n(s), α ≠ I} ∪</u> <u>{I<sub>1</sub>, ..., I<sub>m</sub>}</u>.

(b) For any nodes α, β of S not equal to I: α is a descendant of β if and only if α is a descendant of β.

(c) For any node α of S not equal to I:

(i) α is a descendant of I<sub>j</sub> if and only if α is an ancestor of I<sub>j</sub> if and only if either α is an ancestor of N<sub>j</sub>.

This defines a tree in which the I node is split into the nodes  $\overline{I}_1, \ldots, \overline{I}_m$ . For each j,  $\eta(\overline{I}_j) = \{\overline{\alpha} : \alpha \in N_j\} \cup \{\overline{I}_j\}$ .

In our example, § has the tree of Figure 2.

5. Define the relation  $\rightarrow$  on  $\overline{S}$  as follows. For any occurrence  $\overline{f}, \overline{g}, \text{in } \overline{S}$ , we let  $\overline{f} \rightarrow \overline{g}$  if either: (a)  $\underline{f} \rightarrow \underline{g}$  in  $\underline{S}, \text{ or}$ (b)  $\underline{f} \xrightarrow{-->} \underline{g}, \underline{f} \in N_i, \underline{g} \in N_j$  and either (i)  $i \neq j$ , or (ii) i = j and  $\overline{I_j}$  is a DO SIM node.

In our example, step 5(b) gives the following relations: (i)  $\overline{u1} \rightarrow \overline{u2}$ ,  $\overline{b5} \rightarrow \overline{b2}$  and (ii)  $\overline{u2} \rightarrow \overline{u4}$ ,  $\overline{u5} \rightarrow \overline{u2}$ .

The mapping  $\theta$  of Definition 6 is defined by  $\theta(\overline{\alpha}) = \alpha$  if  $\alpha \neq I$ , and  $\theta(\overline{I}_j) = I$ . Parts S3 and S4 of the specification  $\overline{\mathbb{S}}$  and the coordinate mapping  $\Omega : \mathbb{S} \rightarrow \overline{\mathbb{S}}$  are then defined in the obvious way.

The equivalence of § and  $\overline{\mathbf{s}}$  is implied by Theorem 10 and Theorem 12 below. Note that Theorem 10 indicates how to compute the sets  $<\overline{\mathbf{f}}, \overline{\mathbf{g}} >$  in order to apply the coordinate algorithm

# Figure 5

again to  $\overline{s}$ . Theorems 11 and 13 show that the coordinate algorithm can be used to obtain any desired coordinate mapping.

<u>Theorem 12</u>: Let S be a valid program specification, I a DO node of S, and let  $\overline{S}$  and  $\Omega$ :

$\mathbf{S} \rightarrow \overline{\mathbf{S}}$  be constructed by the coordinate algorithm.

Then  $\overline{s}$  satisfies L2, and  $\Omega$  is a coordinate mapping which satisfies EC.

<u>Theorem 13</u>: Let  $S, \overline{S}$  be valid program specifications, and let  $\Omega: S \rightarrow \overline{S}$  be a coordinate mapping satisfying EC which changes only the node I.

Then  $\overline{\mathbb{S}}$  and  $\Omega$  can be constructed from  $\mathbb{S}$  by the coordinate algorithm.

# Concluding Remarks

# General DO Increments

To handle arbitrary constant DO increments we need only change the definition of the set << f, g >> . Let  $I^1, \ldots, I^k$  be the branch with  $I^k = f \cap g$ . Assume that for each j, the  $I^j$  loop is a DO loop of the following form:

DO

$$I^{j} = \ell^{j} + \sum_{r=1}^{j-1} c_{r}^{j} \star I^{r}, u^{j}, d^{j}$$

where the  $c_r^j$  and  $d^j$  are integer constants, and  $\ell^j$  is any expression not involving the  $\Gamma^r$ . More

general DO loops must be put into this form by changing the index variable. For purposes of the definition, replace a DO SIM I<sup>j</sup> loop by any DO loop whose index set contains  $\mathfrak{I}_{r^j}$ .

Now, define << f, g>> to be the set of all  $(x^1, \ldots, x^k) \in \mathbb{Z}_{f \cap g}$  such that there exist P  $\epsilon \ \mathfrak{I}_f$  and Q  $\epsilon \ \mathfrak{I}_g$  with  $(y^1, \ldots, y^k) = \Pi_{f \cap g}^g(Q)$ -  $\Pi_{f \cap g}^f(P)$  and  $y^j = d^j x^j + \sum_{r=1}^{\Sigma} c_r^j y^r$

for each j.

With this new definition, all of our results remain valid in the general case of arbitrary constant DO increments.

# Further Refinements

Several refinements of the coordinate method to yield more parallelism are possible. For example, it is clear that the computation of U(I+1, J) \*\*2 in statement 10 of Program 1 could be done inside a DO SIM I loop. This involves first splitting the J loop into two loops. In general, any node in the set  $\mathcal{B}$  of the coordinate algorithm is a candidate for splitting. Such refinements will be described in [5].

# Practical Problems

There are many practical problems to be solved in implementing the coordinate method for a real compiler. We list some of these below. Although described separately, they are all closely related. The solutions of these problems will depend upon the particular parallel computer design.

<u>Choice of the DO Node I</u>. To maximize parallelism, by Theorem 11 we would apply the coordinate algorithm successively to each DO node, working up from the bottom of the tree. However, this may produce more parallelism than can be exploited by the computer. Some procedure is needed to choose the nodes to which the coordinate algorithm should be applied.

<u>Choice of the Tree Partition P.</u> Maximizing the parallelism does not necessarily produce the best program. In our example, we assumed an algorithm clever enough not to put b4 into its own separate DO SIM I loop. However, we might have done better to further decrease the parallelism by

putting  $\overline{u6}$  in the  $\overline{I}_5$  loop, eliminating the need for TMP5.

<u>Translation of the Specification</u>. It is necessary to translate the specification into either FORTRAN or some intermediate language from which the compiler can generate code. Our example indicates that conditional branches can always be handled by converting to conditional assignment statements. However, this will not always be the best procedure. Other improvements are also needed. E.g., in Program 2 we can replace TMP1 and TMP3 by new occurrences of P and Q.

Our example shows how complicated these problems can become. However, most real programs are simpler, and simple solutions will usually be good enough. For example, we might always choose P to consist of a single set. The coordinate algorithm would then simply try to rewrite the program with a single DO SIM I loop.

# Conclusion

We have presented a method of detecting parallelism in sequential programs which generalizes several previous methods. It forms the basis of a sequential to parallel conversion phase of a compiler for a parallel array or vector computer. The techniques employed - particularly the use of the < f, g > sets and the relation  $\implies$  should be applicable to other areas of program optimization.

# References

- L. Lamport, <u>Some Remarks on Parallel</u> <u>Programming</u>, Massachusetts Computer Associates, CA-7211-2011, (November, 1972), 17 pp.

- [2] Y. Muroaka, <u>Parallelism Exposure and Exploitation in Programs</u>, Ph.D. Thesis, University of Illinois, Urbana (1971), 236 pp.

- [3] P.B. Schneck, "Automatic Recognition of Vector and Parallel Operations", <u>Proc. of</u> <u>the ACM 25th Anniversary Conference</u> (August, 1972), pp. 772-779.

- [4] L. Lamport, "The Parallel Execution of DO Loops", to appear in the <u>Comm. of the</u> <u>ACM</u>.

- [5] L. Lamport, <u>The Complete Coordinate</u> <u>Method</u>, Massachusetts Computer Associates, to appear.

- [6] C.V. Ramamoorthy, and M.J. Gonzalez, "A Survey of Techniques for Recognizing Parallel Processable Streams in Computer Programs", <u>AFIPS Proceedings, Fall Joint</u> <u>Computer Conference</u> (1969), pp. 1-15.

# MODELING FOR PARALLEL COMPUTATION: A CASE STUDY

J. L. Baer Computer Science Group University of Washington Seattle, Washington 98195

#### Abstract

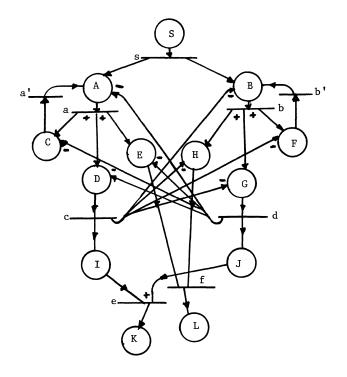

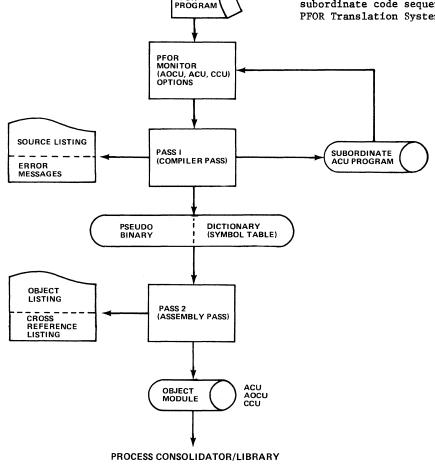

A methodology to build models for parallel computation for some special class of algorithms, namely compilation, is presented. The control graph component of the model is of the extended Petri Net form with switches and token absorbers. A detailed example of the use of the graph is given and some formal properties such as conservation of token and proper termination are proven.

# I. Introduction.

In recent years, we have seen the emergence of numerous graph models for parallel computation [3]. Depending on the investigators' backgrounds (engineers, logicians, mathematicians), the objectives of the models have been varied (e.g. coherent design of modular parallel systems, correct flow of control in the execution of parallel algorithms, relations between sequential programs and their parallel representations, prediction of cost and performance of multiprocessors).

In this paper, we present (first in Section II) the criteria which have led us to select some particular node and arc primitives and graph properties for the modeling of a specific class of algorithms, namely parallel compilation. The choice of this test vehicle for our modeling methodology is motivated by the following observations. First, techniques to handle automatically the detection of parallelism are best suited for high-level languages and scientific applications and do not carry over well for compilation, which has most often been considered as a sequential process. Therefore some "human insight" appears necessary. Second, this will oblige us to try and uncover some parallelism in the compilation process through algorithm modification, changes in data structures, redundancy, etc. Finally, assuming the efficiency of multiprocessors at run-time, means must be found to use them efficiently at compile time.

In Section III, we apply this modeling methodology to an example taken from the compilation process. Different stages in the modeling are successively introduced. They show the importance and the need for the features introduced in Section II.

Section IV defines formally the graph model and some of its properties. It is shown how the latter can be derived through techniques resembling those used in the theory of formal languages.

# II. Graph Primitives and Model Properties.

In the rest of this paper, we assume the reader's familiarity with the basic concepts of graph theory.

# 1. Places and Transitions of the Control Graph.

Like any other algorithmic process, compilation has three components: control, computation and data. We shall separate the modeling into a control graph (control of operators) and a dataflow graph (action of operators on data). In this paper, we investigate the control part.

The amount of interpretation that is present in a model depends mostly on the goals that one wants to achieve in the modeling process. If the primary objective is to describe specific algorithms or systems, then a total interpretation will be most convenient. Adam's Computation Graph [1] is such an example, and it can be regarded as a parallel programming language. On the other hand, if the derivation of general formal properties and the characterization of parallel algorithms are the main goals, then uninterpretation is necessary and schemata have to be introduced [6]. In our case, we are dealing with compilation considered as a class of algorithms and not with the modeling of a particular compiler. Hence, we will not choose total interpretation. At the same time, we wish to be able to retain some descriptive power and we have to rule out complete uninterpretation. Therefore our model is partially interpreted. Most of the interpretation takes place in the data graph, but some nodes/arcs of the control graph possess specific meanings.

One can view compilation as a general pipeline process, namely:

#### lexical analysis $\rightarrow$ syntax analysis $\rightarrow$

#### code generation.

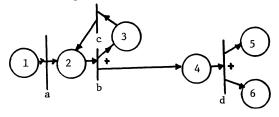

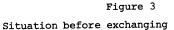

The unit of information flowing through the pipe can vary widely in size. For example, one could choose a subprogram, a block, a statement, a lexical or syntactical entity. Furthermore, each element of the pipe can be broken into a number of substages with appropriate latches. As we shall see in the next section, this pipeline concept can also exist at very fine levels of detail. Independently of the size of the unit of information, a "token machine" is appropriate to represent pipe-line flow. Therefore the control graph is based upon the Petri Net

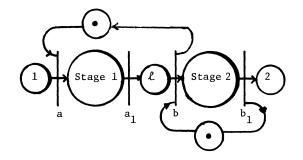

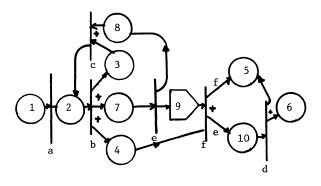

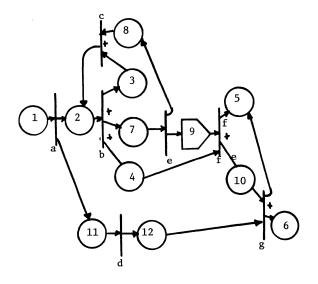

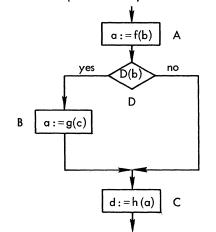

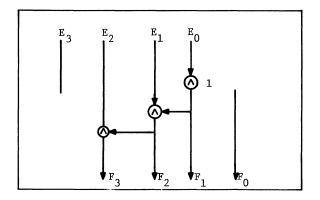

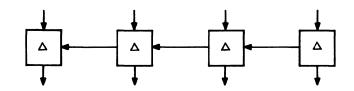

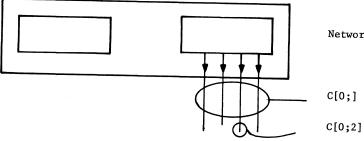

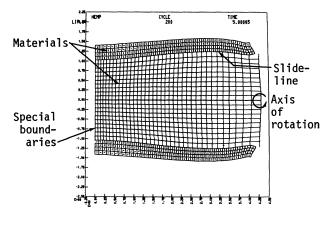

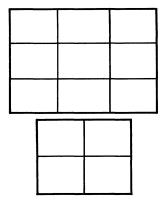

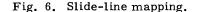

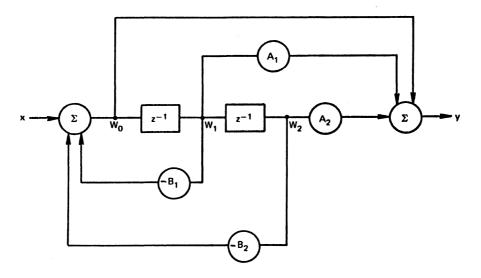

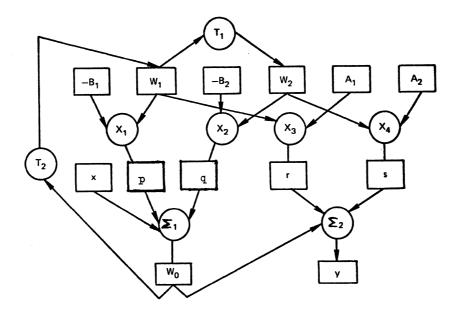

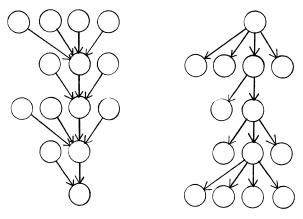

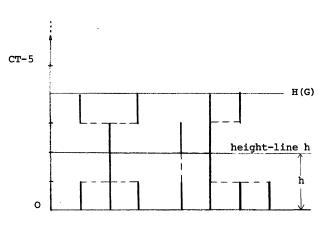

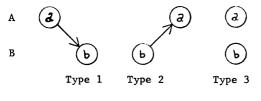

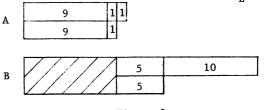

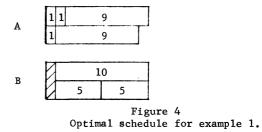

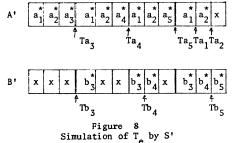

concept [5,9]. The formal definition of the graph being given in Section IV, we recall here only that a Petri Net is composed of a set of transitions (corresponding to events and denoted by | in figures), a set of places (corresponding to the holding of conditions and denoted  ${\boldsymbol{\bigcirc}}$  ), and a set of directed arcs linking (input) places to transitions and transitions to (output) places. Places are able to receive tokens which mark the holding of conditions. A place without token is empty; otherwise it is full and the presence of a token will be shown by 🗿 in the figures. An event can occur (equivalently a transition can fire) if all its input places are full. After the firing, a token is removed from each input place and a token is added to each output place. We do not allow a place to be input and output to the same transition in order to "clarify" the description of holdings. Figure 1 shows a twostage pipe-line process modeled by a Petri Net. When place 1 becomes full, stage 1 can be initiated through the firing of transition a. When stage 1 is completed, transition a will fire and the latch will become full. Now transition b can fire, allowing the processing of stage 2 and the possibility for transition a to fire anew if place 1 becomes full again. Thus, stages 1 and 2 can be active simultaneously. This particular instance of a pipe-line is built in such a way that stage 1 has to wait for the initiation of the  $i^{th}$  computation of stage 2 before being able to initiate its own (i+1)<sup>th</sup> computation. In Figure 2, it is shown how a buffer can be introduced between the two stages (the buffer here being of size 2).

Figure 1. Modeling a Pipe-line Process with Petri Nets.

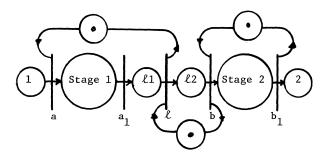

Figure 2. Increasing the size of Buffers between Stages.

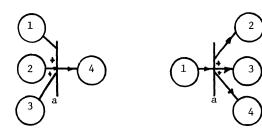

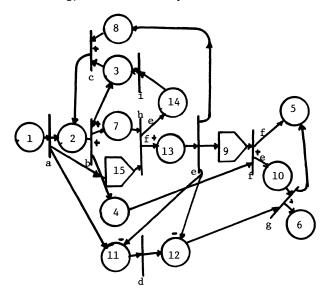

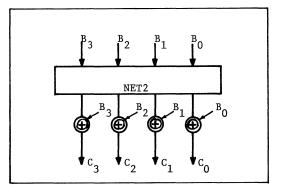

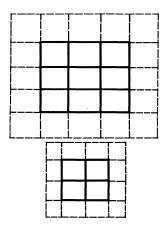

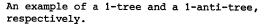

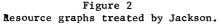

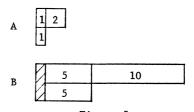

Petri Nets in the above form are not easily amenable to represent predicates. Extensions using conjunctive logic as above and <u>disjunctive</u> <u>logic</u>, i.e. EOR [2], have been used to enhance the descriptive power of models [7] while, at the same time incurring no loss in some formal properties [4]. We follow the same approach here, denoting by + the presence of an EOR condition at either the input or output of a transition (cf. Figure 3). The conjunctive logic, i.e. AND condition, is the assumed default situation. We forbid mixed logics since we can always realize the desired boolean condition with the inclusion of appropriate "dummy" places and transitions with simple logic.

(a)Input Disjunctive Logic. Only one of the input places can be full. Then a can fire. (b)Output Disjunctive Logic. After firing of a, only one of the output places will receive a token.

# Figure 3. Disjunctive Logic.

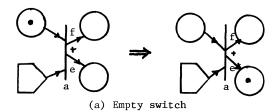

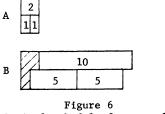

Although the EOR and AND logics have sufficient properties to show the flow of control in algorithms, we introduce nevertheless a new type of place that we call switches. Switches bear some analogy with the construct of the same name found in programming languages and also with Nutt's resolution procedures [8]. However, their actions are purposely more restricted than these procedures so that their presence will not destroy formal properties of the model. As any other place, a switch can either be full or empty. The presence or absence of tokens in a switch does not influence the firing of the transition for which it is an input place; that is to say the conditions for firing are tested on the set of input places from which the switch has been removed. A transition which has a switch as one of its input places (and there cannot be more than one switch per transition) is necessarily of EOR-output logic with only two output places corresponding respectively to a full switch (branch f) and to an empty switch (branch e). Figure 4 illustrates these concepts with the switches denoted by  $m{D}$ . As we shall see in the next section, switches allow flexibility and short cuts in the modeling of algorithms.

# Figure 4. Illustration of the Firing of a Transition with an Input Switch.

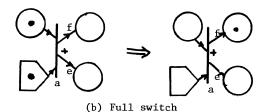

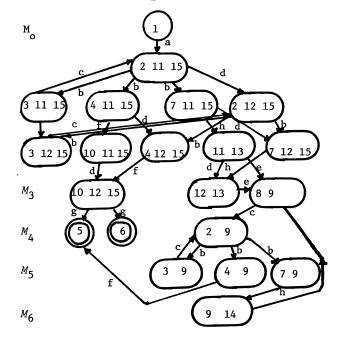

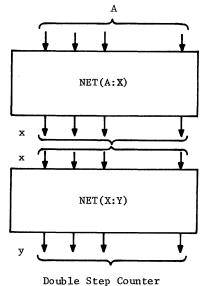

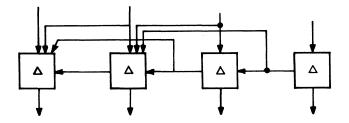

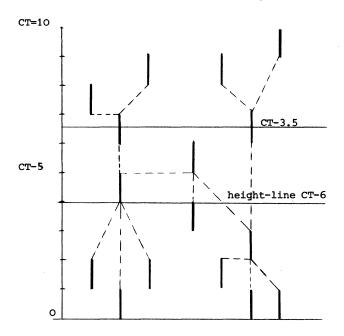

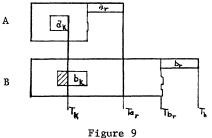

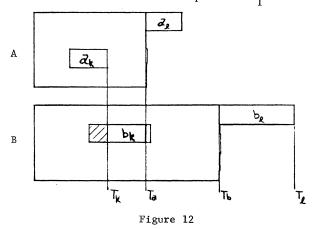

The transformation of a sequential program into parallel form might introduce some justifiable redundancy. However, processing which has become useless should not be allowed to be carried on and to tie up resources that the rest of the system might need. This point is illustrated by the following example. We want to search a linear table for a given key and two processors can be available. Hence, we desire processor 1 to start at the low end of the table with indices being incremented and processor 2 at the other end with decrementing indices. As soon as one of the processors has found a matching entry, both computations should be terminated. Moreover, if processor 1 was started first and had found the match and processor 2 was not yet initiated, it is evident that processor 2 should be prevented from performing a useless task, and vice-versa. In our modeling process, we use arcs which are token absorbers to represent this situation. Token absorbers also permit token conservation, a property needed, as we see below, for modeling pipe-line processes.

A token absorber is a multiarc with one head (a transition) and one or more tails (places). When the transition from where the head originates fires, tokens are removed from each of the full tail places. Figure 5 shows how this cancelling occurs for the previous example. Transitions a and b correspond to the comparison process; places C and F are the conditions of no-matching; E and H also correspond to no-match but in supplement they indicate that the ends of the (half) tables have been reached, and D and G correspond to a match. When either c or d fires, say c for example, tokens which were possibly present on B, F, G and H are removed. (In this example the presence of a token on one of these places implies the emptiness of the three others.) If we had a match on both processors, because of duplicate

elements in the table, c and d could be terminating at the same time. By convention, similar to the realization of an interrupt scheme without priority, two transitions cannot fire simultaneously. If the two signal completion at the same time, one of them will be chosen arbitrarily as the first one to finish. Therefore I and J cannot hold tokens simultaneously (EOR-input logic at transition e), and K corresponds to a match in the search process. On the other hand, transition f will fire when both processors report no success.

Figure 5. Illustration of the Use of Token Absorbers.

# 2. Execution Sequences and Properties of the Graph.

A control graph with places and transitions as above cannot describe a computational process per se. A meaning must be given to places and transitions. A first element of this semantic attachment is the data-flow graph associated with the control flow graph. A transition of the control can be linked to an operator in the dataflow graph. Each operator takes its inputs from a range of memory locations, performs a function and outputs values in a domain of memory locations. Furthermore, if the transition is of EORoutput logic, the operator indicates the output place on which a token is to be placed. An interpretation of the model consists of defining the data graph in terms of specific memory cells and their initial values, the operators' function, ranges and domains, as well as an <u>initial</u> marking of the control graph. The latter indicates which places are initially full, and the number of tokens on each place. In the sequel we will describe markings by the name of places which are full. The name of a place will occur as often as the number of tokens it holds. Starting with this initial marking, an <u>execution</u> <u>sequence</u> in the control graph is a sequence of transition firings. In the example of Figure 5, two out of the possible execution sequences, with an initial marking of a token on S, are:

sabb'ba'ace

saa'bb'aba'b'baf.

After each transition firing, the graph is in a new state, or <u>marking</u>. The execution sequence can also be given in terms of sequence of markings. For the two above, we have respectively:

S,AB,BC,CF,BC,CF,AF,DF,I,K

S,AB,BC,AB,AF,AB,BC,CF,BF,AB,AH,EH,L .

If the execution sequence is finite, the last state reached is called a <u>terminal marking</u>.

The control graph should be constructed in such a way that given an initial marking  ${\rm M}_{\rm O}$  and a set *M* of goals, i.e. terminal markings, all execution sequences starting with M should be finite, reach one of the members of M and no other transition should be able to fire. This is akin to Gostelow's proper termination [4] and resembles strongly the acceptance of strings by a finite state automaton. For the example of Figure 5, an initial marking  $M_0$  of a token on  $\hat{S}$  and a set of goals  $M = \{K,L\}$  yields proper termination for the graph, if one forbids infinite looping through transitions a,a' and b,b'. The rationale for this restriction will be explained in the following section. It is to be noticed that  $M_0$  and M are at the discretion of the model builder, but proper termination is independent of the data graph and of the operators' functions. In supplement, since our model is oriented towards the representation of pipelining, another important property, namely the conservation of tokens, should be considered in conjunction with proper termination. More precisely, stages in the pipe-line have to be reusable after each activation. Therefore the initial and terminal markings should differ only by the presence of tokens on places which receive or deliver tokens from or to other stages. (The foremost stage as well as the last one constitute the environment or outside world [8,9]). The presence of token absorbers becomes very useful for the realization of this constraint.