# PROCEEDINGS

OF THE

# **1976 INTERNATIONAL CONFERENCE**

ON

# **PARALLEL PROCESSING**

PHILIP H. ENSLOW JR. Editor

**1976 CONFERENCE ON PARALLEL PROCESSING**

Enslow, Ed

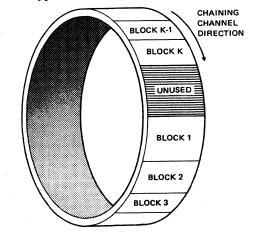

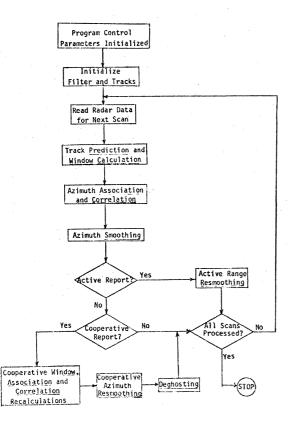

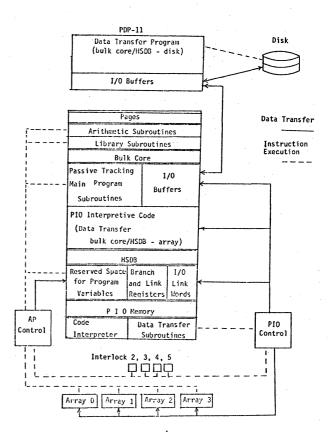

76CH1127-00

Cosponsored by the

Wayne State University

and the

**IEEE Computer Society**

IEEE Catalog No. 76CH1127-0C

# PROCEEDINGS OF THE 1976 INTERNATIONAL CONFERENCE ON PARALLEL PROCESSING

# PHILIP H. ENSLOW JR. Editor

Papers presented on August 24-27, 1976

Co-Sponsored by

Department of Electrical and Computer Engineering WAYNE STATE UNIVERSITY Detroit, Michigan

**IEEE** Computer Society

In Cooperation with the

Association for Computing Machinery

Additional copies are available from: IEEE Computer Society 5855 Naples Plaza, Suite 301 Long Beach, CA 90808

or

IEEE Service Center 445 Hoes Lane Piscataway, NJ 08854

Manufactured in the U.S.A.

## PREFACE

This series of conferences on parallel processing has matured into a truly international event, and I am extremely pleased to have been associated with the 1976 meeting. What started as a very small meeting on a special aspect of parallel processing in 1972 has expanded into a major meeting covering every facet of the subject with contributions from all over the world. The series continues under the general chairmanship of Professor Yse-yun Feng, and I was honored to be able to share some of the work of organizing the 1976 International Conference on Parallel Processing. This year the meeting had the formal support of both the IEEE Computer Society and the Association for Computing Machinery. This support is gratefully acknowledged, especially that of the Computer Society which is handling the production and distribution of these Proceedings and that of SIGARCH for assistance in organizing a session.

All of the papers submitted to this conference were formally reviewed, and I would like to sincerely thank the 59 individuals who served as referees for the more than 80 papers submitted. The efforts of these workers, who are identified at the end of these Proceedings, were essential in organizing a quality meeting. The workload was heavier this year than ever before, but I believe that you will agree with me that they did an outstanding job. I would also like to call your attention to a new feature of this year's meeting and acknowledge the outstanding efforts of the winners of the awards for the Best Presentation and the Best Paper. These individuals, identified on the next page, were selected by the best jury possible, the attendees at the conference.

It has been my pleasure to work on this conference, and I look forward with high anticipation to the 1977 meeting.

Philip H. Enslow, Jr. Program Chairman

iii

# SPECIAL AWARDS 1976 INTERNATIONAL CONFERENCE ON PARALLEL PROCESSING

# **Best Presentation**

Professor David S. Wise Indiana University

"The Impact of Applicative Programming on Multiprocessing" by Daniel P. Friedman and David S. Wise.

# **Best Paper**

Professor Jerome Rothstein Ohio State University

"On the Ultimate Limitations of Parallel Processing"

v

1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 -1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 -

# TABLE OF CONTENTS

Page

| KEYNOTE ADDRESS<br>Parallel Processing: Commercial Needs, Trends, and Perspectives<br>Dr. Robert R. Johnson                              |    |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

| Burroughs Corporation                                                                                                                    |    |

| SESSION 1 APPLICATIONS: IMAGE PROCESSING<br>Chairperson: Professor J. Rothstein                                                          |    |

| Highly Parallel Digitized Geometric Transformations Without Matrix Multiplication<br>C. F. R. Weiman                                     | 1  |

| Enhancement of Computing Power In Multiprocessor Systems For Processing of Digitized<br>Pictures<br>K. Vorgrimler                        | 11 |

| Application Of Distributed Processing To The Production Of Digital Terrain Data<br>Dennis E. Moellman and Robert A. Meyer                | 18 |

| Application Of A Parallel Processing Computer In LACIE<br>Sherwin Ruben, John Lyon, Rudolf Faiss and Matthew Quinn                       | 24 |

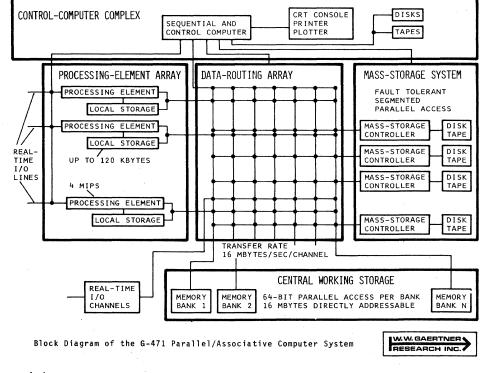

| High-Resolution Image Processing On A Parallel Computer System<br>W. W. Gaertner, M. P. Patel, S. S. Reddi, C. T. Retter and I. M. Singh | 33 |

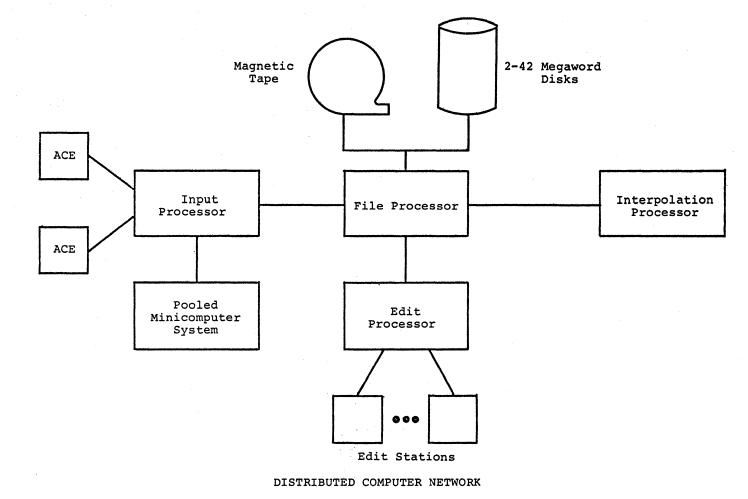

| An Implementation Of The Hadamard Transform On The Staran Associative Array Processor<br>Annette J. Krygiel                              | 34 |

| SESSION 2: OPERATING SYSTEMS<br>Chairperson: Lieutenant Colonel F. J. Hilbing                                                            |    |

| On The Formal Definition Of Processes<br>Pamela Zave                                                                                     | 35 |

| Hierarchical Monitors<br>A. M. Lister and P. J. Sayer                                                                                    | 43 |

| Garbage Collection With Multiple Processes: An Exercise In Parallelism<br>Leslie Lamport                                                 | 50 |

| Hierarchial Properties of Concurrency<br>G. S. Tjaden                                                                                    | 55 |

| SESSION 3: SYSTEM ARCHITECTURE AND ORGANIZATION I<br>Chairperson: M. Kesselman                                                           |    |

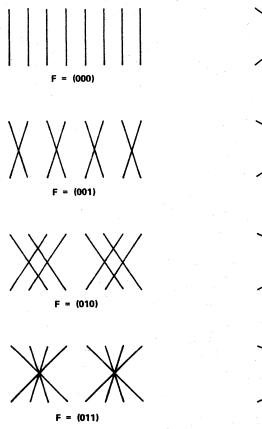

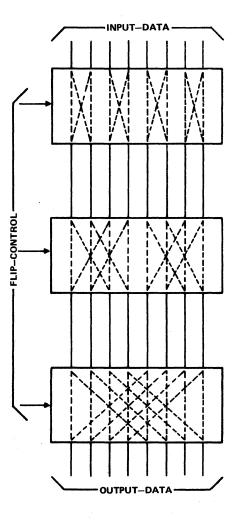

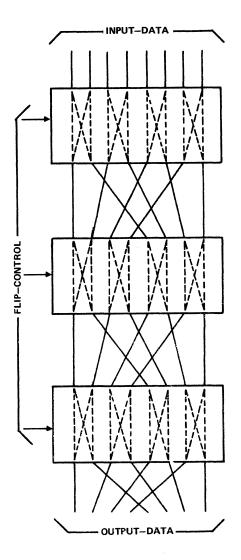

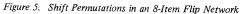

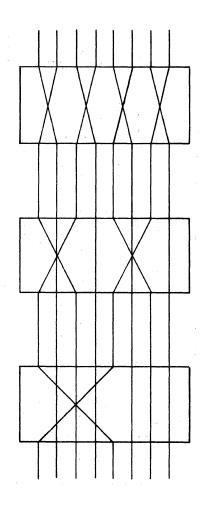

| The Flip Network In Staran<br>Kenneth E. Batcher                                                                                         | 65 |

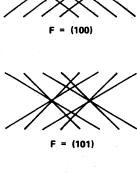

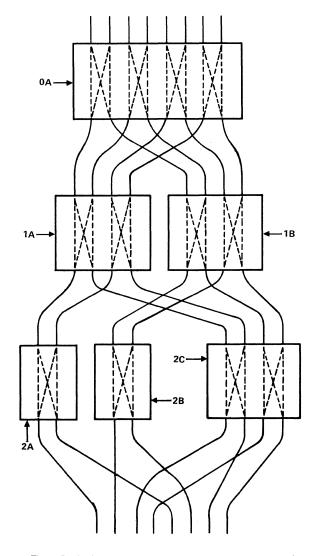

| Construction Of A Versatile Data Manipulator For Parallel/Associative Processors                                                         | 72 |

## TABLE OF CONTENTS (CONT'D)

| SESSION 4: SCHEDULING<br>Chairperson: Dr. C. P. Hsieh                                                                      |     |

|----------------------------------------------------------------------------------------------------------------------------|-----|

| Fast Algorithms For Bounding The Performance Of Multiprocessor Systems<br>Chao-Chih Yang                                   | 73  |

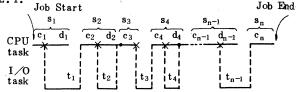

| Two Models Of Task Overlap Within Jobs Of Multiprocessing Multiprogramming<br>Systems<br>Mamoru Maekawa and Donold L. Boyd | 83  |

| Optimal Scheduling Of Vector Computations In A Reconfigurable Shared-<br>Resource Array Processing System                  |     |

| Alexander Thomasian and Algirdas Avizienis                                                                                 | 92  |

| SESSION 5: SYSTEM PERFORMANCE I<br>Chairperson: Joe McKay                                                                  |     |

| A Model For A Shared Resource Multiprocessor<br>Lawrence S. Cheung and Frederic J. Mowle                                   | 93  |

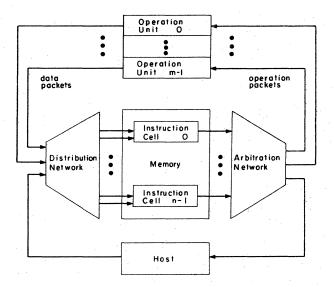

| Performance Analysis Of A Data-Flow Processor<br>David P. Misunas                                                          | 100 |

| An Analytic Approach To Performance Analysis For A Class Of Data Flow<br>Processors<br>Susan C. Meyer                      | 106 |

| On The Evaluation Of Array Computers<br>R. Hemmersbach and D. Schutt                                                       | 116 |

| SESSION 6: RELIABILITY<br>Chairperson: Captain R. A. Johnson                                                               |     |

| Error Detection And Recovery In A Data-Flow Computer<br>David P. Misunas                                                   | 117 |

| Reliability Aspects Of The Illiac IV Computer<br>Iftikhar A. Baqai and Tomas Lang                                          | 123 |

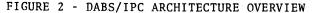

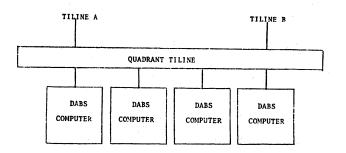

| Computer Architectures For Advanced Air Traffic Control Applications<br>Andres Zellweger                                   | 132 |

| SESSION 7: APPLICATIONS<br>Chairperson: Dr. W. W. Gaertner                                                                 |     |

| Distributed Processing For Signal Processor Using The Building Block<br>Signal Processor<br>Frank P. Hiner III             | 140 |

| Associative-Parallel Applications to Radar Signal Processing<br>K. L. Schaffer                                             | 145 |

| A Receiver For PCM Coded Digitone And MF Signals Using Associative<br>Processing                                           |     |

| Eugene S. Y. Shew and Jack M. Cotton                                                                                       | 154 |

#### Page

## TABLE OF CONTENTS (CONT'D.)

|                                                                                                              | Page |

|--------------------------------------------------------------------------------------------------------------|------|

| Radar Data Processing on the Alap<br>Hubert H. Love                                                          | 161  |

| Architecture and Simulation of an Associative Processor Integrated                                           |      |

| Jackylene Hood, Maitang Mark, and Jack Cotton                                                                | 168  |

| Application of Pepe to Real-Time Digital Filtering<br>D. B. Kimsey, L. E. Hand, and H. T. Nagle, Jr.         | 169  |

| SESSION 8: STARAN AND RELATED TOPICS<br>Chairperson: Oscar Reimann                                           |      |

| High Level Language for Associative and Parallel Computation with Staran                                     |      |

| R. G. Lange                                                                                                  | 170  |

| Analysis of the Awacs Passive Tracking Algorithms on the Radcap<br>Staran                                    |      |

| Robert Katz                                                                                                  | 177  |

| Automatic Track Initiation Using the Radcap Staran<br>Edward C. Stanke, II                                   | 187  |

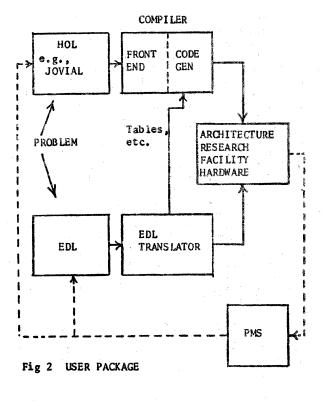

| Concept for a Computer Architecture Research Facility<br>A. Klayton                                          | 189  |

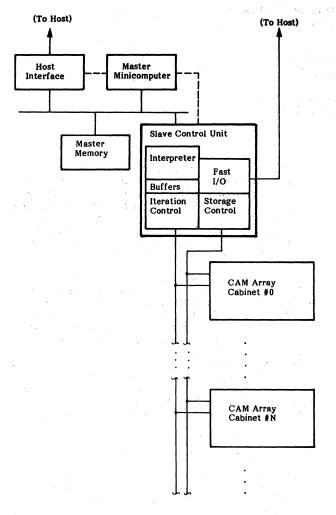

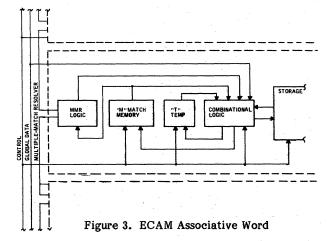

| A Content-Addressed Memory Designed for Data Base Applications<br>George A. Anderson and Richard Y. Kain     | 191  |

| SESSION 9: PERFORMANCE II<br>Chairperson: Dr. L. Lamport                                                     |      |

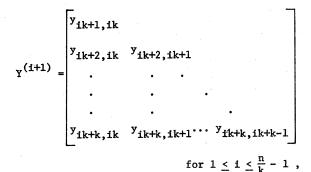

| Time and Parallel Processor Bounds for Linear Recurrence Systems with<br>Constant Coefficients<br>S. C. Chen | 196  |

|                                                                                                              | 190  |

| On the Ultimate Limitations of Parallel Processing<br>Jerome Rothstein                                       | 206  |

| SESSION 10: MULTIPLE-MICROPROCESSORS<br>Chairperson: David Freedman                                          |      |

| An Efficient Multiprocessor Architecture<br>Vincent                                                          | 213  |

| Design Considerations in Multi-Minicomputer Performance<br>Tadaaki Bandoh and Yukio Kawamoto                 | 219  |

| A Modular Vector Processing Unit<br>S. R. Ahuja and J. R. Jump                                               | 220  |

| A Shared Memory Technique for Different Microprocessors<br>Ronald L. Krutz and Bob Reynouard                 | 221  |

## TABLE OF CONTENTS (CONT'D.)

|                                                                                                       | Page     |

|-------------------------------------------------------------------------------------------------------|----------|

| SESSION 11: FUNDAMENTAL THEORY                                                                        |          |

| Chairperson: Professor H. M. Yamada                                                                   |          |

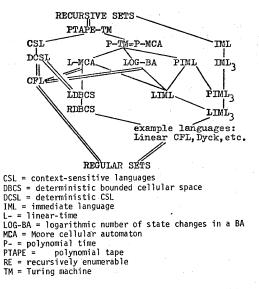

| Parallel Recognition of Patterns: Insights from Formal Language<br>Theory                             | 44,<br>1 |

| Michael Moshell and Jerome Rothstein                                                                  | 222      |

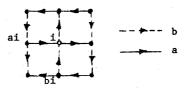

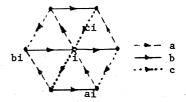

| Some Computational and System Theoretic Properties of Regular<br>Processor Networks                   | 0.0.0    |

| Renato M. Ermann and William I. Grosky                                                                | 230      |

| A Proof Method for Cyclic Programs<br>Nissim Francez and Amir Pnueli                                  | 235      |

| On Determinacy and Equivalence of Parallel Program Schemata                                           | 246      |

| Manilal Daya                                                                                          | 240      |

| SESSION 12: LANGUAGE ISSUES<br>Chairperson: Professor Roy Zingg                                       |          |

| Coordination of Parallel Processes in PL/1<br>Noward S. Modell, Ronnie G. Ward and Ted M. Sparr       |          |

| On the Time Required to Parse an Arithmetic Expression for<br>Parallel Processing                     | 051      |

| Ross A. Towle and Richard P. Brent                                                                    | 254      |

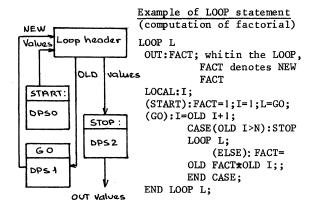

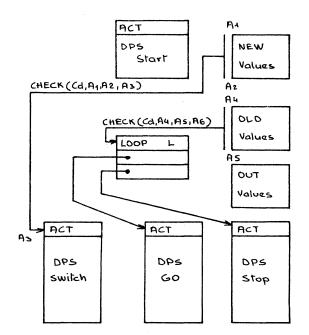

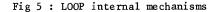

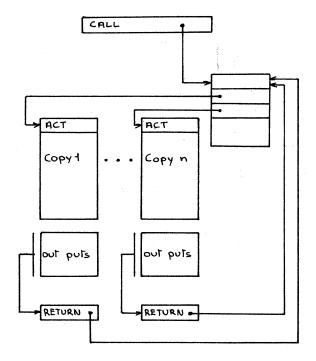

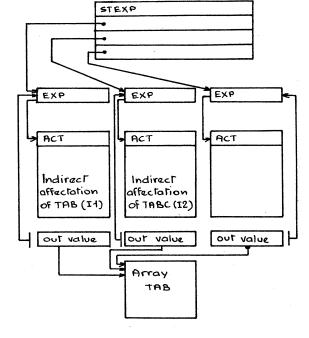

| Lau System Software: A High Level Data Driven Language for<br>Parallel Programming<br>O. Gelly, et.al | 255      |

| A High Level Language Oriented Multiprocessor<br>Mario F. de La Guardia and James A. Field            | 256      |

| The Impact of Applicative Programming on Multiprocessing<br>Daniel P. Friedman and David S. Wise      | 263      |

|                                                                                                       |          |

| SESSION 13: SYSTEM ARCHITECTURE AND ORGANIZATION II<br>Chairperson: John Cornell                      |          |

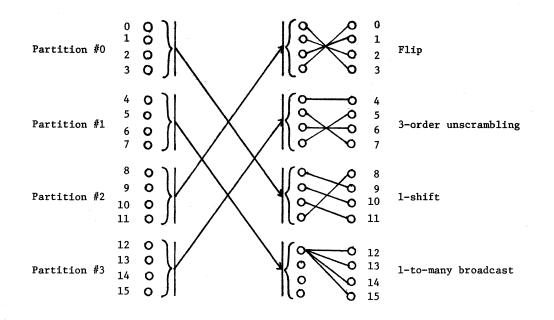

| Single Instruction Stream-Multiple Data Stream Machine<br>Interconnection Network Design              |          |

| Howard Jay Siegel                                                                                     | 273      |

| Effectiveness of Some Processor/Memory Interconnections<br>K. Y. Wen and D. H. Lawrie                 | 283      |

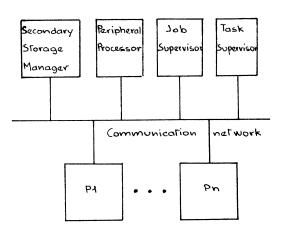

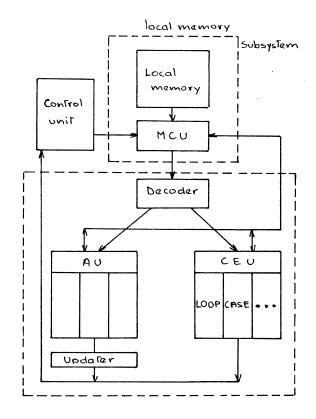

| Lau System Architecture: A Parallel Data-Driven Processor Based<br>on Single Assignment               |          |

| A. Plas, et.al.                                                                                       | 293      |

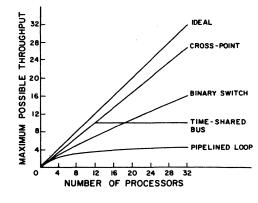

| Upper Bounds on the Performance of Some Processor-Memory<br>Interconnections                          |          |

| R. C. Pearce and J. C. Majithia                                                                       | 303      |

## TABLE OF CONTENTS (CONT'D.)

|                                                                                                 | Page |

|-------------------------------------------------------------------------------------------------|------|

| SESSION 14: SCHEDULING II                                                                       |      |

| Chairperson: Professor David Kuck                                                               | i.   |

| Operating System Modelled as a Conglomerate of Interdependent<br>Activities                     |      |

| T. Fend and C. P. Hsieh                                                                         | 304  |

| A Scheme for the Parallel Execution of Sequential Programs<br>C. V. Ramamoorthy and W. H. Leung | 312  |

| On Further Applications of the Hu Algorithm to Scheduling                                       |      |

| Problems<br>Edgar Nett                                                                          | 317  |

#### HIGHLY PARALLEL DIGITIZED GEOMETRIC TRANSFORMATIONS (a) WITHOUT MATRIX MULTIPLICATION

Carl F. R. Weiman Mathematical and Computing Sciences Dept. Cld Dominion University P.O. Box 6173 Norfolk, Virginia 23508

Abstract -- A new, computationally simple, highly parallel method for performing linear geometric transformations on digitized pictures is presented. Matrix multiplication is avoided by using a weighting scheme. Grid digitization is fundamental to the computation rather than being an undesirable source of error as in conventional methods. Microprocessor implementation based on vector parallelism suggests the possibility of real time animation of grey-scale pictures. Applications are not restricted to computer graphics and image processing, however, but are general to any system in which coordinates and linearity are involved, e.g., the numerical solution of PDE's. The transformation method is based on an interpretation of Rothstein's straight line code as an operator for digitized linear interpolation rather than as the description of a geometric figure.

#### I. Introduction

This paper describes a new, computationally simple and highly parallel method for performing affine transformations on digitized pictures and similar grid-based systems. Geometrically, affine transformations map parallelograms into parallelograms and are involved in linear axis scaling, shearing, and rotation. In picture processing, these transformations are useful in achieving picture registration for comparison, recognition, or mosaicing with other pictures; in computer graphics successive transformations yield animation. Ordinarily, an affine transformation is applied by multiplying all point coordinate tuples by a constant matrix. In transforming grey-scale pictures the original and transformed digitization grids generate 2-D moiré patterns of holes which must be filled by smoothing, thereby destroying information [1]. In the method presented here, matrices are not used and no operations more complex than addition of integers are needed. Grid digitization of the picture is fundamentally involved in the computation rather than being an undesirable source of error. The method is most suitable for parallel implementation on vector processors; real-time animation of arbitrarily rich gray-level pictures is straightforward using present technology.

(a) Research partly supported under ONR grant N00014-75-C-0571. Computation partly supported by ERDA under contract E (11-1) - 3077. Both at Courant Institute, New York University while author was Associate Research Scientist in Computer Science Department. Applications are not restricted to computer graphics and image processing but general to any system in which coordinates and linearity are involved, for example in the numerical solution of partial differential equations. The method is based on an interpretation of Rothstein's digitized straight line code [2] as a rule or operator for digitized linear interpolation rather than as representing a geometric entity.

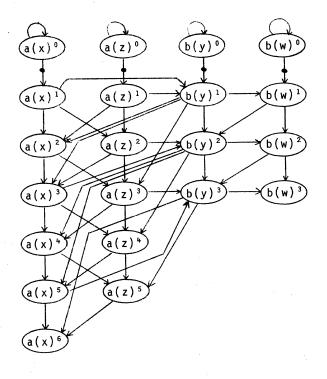

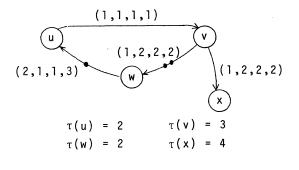

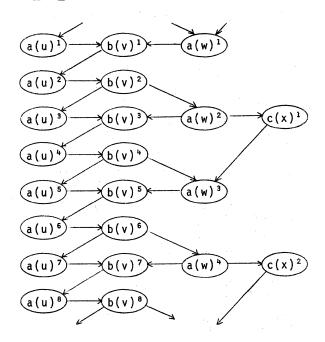

#### II. Rothstein's Code for Digitized Straight Lines

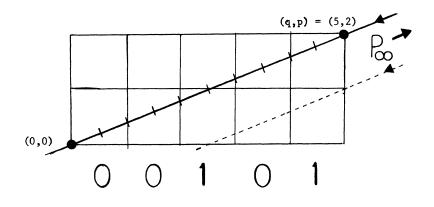

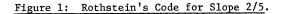

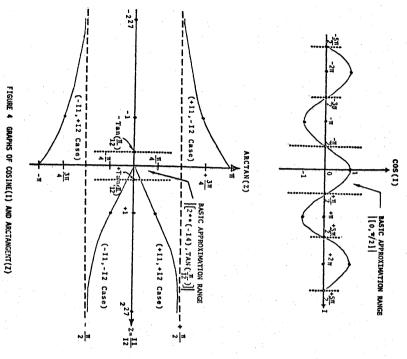

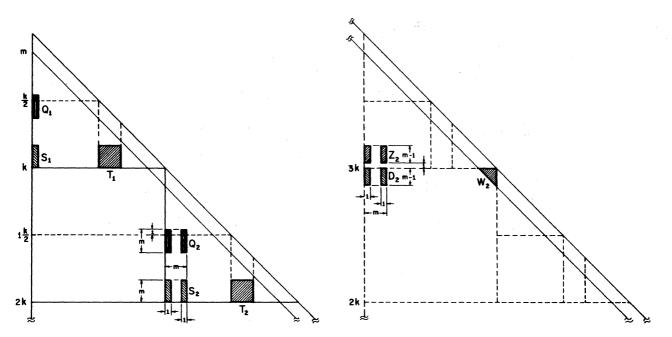

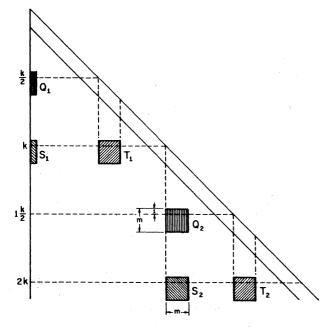

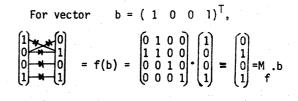

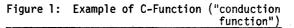

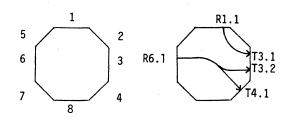

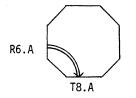

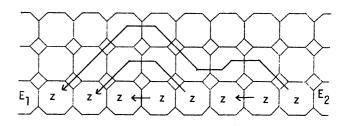

Rothstein's code is a binary sequence, each of whose digits corresponds to the nearest neighbor configuration of a grid cell crossed by a straight line; O corresponds to a cell whose neighbors on opposite sides are crossed by the line and 1 to a cell whose neighbors are crossed on adjacent sides (see figure 1). In the latter case the next cell is ignored, avoiding redundancy and yielding one code digit per grid column (grid row for slopes whose absolute values exceed unity). For a line of slope p/q where 0are integers with no common factors, the code has period q with p 1's per period. The digit sequence can be simply generated without solving the equation of the straight line at intersections with grid parallels by viewing the line between (0,0) and (q,p) as divided into pq equal segments and noticing that a digit occurs once for each interval of p such segments (i.e., the distance between two successive grid verticals). That digit is 1 if the interval in question also happens to contain the termination of an interval of q such segments (i.e., the line crosses a grid horizontal); otherwise, the digit is 0. This can be expressed in hardware (figure 2a) by synchronizing to the same clock, two cyclic binary shift registers of lengths p and q respectively, detecting end-around shifts of a single bit in each to determine code digits. A faster method using more hardware consists of successively adding p to a modulo q counter and detecting values less than p to generate code 1's (figure 2b). The latter can also be expressed as a generating function:

$$f = e^{2\Pi i (p/q)n}$$

$(i=\sqrt{-1})$

The nth code digit is 1 for  $Arg(f) < 2\Pi(p/q)$  and 0 otherwise.

#### III. Digitized Affine Transformations

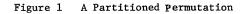

A. Axis Scaling. The geometry of figure 1 shows that the code comprises the most homogeneous

possible distribution of p l's among q digits. This suggests scaling the x-axis of a gray-scale picture by a ratio of q to p by distributing the p columns of the original picture among q of the transformed picture using the same homogeneous distribution. This is a digitized approximation to the affine transformation

$$(\mathbf{x},\mathbf{y}) \quad \begin{pmatrix} \mathbf{q/p} & \mathbf{0} \\ & \\ \mathbf{0} & \mathbf{1} \end{pmatrix} = (\mathbf{x} \cdot \mathbf{q/p},\mathbf{y}) ,$$

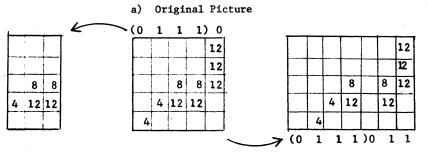

subject to the constraint that the picture grid cannot change. Shrinking the picture along the x-axis (replace q/p with p/q above) similarly corresponds to selecting p columns from q of the original picture according to the same homogeneous distribution. Figure 3 illustrates this technique with the corresponding code written above or below appropriate columns; the number within each cell represents a gray level. Unfortunately, in the case of expansion, empty "seams" are introduced and in contraction, columns are deleted. Such artifacts could be reduced by spatial smoothing, an undesirable solution not only because information is lost but also because gap geometry may "moiré" with picture features. This strong dependence on the relative positions of the grid and picture violates intuitions about picture invariance under translation.

Looking again at figure 2, note that changing the relative phases of the shift registers permutes the resulting code digits cyclically but does not change the average density of code 1's nor the homogeneity of their distribution. Thus, starting the code at any position other than when both registers are at the zero position yields a column selection rule equally as good in terms of homogeneity. Averaging the gray-levels resulting from all cyclic permutations of the column selection code therefore averages gap positions over all columns, eliminating discontinuities. No parts of the picture are selectively altered because all cells are represented. Figure 4 illustrates this averaging process for a ratio of 4/3.

Though the averaging process just described satisfies informational intuitions, it must be proven geometrically correct. That is, the resulting grey-scale picture must be the same as would have resulted from optically scaling the original picture and then redigitizing. The proof requires some results from the geometry of numbers beyond the scope of this paper but covered in detail in [3]. The outline of the proof follows. Stretching a picture in the continuous (non-digitized) case by the factor q/p can be viewed as a perspectivity through a point at infinity which projects p consecutive originally unit width columns of the original picture onto q consecutive unit width columns of the transformed picture; the code for p/q is a description of where column boundaries fall in the image. Each of the p original columns spreads into several of the q columns; the relative contribution of each original column to each new column is proportional to the relative area of the stretched image of the

former occupying the new column in question. Now consider figure 1 as a cross-section of the columns in the obvious sense. Relative area in the preceding sentence becomes relative length under this interpretation. These lengths could be measured by stepping along the q-cells 1/p units at a time counting steps and observing when the image of a p-cell boundary is crossed. Since step lengths are equal, each unit distance is equivalent to a count of p. If this stepping proceeds from each of the p-cell boundary images, q steps are both necessary and sufficient to count the lengths. But this yields precisely the same result as translating a line of slope p/q vertically by one grid cell and noting the number of times a 1 appears in each column. Since 1's change position only when the line crosses lattice points, and between such lattice points the code must be identical to the original, the result of translation must be a sequence of cyclic shifts in the code. That this sequence consists precisely of all possible shifts is also proved in [3].

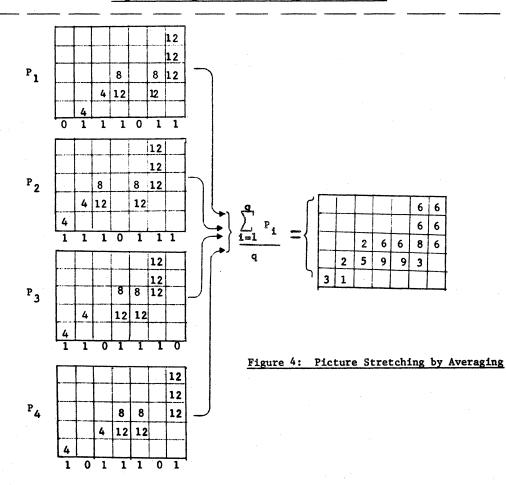

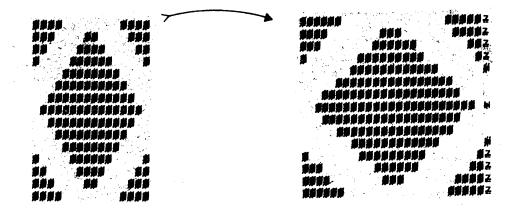

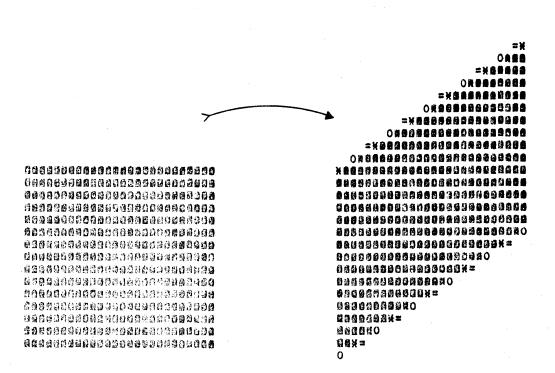

Visual corroboration of the averaging process is illustrated in figure 5a, A mathematically defined test pattern was stretched horizontally using the code averaging algorithm just described. The stretch ratio is approximately the ratio of row to column spacing on the printer and was chosen to correct this distortion caused by erroneously assuming equal spacing. Note that edges in the figure appear to have slopes +1 but a detailed examination reveals a boundary path related to the straight line code. Figure 6 was derived from a digitized photograph of a cat. Line code stretching algorithms applied horizontally and vertically yielded figure 7, illustrating the smoothness of the process even in delicately shaded retions.

<u>B.</u> Shearing Transformations. Combinations of horizontal and vertical stretching map rectangles into rectangles without altering the direction of edges. Shearing transformations, characterized by matrices of the form

$$\begin{pmatrix} 1 & a \\ 0 & 1 \end{pmatrix}^{T}$$

(horizontal) and  $\begin{pmatrix} 1 & 0 \\ b & 1 \end{pmatrix}^{T}$  (vertical)

map rectangles into parallelograms, altering the direction of one set of parallel edges. They are of interest here not only because they can be easily carried out using an averaging method similar to that just described for axis scaling, but also because appropriate combinations of shearing and scaling yield the entire group of affine transformations.

Using the same reasoning as for scaling, the code for p/q can be regarded as a rule for shearing the grid upward by sliding a column and those to its right upward one unit whenever a code digit 1 appears under a column. Just as in scaling, the jagged steps are removed by averaging over all possible cyclic shifts in the code position. For horizontal shearing, the word "column" should be replaced by "row", and "under" by "next to" Figure5b illustrates the application of a shearing. transformation effected by digitized averaging.

The transformations just described which average gray levels according to rules derived from the straight line code are henceforth referred to as digitized affine transformations (DATs) to distinguish them from the ordinary continuous affine transformations (CATs). The way DATs were presented, the computation involves moving columns of the original picture to several different positions in the grid of its transformed image. This computation can be rearranged by regarding each column of the image picture as having contributions from several columns of the original. The weight of each contribution is simply the fraction of the time the code digit 1, corresponding to a column in the original, spends in the column of the image when the code is cyclically permuted. This weighting scheme resembles a digitized version of a filtering or smoothing convolution. An important difference is that here the weighting coefficients are slightly different for each column in a period of code. However, they need only be calculated once for the entire picture by counting code 1's in columns throughout one cyclic permutation of the code. Viewing the computation as a weighting scheme or "pseudoconvolution" has important consequences for parallel implementation as will be discussed in the overview. The code has excellent approximation properties related to continued fractions [2], [3] which permit the use of shorter periods than might be expected to yield accurate results. In particular, accuracy to 1/q th of a grid unit is achieved by codes of period q. Shears and stretches by irrational amounts may thus be approximated to any desired accuracy.

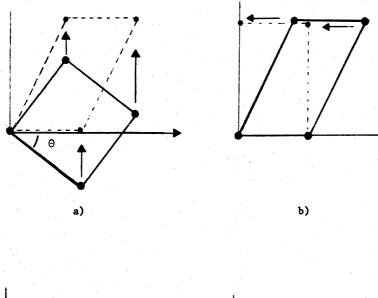

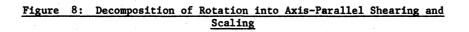

C. Rotation Through Arbitrary Angles. Rotation of a digitized picture through an arbitrary angle is computationally complex using conventional matrix multiplication methods [1]. It is nevertheless important for several reasons. At least one direction which is invariant under each DAT described above must be parallel to a grid axis. Shearing and stretching in an arbitrary direction cannot be accomplished by applying such transformations. However, if composition with an arbitrary rotation were possible, this directional constraint would be relaxed. Then, choice of coordinate directions is arbitrary, a necessary property of any general geometric system [4]. In picture processing applications, rotation is vital to picture registration; in computer graphics it is important for non-trivial animation. Fortunately, arbitrary rotation in the continuous case can be decomposed into shearing and scaling CAT's with the same special orientations as the DAT's presented above. Replacing these CAT's with the corresponding DAT's yields arbitrary rotation of digitized pictures using DAT's only. The accuracy of the result is as good as that of the shearing and scaling DAT's. Details follow.

Consider a unit square with one corner at the origin and a side in the fourth quadrant making an internal angle  $-\Theta$  with the x-axis. (Refer to figure 8a). Applying the shear

$$\left(\begin{array}{ccc}

1 & tan \\

0 & 1

\end{array}\right)$$

yields a parallelogram with one pair of sides parallel to the x-axis (figure 8 b). Next applying

$$\begin{pmatrix} 1 & 0 \\ -\sin\Theta\cos\Theta & 1 \end{pmatrix}$$

yields a rectangle with pairs of sides parallel to x and y axes (figure 8 c). Applying the scaling transformations

$$\begin{pmatrix} 1 & 0 \\ & \\ 0 & \cos \theta \end{pmatrix} \quad \text{and} \quad \begin{pmatrix} \frac{1}{\cos \theta} & 0 \\ 0 & 1 \end{pmatrix}$$

then yields a unit square (figure 8 d). Clearly the result is a rotation by  $\Theta$  degrees since the product of the transformations is

$$\begin{pmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{pmatrix}$$

The digitized versions of these transformations can be applied by using the codes corresponding to the non-integer quantities in the matrices above, approximated to any desired accuracy. At first sight, this approximation appears to involve several trigonometric calculations, but if an angle is specified by giving the direction (q,p) of the line making that angle with the xaxis, no trigonometric calculations are necessary. The tangent is p/q and the code can be generated directly using the schemes illustrated in figures 2 a and b. The sine and cosine can be derived from pythagorean relationships with  $\sqrt{p^2 + q^2}$ . Taking reciprocals requires no calculation; one simply interchanges stretching and shrinking. Though these calculations are more complex than addition, they involve small integers and need only be performed once, i.e., to generate four codes, regardless of the number of cells in the grid.

#### IV. Overview of Geometric and Complexity Considerations in a Parallel Computation Schema

Geometrically, DAT's appear to be a valid alternative to matrix multiplication for applying linear transformations. In sequential implementations such as those which generated the illustrations just presented, however, each matrix operation is replaced by several additions, somewhat offsetting the possible advantage of algorithm simplicity by increasing computation time. The following vector oriented parallel computation schema exploits DAT characteristics to permit speedups by several orders of magnitude. The design depends on the fact that all DAT's are characterized by the summation of grey values from cells in a restricted neighborhood which is

oriented in the same direction (either horizontal or vertical) for all cells on the grid. Thus, computations for cells which are neighbors perpendicular to this direction can be carried out simultaneously without interaction. Consider the example the stretching process illustrated in figure 4. Summation neighborhoods are horizontally oriented; e.g., the grey value of any cell in column three in the new picture is the average of values from columns three and two (the latter twice) in the original picture. This same weighting rule could be applied to all cells in that column in a single step. The design thus calls for a vector of identical accumulators, each vector component representing a cell in the column of the new picture. Computational capabilities required include addressing a small number of neighboring vectors and adding them up (preserving vector component independence). As the vector of accumulators looks at successive columns, neighborhood shape (weighting rule) changes according to the straight line code for the stretching ratio. For example, in figure 4 column four of the new picture receives contributions only from column three of the original picture.

A reasonably high resolution picture consisting of 1000 x 1000 pixels would require a processing vector of length 1000. Factors vitally important to practical LSI implementation are identical structure and weighting rules for each vector component (redundancy) and complete avoidance of thousand-fold construction of either multiplication hardware or interconnection between components [5]. The thousand-fold speedup afforded by vector organization could reduce computation time from a half-minute per frame (i.e., thirty microseconds, per pixel) to thirty milliseconds, well within the range of real-time animation of arbitrarily rich grey-scale pictures consisting of a million pixels. Such speeds are inconceivable with current computer graphics techniques which matrix multiply coordinate lists. Similar transformation speeds are essential (and achievable) for real-time robot visual perception. The weighted averaging capabilities of this design can also be used to implement smoothing, edge detection and enhancement, and other conventional local picture processing operations at high speed.

A variety of potential applications for broader than computer graphics and image processing are possible because DAT's are the basis of a new kind of computational geometry which converges to affine Euclidean geometry. This digitized geometry is well matched to the discrete nature of digital computation and should be useful in many areas of applied mathematics. For example, in the numerical solution of partial differential equations by relaxation on uniform grids, linear changes of coordinates can be rapidly effected without redefining the grid. This might be useful when boundary geometry or wave propagation directions are approximated by straight line paths making arbitrary angles with grid parallels. Many promising theoretical areas of investigation are suggested as well. These include extension to digitized projective geometry, curvilinear coordinates, higher dimensional spaces, and many other areas traditionally described in terms of

continuity. There are some fundamental differences between the continuous approach and the digitized approach presented here. One example is the use of lines (digitized) rather than points as the fundamental objects manipulated by computation. Though duality between these elements is well known [4] applications conventionally involve point manipulation. With DAT's, the line codes correspond to scan paths in arbitrary directions whose discontinuities resulting from digitization are smoothed by averaging (pseudo-convolution). The quantized geometry of the grid yields an "uncertainty principle" which corresponds to the inability to localize points in any neighborhood smaller than a grid cell, an inherent constant of the system. While this would be intolerable in continuous geometry, it simplifies the computations of our "transformational" geometry using DAT's.

#### Acknowledgements

Professor Rothstein embodied elements of geometry, number theory, approximation theory, information theory, ergodic theory, and theory of formal languages in a clear notation in the design of the straight line code. The DAT application presented here is one of many possible applications. I am deeply indebted to him for the code and exploration of related worlds during and after my Ph.D. dissertation research under him.

I am also indebted to Bernard Shunfenthal who as a student of mine at New York University converted my conjectures about DAT's into computer programs for generating and transforming greyscale overprint pictures. These not only visually confirmed the feasibility of the method but gave me a great deal of intellectual and aesthetic satisfaction. Some of the products of his work are shown in the figures illustrating transformations of test patterns. The cat is an overprint version of a digitized picture of Sam Harbison's cat "Schopenhauer". The deck was provided to me by Leonard Vanek, formerly associated with the Princeton picture processing group but now at The Courant Institute. The blow-up of the eye was executed by Hartsell Teagle at Old Dominion University.

#### References

- E. G. Johnston and A. Rosenfeld, "Geometrical Operations on Digitized Pictures" in B. Lipkin and A. Rosenfeld (eds.), <u>Picture</u> <u>Processing and Psychopictorics</u>, Academic Press, New York, (1970), pp. 217-240.

- [2] J. Rothstein and C. F. R. Weiman, "Parallel and Sequential Specification of a Context Sensitive Language for Straight Lines on Grids", <u>Computer Graphics and Image</u> <u>Processing</u>, Vol. 5, (March, 1976), pp. 106-124.

- [3] C. F. R. Weiman and J. Rothstein, <u>Pattern</u> <u>Recognition by Retina-Like Devices</u>, Computer and Information Science Dept., Ohio State University, OSU-CISRC-TR-72-8,

(AD 214 665/2), (1972), 154 pp.

- [4] A. Tuller, <u>A Modern Introduction to Geometries</u>, van Nostrand, New York, 1967, 201 pp.

- [5] B. R. Borgerson, "The Viability of Multimicroprocessor Systems", <u>Computer</u>, (IEEE Computer Society), Vol. 9, (January, 1976), pp. 26-30.

- [6] C. F. R. Weiman and J. Rothstein, "Polyautomaton Design for Recognizing Certain L System Languages by Parallel Computation", in Proceedings of 1975 Sagamore Computer Conference on Parallel Processing, Syracuse University and IEEE Computer Society (1975), pp. 168-170.

- [7] E. Artzy, J. A. Hinds, and H. J. Saal, "A Fast Division Technique for Constant Divisors", <u>Comm. of the ACM</u>, Vol. 19, (February 1976), pp. 98-101.

Figure 2: Code Generating Hardware

b) Shrunk Version

c) Stretched Version

#### Figure 5a: Illustration of Digitized Stretching

#### Figure 5b: Illustration of Digitized Shearing

Figure 6: Digitized Cat

Figure 7: Digitally Magnified Cat's Eye

ENHANCEMENT OF COMPUTING POWER IN MULTIPROCESSOR SYSTEMS FOR PROCESSING OF DIGITIZED PICTURES

K. Vorgrimler Forschungsgesellschaft für Angewandte Naturwissenschaften e.V. (FGAN) Forschungsinstitut für Informationsverarbeitung und Mustererkennung (FIM) 7500 Karlsruhe 1, Breslauerstr. 48 W. Germany

Abstract -- There is an increasing trend to solve picture-processing tasks on computers. The computation of local homogeneous window operations (convolution) tends to be impractical when a conventional computer is used because of the resulting time requirements. A structurally programmable multiprocessor is able to solve these tasks in one to two orders of magnitude faster. The principle of operation of the system and the individual processor are presented.

#### Introduction

Pictures serve as the primary information in a great variety of fields of interest for scientific research. Examples are the area of both bio- and/ or human medicine with cellular analysis or evaluation of X-ray-pictures. Another important field of application of picture processing techniques is connected with various satellite programs, where weather forecast, surveillance of industrial emission or vegetation etc. are the aims of picture interpretation.

Usually picture processing is dividable into five functionally different steps:

- picture scanning and digitizing

- picture preprocessing

- feature extraction

- feature analysis

- classification.

One major problem in this processing chain is the almost unrealistic computing time or necessary computing power in the domain of picture preprocessing. Using a conventional uni-processor to perform these tasks results in computing times of a few minutes to several hours depending on the algorithm and picture size.

With a special multiprocessor configuration actually being constructed at FIM, the implementation of many preprocessing algorithms proves to be faster by one to two orders of magnitude compared with the use of a conventional computer for the same task.

#### Local picture processing

Generally there are two mathematical techniques available for the implementation of picture preprocessing principles like spatial filtering. In a computer a picture is usually represented by a twodimensional point-matrix of grey-levels. One technique - convolution - is applied directly in this grey-level-domain whereas the second technique is applied in the so-called frequency-domain. This domain is obtained after the application of an integral transform e.g. Fouriertransform to both the grey-level picture and the respective filter. The philosophy of this technique is that relatively complex operations like correlation in the frequency domain can be obtained by simple matrix multiplications. This technique has attained a practicable aspect after the presentation of the Fast Fourier Transform algorithm by Cooley and Tukey.

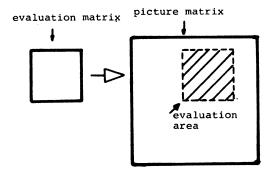

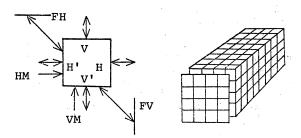

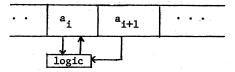

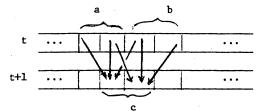

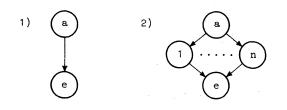

In local picture processing a special application dependent evaluation matrix is applied to a picture area of corresponding size (fig. 1).

#### fig. 1: Local picture processing

Fourier techniques are used in such cases where the evaluation matrix covers a great picture area or the entire picture. But in contrast to the advantages of this technique there are mainly two grave limitations:

- In addition to the fast matrix multiplication three time-consuming transformations are necessary: picture transformation, filter transformation and the transformation of the product back to the original domain.

- Due to the linearity of the transform the use is restricted to linear operations whereas in many picture preprocessing applications nonlinear logical operations or thresholding are highly efficient.

In the grey-level domain most operations are socalled window operations. These simple local operations have the following properties:

- The window (evaluation area) implies a relative small neighbourhood e.g. a square picturesubmatrix of 3x3 up to 11x11 picture elements.

- Window operations are position-invariant or homogeneous which means that the evaluation function remains unchanged when the window is shifted point by point over the entire picture.

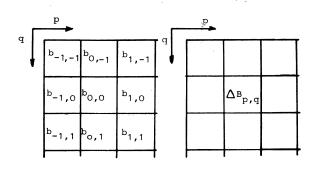

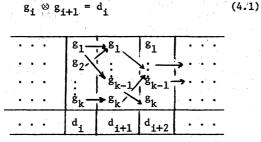

As a simple example an algorithm known as "stroke difference" is presented which leads to a "derivative" of a given picture B. With the submatrix-notation in fig. 2 the stroke difference is given by

(1)

$$\Delta B_{pq} = \frac{1}{2} \left[ \Delta B_{pq} + \Delta B_{pq} \right]_{x}$$

٨B

where

$$\Delta B_{pq_{x}} = \frac{1}{3} | (\underline{b}_{1,-1} + \underline{b}_{-1,0} + \underline{b}_{-1,1}) - (\underline{b}_{1,-1} + \underline{b}_{1,0} + \underline{b}_{1,1}) |$$

$$\Delta B_{pq_{y}} = \frac{1}{3} | (\underline{b}_{-1,-1} + \underline{b}_{0,-1} + \underline{b}_{1,-1}) - (\underline{b}_{-1,1} + \underline{b}_{0,1} + \underline{b}_{1,1}) |$$

As depicted in fig. 2 the result is related to a position within the resulting-matrix which corresponds to the position of the central element of the window in the original picture-matrix. The edge-elements in the resulting-matrix in fig. 3b are supposed to be filled with zeros.

#### fig. 2: Notation within a 3x3 window

a) originals (B)

b) derivatives ( $\Delta B$ )

#### fig. 3: Stroke-difference applied on picture B

Fig. 3a shows an aereal photo and fig. 3b the result after the evaluation of the stroke-difference algorithm. The resulting values of the stroke difference are displayed as grey levels.

#### Cascading of window operations

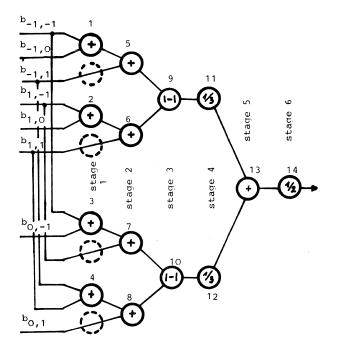

To exploit a given analytical expression with regard to the degree of its inherent parallelism the simplest way is to depict the corresponding computing graph. For the simple expression given in (1) this is shown in fig. 4.

#### fig. 4: Cascading of stroke difference

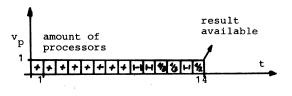

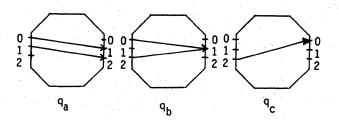

The evident parallelism in a computing graph usually is not exploited in practice. The user of a conventional computer streches the parallelism into a task suitable for a one-at-a-time hardware. Assuming for simplicity that each of the operations within the circles in fig. 4 require one timeunit of occupation in an uni-processor-equipment, a space-time diagram results as depicted in fig. 5.

fig. 5: Space-time diagram for one processor On the other hand the minimum processing-time

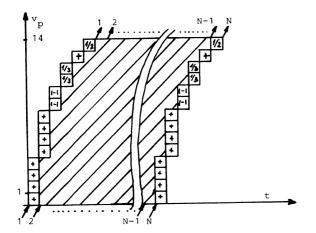

is obtained when the problem-inherent parallelism could be covered by an appropriate hardware multiplicity (fig. 6).

fig. 6: Complete coverage of parallelism

Note that the coverage in the sense of fig. 6 requires to redefine the conception of parallelism. In array computers a number of processors with identical properties work on a set of multiple data. In the complementary pipeline computer a single data stream is submitted to a sequence of operations within the processors forming the pipeline. In this case the processors work simultaneously on the single data stream where data coexist within the pipeline at a different processing state. By this way a kind of pseudo-parallel processing - better simultaneous processing - takes place. When data are available on the respective data buses (fig. 4) processors 1 to 4 can start simultaneously with the addition of their input-data. In the space-time diagram (fig. 6) this fact is represented by the occupance of 4 units in the first time-interval. When the addition is completed these processors can transmit their results to the units 5,6,7 and 8 respectively etc. Note that the final result is available after a "filling time" of 6 time-units corresponding to the 6 stages in the cascade.

The next input data can be offered to the system after the first time interval when the four "pseudo-processors" represented by dotted circles (fig. 4) are inserted. These processors are simple buffer-registers capable of holding the data during one time interval to avoid conflicts. Note that without the buffers their respective input data could not be changed until stage 2 would have completed the operation. Now the first processors can start operating on the second data-set when the following stages are still working on the first etc. This results in the same effect as in linear pipelines, namely that results are available in the same rate as input data are supplied.

The configuration shown in fig. 4 could be realized and fix-wired for the given algorithm. Beyond that provisions must be made to control the data flow and the synchronisation of the different processing units. Under the aspect of flexibility this solution would be a grave restriction and would lead to an immense number of special circuitry. Although this method cannot be excluded for a set of frequently used operations, a more flexible system requires a programmable structure. This means that the individual processor-properties and their mutual interconnection must be controllable by a program.

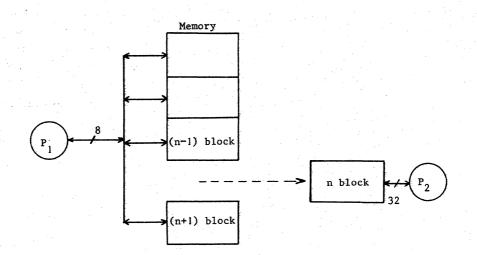

#### The Flexible Multi-Pipeline-Processor-System (FMPP)

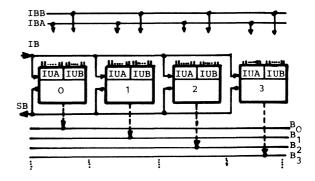

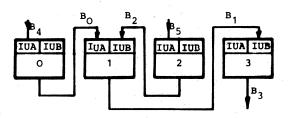

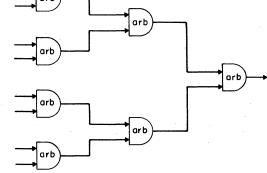

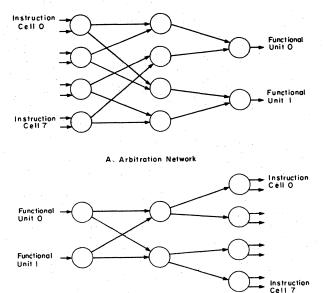

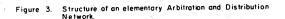

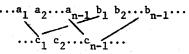

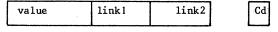

The system consists of a set of (max. 64) originally isolated processors and a set of data connections (B $_{0}$ ...B $_{1}$ ). Four of these processors are shown in fig. 7.1 At the output each processor is associated to a single of these data paths as indicated by dotted lines.

fig. 7: 4-Processor-System (non-programmed)

Additionally two data buses (IBA, IBB) are available. The buses IB and SB are common to all processors. IB serves to transmit the instructions to the individual processors, SB retransmits selectable internal processor status. The buses cam uniquely be used to transport information in the directions indicated by arrows.

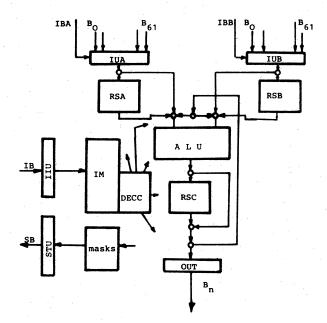

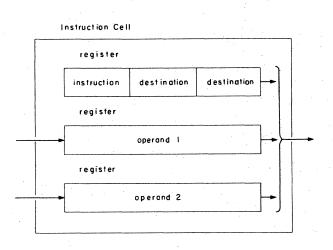

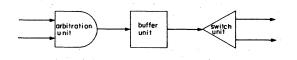

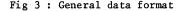

To establish a desired configuration the processors are sequentially programed via IB and the transferred instructions are stored within each processor. Each processor is realized as a threeaddress machine, this means that one single instruction contains two operand-source addresses and one operand destination address in addition to the operation code. Each processor has two independent input-control-units (IUA, IUB) affected by the destination parts of the instruction code. Each of these units is capable of establishing a connection to one of the existing data buses (e.g. 64) at a time. As the two input-units are independent, they can fetch two operands from two different buses simultaneously. The output is controllable by an output-mode-control code which allows results to be transfered directly via the corresponding bus or to be served in a processor-internal registerstack for further use.

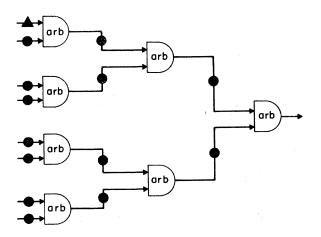

After the proper programming a configuration shown in fig. 8 can be "switched" together. It should be remarked that the interconnections shown are not necessarily everlasting and consisting simultaneously. The data are buffered at the end of the sending equipment (processor) and the transfer only takes place when the receiving unit (processor) requests data exactly on the respective bus.

# fig. 8: Processor interconnection after appropriate programming

Note that the buses IBA, IBB, SB and IB are omitted for simplicity. The interconnection shown could be used to implement the last three stages in the cascade in fig. 4 when the input-data are submitted via  $B_A$  and  $B_5$ .

It should be pointed out that the two additional data buses IBA, IBB are organized as selector buses. This was made as a concession to the preliminary use of the system and will be explained later.

#### Basic building blocks of each processor

Each of the processors within the multiprocessorsystem includes the subunits shown in fig. 7. Two input-units (IUA, IUB) control the transfer of data into the attached register stacks (RSA, RSB) or directly into the arithmetic logic-unit (ALU) respectively. The output (OUT) unit controls the transport of intermediate results via an output data-bus. Output data can be selected directly from the ALU or from a register-stack (RSC). Each processor has a bipolar instruction memory (IM) capable of holding up to 256 instructions. Attached to this memory is a decode and control unit (DECC) and an instruction-input unit (IIU) which control the loading of instructions into the memory via the instruction-bus (IB). A status-bus (SB) with a corresponding control unit (STU) serves to transmit some selectable internal conditions and is used for tests and processing control. It should be pointed out, that all connections for data or instructions from or to the processors environment are physically existent. The buses IBA, IBB, IB, SB are organized as selector-buses. This means that all processors within the system are connected in parallel to these buses and a transfer over them must be established logically. The data buses ( $B_0$  -  $B_{63}$ , IBA, IBB) at the inputs are data paths of the system-internal multi-bus-system. They are organized to handle the input or output of one single word from or to the environment, depending on the respective input- or output-instruction.

As the use is mainly restricted to picture processing tasks, the word-length is adapted to those requirements. All data buses are 8 bit wide with a set of supplementary control lines. The word-length of a single instruction is 32 bits subdivided in 4 bytes. The first byte controls the function of the ALU, whereas the next three bytes are the addresses of the selected input and output data sources respectively.

The technology used is standard and low Power Schottky-TTI, requiring a total of 200 packages per one processor.

#### fig. 9: Building blocks of processor n

#### Principle of operation

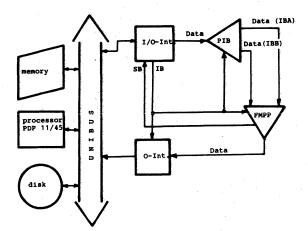

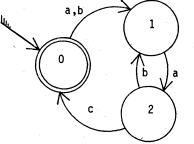

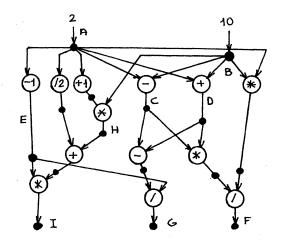

To explain the asynchroneous and data-controlled principle of operation a simplified evaluation-net-representation of a single processor will be used as depicted in fig. 8. Note that this representation here is used only as an informed descriptive method. For details the reader is referred to [1].

The actions within a processor can be described by a set of transitions (depicted as horizontal lines). Connected to these transitions there are a set of locations (circles) and resolution locations (hexagons).

Both data inputs of the processor are depicted as N-way-input-switches. The resolution locations  $r_A$  and  $r_B$  hold the address of the data path to be selected. The transition fires if the selected in-

put location (data bus) contains a valid data and location ( $b_A$ ,  $b_B$ ) is empty. After the transition, data are removed from the corresponding input locations and placed on the output locations ( $b_A$ ,  $b_B$ ). Depending on the values of the resolution locations  $r_{A1}$  and  $r_{A2}$  and the contents of the associated locations, the firing of the transitions  $a_1$  and  $a_2$  may be activated and hence the filling of  $b_{A1}$  and/ or  $b_{A2}$ .

These locations are the inputs for the processingtransitions a carrying out the data alteration placed in  $b_{C}$ . Transition  $a_{C}$  controls the way of the result either to locations internal to the processor ( $b_{TC}$ ) or to its environment ( $B_{n}$ ). It should be noted that in the formal abstraction of the processors activity given in fig. 8 one single instruction of the processor contains information concerning the following:

- value of  $r_A$ ,  $r_B$ ,  $r_{A1}$ ,  $r_{A2}$ ,  $r_C$

- content of b<sub>IA</sub>, b<sub>IB</sub>

- transition procedure of transition a

Depending on this information (instruction) the processors activity is either controlled by the content of the peripheral locations  $B_O^{-}B_{63}$ , IBA, IBB or the inner locations  $b_{IA}$ ,  $b_{IB}$ . Note, that the instruction is completed after the firing of transition  $a_c$  and a new instruction is fetched.

By this pipelining of transitions the processed activity is triggerable by the presence of valid data at the peripheral locations. At the input side the activity is interrupted until the firing conditions of  $a_A = a_B$  are fulfilled (content of selected location). At the output side the activity stops when the data at  $B_n$  has not been removed.

fig. 10: E-net representation of a single processor n

By this way the programs within the distributed processors contain not only their individual processing properties (a) but also the sources and destination of data. In addition to that no superior timing control mechanism must be provided to synchronize the active processors since data flow itself acts as start-stop-signal for the individual unit. Furthermore no internal clock is needed because each instruction consists of a chain of transitions with their individual firing conditions and time requirements and the new instruction is only initiated after the firing of a,

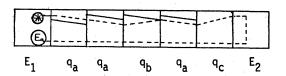

To compute a given window operation the user has to subdivide the entire task into a cascade as depicted in fig.4 with the notational understanding that there are a limited number of processors available. As a single processor is capable of holding up to 256 instructions this limitation is not grave. As in a linear pipeline the traversal time of a single task is mainly determined by the "slowest" pipeline segment. This fact also holds true in a "mixed" configuration, because due to the data dependent control no critical races can occur. The structure adapts itself to the slowest segment. Therefore as a general rule the task should be divided in a number of subtasks, each as small as possible (small number of instructions). As pipelining and parallel processing is combinable there is a high degree of freedom to handle the trade-off between the length of the subprograms and the number of processors to be used. Once the structure is fixed the user transforms it to the adequate processor configuration by programming each of the processors. The programs are delivered to the processors via the instruction bus (IB) in fig. 7. After the programming phase the structure is fixed and additionally a mechanism must be provided to deliver the input data to the configuration as well as to transfer the results back to the picture storage.

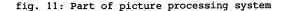

#### Realized system configuration

Fig. 9 shows the preliminary location of the FMPP as a peripheral equipment of a PDP 11/45 minicomputer.

In addition to the FMPP, 3 supporting modules are necessary. The input-output-interface (I/O Int.) delivers the programs to the submits and to the single processors within the FMPP via the instruction bus (IB) during the programming phase. After programming the properties of the system are fixed and processing is taking place according to the data-rate of picture-data transferred to and back from the system. The output-interface handles the transfer of the results back to the PDP's memory which acts as a buffer for the picture data normally stored on disks. The I/O-interface also serves to transfer selected status information from the processors back to the host computer.

In this mode of operation two difficulties arise:

- picture data can only be transferred serially via the UNIBUS so that the multiple stream of input data for the FMPP is not available di-

#### rectly;

- as the window is shifted point by point over the picture, each pixel belongs to n<sup>2</sup> different locations of the window, n being the dimension of the used submatrix. This would require to transport roughly (nxW)<sup>2</sup> pixels (N= dimension of picture) to the peripheral equipment;

A multiport semiconductor-memory actually being constructed at FIM is expected to be operational in late 1977. In order to get familiarized with the system the decision was made to put it to work preliminarily in the environment shown in fig. 9 by adding a third module. The programmable inputbuffer (PIB) spreads the single data stream. It essentially consists of a set of interconnectable (program controlled) shift registers. Each register row has a capacity to store 1024 pixels.

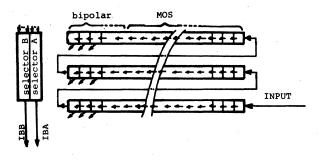

Each row consists of static shift registers realized in MOS-technology and a supplement of 16 registers in TTL-technology. These "tail"-registers are random accessable. In fig. 12 the interconnection of 3 rows is shown. This interconnection is chosen when an operation requires a 3x3 window. Instead of shifting the window over the picture, within the PIB the operation is inverted by shifting picture data below the fixed window. While the data input-rate is relatively slow due to the access time of the mass-storage (disk) the output data (window) can be transferred to the FMPP at high speed. This is done via the two previously mentioned selector-buses IBA, IBB according to a delivering-program stored within the PIB. The two buses have their own program-memory and transfer control units so that they can operate simultaneously. With the use of the PIB it is only necessary to transport picture data once to the peripheral equipment. When the shift registers within PIB are filled with 3 picture-rows (fig. 12) the operation can begin. The first result must be transported back via the output-interface, then a new input pixel activates the computation of the next result etc.

The transport of a picture with the size of 1024x 1024 to and back from the peripheral system requires roughly 10 seconds. This time results when the specifications of all the building blocks in fig. 11 are taken into consideration. The realized system is configurated so that all the window operations presently used or having been developped at FIM [2][3] can run in this time, when applied on a of the size mentioned. This fact correspicture ponds to a speed increase by a factor of 7 up to 300 when it is compared with the run times for the computation of the same algorithms on a CDC 3300 computer. The speed increase depends on the amount of parallelism of the given algorithm and the number of picture elements required within the submatrix for its computation. Note that some nonlinear operations like the stroke difference (1) do not use all pixels within the window.

#### Conclusion

Hardware parallelism and pipelining are combinable to cover a maximum of parallelism inherent to a given algorithm. Due to the data controlled mode of operation the desired structure can be established by programming the individual processors without the need of a special equipment to control the mutual data interconnections. The data flow in a cascade is unidirectional, so that the control units are relatively simple justifying the additional implementations of these units in each of the processors.

By adequate programming the FMPP can serve to overcome one of major problems in picture preprocessing, namely the unrealistic processing times necessary when conventional computers are used. From the user's point of view a great disadvantage is the fact, that for the moment almost all software support is missing, so that the programming is rather cumbersome. The future work will overcome this problem by developing software basing on a simple assembler at the single processors level. It should finally be noted that the software support must be provided by a general purpose host computer. Presently 3 processors have been realized. The system with a preliminary number of 16 individual processors is expected to be operational in early 1977.

#### REFERENCES

[1] G.J. Nutt "The formulation and application of evaluation nets"

> Comput.Sci.Group, Univ. Washington, Seattle, TR 72-07-02 1972

[2] F. Holdermann "Processing of Gray Scale H. Kazmierczak Pictures"

> Computer Graphics and Image Processing, Vol 1, No 1, 1972

[3] K. Vorgrimler "Zur Leistungssteigerung von Mehrprozessorsystemen für die Verarbeitung digitaler Bildinformation"

> Dissertation Fak. Elektrotechnik, Univ. Karlsruhe, 1976 (being printed presently)

# APPLICATION OF DISTRIBUTED PROCESSING \* TO THE PRODUCTION OF DIGITAL TERRAIN DATA

Dennis E. Moellman Defense Mapping Agency Washington, D. C. Robert A. Meyer Department of Electrical and Computer Engineering Clarkson College of Technology Potsdam, New York

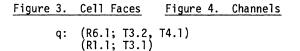

particular area form a product called a digital terrain data base.

described which forms an integrated system for the production of digital terrain data from stereo aerial photography. This system includes on-line processing of data collected by high-speed digitizing instruments, man-machine interactive editing capability, and a centralized processor for managing inter-processor data transfers. This paper analyzes the system requirements in terms of specific architectural features which must be provided. We describe the use of a SIMSCRIPT simulation to test the feasibility of the basic design concept. Simulation results were also used in determining design parameters such as the number of processors, memory size, and expected throughput rates. Significant characteristics of the system such as modularity and reliability are discussed.

Abstract -- A distributed computer network is

#### I. INTRODUCTION

In a recent paper [1] concerned with computer interconnection structures, Anderson and Jensen discuss the lack of published material describing the basis for design of these systems or making a comparative evaluation. This paper takes a step toward filling that need by presenting the design of a distributed computer network together with an analysis of the system requirements which led to this specific design. Our goal is not to describe the implementation details, but rather to provide the reader with a view of the design process and an understanding of the relationship between system requirements and the network architecture.

The distributed computer network (DCN) has been designed to solve a real-time system integration and data processing problem encountered in the production of digital terrain information by the Defense Mapping Agency (DMA). In a mapping sense, an aerial photograph represents a state-of-the-art high-density storage medium for storing terrain information. Two such photographs appropriately exposed comprise a stereomodel of the earth's surface from which three-dimensional terrain data can be extracted. The most efficient means for extracting such data is to digitize the analog information contained within each photograph so that the photographic density (gray shade) of each picture element (pixel) is represented by an integer. Sophisticated correlation algorithms coupled with perspective geometry calculations are employed to determine the three-dimensional relationship of a specific point to a reference datum. A collection of such points covering a

This work was supported by the Defense Mapping Agency Aerospace Center through Rome Air Development Center and the Post Doctoral Program. In order to meet an ever increasing demand for digital terrain data bases, DMA has sought to increase their productivity by utilizing digitizing instruments which operate automatically with little or no manual intervention. These newer digitizers are capable of operating between 10 and 40 times faster than the previously used manual instruments. The immediate problem resulting from such a change is the inability of the existing off-line, batch computer system to meet the increased processing load. The problem is further complicated by the additional requirements for manually prepared initiallization data and limited manual editing capability.

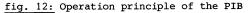

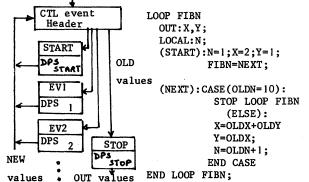

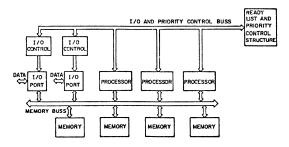

A block diagram of the DCN is shown in Figure 1. This system was proposed by the group at Clarkson College and has been accepted for implementation by DMA. At the present time detailed software specifications for the system are being written at Clarkson. The final design resulted from the contributions of several people at Clarkson, DMA and the Rome Air Development Center (RADC). In the remaining sections of this paper, we describe the operating environment, analyze the system requirements, and discuss the important characteristics of the design including the application of system modeling and simulation techniques to predict expected performance.

#### II. BACKGROUND

Digital terrain data bases are rapidly replacing conventional line maps. This is particularly true because advancements in computer technology have influenced navigational systems so that the application of digital terrain data is more economical and practical. Digital terrain data can now provide radar images for flight simulation and navigation by real time on-board correlation as well as terrain profiles between two points for flight planning and conventional contour maps [2].

Recognizing that present equipment could not effectively satisfy the increasing demand for digital terrain data, DMA contracted with Bendix Research Laboratories for the development, under the direction of RADC, of a new digitizing device, the Automatic Compilation Equipment (ACE). The prototype instrument consists of a conventional manual unit retrofitted with a laser scanner and a digital correlator consisting of two microprogrammable minicomputers. Based on new concepts in scanning and digitizing, the ACE is able to scan and digitize each pixel of a stereo pair of photographs, perform automatic digital correlation (image matching), and compute 58 terrain elevation profiles simultaneously. The collection rate is 250,000 points in approximately 10 minutes at a density of 6500 points/ square inch [2].

In order to achieve these rates an ACE must operate in an automatic mode which produces raw data in the form of irregularly spaced terrain profiles in a local coordinate system. The raw data must then be transformed to global geographic coordinates and interpolated to a uniform grid of elevation values.

Two difficulties with completely automatic digitizing are the inability of the machine to exactly track terrain peaks and valleys and the loss of correlation in adverse areas of the photograph. These problems could be solved by relying on partial manual operation; however, this would seriously degrade the overall efficiency of the ACE. An alternative formulated by DMA is the use of currently available, manual digitizing instruments to produce additional data for each stereopair of photographs. This additional data includes peaks and valleys, "fill-in" areas not digitized by an ACE due to poor correlation, and also certain information used by an ACE operator to reduce the setup time prior to ACE operation. Several of these manual digitizing instruments have been linked together with a host

minicomputer to form the pooled minicomputer system [3].

The ACE's and pooled minicomputer system may therefore be viewed as sources of raw input data which must be processed and edited in order to be acceptable to the user. The rate at which large volumes of data are being collected clearly indicates that off-line data transfers (such as magnetic tapes) and processing must be replaced with an integrated on-line system.

#### III. SYSTEM REQUIREMENTS

The operating environment described in the previous section provides a basis for determining the computational requirements of the proposed system. These requirements may be divided into five major functional tasks:

- 1) data collection

- 2) processing

- 3) editing

- 4) file management

- 5) job control.

Each of these tasks places specific demands on the system and thereby influences the overall architectural configuration. In this section, we analyze these requirements in terms of a general processing system and show how the DCN meets these demands.

Data collection consists of accepting input data from two distinct categories of sources: real time and non-real time. Real time input is received from each of two ACE's at the rate of 1600 words/second (16-bit words) per ACE. These transfers occur as 192-word blocks which must be received every 120 milliseconds. Failure of the collecting processor to perform the transfer within the stated time period results in loss of data.

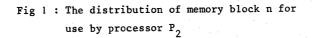

The second category of input data is produced by the pooled minicomputer system. This system contains sufficient local storage that a data transfer may be deferred until the collecting processor requests it. It should, therefore, be possible to use a single processor to receive input from all collection devices. This processor is called the input processor in the DCN (see Figure 1). During periods when one or both ACE's are not actively operating, the input processor requests the current backlog of input data from the pooled minicomputer system.

The processing task includes two basic operations which must be performed on the data. As described in Section II, the ACE output consists of terrain data samples giving a location and elevation, (x,y,z), in the local coordinate system of the stereophotographs. The first operation required is a coordinate transformation which maps the triple (x,y,z) into a geographic coordinate system. The transformation requires 22 multiplications and 20 additions using 32-bit floating point arithmetic and approximately 13 additional load and store instructions. Since the transformation is applied to every input data sample from an ACE, the system must be capable of executing about 3200 floating point instructions for each 192word block of 58 samples. In practice the system processing capability must be somewhat higher to allow for the overhead associated with the I/O operations. Of course, the transformation could be done in non-real time. However, in the next paragraph we present compelling reasons for providing sufficient speed to perform the transformation in real time.

The second operation to be performed is interpolation. Unlike coordinate transformation, the interpolation function requires all of the input samples in a neighborhood of the output point. Therefore, the data should be sorted prior to interpolation so that points within a neighborhood may be easily located. Since a pair of stereophotographs produces approximately  $5.0 \times 10^6$  words of data, a conventional batch sorting procedure could be very costly. The solution we have proposed sorts the data into tractable geographic regions as it is being

collected. Thus, the primary data structure for interim storage allows one to access a particular region of any geographic point within the domain of the stereophotography. Since the sort is performed on the basis of the geographic coordinates of a sample, it is necessary to execute the coordinate transformation as the data is collected and before the interim storage structure is built. The interpolation algorithm requires approximately 16N floating point operations per output point, where N is the number of input samples in the neighborhood of the output point. In a typical situation a pair of stereophotographs will cover  $7.5 \times 10^5$  output points with N = 8. The expected maximum operating rate of an ACE is one stereopair per hour giving a computational requirement for interpolation of  $2.7 \times 10^4$  floating point operations per second for each ACE.

To summarize the processing load on the system we find that each ACE demands the execution of  $5.4 \times 10^4$  floating point operations per second. These calculations do not include time required for sorting or I/O. In order to support at least two ACE's (and perhaps three in the future) with a reasonable safety margin in the timing, we partitioned the processing task in a natural way into two parallel operations, coordinate transformation and interpolation. As described previously coordinate transformation should be performed in real time as the data is collected and sorted; this operation is done by the input processor. A second processing capability is provided for interpolation. The interpolation processor could be either a single processor with an average floating point instruction time of less than 10 µsec. or two processors with appropriately slower hardware. The primary decision criterion is cost.

Editing of the input data is required after collection to check validity and to identify areas which require manual fill-in. Editing is also required after interpolation to insure overall consistency. Given the volume of data which must be examined it is necessary to automate as much of the editing task as possible. As data is collected it can be separated into two groups, good quality and poor quality. This separation is made on the basis of a correlation coefficient associated with each input sample and can be performed automatically. Additional

editing requires manual intervention and is performed with a man-machine interactive graphics facility consisting of several minicomputer controlled CRT displays. To service this facility requires data format conversions and selected subfile retrieval and update operations. These are performed in the DCN by the edit processor.

The most complex problem to be solved is data storage and management. A single typical file will consist of approximately  $5.\times10^6$  words. At any time, we expect about fifteen files to be active thus requiring  $7.5\times10^7$  words of readily accessible storage. Read/write requests may be generated by the collection, editing and interpolation tasks. Since these are concurrent operations, a means for coordinating simultaneous requests must be provided. A single file processor provides this capability in the DCN. Active files are stored on two 42M word disks with magnetic tape backup.

A second aspect of the data management problem concerns the organization of individual

files. Although the choice of data structure has not directly influenced the hardware features of the network architecture, it has been a consideration in the design of the software message handling system. Briefly, each file is composed of a two-level hierarchy of subfiles. The first level partitions the data by collection source and the second level by geographic region. Since a subfile is of variable length to allow for data addition or deletion, a convenient data structure is a linked list. Each item in the list is a block of 128 words corresponding to one disk sector. The bulk of messages between processors is data for either file storage or retrieval, and therefore a message consists of a variable number of 128-word blocks.

Job control is a system level task designed to meet not only the processing requirements of the operating environment, but also the needs of the computational system itself. For the DCN we have a collection of nearly autonomous processors, each performing a specific task. The goal of job control is to insure that a set of input data is processed according to a prescribed procedure and that efficient use of system resources is made. Since the file processor is the only centralized processor with access to all data, the job control task is executed in the file processor.

#### IV. SYSTEM CHARACTERISTICS

Within the context of [1], the DCN is a hybrid network. It most closely resembles the "star" architecture which is defined as a set of processors, indirectly connected through a centralized routing mechanism using dedicated message paths in a star shaped arrangement. In the DCN the central switch is a processor itself, and thus we have both direct and indirect processor-processor interconnection. However, from the job processing viewpoint, the file processor is transparent and serves only to direct the data flow. The analysis of system characteristics we give in this section will demonstrate the similarity of the DCN to a "star" architecture in terms of advantages and disadvantages.