OF THE

# **1988 INTERNATIONAL CONFERENCE**

ON

# PARALLEL PROCESSING

August 15-19, 1988

Vol. III Algorithms and Applications David H. Bailey, Editor

Sponsored by

Department of Electrical Engineering PENN STATE UNIVERSITY University Park, Pennsylvania

1988 INTERNATIONAL CONFERENCE Vol. III Algorithms and Applications **ON PARALLEL PROCESSING** Bailey

> THE PENNSYLVANIA STATE UNIVERSITY PRESS UNIVERSITY PARK AND LONDON

# OF THE

# **1988 INTERNATIONAL CONFERENCE**

ON

# **PARALLEL PROCESSING**

August 15-19, 1988

Vol. III Algorithms and Applications David H. Bailey, Editor

Sponsored by

Department of Electrical Engineering PENN STATE UNIVERSITY University Park, Pennsylvania

THE PENNSYLVANIA STATE UNIVERSITY PRESS UNIVERSITY PARK AND LONDON The papers appearing in this book comprise the proceedings of the meeting mentioned on the cover and title page. They reflect the authors' opinions and are published as presented and without change in the interests of timely dissemination. Their inclusion in this publication does not necessarily constitute endorsement by the editors, Penn State Press, or the Institute of Electrical and Electronics Engineers, Inc.

> Library of Congress Catalog Card Number 79-640377 ISSN 0190-3918 ISBN 0-271-00654-4 IEEE Computer Society Order Number 889 IEEE Catalog Number 88CH2625-2

Copyright © 1988 The Pennsylvania State University All rights reserved Printed in the United States of America

Additional copies may be obtained from: Penn State Press 215 Wagner Building University Park, PA 16802

### PREFACE

Interest in the field of parallel processing continues to climb. This trend is evidenced by the sharp increase in papers submitted to the International Conference on Parallel Processing during recent years:

| Papers<br>Submitted | Papers<br>Accepted                    | Percent                                                                                                                           |

|---------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 170                 | 65                                    | 57                                                                                                                                |

| <b>240</b>          | 136                                   | 57                                                                                                                                |

| 400                 | 170                                   | 43                                                                                                                                |

| 487                 | 174                                   | 36                                                                                                                                |

| 590                 | 173                                   | 29                                                                                                                                |

|                     | Submitted<br>170<br>240<br>400<br>487 | Submitted         Accepted           170         65           240         136           400         170           487         174 |

Although the number of submissions continues to increase, the number of accepted papers this year and in the past two years has remained relatively unchanged. This is due to the limitation imposed by the fixed number of hours available for the conference. As a result, a record number of papers had to be rejected. This year, the conference proceedings is being published in three volumes according to the subject category. The breakdown of submissions and acceptances in the three main categories of this conference is as follows:

|                             | Papers    | Papers   |         |

|-----------------------------|-----------|----------|---------|

| Category                    | Submitted | Accepted | Percent |

| Architecture                | 264       | 74       | 28      |

| Software                    | 144       | 43       | 30      |

| Algorithms and Applications | 182       | 56       | 31      |

Of the 173 papers that were accepted, 79 were accepted as regular papers and 94 were accepted as short papers. Many papers that normally would have been accepted as long papers were accepted as short papers in order to meet the maximum number of paper-sessions allotted for the conference.

Finding sufficient numbers of qualified reviewers was a particularly challenging task this year, due to the record number of submissions. Over 1,000 professionals in the field participated in this process. This year the process of selecting referees was simplified by the use of questionnaires, which were mailed to previous participants in the conference. The information on the completed questionnaires were entered into databases, which then allowed the conference chairmen to select reviewers qualified in fairly specialized fields. Even so, numerous papers were so highly specialized that custom selection of referees was still required. It appears that an even more detailed breakdown of specializations will be needed for these questionnaires in the future. Greater effort will also be required in the future to find additional reviewers to adequately evaluate the increasing numbers of submissions.

I wish to thank the management of the Numerical Aerodynamic Simulation Systems Division at NASA Ames for providing me the opportunity to serve on the program committee this year. I also wish to thank the following persons on our staff who assisted in selecting referees and in handling the correspondence: Liviu Lustman, Martin Fouts, Julie Swisshelm, Horst Simon, Creon Levit, Gina Riley, Saundra Ramirez, and Reina Trinwith. I wish also to thank Prof. Tse-yun Feng for his support and encouragement in this effort.

David H. Bailey NASA Ames Research Center Moffett Field, CA 94035

### LIST OF REFEREES

Abello, J. Abileah, R. Adams, G. B. Agrawal, D. P. Agrawala, A. Ahmad, M. O. Alaghband, G. Alexander, W. E. Altmann, E. Antony, R. U.S. Army Armstrong, J. Bailey, D. H. Bappana, R. V. Baru, C. K. Bastani, F. B. Berger, M. Berkling, K. Bermudez, M. E. Bhanu, B. Bhargava, B. Bhasker, J. Blelloch, G. Bodorik, P. Bose, P. Bourbakis, N. Bowyer, K. W. Braaten, M. E. Breitkreutz, T. IDA - SRC Brenner, A. E. Breuer, M. A. Browne, J. C. Bryant, B. Bryant, R. M. Buell, D. IDA - SRC Bui, T. D. Burn, R. Buzbee, B. L. NCAR. Cappello, P. R. Cargo, D. Carlson, D. A. IDA - SRC Carty, F. G. Cazes, A. Cerny, E. Chan, M. Y. Chan, T. Chandran, S.

U. C. Santa Barbara SRI International Purdue Univ. North Carolina St. Univ. Univ. of Maryland Concordia Univ. Univ. of Colorado North Carolina St. Univ. Carnegie Mellon Univ. Convex Computer Corp. NASA Ames Research Ctr. Univ. of Southern Cal. Univ. of Michigan Univ. of Houston Courant Inst. Svracuse Univ. Univ. of Florida Honeywell Research Ctr. Purdue Univ. Honeywell, Inc. MIT AI Lab. Tech. Univ. Nova Scotia IBM Watson Research Ctr. George Mason Univ. Univ. of South Florida G. E. Res. and Dev. Ctr. Univ. of Alberta Univ. of Southern Cal. Univ. of Texas Univ. of Alabama Birm. IBM Watson Research Ctr. Concordia Univ. Systems Control U. C. Santa Barbara U.S. Dept. of Defense Goodyear Aerospace Corp. IBM Watson Research Ctr. Univ. de Montreal Univ. of Texas at Dallas U. C. Los Angeles Univ. of Maryland

Chang, C. K. Chang, D. Chang, H. Chang, P. R. Chang, S. Chellappa, R. Chen, S. Chennagiri, R. K. Cherkassy, V. Christian, F. Chung, M. J. Coffman, E. G. Conroy, J. M. Cuny, J. E. Curoe, J. E. Cybenko, G. Cypher, R. Darema, F. De Forcrand, P. De Young, G. E. Dehne, F. Dekel, E. Despain, A. M. Dey, P. Diamond, M. D. Dixit, V. V. Downes, E. H. Dyer, C. R. Egecioglu, O. El-Sharkawy, M. Ellis, C. Eltgroth, P. Ercegovac, M. D. Eshaghian, M. M. Fahlman, S. E. Fang, Z. Fatoohi, R. Felten, E. W. Feo, J. Ferguson, D. Ferreira, A. G. Fiduccia, C. M. Fier, J. Finkel, R. Fornberg, B. Foulser, D.

Univ. of Ill. Chicago Univ. of Louisville Univ. of Miami Purdue Univ. Univ. of Maryland Univ. of Southern Cal. Univ. of North Carolina Univ. of Southern Cal. Univ. of Minnesota IBM Almaden Research Ctr. Michigan St. Univ. AT&T Bell Labs IDA - SRC Univ. of Massachusetts Mobil Corp. Tufts Univ. Univ. of Washington IBM Hawthorne Res. Lab. Cray Research Inc. Winchester, MA Carleton Univ. Univ. of Texas, Dallas U. C. Berkeley Univ. of Alabama Birm. FMC Corp. Univ. of Southern Cal. Reston, VA Univ. of Wisconsin U. C. Santa Barbara Bucknell Univ. Duke Univ. Lawrence Livermore Lab. U. C. Los Angeles Univ. of Southern Cal. Carnegie-Mellon Univ. Concurrent Comp. Corp. NASA Ames Research Ctr. Cal. Inst. of Tech. Lawrence Livermore Lab. Boeing Computer Serv. Grenoble, France G. E. Res. and Dev. Ctr. Ametek Lexington, KY Exxon Research and Eng. Yale Univ.

| The Area Mart          | NACA And Daniel Cha      |

|------------------------|--------------------------|

| Fouts, M. J.           | NASA Ames Research Ctr.  |

| Franklin, M.           | Washington Univ.         |

| Friesen, D.            | Texas A&M Univ.          |

| Fujimoto, R. M.        | Univ. of Utah            |

| Gallopoulos, E.        | Univ. of Illinois Urbana |

| Gao, G. R.             | McGill Univ.             |

| Gaushell, D. J.        | Westin Power Consultants |

| Gear, C. W.            | Univ. of Illinois        |

| Ghosh, A. K.           | Univ. of Iowa            |

| Goel, A.               | Ohio St. Univ.           |

| Goel, P.               | Univ. of Michigan        |

| Gonzalez, T. F.        | U. C. Santa Barbara      |

| Gorin, A. L.           | AT&T Bell Labs           |

| Graf, K.               | SRI International        |

| Greenbaum, A.          | New York Univ.           |

| Greening, D. R.        | Nashua, NH               |

| Grefenstette, J. J.    | Vanderbilt Univ.         |

| Grimes, R.             | Boeing Computer Serv.    |

| Guha, S.               | Univ. of Michigan        |

| Gunta, D.<br>Gupta, A. | Carnegie-Mellon Univ.    |

| Hac, A.                | AT&T Bell Labs           |

| Hachtel, G. D.         | Univ. of Colordo         |

| Hadlock, F. O.         | Tennessee Tech. Univ.    |

|                        |                          |

| Haghighi, M.           | Bradley Univ.            |

| Han, J.<br>Han, V      | Southern Illinois Univ.  |

| Han, Y.                | Univ. of Kentucky        |

| Hanson, F. B.          | Argonne National Lab.    |

| Heath, M.              | Oak Ridge National Lab   |

| Hewitt, C. E.          | MIT AI Lab.              |

| Ho, C.                 | Yale Univ.               |

| Hong, Y.               | U. C. Riverside          |

| Hume, D.               | Tennessee Tech. Univ.    |

| Hyatt, R.              | Univ. of Alabama Birm.   |

| Ibarra, O. H.          | Univ. of Minnesota       |

| Ipsen, I.              | Yale Univ.               |

| Iyengar, S. S.         | Louisiana St. Univ.      |

| JaJa, J.               | Univ. of Maryland        |

| Janakiram, V. K.       | North Carolina St. Univ. |

| Janardan, R.           | Univ. of Minnesota       |

| Janicki, R.            | McMaster Univ.           |

| Jones, J.              | Air Force Inst. of Tech. |

| Josephson, J. R.       | Ohio St. Univ.           |

| Kailath, T.            | Stanford Univ.           |

| Kamath, C.             | Digital Equipment Corp.  |

| Karabeg, D.            | U. C. San Diego          |

| Karp, A.               | IBM Scientific Ctr.      |

| Keller, R. M.          | Quintus Computer Sys.    |

| Kender, J. R.          | Columbia Univ.           |

| Kim, M. H.             | Michigan St. Univ.       |

| Kirkpatrick, S.        | IBM Watson Research Ctr. |

| -                      |                          |

|                        |                          |

Kocay, W. Kodeih, M. Koenig, E. C. Kosaraju, S. R. Kountanis, D. Kowalik, J. S. Krishnamoorthy, M. S. Krishnamurthy, B. Kruskal, C. Kumar, D. Kumar, V. Kung, H. T. Kung, S. Kurtzberg, J. Ladner, R. E. Lai, T. Lander, E. Lazowska, E. D. LeBlanc, T. J. Lee, C. S. G. Lee, D. L. Lee, S. Leiserson, C. E. Leite, T. R. Lesser, V. Leu, D. Lewis, J. Li, H. Li, X. Liao, Y. Lin, A. Lin, W. Liu, W. Livingston, M. L. Loganantharaj, R. Logothetis, G. Lowrie, M. B. Lubachevsky, B. D. Lustman, L. R. Lynch, N. A. Makhoul, J. Mandell, D. Manhardt, P. D. Mann, T. Marsland, T. A. Mattheyses, R. M. McMillin, B. M. Mei, G. Mesirov, J. P. Messerschmitt, D. G.

Univ. of Manitoba Rensselaer Poly. Inst. Univ. of Wisconsin Johns Hopkins Univ. Western Michigan Univ. Boeing Computer Serv. Rensselaer Poly. Inst. Tektronix Inc. Univ. of Maryland St. Univ. of New York Univ. of Texas Carnegie Mellon Univ. Princeton Univ. IBM Watson Research Ctr. Univ. of Washington Ohio St. Univ. Whitehead Inst. Univ. of Washington Univ. of Rochester Purdue Univ. Ohio St. Univ. Cornell Univ. MIT IMSL Univ. of Massachusetts Univ. of Houston Boeing Computer Serv. IBM Watson Research Ctr. Univ. of Alberta Digital Equipment Corp. Temple Univ. Pennsylvania St. Univ. North Carolina St. Univ. Southern Illinois Univ. Univ. of S. Louisianna Univ. of Florida Univ. of Illinois Urbana AT&T Bell Labs NASA Ames Research Ctr. MIT Lab for Computer Sci. BBN, Inc. Los Alamos National Lab COMCO, Inc. DEC Systems Research Ctr. Univ. of Alberta G. E. Res. and Dev. Ctr. Michigan St. Univ. North Carolina St. Univ. Thinking Machines Corp. U. C. Berkeley

Miller, G. L. Miller, R. Miller, T. K. Moceyunas, P. H. Moldovan, D. I. Molloy, M. K. Montry, G. Morgan, A. P. Morris, R. A. Morris, R. J. T. Mudge, T. Mueller, R. A. Mukherjee, A. Nakazawa, S. Nassimi, D. Natarajan, K. S. Newman-Wolfe, R. Ng, E. Nichols, K. M. Noga, M. T. Norton, A. Nuttal, L. A. O'Hallaron, D. R. O'Leary, D. P. Oh, S. J. Oliger, J. Omiecinski, E. Ortega, J. M. Otto, S. W. Ougouag, A. M. Ozguner, F. Pargas, R. P. Park, S. Patrick, M. L. Pawagi, S. Payne, T. H. Peng, S. Perry, R. J. Peskin, R. L. Peterson, J. L. Pham, Q. T. Pong, T. C. Prabhu, G. M. Pramanik, S. Quinn, M. J. Raefsky, A. Raghavendra, C. S. Ramachandran, V. Ramakrishnan, I. V. Ramamoorthy, C. V.

Univ. of Southern Cal. SUNY Buffalo North Carolina St. Univ. Univ. of Colordo Univ. of Southern Cal. Univ. of Texas Sandia National Labs General Motors Res. Lab. U. S. Dept. of Defense AT&T Bell Labs Univ. of Michigan Colorado St. Univ. Univ. of Cent. Florida MARC Analytical Res. Univ. of Delaware IBM Watson Research Ctr. Univ. of Florida Oak Ridge Natl. Labs AT&T Bell Labs Lockheed Palo Alto IBM Watson Research Ctr. Univ. of Utah G. E. Res. and Dev. Ctr. Univ. of Maryland Syracuse Univ. Stanford Univ. Georgia Inst. of Tech. Univ. of Virginia Cal. Inst. of Tech. Univ. of Illinois Urbana Ohio St. Univ. Clemson Univ. North Carolina St. Univ. Duke Univ. SUNY Stony Brook U. C. Riverside Univ. of Maryland BC Villanova Univ. Rutgers Univ. MCC BNR, Canada Univ. of Minnesota Iowa St. Univ. Michigan St. Univ. Univ. of New Hampshire Palo Alto, CA Univ. of Southern Cal. Univ. of Illinois Urbana SUNY Stony Brook U. C. Berkeley

Ramesh, K. Univ. of Texas Ranka, S. Univ. of Minnesota Rao, V. N. Univ. of Texas Reddy, S. M. Univ. of Iowa Reed, D. A. Univ. of Illinois Urbana Reeves, A. P. Reynolds, P. F. Rivest, R. L. MIT Robertson, G. G. Robinson, J. Rodrigue, G. U. C. Davis Rogers, E. H. Ruiu, L. A. Griffis AFB Saad, Y. Sahni, S. Saltz, J. Yale Univ. Sangiovanni-V, A. Sanz, J. L. C. Sarrafzadeh, M. Sawafzadeh, M. Schaper, G. A. Schwetman, H. MCC Seager, M. Sen, A. Sen, S. Sengupta, A. Shaffer. P. Shannon, G. E. Shields, M. W. Shokooh, A. Shyu, W. C. H. Simmes, S. D. Simon, H. D. Sinclair, B. Rice Univ. Singhal, M. Somani, A. K. Sorensen, D. Sridhar, M. A. Srimani, P. K. Srinidhi, H. N. Starzyk, J. Ohio Univ. Stiles, G. S. Stojmenovic, I. Stolfo, S. J. Stotts, D. Stout, Q. F. Strader, R. Strong, R. Stunkel, C. B. Suk, M.

Univ. of Illinois The Univ. of Virginia Thinking Machines Corp. IBM Watson Research Ctr. Rensselaer Poly. Inst. Univ. of Illinois Univ. of Minnesota U. C. Berkeley IBM Almaden Research Ctr. Northwestern Univ. Northwestern Univ. Univ. of Central Florida Lawrence Livermore Lab. Arizona St. Univ. Univ. of Alabama Univ. of South Carolina G. E. Res. and Dev. Ctr. Purdue Univ. Univ. of Kent, GB Tennessee Tech. Univ. Old Dominion Univ. Science Appl. Inc. NASA Ames Research Ctr. Ohio St. Univ. Univ. of Washington Argonne National Lab Univ. of S. Carolina Southern Illinois Univ. Univ. of Cent. Florida Utah St. Univ. Univ. of Miami Columbia Univ. Univ. of Maryland Univ. of Michigan Texas A&M Univ. IBM Almaden Res. Ctr. Univ. of Illinois Urbana Syracuse Univ.

| a 14 T                  |                          |

|-------------------------|--------------------------|

| Suzuki, I.              | Univ. of Wisconsin       |

| Swarztrauber, P.        | NCAR                     |

| Swisshelm, J. M.        | NASA Ames Research Ctr.  |

| Tang, W.                | Univ. of Waterloo        |

| Tanik, M. M.            | Southern Methodist Univ. |

| Tao, L.                 | Univ. of Pennsylvania    |

| Tham, K. Y.             | Mentor Graphics Corp.    |

| Thomborson, C. D.       | Univ. of Minn. Duluth    |

| Tokuta, A. O.           | Univ. of South Florida   |

| Tomboulian, S. J.       | NASA Langley Res. Ctr.   |

| Tong, Z.                | Univ. of Minnesota       |

| Tsin, Y. H.             | Univ. of Windsor         |

| Turner, C. J.           | Science Appl. Inc.       |

| Tymann, P. T.           | SUNY Oswego              |

| Ursein, Á.              | Los Angeles, CA          |

| Van Loan, C.            | Cornell Univ.            |

| Varman, P.              | Rice Univ.               |

| Venkatesan, S.          | Univ. of Minnesota       |

| Vernon, M. K.           | Univ. of Wisconsin       |

| Vishwanathan, S.        | Univ. of South Carolina  |

| Visvanathan, V.         | AT&T Bell Labs           |

| Wagar, B.               | Univ. of Michigan        |

| Wagar, B.<br>Wah, B. W. | Purdue Univ.             |

| Waid, B.                | Glen Ellyn, IL           |

|                         | Southern Illinois Univ.  |

| Wainer, M.              |                          |

| Walicki, J.             | Colorado St. Univ.       |

| Walton, S.              | Cal. St. Northridge      |

| Wang, C. Y.             | Southern Illinois Univ.  |

| Wang, C.                | Cal. St. Sacramento      |

| Waramahaputi, J.        | Univ. of S. Louisiana    |

| White, W.               | Ohio St. Univ.           |

| Willebeek-LeMair, M.    | Cornell Univ.            |

| Winter, C. L.           | Science Appl. Inc.       |

| Witten, M.              | Univ. of Louisville      |

| Wu, C.                  | Univ. of Col. Denver     |

| Wunderlich, M. C.       | U.S. Dept. of Defense    |

| Young-Myers, H.         | Columbia, MD             |

| Yu, K.                  | Univ. of Alabama Birm.   |

| Zargham, M.             | Southern Illinois Univ.  |

| Zeigler, B. P.          | Univ. of Arizona         |

| Zeigler, G. M.          | Hewlett Packard          |

| Zhang, C. N.            | North Carolina A&T Univ. |

| Zhang, H.               | Temple Univ.             |

| Zhao, F.                | MIT                      |

| Zyda, M. J.             | Naval Postgrad. School   |

|                         | -                        |

1

## AUTHOR INDEX

Agrawal, D. P. 69 Alaghband, G. 177Alexander, W. E. 124Allison, D. C. S. 165Altmann, E. 198 Armstrong, J. 161Atwood, G. H. 120 Baheti, R. S. 108Bermudez, M. E. 151Blelloch, G. 218Braaten, M. E. 243Breitkreutz, T. 198 Browne, J. C. 1 Burdick, S. 251Chan, M. Y. 295 Chang, P. R. 290 Chang, S-C. 9 Chang, S-C. 18 Chen, G-H. 112Cuny, J. E. 141Cypher, R. 308 Diamond, M. . 272Doshi, K. 202Fatoohi, R. 235Foulser, D. 42Frederickson, G. N. 282Fujimoto, R. M. 34 Gao, G. R. 47 Gao, G. R. 181 Goel, A. 156Greenberg, M. 141 Grosch, C. E. 235Hachtel, G. D. 133Han, Y. 194 Hanson, F. B. 117Harimoto, S. 165Ho, H. F. 112Huang, Y. M. 26Hudson, T. F. 173Ibarra, O. H. 190 Igaraski, Y. 194 JaJa, J. 9 JaJa, J. 18 Janakiram, V. K. 69 Janardan, R. 282Josephson, J. R. 156Jun, M. S. 169

| Kim, J. H.              | 124  |

|-------------------------|------|

| Kim, M. H.              | 76   |

| Kim, S. J.              | 1    |

| Kimbel, J.              | 272  |

| Kumar, V.               | 128  |

| Kumar, V.               | 207  |

| Kumar, V.<br>Lander, E. | 257  |

| Lee, C. S. G.           | 290  |

| Li, X.                  | 223  |

| Lin, S. H.              | 112  |

| Lingas, A.              | 304  |

| Little, J. J.           | 218  |

| Logothetis, G.          | 151  |

| Madala, S.              | 62   |

| Marsland, T. A.         | 198  |

| Mehrotra, R.            | 69   |

| Mesirov, J. P.          | 257  |

| Moceyunas, P. H.        | 133  |

| Moona, R.               | 227  |

| Nandy, S. K.            | 227  |

| Newhouse, J.            | 272  |

| Newman-Wolfe, R.        | 151  |

| O'Hallaron, D. R.       | 108  |

| Park, S-M.              | 124  |

| Peng, S-T.              | 169  |

| Peng, S-T.              | 173  |

| Pong, T-C.              | 190  |

| Pramanik, S.            | 76   |

| Qu, X.                  | 223  |

| Rajagopalan, S.         | 227  |

| Ramesh, K.              | 128  |

| Ranka, S.               | 84   |

| Ranka, S.               | 92   |

| Ranka, S.               | 212  |

| Rao, V. N.              | 128  |

| Rao, V. N.              | 207  |

| Roberts, J. B. G.       | 230  |

| Sadayappan, P.          | 54   |

| Sadayappan, P.          | 156  |

| Sahni, S.               | 84   |

| Sahni, S.               | 92   |

| Sahni, S.               | 212  |

| Sanz, J.                | 308  |

| Sarrafzadeh, M.         | 26   |

| Schwetman, H.           | 251  |

| Sheu, J. P.             | 112  |

| Simmes, S. D.           | 146  |

| Similion, 5. D.         | - 10 |

|   | Sinclair, J. B.  | 62  |  |

|---|------------------|-----|--|

|   | Singhal, M.      | 186 |  |

|   | Sohn, S. M.      | 190 |  |

|   | Sridhar, M. A.   | 299 |  |

|   | Stojmenovic, I.  | 100 |  |

|   | Stout, Q. F.     | 104 |  |

|   | Stunkel, C. B.   | 264 |  |

|   | Sugihara, K.     | 14  |  |

|   | Suzuki, I.       | 14  |  |

|   | Taylor, W.       | 257 |  |

|   | Thomas, S. J.    | 47  |  |

|   | Turner, C. J.    | 146 |  |

|   | Varman, P.       | 202 |  |

|   | Vishwanathan, S. | 299 |  |

|   | Visvanathan, V.  | 54  |  |

| , | Ward, J. S.      | 230 |  |

|   | Watson, L. T.    | 165 |  |

|   | Whelan, M.       | 181 |  |

|   | Yum, T. K.       | 181 |  |

|   |                  |     |  |

# TABLE OF CONTENTS

| Preface       iii         List of Referees       iv         Author Index       viii                                     |

|-------------------------------------------------------------------------------------------------------------------------|

| SESSION 1C: Computational Complexity                                                                                    |

| <ol> <li>(R) A General Approach to the Mapping of Parallel Computations Upon<br/>Multiprocessor Architectures</li></ol> |

| 2. (S) Parallel Algorithms for River Routing                                                                            |

| 3. (S) Nearly Optimal Clock Synchronization Under Unbounded Message<br>Transmission Time                                |

| SESSION 2C: Applications I                                                                                              |

| 1. (R) Parallel Algorithms for Channel Routing in the Knock-Knee Model                                                  |

| <ul> <li>2. (R) A Parallel Algorithm for Minimum Dual-Cover with Application to<br/>CMOS Layout</li></ul>               |

| 3. (R) Lookahead in Parallel Discrete Event Simulation                                                                  |

| SESSION 4C: Numeric Algorithms I                                                                                        |

| 1. (R) A Blocked Jacobi Method for the Symmetric Eigenproblem                                                           |

| <ul> <li>2. (R) An Optimal Parallel Jacobi-Like Solution Method for the Singular Value<br/>Decomposition</li></ul>      |

| 3. (R) Modeling and Optimal Scheduling of Parallel Sparse Gaussian Estimation                                           |

| SESSION 5C: Non-Numeric Algorithms I                                                                                    |

| 1. (R) Performance of Parallel Partitioning Algorithms                                                                  |

| <ol> <li>(R) A Randomized Parallel Branch and Bound Algorithm</li></ol>                                                 |

| 3. (R) Generalized Parallel Processing Model for Database Systems                                                       |

SESSION 6C: Image Analysis and Geometry I

| 1. | (R) Image Template Matching on SIMD Hypercube Multicomputers                                                          |

|----|-----------------------------------------------------------------------------------------------------------------------|

| 2. | (R) Image Template Matching on MIMD Hypercube Multicomputers                                                          |

| 3. | (S) Computational Geometry on a Hypercube                                                                             |

| 4. | (S) Constant-Time Geometry on PRAMs                                                                                   |

| S  | ESSION 7C: Applications II                                                                                            |

| 1. | (S) Parallel Implementation of a Kalman Filter on the Warp Computer                                                   |

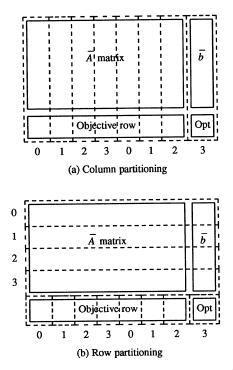

| 2. | (S) Solving Linear Programming on Fixed-Size Hypercubes                                                               |

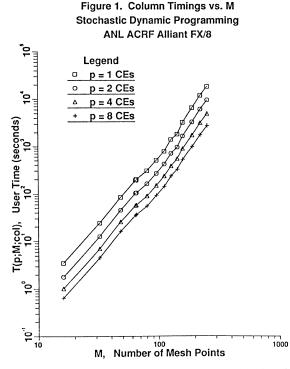

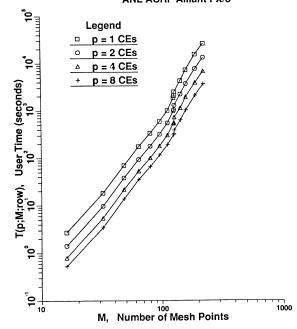

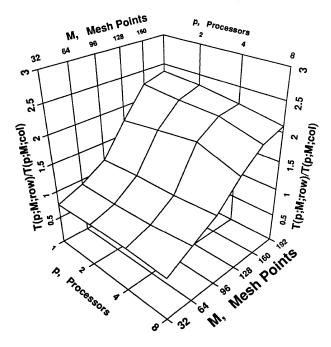

| 3. | (S) Parallel Computation for Stochastic Dynamic Programming: Row Versus<br>Column Orientation                         |

| 4. | (S) Parallel Langrangian Interpolation                                                                                |

| 5. | <ul> <li>(S) A New Approach to the Implementation of Multidimensional Signal</li> <li>Processing Algorithms</li></ul> |

| 6. | (S) Parallel Depth First Search on a Ring Architecture                                                                |

| S  | ESSION 8C: Artificial Intelligence                                                                                    |

| 1. | (R) Parallel Algorithms for Answering the Tautology Question                                                          |

| 2. | (S) Parallelism in Knowledge-Based Systems with Inheritance                                                           |

| 3. | (S) Associative Memories on the Connection Machine                                                                    |

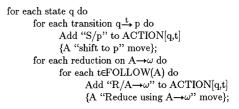

| 4. | (S) Parallel Generation of LR Parsers                                                                                 |

| 5. | (S) Concurrent Design of Composite Explanatory Hypotheses                                                             |

| S  | ESSION 9C: Numeric Algorithms II                                                                                      |

| 1. | (S) Algorithm and Performance Notes for Block LU Factorization                                                        |

| 2. | (S) The Granularity of Parallel Homotopy Algorithms for Polynomial Systems<br>of Equations                                   |

|----|------------------------------------------------------------------------------------------------------------------------------|

| 3. | (S) A New VLSI 2-D Systolic Array for Matrix Multiplication and Its Applications 169                                         |

|    | S-T. Peng and M. S. Jun (U. of Maryland B.C., USA)                                                                           |

| 4. | (S) Parallel Algorithms for Multiplying Very Large Integers                                                                  |

| 5. | (S) A Parallel Pivoting Algorithm on a Shared Memory Multiprocessor with<br>Fill-in Control                                  |

| 6. | (S) Optimal Decomposition of Matrix Multiplication on Multiprocessor<br>Architectures                                        |

|    | M. Whelan, R. G. Guang and T. K. Yum (Philips Labs, USA)                                                                     |

| S  | ESSION 10C: Non-Numeric Algorithms II                                                                                        |

| 1. | (S) Performance Analysis of an Optimistic Concurrency Control Algorithm<br>in Replicated Database Systems                    |

| 2. | (S) Hypercube Algorithms for Some String Comparison Problems                                                                 |

| 3. | (S) Time Lower Bounds for Sorting on Multi-Dimensional Mesh-Connected<br>Processor Arrays                                    |

| 4. | (S) Accounting for Parallel Tree Search Overheads                                                                            |

| 5. | (S) Sorting with Linear Speedup on a VLSI Network                                                                            |

| 6. | (S) Concurrent Insertions and Deletions in a Priority Queue                                                                  |

| S  | ESSION 11C: Image Analysis and Geometry II                                                                                   |

| 1. | (R) Convolution on SIMD Mesh Connected Multicomputers                                                                        |

| 2. | (S) Parallel Solutions to Geometric Problems on the Scan Model of Computation 218<br>G. Blelloch and J. J. Little (MIT, USA) |

| 3. | (S) Parallel Template Matching Algorithms                                                                                    |

| 4. | (S) Linear Quadtree Algorithms on the Hypercube                                                                              |

| <ul> <li>5. (S) Optimising a Reconfigurable MIMD Transputer Machine for Line-of-Sight<br/>Calculations on Large Digital Maps</li></ul> |

|----------------------------------------------------------------------------------------------------------------------------------------|

| SESSION 12C: Applications III                                                                                                          |

| 1. (R) Implementation and Analysis of a Navier-Stokes Algorithm on<br>Parallel Computers                                               |

| <ul> <li>2. (R) Solution of Viscous Fluid Flows on a Distributed Memory Concurrent<br/>Computer</li></ul>                              |

| 3. (R) Parallelizing an Electron Transport Monte Carlo Simulator                                                                       |

| SESSION 14C: Applications IV                                                                                                           |

| 1. (R) Protein Sequence Comparison on a Data Parallel Computer                                                                         |

| <ul> <li>2. (R) Linear Optimization Via Message-Based Parallel Processing</li></ul>                                                    |

| 3. (R) Results of a Multiprocessor Implementation for Sequential Decision<br>Processes                                                 |

| SESSION 15C: Graph Theory                                                                                                              |

| <ol> <li>(R) Space-Efficient and Fault-Tolerant Message Routing in Outerplanar<br/>Networks</li></ol>                                  |

| <ol> <li>(S) A Decomposition Approach for Balancing Large-Scale Acyclic Data<br/>Flow Graphs</li></ol>                                 |

| 3. (S) Dilation-2 Embeddings of Grids into Hypercubes                                                                                  |

| 4. (S) Some Results on Graph Coloring in Parallel                                                                                      |

| <ul> <li>5. (S) Subgraph Isomorphism for Connected Graphs of Bounded Valence and<br/>Bounded Separator is in NC</li></ul>              |

| LATE PAPER - SESSION 1C                                                                                                                |

| 1. (S) Optimal Sorting on Reduced Architectures                                                                                        |

#### A GENERAL APPROACH TO MAPPING OF PARALLEL COMPUTATIONS UPON MULTIPROCESSOR ARCHITECTURES

#### S. J. Kim and J. C. Browne

Department of Computer Sciences The University of Texas at Austin Austin, TX 78712-1188

Abstract -- This paper defines and describes a broadly applicable approach to mapping of parallel computations upon multiprocessors, and briefly sketches the related mapping algorithms. The approach begins with a graph representation of a parallel computation and first generates a reduced graph by merging nodes with high internode communication cost through iterative use of a critical path algorithm. This graph is then mapped to a graphical representation of a multiprocessor architecture by the mapping algorithms. These algorithms attempt to minimize the total execution time including both computation and communication times. The algorithms, while they are heuristic rather than true optimal algorithms, are shown to yield excellent results in example applications and have modest execution costs.

#### 1. INTRODUCTION

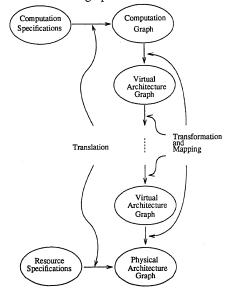

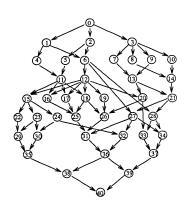

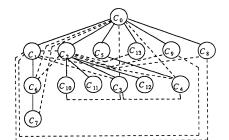

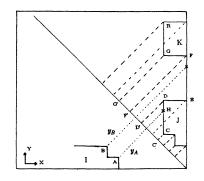

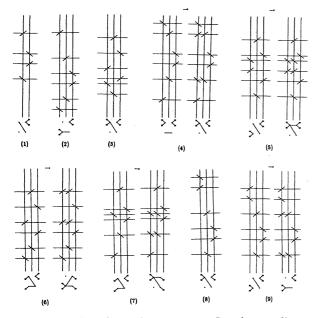

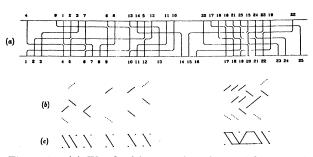

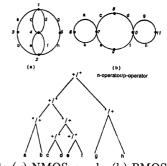

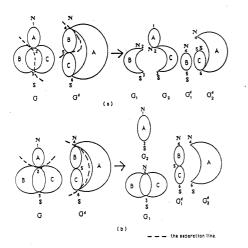

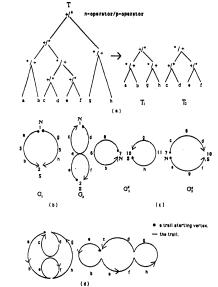

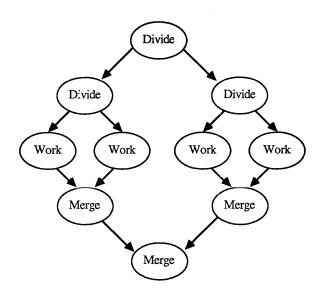

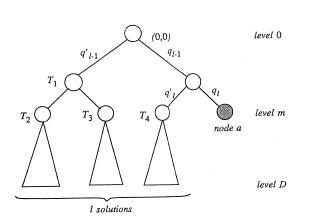

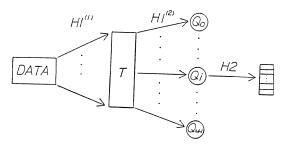

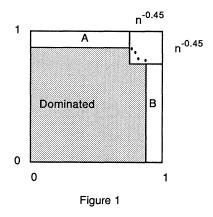

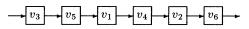

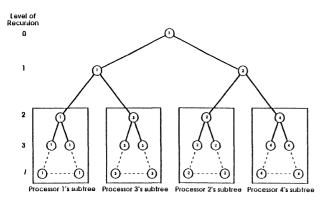

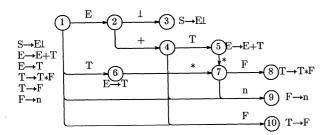

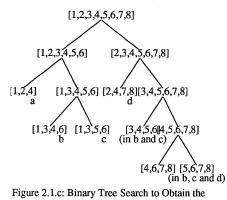

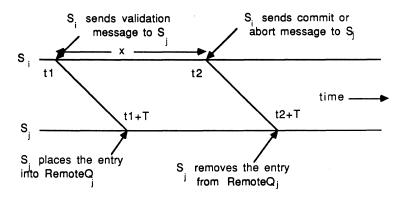

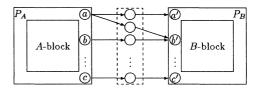

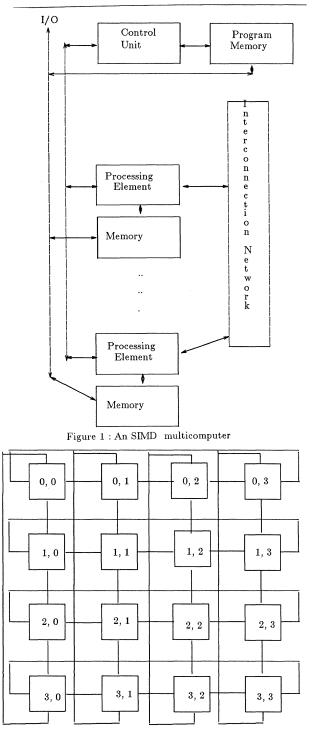

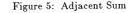

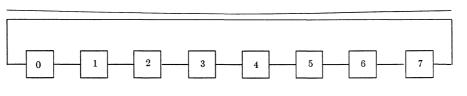

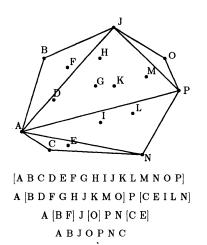

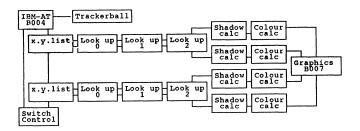

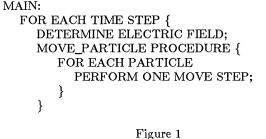

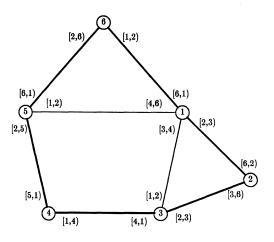

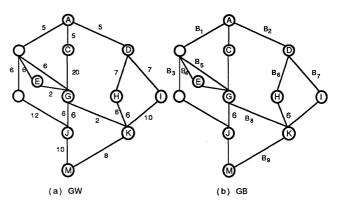

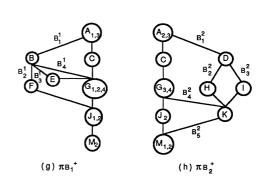

This paper defines and describes a broadly applicable approach to mapping of parallel computation structures (consisting of mutually dependent schedulable units of computations) upon MIMD multiprocessor architectures, and then sketches the related heuristic mapping algorithms. It also gives examples of the results obtained by application of the algorithms to different types of parallel computation structures and different multiprocessor architectures. The algorithms are based upon the mapping of a graphical representa-tion of a parallel computation structure [4, 5] upon a graphical representation of a multiprocessor architecture. In fact, we consider a series of transformations and mappings between a computation graph and an architecture graph as illustrated in Fig. 1-1.

The algorithms are described informally herein but complete formal definitions can be found in [17]. The algorithms apply to a broad class of graphs which can be derived from

Figure 1-1 General Overview of Our Approach

programs with various types of loop structures, and to a wide class of architectures. The algorithms attempt to minimize the total execution time (computation time and communication time) of the parallel computation. Reduction of execution time is attained mainly by reduction of communication time by merging of schedulable units of computation. The first step of each of the algorithms is the reduction of the computation graph to a virtual architecture graph through transformations determined by iterative application of a critical path algorithm. This virtual architecture graph is then either transformed into another virtual architecture graph or mapped onto an abstracted graphical representation of a multiprocessor architecture (called physical architecture graph). Note that a computation graph is assumed to have one root node and one leaf node without loss of generality.

The algorithms are heuristics with modest execution cost. True optimal algorithms for the scheduling problem as stated in Section 2 are known to be NP-complete. Three applications are given: mapping of the Sieve of Eratosthenes to an Intel iPSC/5 [15], mapping of a Gaussian (forward) elimination to a Sequent Balance and mapping of a molecular physics code to an emulated Intel iPSC/5 configuration with a mixture of fast and slow processors and communication channels. The results of the applications are surprisingly good. Near optimal total execution times are coupled with near minimal resource requirements and good workload balancing.

This paper is organized as follows: After giving the problem statement in Section 2, we briefly review previous work in Section 3. Then, in Section 4, after discussing our approach and the models for computation and architecture graphs, we explain mapping algorithms based on linear clusters. Section 5 gives a brief summary of performance results and Section 6 summarizes the status of the research.

#### 2. PROBLEM STATEMENT

A parallel computation can be represented by a direct acyclic graph  $G_C = (N_C, E_C)$ , where  $N_C = \{n_1, n_2, \dots, n_l\}$ is a set of schedulable units of computation to be executed, and  $E_C$  specifies scheduling constraints and data dependencies defined on  $N_C$ . A multiprocessor architecture can be represented by an undirected graph  $G_P = (N_P, E_P)$ , where  $N_P = \{p_1, p_2, \dots, p_m\}$  is a set of processors, and  $E_P$  specifies interconnection topology among the processors. The basic problem is to find a mapping of  $G_C$  onto  $G_P$  which minimizes schedule length (or makespan) defined as:

where  $\phi = \{\phi_1, \phi_2, \dots, \phi_s\}$  represents a set of paths from the root node to the leaf node in  $\hat{G}_C$ , node  $n_j$  (assigned to processor  $p_y \in N_P$  ( $1 \le y \le m$ )) is a direct descendant of node  $n_i$ (assigned to processor  $p_x \in N_P$   $(1 \le x \le m)$ ) in  $G_C$ ,  $comp_i$  is computation time of  $n_i$ , and  $comm_{ij}$  is communication time from  $n_i$  to  $n_j$  ( $comm_{ij} = 0$ , if  $p_x = p_y$  or  $n_i$  has no direct descendants).

An optimal schedule is one which meets the criteria of the minimum schedule length for a single parallel computation structure or the maximum total throughput for a set of simultaneously executing parallel computation structures. It must integrate scheduling of computations and dependency relations to resources. An approach which integrates consideration of all the interacting factors is one which maps a computation graph defining the computation structure (including the resource requirements for execution of each element of the computation structure) onto an architecture graph which defines the capability and capacity of the resource set of the execution environment. From here on we use the term *task* and *schedulable units of computation*, which corresponds to a node in a computation graph, interchangeably.

#### **3. PREVIOUS WORK**

The problem of optimal scheduling (as defined in Section 2) of parallel computations upon multiprocessor architectures has received generous attention in the literature. Algorithms which yield true optimal solutions in the absence of resource constraints are well known to be NP-complete [12, 21]. In fact, it is proven by Kim [17] that the other interesting scheduling problems are also NP-complete or worse in computation complexity.

There have been many heuristic algorithms proposed in the past. Previous approaches have focused mainly on the development of specific mapping strategies for particular multiprocessor architectures. Some attempt to take advantage of the unique hardware characteristics such as interconnection topologies of multiprocessor architectures under consideration. Since each strategy is usually an ad-hoc scheme, it is in most cases applicable to some limited class of multiprocessor architectures (e.g., tightly-coupled homogeneous architectures [2], loosely-coupled homogeneous architectures [23], loosely-coupled heterogeneous architectures [11], or multicomputers connected in point-to-point fashion [6]).

Various simplifying assumptions are common. For example, Bokhari [3] studies the assignment of tasks to processors with the restriction that the number of tasks should be less than or equal to the number of processors. Shen and Tsai [20] propose a graph matching approach for solving task assignment to processors, but ignore dependency relations among tasks. Some approaches have limited scheduling objectives; they find the best schedule with respect to either the total computation time [13] or interprocessor communication time [14]. Other approaches are interested in balancing the workload of the total multiprocessor architecture [10, 22].

In most scheduling strategies for tightly-coupled architectures, specific interconnection networks such as the Butterfly switch, the Omega network, the SW-Banyan network or a composition of them [19] are assumed. On the other hand, most research has not taken into account scheduling constraints, resource limitations, and/or the current workloads of processors. It is frequently assumed that each processor is identical (i.e., all have the same processing speed, equal number of communication channels, and identical memory capacity). Finally, while most scheduling strategies make heavy use of busy-waiting as a synchronization mechanism, there is little attempt to reduce or avoid using it.

All in all, there are a myriad of multiprocessor scheduling strategies which can be applied to specific multiprocessor architectures. On the other hand, there is little research which attempts an integrated approach to multiprocessor scheduling which could be applicable to various multiprocessor architectures regardless of underlying architectural characteristics.

#### 4. APPROACH AND ALGORITHMS

4.1. Approach

One of the contributions of this paper is to propose algorithms based on linear clustering. A linear cluster is a connected subgraph of a computation graph which is in the form of a linear list of schedulable units of computation. Linear clustering is an effectual heuristic to compromise between two conflicting goals of multiprocessor scheduling, minimization of interprocessor communication and maximization of potential parallelism, and to satisfy the other goals, throughput enhancement and workload balance, relatively The underlying idea of linear clustering is that the well. schedulable units of computation that are sequentially dependent on each other are to be assigned to one processor, while those that are mutually independent are to be allocated to separate processors. We select linear clusters on the basis of total execution time on an architecture with a processor for each node of the graph and a distinct communication channel per each edge of the graph. The critical restriction of linear clustering is that it expects a computation graph to be acyclic. To minimize this restriction, we identify cases in which cyclic computation graphs can be transformed into acyclic graphs in a straightforward manner [17].

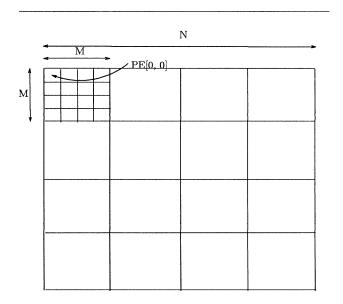

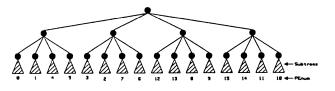

A computation graph is transformed into a virtual architecture graph (VAG) by linear clustering. The VAG in fact represents an optimal multiprocessor architecture for the computation graph. The optimal architecture provides one processor to every linear cluster so that mutually independent tasks belonging to different linear clusters can be executed in parallel as long as possible. Furthermore, direct communication channels are always available for any adjacent linear clusters in the optimal architecture.

The VAG may be transformed into another VAG by merging two or more linear clusters into one cluster. Two linear clusters  $K_1$  and  $K_2$  are combined into one if  $K_2$  may start only after  $K_1$  finishes or may be executed only while  $K_1$  is idle. It contributes to further balancing the workload of processors, and further reducing the amount of resources to be utilized and interprocessor communication overhead.

After constructing a VAG which represents the optimal multiprocessor architecture for a given computation graph, we then find an optimal mapping of the VAG onto a *physical architecture graph* (PAG) which represents the target architecture. This mapping is called a *physical mapping* as it is the final mapping of a computation graph onto a real physical multiprocessor architecture. We develop *homogeneous* and *heterogeneous* mapping algorithms for homogeneous and heterogeneous architectures, respectively.

These algorithms rely on not only local information but also on limited global information. The key issue is how to reduce the mapping complexity while sacrificing as little optimality as possible. A *dominant request tree* is a maximal spanning tree of a VAG. It provides limited global information on the VAG such as the mapping order of the nodes and the edges whose adjacency should be maintained. Both mapping algorithms utilize dominant request trees, but take quite different approaches to mapping the trees onto PAG's. Most importantly, in the case of homogeneous mappings, the trees are directly mapped onto PAG's. On the other hand, in the case of heterogeneous mappings, they are mapped onto dominant service trees. A *dominant service tree* is a maximal spanning tree of a PAG. For heterogeneous mappings, one of the important issues is how to identify and utilize resources with high performance. A dominant service tree provides such information.

#### 4.2. Model of Computation

Browne [5] proposes a directed graph as a representation basis of a parallel computation, in which the nodes represent the bindings of operations to data and the edges represent dependency relations between schedulable units of computation executed at the nodes. Our computation graph model is a triple  $(G_c, f_c^{comp}, f_c^{comm})$ , whose first component  $G_c = (N_c, E_c)$  specifies a parallel computation. Computation graph  $G_c$  is a directed acyclic graph and defined as follows:

- (i) A node set  $N_c = \{n_1, n_2, \dots, n_l\};$

- (ii) An edge set  $E_c = \{e_1, e_2, \dots, e_t\}$ , where any given edge  $e_p = (n_i, n_j)$  is directed from node  $n_i$  to node  $n_j$ .

To be specific, graph  $G_c$  defines computation steps by the nodes and sequencing among the steps by the edges. The remaining components provide information necessary for mapping the computation graph onto a target architecture. The second component  $f_c^{comp}$  is a function which maps each node in  $N_c$  onto a positive integer which is the expected computation time used by the schedulable unit of computation corresponding to the node. The next function  $f_c^{comm}$  maps each edge  $(n_i, n_j)$  in  $E_c$  onto a nonnegative integer which is the expected amount of internode communication from node  $n_i$  to node  $n_j$ . For example, if  $f_c^{comm}(e_p) = N_{bytes}$  for  $e_p =$  $(n_i, n_j)$ , then the total length of messages sent from  $n_i$  to  $n_j$  is  $N_{bytes}$  bytes.

Our computation graph is a restricted model in a couple of ways. The critical restriction that makes the model inappropriate for representing some parallel computations is that a set of edges entering and leaving a given node may not be joined by *or* conditions. The other restriction is that computation graphs are required to be static; neither new nodes nor new edges can be created during runtime. The main reason for these restrictions is to avoid ambiguity in determining the computation and communication requirements of the nodes and edges in a computation graph.

The model for architecture graphs provides a representation basis for the structural description of multiprocessor architectures. We consider three types of resources: processors, communication channels and memory. Our architecture graph model is also a triple  $(G_a, f_a^{comp}, f_a^{comm})$ , whose first component  $G_a = (N_a, E_a)$  is an undirected graph defined as follows:

- (i) An architecture node set  $N_a = \{an_1, an_2, \dots, an_l\};$

- (ii) An architecture edge set  $E_a = \{ae_1, ae_2, \dots, ae_t\}$ , where any architecture edge  $ae_p = (an_i, an_j)$  is undirected.

In an architecture graph, an architecture node represents a processor as well as a memory module, and an architecture edge represents a communication channel between two processors. The second component  $f_a^{comp}$  is a function which maps each architecture node in  $N_a$  onto a pair of positive integers which denote the level of computing power of a processor relative to the others in the architecture and the current local memory size. A common global memory may be specified by a *dummy* architecture node which is fullyconnected with the other architecture nodes. The next function  $f_a^{comm}$  maps an architecture edge  $(an_i, an_j)$  in  $E_a$  onto a positive integer which represents the bandwidth of communication channel from  $an_i$  to  $an_j$  and vice versa.

It is assumed that an architecture graph is static; the resource configuration of a physical multiprocessor architecture will not be changed dynamically during runtime. Moreover, it maintains the exact current status of the architecture. The status includes the information on which processors are currently active/inactive, which communication channels are currently available and what is the current memory capacity available in each processor.

#### 4.3. Mapping Based on Linear Clusters

Clustering techniques have been used in a variety of

areas in computer science [1, 7]. In this section, we propose a new mapping technique based on linear clustering and linear cluster merging. After discussing linear clustering and merging, we explain how to iteratively refine linear clusters (if necessary) for the minimization of schedule length.

#### 4.3.1. Linear Clustering

Linear clustering is a fundamental idea of our mapping algorithms discussed in Section 4.4. A cluster of  $G_C = (N_C, E_C)$  is called a *linear cluster K* if it satisfies the following conditions:

- K is nonempty;

- K is a connected subgraph of  $G_C$ ;

- Both indegree and outdegree of every node in K is less than or equal to 1.

Linear clustering is a special case of general clustering in that a linear cluster is a degenerate tree in which each node has at most one direct ancestor and/or one direct descendant, while a cluster, in general, is an arbitrary graph.

The following algorithm *LinearCluster* illustrates how to identify linear clusters:

```

LinearCluster (G, K)

/* G is a (cycle-free) computation graph. */

/* K is a set of linear clusters. */

Begin

Let K = \emptyset;

Find a longest path P from the root to a leaf node in G;

During traversing path P backward

from the leaf to the root node,

cut all the incoming and outgoing edges

except the one belonging to \overline{P};

For each connected subgraph S of G

If both indegree and outdegree of each node in S

is less than or equal to 1,

Then

K = K \cup S

Else Do

LinearCluster (S, K');

K = K \bigcup K';

End Do;

End LinearCluster.

```

A path  $(n_1, n_2, ..., n_l)$  of graph  $G_C = (N_C, E_C)$  such that  $n_i \in N_C$  and  $(n_i, n_{(i+1)}) \in E_C$  is considered the longest path if it maximizes the following function:

$$\sum_{i=1}^{r} (\omega_1 \cdot T_{comp_i} + (1-\omega_1) \cdot (\omega_2 \cdot T_{comm_{ig+1}} + (1-\omega_2) \cdot \sum_{j \in N_{ig}^{(d+1)}} T_{comm_{ig+1y}})) + \omega_1 \cdot T_{comp_i},$$

where  $T_{comp_k}$  is the computation time of node  $n_k$   $(1 \le k \le l)$ ,  $T_{comm_{sl}}$  is the communication time of node  $n_s$  with an adjacent node  $n_t$   $(1 \le s < l \text{ and } 1 < t \le l)$ ,  $N_{adj}^t$  denotes a set of nodes adjacent to  $n_t$   $(1 < t \le l)$ , and both  $\omega_1$  and  $\omega_2$  are normalization factors.

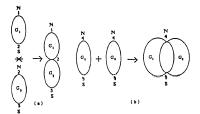

#### 4.3.2. Linear Cluster Merging

In this section, we investigate a means to merge two or more linear clusters into one without affecting potential parallelism existing in a computation graph. It may contribute to further balancing the workload of processors. It may also contribute further reducing the amount of resources to be utilized and interprocessor communication overhead.

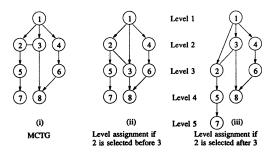

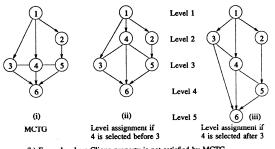

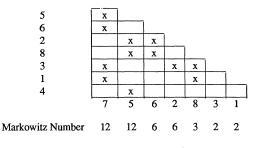

The level numbers may be used to identify potential parallelism [18] in a computation graph if defined as follows:

level(T) = 1 if T is a root node;

=  $[\max(level(A) \text{ for each direct ancestor } A \text{ of } T)]$

#### + 1, otherwise.

Then, the same level number implies mutual independence. To be more specific, if a group of tasks have the same level number, they are mutually independent and may be simultaneously executable.

In order to define conditions for merging linear clusters, let  $L_i$  represent a set of level numbers assigned to tasks in linear cluster  $K_i$ . Two linear clusters  $K_i$  and  $K_j$  are said to be sequentially strong-dependent if they satisfy the following conditions:

1)  $L_i \cap L_j = \emptyset;$

2) The trailer node of linear cluster  $K_i$  precedes the header node of linear cluster  $K_i$ .

Two linear clusters  $K_i$  and  $K_j$  are said to be *mutually* strong-dependent if they satisfy the following conditions:

- 1)  $L_i \cap L_j = \emptyset;$

- 2) For two tasks  $T_1$  and  $T_2$  in  $K_i$ ,  $T_1$  is a direct ancestor of  $T_2$ , where the former is one of direct ancestors of the header node of  $K_j$  and has the largest level number among the direct ancestors, and the latter is one of direct descendants of the trailer node of  $K_j$  and has the smallest level number among the direct descendants.

If a pair of linear clusters satisfy any of the merging conditions, they can be merged into one cluster without affecting the execution time of the computation.

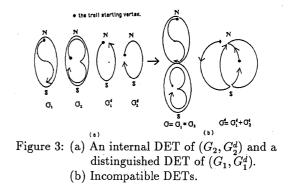

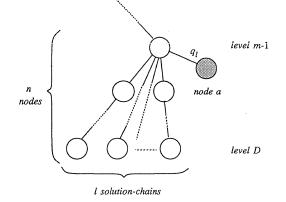

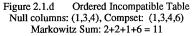

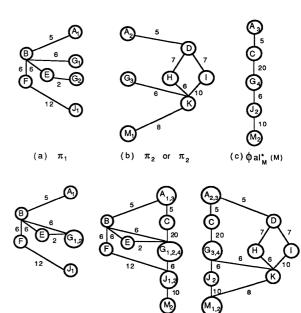

#### 4.3.3. Iterative Refinement of Linear Cluster

In the previous sections, we discussed how to transform a computation graph  $G_C$  into a virtual architecture graph by linear clustering and merging. It is expected that a linear cluster consisting of schedulable units of computation on the critical path of  $G_C$  takes the longest time to finish in the VAG in most cases. In this case, we can make use of the VAG for the mapping onto a physical architecture graph without any modification. This may not be true if the computation graph has extremely heavy communication requirements on edges not on the initial critical path. If that is the case, we may need to iteratively refine linear clusters in the VAG so that we can further reduce the total length of schedule prior to mapping. It consists of two steps:

Linear cluster labeling;

• Linear cluster refinement.

During labeling step, we label edges in a computation graph  $G_C = (N_C, E_C)$ . The level number  $level_{edge}$  of edge  $e_{ij} = (n_i, n_j)$  may be defined as follows:

$level_{edge}(e_{ij}) = \omega \cdot comp_j + (1-\omega) \cdot comm_{ij} + level_{node}(n_j)$ , where  $level_{node}(n_j)$  is the level number of node  $n_j$ ,  $comp_j$ and  $comm_{ij}$  are computation time of  $n_j$  and communication time from  $n_i$  to  $n_j$ , respectively, and  $\omega$  is a normalization factor. Note that  $level_{node}(n_j)$  is defined as  $\max_{n_k \in D_j} (level_{edge}(e_{jk}))$ where  $D_j$  is a set of direct descendants of node  $n_j$ . These

where  $D_j$  is a set of direct descendants of node  $n_j$ . These edge labels allow us to identify the longest path to be considered for the minimization of the total schedule length in a VAG.

After linear cluster labeling, we can determine if there are paths through a VAG, each of whose length is longer than the total computation time of a linear cluster corresponding to the critical path of the original computation graph  $G_C$ . If there exist such paths, we modify the current set of linear clusters in order to further reduce the total schedule length through iterative refinements of them.

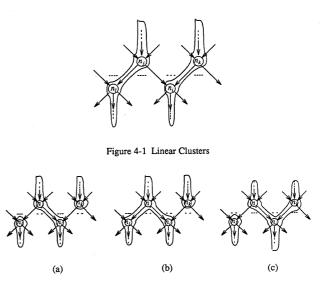

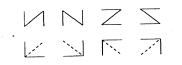

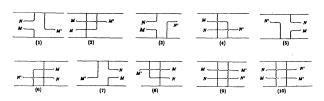

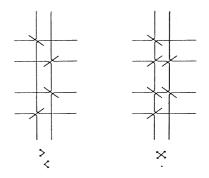

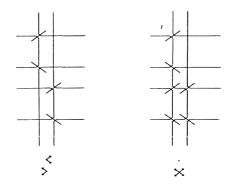

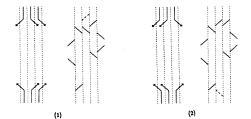

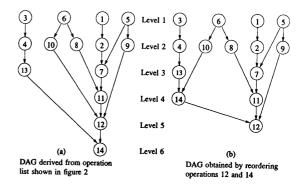

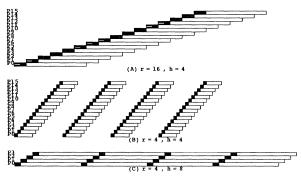

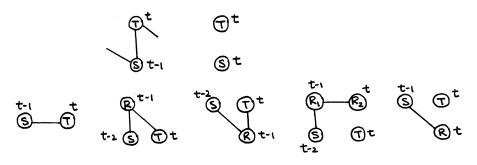

Figure 4-2 Possible Refinements of Linear Clusters

In Fig. 4-1, let us assume that a new longest path is passing through nodes  $n_j$  and  $n_i$ , i.e., the new longest path is  $(\cdots, n_i, n_i, \cdots)$ . The basic idea of linear cluster refinement is to locate a cut edge  $(n_i, n_i)$  on the longest path and to reduce the length by merging nodes  $n_i$  and  $n_i$  (belonging to separate linear clusters) into one. After the two nodes  $n_i$  and  $n_i$  are merged, linear clusters shown in Fig. 4-1 can be refined as shown in Fig. 4-2. In Fig. 4-2-a, we merge  $n_i$  and  $n_j$  into one cluster, and cut the edges like  $(n_i, n_l)$  and  $(n_k, n_i)$  so that all the clusters remain as linear clusters. In Fig. 4-2-b and Fig. 4-2-c, however, we merge them, but leave one of the edges uncut while we cut the other edge. This type of refinement may force us to sacrifice some potential parallelism since two or more nodes (e.g.,  $n_l$  and  $n_i$  in Fig. 4-2-b,  $n_j$ and  $n_k$  in Fig. 4-2-c) executable in parallel are to be assigned to the same cluster. Nonetheless, it is worthwhile to merge two linear clusters in this way if internode communication overhead from  $n_j$  to  $n_l$  is larger than the schedule extension caused by sequential execution of nodes (e.g.,  $n_l$  and  $n_i$  in Fig. 4-2-b,  $n_i$  and  $n_k$  in Fig. 4-2-c).

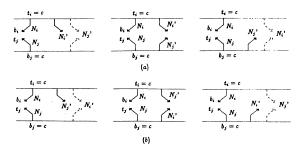

#### 4.4. Mapping Algorithms

The subject of this section is how to map a VAG onto a PAG. The important goal of our proposed algorithms is to compromise between two extreme approaches [8, 18] by reducing the complexity of the mapping algorithms while sacrificing their optimality as little as possible. For physical mapping, we need to take into consideration as much global information as possible during mapping.

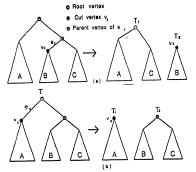

#### **4.4.1.** Dominant Request Tree

The basic idea of our algorithm is to find a subgraph isomorphism [12] from a VAG to a PAG which minimizes the total schedule length and satisfies given scheduling constraints. We can easily show that the subgraph isomorphism problem is NP -complete, making use of the fact that the Undirected Hamilton Circuit problem is NP -complete. This fact forces us to rely on heuristics. We map each node of a VAG one by one in a sequential order. The key issue is then how to determine the mapping order which leads to the minimization of the schedule length. For this purpose, we propose another transformation of a VAG into a tree called Dominant Request Tree (DRT). This transformation can be done irdependently of the target architecture (i.e., whether it is homogeneous or heterogeneous).

A DRT is a maximal spanning tree of a VAG. We construct the DRT starting from a node called the Most Dominant Node (MDN) rather than starting from an arbitrary node in the VAG. The MDN is that node n which maximizes the cost function defined as:

$\omega T_{comp} + (1-\omega) T_{comm}$ , where  $T_{comp}$  is the computation time of *n*,  $T_{comm}$  is the total communication time of *n* with its adjacent node(s), and  $\omega$  is a normalization factor. The *MDN* is considered to be the most important node in the VAG in the sense that it represents a linear cluster which includes all tasks on the critical path in a given computation graph. Since it is usually the case that the MDN requires the largest weighted sum of computation and communication times among nodes in the VAG, we would better assign the MDN to the most appropriate processor in a PAG.

Starting from the MDN of a DRT, we select a node with the highest binding power among unassigned nodes incident upon any already assigned node until all the nodes in the DRT are selected. The binding power of node  $n_i$  with respect to an adjacent node  $n_i$  is determined by:

$$\omega_1 \cdot T_{comp_j} + (1 - \omega_1) \cdot (\omega_2 \cdot T_{comm_{ij}} + (1 - \omega_2) \cdot \sum_{k \in A_j} T_{comp_{jk}}),$$

where  $T_{comp_j}$  is the computation time of  $n_j^{kri}$ ,  $T_{comm_{ij}}$  is the communication time of node  $n_i$  with node  $n_j$ , and  $A_j$ represents a set of nodes adjacent to  $n_j$ .  $\omega_1$  and  $\omega_2$  are again normalization factors. A DRT of a VAG has two types of edges: the primary and secondary edges. The former are edges belonging to the DRT, while the latter are edges belonging to the VAG but not to the DRT. Note that the order in which each cluster is included in the DRT determines the priority list L.

#### 4.4.2. Homogeneous Mapping

The goal of homogeneous mapping is to find a subgraph in a PAG to which a DRT of a VAG is isomorphic, relying on various heuristics like connectivity, exclusion, perturbation, foster mapping, and restricted pairwise exchange. The basic approach of the homogeneous mapping is to try to maintain adjacency of each node in the DRT with its neighbors as far as possible; whenever there is a direct primary edge from cluster  $K_1$  to cluster  $K_2$ , we choose processor  $P_{K_2}$ which has a direct channel from  $P_{K_1}$ . Note that  $P_K$  and  $K_{da}$ denote a processor onto which cluster K is to be mapped and the direct ancestor of K, respectively.

Each node of the VAG is assigned to a processor in the order determined during transforming the  $VA\hat{G}$  into the DRT. For each cluster K in the order of the priority list L, if there are at least two clusters which form full-connectivity with K, we first apply connectivity mapping. This heuristic attempts to maintain full-connectivity among clusters during mapping. If it is not successful to maintain the connectivity or there exist no clusters which form full-connectivity with K, then we try to assign K to a free processor in PAG adjacent to  $P_{K_{da}}$ . During this mapping, we apply exclusion mapping to exclude processors in PAG which might be crucial to other clusters yet to be assigned.

Next, we consider the case that  $P_{K_{da}}$  has no more free adjacent processors. Then, K may be mapped onto a processor which is not adjacent to  $P_{K_{da}}$ . For this case, we provide two heuristics: perturbation and foster mappings. In both heuristics, we first choose a processor which has the most appropriate number of channels among currently unassigned processors. If there is more than one, we choose the one which is the nearest to  $P_{K_{da}}$ . Those unassigned processors should be adjacent to at least one processor to which a cluster has already been assigned.

In *perturbation mapping*, we attempt to preempt a linear cluster which has already been assigned to a processor adjacent to  $P_{K_{da}}$ , and to assign K to the processor. There are two possible cases that a linear cluster may be preempted after being assigned to a processor. First, an adjacent processor (say,  $P_{K_{adj}}$ ) of  $P_{K_{da}}$  might be assigned to cluster  $K_{adj}$  which is not in fact adjacent to cluster  $K_{da}$  in the VAG. The other possible case is that all the clusters assigned to adjacent pro-cessors of  $P_{K_{da}}$  are in fact neighbors of  $K_{da}$ , but  $K_{adj}$  might have less communication overhead with  $K_{da}$  than K in the VAG.

As long as perturbation mapping does not make any improvement, it is not possible to maintain adjacency using a primary edge for this particular mapping. That is, cluster Kcan not communicate directly with cluster  $K_{da}$ . In order to lessen the effect of the indirect communication, we first check whether there is another cluster adjacent to K through a primary edge which has already been assigned to a processor. If there is more than one, we choose a cluster  $K_{fa}$  which has the highest binding power (other than  $K_{da}$ ) with K. After has the highest binding power (bind than  $K_{da}$ ) with K. These assuming  $K_{fa}$  as a direct ancestor of K, we reiterate the same mapping procedure mentioned above (i.e., finding the best mapping from processor  $P_{K_{fa}}$ ). We call such a mapping foster mapping. The only difference is that  $K_{fa}$  is now assumed to be the direct ancestor of K for  $K_{da}$  in the VAG. If there does not exist such a primary edge, utilizing the secondary edges, we repeat the same procedure as we do for the primary edge.

Since the previous heuristics do not guarantee an optimal mapping, we try to further improve the result by applying restricted pairwise exchange; we do allow random pairwise exchange of clusters to which specific codes have been assigned during mapping [17]. Note that we keep track of such codes based on how the clusters have been assigned during mapping.

### 4.4.3. Heterogeneous Mapping

Heterogeneous mapping is a mapping of computation graphs onto architecture graphs which represent heterogeneous multiprocessors. For heterogeneous mappings, it is important to utilize resources with high performance as far as possible so that the total schedule length can be minimized and the workload balance can be achieved. We first need to distinguish resources with higher performance from those with lower performance. A Dominant Service Tree (DST) provides a limited amount of global information on resources in a heterogeneous multiprocessor lest our mapping algorithms become totally greedy based on local information. We can construct a *DST* by utilizing a maximal spanning tree algorithm. This may be considered as a transformation of a PAG into another PAG. In a sense, the transformation can be regarded as prescanning of architecture graphs prior to physical mapping. During the scanning, we collect information like which processors have more computing power and which communication channels have more bandwidth than others.

After the transformation of a PAG into a DST, the scheduling problems for heterogeneous multiprocessor architectures turn into the tree-to-tree mapping problems. The edges in the PAG are to be divided into two different types: the primary and secondary edges. Analogous to a DRT, the edges belonging to the DST are called the primary edges, while the edges belonging to the PAG but not to the DST are called the secondary edges. The main goal of heterogeneous mapping is to identify a mapping which maintains adjacency of the primary edges of the VAG with those of the PAG. When there are no primary edges available, however, we utilize secondary edges of the *PAG* during mapping. Specific scheduling constraints (e.g., available local memory size) are also to be applied on the fly during the mapping.

Since it is still an NP-complete problem to find an optimal mapping from one tree to another, the issue is how to develop efficient heuristic mapping algorithms between a DRT and a DST. We exploit sequential mapping order of nodes determined during constructing a DRT, and so-called node information [17] as a means to avoid exhaustive matching between two trees.

#### 5. APPLICATIONS

The applications described here cover regular (Sieve of Eratosthenes, Gaussian elimination) and irregular (molecular physics code) computation graphs, and partitioned (Intel iPSC) and shared memory (Sequent Balance) multiprocessor architectures.

#### 5.1 Mapping of Sieve of Eratosthenes to an Intel iPSC

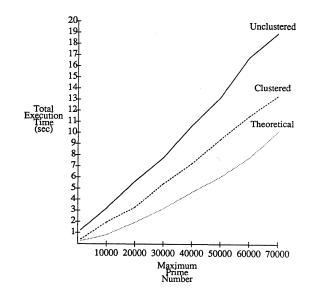

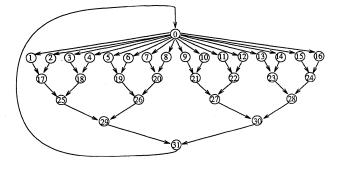

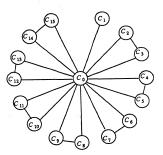

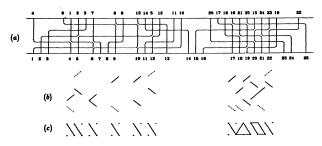

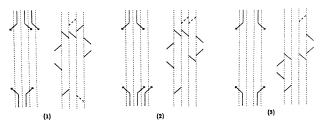

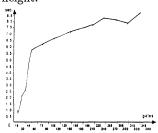

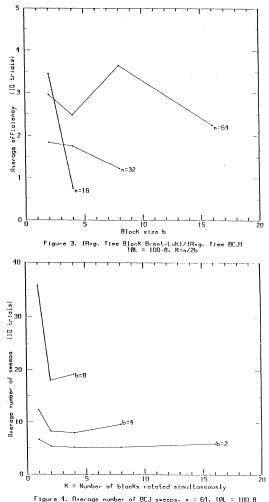

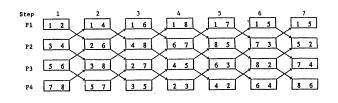

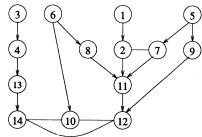

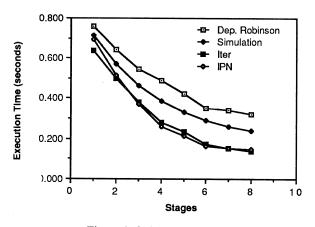

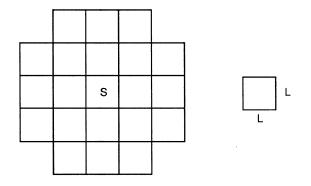

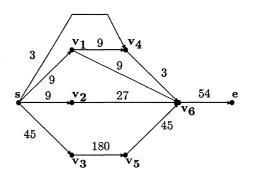

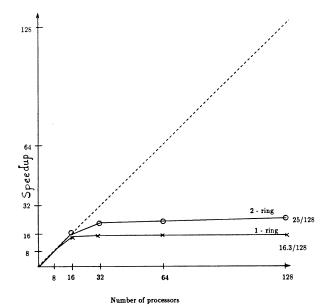

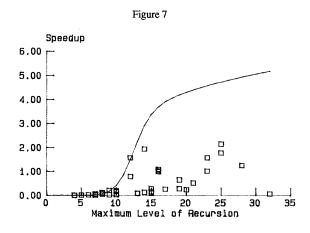

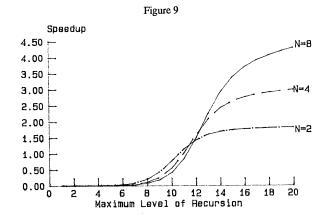

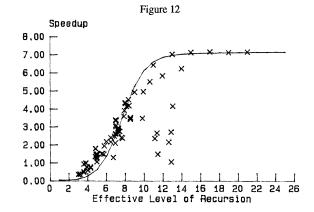

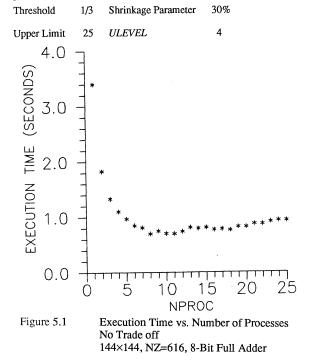

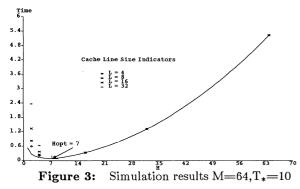

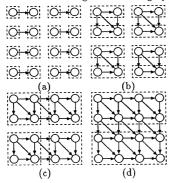

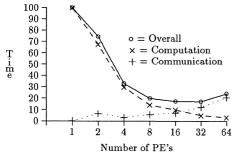

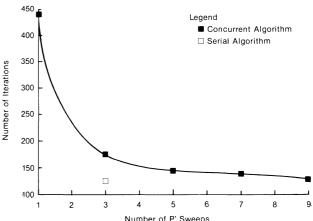

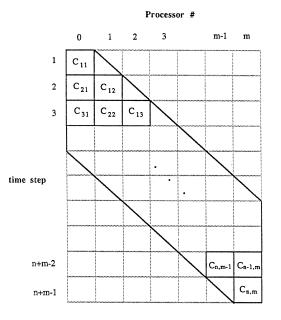

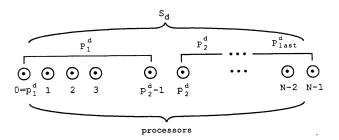

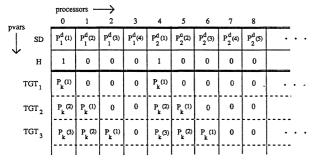

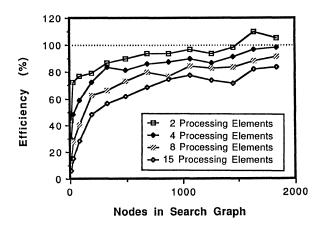

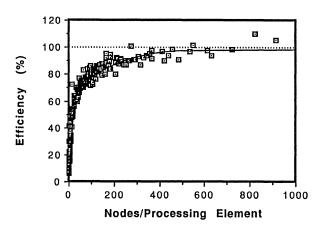

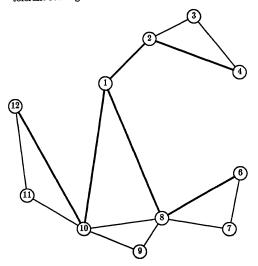

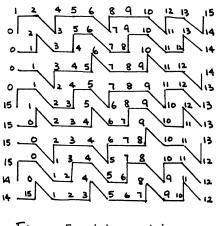

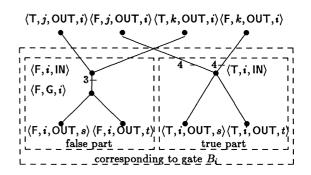

We seek here decrease of the communication time component of the total execution time. The computation graph for the algorithm is shown in Fig. 5-1. The VAG for the computation graph is shown in Fig. 5-2. Fig. 5-3 shows the improvement in total execution time obtained by application of the algorithm together with the lower bound of total execution time for this execution environment.

Figure 5-3 Comparison of Total Execution Times

Figure 5-1 Computation Graph

Figure 5-2 Virtual Architecture Graph

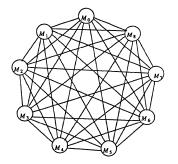

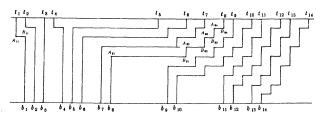

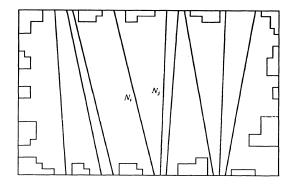

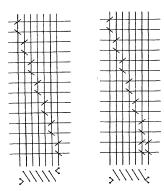

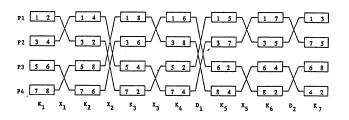

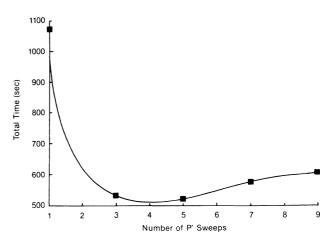

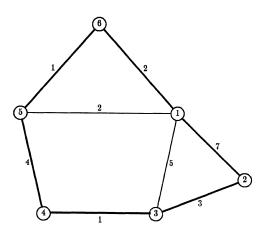

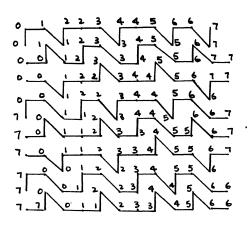

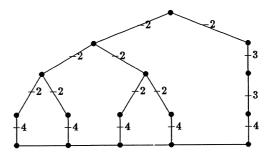

#### 5.2. Gaussian Elimination on a Sequent Balance

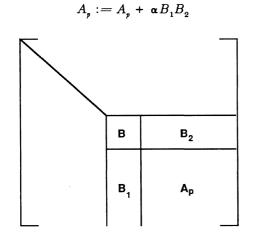

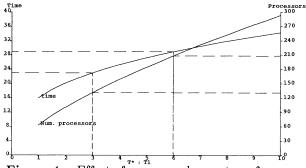

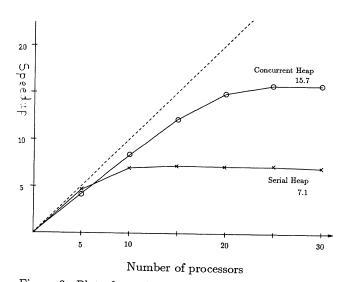

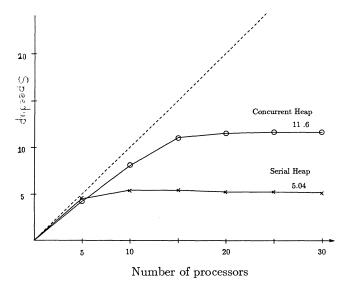

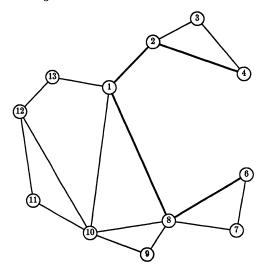

The principal benefit to be obtained from application of one algorithm to scheduling for a shared memory multiprocessor is decrease in overhead without loss of parallelism caused by an optimal selection of schedulable units of computation. The computation graph for forward elimination is shown in Fig. 5-4. Each node  $A_{k,l}$  in Fig. 5-4 represents the row operation to force  $A_{k,l}$  to zero. The VAG is shown in Fig. 5-5. The saving in overhead is shown in Fig. 5-6 for 9 processors across a range of array sizes after linear clustering and merging. The gain is substantial (~15%-20%) for larger array sizes.

Figure 5-4 Computation Graph

Figure 5-5 Virtual Architecture Graph

Figure 5-6 Comparison of Total Execution Times using 9 Processors

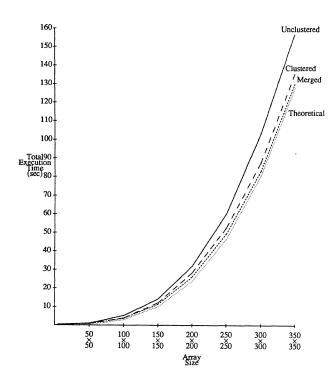

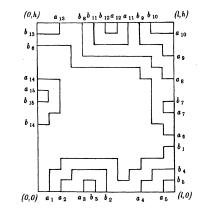

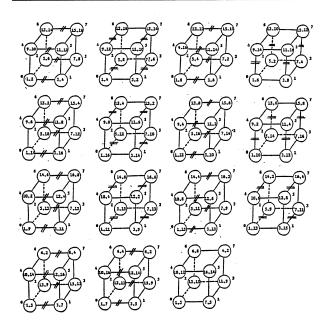

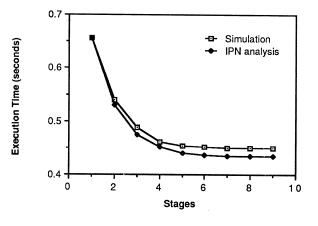

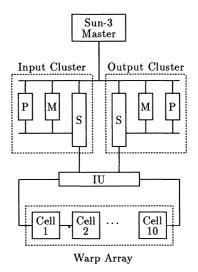

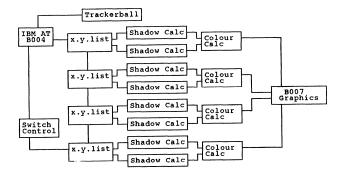

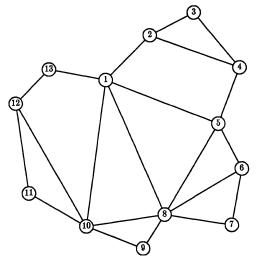

#### 5.3. Modified Molecular Dynamics Code on a "Heterogeneous" Intel iPSC

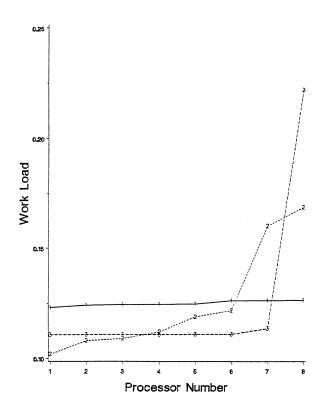

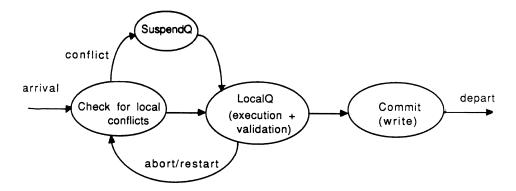

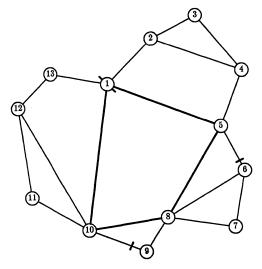

The effects to be studied here are those of an irregular computation graph on a heterogeneous architecture. The computation graph is shown in Fig. 5-7 and the VAG in Fig. 5-8. In order to obtain the effect of a heterogeneous multiprocessor, we assume that 50% of processors and 20% of communication channels are twice as fast as real ones by setting computation times of nodes and communication times of edges in the VAG to  $\frac{1}{2}$  of their actual values if they are assigned to faster processors or channels, respectively. Fig. 5-9 compares total execution times for four cases (**x**, **y**) where **x** = (homogeneous, heterogeneous) and **y** = (measured, theoretical). It is not surprising that the improvement in execution time is greater for the heterogeneous architecture than for the homogeneous architecture since the clusters with

greater resource requirements can be assigned to faster processors and channels of the heterogeneous one as far as possible.

Figure 5-7 Computation Graph

Figure 5-8 Virtual Architecture Graph

Figure 5-9 Comparison of Total Execution Times (Unclustered vs Clustered)

#### 6. SUMMARY

The conceptually simple and computationally tractable heuristics based on linear clustering have been found in application to be effective and, so far as can be judged by the limited sample of applications, robust.

Future work will include test of a large number of applications, incorporation of various scheduling constraints into the model, and analytic definition of the class of graphs where the heuristics yield optimal schedules.

#### 7. ACKNOWLEDGEMENT

We are grateful to Al Mok for pointing out a drawback in the original linear clustering algorithm. This research is partially supported by DARPA grant N00039-86-C-0167, and DOE grant DE-FG05-85ER-25010.

#### REFERENCES

- [1] Banerjee, J., Kim, W., Kim, S. J., and Garza, J. F., "Clustering a DAG for CAD Databases," To appear in *IEEE-SE*.

- [2] "Butterfly (TM) Parallel Processor Overview," Bolt Beranek and Newman Inc., Cambridge, MA, June 1985.

- [3] Bokhari, S. H., "On the Mapping Problem," *IEEE-TC*, Vol. C-30, No. 3, Mar. 1981, pp. 207-214.

- [4] Browne, J. C., "Formulation and Programming of Parallel Computations: A Unified Approach," Proc. of Int'l Conf. on Parallel Processing, Aug. 1985, pp. 624-631.

- [5] Browne, J. C., "Framework for Formulation and Analysis of Parallel Computation Structures," *Parallel Computing* 3, 1986, pp. 1-9.

- [6] Bryant, R. M., and Finkel, R. A., "A Stable Distributed Scheduling Algorithm," 2nd Int'l. Conf. on Distributed Computing Systems, 1981, pp. 314-323.

- [7] Chiang, W. P., "Optimal Graph Clustering Problems with Applications to Information System Design," Technical Report CRL-TR-30-84, The Univ. of Michigan, June 1984.

- [8] Coffman, E. G., Jr., and Graham, R. L., "Optimal Scheduling for Two-Processor Systems," Acta Informatica 1, 1972, pp. 200-213.

- [9] Coffman, E. G., Jr. (Ed.), *Computer and Job-Shop Scheduling Theory*, John Wiley and Son, N. Y., 1976.

- [10] Eager, D. L., Lazowska, E. D., and Zahorjan, J., "Dynamic Load Sharing in Homogeneous Distributes Systems," *IEEE-SE*, Vol. SE-12, No. 5, May 1986, pp. 662-675.

- [11] Forsdick, H., Schantz, R., and Thomas, R., "Operating Systems for Computer Networks," *IEEE Computer*, Vol. 11, Jan. 1978.

- [12] Garey, M. R., and Johnson, D. S., Computers and Intractability: A Guide to the Theory of NP-Completeness, W. M. Freeman and Company, New York, 1979.

- [13] Gottlieb, A., Grishman, R., Kruskal, C. P., McAuliffe, K. P., Rudolph, L., and Snir, M., "The NYU Ultracomputer - Designing an MIMD Shared Memory Parallel Computer," *IEEE-TC*, Vol. C-32, No. 2, Feb. 1983, pp. 175-189.

- [14] Haessig, K., and Jenny, C. J., "Partitioning and Allocating Computational Objects in Distributed Computing Systems," *IFIP*, 1980, pp. 503-508.

- [15] "iPSC User's Guide," Intel Corporation, Apr. 1987.

- [16] Karp, R. M., and Miller, R. E., "Properties of a Model for Parallel Computations: Determinacy, Termination, Queueing," *SIAM J. Appl. Math.*, Vol. 14, No. 6, Nov. 1966, pp. 1390-1411.

- [17] Kim, S. J., "A General Approach to Multiprocessor Scheduling," TR-88-4, The Univ. of Texas at Austin, Feb. 1988.

- [18] Pathak, G. C., "Towards Automated Design of Multicomputer System for Real-time Applications," Ph. D. Thesis, North Carolina State Univ., 1984.

- [19] Pfister, G. F., "The Architecture of the IBM Research Parallel Processor Prototype (RP3)," IBM Research Report RC 11210, June 1985.

- [20] Shen, C.-C., and Tsai, W.-H., "A Graph Matching Approach to Optimal Task Assignment in Distributed Computing Systems Using a Minimax Criterion," *IEEE-TC*, Vol. C-34, No. 3, Mar. 1985, pp. 197-203.

- [21] Ullman, J. D., "NP-complete Scheduling Problem," J. of Computer System Science, Vol. 10, 1975, pp. 384-393.

- [22] Wang, Y.-T., and Morris, R. J. T., "Load Sharing in Distributed Systems," *IEEE-TC*, Vol. C-34, No. 3, Mar. 1985, pp. 204-217.

- [23] Wittie, L. D., and van Tilborg, A. M., "MICROS, A Distributed Operating System for MICRONET, A Reconfigurable Network Computer," *IEEE-TC*, Vol. C-29, No. 12, Dec. 1980, pp. 1133-1144.

# Parallel Algorithms For River Routing<sup>1</sup> (Extended Abstract)

Shing-Chong Chang Department of Electrical Engineering and Systems Research Center University of Maryland College Park, MD 20742

#### Abstract

We develop efficient parallel algorithms for several river routing problems. These algorithms can be implemented on the CREW-PRAM model in  $O(\log n)$  or  $O(\log^2 n)$  time with O(n) processors, where n is the size of the input. Our algorithms have fast implementations on other parallel models such as the mesh or the hypercube.

# 1 Introduction

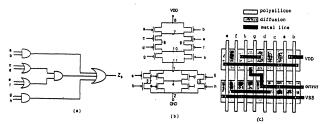

It is well-known that many of the optimization problems arising in VLSI routing are NP-complete (e.g. [KL],[L], [SB],[S]). One notable exception is the class of *river routing* problems associated with a hierechical layout strategy such as Bristle-Blocks([J]). See ([CS],[D et al],[LM],[LP], [M],[P],[SD],[T]) for more examples. In this paper, fast parallel algorithms for several river routing problems are presented. In particular,  $O(\log n)$  or  $O(\log^2 n)$  time algorithms with O(n) processors are developed for the separation problem and for the routability problem around a rectilinear polygon ([P]).

The above problems are considered in the CREW-PRAM model, which is characterized by the presence of an unlimited number of processors which can access a shared memory unit. Concurrent read is allowed while concurrent write is not. We are aiming for efficient parallel algorithms that run in  $O(\frac{T(n)}{p})$ , where p is the number of processors and T(n) is the running time of the best known sequential algorithm with input length n. In the rest of the paper, we assume that the reader is familiar with some of the basic parallel techniques such as path doubling, parallel prefix, and the Euler tour technique. Our algorithms can be mapped into fixed-interconnection parallel architectures such as the array architecture or the hypercube. For example, all the algorithms stated in this paper can be implemented on a  $\sqrt{n} \times \sqrt{n}$  mesh in time  $O(\sqrt{n})$ , where n is the input length.

Joseph JáJá

Department of Electrical Engineering Institute For Advanced Computer Studies and Systems Research Center University of Maryland College Park, MD 20742

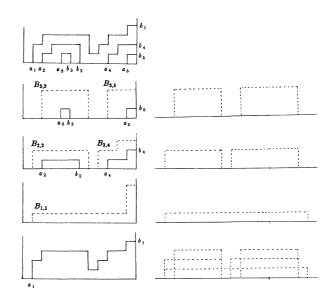

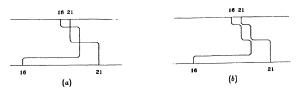

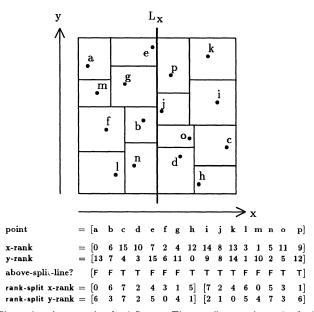

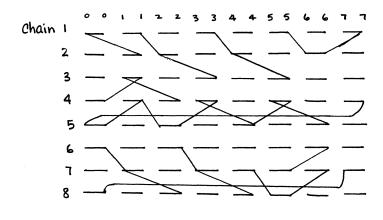

The class of general river routing problems involves routing between ordered sequences of terminals such that the final layout is planar. One such problem is the wiring of two ordered sets of terminals  $\{b_0, b_1, \ldots, b_{n-1}\}$  and  $\{t_0, t_1, \ldots, t_{n-1}\}$  across a channel between the parallel boundaries of two rectangles. The width of the channel is the vertical distance between the two lines forming the channel. The *separation problem* is to find the minimum width of the channel necessary to wire all nets such that any two wires are separated by a unit distance. We will restrict ourselves to the case where the wires are rectilinear, i.e., there is a grid structure such that each wire consists of a set of grid line segments. Our methods generalize for all the other known variations ([SD],[T]).

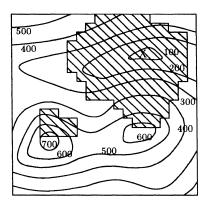

A more general version of the river routing problem that is known to have an efficient serial algorithm is to perform planar routing where the ports lie on the boundary of a simple rectilinear polygon. In this case, we are interested in whether the routing is possible or not and, if it is possible, we have to provide the detailed routing. Several interesting subproblems such as finding the contour of the union of a set of rectilinear polygons or determining whether a set of nets can be wired within a set "passages" are also tackled.

# 2 The Separation Problem