LNW Research Corp.

# LNW80 Technical Reference Manual

5000/5200-882

# LNW80 MICRO COMPUTER

# TECHNICAL REFERENCE MANUAL

ΒY

# DAVID L. KELLY

# FIRST EDITION - 1982

All rights reserved. Reproduction or use, without express permission is prohibited. While every effort was taken in the preparation of this book, the publisher assumes no liability for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

Copyright©1982, LNW RESEARCH CORP.

# CONTENTS

|         | P AG E                                      |

|---------|---------------------------------------------|

| I.      | SYSTEM OVERVIEW                             |

|         | CENTRAL PROCESSING UNIT                     |

|         | READ ONLY MEMORY                            |

|         | RANDOM ACCESS MEMORY                        |

|         | XEYBOARD                                    |

|         | VIDEO & VIDEO PROCESSING                    |

|         | TAPE INTERFACE                              |

|         | SERIAL INTERFACE                            |

|         | · · · · · · · · · · · · · · · · · · ·       |

|         | FLOPPY DISK CONTROLLER                      |

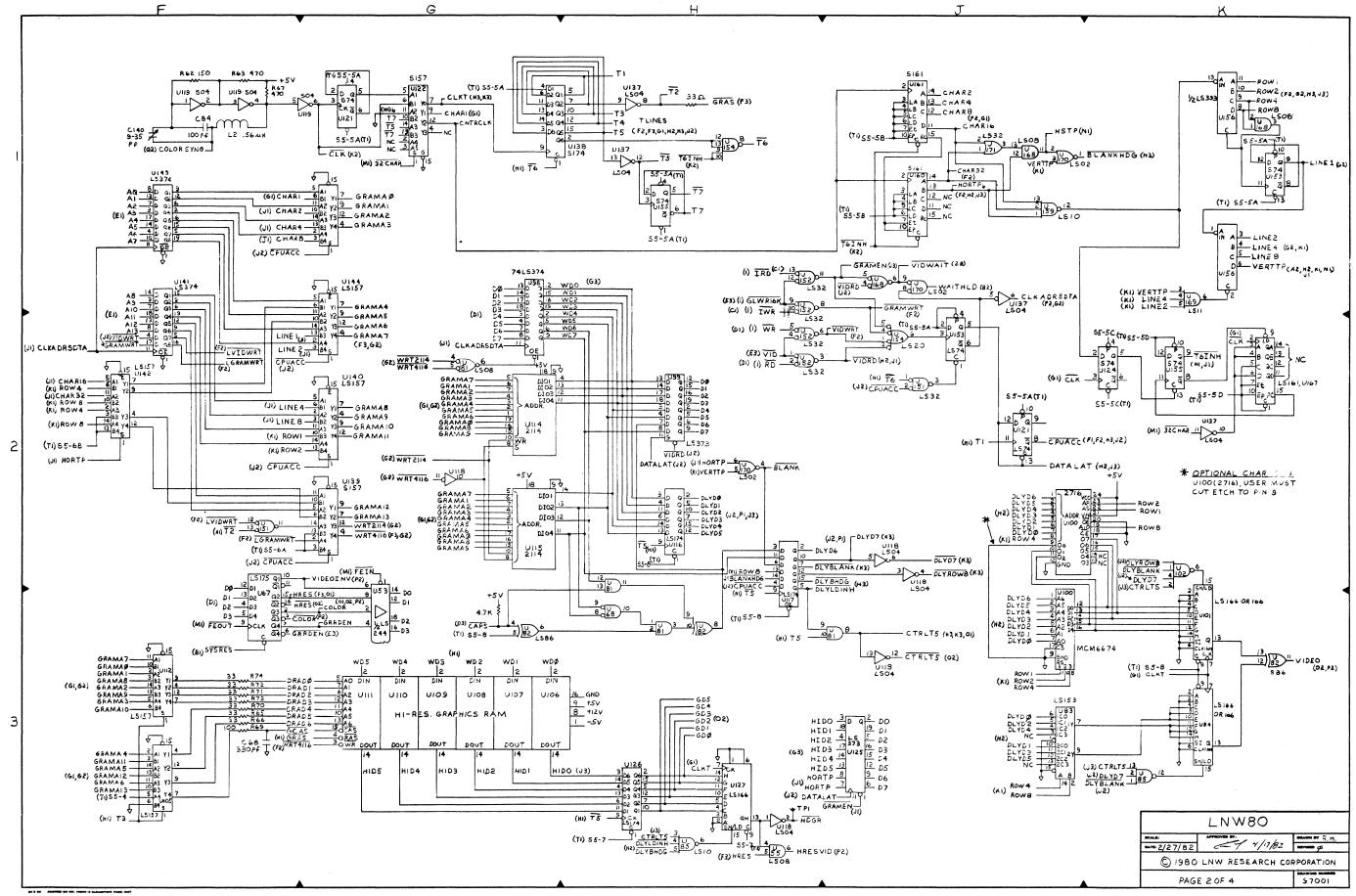

| II.     | THEORY OF OPERATIONS LNW80 BOARD            |

| <b></b> | SYSTEM CLOCK                                |

|         | CPU ADDRESS LINES                           |

|         |                                             |

|         | CPU DATA BUS                                |

|         | • •                                         |

|         | CPU CONTROL SIGNALS                         |

|         | ADDRESS DECODING CIRCUIT                    |

|         | INW80 MEMORY MAP                            |

|         | READ ONLY MEMORY                            |

|         | PROGRAM RAM                                 |

|         | XEYBOARD                                    |

|         | /IDEO DIVIDER CHAIN                         |

|         | /IDEO RAM ADDRESSING14                      |

|         | OW RESOLUTION VIDEO RAM                     |

|         | II RESOLUTION GRAPHICS RAM                  |

|         | /IDEO DATA LATCH                            |

|         | CHARACTER GENERATOR                         |

|         | GRAPHICS GENERATOR                          |

|         | ALPHA NUMERIC/GRAPHIC SHIFT REGISTERS       |

|         |                                             |

|         | INVERSE VIDEO                               |

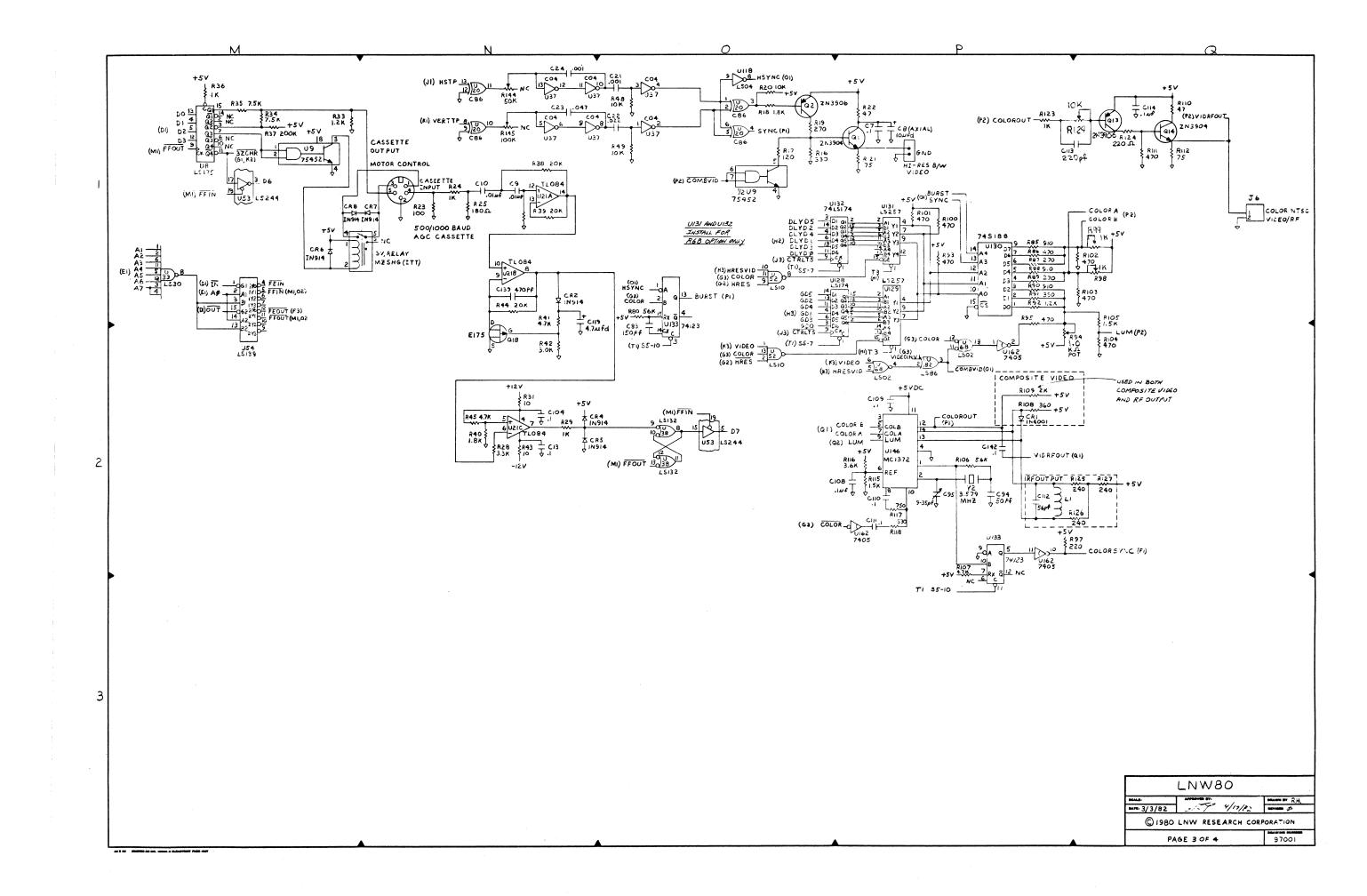

|         | HORIZONTAL & VERTICAL SYNC TIMING           |

|         | COMPOSITE VIDEO MIXING CIRCUITS             |

|         | NTSC COLOR VIDEO                            |

|         | COLOR BURST ONE-SHOT                        |

|         | J146 - MC1372 COLOR ENCODER                 |

|         | HI RESOLUTION COLOR                         |

|         | BLACK & WHITE THRU NTSC CHANNEL             |

|         | CASSETTE                                    |

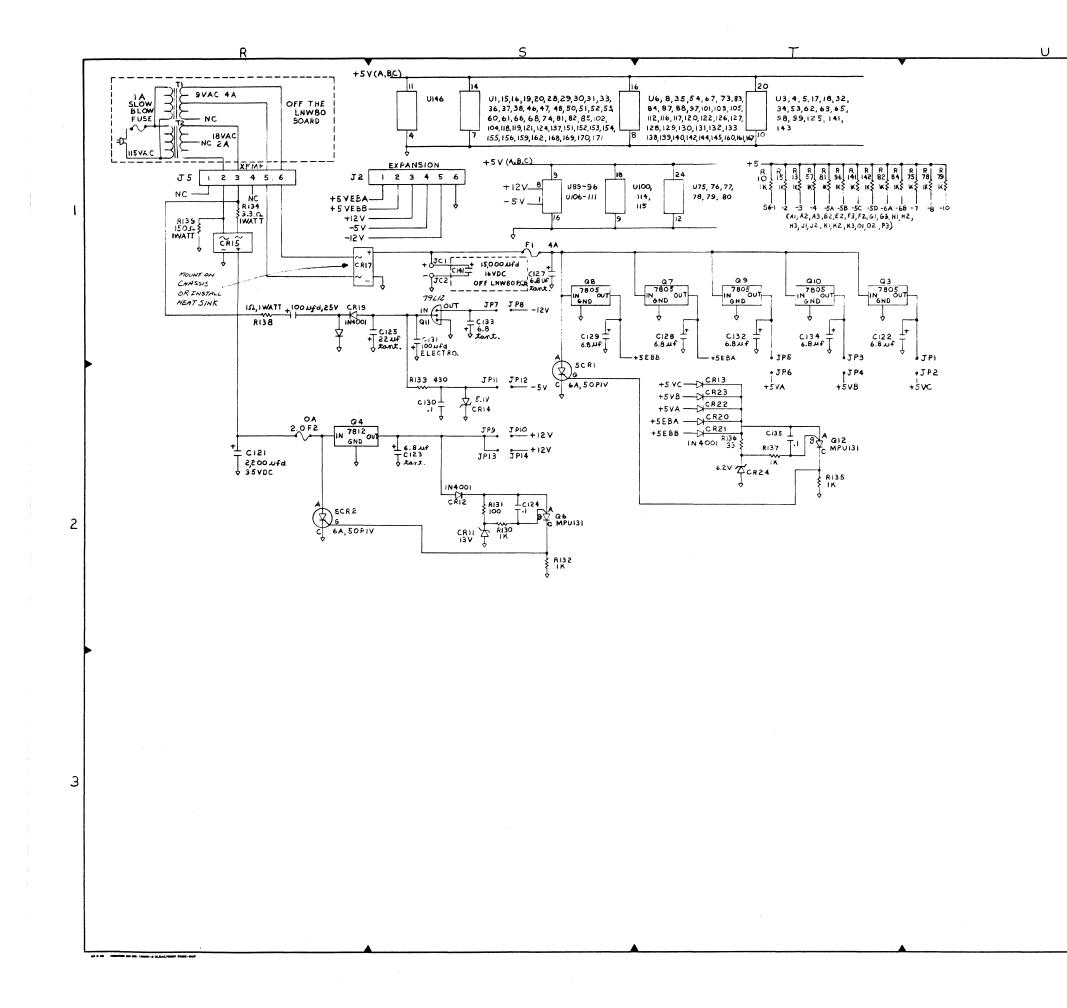

|         | POWER                                       |

|         |                                             |

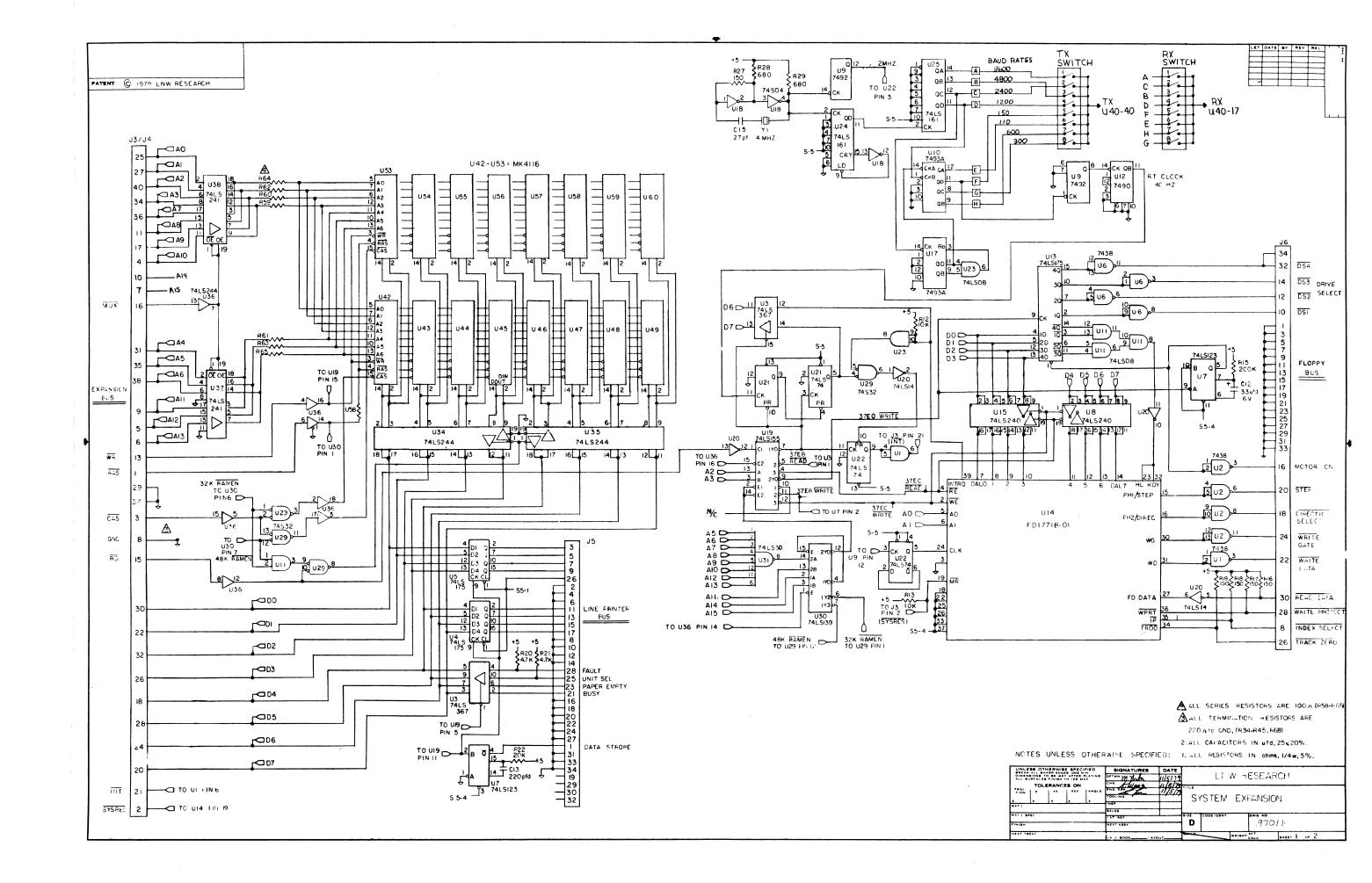

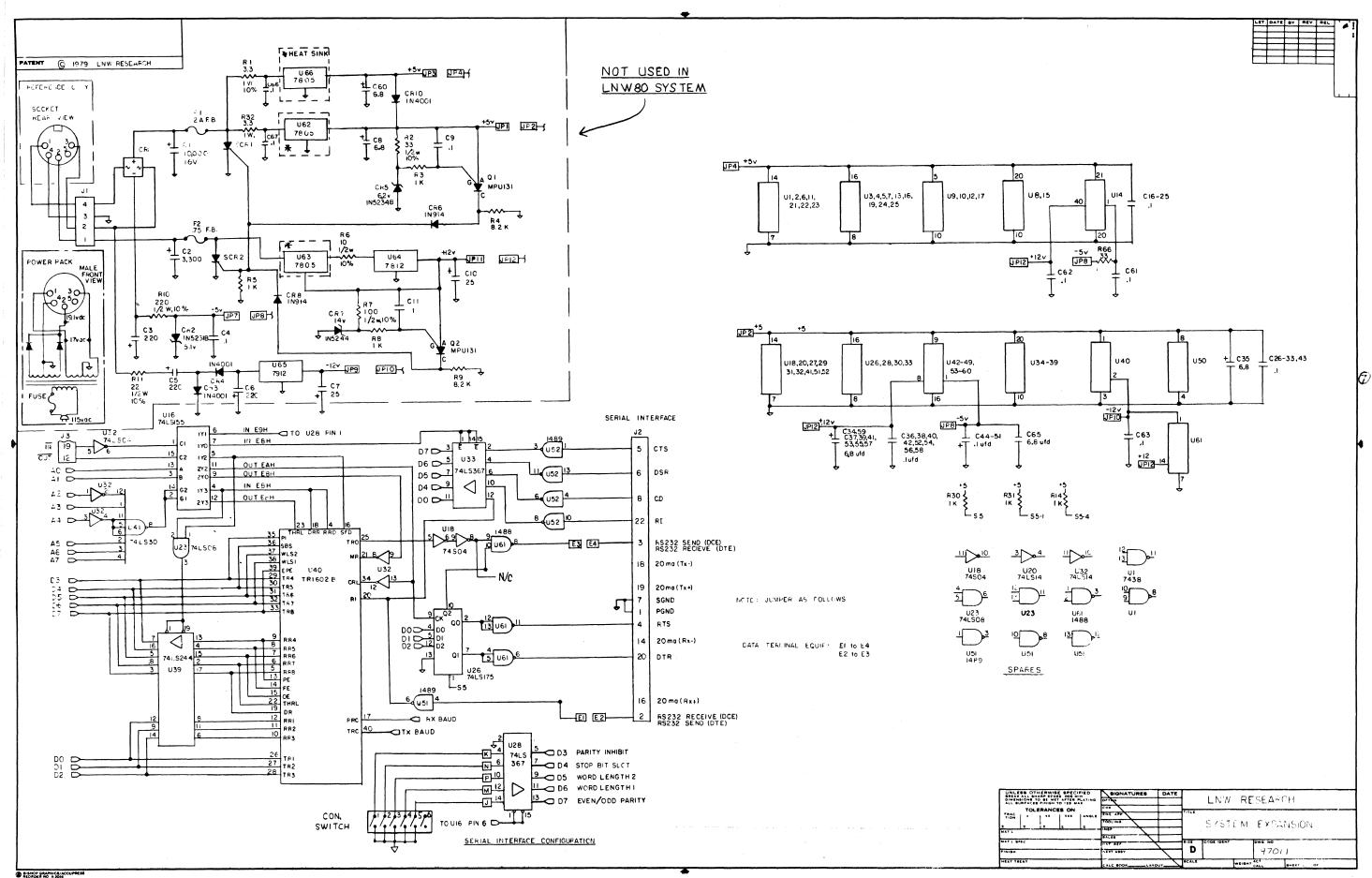

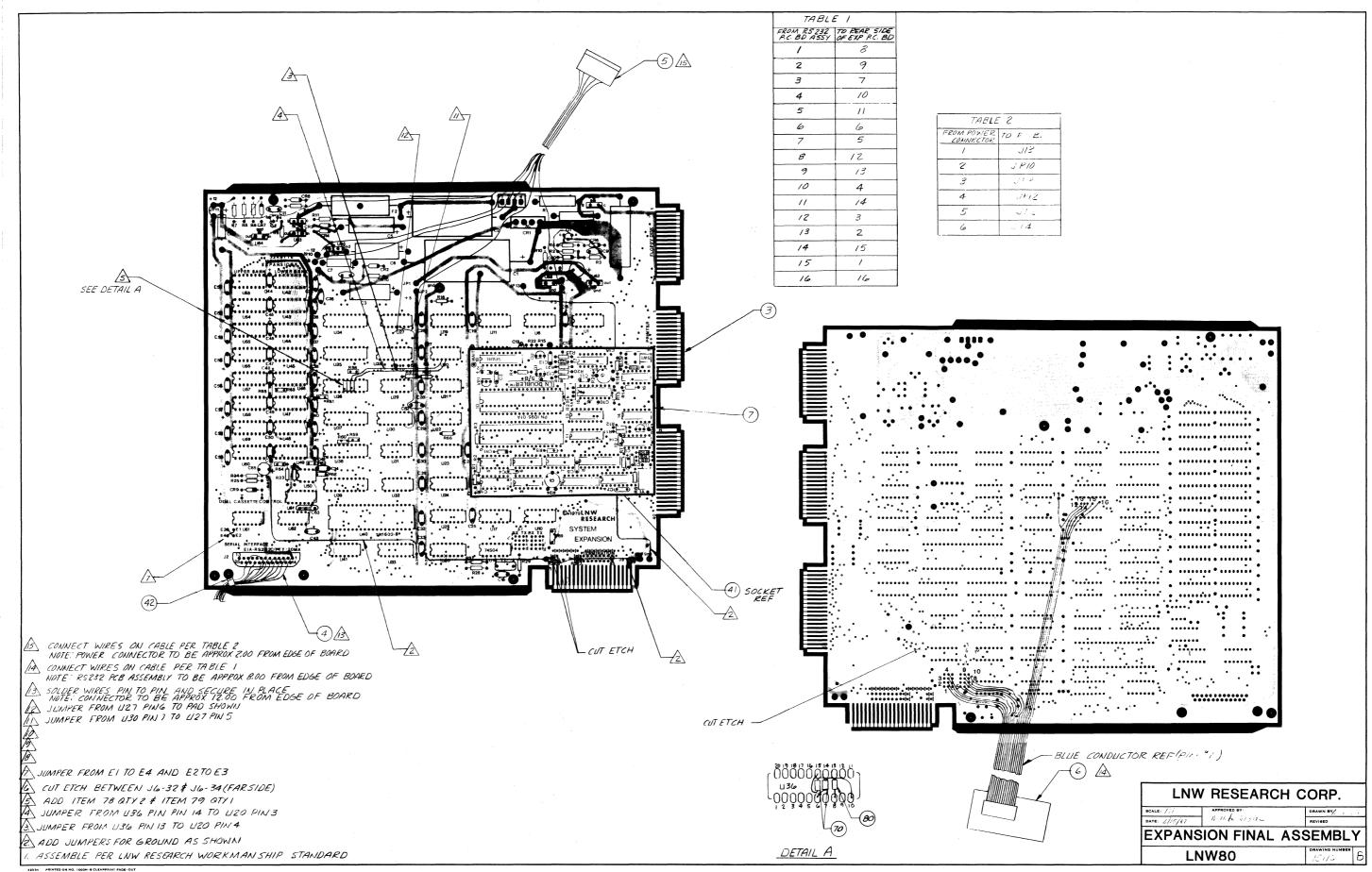

| III.    | THEORY OPERATIONS EXPANSION BOARD           |

|         | EXPANSION BUS                               |

|         | MEMORY EXPANSION                            |

|         | FLOPPY CONTROLLER & PRINTER DECODING        |

|         | PARALLEL LINE PRINTER PORT                  |

|         | CLOCK CIRCUIT                               |

|         | FLOPPY DISK INTERFACE                       |

|         | SERIAL INTERFACE                            |

|         | BAUD RATE GENERATION                        |

|         | TR1602B UART                                |

|         | E1A RS232C & 20 mA LEVEL SHIFTS & RECEIVERS |

|         |                                             |

|         | HANDSHAKE LATCH                             |

|         | MODEM STATUS BUFFER                         |

|         | CONFIGURATION SENSE JUMPERS                 |

|         | DECODING & LOGIC CONTROL                    |

|         | SERIAL INTERFACE PORT ADDRESSING40          |

|         | REAL TIME CLOCK                             |

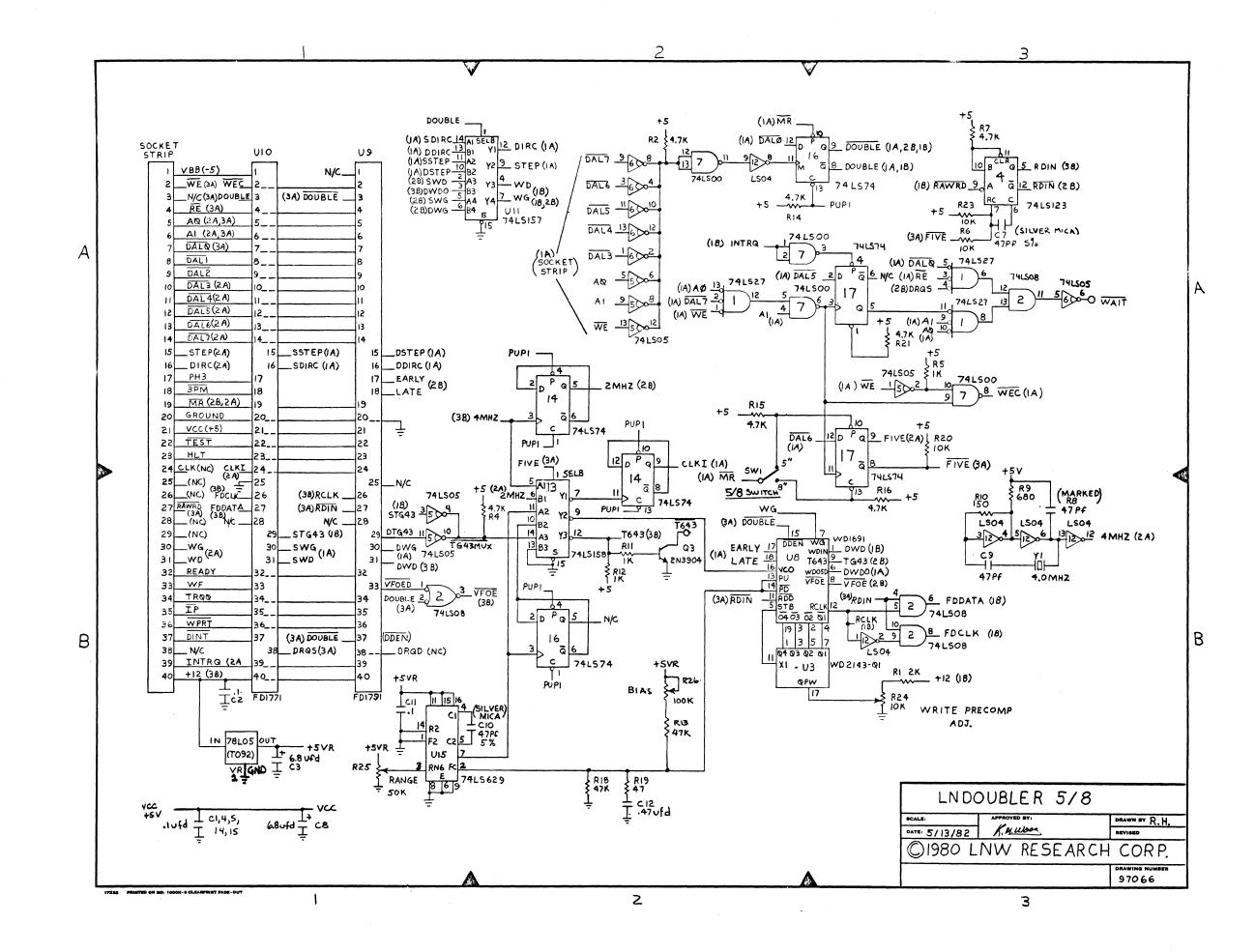

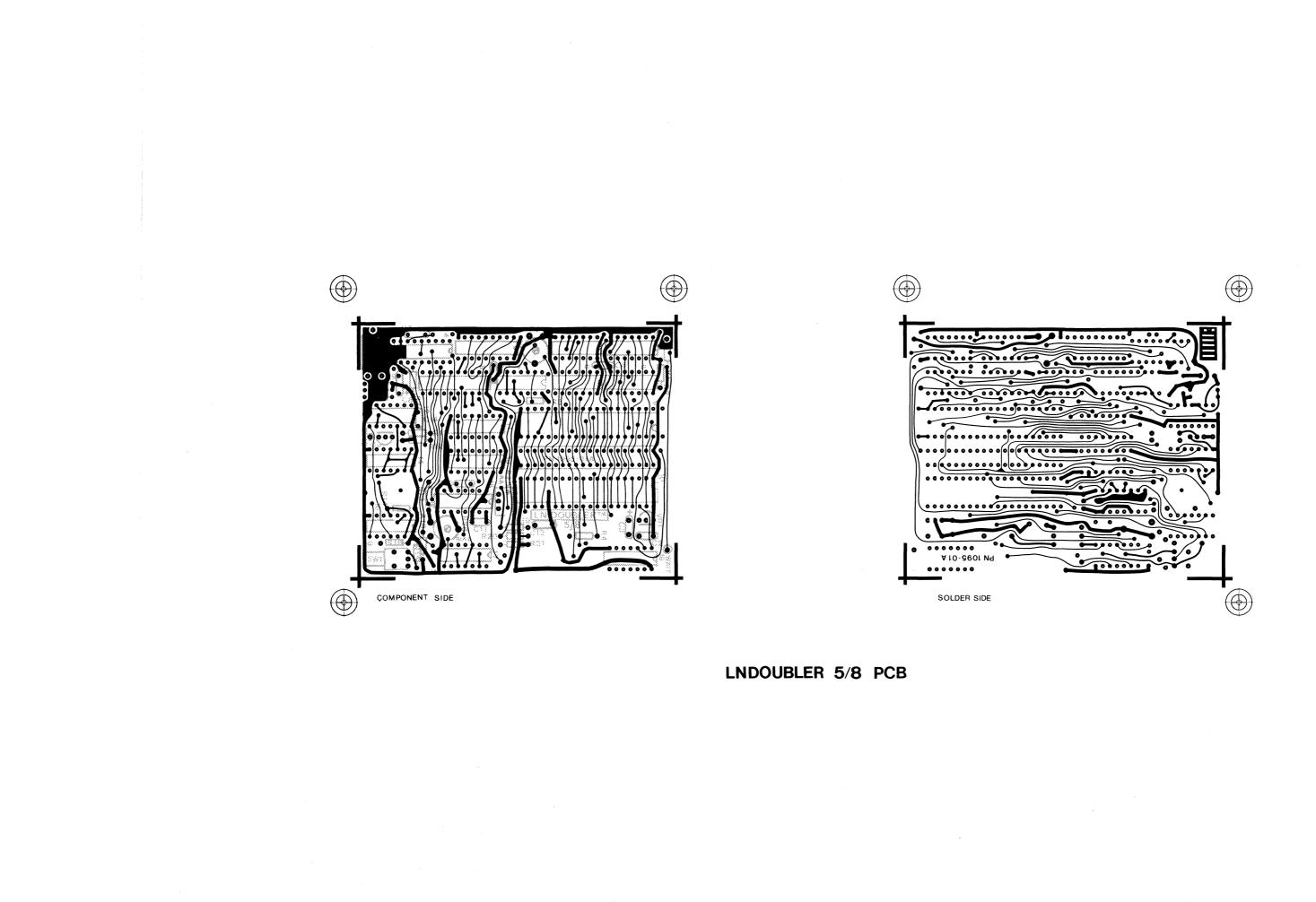

| IV.   | THEORY OPERATIONS 5/8 DOUBLER                                                                                                                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ν.    | TROUBLESHOOTING46POWER SUPPLY46VIDEO OUTPUT/ADJUSTMENTS46SYSTEM CLOCK46CPU/CPU TEST47CPU/CPU TEST PROGRAM48SCOTCH TAPE TRICK50HI RESOLUTION GRAPHICS50HI RESOLUTION GRAPHICS TEST51COLOR GRAPHICS TEST & ADJUSTMENT52 |

| VI.   | TROUBLESHOOTING THE EXPANSION INTERFACE                                                                                                                                                                               |

| VII.  | 5/8 DOUBLER ALIGNMENT                                                                                                                                                                                                 |

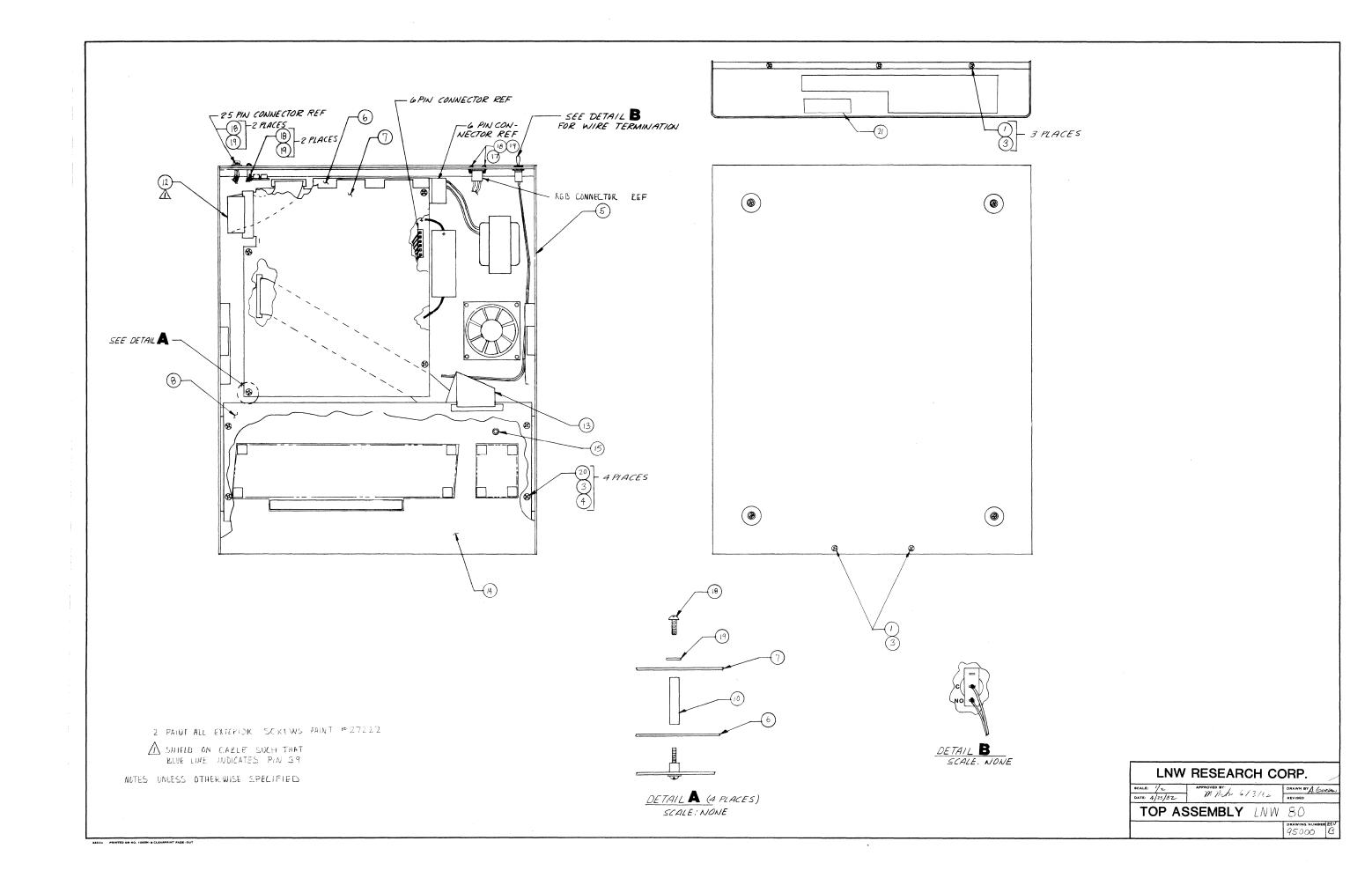

| VIII. | DISASSEMBLY/ASSEMBLY                                                                                                                                                                                                  |

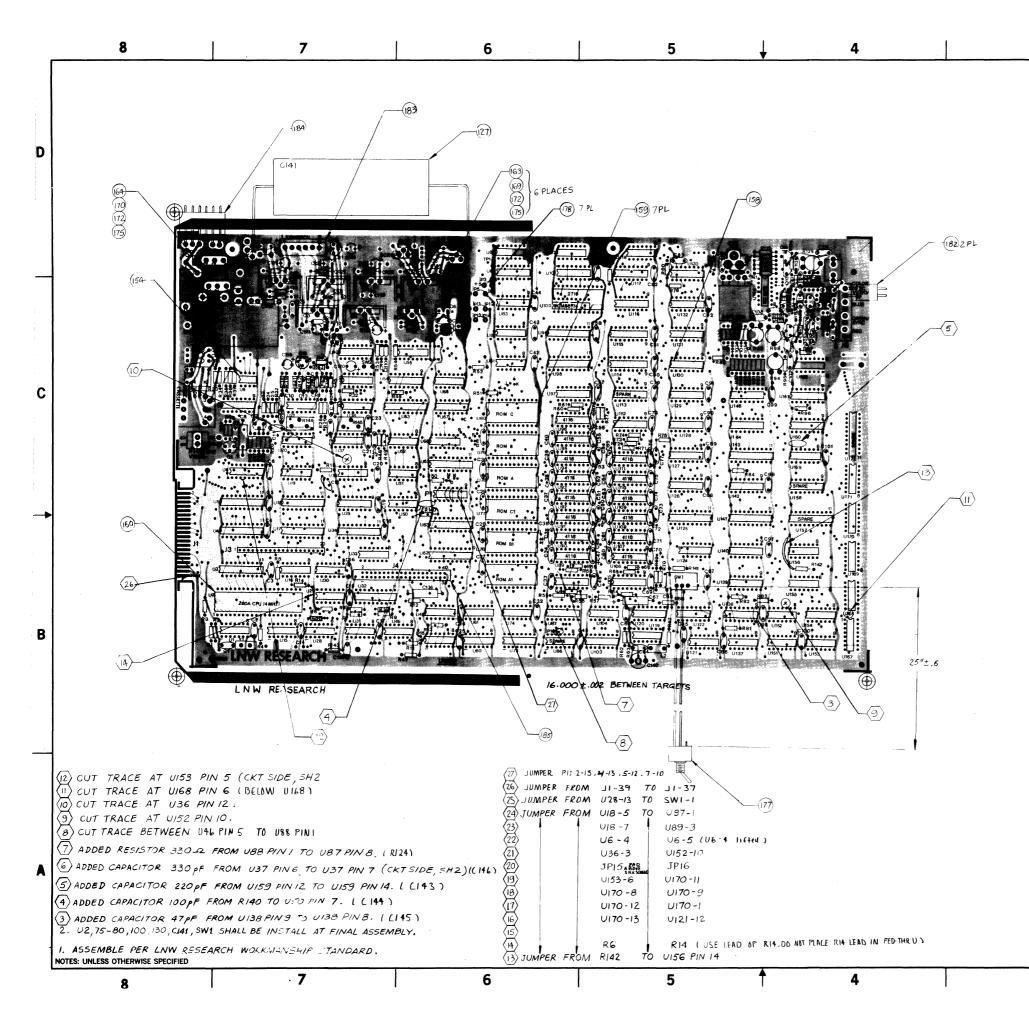

| IX.   | ENGINEERING CHANGE NOTICES                                                                                                                                                                                            |

| Χ.    | RGB OPTION                                                                                                                                                                                                            |

| XI.   | PARTS LIST LNW80 COMPUTER BOARD                                                                                                                                                                                       |

| XII.  | PARTS LIST EXPANSION INTERFACE                                                                                                                                                                                        |

| XIII. | PARTS LIST 5/8 DOUBLER                                                                                                                                                                                                |

| XIV.  | PARTS LIST CASE ASSEMBLY                                                                                                                                                                                              |

| XV.   | APPENDIX 1 - DATA SHEETS                                                                                                                                                                                              |

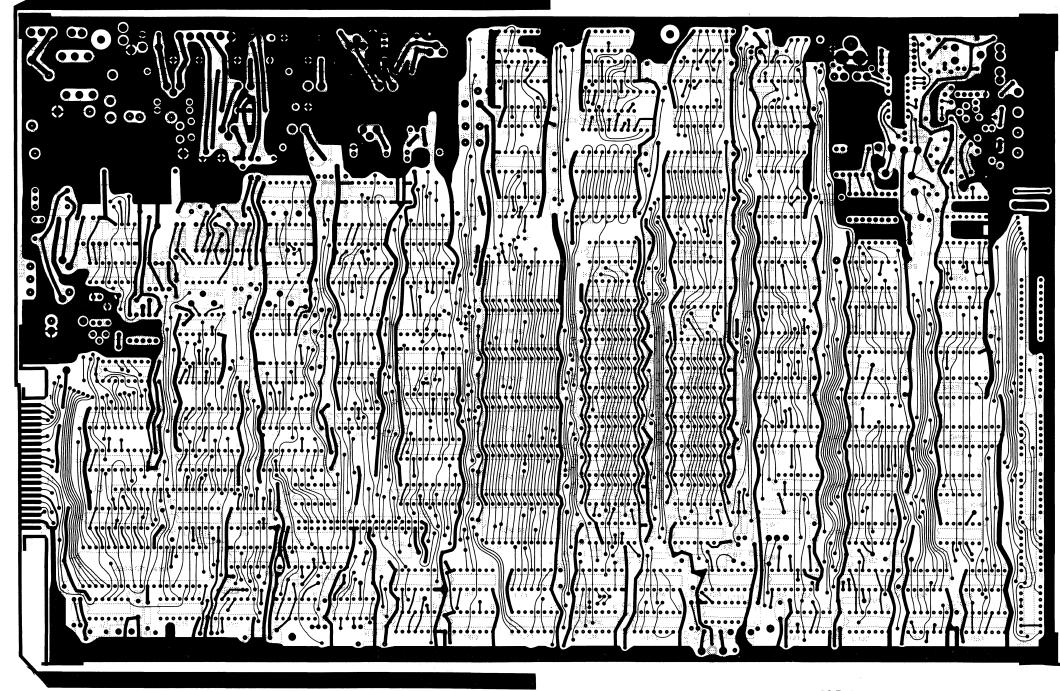

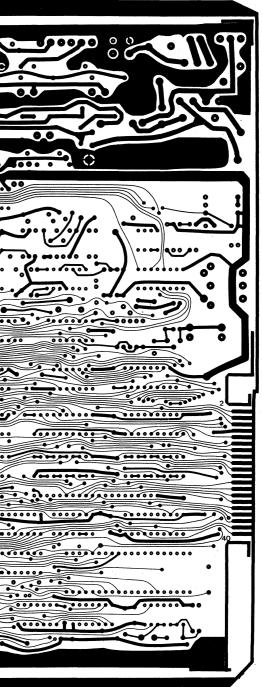

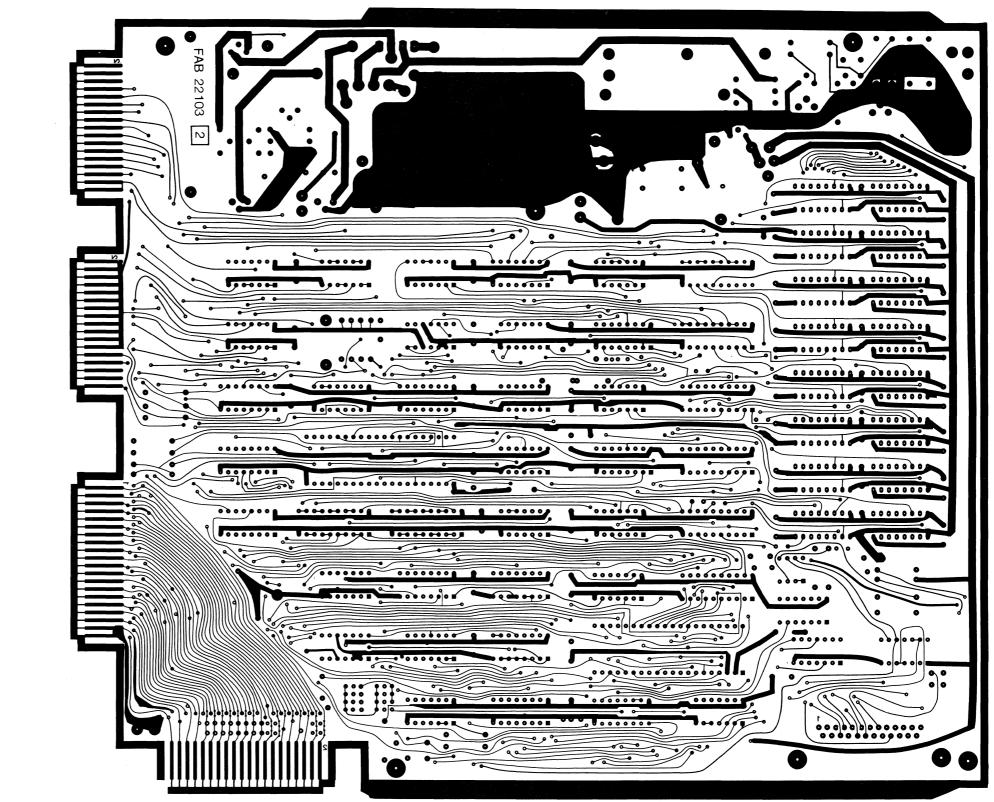

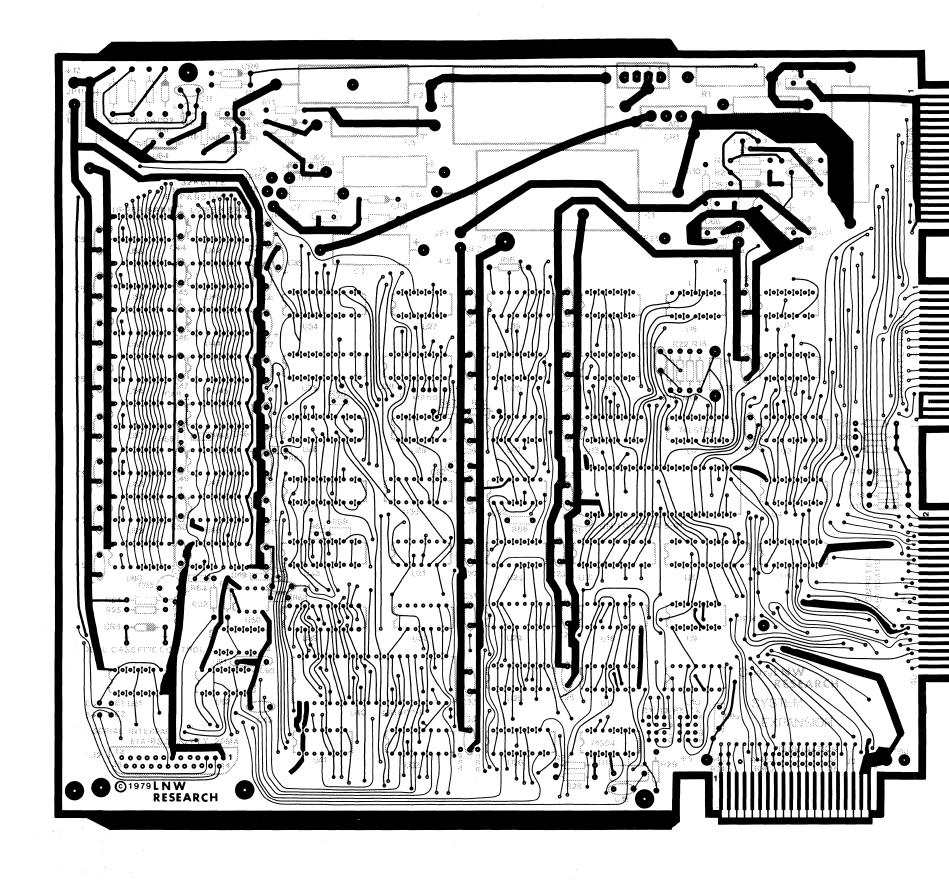

| XVI.  | APPENDIX 2 - ENGINEERING DRAWINGS                                                                                                                                                                                     |

# INTRODUCTION

This book was written for those people who have the technical knowledge to understand how a computer operates. This requires that the reader has a through understanding of digital logic. Armed with a TTL DATA BOOK and this manual such a person can understand the complex internal operation of the LNW80 COMPUTER.

Remember that any work you do to your LNW80 voids all warranties, implied or expressed. Also we will not repair or correct owner modifications. We cannot possibly support owner hardware/circuit ideas on how to customize the LNW80.

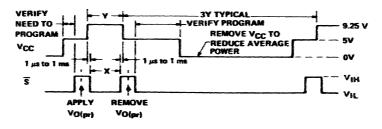

In the following sections refer closely to the schematics and the system block diagram which can be found at the end of the manual. Good luck and have fun.

## SYSTEM OVERVIEW

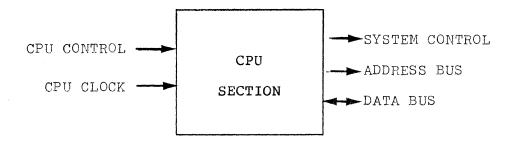

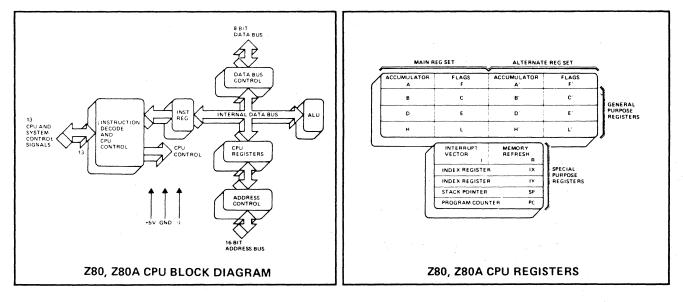

#### CENTRAL PROCESSING UNIT (CPU)

The heart of the LNW80 is the Z80A CPU. The Z80A has 16 address lines and therefore 65536 addressable memory locations. The Z80A receives instructions from the ROM or RAM and proceeds to execute them. Only the CPU interacts with all other sections within the computer. The CPU section includes not only the Z80A but also the data and address buffers, wait logic, and system control logic.

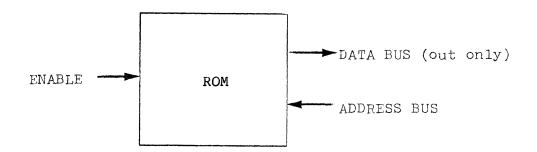

READ ONLY MEMORY (ROM)

The ROM contains non-erasable data that is used to provide the CPU with instructions necessary for the system's operation. Upon power up the CPU outputs to the ROM for its first instruction after which the ROM takes over and instructs the CPU exactly how to perform the necessary functions to get the system operating.

1

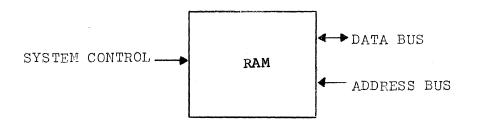

## RANDOM ACCESS MEMORY (RAM)

The RAM is where the CPU stores data. This data may consist of program information. The RAM differs from the ROM in that data may be written to as well as read from the RAM by the CPU.

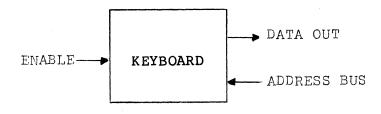

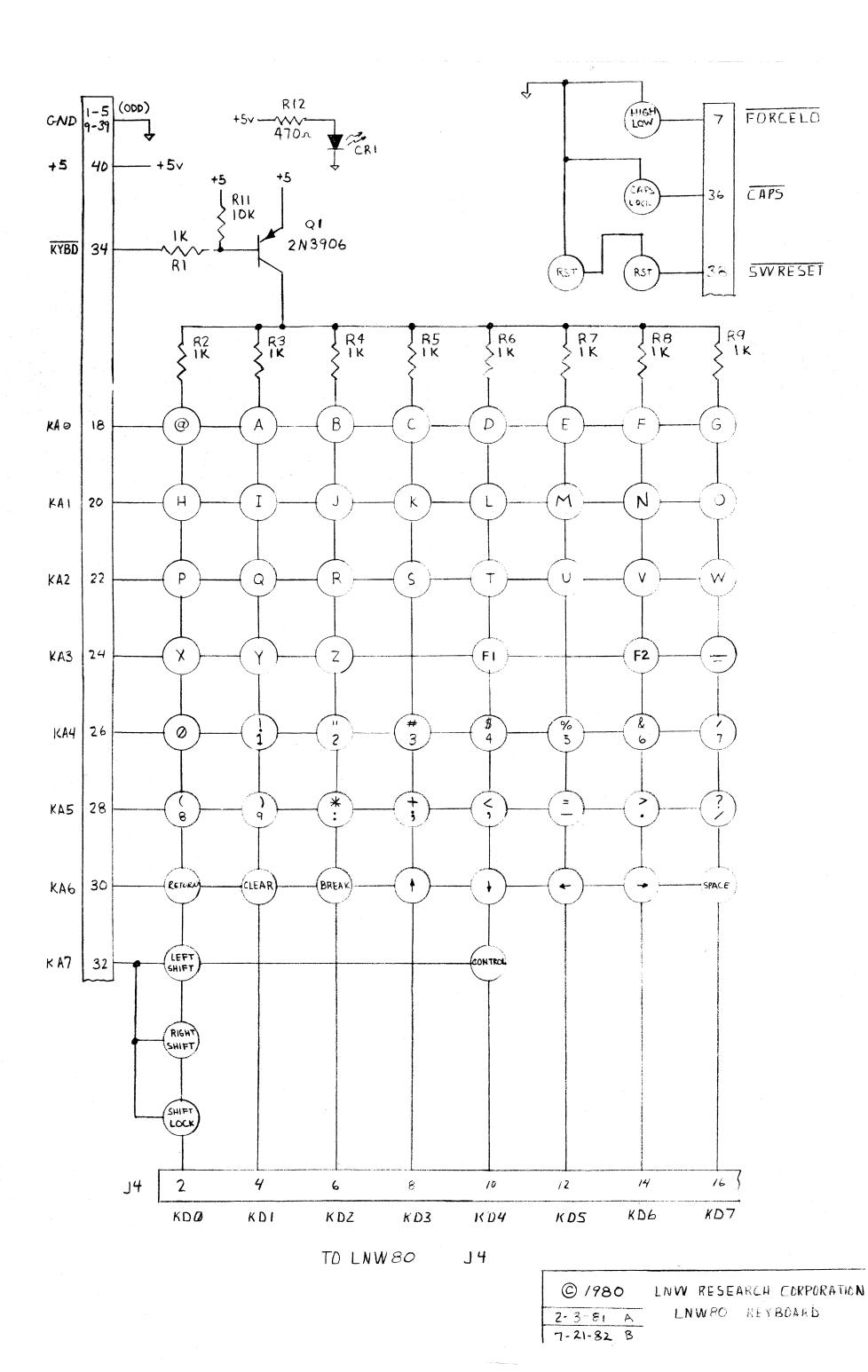

#### KEYBOARD

The keyboard is used to input instructions from the user to the CPU.

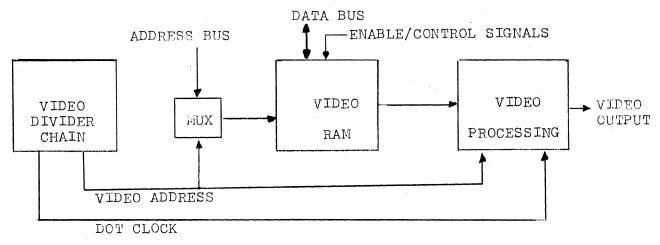

## VIDEO RAM AND PROCESSING

The video is used to inform the user what the system is doing. All data that is stored in the video ram is automatically displayed on the CRT by the video processing unit. The data within the video ram is stored in ASCII. Utilizing the Character Generator the ASCII is translated into a dot pattern that represents the desired character.

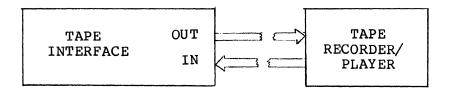

TAPE INTERFACE

The tape interface stores data on tape so that it can be recovered at a later date.

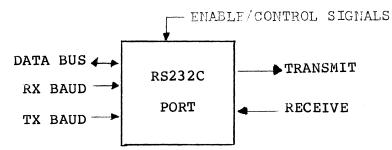

SERIAL INTERFACE

The RS232C serial interface sends and receives data in serial fashion and converts that data to parallel form to be received by the CPU. This section is used to connect to such devices as modems and serial printers.

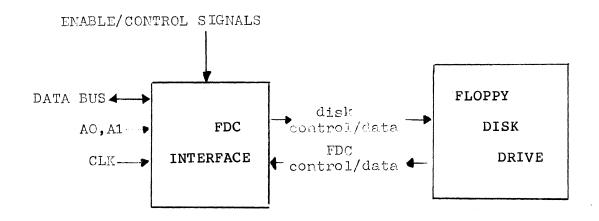

FLOPPY DISK CONTROLLER (FDC)

The FDC stores large amounts of data and thus increases the storage copacity of the system.

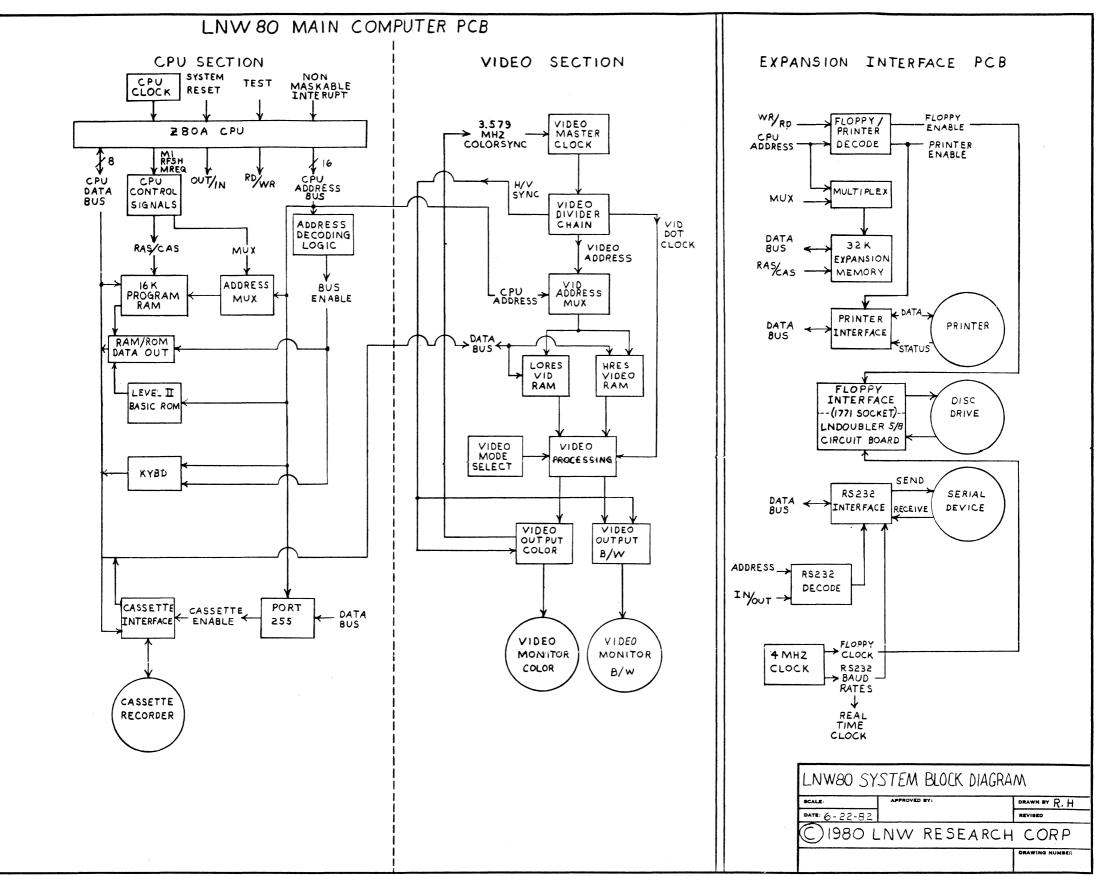

## THEORY OF OPERATIONS LNW80 BOARD

## SYSTEM CLOCK

The system clock is a 16MHz oscillator utilizing Y1 and U1 to form a series resonant circuit. U87, a synchronous 4-bit counter, is used to perform the divide by four for the 4MHz and a divide by nine for the 1.77MHz CPU operation. When the HI/LO switch is depressed, the signal FORCELO\* (U29-5) is a logic "Ø" resulting with a preset of 1,0,0 at U87 pins 3,4, and 5 respectively. This preset will program U87 to divide by nine resulting in a 1.77MHz CPU clock at U2-6.

During 4MHz operation, U87 will be preset with Ø,1,1 at pins 3,4, and 5 respectively resulting in a divide by four of the system clock. At 4MHz, the signal NHI\* (U15-2) will be a logic "Ø". Thus when ROMRD\* (U15-1) is active, a WAIT\* will be generated through U31 to the CPU pin 24 allowing for the relatively slow access time of the ROM.

During automatic switching (SW1=1) when the floppy address (37EC) is decoded along with a logic "0" at IMREQ\*, the one-shot at U120 will be triggered forcing U120-4 low. This results with a logic "0" at U29-4 resulting in a CPU speed of 1.77MHz as when the HI/LO switch was depressed. The clock speed will remain at this state until the one-shot expires at which time the CPU automatically and synchronously returns to 4MHz.

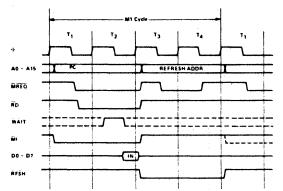

### CPU ADDRESS LINES

The Z80A provides 16 address lines which define the 64K of addressable memory locations. These address lines are buffered from the Z80A through U3 and U5. U3-1 and U5-1 should be a logic "0" thus enabling their outputs at all times. The upper addresses are latched through U5, an LS373, to prevent the address from changing prematurely. During refresh time, the lower 7 bits contain a valid refresh address.

#### CPU DATA BUS

The CPU utilizes an 8-bit bidirectional data bus. The data bus is used for data exchanges with memory and I/O devices. The data is buffered through U4 and U17. DBIN (U1-10) is used for directional control. When DBIN is a logic "1" the CPU is receiving data. When DBIN is low the CPU is sending data.

# WAIT\*, INT\*, and TEST\*

The WAIT\* input to the Z80A CPU will cause the Z80A to extend its cycle, resulting in slowing down the CPU. The LNW80 utilizes one WAIT function when a ROM read is in process and one or two waits when accessing the video memory. These waits are required in the hi-speed mode of 4MHz to ensure data validity when accessing the slower memory devices. There are no wait states when accessing the program memory (RAM) on the LNW80 (requiring 200ns or faster RAM's).

The wait term is generated by U31. U31-3, the clock, is delayed by U16. This clock delay results in proper data setup time to U31. U61-3 is WAITHLD. This will increase the wait from the usual one wait state for the Level II ROM's, to multiple wait states when reading from the video memory. Pin 33 of J1 is the bus WAIT signal. This input may be utilized by other external devices that may wish to pose a wait condition on the Z80A procesor.

The INT\* signal is a maskable interrupt to the Z8ØA pin 16. The Level II Basic ROM utilizes interrupt mode 1. When the CPU is interrupted, a restart to location ØØ38H is executed.

Pin 23 of Jl is TEST\* which is a busrequest signal to the Z8ØA CPU. The CPU responds by tri-stating its data, address and output control signals. Since the Z8ØA CPU is fully buffered, all the buffers (U3, U4, U5, U17, and U18) will also be tri-stated. Once these buffers are tri-stated, any device on the expansion bus may control the function of the LNW8Ø board. One important consideration is that the dynamic program RAM's are refreshed by the Z8ØA processor. Therefore, any controlling device on the expansion bus must consider memory refresh.

## CPU CONTROL SIGNALS

The ZRD\* signal is a tri-state output, active low. ZRD\* indicates that the CPU is ready to receive data from memory or an I/O device. It is input to U36 pins 4 and 12. When U36-12 goes low it enables DBIN. When ZRD\* and ZMREQ\* go low, they enable IRD\* (U36-6). RDOUT\* will also be enabled if RDWRDIS (U51-8) is true. Note that RDWRDIS is used to disable the lower 16K when the HI RESOLUTION GRAPHICS RAM are enabled.

ZWR\* indicates that the CPU holds valid data to be stored in memory or an I/O device. When ZWR\* and ZMREQ\* both go low, IWR\* (U36-3) is enabled. WROUT\* (U36-11) will also be enabled if RDWRDIS is true.

ZMREQ\* indicates that the address bus holds a valid address for a read or write operation. Note that it is also used for memory refreshing.

ZIORQ\* indicates that the lower half of the address bus holds a valid I/O address for an I/O read or write operation. It is used as the enable at U35-15. When combined with a WR\*, IOUT\* will be enabled (U35-9). When ZIORQ\* is combined with a RD\*, IIN\* will be enabled (U35-11). ZIORQ\* is also combined with ZM1\* when an interupt is being acknowledged.

RFSH\* indicates that the lower 7 bits of the address contains a refresh address for dynamic memories and the current MREQ\* signal is used to do a refresh read to all dynamic memories. Note that it is used to clear U46-5 during refresh time. Resulting in the selection of the lower seven address lines and a logic "1" for the CAS\* signal.

#### ADDRESS DECODING CIRCUIT

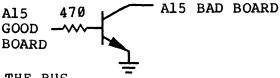

The address decoding circuit consists of U6 and U35. The decoding circuit uses the higher order address bits to enable the locations within the memory map which the CPU wishes to access. U6 is a 3 to 8 line decoder. It uses Al5 and IMREQ\* as enables and Al2, Al3, and Al4 as inputs. Refer below for a listing of the memory mapped sections of the LNW80 along with their decoded addresses.

| ADDRESS                                                     |                                                      |                                                                                                                                                                                                        |  |  |

|-------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DECIMAL                                                     | HEX                                                  | DEVICE                                                                                                                                                                                                 |  |  |

| Ø<br>12288                                                  | Ø<br>3000                                            | BASIC ROM                                                                                                                                                                                              |  |  |

| 12289<br>14301                                              | 3001<br>37DD                                         | UNUSED                                                                                                                                                                                                 |  |  |

| 14302<br>14303<br>14304<br>14305<br>14308<br>14312<br>14316 | 37DE<br>37DF<br>37EØ<br>37E1<br>37E4<br>37E8<br>37EC | COMMUNICATION STATUS ADDRESS<br>COMMUNICATION DATA ADDRESS<br>INTERUPT BATCH ADDRESS<br>DISK DRIVE SELECT LATCH<br>CASSETTE SELECT LATCH<br>PARALLEL PRINTER ADDRESS<br>FLOPPY DISK CONTROLLER ADDRESS |  |  |

| 14336<br>14591                                              | 38ØØ<br>38FF                                         | KEYBOARD                                                                                                                                                                                               |  |  |

| 1536Ø<br>16383                                              | 3CØØ<br>3FFF                                         | LO-RES VIDEO RAM                                                                                                                                                                                       |  |  |

| 16384<br>32767                                              | 4000<br>7FFF                                         | 16K PROGRAM RAM                                                                                                                                                                                        |  |  |

| 32768<br>65535                                              | 8000<br>FFFF                                         | 32K RAM (EXPANSION BOARD)                                                                                                                                                                              |  |  |

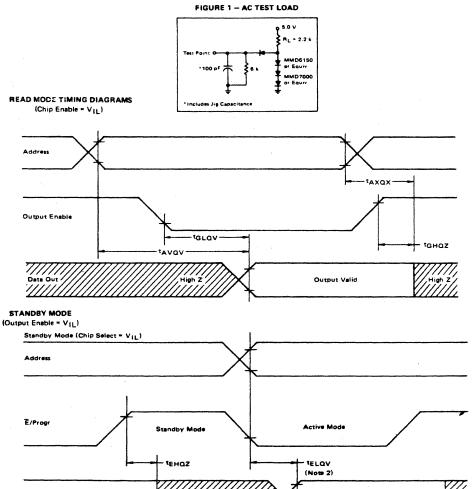

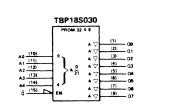

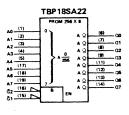

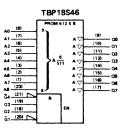

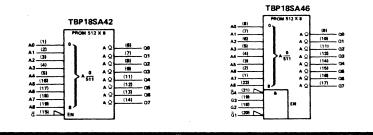

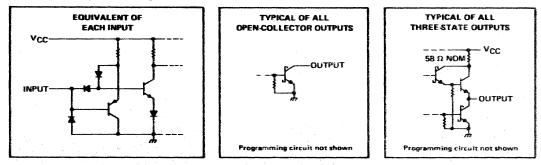

## ROM

The LNW80 ROM consists of six EPROMs. ROMA is memory mapped from 0 to 2K, ROMAl from 2K to 4K, ROMB from 4k to 6K, ROMBl from 6K to 8K, ROMC from 8K to 10K, and ROMCl from 10K to 12K.

Each ROM has three enables. Pin 21 is an active high enable and pins 18 and 20 are active low enables. Pin 21 is pulled high on all ROMs with 33 ohm pull-up resisters.

ROMA and ROMA1, pins 20 are enabled by "0-4K\*" (U6-15). "0-4K\*" goes low when U6 pins 1,2,3,4, and 5 are at logic levels "0", "0", "0", "0, and "0" respectively. RAll is inverted at U50-8 and enables either ROMA and ROMA1 at pins 18.

ROMB and ROMB1, pins 20 are enabled by "4-8K\*" (U6-14). "4-8K\*" goes low when U6 pins 1,2,3,4, and 5 are

at logic levels "l","0","0","0", and "0" respectively. RAll enables either ROMB or ROMB1 at pins 18.

ROMC and ROMC1, pins 20 are enabled by "8-12K\*" (U6-13). "8-12K\*" goes low when U6 pins 1,2,3,4, and 5 are at logic levels "0,"1","0","0", and "0" respectively. RAll enables ROMC or ROMC1 at pins 18.

Addresses AØ through All are buffered through U62 and U65, LS244's. The data bus out is buffered through U63 and is enabled by "RAM/ROM\*" (U52-6). "RAM/ROM\*" goes low when RD\* occurs with either "Ø-4K\*", "4-8K\*", or "8-12K\*".

# PROGRAM RAM

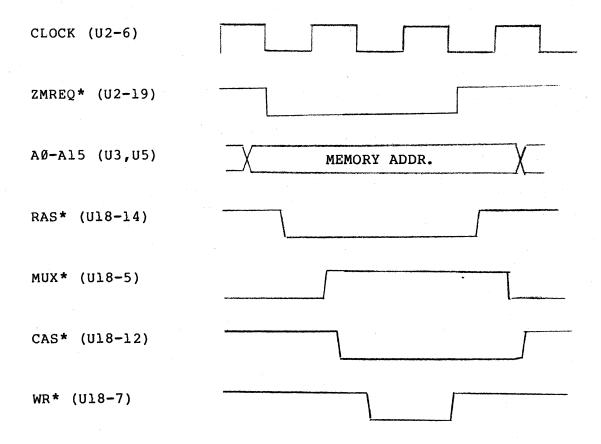

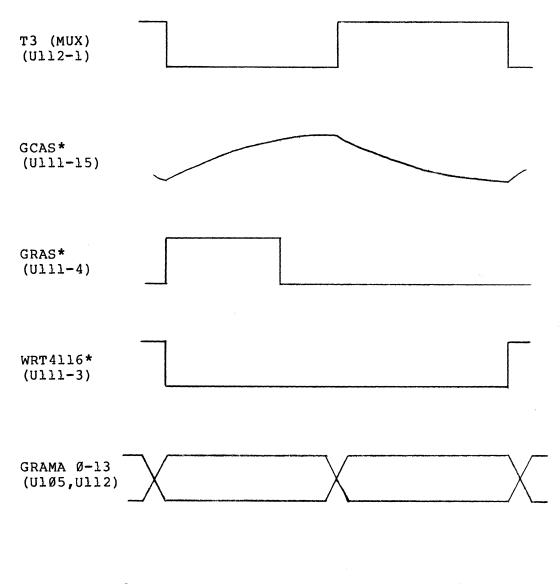

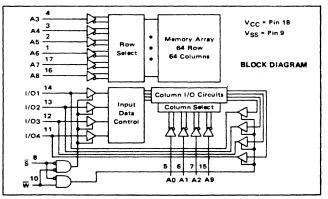

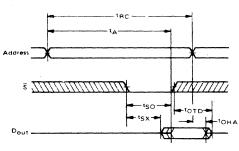

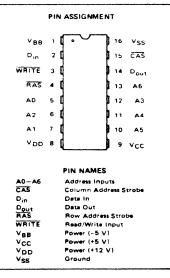

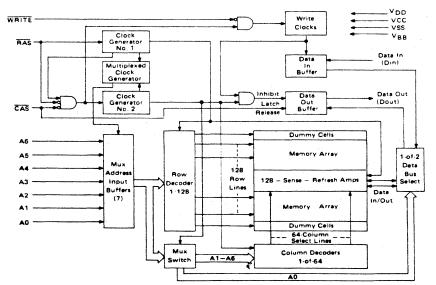

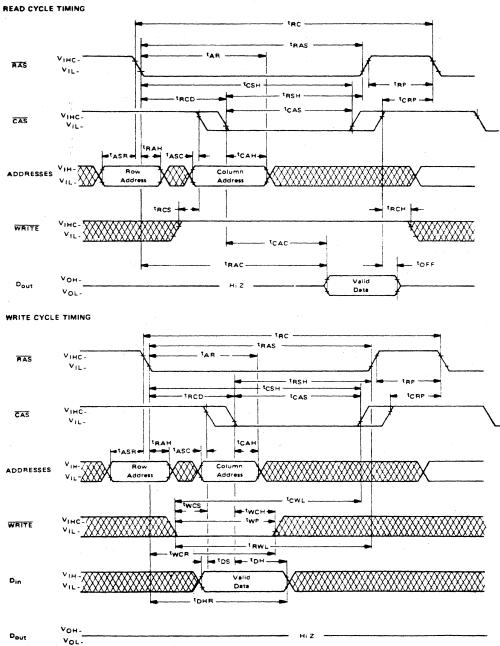

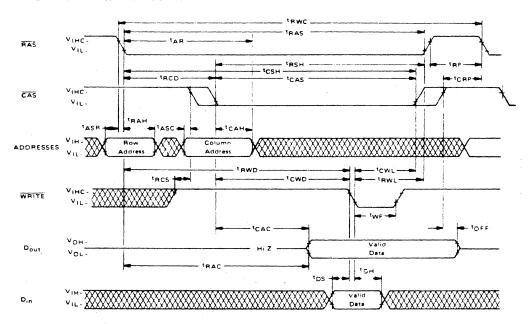

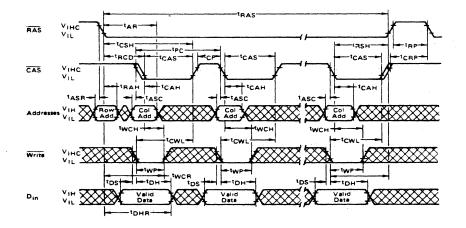

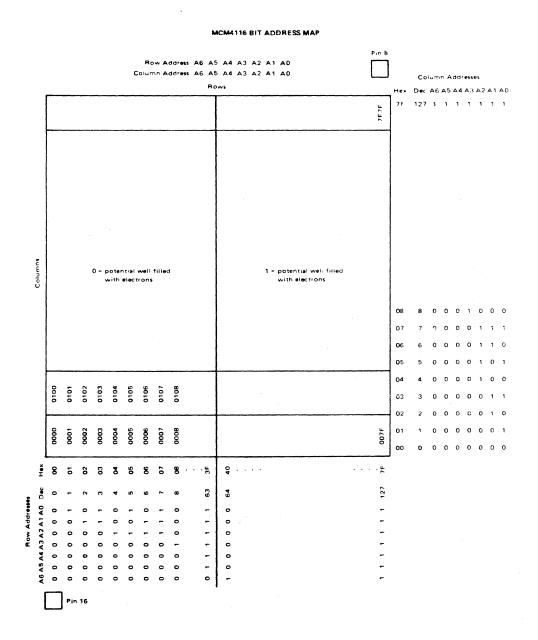

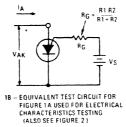

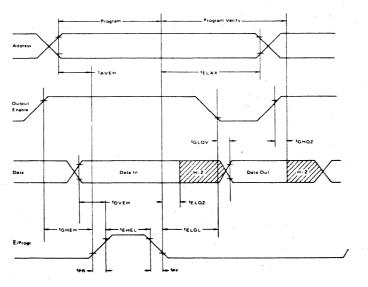

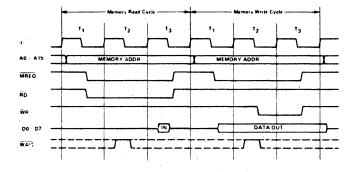

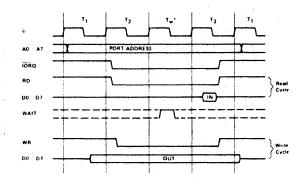

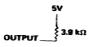

The LNW80 utilizes the 16Kxl dynamic memories (4116 type) with maximum access time of 200ns. The 14 address lines are multiplexed into the 7 address inputs. The addressing sequence is RAS\* (Row Address Select), MUX (Multiplex), and then CAS\* (Column Address Select). The timing diagram for a write operation of the memory control signals is displayed in the following diagram. The RAM data bus out is enabled by "RAM/ROM\*" at U63 when RAM\* is decoded at U19-6 during a read operation.

## FIGURE 1. MEMORY WRITE TIMING DIAGRAM

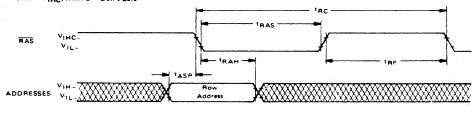

#### RAM REFRESH

Dynamic RAM require periodic refreshing to retain data information. If the system does not receive periodic refreshing the dynamic RAMs will begin to "forget" data.

The LNW80 utilizes the Z80A CPU to generate the refresh to the RAM's. The memory refresh address is output on the lower 7 address bits during refresh time. An instruction fetch will increment the refresh register.

The LNW80 uses a "RAS\*" only refresh, where RAS\* will be low and CAS\* will be high during refresh. At refresh time MUX will be low selecting A0-A7 as the RAM address.

#### **KEYBOARD**

The LNW80 keyboard is designed specifically for the LNW80 computer providing a 62 keypad, an 11 key numeric keypad, and all the special functions that are available to you through the LNW80 computer.

The keyboard is a scanning type keyboard based on an eight by eight matrix. Normally, all lines are floating until the KYBD\* signal goes low which turns Ql on and pulls all signals high indicating a keyboard scan operation. KYBD\* is decoded through U35 when a keyboard address is placed on the address bus and RD\* is active.

Note that lower case is enabled only with software driver routines such as those available in DOS+, NEWDOS80, and ELECTRIC PENCIL.

#### SPECIAL KEYBOARD FUNCTIONS

- RESET (RST): Both RST keys must be depressed to reset the computer.

- HIGH LOW: Forced LOW Speed switch. When depressed the system will operate in LOW speed. Otherwise the system will operate in forced high speed.

- CONTROL: This is a special software controlled key. It is used in software such as the ELECTRIC PENCIL word processing program.

- CAPS LOCK: Disables lower case characters.

F1, F2: User definable keys. Needs special software driver.

# VIDEO DIVIDER CHAIN

The video divider chain provides the necessary logic for video processing, including video ram addressing, and vertical and horizontal timing pulses. The basis of the video divider chain is the 10.738MHz clock at Ul19-6. This signal appears as a sine wave and is exactly 3 times the color frequency of 3.579MHz. Ul21 executes a divide by 2. This results in 2 input frequencies to the divider chain at Ul22.

In the standard 64 character mode, 32CHAR\*(U122-1) will be high so that the B inputs to U122 will be selected therefore the clock input at U138-9, CLKT, will be 10.738MHz. U138 provides the basic timing signals for video processing. Figure 2 represents a timing diagram for the outputs of U138 and U155 in the 64 character mode.

| CLKT<br>(U138-9) |  |

|------------------|--|

| Tl<br>(U138-5)   |  |

| T2<br>(U138-7)   |  |

| T3<br>(U138-10)  |  |

| T4<br>(U138-12)  |  |

| T5<br>(U138-15)  |  |

| T6<br>(U138-2)   |  |

| T7<br>(U155-6)   |  |

During 64 character mode, T7\* is selected as the control clock(CNTRCLK) for the video timing chain(Ul22-l2). The circuitry of Ul38 and Ul55 effectively produces a divide by l2 such that T7\* is 10.738MHz/l2 or 894.8KHz. Note also that T7 is selected as CHAR1(Ul22-9). CNTRCLK is the clock input to Ul60 and Ul61(Sl61's). Figure 3 illustrates the outputs of Ul60 and Ul61.

| T7 (U155-6)<br>894.88KHz     |  |

|------------------------------|--|

| CHAR2 (U161-14)<br>447.4KHz  |  |

| CHAR4 (U161-13)<br>223.7KHz  |  |

| CHAR8 (U161-12)<br>111.86KHz |  |

| CHAR16 (U161-11)<br>55.93KHz |  |

| CHAR32 (U160-14)<br>27.97KHz |  |

FIGURE3

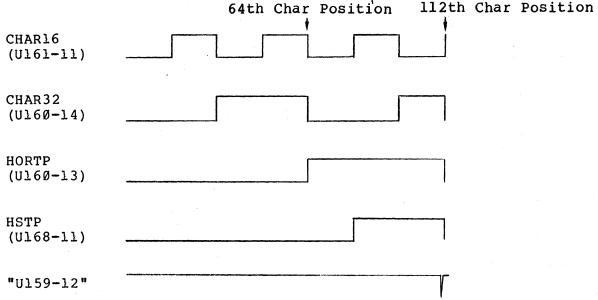

Note that HORTP(U160-13) is not half the frequency of CHAR32(U160-14). T6INH\*(U155-9) prevents the completion of its period by clearing U160 and U161 at the end of each horizontal line. The frequency of HORTP is 15.750KHz resulting in a period of 63.49us for each line.

Each line consists of 112 characters. Allowing one CHAR1 period for each 2 characters the time span for 112 characters is 62.58us. Note that we are left with Ø.91us at the end of each horizontal line. T6INH\* is used to delay the timing chain to "waste" this additional time before starting the next cycle. U167 is used to add the additional delay in T6INH\*. It is ANDed with T6 at U154 thus delaying T6\*(U154-8) from clearing U138.

HSTP(U168-11) is the ORing of CHAR16 and CHAR32, ANDed with HORTP. This is the horizontal sinc timing pulse. Its frequency is 15.750KHz. Refer to figure 4 for the timing diagram. U159-12 is also displayed in figure 4. It goes low after the 112th character and also has a frequency of 15.750KHz. It serves 2 important purposes. 1st, it is the data input to U124 which when clocked clears U155 and thus enabling T6INH\*. Also it is the input to U156-13 and thus increments the row count.

#### FIGURE 4.

Each character position consists of a 6x12 matrix. Six dots and 12 horizontal rows. U156 increments by one after each horizontal scan. When the row count is equal to 12, U168-3 will go high thus clearing U156 setting the row count back to zero and also clocking U153-11 and incrementing the line count by one.

Note that the screen consists of 22 lines (only 16 are displayed) and each line has 12 rows. LINE1, the least signicicant bit of the line counter, changes state every 2nd line and thus has the same period as 24 rows or 24x63.49us or 1.524ms. Its frequency is therefore 656.3Hz. Using similar logic, you can find that LINE2=328.1Hz, LINE4=164.1Hz, and LINE8=82.0Hz.

A similar situation exists for VERTP(U156-6) as did for HORTP in that U156 is cleared before VERTP, which represents line16, completes its full period. When the total line count is 22 the inputs to U169 pins 3,4 and 5 are high, thus its output pin6 clears the line count back to zero. In 22 lines LINE1 changes state 11 times so that the period of VERTP is 11 times that of LINE1 or 16.76ms. The resultant VERTP frequency is 59.66Hz.

In the 32 character mode, Ul22-1 goes low selecting the 5.369MHz clock for CLKT. The result is that all of the outputs of Ul38 are exactly one half the frequency that they VIDEO MEMORY MAP

13

were in 64 character mode. T5\* is selected as CNTRCLK and CHAR1 is ground. Note that because T7\* is 1/2 the frequency of T5\*, by selecting T5\* in 32 character mode CNTRCLK does not change and therefore nor does the resulting logic of U160 and U161.

The signals that did change, T2 through T5 and CHAR1, are very important to the video processor section. CHAR1 determines whether the video ram have 1024 or512 usable addresses. T2 through T5 determine how many characters may be processed to the character generator per line.

# VIDEO RAM ADDRESSING

The video rams are addressed by 2 sources. The video divider chain addresses the video ram so that data contained in memory can be processed and displayed on the screen. The CPU must address the video ram so that data can be read from or writen to specific locations. Multiplexers are used to select either the video chain or CPU address.

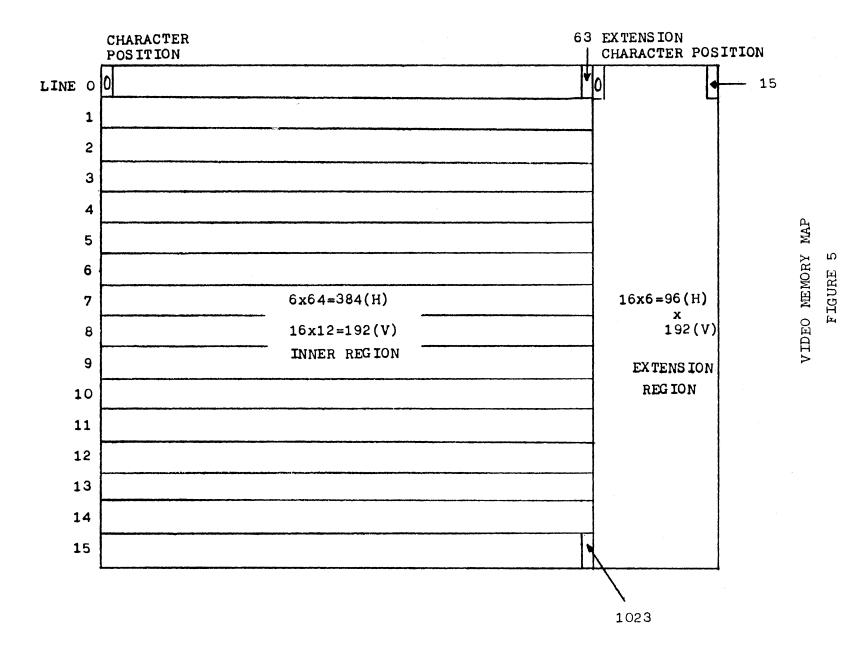

For the following discussion refer to figure 5, the VIDEO MEMORY MAP. Note that the low resolution video is defined only within the inner region and that A10-A13, which specify the row count are not used by the low resolution video ram. By definition A10-A13 are at a logic "1" voltage state during CPU access of the low resolution video ram.

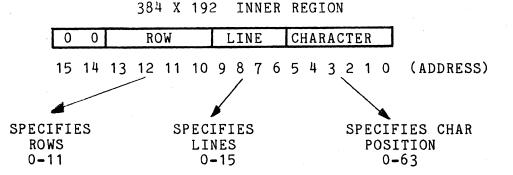

The inner region represents the standard TRS80\* video display. This region is memory mapped at locations 15360 through 16383. It has 63 characters and 16 lines, each line with 12 rows. The video addressing of this region is represented by the following:

A0-A5 specify character position 0-63, A6-A9 specify line position 0-15, and A10-A13 specify row position 0-11. A14 and A15 will be low.

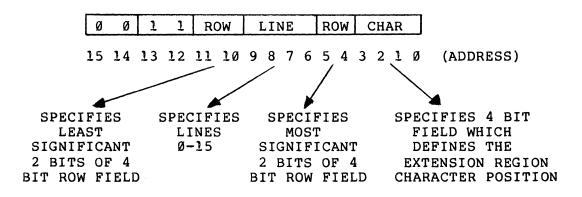

The extension region, refer to figure 5, adds an additional 16 character positions for a total of 80. The following illustrates the addressing of this region:

#### 96 X 192 EXTENSION REGION

AØ-A3 specify character Ø-15 of the extension region, A4-A5 specify the most significant 2 bits of the 4 bit row field, A6-A9 specify lines Ø-15, and AlØ-All specify the least significant 2 bits of the 4 bit row field. Al2 and Al3 are high. Note that the extension region is uniquely defined by a logic"1" at Al2 and Al3 because in the inner region this would specify a row count greater than 11.

When the CPU is not accessing the video ram, the video addresses are controlled by the video divider chain. The selects at Ul39, Ul40, Ul44, and Ul45 will be high selecting the B inputs.

U142 specifies whether we are in the inner or extension region. Prior to the 64th character HORTP(U142-1) will be low, selecting the A inputs. At the 64th character HORTP will go high selecting the B inputs thus selecting the extension region addresses.

CPUACC\*(U121-8) is the select for U139, U140, U144, and U145. When the CPU is accessing the video ram, CPUACC\* will go low selecting the A inputs. The procedure by which CPUACC\* goes low and the CPU addresses are latched into the address multiplexers will be covered in a following section.

#### LOW RESOLUTION VIDEO RAM

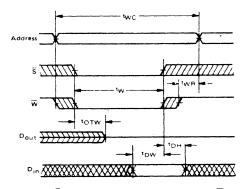

The Low-Resolution Video Ram consists of two 2114 type 1Kx4 static ram chips. For either read or write operations the select (pin 8) must be low. They have an active low write enable, 10 address lines, and 4 data lines each. Ull4 uses the least 4 significant data bits and Ull5 the 4 most significant data bits. When the CPU wishes to access the video ram it must execute a read or write operation while placing a video address on the address bus. For the Low-Resolution (LORES) Video Ram this address must be from (3C00-3FFF)Hex. The following illustrates the sequence of events during a LORES video write.

During the execution of a LORES video write, the CPU will place a video address on the address bus. This address will be decoded at U6 and U35 resulting with a logic "0" at VID\*(U35-7). WR\* will be low. These are the inputs to U152 pins 4 and 5 respectively. When both are low the output, VIDWRT\*(U152-6), will go low. This is the input to U154, a four input nand gate. Note that the four inputs represent LORES video write, LORES video read, HIRES video write, and HIRES video read. When any of the four inputs goes low the output, pin6 will go high clocking U153. DATALAT(U153-5) will be high and U153-6 will be low. CLKADRSDTA (U137-6) will go high latching U98, U141, and U143. Thus the CPU addresses, the CPU data, and VIDWRT\* are latched. VIDWRT\* is latched at U141-4. It becomes LVIDWRT\*. LVIDWRT\* and T2\* are input at U151 pins 12 and 13 respectively. T2\* prevents the LORES video ram to be written to before the video addresses are stabilized. At the beginning of the next video timing cycle Tl will clock DATALAT into Ul21 resulting in a logic "Ø" at CPUACC\*(Ul21-8). CPUACC\* is the select of the video address multiplexers and when it is low the CPU addresses are selected. At T2\*, LVIDWRT\* will be output to WRT2114\* (U139-12). WRT2114\* enables the data output of U98 through U81 and is the write enable to the LORES rams. The write operation is completed when T6\* clears U153, and the resulting low signal at DATALAT clears U121. CPUACC\* goes high and the video address is returned to the video divider chain.

A LORES video read is very similar to the write. VID\* will be decoded from the video address. RD\* will be low. These are the inputs to UL52 pins 1 and 2 respectively. This will place a low input to UL54 as before and the same signals will result except VIDWRT\* will be high and VIDRD\* will be low. At the end of the operation DATALAT will go low latching in data at U99 and UL25. VIDRD\* enables the output of U99 from which the CPU will read the data.

## HI RESOLUTION GRAPHICS RAM

The Hi Resolution (HIRES) Graphics Ram are located at the lower 16K of the LNW80 address space. Note that this is also where the Roms, keyboard, LORES video ram, and miscellaneous I/O are mapped. I/O port 254 bit-D3 selects which devices are enabled. With D3=1, the graphics memory is enabled. Note that since the Roms are also disabled by D3=1, using the OUT command in basic to turn on this bit will be fatal to the computer since the computer will execute out of graphics Ram instead of Rom.

FIGURE 6. HIRES GRAPHICS RAM WRITE TIMING DIAGRAM

The HIRES Ram utilizes six, 16Kx1 dynamic memories. The addressing sequence of events is GRAS\*(row address select), T3(multiplex), then GCAS\*(column address select) to multiplex the 14 bits of address into 7-bit parts. The sequence of events during a write operation are as follows.

I/O Port 254 is decoded by U33 and U54. FEOUT\* (U54-12) is used to clock U67. When U67 is clocked and D3=1, GRRDEN\* (U67-6) becomes logic "Ø". This inputs to U66-12. When the CPU places an address of the lower 16K on the address bus, Al4 and Al5 will be low at U66 pins 10 and 9 respectively. This is used to decode the lower 16K. The output of U66-8 goes low and inputs to U66-13. This enables GLWR16K\* at U66-11. GLWR16K\* is inverted at U51 and becomes RDWRDIS (read write disable). RDWRDIS disables RDOUT\*(U36-8) and WROUT\*(U36-11) preventing a conflict on the data bus. GLWR16K\* is input to U152 pins 9 and 12. When accompanied with either IRD\* or IWR\* a read or write operation will occur at the HIRES Ram. Suppose that IWR\* (U152-10) goes low. Then GRAMWRT\* (U152-8) will enable The video address and data control signals are the U154-4. same as for the LORES write operation. WRT4116\* (U139-4) is inverted through Ull8 to disable the LORES Ram. Figure 6 illustrates the timing diagram during a write operation.

The read operation is very similar except that GRAMWRT\* remains high and GRAMEN\* goes low enabling U154. Refer to the write operation for complete details of the address latching and multiplexing. The data is latched into U125 from pin 14 of the HRES Ram by DATALAT, and the outputs of U125 are enabled by GRAMEN\*. The CPU reads the data from U125. Note that D6 and D7 have inputs HORTP and VERTTP. In the present usage these bits are not used.

## VIDEO DATA LATCH

The first step of the video processing is the data latch. For the LORES video this occurs at Ull6 and Ull7 (LS174's). Ull6 latches the lower 5 data bits. Ull7 latches D6 and D7, also the video control signals. DØ-D5 and D7 are latched directly at the end of the timing chain cycle by T5\*. D6 passes through U81 and U82. When CAPS\* (U82-4) is true D6 is disabled, and DLYD6 becomes a function of D5 and D7. The purpose of the CAPS\* key is to disable lower case characters. The ASCII code for lower case is within (6Ø-7F)Hex. D6 is a "1" for all lower case characters. When a lower case character is decoded and the CAPS\* key is depressed, DLYD6 will be "Ø" thus disabling lower case. The HIRES video also uses an LS174, Ul26, and it too is clocked by T5\*.

## CHARACTER GENERATOR

Each character consists of a 5x7 dot matrix. Between any two characters there is a dot that is never turned on. Vertical spacing between dots is determined by CLKT. Note that in 32 character mode CLKT is 1/2 the 64 character mode CLKT frequency. This means that in 32 character mode there will be twice the vertical spacing between dots.

Ul00 is the Character Generator. The ASCII word is presented to Ul00 pins 1 through 7 from Ul16 and Ul17. Ul00 uses the ROW count to determine which patern of five dots to print on each row. It must output 7 times to complete one character after which five rows of blanks are output and the line increments and we're ready to output the first row of dot information to the 2nd character line.

## **GRAPHICS GENERATOR**

U83 functions as the Graphics (LORES) Generator. The Graphics Character may use the entire character position, a 6xl2 dot matrix. This matrix is divided into six rectangles as shown in figure 7. U83 is a dual 4xl data multiplexer. It uses ROW4 and ROW8 as selects. Each 3x4 rectangle is either "on" of "off". When the ROW count is between Ø and 3, DLYDØ AND DLYD1 are selected. When the ROW count is between 3 and 7, DLYD2 and DLYD3 are selected. And finally for a ROW count between 8 and 11, DLYD4 and DLYD5 are selected. Each scan line, 3 dots may be written in each of two rectangles per graphic character. Each rectangle is defined by one data bit. DLYD7 defines a graphics character when true.

| 0         | 1 | ONE CHARACTER POSITION 6x12 DOTS<br>6 GRAPHIC CELLS<br>EACH CELL 3x4 |  |  |  |  |

|-----------|---|----------------------------------------------------------------------|--|--|--|--|

|           |   | <u>1</u> X "5""4""3""2""1""Ø"                                        |  |  |  |  |

| 2         | 3 | 7654321Ø (DATA BIT)                                                  |  |  |  |  |

| 4 :       | 5 | 4 SCAN LINES                                                         |  |  |  |  |

| ← 3 DOTS→ |   | FIGURE 7                                                             |  |  |  |  |

# ALPHANUMERIC/GRAPHIC SHIFT REGISTERS

Ul01 is the alphanumeric shift register, U84 is the LORES graphic shift register, and U127 is the HIRES graphic shift register. All three receive parallel data and shift that data out to the video display in serial form.

All three behave in the same manner but have different restrictions that if not met will prevent data from being serialized.

The inputs to U102 pins 1,2,4, and 5 represent the restrictions to the alphanumeric shift register. If any of the inputs go low, the output will go high thus preventing the loading of data. DLYROW8\* provides the blanking of ROWs 8 through 11 for alphanumeric characters. DLYBLANK\* provides blanking beyond the 64th character position and below the 16th line. DLYD7\* defines an alpha numeric

character when true. And CTRLT5(U81-8) provides that data in not loaded during CPU access time. Note that there are only 5 inputs to U101. This is because the sixth bit is tied to gnd to blank the sixth dot between characters.

The inputs to U85 pins 1,2, and 13 represent the restrictions to the LORES graphics shift register. If any of its inputs go low its output will go high preventing data from being loaded. There are two differences in the restrictions of the LORES graphics and the alphanumeric shift registers. The first is that for graphics characters the entire character position may be used therefore ROWs 8 through 11 are not blanked out. And DLYD7 defines a graphics character when true. The restriction regarding CTRLT5 still applies.

The inputs to U85 pins 3,4, and 5 represent the restrictions to the HIRES graphics shift register. CTRLT5 has the same purpose as described for the alphanumeric shift register. DLYLDHDG\* provides blanking after the 80th character and below the 16th line. DLYLDINH\* prevents loading during CPU access time.

#### INVERSE VIDEO

Inverse Video is controlled through Port 254. When DØ is set to a one and output to Port 254, VIDEOINV (U67-1Ø) becomes a logic one. VIDEOINV drives U82-1 an input of an exclusive or gate (74LS86). When VIDEOINV is a "1" the combined video output of U68-4 (VIDEO "NORed" with HRESVID) is complemented thus inverting the video content. This is full screen video. When VIDEOINV is low the combined video information passes unchanged (standard video). The output of U82-3 COMBINED VIDEO (COMBVID\*) drives both the high resolution B/W video output circuitry (U9-6,7) and the NTSC color channel (in the non-color display modes) at U68-11.

# HORIZONTAL AND VERTICAL SYNC TIMING

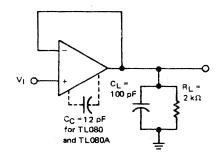

U20 and U37 form the sync generator circuit. The horizontal and vertical sync generator circuits take the timing pulses from the divider chain, delays are applied to them, and the pulses are one-shot to fix the pulse width. This allows the vertical and horizontal positions to be adjustable and the correct pulse width is supplied to the video monitor to provide the correct horizontal and vertical synchronization.

The VERTICAL TIMING PULSE (VERTTP) from the divider chain is buffered by  $U2\emptyset-8$  (a CMOS exclusive or acting as a buffer only) and drives potentiometer R145. When R145 is set for some resistance U20-10 directly drives an RC timing delay circuit formed by R145 and C23. When VERTTP goes to a logic "1", C23 begins to charge. As it charges, the voltage at the input of U37-5 (74CØ4) rises. When the voltage reaches the threshold of a logic "1" (around 4 volts since this is CMOS logic), the output of U37-6 becomes a logic  $\emptyset$ (U37 is an inverter). The logic Ø output of U37-6 drives the input of the next inversion stage of U37-9. The logic Ø is inverted and the output of U37-8 becomes a logic "1" and stays that way until VERTTP returns to a logic " $\emptyset$ ". By changing the "R" of the R145 and C23 "RC" circuit the vertical sync pulse is varied. This allows the adjustable vertical screen position to compensate for variance in video monitors. The output of U37-8 is now given a fixed pulse width by the monostable circuitry of C22, R49 and the input of U37-1.

The horizontal sync circuits work in a similar manner with the HORIZONTAL SYNC TIMING PULSE (HSTP) driving U20-13. R144 and C24 form the RC delay, and C21 and R48 form the pulse shaping and width. The horizontal and vertical sync pulses are mixed by two EXCLUSIVE OR gates of U20. The output of U20-3 directly drives the video mixing circuits of the Hi-resolution B/W video output. U20-4 drives the Sync input to the NTSC Prom.

Ull8-9,8 buffers the horizontal sync circuits to signal the Burst one-shot (Ul33-1) of the horzontal sync period. The Burst one-shot is described further in the section entitled "COLOR VIDEO".

#### COMPOSITE VIDEO MIXING CIRCUITS (HI-RES)

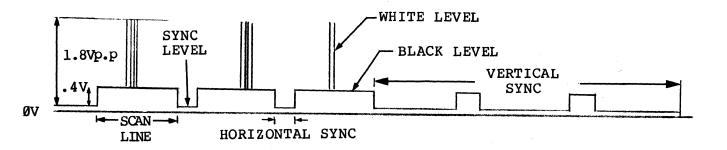

The following drawing illustates what the black and white video output would look like with an oscilloscope.

The "sync level" extends from Ø volts to .4 volts. This .4 volt level is commonly referred to as the "black level" or the voltage that would leave the display black. Above 1.2 volts is the white level. Between these levels are shades of gray. When a pixel is displayed on the CRT, the voltage goes above 1.2 volts for just enough time to display the dot. If most of the screen is blanked, looking at the video signal with an oscilloscope should show few very thin pulses extending to 1.2 volts with most of the time the voltage staying below .4 volts.

The combined sync output of U20-3 directly drives the base of Q2. When there is sync, U20-3 is high and Q2 is turned off. This provides no drive to Q1 and thus the video output is 0 volts. During the non-sync period U20-3 is "low" and "turns on" Q2. This causes 5 volts to be driven into voltage divider R19 and R16 and the base of Q1. The COMBINED VIDEO output (COMBVID\*) drives peripheral and driver U9. When the video dot is to be displayed (COMBVID\*=0) then the output transistor in U9 is "off" thus high impedance. This means that R17 has no effect in the circuit and around 2.5 volts drives the base of emitter-follower Q1. With around .7 volts drop the output of Q1 (75 ohms impedance) is 1.8 volts. When the video dot is NOT to be displayed, COMBVID\* is high and R17 now appears in the circuit from the base of Q1 to ground. This causes the voltage at the base of Q1 to be reduced to around 1 volt thus with a .7 volt drop at Q1 (base to emitter) the output is at the "black level" or .4 volts. C7, R22, and C8 serve to filter, reduce power dissipation in Q1, and serve as short-circuit protection. R121 serves to set the output impedance of the video signal.

#### NTSC COLOR VIDEO

NTSC stands for the television standard first, developed and implemented in the United States. Japan, Canada, and Mexico also adopted this (the first) television standard. NTSC color video uses the same timing and levels as Black and White video. It has a 60 hz vertical sync rate which corresponds to 262 scanned lines (including sync). The LNW80 refreshes the screen at a rate of 60 hz with 262 lines. Countries which have AC power frequencies of 50 hz use PAL, SECAM, or other color systems with 312 scanned lines at a 50 hz vertical rate. These systems are not compatible with the LNW80 set up for NTSC at 60 hz.

Color video works much the same as black and white. The video signal also is 1.8v p-p and .4 v is the black level and 1.2v is the white level. Horizontal and vertical sync are identical. Here are the differences:

#### 1. COLOR ENCODING

In order to encode color information on the video signal there is a COLOR CARRIER. This color carrier allows the luminance information to be encoded with a PHASE relationship with the carrier thus specifying the color to be displayed.

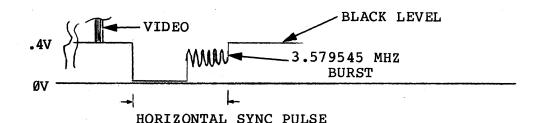

#### 2. COLOR BURST

The color carrier cannot be present during the displayed video period and thus is maintained by the monitor (or TV). This 3.579545 MHz signal is transmitted only for a small period of time by the computer (or TV station) to keep the color oscillator in the monitor (or TV) "locked in at the same exact frequency". This "burst" of color carrier is transmitted only for about 8 cycles and only at the very end of the horizontal sync pulse. This is commonly referred to as the "back porch" of the horizontal sync or the COLOR BURST and is illustated below:

#### COLOR MODES

In the LNW80 there are two possible color modes-low resolution and high resolution. The bandwidth of NTSC video only allows the low resolution mode to be displayed. In order to display the high resolution color, an RGB type direct drive monitor must be used and the optional RGB interface circuitry must be installed.

Port 254 data bit 2 selects whether or not color is enabled. COLOR (U67-2) and COLOR\* (U67-3) do the logic switching to enable or disable color operation.

#### LOW RESOLUTION COLOR

In low resolution color mode, HRES will be low and HRES\* will be high. This causes U129 to be enabled and U131 to be disabled via two gates of U52. U52-13 (COLOR) is high, U52-2 (HRES\*) is high and U52-1 is VIDEO, thus the output of U52-12 which allows U129 to be selected to drive color information to U130 (NTSC ROM) will go low along with VIDEO. This means that the low resolution text and graphics information from the MODE Ø display will select whether or not the color information is to be passed on the NTSC ROM or the display will be black. When U129 is not enabled (it is a tri-state) gate pull-up resistors R101, R100, and R93 pull the floating inputs of the NTSC ROM to a logic "1". A logic "1" on all three bits of the color code or a 7 is defined as the color black. This means that there are two ways that the screen can be programmed black. One by putting 7 as the color information in the color memory or by blanking the low res screen.

Color information is stored in the same memory as the high resolution graphics memory U106-U111. The 6 bits of data, instead of being fed into a shift register (U127) to be sent out one bit at a time (as in high resolution graphics), is latched again into Ul28. It is fed to Ul28 for another level of delay to syncronize the Black and White video information (being shifted out of UlØl or U84). Once latched into Ul28, the 6 bits represent two 3 bit (1 of 7 colors and black) fields. During the period that the first 3 dots (of the character position time) are being shifted out of U84 or UlØl, T3 is a logic Ø. This drives the least significant 3 bits of Ul28 into the NTSC ROM to define the color. During the next 3 dot periods, T3 is a logic 1 and the most significant 3 bits of Ul28 are driven into Ul3Ø to define the color. Remember that if VIDEO was false, Ul29 is disabled completely thus overriding the contents of Ul28 (displaying black).

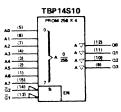

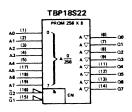

# NTSC COLOR ROM

The NTSC COLOR ROM translates a 3 bit color code  $(\emptyset-7)$ , SYNC and BURST (timing) into the proper R-Y (COLORB), B-Y (COLORA), and LUMINANCE (LUM) that the MC1372 requires to do the color encoding. The NTSC ROM (U130) is a high speed bipolar open collector prom. U130 combined with ladder resistors R85-92, R94, R99 and R102-105 form a high speed digital to analog converter to translate the digital color codes and sync information into the analog levels needed by the MC1372.

The following is the truth table for the NTSC ROM and the voltage levels developed for COLORA, COLORB, and LUM.

ADDRESS

DATA(Hex) COLORA COLORB LUM

| (Hex) COLOR SYNC BURST                 |                                         |    |    |    |    |     |         |      |      |             |

|----------------------------------------|-----------------------------------------|----|----|----|----|-----|---------|------|------|-------------|

|                                        | AØ                                      | A1 | A2 | A3 | A4 |     | COLOR   |      |      |             |

| 2223                                   | 242222222222222222222222222222222222222 |    |    |    |    |     |         |      |      |             |

| ØØ                                     | Ø                                       | Ø  | Ø  | Ø  | Ø  | 6C  | WHITE   | 1.5V | 1.5V | .38         |

| Ø1                                     | 1                                       | Ø  | Ø  | Ø  | Ø  | D5  | GREEN   | 1.0  | 1.0  | • 5         |

| Ø2                                     | ø                                       | 1  | Ø  | Ø  | Ø  | CC  | YELLOW  | 1.5  | 1.0  | .38         |

| øз                                     | 1                                       | 1  | Ø  | Ø  | Ø  | 7A  | RED     | 2.0  | 1.5  | .62         |

| Ø 4                                    | Ø                                       | Ø  | 1  | Ø  | Ø  | FD  | MAGENTA | 2.0  | 2.0  | .50         |

| Ø5                                     | 1                                       | ø  | 1  | Ø  | Ø  | EA  | BLUE    | 1.5  | 2.0  | .62         |

| Ø6                                     | Ø                                       | 1  | 1  | Ø  | Ø  | 75  | CYAN    | 1.0  | 1.5  | <b>.</b> 5Ø |

| Ø7                                     | 1                                       | 1  | 1  | Ø  | Ø  | 6B  | BLACK   | 1.5  | 1.5  | <b>.</b> 7ø |

| Ø8                                     | Ø                                       | Ø  | Ø  | 1  | Ø  | 6F  | SYNC    | 1.5  | 1.5  | 1.00        |

| =================== to                 |                                         |    |    |    |    |     |         |      |      |             |

| ØF                                     | 1                                       | 1  | 1  | 1  | Ø  | 6F  | SYNC    | 1.5  | 1.5  | 1.00        |

| 10                                     | Ø                                       | Ø  | Ø  | Ø  | 1  | AE  | BURST   | 1.5  | 1.25 | .75         |

| ====================================== |                                         |    |    |    |    |     |         |      |      |             |

| 17                                     | 1                                       | 1  | 1  | Ø  | 1  | AE  | BURST   | 1.5  | 1.25 | .75         |

| 18                                     | Ø                                       | ø  | Ø  | 1  | l  | 6 F | SYNC    | 1.5  | 1.5  | 1.00        |

| ====================================== |                                         |    |    |    |    |     |         |      |      |             |

| lF                                     | 1                                       | 1  | 1  | 1  | 1  | 6F  | SYNC    | 1.5  | 1.5  | 1.00        |

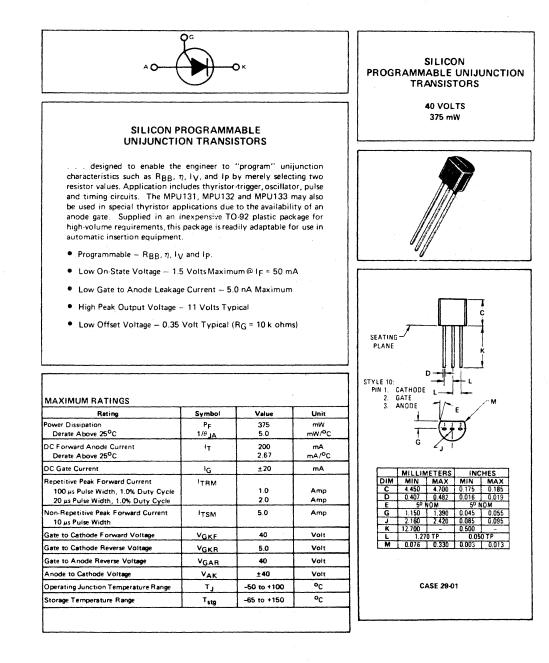

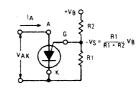

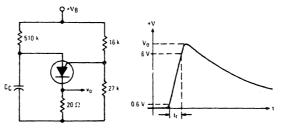

## COLOR BURST ONE-SHOT

When HSYNC transitions from high to low (the end of the horizontal sync pulse) U133-13 strobes, using R80 and C83 for RC timing. The one-shot time is approximately 2usec. During this time, BURST is high and drives A4 of U130, the NTSC ROM. When A4 is high, the correct analog levels are supplied to U146 (MC1372) to output a burst reference signal with the correct phase and amplitude.

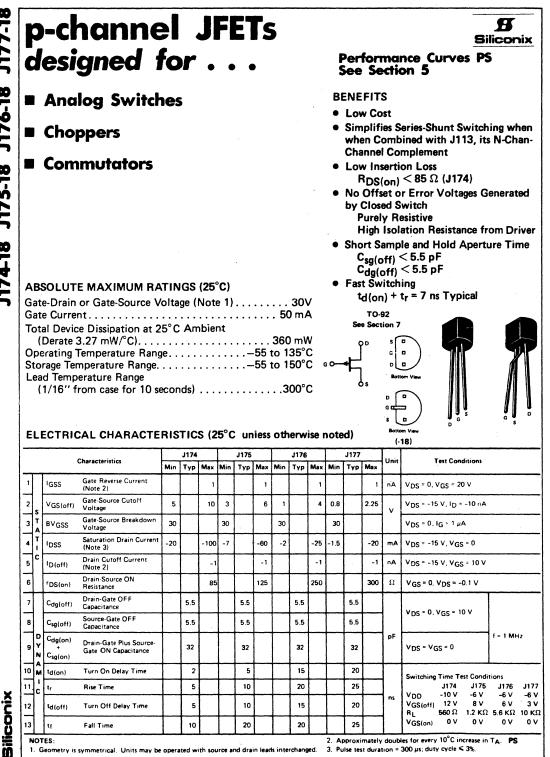

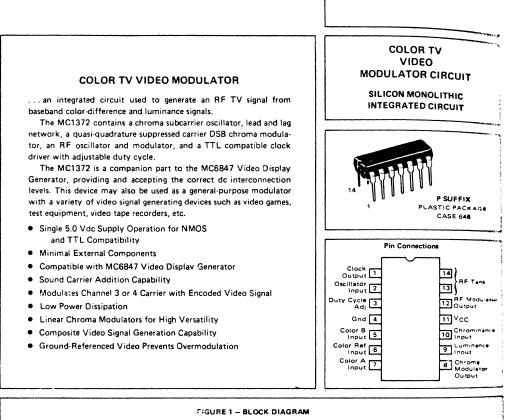

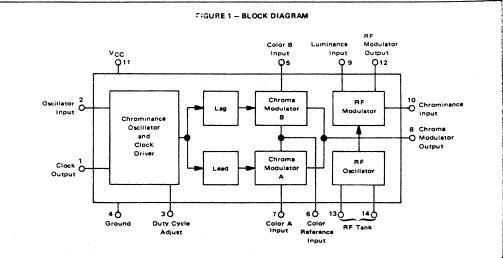

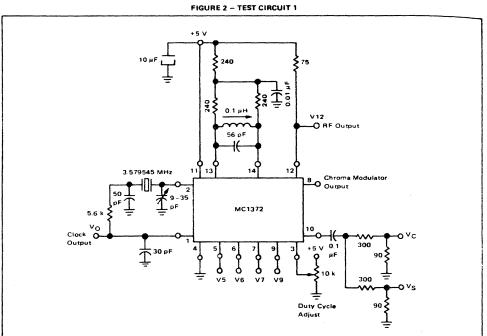

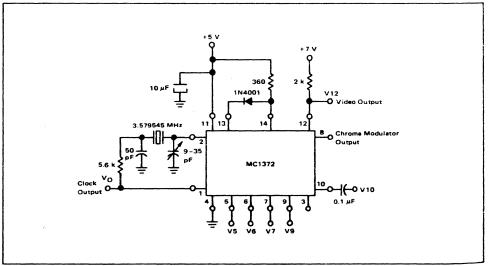

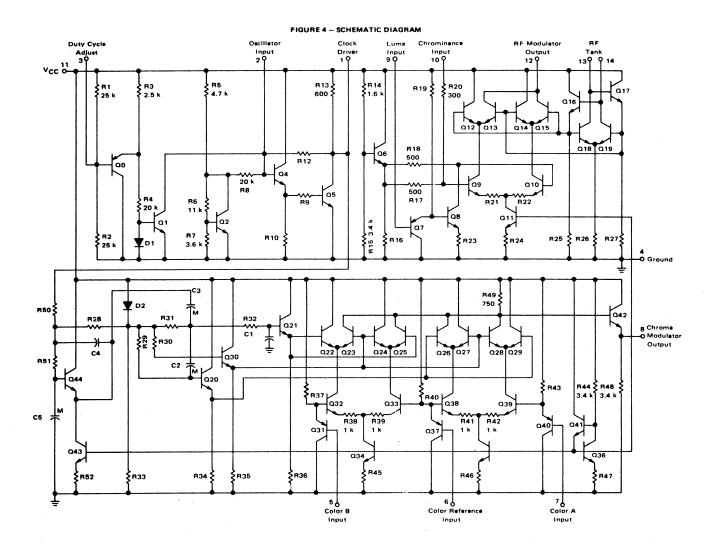

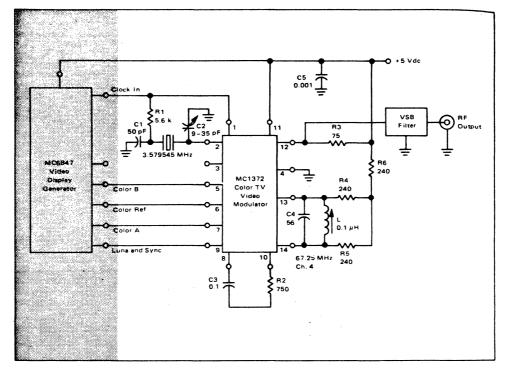

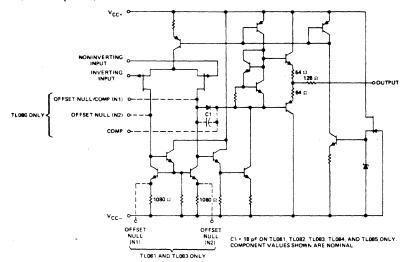

# U146-MC1372 COLOR ENCODER

The MCl372 is a linear IC which contains both a chroma oscillator and the necessary chroma (color) encoder. Ul46 pins 1 and 2 along with Y2 the 3.579545 MHz crystal, C94 and 95, and R106 form the complete color reference oscillator (chroma oscillator) circuit. C95 is the chroma frequency trimmer adjustment. Ul46-1 is the square wave output of the 3.579 MHz color frequency and drives one-shot Ul33-10 to provide the color to luminance dot clock synchronization signal (COLORSYNC). Ul33 with timing resistor R107 (and no timing capacitor) forms a 50-70 nanosecond pulse generator. Ul33-5 drives open-collector inverter Ul62-11. Inverted and pulled up by R97, this generates COLORSYNC.

COLORA, COLORB, and LUM information from U130 determines the luminance level and the phase encoding of the video information that is output by the MC1372 on pin 12. R109 sets the output bias and CR1 selects the composite video polarity. The output of U146-12 (COLOROUT) is amplified and level shifted by Q13, R123 and R129. Q14 is an emitter follower to provide current amplification and 75 ohm impedance matching.

The MCl372 has the chroma encoder circuit separate from the final composite video mixing circuit. The chroma encoder output (Ul46-10) is fed back into Ul46-8 through Rll7 and blocking capacitor Cl10. Ul62-12, Cl11, and Rll8 form the chroma killer circuit that disables any chroma content in the video signal when COLOR is disabled. It does this by shorting the chroma signal to ground (through open-collector Ul62-12).

For more details on the operation of Ul46 refer to the data sheets on the MCl372.

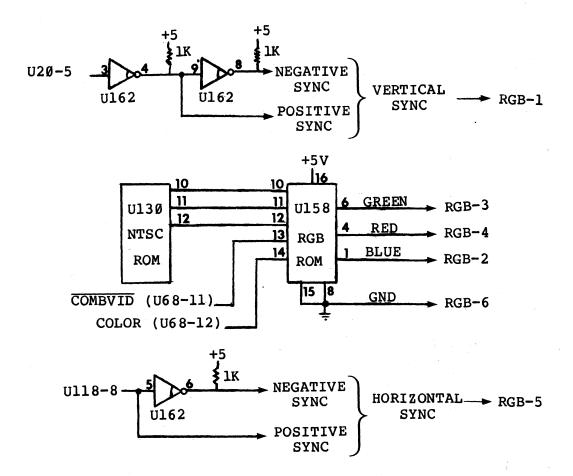

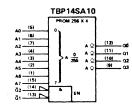

## HIGH RESOLUTION COLOR

Assuming that the RGB ROM is installed, wired, and usable, then high resolution color is possible. In high resolution color Ul29 is disabled and Ul31 is enabled via U52-8 when HRESVID (U52-10), COLOR (U52-11), and HRES (U52-9) are true. In the high resolution color mode the dot information is supplied by the high resolution memory (480x192) and the color information is supplied by the low resolution memory (128x16 lines). Ul32 latches the output of the text memory and drives the multiplexer Ul31. Ul31 provides the RGB ROM with the least 3 bits of the text data (DLY0-DLY2) during the first half of the character position when T3 is "low" (first 3 dots) and then switches the output of Ul31 to the most significant 3 bits of the text data for the last 3 dot clocks (T3 is high).

#### BLACK AND WHITE DISPLAY THROUGH THE NTSC CHANNEL

In the low or high resolution black and white display modes, COLOR is low (U68-12). This disables both U131 and U129. Thus U130 receives no color or luminance information from U131 or U129. U130 still receives Sync information. Since U68-12 is low, video information passes directly through to U68-13 to drive the open-collector driver, U162-1. This through R95 then feeds dot information (luminance) directly into the MC1372 (U146) while U130 supplies the correct information to luminance during sync.

#### CASSETTE

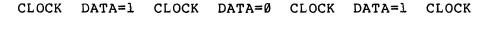

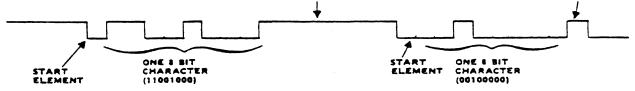

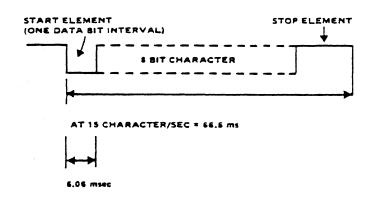

Programs are loaded onto tape in serial fashion. The serial data contains both clock and data information as shown below:

The time "T" is dependent upon whether the computer is in high speed or low speed. In low speed the time "T" is 2 ms. In high speed this time is 1 ms. This timing results in a transfer rate of 500 baud and 1000 baud respectively. The cassette routines are resident in the Level II ROM's and cassette is accessed as an I/O port. When a CSAVE is entered, the address FF is placed on the address bus along with OUT\* (U18-3) going low. The result is that FFOUT\* (U54-11) goes low. When this happens D2 will go high and will be clocked into U8. This will turn U9 on and therefore the relay K1. This shorting of pins 1 and 3 of the cassette connector through K1 will turn the cassette motor on. DØ and D1 also get clocked into U8 with timing that results in the above diagram.

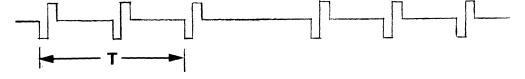

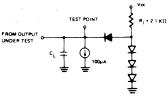

The cassette loading operation is accomplished through U21 A, B, and C. Refer to the figure below.

CASSETTE WAVEFORMS

The signal from the cassette is voltage divided by R24 and R25. U21A is a two pole active high pass filter which will eliminate noise. U21B along with U18 function as an automatic gain controlled (AGC) amplifier. The amplitude at U21B is peak detected by CR2 and C119 to get an average signal level. The voltage at the gate of Q18 will then be higher as the signal amplitude goes higher. The higher the voltage at the gate, the higher the resistance between the source and drain which will have the effect of lowering the gain of this stage. The lower the gate voltage, the lower the drain to source resistance and the higher the gain. The voltage level of U21B will be controlled to a maximum of about 8.0 volts. U21C is a comparator who's trip level is dependent upon the voltage at U21C pin 5. The output at pin 7 is normally high which will go low when a data or clock signal is encountered.

U38 is a flip flop who is set and reset by U21C pin 7 and FFOUT\* respectively. The decoded signal FFIN\* will then place the cassette information onto D7.

#### POWER SUPPLY

The LNW80 power supply section is designed to power both the LNW80 computer board and the LNW expansion board.

The LNW80 transformer is 9 volts AC rated at 4 amps and 18 volts AC rated at 2 amps. The unregulated AC voltage of the transformer is rectified by CR17 and filtered by the 15,000 ufd capacitor. This capacitor must be located somewhere off the LNW80 board. Q3, Q7, Q8, Q9, and Q10 provide the regulated +5 volt supplies. All +5 volt outputs are connected through diodes to a summing point at thte anode of Q12. If any of these voltages exceeds approximately 6.2V then CR24 will begin to conduct. While the gate of Q12 remains unchanged, the anode voltage will begin to rise higher than the gate. This will cause Q12 to begin conducting which will fire SCR1 causing F1 to open. This overvoltage protection prevents damage to components due to high voltage.

CR15 rectifies the AC signal which is then filtered by Cl21. Q4 regulates thte voltage to +12 volts. If the voltage at JP9 exceeds 13 volts, CR11 will begin to conduct. While the gate of Q6 remains unchanged, the anode will rise above the gate voltage. This will cause Q6 to begin conducting and result in turning SCR2 on and F2 will open.

R138 limits the current, C137 provides DC blocking and CR19 and CR16 provide a voltage doubler. Q11 will then provide a -12 volt regulated output which supplies both the LNW80 computer and expansion board.

The voltage at the negative lead of Cl31 is regulated by Rl33 and CR14 and it is then filtered by Cl30. This -5 volts is used both for the LNW80 computer and expansion board.

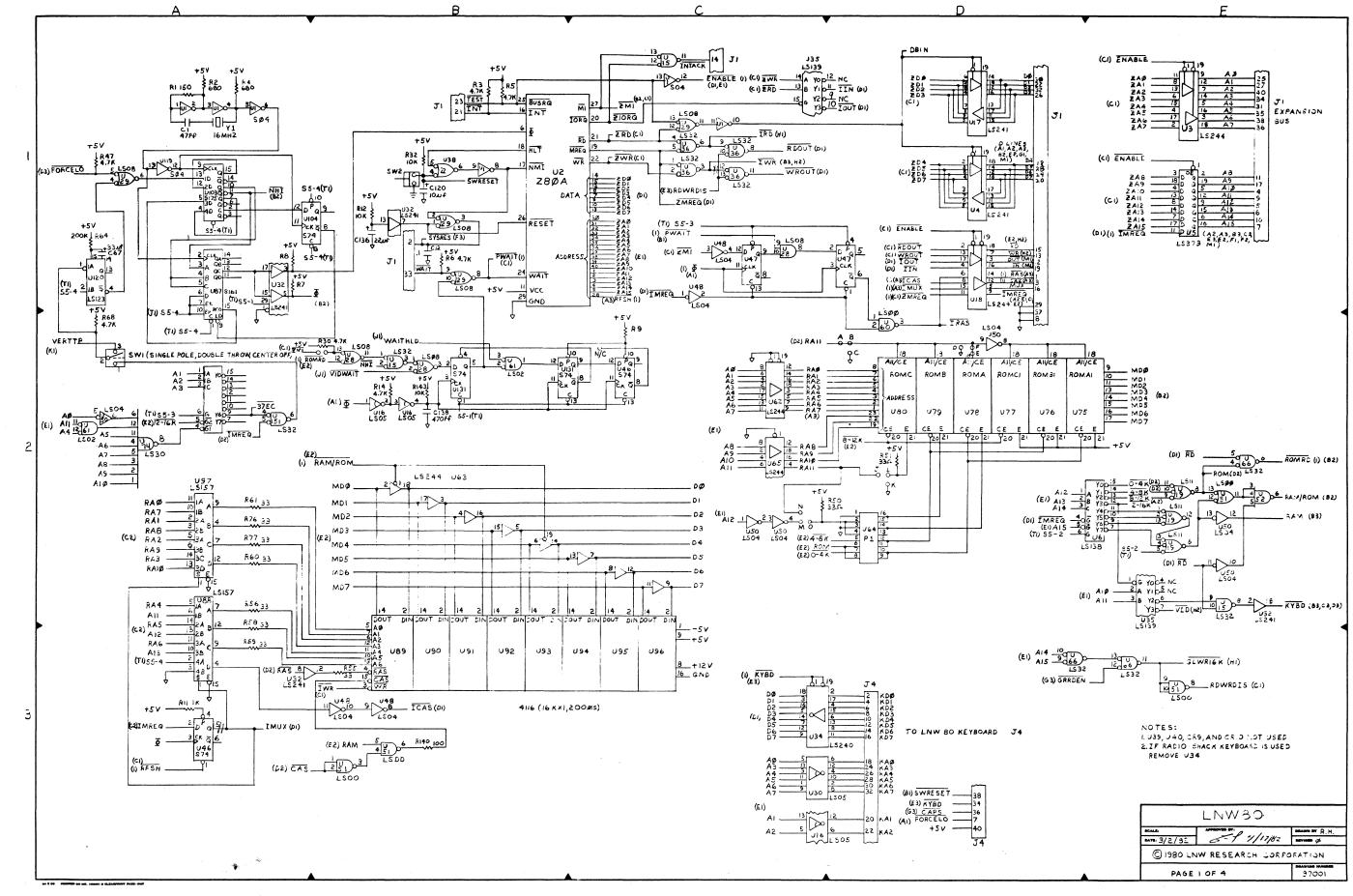

# THEORY OF OPERATIONS EXPANSION BOARD

The Expansion board is merely an extension of the main computer board. A number of the functions of the LNW80 Computer are performed on the expansion board. These functions include additional memory, real time clock, floppy disk controller, parallel printer, and RS232C serial port. The expansion bus is a 40 pin connector that contains all of the necessary control, data, and address lines necessary for operation.

# LNW80 EXPANSION BUS

The 40 pin bus is equivalent to the TRS80's 40 pin expansion bus. The following are the signals and their descriptions for the expansion bus:

| PIN #    | SIGNAL NAME     | DESCRIPTION                      |

|----------|-----------------|----------------------------------|

| 1        | RAS*            | ROW ADDRESS STROBE               |

| 2        | SYSRES*         | SYSTEM RESET                     |

| 3        | CAS*            | COLUMN ADDRESS STROBE            |

| 4        | Alø             | ADDRESS INPUT                    |

| 5        | Al2             | ADDRESS INPUT                    |

| 6        | Al3             | ADDRESS INPUT                    |

| 7        | Al5             | ADDRESS INPUT                    |

| 8        | GND             | GROUND                           |

| 9        | All             | ADDRESS INPUT                    |

| 10       | Al4             | ADDRESS INPUT                    |

| 11       |                 | ADDRESS INPUT                    |

| 12       | OUT*            | I/O WRITE STROBE<br>WRITE STROBE |

| 13       |                 |                                  |

| 14       | INTACK*         | INTERUPT ACKNOWLEDGE             |

| 15       | RD*             | READ STROBE                      |

| 16       | MUX             | ADDRESS MULTIPLEXER              |

| 17       | A9              | ADDRESS INPUT                    |

| 18       | D4              | DATA BUS                         |

| 19       | IN*             | I/O READ STROBE                  |

| 20       | D7              | DATA BUS                         |

| 21       | INT*            | MASKABLE INTERUPT                |

| 22       |                 | REQUEST                          |

| 22       | Dl              | DATA BUS                         |

| 23       | TEST*           | BUS REQUEST                      |

| 24<br>25 | D6<br>AØ        | DATA BUS                         |

| 25       | D3              | ADDRESS INPUT                    |

| 20<br>27 | D3<br>Al        | DATA BUS                         |

| 28       | D5              | ADDRESS INPUT<br>DATA BUS        |

| 20       | GND             | GROUND                           |

| 30       | DØ              | DATA BUS                         |

| 31       | A4              | ADDRESS INPUT                    |

| 32       | D2              | DATA BUS                         |

| 33       | WAIT*           | Z8ØA CPU WAIT                    |

| 34       | A3              | ADDRESS INPUT                    |

| 35       | A5              |                                  |

| 35       | A5<br>A7        | ADDRESS INPUT<br>ADDRESS INPUT   |

| 37       | GND             | GROUND                           |

| 38       | AG              | ADDRESS INPUT                    |

| 39       | GND             | GROUND                           |

| 40       | A2              | ADDRESS INPUT                    |

| -10      | £™ <del>C</del> | PROVIDO IMEGI                    |

# MEMORY EXPANSION

The Expansion Board contains 16 additional 4116 type RAM chips at U42-49 and U53-60. U37 and U38 (LS241's) are used to multiplex the address lines. U34 and U35 are used to buffer the data lines both input and output.

RAS\* is buffered to all of the RAMS while CAS\* is gated by U29 with 48KRAMEN\* and 32KRAMEN\*. When the CPU wishes to access the upper memory it places an address from 7FFF to FFFF on the expansion bus. The address is decoded at U30. When Al5 and Al4 are high and RAS\* is low, 48KRAMEN\* (U30-7) will go low enabling CAS\* to the upper bank of memory. When Al5 is high and Al4 and RAS\* are low, 32KRAMEN\* (U30-6) will go low enabling CAS\* to the lower bank.

The data bus is buffered by U34 and U35. These buffers will pass data from the memory onto the data bus when pin 1 of U34 and U35 is low. 32KRAMEN\* and 48KRAMEN\* are fed into U11 pins 2 and 1 respectively. When either goes low the output (U11-3) will go low. This signal is used to gate RD\* through U29 pins 9 and 10 respectively. U29-8 is then fed into U34 and U35 and is used to enable memory data onto the data bus. U34 and U35 is tied to gnd thus enabling data from the data bus to the data input of the memory array at all times.

For further information on the operation of 4116 type dynamic rams refer to the section on program memory in the theory of operations of the LNW80 computer board.

# FLOPPY CONTROLLER AND PRINTER DECODING

U19 is used to decode the various signals involved in the floppy disk and parallel printer circuits. All addresses memory mapped within the range 37EØ to 37EC (HEX) are decoded through U19.

When the CPU places an address in this range on the address bus RAS\* (U30-1) will go low indicating a valid address. All of the inputs to U31 will go high resulting in a logic "0" at U31-8. All, Al4, and Al5 will be low such that all of the inputs to U30, pins 1,2,3,13, and 14, will be low. U30-4 will go low enabling U30-12 which will also go low. U30-12 is used to enable the outputs of U19 which effectively produces a "double" 2/4 line decoder.

The outputs of U19 are used as control signals for both the Floppy Controller and the Parallel Printer Interfaces. Explanations of these signals and the addresses that decode them may be found below:

| PIN# FUNCTION                                                                                                                             |                | ADDRESS<br>DECODE                                                             | WR*                                  | RD*                   |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------|--------------------------------------|-----------------------|

| 7 INTERUPT RESET<br>6 N/C<br>5 PRINTER STATUS<br>4 FLOPPY READ<br>9 MOTOR ON/DRIVE<br>10 CASSETTE<br>11 PRINTER WR STR<br>12 FLOPPY WRITE | READ<br>SELECT | 37EØH<br>37E4<br>37E8<br>37EC<br>37EØ<br>37EØ<br>37E4<br>37E8<br>37E8<br>37EC | 1<br>1<br>1<br>1<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>1 |

### PARALLEL LINE PRINTER PORT

The expansion board contains an interface to the Radio Shack/Centronic Printer. This Printer Interface consists of an eight bit output port and a four bit input port.

This I/O port is accessed by either writing or reading from address 37E8 Hex. This address is decoded at U30, U31, and U19.

When reading the memory address 37E8, the printer status is read through U3. Only the 4 most significant data bits contain valid information. The meaning of each data bit is as follows:

| Data Bit | Printer Status |

|----------|----------------|

| ======== |                |

| D7       | Printer Busy   |

| D6       | Paper Empty    |

| D5       | Unit Select    |

| D4       | Fault          |

The Radio Shack's parallel printer has wire ORed internally, the printer busy status, and the paper empty signal. When using the Radio Shack/Centronic Printer, only one of these two bits, D6 or D7, needs to be checked. The printer busy indication is issued by asserting a logic "l". When this occurs, the paper empty status will also be a logic "l". The unit select and fault status bits are not used by the Radio Shack's printer. A write to memory location 37E8 will load the output latch U4 and U5 to the line printer's internal data buffer and also generate a signal through U7 called DATA STROBE (U7-4). DATA STROBE will be a low-going pulse of approximately 1.5us.

The Radio Shack's printer is set up to recognize the following control characters for the line feed and carriage return:

| Character     | Function                     |  |

|---------------|------------------------------|--|

|               | 22222222                     |  |

| ØA(Hex)<br>ØD | Line Feed<br>Carriage Return |  |

When either of these control characters are received by the printer, the printer will assert a logic "1" at the printer busy status.

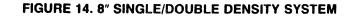

# CLOCK CIRCUIT

The Expansion Board Main Clock is a 4 MHz oscillator, utilizing Yl and Ul8 to form a series resonant circuit. The 4MHz clock is input to U9-14 and U24-2.

U9 provides a divide by 2 resulting in a 2 MHz clock at U9-12, which is then input to U22-3 which again divides by 2 resulting in the 1 MHz clock input to the FLOPPY CONTROLLER (U14).

U24 effectively produces a divide by 13 of the 4 MHz clock resulting in a 307 KHz clock at U24-11. This is used to clock U25, a 4 bit binary counter. Its output produces 4 of the 8 baud rates used for the SERIAL INTERFACE. The frequencies of the outputs can be calculated by multiplying the baud frequency by 16 for the frequency in Hz.

Ul7 is clocked by U25-12 (38.4KHz) and provides a divide by ll resulting in a 3.49KHz clock at Ul7-11. This is input to Ul0-14, which does a divide by two such that Ul0-12 is a 1.75KHz clock.

The 2nd half of UlØ is clocked by U25-11 (19.2KHz) and does a divide by 8. The outputs of UlØ provide the other 4 baud rate clock signals. Baud rate clocks will be discussed in the section entitled "SERIAL INTERFACE". Ul0-ll (2.4KHz) is clocked into U9-l which set for a divide by 6 resulting in an output of 400Hz. This is then input to Ul2 which is set for a divide by ten resulting in the 40Hz clock signal used to provide the REAL TIME CLOCK.

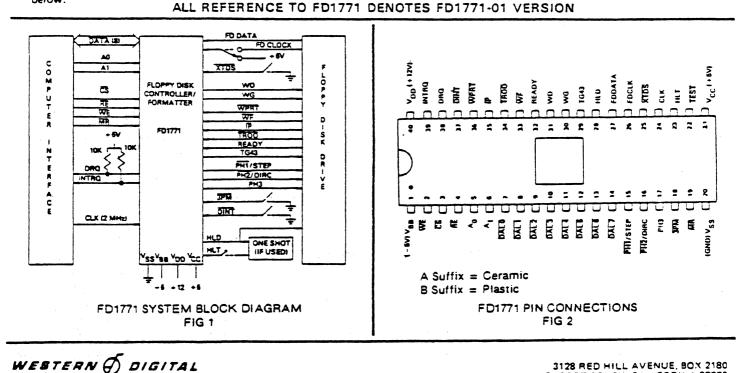

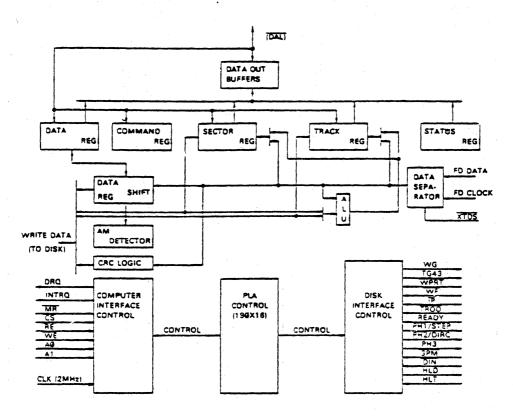

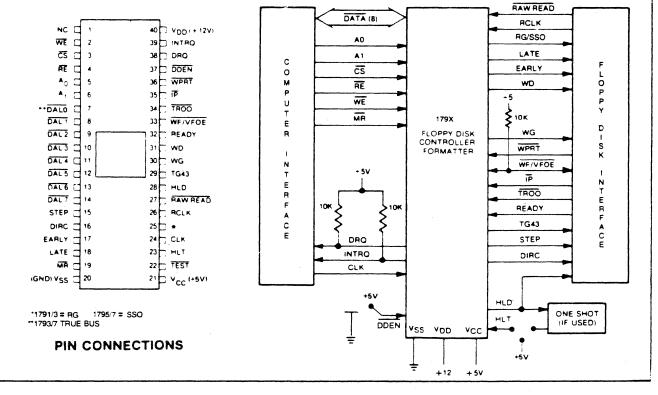

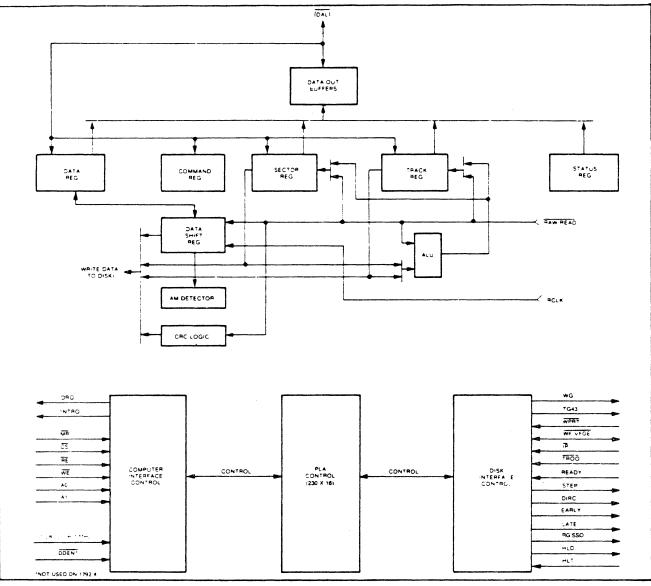

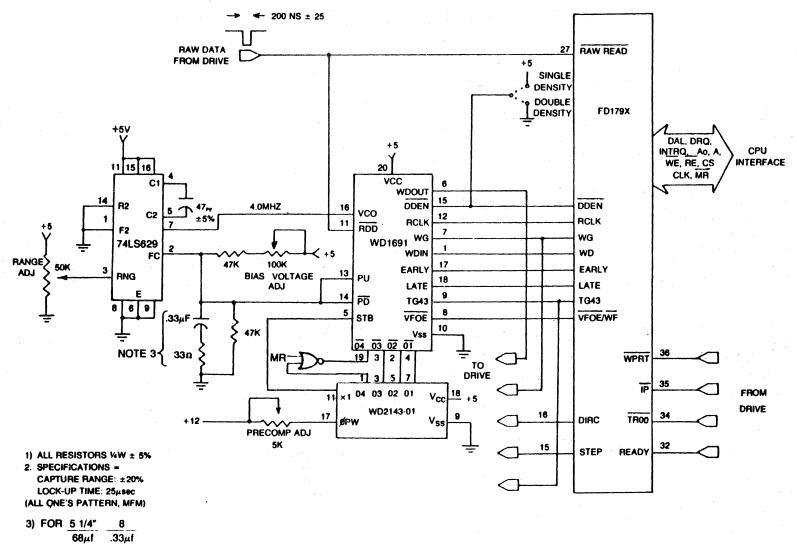

# FLOPPY DISK INTERFACE

The function of interfacing to a floppy disk drive is performed primarily by the Western Digital's FD1771B-Ø1 Floppy Disk Formatter/Controller chip. Note that when using double density adapters, the "doubler" performs the duties of the controller chip. The LNDOUBLER 5/8 will be explained in a further section.

The FD1771, a MOS/LSI device which performs much of the housekeeping involved in reading and writing data to and from the disk has the following internal features:

- Cyclic redundancy check and generation for error checking.

- 2. Internally seperates disk head outpput into data.

- 3. Checks for desired section, check ID field and locate it's data address mark.

- 4. Accounts for track number of the current read/write head position

The interface to the processor is accomplished through the eight Data Access Line (DAL) and the associated control signals.

When reading from the DAL, the address decoder U19-4 (37EC READ\*) will be low enabling U8 and U15 to buffer data from U14 to the data bus. U8 and U15 are LS240's, OCTAL BUFFERS/LINE DRIVERS/LINE RECEIVERS with inverted 3-state outputs.

When writing from the data bus to the DAL, the address decoder U19-12 (37EC WRITE\*) will be low enabling U8 and U15 to buffer data from the data bus to the floppy controller. The least two significant addresses, AØ and Al, are decoded by the floppy controller to interpret the selected registers of the read and write operations. These registers are decoded as follows:

| Al- | AØ | READ        | WRITE        |

|-----|----|-------------|--------------|

| === | == | ==========  |              |

| Ø   | Ø  | STATUS REG. | COMMAND REG. |

| Ø   | 1  | TRACK REG.  | TRACK REG.   |

| 1   | Ø  | SECTOR REG. | SECTOR REG.  |

| 1   | ł  | DATA REG.   | DATA REG.    |

The interrupt request (INTRQ) of the FDC (Ul4-39) indicates the completion or termination of any operation. INTRQ presets U22A presenting a high to Ul pins 4 and 5, which is reset by reading the FDC Status Register. Reading from 37E0H will reset the interupt signal (Ul-6) by clocking a low at the output of U22A.

The FDC requires a 1 MHz clock input to U14-24 which is generated from the 4 MHz main clock circuit and is explained in the clock discription of the expansion board.

Drive Selection through Data Lines DØ-D3 is clocked into Ul3 by 37EØ WRITE\* (Ul9-9). This also triggers the one-shot, U7A, generating the motor on signal. The drive selection is only activated when the motor on signal (U7-5) is high.

When U7-5 is low, clearing Ul3, a high is generated at Ull-8. This signal is then inverted at U20-10 providing a low command and indicating that the floppy status is ready.

Ul4-19 is the MASTER RESET, and is driven by SYSRES\* from the main computer board. When MR\* goes low, the FDC is reset and HEX  $\emptyset$ 3 is loaded into the command register and the system will proceed to reboot. For further details of the internal operations and the programing of the FDC refer to the data sheets.

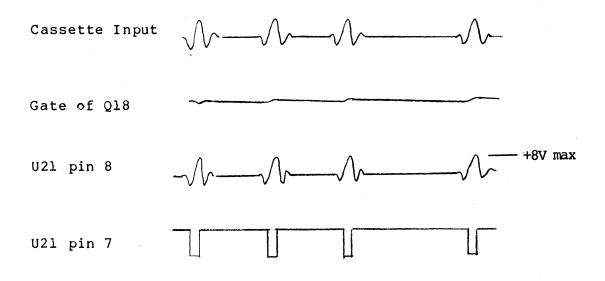

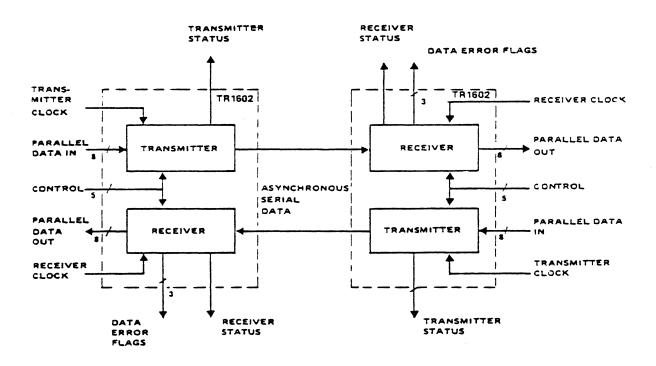

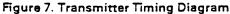

# SERIAL INTERFACE

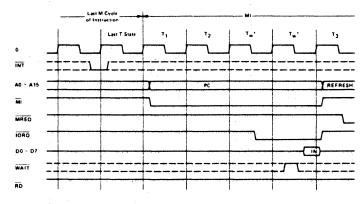

The Block Diagram (figure 8) outlines the major sections of the Serial Interface. For the following circuit description, use the schmatics along with the Block Diagram to aid in visualizing the circuit theory.

# BAUD RATE GENERATION

In order to provide the receive and transmit baud clocks for the UART, the 4 MHz clock is divided down. Details of the clock divider circuitry is given in the section entitled CLOCK CIRCUIT.

The Baud Rate is programmed by jumpering A,B,C,D,E,F,G, or H to the RX and TX line. (Note that on the pre-assembled LNW80 Systems, these have been jumpered using two 8-pin dip switches.) These RX and TX lines are used by the UART for the RECEIVE and TRANSMIT BAUD CLOCKS.

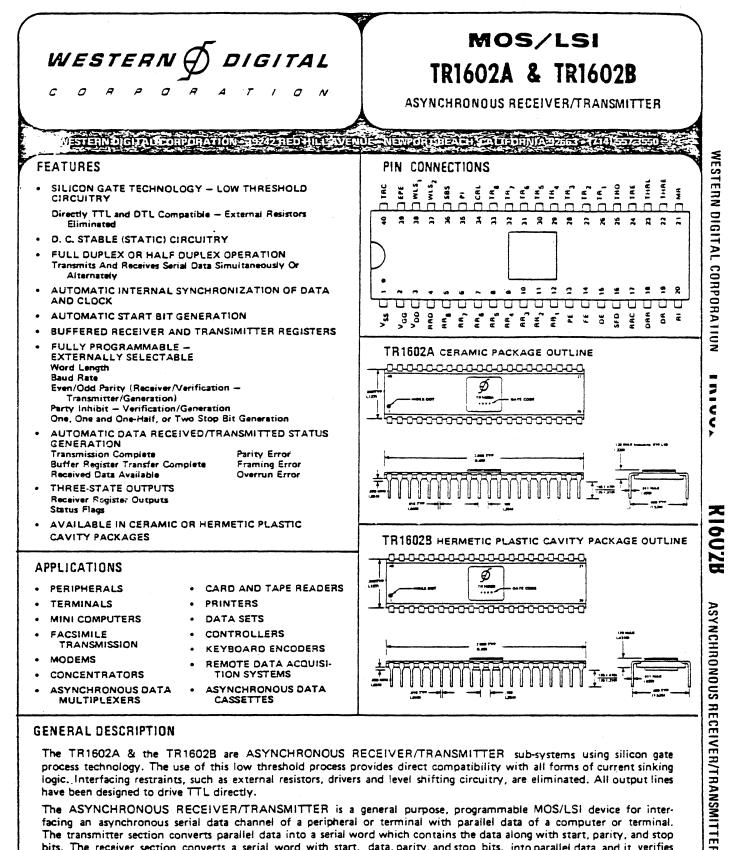

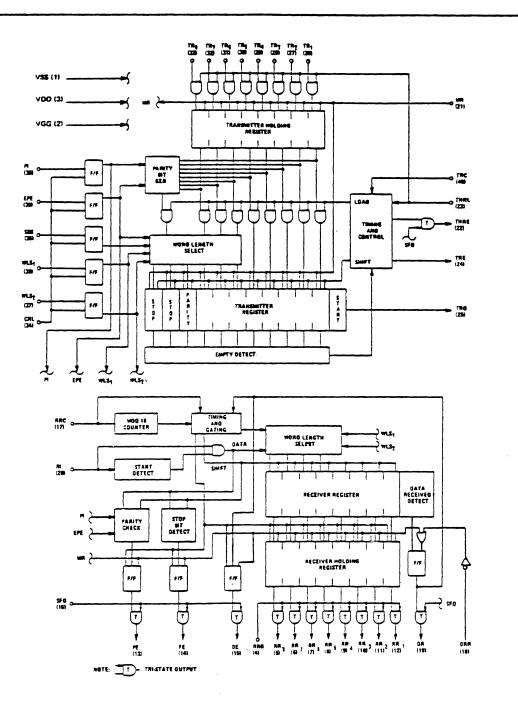

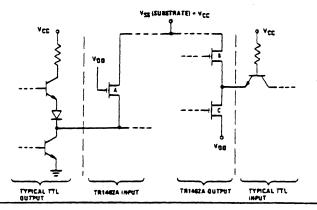

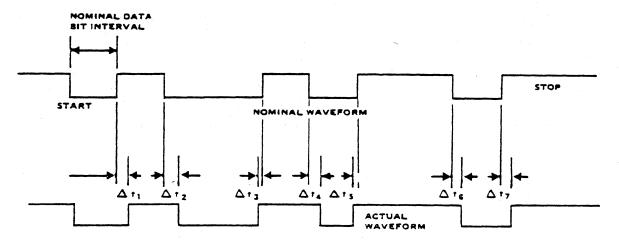

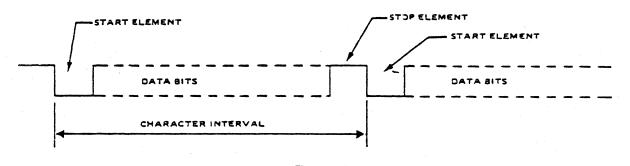

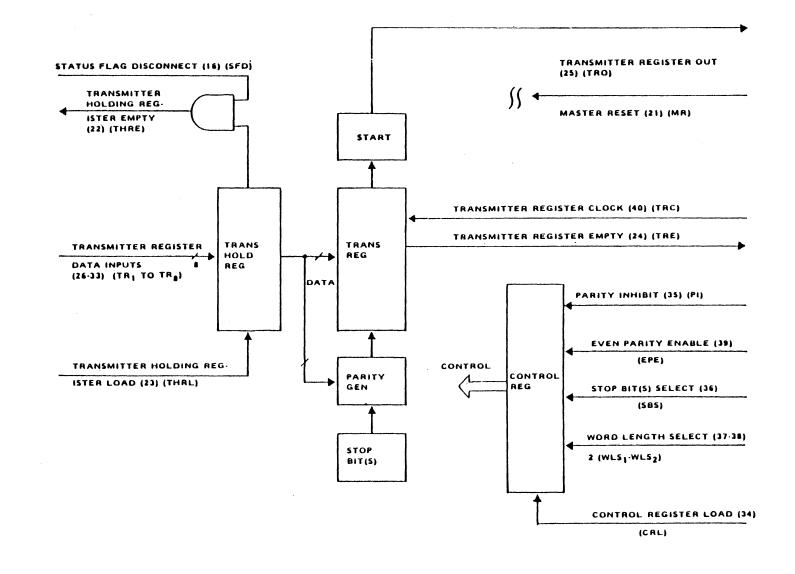

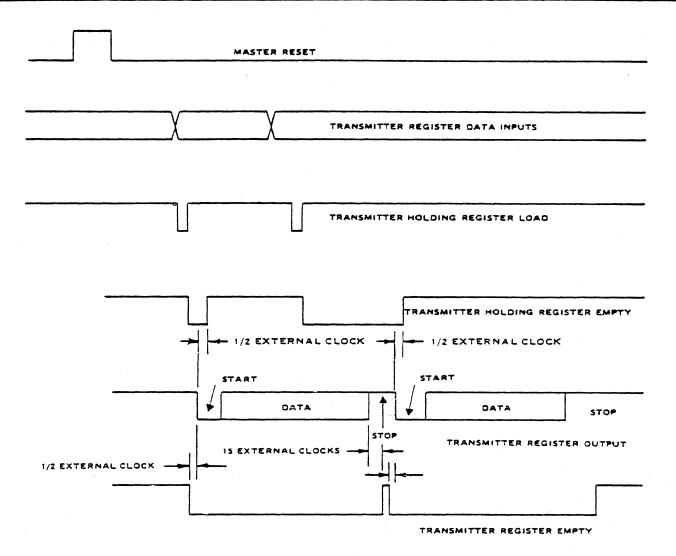

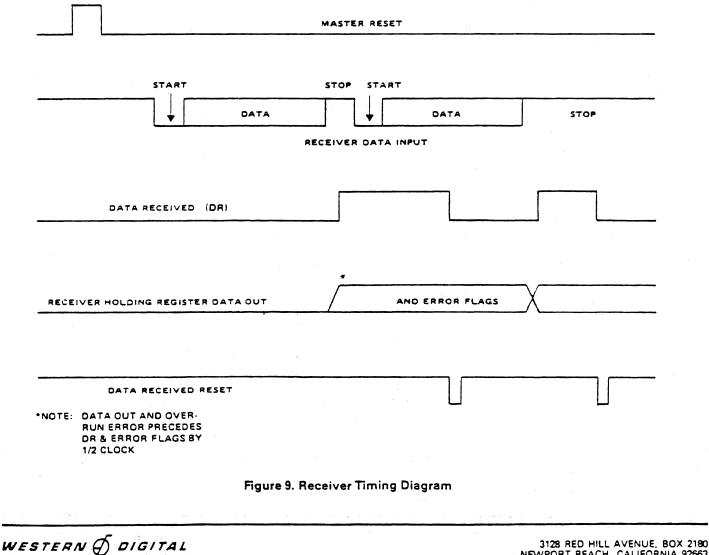

### TR1602B UART

The TR1602B Universal Asynchronoous Receiver/Transmitter (UART) is the heart of the serial interface. It takes parallel data from the CPU BUS and converts it to serial data and at the same time can receive serial data and convert it to parallel. It has two registers which can be read--one for the status and the other with received data. It has two registers which can be loaded--one with transmit data and the other with control information (word length, parity, stop bits). Refer to the Data Sheet of the Western Digital TR1602B for further details of operation.

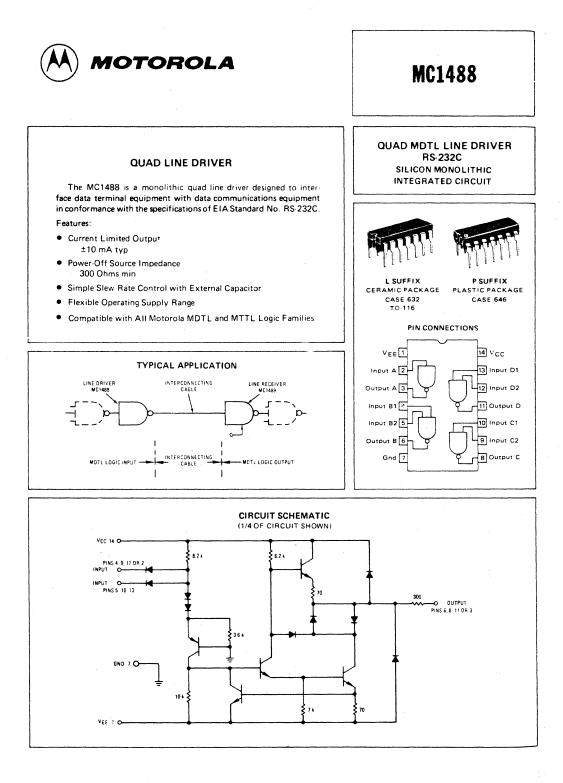

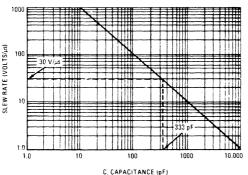

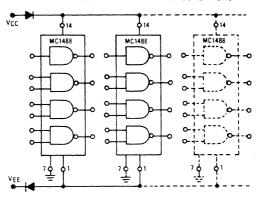

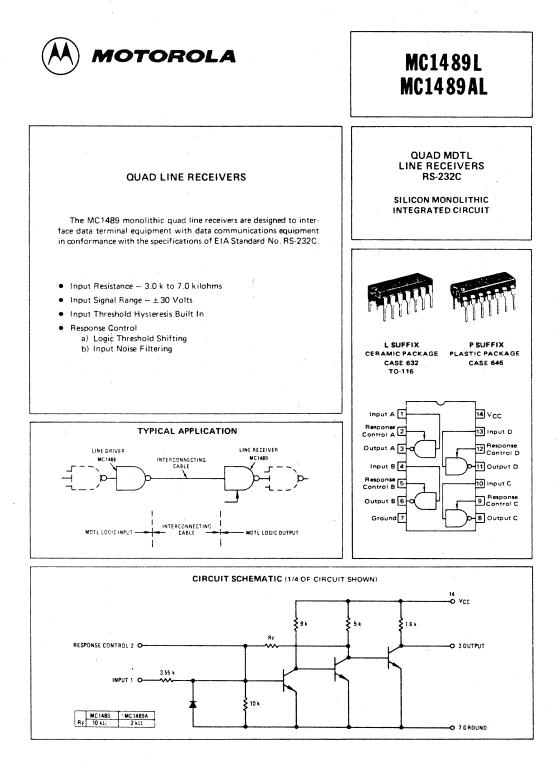

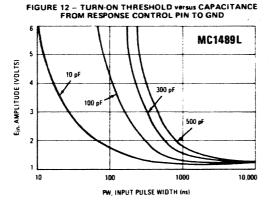

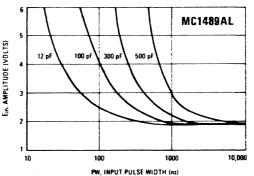

# EIA RS232C and 20mA LEVEL SHIFTERS AND DRIVERS

The serial output of U40 is pin25 (TRQ). It drives U18 for buffering to EIA Driver U61-9 and the 20mA driver U50-6. Serial data can be output by U26-10 which drives both U50-7 and U61-10. U50, R23, and R24 provide the 20mA interface. When U50 conducts it allows about 20mA of current to flow (20mA=mark,0mA=space). Received serial data is brought in to U51-4. U51 is an EIA to TTL receiver. The 20mA serial input is accomplished by the current to voltage conversion of R25 and R26. The TTL received data is fed to the Receive Data (RI,U40-20) of the UART and is fed to U33-12 to be read as part of the Modem Status Buffer.

### HANDSHAKE LATCH

U26 is the handshake latch.  $D\emptyset-D2$  inputs to U26 pins 4, 5, and 12 respectively. The latch is loaded when OUT EAH (U16-5) goes low which is input to U26-9. The outputs of U26 are fed to U61-12,13 and U61-4,5 for level conversion to EIA standards.

# MODEM STATUS BUFFER

U33 is the modem status buffer. U52, an EIA receiver, converts EIA levels to TTL. This is input to U33 and enabled to the data bus when IN E8H (U16-7) goes low. In addition, the Serial Input (TTL) is fed to U33-12 to allow the CPU to directly input the serial data.

# CONFIGURATION SENSE JUMPERS

Jumper wires from K,N,P,M, and J connected to E5 or E6 select whether the associated data bit is a "l" or a " $\emptyset$ " when U28 is enabled onto the data bus. It is enabled by IN E9H (U16-6) and is used by serial driver programs so that stop bits, parity, and word length can be selected by hardware configuration.

### DECODING AND CONTROL LOGIC

The port address decoding (IN,OUT-E8,E9,EA,EB) is accomplished by U41 and U16. U41 decodes the upper 6 bits (E8) and outputs to the strobe inputs of U16. The lower two address bits (A1,A0) feed to the A and B inputs of U16. U16 is a 2/4 line decoder and its outputs (active low) select which port is addressed and whether it is an IN or OUT instruction. U23 pins 1 and 2 are driven by INEAH and INEBH such that whenever the Receive Register and the Status Regiser of the UART are read, U39 drives the data onto the data bus. Below is a summary of the address decoding:

IN E8H - Modum Status Register IN E9H - Configuration Jumpers IN EAH - UART Status Register IN EBH - UART Receive Register, Data Received Reset OUT E8H - Master Reset OUT E9H - Not Used OUT EAH - Control Register Load, Handshake Latch Load OUT EBH - Transmit Holding Register Load

# SERIAL INTERFACE PORT ADDRESSING

| Data<br>Bit | Jumper<br>Letter | Configuration<br>Jumpers        | UART Control<br>Register<br>Handshake Latch | UART Status<br>Register | Modem Status<br>Register      |

|-------------|------------------|---------------------------------|---------------------------------------------|-------------------------|-------------------------------|

| D7          | j                | Even/Odd Parity<br>1=Even 0=Odd | Even/Odd Parity                             | Data Received<br>l=True | Clear to send<br>Pin 5 DB-25  |

| D6          | m                | Word Length 1                   | Word Length 1                               | THRE 1=True             | DSR<br>Pin 6 DB-25            |

| D5          | р                | Word Length 2                   | Word Length 2                               | OverrunError<br>1=True  | CD<br>Pin 8 DB-25             |

| D4          | n                |                                 | Stop Bit Slct.<br>1=2bits,0=1bit            | Framing Err.<br>1=True  | Ring Indctor.<br>Pin 22 DB-25 |

| D3          | k                |                                 | Parity Inhibit<br>1 disabled par.           | Parity Error<br>1=True  |                               |

| D2          |                  |                                 | Break,O Disable<br>Transmit Data            |                         |                               |

| D1          |                  |                                 | Request to Send<br>Pin 4 DB-25              |                         | Receiver In.<br>UART Pin 20   |

| DO          |                  |                                 | Data Terminal<br>Ready<br>Pin 20 DB-25      |                         |                               |

|             |                  | IN ØE9H                         | OUT ØEAH                                    | IN ØEAH                 | IN ØE8H                       |

# REAL TIME CLOCK