# ILLIAC IV SYSTEM STUDY PROGRESS REPORT NO. 2

SUBMITTED TO

UNIVERSITY OF ILLINOIS

UNIVERSITY OF ILLINOIS PURCHASE ORDER NO. 09852-B

Burroughs Corporation

# CONTENTS

|                                        |                                          |   |   |     | Page |

|----------------------------------------|------------------------------------------|---|---|-----|------|

| SECTION I                              | INTRODUCTION                             | • |   | •   | 1-1  |

| SECTION II                             | THE ILLIAC IV SYSTEM                     |   |   |     | 2-1  |

|                                        | ROUTING                                  | • | • | •   | 2-1  |

|                                        | Shifting at the PE Level                 |   | • |     | 2-3  |

|                                        | Shifting at the Quadrant Level           | • | • |     | 2-3  |

|                                        | Inter-Quadrant Transfers                 |   | • | •   | 2-7  |

|                                        | Machine Instruction                      |   | • |     | 2-8  |

|                                        | THE MULTIPLY ALGORITHM                   |   |   |     | 2-8  |

| ************************************** | EIGHT-BIT WORD LENGTHS                   | • |   |     | 2-12 |

|                                        | COMMON DATA PATHS                        |   |   |     | 2-14 |

|                                        | Input-Output Buffering                   |   |   |     | 2-14 |

|                                        | From Control Unit to Processing Element. |   |   |     | 2-15 |

| <b>S</b>                               | From Processing Element to Control Unit. |   |   |     | 2-16 |

|                                        | Evaluation                               |   | • | i   | 2-16 |

|                                        | MODE                                     |   |   |     | 2-17 |

|                                        | Introductory Considerations              | • |   |     | 2-17 |

|                                        | The Problem                              |   |   |     | 2-18 |

|                                        | Back-up Storage in the Control Unit      |   |   |     | 2-18 |

|                                        | Back-up Storage in Processing Element.   |   |   | •   | 2-19 |

|                                        | Functional Capability                    |   |   |     | 2-20 |

|                                        | Comparison                               |   |   |     | 2-20 |

|                                        |                                          |   |   | , Š |      |

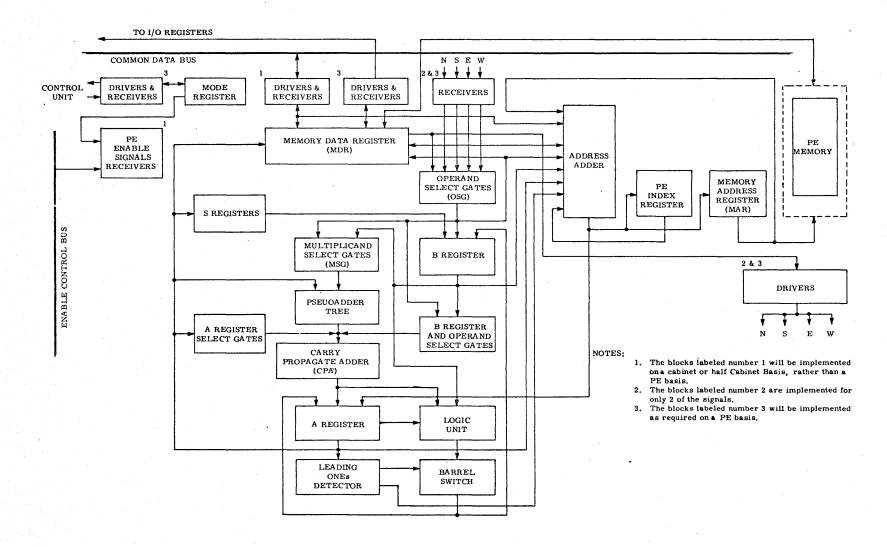

| SECTION III                            | REVISED PE LOGIC DESIGN                  |   |   |     | 3-1  |

|                                        | PROCESSING ELEMENT DESCRIPTION           | • |   |     | 3-1  |

|                                        | MEMORY DATA REGISTER (MDR)               |   |   |     | 3-1  |

|                                        | OPERAND SELECT GATES (OSG)               |   |   | •   | 3-4  |

|                                        | A-B REGISTER (ACCUMULATOR)               |   |   |     | 3-4  |

|                                        | LOGIC UNIT                               | • |   |     | 3-4  |

|                                        | BARREL SWITCH                            |   | • |     | 3-5  |

|                                        | LEADING ONES DETECTOR                    | • |   |     | 3-5  |

|                                        | MULTIPLICAND SELECT GATES                |   |   |     | 3-5  |

# CONTENTS (Cont.)

|             |                                           | Page  |

|-------------|-------------------------------------------|-------|

| SECTION III | (Continued)                               |       |

|             | PSEUDOADDER TREE                          | 3 - 5 |

|             | CARRY PROPAGATE ADDER (CPA)               | 3-5   |

|             | MODE REGISTER                             | 3-6   |

|             | ADDRESS REGISTER                          | 3-6   |

|             | PE INDEX REGISTER                         | 3-6   |

| •           | MEMORY ADDRESS REGISTER (MAR)             | 3-7   |

|             | SPECIAL REGISTER (SR)                     | 3-7   |

| SECTION IV  | THE I/O SUBSYSTEM                         | 4-1   |

|             | GENERAL CONSIDERATIONS                    | 4-1   |

|             | DISK STORAGE                              | 4-2   |

|             |                                           |       |

| SECTION V   | PROGRAMMING                               | 5-1   |

|             | REVISED PE INSTRUCTIONS                   | 5-1   |

|             | CONTROL UNIT INSTRUCTIONS                 | 5-4   |

|             | Elements of the Control Unit              | 5-6   |

|             | Discussion of the Instructions            | 5-6   |

| SECTION VI  | ILLIAC IV APPLICATIONS STUDY              | 6-1   |

|             | DESCRIPTION OF THE COOLEY-TUKEY ALGORITHM | 6-1   |

|             | MACHINE IMPLEMENTATION                    | 6-3   |

|             | IMPLEMENTATION ON ILLIAC IV               | 6-4   |

|             | STORAGE OF THE COEFFICIENTS A(k)          | 6-6   |

|             | COMPUTATION AND STORAGE OF INTERMEDIATE   |       |

|             | RESULTS                                   | 6-6   |

|             | COMPUTATIONS REQUIRED                     | 6-10  |

| SECTION VII | CIRCUIT DESIGN - THE ECL CIRCUIT          | 7-1   |

# LIST OF ILLUSTRATIONS

|                                                                   | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE Level Shifting                                                 | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Quadrant Nearest Neighbor Connections                             | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pseudo Physical Layout of a Quadrant                              | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| "Nearest Neighbors" Arrangement of Full Array,                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Showing Quadrant Subarrays                                        | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Logic Elements Involved in Multiply Algorithm                     | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| System for Handling Data From Control Unit to                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Processing Element, Block Diagram                                 | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Revised PE Logic Design, Block Diagram                            | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Intermedian of heart Dinama Number to Define                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                   | 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   | 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| The Distribution of the Coefficients A(k) in the Array Initially. | 6-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

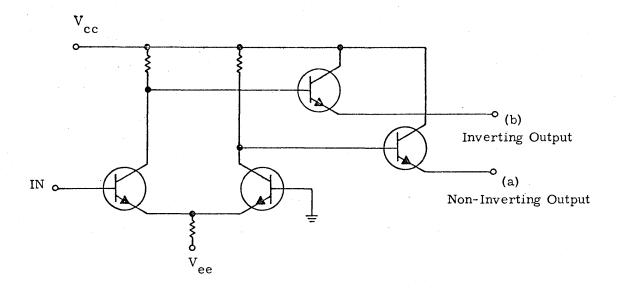

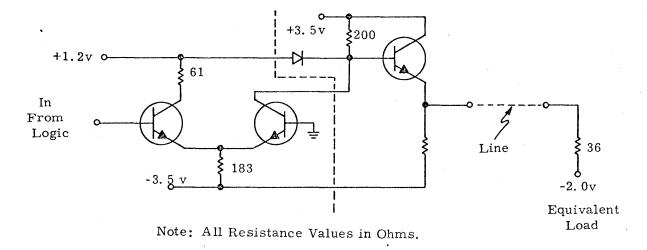

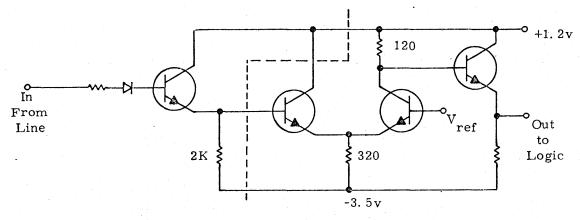

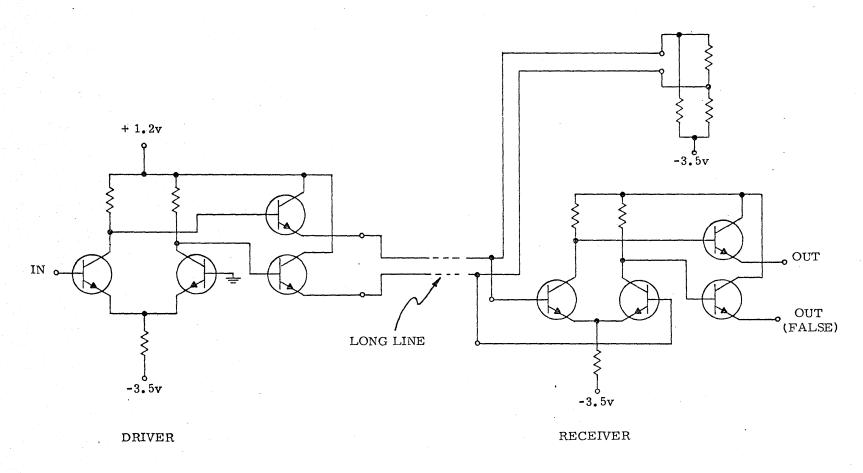

| ECL Gate. Schematic Diagram                                       | 7-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   | 7-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   | 7-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   | 7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

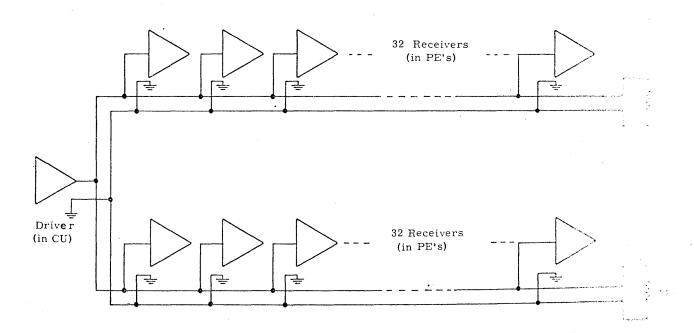

| Signals from CU to PE's                                           | 7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Shift Table, Showing Shifts by One's and Shifts by Eight's        | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Relationship of Gate Size to Multiplier Size                      | 2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                   | Quadrant Nearest Neighbor Connections. Pseudo Physical Layout of a Quadrant "Nearest Neighbors" Arrangement of Full Array, Showing Quadrant Subarrays Logic Elements Involved in Multiply Algorithm System for Handling Data From Control Unit to Processing Element, Block Diagram  Revised PE Logic Design, Block Diagram  Interpretation of k as a Binary Number to Define Storage Location of A(k) The Numbering of the PE's Within a Quadrant The Distribution of the Coefficients A(k) in the Array Initially  ECL Gate, Schematic Diagram Driver, Schematic Diagram Receiver, Schematic Diagram ECL Driver-Receiver, Balanced Signals, Schematic Diagram Use of Drivers and Receivers for Distributing Control Signals from CU to PE's  Shift Table, Showing Shifts by One's and Shifts by Eight's. |

# LIST OF ILLUSTRATIONS (Cont'd)

| Table      |                                                                                                                     | Page       |

|------------|---------------------------------------------------------------------------------------------------------------------|------------|

| 3-1        | PE Logic Requirements                                                                                               | 3-3        |

| 4-1        | 512-Bit, Parallel Organizations for the Librascope 4802                                                             | 4-6        |

| 6-1<br>6-2 | Shifts Required for Combinations of Bits $j_{r-2}$ and $k_{m-r}$ . Shifting Required for the Final Eight Iterations | 6-8<br>6-9 |

| 7-1        | Signals Requiring Driver and Receiver                                                                               | 7-6        |

# SECTION I

#### INTRODUCTION

This report is the second of three reports to be submitted during the Phase I effort of the ILLIAC IV Program. At this measured milestone in the development of the ILLIAC IV system real progress is indeed evident.

There exists now a detailed specification of the Processing Element for which a fully compatible and complete instruction repertoire has been developed. In addition, the data transfer paths establishing the links between the Input-Output and the Array, between the Control Unit and the Array, and between the elements of the Array have been specified.

Progress in defining the system hardware has also been made. A family of logic circuits has been selected and is currently undergoing an intense packaging effort. The size, type and speed of the memory system for the Array has been selected.

Progress in defining the applications areas, particularly that progress made at the University of Illinois, is especially evident.

The contents of this report in conjunction with the first report contain much of the rationale for the present system definition.

For the remainder of Phase I, much work remains. Although most of the functions and specifications of the I/O and the Control Units have been identified some additional work is needed.

In the area of packaging, both at the cabinet level and the logic level, detail design remains. Such items as power distribution, system cooling and general installation detail must be specified. Finally the entire procurement must be matched to a comprehensive program plan of schedule and delivery which is mutually acceptable.

#### SECTION II

#### THE ILLIAC IV SYSTEM

This section contains discussions of specific systems problems which are considered to be of major importance in the design of the ILLIAC IV System.

#### ROUTING

One of the instructions in ILLIAC IV is to transfer data residing in the PE array to new locations in that array. This is called the "routing" instruction. One version of this instruction will take the data from the nth PE and transfer it to the (n + m)th PE, where m is an indexable variant contained within the instruction, and n runs over all PE's. Disabled PE's are not to receive any new data or lose any of the data they are currently holding as a result of this instruction.

The immediate reaction to such a requirement is to implement all the required various paths by brute force. Such a solution is not only expensive, but unnecessary, and of inferior performance. To find a superior method of implementing routing, it will help to consider individual properties of the routing process. From a functional viewpoint the four properties of concern for routing are the level, the timing, the modulo, and the increment.

In the array of 256 PE's the levels of shifting with which we are concerned may be divided into shifts between quadrants, shifts between the same elements of a quadrant and shifts within a Processing Element.

The timing refers to the execution time of the shift and its concurrency with other array instructions.

The modulo is the end-around size of the shift which can be variable up to a given maximum size. For instance a 64-bit shifter may be designed to shift 64 bits end-around or eight 8-bit bytes end-around depending on the modulo control.

The increment is the smallest shifting amount of which all shifts are a multiple. Bit shifts would have an increment of 1, byte shifts would require 8, etc.

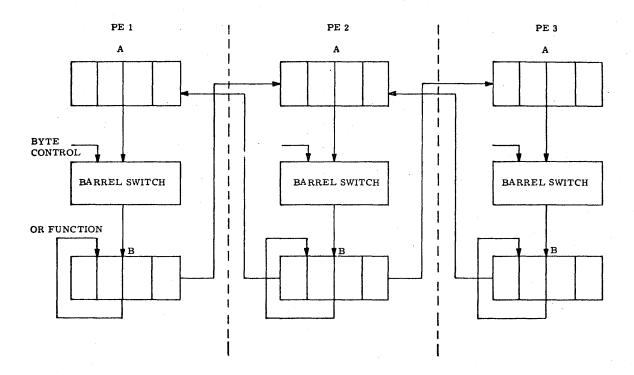

Figure 2-1. PE Level Shifting

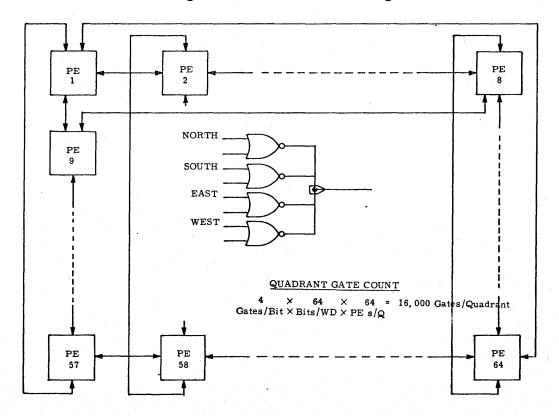

Figure 2-2. Quadrant Nearest Neighbor Connections

The variations on these properties are many, and since the function involves a very large number of bits the different variations involve substantial differences in cost.

## Shifting at the PE Level

The first level of consideration is the shifting of operands within the PE. Here a barrel switch is provided which will shift in increments of 1-bit-multiples at the 64-bit-operand level.

A modulo control may be employed by adding an additional logic input to the first level of gating in the barrel switch and an additional gate to the receiving register input. Such modulo capability may include 8-, 32-, and 64-bit bytes and be extended to link PE's by a full word transfer at the end of the switching cycle (figure 2-1).

The execution time of this shifting will require one pass through the barrel switch for modulo 64 shifts, two passes through the barrel switch for end off switching, and four passes for end-around. Otherwise a transfer of Register B to the neighboring Register A will extend this capability between PE's. For the most part this logic capability exists within a PE, and there is no concurrency of execution at this level.

# Shifting at the Quadrant Level

At this level of shifting, considering the variety of desirable shifting properties available, there are many possibilities. Two seemingly practical forms at the Quadrant level are nearest neighbor connections and the quadrant barrel switch. These two shifting approaches represent the practical minimum and maximum cost for the ILLIAC IV System.

NEAREST NEIGHBOR CONNECTIONS - Figure 2-2 shows the necessary data paths and gates to implement this shift approach. It has the capability of shifting left or right 4096 bits in increments of 64 and 512 bits. Increments smaller than this may be shifted with the local barrel switch if desirable since concurrency is not possible here.

All shifting must be done in sequence with all arithmetic and logic instructions; all shifted amounts are combinations of the basic two increments. Shifting of a modulo size smaller than the whole quadrant is done by mode control of the PE's.

THE QUADRANT BARREL SWITCH - The main advantage of the quadrant barrel switch is its ability to execute any shifted amount (in increments of 8) in two passes through it. Each shift can be executed concurrently with other instructions

in the PE. Modulo control is accomplished by controlling the contents of the Routing Register between partial shifts.

# A COMPARISON OF THE TWO APPROACHES -

- 1. The two methods can produce identical results with differences in execution time and cost. Ignoring time and cost the methods are functionally equivalent.

- 2. There is an approximate cost difference of six to one. If we ignore the requirement for special circuits to transmit signals long distances, the simple gate count for the quadrant barrel amounts to 20% of the total system.

- 3. Physical distance is an important consideration. Figure 2-3 depicts a psuedo physical layout of the quadrant in which the interconnected PE for the Nearest Neighbor Connections may be reasonably close. Perhaps a maximum distance of 6 feet may be realized.

With the quadrant barrel however some paths are long. Considering a centrally placed barrel switch in the middle of a 27 foot quadrant cabinet row, one row per quadrant, the worst-case distance would be about 30 feet.

This means that every shift, however short, will involve 30 feet of cable delay plus logic. The following computation shows anticipated delay times.

#### Barrel Switch

Cable:  $30^{1} \times 1.7 \text{ nsecs/ft.}$  = 51.0 nsecs.

Logic: 8 gates  $\times$  3 nsecs/levels =  $\frac{24.0}{75.0}$  nsec/shift

# Nearest Neighbor

Cable:  $6^{1} \times 1.7 \text{ nsecs/ft.}$  = 10.2 nsecs.

Logic: 3 gates  $\times$  3 nsecs/gate =  $\frac{9.0}{19.2}$  nsecs/shift

Average Barrel Switch Time = 75.0 nsecs.

Average Nearest Neighbor Time = 4 × 19.2 = 76.8 nsecs.

$<sup>^*</sup>$ Refer to table 2-1, page 2-5.

Table 2-1. Shift Table, Showing Shifts by One's and Shifts by Eight's

| Desired | Shift    | Shift                             |                   | Desired | Shift    | Shift      |       |

|---------|----------|-----------------------------------|-------------------|---------|----------|------------|-------|

| Shift   | by One's | by Eight's                        | Total             | Shift   | by One's | by Eight's | Total |

| 0       | 0        | 0                                 | 0                 | 32      | 0        | 4          | 4     |

| 1       | +1       | 0                                 | 1                 | 33      | +1       | 4          | 5     |

| 2       | +2       | 0                                 | 2                 | 34      | +2       | 4          | 6     |

| 3       | +3       | 0                                 | 3                 | 35      | +3       | 4          | 7     |

| 4       | +4       | 0                                 | 4                 | 36      | -4       | -3         | 7     |

| 5       | -3       | +1                                | 4                 | 37      | -3       | -3         | 6     |

| 6       | -2       | +1                                | 3                 | 38      | -2       | -3         | 5     |

| 7       | -1       | +1                                | 2                 | 39      | -1       | -3         | 4     |

| 8       | 0        | +1                                | 1                 | 40      | 0        | -3         | 3     |

| 9       | +1       | +1                                | 2                 | 41      | +1       | -3         | 4     |

| 10      | +2       | +1                                | 3                 | 42      | +2       | -3         | 5     |

| 11      | +3       | +1                                | 4                 | 43      | +3       | -3         | 6     |

| 12      | +4       | +1                                | 5                 | 44      | -4       | -2         | 6     |

| 13      | -3       | +2                                | 5                 | 45      | - 3      | -2         | 5     |

| 14      | -2       | +2                                | 4                 | 46      | -2       | -2         | 4     |

| 15      | -1       | +2                                | 3                 | 47      | -1       | -2         | 3     |

| 16      | 0        | +2                                | 2                 | 48      | 0        | -2         | 2     |

| 17      | +1       | +2                                | 3                 | 49      | +1       | -2         | 3     |

| 18      | +2       | +2                                | 4                 | 50      | +2       | -2         | 4     |

| 19      | +3       | +2                                | 5                 | 51      | +3       | -2         | 5     |

| 20      | +4       | +2                                | 6                 | 52      | -4       | - 1        | 5     |

| 21      | - 3      | +3                                | 6                 | 53      | -3       | -1         | 4     |

| 22      | -2       | +3                                | 5                 | 54      | -2       | -1         | 3     |

| 23      | - 1      | +3                                | 4                 | 55      | -1       | - 1        | 2     |

| 24      | 0        | +3                                | 3                 | 56      | 0        | -1         | 1     |

| 25      | +1       | +3                                | 4                 | 57      | +1       | -1         | 2     |

| 26      | +2       | +3                                | 5                 | 58      | +2       | -1         | 3     |

| 27      | +3       | +3                                | 6                 | 59      | +3       | -1         | 4     |

| 28      | +4       | +3                                | 7                 | 60      | -4       | 0          | 4     |

| 29      | -3       | 4                                 | 7                 | 61      | -3       | 0          | 3     |

| 30      | -2       | 4                                 | 6                 | 62      | -2       | 0          | 2     |

| 31      | - 1      | 4                                 | 5                 | 63      | -1       | . 0        | 1     |

| Average | number o | $f \text{ shifts} = \frac{25}{6}$ | $\frac{5}{4} = 4$ |         |          |            |       |

- 4. However, real problems are not random with average shifts. The data to be shifted often falls into patterns which, with proper programming, can be made to somewhat fit the available shifting patterns of the partial shifting scheme, and save time over the average time taken for transfer of randomly placed data. Some examples of such savings follow.

- (a) The Cooley-Tukey algorithm for spectrum analysis in one form involves swapping data between PE's which are half an array apart at the first swap, a quarter of an array apart at the second swap, an eighth at the third, and so on. Over each 64-PE quadrant, these transfers are accomplished with four, two, and one partial shifts respectively, or an average of 2.333 partial shifts for each actual data transfer. This is considerably faster than the four partial shifts required for a random data transfer, and is faster than the data transfer effected through the all-possible-paths scheme.

- (b) Another use for the data transfer paths which cover the array is in the computation of global variables ("Global" here means a variable which acquires its definition from data which covers all the PE's). Maximum, minimum, logical AND, across-word parity, sum, product, are examples of functions which one might want to perform on corresponding words in all PE's, more or less in parallel across the array, producing a one-word result. Since PE's are only capable of two-operand operations, a combination of the 64 corresponding variables from the 64 PEs of one quadrant into one resulting variable must take at least six operational steps, consisting of 32 operations on the variables by pairs, then a pairwise combining of the 16 resulting pairs, and so on. Between

Figure 2-3. Pseudo Physical Layout of a Quadrant

| 0   | 17  | 1   | 16  | 2   | 15  | 3    | 14  | 4             | 13  | 5   | 12  | 6   | 11  | 7   | 10  |   |

|-----|-----|-----|-----|-----|-----|------|-----|---------------|-----|-----|-----|-----|-----|-----|-----|---|

| 360 | 377 | 361 | 376 | 362 | 375 | 363  | 374 | 364           | 373 | 365 | 372 | 366 | 371 | 367 | 370 |   |

| 20  | 37  | 21  | 36  | 22  | 35  | 23   | 34  | 24            | 33  | 25  | 32  | 26  | 31  | 27  | 30  |   |

| 340 | 357 | 341 | 356 | 342 | 355 | 343  | 354 | <br>  344     | 353 | 345 | 352 | 346 | 351 | 347 | 350 |   |

| 40  | 57  | 41  | 56  | 42  | 55  | 43   | 54  | <br>  44<br>  | 53  | 45  | 52  | 46  | 51  | 47  | 50  |   |

| 320 | 337 | 321 | 336 | 322 | 335 | 323  | 334 | 324           | 333 | 325 | 332 | 326 | 331 | 327 | 330 |   |

| 60  | 77  | 61  | 76  | 62  | 75  | 63   | 74  | 64            | 73  | 65  | 72  | 66  | 71  | 67  | 70  |   |

| 300 | 317 | 301 | 316 | 302 | 315 | 3 03 | 314 | <br>  304<br> | 313 | 305 | 312 | 306 | 311 | 307 | 310 | _ |

| 100 | 117 | 101 | 116 | 102 | 115 | 103  | 114 | 104           | 113 | 105 | 112 | 106 | 111 | 107 | 110 |   |

| 260 | 277 | 261 | 276 | 262 | 275 | 263  | 274 | 264           | 273 | 265 | 272 | 266 | 271 | 267 | 270 |   |

| 120 | 137 | 121 | 136 | 122 | 135 | 123  | 134 | 124           | 133 | 125 | 132 | 126 | 131 | 127 | 130 |   |

| 240 | 257 | 241 | 256 | 242 | 255 | 243  | 254 | 244           | 253 | 245 | 252 | 246 | 251 | 247 | 250 |   |

| 140 | 157 | 141 | 156 | 142 | 155 | 143  | 154 | 144           | 153 | 145 | 152 | 146 | 151 | 147 | 150 |   |

| 220 | 237 | 221 | 236 | 222 | 235 | 223  | 234 | 224           | 233 | 225 | 232 | 226 | 231 | 227 | 230 |   |

| 160 | 177 | 161 | 176 | 162 | 175 | 163  | 174 | 164           | 173 | 165 | 172 | 166 | 171 | 167 | 170 |   |

| 200 | 217 | 201 | 216 | 202 | 215 | 203  | 214 | 204           | 213 | 205 | 212 | 206 | 211 | 207 | 210 |   |

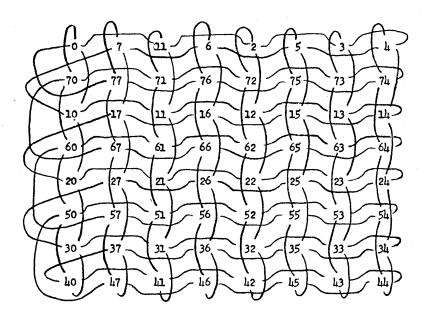

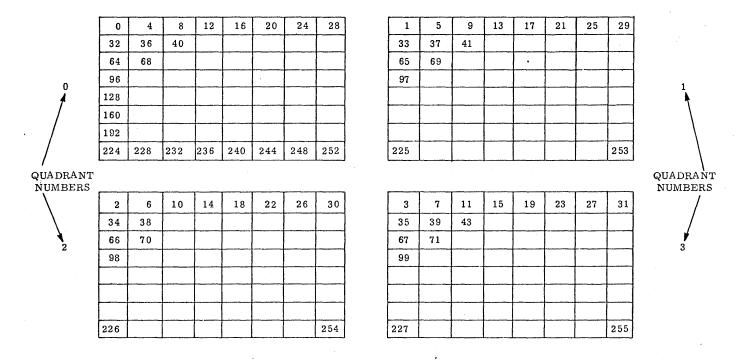

Figure 2-4. "Nearest Neighbors" Arrangement of Full Array, Showing Quadrant Subarrays

each operation a transfer of data occurs to place it in position for the next operation. Thus a global function takes six binary operations and five data transfer times when implemented within the system which has all possible paths. The above description of a sequence of steps is correct even if a single instruction calls forth the whole sequence.

Global functions are in the same category as the Cooley-Tukey algorithm as far as data transfer is concerned. The data is shifted by 2 and combined with an unshifted copy, and so on up to a shift of 32, for the 64-element subarray. For the nearest neighbors scheme, an average of 2.33 partial shifts per actual shift is called for. The nearest neighbor connections would thus seem to have a slight advantage in speed over the quadrant barrel in executing global functions such as maximum, minimum, global AND, global OR, and across-word parity.

5. The conclusion is that we do not buy anything by implementing schemes which transer data across from one side of the array to the other with a single step. The time it takes for the data to travel across the array is sufficient to permit several logical operations. It is possible to find a set of partial data transfer paths which result in simpler mechanization and lesser wiring, and which do not degrade performance. Furthermore, by avoiding the barrel, we also avoid the necessity for allowing maximum delay on each transfer, and when the data is ordered, or partially ordered, a speedup is accomplished which would be impossible in the more expensive system.

#### Inter-Quadrant Transfers

Shifting between quadrants is dependent on the type of intraquadrant shifting selected, but the considerations at the interface are similar. The choice of transferring all words of a quadrant as a column (row) may be made for either case.

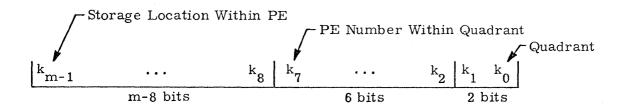

Here also a similar layout of PE as was done for the quadrant (figure 2-3) can make edge switching faster than quadrant switching. Figure 2-4 shows an arrangement of the whole array, 256 PE's, with the same properties for the whole array that figure 2-3 has for the 64 PE's of the single quadrant. PE's which differ in number by ±1 or ±16 from a subject PE are physical neighbors of it, just as in figure 2-3, where PE's which differ in number by ±1 or ±8 of a given PE are physical neighbors thereof. Furthermore, each quarter of the diagram of figure 2-4, as indicated by the dotted lines, is a copy of figure 2-3. To allow one to see this latter point, the PE's in figure 2-4 are numbered from 0 to 377 in octal. To translate from an entire array PE numbering, as shown in figure 2-4, to quadrant numbering, one may suppress the first and fifth bit of the binary equivalent of the octal PE number. When this is done, each quarter of figure 2-4 is like figure 2-3, with those on the right reflected about the vertical axis, and those on the bottom reflected about the horizontal axis. The lower right quadrant, for example, is like figure 2-3 both upside down and backwards.

#### Machine Instruction

The machine instruction to use this equipment thus requires considerable equipment to translate the instruction into the various shifts required. The number of shifts will differ, depending upon how far around a given quadrant, or whole array, the data is to be shifted. Variants of the shift instruction will be able to call upon the intraquadrant shift even when the entire array is being used. This is of advantage during one possible implementation of the Cooley-Tukey algorithm, for example. A shift of one in the 32-bit-word mode also involves a transfer of half-words between neighboring PE's, since each one is now acting as two half-word PE's.

The shift instruction therefore calls up, possibly an internal barrel shift in the PE, possibly a half-word transfer between neighboring PE's, a variable number of east-west neighbor shifts, and a variable number of north-south shifts. To preserve the contents of the A and B registers of the disabled PE's, intervening steps must avoid the A and B registers, which may be only an initial source of data, or the destination at the final shift. Either the MDR or the S register, therefore, is involved in routing, with strong preference to the MDR, since it is desirable, even though maybe not as absolutely necessary, to save the S register as well as the A and B.

#### THE MULTIPLY ALGORITHM

The most important single logic function from the standpoint of both performance and cost is the multiply. The emphasis placed on this instruction in its design and application singles it out for special discussion.

When first considering the many different ways to implement the multiply the ILLIAC array itself offers the first direction. There is a class of algorithms which takes advantage of the statistical nature of the ONE and ZERO trains in the multiplier. The average execution time of such a multiply is always less than a worst-case pattern of ONE and ZERO in the multiplier and, therefore, in the course of a program run, the multiply time is the average multiply time.

However, because of the lock-step synchronous operation of the Array which handles up to 256 pairs of operands simultaneously, the average execution time becomes the worst-case time. Such methods therefore are not applicable to the ILLIAC system.

Following the above, the next decision to be made is how many bits of the multiplier are to be examined and disposed of simultaneously during a single step in the cyclic multiply sequence. Apart from circuit speeds, this is the single basis for determining the speed of the multiply. Two separate, yet interdependent, techniques, are available to do this. One technique is to encode fields of the multiplier into a larger number base\*; and the second technique is to combine manifold summands selected by the conditions of the multiplier bits. In practice these two techniques are combined into a single comprehensive design. The following general relation is useful in determining the size of the partial multiplier:

Execution time:

$$(\frac{MB}{XB} + 3)$$

G·  $\triangle$  t

#### Where:

MB = Number of bits in the mantissia

XB = Number of bits in the partial multiplier

G = Number of gates in typical delay chain

$\Delta_{+}$  = Nominal gate delay including loading, wire length, etc.

Reasonable values for the above parameter are:

MB = 48 bits

G = 10 gates selected as typical PE logic chain

$\Delta_t$  = 3 nanoseconds/gate

Execution time = memory cycle time = 250 nanoseconds.

Therefore: XB = 8 bits.

Table 2-2 shows the relative speed-cost relation for the range of possible partial multiply sizes. The important feature in this table is the gate count differences for the different selected sizes. In terms of a 10K-gate Processing Element the 8-bit selection appears to be a reasonable maximum hardware investment.

<sup>\*</sup>MacSorley, O. L., "High-Speed Arithmetic in Binary Computer." Proceedings of the IRE, pp. 67-71, January 1961.

Wallace, C.S., "A Suggestion for a Fast Multiplier, "IEEE Transactions on Electronic Computers, V. EC-13, February 1964.

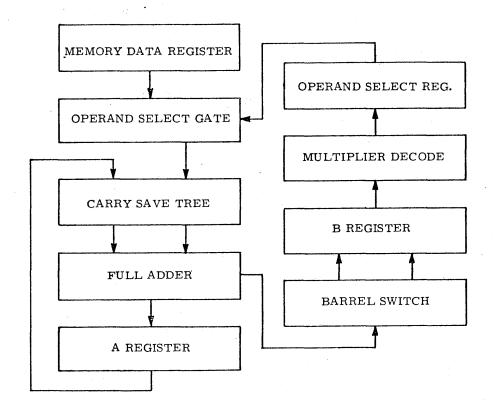

Figure 2-5. Logic Elements Involved in Multiply Algorithm

Figure 2-6. System for Handling Data From Control Unit to Processing Element, Block Diagram

Table 2-2. Relationship of Gate Size to Multiplier Size

| Number of<br>Partial Multiplier Bits | 1 0   |     |  |  |  |

|--------------------------------------|-------|-----|--|--|--|

| 6                                    | 2,000 | 330 |  |  |  |

| 8                                    | 2,800 | 270 |  |  |  |

| 12                                   | 4,800 | 210 |  |  |  |

Having decided what constitutes a reasonable number of multiplier bits to handle in a single cycle (in this case 8 bits), the next consideration is to determine how to maintain a 10-gate delay for the worst-case logic chain. To evaluate this criteria the following substeps in the multiply must be completed within a 10-gate chain:

- 1. Decode the partial multiplier.

- 2. Add the next summand to the partial product.

- 3. Shift the multiplier and the partial product.

- 4. Normalize the result.

Figure 2-5 is a block diagram of the logic elements involved in the execution of this algorithm. The delay chain involved is the time to go from register to register.

The multiply algorithm selected first decodes the 8 bits of the multiplier into a base-4 representation into which 0,+1,-1, and +2 values of the operand are selected. This decode is stored in the Operand Select Register (OSR). The OSR is 12 bits long for storing the fully decoded four conditions for each of four operands.

Because the 8 bits of the multiplier are taken as bit pairs, four summands must be added to the partial product in a single cycle. The carry save tree, which contains three full length carry save adders (2 less than the total number of summands) combines four summands plus the partial product into a new sum and carry value. The full adder now combines this sum and carry into a new partial product.

In terms of worst-case delay, the logic chain through the operand select gate, the carry save tree, and the full adder represents the worst-case delay.

Detailed logic design analysis has shown that a nominal 30-nanosecond delay through the chains is possible. A breadboard of the actual hardware must be built and operated to obtain a true final result.

#### EIGHT-BIT WORD LENGTHS

The ILLIAC IV is to be built with several different word lengths. Each 64-bit PE is capable of being split, effectively, into at least two 32-bit PE's. Another desirable word-length breakpoint is at eight 8-bit effective PE's within any given PE. To evaluate this possibility we require, first to know what it costs to expand PE capability to handle eight independent 8-bit words, and second, we need to estimate the worth of the extra capability produced by such an expansion over and above the capability already inherent in the 64-bit PE for handling 8-bit pieces. The conclusion is that all logical operations, probably even add and subtract, are easily programmed for the 64-bit PE so that they make effective use of the parallelism of the 64-bit machine. The only feature that is lacking is the independent mode control of the 8-bit sections of the 64-bit PE.

The price for 8-bit words is mainly in the fragmentation of the controls which results. Existing circuit design contemplates a buffer capable of driving 24 loads. With independent mode control on every 8-bit slice, each 8 bits of a 64-gate transfer command would have to be independently controlled, thus requiring 8 gates instead of the 3 gates required by straightforward implementation of the 64-bit PE. Since there are estimated to be 150 command lines, and the 64-gate transfer command is typical of them, we estimate that 750 gates per PE are added by the fragmentation of the command lines. In addition, the barrel controls multiply, from the three control signals per level required by only one word size, to 24 control signals per level. However, only two levels of control are used in the module eight barrel, so that 42 additional gates are added from this account.

The extra mode register bits for 8-bit operation imply extra lines to the control unit, and extra drivers and receivers for them Twenty-eight such bits per PE will require 28 drivers and 28 receivers in the PE itself, and 3,584 extra drivers and receivers in the control unit. The design difficulties of cable bundles of this bulkiness are considerable at the speeds under consideration.

The 8-bit operation contemplated here assumes we still have no more than one index register per PE. To get eight 8-bit words out of independently specified memory addresses requires eight memory accesses, a situation which is exactly the same as though 8-bit fields were programmatically extracted from 64-bit words in 64-bit operation.

The most promising design of the memory currently contemplated for the ILLIAC IV, representing the best compromise between cost and cycle time, is a nondestructively read memory. Writing a small field, such as 8 bits, into a memory word will require two memory cycles, one to read those portions of the word which are not to be changed, and one to write back the word, one 8-bit field of which has been changed. A store instruction in 8-bit operation, if independent addressing is called for, on each 8-bit word, will require, therefore, 16 memory cycles.

The above hardware operations are hardly better than programmatic implementation in 64-bit mode. Apparently, the chief virtue of implementing 8-bit operations in the PE hardware is that mode register control over the individual operations can be achieved.

All the above circuitry amounts to an additional 800 gates in the PE for 8-bit operation. Probably 1000 gates is a better estimate. From this we conclude that adding 8-bit operation to the 64-bit PE adds about 10% to the equivalent gate count, and presumably also adds 10% to the estimated cost of the PE exclusive of memory.

In addition to the direct cost, there is degradation of the performance in normal 64-bit mode. Were the equipment packaged as a solid volume, lengths would be increased by 3.2% as a result of the 10% increase in components. In a well-matched system, equally sensitive to memory and logic speeds, the result would be a net 1.6% slowdown. Power and cooling requirements also follow the component count.

The opposite question is to enquire to what extent can 8-bit operations be carried on in parallel in a 64-bit PE without the assistance of specific 8-bit operations in the hardware.

Certain operations, which are expected to be frequent operations in 8-bit programming, are independent of word length, such as all bit-by-bit Boolean operations, compare all words against zero, set to specified value, read from memory, store to memory, and others.

Certain operations are programmable in such a way as to make use of much of the parallelism of the 64-bit machine even though the entities being manipulated are only 8 bits long. Add, subtract, and routing, are examples of this class of operation. Add, for example, on words of 7 bits plus sign each, can be handled by removing the sign bit and using the resulting space for overflow control, thus allowing as many adds in parallel as the adder is long. Routing can be partially implemented on all eight 8-bit words at once by means of the barrel. End-around shifts can be implemented by two shifts, which are then partially blanked in accordance with a mask which could be held in the S register, and the two shifted words then ORed together.

The only operations of any signifigance which are not included in the above paragraph are either things such as multiply or independent indexibility, which were never intended for 8-bit operation because of their expense, and mode control.

To program mode control, without actually having it in the hardware, requires manufacturing masks, which blank out whole 8-bit segments of the 64-bit word, in response to decision bits which usually will show up in the sign-bit position of the 8-bit words.

This programming, while facilitated by the one-clock-time barrel, by the complete set of Boolean operations, and by the fast single-bit instructions, will not be trivial

#### COMMON DATA PATHS

This section describes the various paths by which information is transferred between the PE and its memory both to the input-output interface, and to the control unit. As a result of the conflicting requirements on transfer rates, frequency of use, and destination, there are three segments of the equipment provided for data transfer. These segments are an input-output buffer, a memory access buffer with each control unit, and direct lines from the control unit to and from the PE. The rest of this section describes this hardware in terms of its use in each class of signals which must be handled into and out of each PE.

# Input-Output Buffering

Present plans are to provide an input-output buffer of 4096 bits for each quadrant of the array. Each bit of the I/O buffer has connection to one bit of the memory data register of one PE. When data is to be transferred to or from a PE memory from the I/O buffer, one memory cycle is taken from PE operations, and all 64 PE's insert one data word into their memory at that memory cycle.

Data is transferred across the external interface of the I/O buffer in word sizes appropriate to the device found at that interface. The external device may be a buffer memory with very long words, say 4096 bits each. In this case, I/O operations are accomplished by stealing one PE memory cycle from the array for each cycle of the external buffer memory. On the other hand, the external device could conceivably be a device of lesser word size, 512/bits per word, for example, in which case an independent loading and unloading control is required to assemble the shorter external words into the 4096-bit word in the I/O buffer. This independent control communicates with the array control unit both to steal memory cycles, and to report I/O complete when a whole block of data has been successfully transferred.

The design of this interface is almost independent of the rest of ILLIAC IV.

It is not the intent of this section of this report to discuss the design of the independent I/O control unit, as this design is dependent upon matters discussed elsewhere in this report.

# From Control Unit to Processing Element

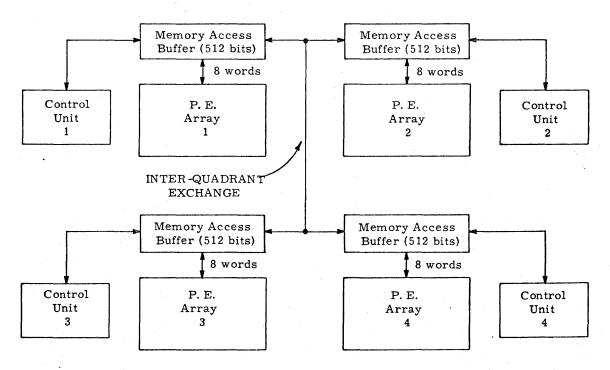

Data for the use of the PE, data to be stored in the PE memory for the control unit's own use, and commands for the PE are transmitted from the control unit to the processing element. Common data lines from the control unit are used for data which goes from the control unit to the PE, whether this data is for PE use or for the control unit's private use. To avoid continually interrupting PE operations for data fetches and stores which are related to control unit purposes, many words should be fetched and stored in parallel. A reasonable compromise between amount of hardware and interference with PE operation appears to be no more than 32 words of data transmitted to the PE array in parallel. Further discussion of the buffer size is found below. We plan to provide 32 words of buffering. Of these 32 words, eight are assigned to each quadrant. A block diagram of the system for handling data is shown in figure 2-6 (page 2-10).

It is simplest to describe operation by starting with the isolated quadrant. Eight words of data are transmitted to the memory access buffer from the control unit. This transmission is overlapped with PE operations provided that the program is such that the requirement for transmitting data can be recognized far enough ahead of time. This will generally always be recognizable ahead of time when the data is simply to be stored in memory. One clock time per word is expected to be required, since the data paths within the control unit are expected to be typically one word wide. Each word in the memory access buffer has access to a column in the array. The eight words have simultaneous access to one element in every column, namely a row. As a result, the eight words can be transmitted in parallel to every row in the array. If data is to be stored in memory, one row accepts the data.

If data is being broadcast, rows receive the data. In this case, the eight words of data are eight copies of a single word which originated in the control unit.

When the array is operating as a coherent whole, all four control units operate on the same program string and data in parallel, and have identical internal states. Out of a package of 32 words to be sent, the first eight can be derived from information supplied by the first control unit, the second eight can be derived from information supplied by the second control unit, and so on. Likewise, when broadcasting data, the four control units will have four identical copies of the word to be broadcast, each of the four is copied eightfold into the memory access buffers, and each of the resulting 32 copies is then used to drive eight PE's.

Also transmitted from the control unit to all PE's in parallel are control signals. These control signals, are identical for all PE's. Retiming considerations will demand that there be a flip-flop in the control unit for each such line. Present planning calls for a receiver per cabinet for each such signal, and eight PE's per cabinet.

Addresses must also be issued from the control unit to all PE's. These will use the least significant 12 bits of each word in the memory access register, and the broadcast data bus.

Issuing of addresses and broadcasting of data require a fixed delay of several clock times. The design of the microsequences as manufactured by the control unit is such as to allow for this constant delay.

# From Processing Element to Control Unit

When data is fetched from PE to control unit in the isolated quadrant, the mechanism is the reverse of the process described above for disseminating data. Namely, the information is collected in the form of a single word from each single column of the quadrant, and the eight words from each row are then transmitted to the control unit. For the instruction "store to broadcast register," the eight words are ORed together to form a single word in the control unit, very like a broadcast in reverse.

When data, or program string, are being fetched in 32-word packages from the united array an additional complication sets in, since each one of the memory access buffers contains only a quarter (eight words) of the 32-word package and each control units wants all 32 words. In this case it will be necessary to transfer data around among the memory access buffers until each quarter package of eight words has shown up once in each of the eight-word memory access buffers.

Single word fetching makes use of the same paths by disabling all but one of the words being received.

Also entering the control unit are lines from each of the mode register flip-flops in the PE's. To the control unit of one quadrant, a bit in the mode register appears as a 64-bit register to the control unit, which may be set, read, compared with other registers available to the control unit, etc. When operating in united mode, control units must cooperate in the sensing of the state or mode registers. For example, a "jump on any bit equal to ONE" means to jump if any bit in any one of the four 64-bit registers involved is ONE. Since all four control units run the same program instructions at the same time, only twelve wires, one to communicate between each pair of control units, are required to secure the necessary cooperation.

# Evaluation

Some of the above described data-transferring procedures take more time than one might at first expect. One 250-nsec. memory cycle is required to load the memory access buffer. This memory cycle interferes with the action of the PE only insofar as the PE memory or memory data buffer is required.

The memory access buffer for a single quadrant can be unloaded into the appropriate area in program lookahead or local data buffer in eight clock times. However, these potentially interfere with other used of program lookahead or local data buffer. With proper implementation of the controls, these eight clock times can be largely hidden by being taken from otherwise idle time in the two buffer areas in the control unit.

When the array is in united operation, one must count not only 32 clock times rather than 8, one also must transfer the data from one memory access buffer to another.

If cables of up to 30 or 40 feet long separate the memory access buffers, then the time to transfer data from one memory access buffer to another may well be three clock times, and three transfers are needed. The conclusion is that as much as 41 clock times are needed to transfer the 32 words, read in one memory cycle time, into the appropriate areas of the four control units. Seven clock cycles in each memory cycle is a likely design choice. In this case, 41 clock cycles represents 1.46 microseconds. This 1.46 microseconds is overlapped with other operations as long as a reservoir of instructions for PE operation can be maintained in the control unit.

However, this 1.46 microseconds often gets in the way when loading the program lookahead. It is a penalty to be taken whenever the program jumps to a location not contained in program lookahead. Further, the coarser block size means that loops between 32 and 64 words long will less often be found within the program lookahead, and program fetching will take place more often when the block which is fetched is larger. Large block size also interferes with broadcast operations, since a larger delay occurs between the instruction to fetch a block of data to the data buffer and the first opportunity to broadcast one of those words, when blocks are larger.

Optimum block size is that which finds the best tradeoff between interference with the operation of the PE's in the array, and slowing of operations in the control unit. Block sizes of 8, 16, and 32 words are easily available with minor modifications of the structure here described, and a choice of a smaller block size than the 32 words here proposed can be easily made during the early, design months of the next contract.

# MODE

# Introductory Considerations

Each PE is supplied with a mode register, which it can change as the result of tests, and which the control unit can set at will. Instructions will be executed or not as a result of the setting of the mode register. This arrangement is in lieu of branching at the PE level, since all PE's must share the common instruction stream, and therefore cannot independently execute transfers of control.

Modes should be remembered and recoverable. At the very least, each routine which one enters must be supplied with fresh capability for setting and changing its mode, while remembering the mode of the calling sequence. Actually, it seems that considerably more flexibility is desirable. In the limit, one could specify a particular mode register, out of some set of mode registers, for each instruction.

# The Problem

At issue is the question of the location of the backup storage of the noncurrent modes. The choice is between supplying back-up mode register storage in the PE's, or of supplying the control unit with the capability of reading, storing, and restoring the PE modes. The implementation of mode control is considerably different, depending on the results of this choice, so that we are really choosing between two different systems for controlling PE operations in response to mode.

# Back-Up Storage In The Control Unit

The first system to discuss is that with back-up storage for other than current modes in the control unit. In this system, only one mode register's worth of flip-flops are in the PE, and the setting of the mode register, for which a given instruction will be executed in a specific PE is known at the time of that instruction. Either four bits accompany the instruction, specifying which of the possible modes permit the execution of the instruction, or else a pre-existing decision, based on the content of the mode register, controls the execution or nonexecution of instructions in the PE. Bit economy in the instruction stream favors the latter, if mode is not to change at every instruction. A decision based on speed also favors separation of the mode decision from the execution of the instruction, since then less control gating is involved for the individual instruction at the PE.

One of the savings in speed of the ILLIAC IV type of computer ought to lie in the fact that the subcommand matrix of a normal computer finds itself mostly in the control unit, so that the instruction decoding and timing which consumes one clock time per instruction in most computers can be spent in the control unit, overlapped with useful arithmetic work in the PE. For most complete overlap, the PE has an "on-off" flip-flop to control the execution or nonexecution of the next instruction. Individual instructions in such a scheme will never wait for the decoding of mode information before they can start and noninterfering microsequences can freely overlap. Occasionally a one-clock-time instruction would be needed to change the setting of the "on-off" flip-flop in response to some new interpretation of the mode register.

The "on-off" flip-flop also must respond (sometimes) to arithmetic overflow as well as to programmed tests which change the mode bits. There is an overflow flip-flop which appears to the control unit much like third mode bit.

In this system there are therefore four flip-flops per effective PE with mode-like functions. Thus there are four flip-flops per 32-bit word, or eight flip-flops per actual PE, two programmatically specifiable mode bits, the overflow flip-flop, and the "enable-disable" flip-flop. There are PE instructions to set or reset each mode bit in response to programmed tests. Each bit in the PE appears to the control unit as a 64-bit word, since there are 64 PE's per control unit. There are instructions to read, save, and set these words, the instructions being control unit instructions rather than PE instructions. The control unit is provided with high-speed register storage for such saving. It is also provided with logical instructions to manipulate the modes, namely AND, OR, and COMPLEMENT instructions which can operate on the words formed from the mode register bits. Jump instructions in the control unit would test mode bits (either "any mode bit" or "all mode bits"). They would also test old modes stored in the control unit.

This system thus has a reservoir of old modes which can be reactivated on short notice. This back-up is in the control unit. Response to old mode settings is effected in one clock time by setting the "on-off" flip-flop in each PE. The instruction stream has no mode field per instruction, but does have mode-manipulating instructions, which are decoded by the control unit in parallel with the issuing of instructions to the PE.

Storage of old modes in the control unit is backed up further by the storage of words from old mode registers back to memory. It is assumed that the control unit has some means of addressing memory, both for read and write.

# Back-Up Storage In The Processing Element

The second system we discuss is that with back-up storage of old modes assigned to the PE's. In this system, where several modes are stored in the PE, a method must be chosen for choosing the applicable mode for any given stream of instructions. A settable pointer could be used, and the pointer setting changed on command from the control unit, in between actual processing instructions. Using the pointer, the operation would be fully equivalent to operation with back-up storage in the control unit except for the location of the stored bits. When a mode register address is visued with each instruction, more flexibility is obtained. As described to us, the system was used with six mode bits with each instruction: Two bits of mode register address, and four bits to interpret the contents of that register.

Arithmetic overflows are lost in the implementation unless tested for immediately by means of a jump instruction in the control unit. They cannot influence mode directly, although, clearly, when tested, they can be used to control modes. Even with back-up storage of modes in the PE's, some means of setting new modes under control unit control is required. Whether a path directly from control unit to PE for loading the mode registers is needed, or whether indirect methods suffice, has not yet been determined.

Each instruction in the PE must therefore look to the mode register for conditions against which execution is made conditional. Some instructions are made one clock time longer because of this. Furthermore, no overlapping of non-interfering microsequences appears possible.